### TENTATIVE SPECIFICATIONS

PRODUCT NAME:

LC706200CM

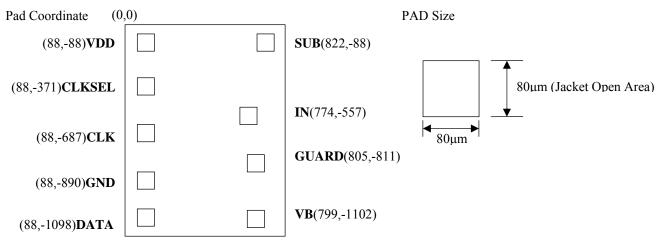

- 1. Case Outline: Wafer Ring(8inch)

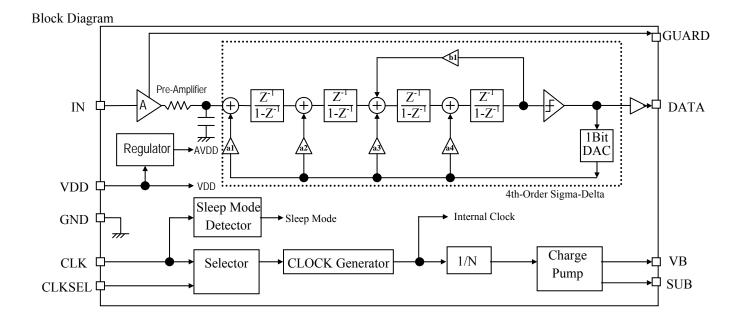

- 2. Function: Semiconductor IC for Digital Silicon Microphone includes Pre-amplifier and Sigma Delta Modulator and Charge Pump.

- 3. Application: Cellular phone and other

- 4. Absolute Maximum Ratings at Ta=25°C, GND = 0V

| Parameter                    | Symbol               | Pin Name   | Min  | Max     | Units                   |

|------------------------------|----------------------|------------|------|---------|-------------------------|

| Maximum power supply voltage | V <sub>DD</sub> max  | VDD        | -0.3 | +4.0    | V                       |

| Maximum input voltage        | V <sub>CLK</sub> max | CLK,CLKSEL | -0.3 | VDD+0.3 | V                       |

| Waximum input voltage        | V <sub>IN</sub> max  | IN         | -0.3 | VDD+0.3 | V                       |

| Maximum output voltage       | Vomax                | DATA       | -0.3 | VDD+0.3 | V                       |

| Operating temperature range  | Ta                   |            | -30  | 70      | $^{\circ}\!\mathbb{C}$  |

| Storage temperature range    | Tstg                 |            | -40  | 85      | $^{\circ}\! \mathbb{C}$ |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### 5. Circuit Parameters

|    | Parameter              | Symbol | Pin Name | Test Condition | Min | Тур | Max | Units |

|----|------------------------|--------|----------|----------------|-----|-----|-----|-------|

| In | put capacitance of die | Cin    | IN       |                |     | 0.4 |     | pF    |

Note: IN-Pin has a limited protection against ESD. Value of IN-Pin is proven by design.

6. DC Electrical Characteristics Ratings at Ta=25°C,VDD=3.3V,GND=0V,Fclk=2.4MHz, Fduty=50%

| Parameter                                                | Symbol | Pin Name            | Condition        | Min      | Тур | Max      | Units |

|----------------------------------------------------------|--------|---------------------|------------------|----------|-----|----------|-------|

| Power supply voltage                                     | VDD    | VDD                 |                  | 1.64     | 3.3 | 3.6      | V     |

| Power consumption (IO Power consumption is not Included) | IDD    | VDD                 | VDD=3.3V         |          | 800 |          | uA    |

| Standby Current                                          | ISTBY  | VDD                 | VDD=3.3V         |          |     | 200      | nA    |

| Input/Output LOW level                                   | Viol   | CLK, DATA<br>CLKSEL | DATA: Iol=0.5mA  |          |     | 0.35×VDD | V     |

| Input/Output HIGH level                                  | Vioh   | CLK, DATA<br>CLKSEL | DATA: Ioh=-0.5mA | 0.65×VDD |     |          | V     |

| Charge pump voltage           | Vbias     | VB/SUB   | VDD=3.3V  |     | 10.5 |     | V     |

|-------------------------------|-----------|----------|-----------|-----|------|-----|-------|

| Parameter                     | Symbol    | Pin Name | Condition | Min | Тур  | Max | Units |

| Charge Pump voltage tolerance | Tolerance | VB/SUB   |           | -8  |      | +8  | %     |

7. AC Electrical Characteristics Ratings at Ta=+25°C,VDD=3.3V,GND=0V, Signal Frequency=1KHz, Measurement frequency=100Hz~20KHz, Fclk=2.4MHz,Fduty=50%, Bypass capacitor=0.1uF(VDD-GND)

| Parameter                                        | Symbol        | Pin Name | Condition                                                         | Min | Тур   | Max  | Units        |

|--------------------------------------------------|---------------|----------|-------------------------------------------------------------------|-----|-------|------|--------------|

| Clock Frequency ( Normal Operation )             | Fclk          | CLK      |                                                                   | 1   | 2.4   | 3.25 | MHz          |

| Clock Frequency ( Sleep Mode )                   | Fclk_SL       | CLK      |                                                                   |     |       | 1    | KHz          |

| Clock Duty                                       | Fduty         | CLK      |                                                                   | 40  |       | 60   | %            |

| Over Sampling Ratio                              | OSR           |          |                                                                   |     | 50    |      |              |

| Maximum Input Voltage (Input Full Scale Voltage) | Vin           | IN       | 0dBFS<br>(=120dBSPL)                                              |     | 158.5 |      | mVrms        |

|                                                  | THD_0         | DATA     | Vout=0dBFS<br>(= 120dBSPL)<br>(= 158.5mVrms)                      |     |       | 10   | %<br>(THD)   |

| THD / THD+N                                      | THD+N_1<br>※1 | DATA     | Vout=-5dBFS<br>(= 115dBSPL)<br>(= 89.1mVrms)<br>1KHz Sin-Wave     |     |       | 5    | %<br>(THD+N) |

|                                                  | THD+N_2<br>※1 | DATA     | Vout=-20dBFS<br>(= 100dBSPL)<br>(= 15.8mVrms)<br>50-4KHz Sin-Wave |     |       | 1    | %<br>(THD+N) |

| Digital Noise Floor                              | DNF1          | DATA     | Bandwidth 20KHz<br>A-weighted                                     |     | -87   |      | dBFS         |

| PSRR ※1                                          | PSRR          | DATA     | 217Hz Square,<br>10MHz-Broadband<br>Noise, 100mVpp                |     | -70   |      | dBFS         |

| Transfer function *2                             | TF1           | DATA     |                                                                   |     | 18    |      | dB           |

| Wake Up Time **1                                 | WUT           | CLK      | Fclk=2.4MHz                                                       |     |       | 10   | ms           |

| Fall Asleep Time **1                             | FAT           |          | Fclk=1KHz                                                         |     |       | 10   | ms           |

Note1: \*\*1 are Reference data:No measurement.

Note2: \*\*2 Each product has been designed with performance of +/-0.5dB tolerance for transfer function however it's not checked in outgoing inspection.

Note3: Input Full Scale Voltage 0dBFS is equivalent to 120dBSPL (= 158.5mVrms).

Note4: SNR Input Level Condition is -26dBFS (= 7.9mVrms, 94dBSPL, 1Pa).

( - ) <u>No. 2</u>

#### Pin Descriptions

| No. | Pin Name | Function                                                                                                                                                                                         | I/O    | Pin conditions |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| -   | GND      | Ground                                                                                                                                                                                           | _      | _              |

| -   | VDD      | Power Supply                                                                                                                                                                                     | _      | _              |

| -   | GUARD    | Connect to GUARD of MEMS                                                                                                                                                                         | _      | _              |

|     | SUB      | Connect to SUB of MEMS                                                                                                                                                                           |        | _              |

| -   | DATA     | PDM Data Output                                                                                                                                                                                  | output |                |

| -   | CLKSEL   | CLK Select signal input Case1: When CLKSEL is LOW, PDM data is outputted in sync with negative edge of CLK. Case2: When CLKSEL is HIGH, PDM data is outputted in sync with positive edge of CLK. | Input  |                |

| -   | CLK      | Clock input                                                                                                                                                                                      | Input  |                |

| -   | VB       | Charge Pump Voltage Output                                                                                                                                                                       | output | -              |

| -   | IN       | Audio signal input                                                                                                                                                                               | Input  |                |

- ) <u>No. 3</u>

No. 4

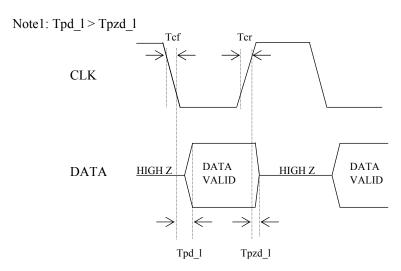

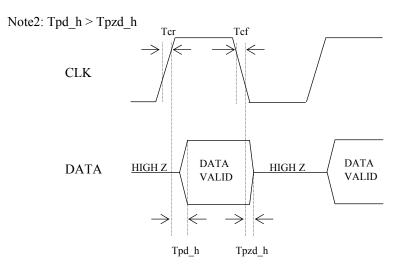

## **Switching Characteristics**

$(Ta=+25^{\circ}C, VDD=1.8V,GND=0V,Fclk=2.4MHz,Fduty=50\%)$

Case1: CLKSEL=LOW

| Parameter         | Symbol | Pin Name | Condition              | Min | Тур | Max | Units |

|-------------------|--------|----------|------------------------|-----|-----|-----|-------|

| Clock Rise Time   | Tcr    | CLK      |                        |     |     | 10  | ns    |

| Clock Fall Time   | Tcf    | CLK      |                        |     |     | 10  | ns    |

| Output Data Delay | Tpd_1  | DATA     | CL=13pF,RL=1M $\Omega$ | 20  | 31  | 40  | ns    |

| Output Hi-Z Delay | Tpzd_1 | DATA     | CL=13pF,RL=1M $\Omega$ | 0   | 8   | 15  | ns    |

$Case 2: CLKSEL {=} HIGH$

| Parameter         | Symbol | Pin Name | Condition              | Min | Тур | Max | Units |

|-------------------|--------|----------|------------------------|-----|-----|-----|-------|

| Clock Rise Time   | Ter    | CLK      |                        |     |     | 10  | ns    |

| Clock Fall Time   | Tcf    | CLK      |                        |     |     | 10  | ns    |

| Output Data Delay | Tpd_h  | DATA     | CL=13pF,RL=1M $\Omega$ | 20  | 31  | 40  | ns    |

| Output Hi-Z Delay | Tpzd h | DATA     | CL=13pF,RL=1M $\Omega$ | 0   | 8   | 15  | ns    |

( - )

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

- ) <u>No. 5</u>

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio Amplifiers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

LV47002P-E NCP2811AFCT1G NCP2890AFCT2G SSM2377ACBZ-R7 IS31AP4915A-QFLS2-TR NCP2820FCT2G TDA1591T

TDA7563AH SSM2529ACBZ-R7 MAX9890AETA+T TS2012EIJT NCP2809BMUTXG NJW1157BFC2 SSM2375CBZ-REEL7

IS31AP4996-GRLS2-TR STPA002OD-4WX NCP2823BFCT1G MAX9717DETA+T MAX9717CETA+T MAX9724AEBC+TG45

LA4450L-E IS31AP2036A-CLS2-TR MAX9723DEBE+T TDA7563ASMTR AS3561-DWLT SSM2517CBZ-R7 MP1720DH-12-LF-P

SABRE9601K THAT1646W16-U MAX98396EWB+ PAM8965ZLA40-13 BD37532FV-E2 BD5638NUX-TR BD37512FS-E2 BD37543FS

E2 BD3814FV-E2 TPA3140D2PWPR TS2007EIJT IS31AP2005-DLS2-TR SSM2518CPZ-R7 AS3410-EQFP-500 FDA4100LV

MAX98306ETD+T TS4994EIJT NCP2820FCT1G NCP2823AFCT2G NCS2211MNTXG CPA2233CQ16-A1 OPA1604AIPWR

OPA1612AQDRQ1