# ON Semiconductor®

**CMOSIC**

# RDS(RBDS) Demodulation IC

http://onsemi.com

#### Overview

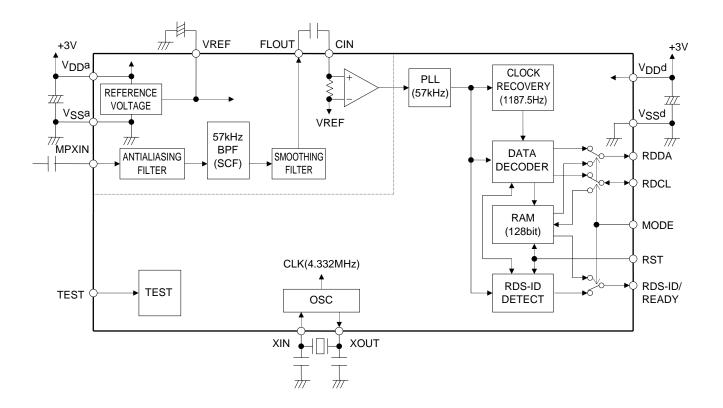

The LC72725KV is IC that implement the signal processing required by the European Broadcasting Union RDS (Radio Data System) standard and by the US NRSC (National Radio System Committee) RBDS (Radio Broadcast Data System) standard. This IC include band-pass filter, demodulator, and data buffer on chip. RDS data can be read out from this on-chip memory by external clock input in slave operation mode.

#### **Functions**

- Bandpass filter: Switched capacitor filter (SCF)

- RDS Demodulation: 57KHz carrier and RDS data clock regeneration, biphase decode, differential decode.

- Buffer: 128 bit (about 100ms) can be restored in the on-chip data buffer RAM.

- Data output: Master or slave output mode can be selected.

- RDS-ID: Detect RDS signal which can be reset by RST signal input.

- Standby control: Crystal oscillator can be stopped.

- Fully adjustment free

- Low Voltage

#### **Specifications**

**Absolute Maximum Ratings** at Ta = 25°C,  $V_{SS}d = V_{SS}a = 0V$

| Parameter              | Symbol                   | Pin Name                               | Conditions                               | Ratings                       | Unit |

|------------------------|--------------------------|----------------------------------------|------------------------------------------|-------------------------------|------|

| Maximum supply voltage | V <sub>DD</sub> max      | V <sub>DD</sub> d, V <sub>DD</sub> a * | V <sub>DD</sub> a≤V <sub>DD</sub> d+0.3V | -0.3 to +6.5                  | V    |

| Maximum input voltage  | V <sub>IN</sub> 1<br>max | TEST, MODE, XIN, RDCL, RST             | -0.3 to V <sub>DD</sub> d+0.3            |                               | V    |

|                        | V <sub>IN</sub> 2<br>max | MPXIN, CIN                             |                                          | -0.3 to V <sub>DD</sub> a+0.3 | V    |

| Maximum output voltage | V <sub>O</sub> 1 max     | RDS-ID(READY)                          |                                          | -0.3 to +6.5                  | V    |

|                        | V <sub>O</sub> 2 max     | XOUT, RDDA, RDCL                       |                                          | -0.3 to V <sub>DD</sub> d+0.3 | V    |

|                        | V <sub>O</sub> 3 max     | FLOUT                                  |                                          | -0.3 to V <sub>DD</sub> a+0.3 | V    |

| Maximum output current | I <sub>O</sub> 1 max     | XOUT, FLOUT, RDDA, RDCL                |                                          | +2.0                          | mA   |

|                        | I <sub>O</sub> 2 max     | RDS-ID(READY)                          |                                          | +8.0                          | mA   |

<sup>\*</sup> VDDa≤VDDd+0.3V

Continued on next page.

Continued from preceding page.

| Parameter                   | Symbol | Pin Name | Conditions                     | Ratings     | Unit |

|-----------------------------|--------|----------|--------------------------------|-------------|------|

| Allowable power dissipation | Pd max |          | Ta≤85°C                        | 100         | mW   |

| Operating temperature       | Topr1  |          | V <sub>DD</sub> = 2.7V to 5.5V | -20 to +70  | °C   |

|                             | Topr2  |          | V <sub>DD</sub> = 3.0V to 5.5V | -40 to +85  | °C   |

| Storage temperature         | Tstg   |          |                                | -40 to +125 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Allowable Operating Ranges at Ta = -20 to +70 °C, $V_{SS}d = V_{SS}a = 0$ V, $V_{DD}d = V_{DD}a = 2.7$ V to 5.5V to 5.5V and 5.5V to 5.5

$Ta = -40 \text{ to } +85^{\circ}\text{C}, V_{SS}d = V_{SS}a = 0\text{V}, V_{DD}d = V_{DD}a = 3.0\text{V to } 5.5\text{V}$

| B                                         | 0 1 1             | D'. N                                | Name Conditions   |                      | Ratings |                      |       |  |

|-------------------------------------------|-------------------|--------------------------------------|-------------------|----------------------|---------|----------------------|-------|--|

| Parameter                                 | Symbol            | Pin Name                             |                   | min                  | typ     | max                  | unit  |  |

| Supply voltage                            | V <sub>DD</sub> 1 | V <sub>DD</sub> d, V <sub>DD</sub> a | Ta = -20 to +70°C | 2.7                  |         | 5.5                  | V     |  |

|                                           | V <sub>DD</sub> 2 | V <sub>DD</sub> d, V <sub>DD</sub> a | Ta = -40 to +85°C | 3.0                  |         | 5.5                  | V     |  |

| Input high-level voltage                  | V <sub>IH</sub> 1 | TEST, MODE, RST                      |                   | 0.7V <sub>DD</sub> d |         | 6.5                  | V     |  |

|                                           | V <sub>IH</sub> 2 | RDCL                                 |                   | 0.7V <sub>DD</sub> d |         | $V_{DD}d$            | V     |  |

| Input low-level voltage                   | V <sub>IL</sub>   | TEST, MODE, RST,<br>RDCL             |                   | 0                    |         | 0.3V <sub>DD</sub> d | ٧     |  |

| Output voltage                            | V <sub>O</sub> 1  | RDDA, RDCL                           |                   |                      |         | V <sub>DD</sub> d    | V     |  |

|                                           | V <sub>O</sub> 2  | RDS-ID(READY)                        |                   |                      |         | 6.5                  | V     |  |

| Input amplitude                           | VIN               | MPXIN                                | f = 57±2kHz       | 1.6                  |         | 50                   | mVrms |  |

|                                           | VXIN              | XIN                                  |                   | 400                  |         | 1500                 | mVrms |  |

| Guaranteed crystal oscillator frequencies | Xtal              | XIN, XOUT                            | Cl≤120Ω           |                      | 4.332   |                      | MHz   |  |

| Crystal oscillator operating range        | TXtal             | XIN, XOUT                            | Fo = 4.332MHz     |                      |         | ±100                 | ppm   |  |

| RDCL setup time                           | tCS               | RDCL, RDDA                           |                   | 0                    |         |                      | μs    |  |

| RDCL high-level time                      | tCH               | RDCL                                 |                   | 0.75                 |         |                      | μs    |  |

| RDCL low-level time                       | tCL               | RDCL                                 |                   | 0.75                 |         |                      | μs    |  |

| Data output time                          | tDC               | RDCL, RDDA                           |                   |                      |         | 0.75                 | μs    |  |

| READY output time                         | tRC               | RDCL, READY                          |                   |                      |         | 0.75                 | μs    |  |

| READY low-level time                      | tRL               | READY                                |                   |                      |         | 107                  | ms    |  |

# **Electrical Characteristics** for the Allowable Operating Ranges

| Parameter                    | 0                 | I Din Nama                          | 0 - 12                                      |                       | Ratings              |      |      |

|------------------------------|-------------------|-------------------------------------|---------------------------------------------|-----------------------|----------------------|------|------|

| Parameter                    | Symbol            | Pin Name                            | Conditions                                  | min                   | typ                  | max  | unit |

| Input resistance             | Rmpxin            | MPXIN-V <sub>SS</sub> a             | f = 57kHz                                   |                       | 100                  |      | kΩ   |

|                              | Rcin              | CIN-V <sub>SS</sub> a               | f = 57kHz                                   |                       | 100                  |      | kΩ   |

| Internal feedback resistance | Rf                | XIN                                 |                                             |                       | 1.0                  |      | МΩ   |

| Center frequency             | fc                | FLOUT                               |                                             | 56.5                  | 57.0                 | 57.5 | kHz  |

| -3dB band width              | BW-3dB            | FLOUT                               |                                             | 2.5                   | 3.0                  | 3.5  | kHz  |

| Gain                         | Gain              | MPXIN-FLOUT                         | f = 57kHz                                   | 28                    | 31                   | 34   | dB   |

| Stop band attenuation        | Att1              | FLOUT                               | $\Delta f = \pm 7kHz$                       | 30                    |                      |      | dB   |

|                              | Att2              | FLOUT                               | F<45kHz, f>70kHz                            | 40                    |                      |      | dB   |

|                              | Att3              | FLOUT                               | F<20kHz                                     | 50                    |                      |      | dB   |

| Reference voltage output     | Vref              | Vref                                | V <sub>DD</sub> a = 3V                      |                       | 1.5                  |      | V    |

| Hysteresis                   | VHIS              | TEST, MODE, RST,<br>RDCL            |                                             |                       | 0.1V <sub>DD</sub> d |      | ٧    |

| Output low-level voltage     | V <sub>OL</sub> 1 | RDDA, RDCL                          | I = 2mA                                     |                       |                      | 0.4  | V    |

|                              | V <sub>OL</sub> 2 | RDS-ID(READY)                       | I = 8mA                                     |                       |                      | 0.4  | V    |

| Output high-level voltage    | Vон               | RDDA, RDCL                          | I = 2mA                                     | V <sub>DD</sub> d-0.4 |                      |      | V    |

| Input high-level current     | I <sub>IH</sub> 1 | TEST, MODE, RST,<br>RDCL            | V <sub>I</sub> = 6.5V                       |                       |                      | 5.0  | μΑ   |

|                              | I <sub>IH</sub> 2 | XIN                                 | $V_I = V_{DD}d$                             | 2.0                   |                      | 11   | μΑ   |

| Input low-level current      | I <sub>IL</sub> 1 | TEST, MODE, RST,<br>RDCL            | V <sub>I</sub> = 0V                         |                       |                      | 5.0  | μА   |

|                              | I <sub>IL</sub> 2 | XIN                                 | V <sub>I</sub> = 0V                         | 2.0                   |                      | 11   | μА   |

| Output off leakage current   | IOFF              | RDS-ID(READY)                       | V <sub>O</sub> = 6.5V                       |                       |                      | 5.0  | μΑ   |

| Current drain                | I <sub>DD</sub>   | V <sub>DD</sub> d+V <sub>DD</sub> a | $V_{DD}d+V_{DD}a$<br>$(V_{DD}d=V_{DD}a=3V)$ |                       | 5                    |      | mA   |

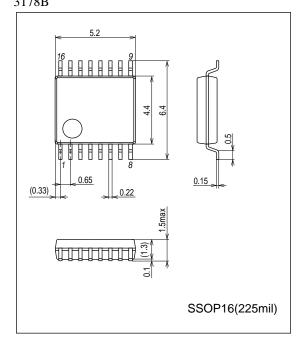

# **Package Dimensions**

unit: mm (typ) 3178B

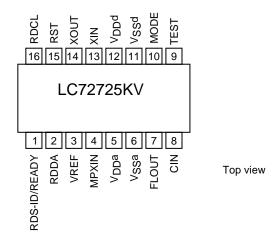

#### **Pin Assignment**

#### **Block Diagram**

# **Pin Descriptions**

|         | Cription          |        |                                                                                                                                 |                                                      |

|---------|-------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Pin No. | Pin Name          | I/O    | Function                                                                                                                        | Pin Circuit                                          |

| 3       | VREF              | Output | Reference voltage output (Vdda/2)                                                                                               | V <sub>DD</sub> a V <sub>SS</sub> a                  |

| 4       | MPXIN             | Input  | Baseband (multiplexed) signal input                                                                                             | V <sub>DD</sub> d<br>W-<br>V <sub>SS</sub> d         |

| 7       | FLOUT             | Output | Subcarrier output (filter output)                                                                                               |                                                      |

| 8       | CIN               | Input  | Subcarrier input (comparator input)                                                                                             | V <sub>DD</sub> a A V <sub>SSa</sub> /// VREF        |

| 5       | V <sub>DD</sub> a | 1      | Analog system power supply (+3V)                                                                                                |                                                      |

| 6       | V <sub>SS</sub> a | -      | Analog system ground                                                                                                            |                                                      |

| 14      | XOUT              | Output | Crystal oscillator output (4.332MHz)                                                                                            | V <sub>DD</sub> d                                    |

| 13      | XIN               | Input  | Crystal oscillator input (external reference signal input)                                                                      | XIN VSSd XOUT                                        |

| 9       | TEST              |        | Test input                                                                                                                      |                                                      |

| 10      | MODE              |        | Read out mode (0:master, 1:slave)                                                                                               |                                                      |

| 15      | RST               |        | RDS-ID/RAM reset (active high)                                                                                                  | 777 V <sub>SS</sub> d                                |

| 2       | RDDA              | Output | RDS data output                                                                                                                 | ↑ V <sub>DD</sub> d<br>→ → → → → → V <sub>SS</sub> d |

| 16      | RDCL              | I/O    | RDS clock output (master mode) / RDS read out clock input (slave mode)                                                          | V <sub>DD</sub> d<br>V <sub>SS</sub> d               |

| 1       | RDS-ID/<br>READY  | Output | RDS reliability data output (High:data with high RDS reliability Low: data with low RDS reliability) READY output (active high) | V <sub>SS</sub> d ///                                |

| 12      | V <sub>DD</sub> d | -      | Digital system power supply (+3V)                                                                                               |                                                      |

| 11      | V <sub>SS</sub> d | -      | Digital system ground                                                                                                           |                                                      |

#### **Input/Output Data Format**

| TEST | MODE | Circuit Operation Mode                                    | RDCL Pin     | RDS-ID/READY Pin |

|------|------|-----------------------------------------------------------|--------------|------------------|

| 0    | 0    | Master read out mode                                      | Clock output | RDS-ID output    |

| 0    | 1    | Slave read out mode                                       | Clock input  | READY output     |

| 1    | 0    | Standby mode (crystal oscillator stopped)                 | -            | -                |

| 1    | 1    | IC test mode which is not available to user applications. | -            | -                |

|         | RST Pin                                                                      |

|---------|------------------------------------------------------------------------------|

| RST = 0 | Normal operation                                                             |

| RST = 1 | RDS-ID • demodulation circuit clear + READY • memory clear (when slave mode) |

| RDS-ID/READY Pin |                             |

|------------------|-----------------------------|

| Master mode      | RDS-ID output (Active-high) |

| Slave mode       | READY output (Active-high)  |

Note: RDS-ID(READY) pin is an n-channel open-drain output, and requires an external pull-up resistor to output data.

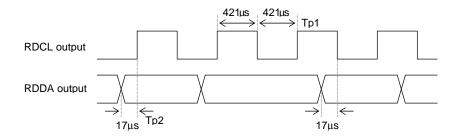

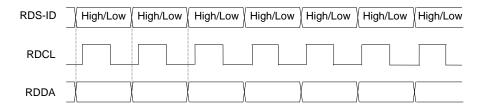

#### **RDCL/RDDA Output Timing in Master Mode**

#### **RDS-ID Output Timing**

Note: RDS-ID is High: data with high RDS reliability, Low: data with low RDS reliability

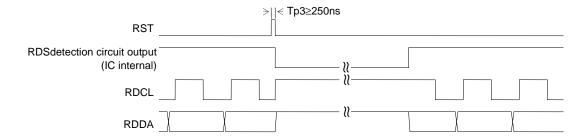

# **RST Operation in Master Mode**

Note: RDCL and RDDA outputs keep high level after input of RST until RDS detection circuit output is detected.

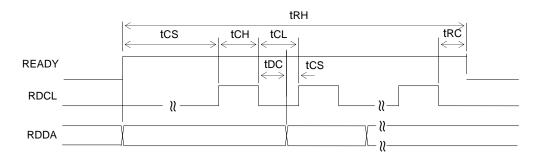

# **RDCL Operation in Slave Mode**

| Parameter             | Symbol Pin Name | Dia Nasa   | Pin Name Conditions | Ratings |     |      |      |

|-----------------------|-----------------|------------|---------------------|---------|-----|------|------|

|                       |                 | Pin Name   |                     | min     | typ | max  | unit |

| RDCL setup time       | tCS             | RDCL,RDDA  |                     | 0       |     |      | μs   |

| RDCL high-level time  | tCH             | RDCL       |                     | 0.75    |     |      | μs   |

| RDCL low-level time   | tCL             | RDCL       |                     | 0.75    |     |      | μs   |

| Data output time      | tDC             | RDCL,RDDA  |                     |         |     | 0.75 | μs   |

| READY output time     | tRC             | RDCL,READY |                     |         |     | 0.75 | μs   |

| READY high-level time | tRH             | READY      |                     |         |     | 107  | ms   |

- Notes: 1. RDCL input must be started after READY signal goes high. When READY signal is low, RDCL must be low level.

- 2. READY status must be checked after tRC time from RDCL is set low. If the READY status is high, then next read cycle can be continued. If the READY status is low, next RDCL clock input must be stopped.

- 3. If the above condition is satisfied, RDS data (RDDA) can be read out at both rising and falling edge of RDCL.

- 4. READY signal goes low after the last data is read out from on-chip memory. If one RDS data is stored in the memory, READY signal goes high again.

- 5. When the reception channel is changed, a memory and READY reset must be applied using RST input. If a reset is not applied, reception data from the previous channel may remain in memory. If RST input is applied, reception data is not stored in memory until the first RDS-ID is detected, and READY output goes high after the first RDS-ID is detected. After the first RDS-ID is detected, reception data is stored even if RDS-ID is not detected.

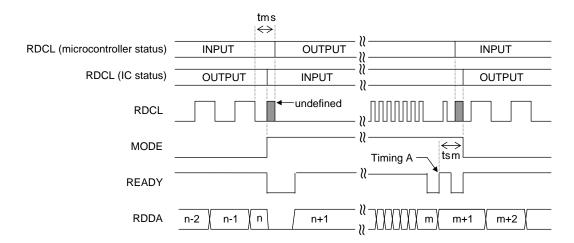

- 6. The readout mode may be switched between master and slave modes during readout.

Applications must observe the following points to assure data continuity during this operation.

- Data acquisition timing in master made

Data must be read on the falling edge of RDCL

- 2) Timing of the switch from master mode to slave mode

After the RDCL output goes low and the RDDA data has been acquired, the application must set MODE high immediately.

Then, the microcontroller starts output by setting the RDCL signal low.

The microcontroller RDCL output must start within 840µs (tms) after RDCL went low.

In this case, if the last data read in master mode was data item n, then data starting with item n+1 will be written to memory.

3) Timing of the switch from slave mode to master mode

After all data has been read from memory and READY has gone high, the application must then wait until READY goes low once again the next time (timing A in the figure), immediately read out one bit of data and input the RDCL clock.

Then, at the point READY goes high, the microcontroller must terminate RDCL output and then set MODE low.

The application must switch MODE to low within 840µs (tms) after READY goes low (timing A in the figure).

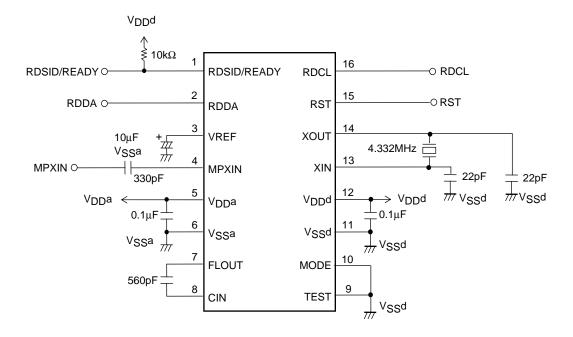

#### Sample Application Connection Circuit (for master mode operation)

Note: If the RST pin is unused, it must be connected to ground.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Modulator/Demodulator category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

LC72722PM-TLM-E HMC495LP3TR LT5571EUF#PBF LT5528EUF#PBF LT5502EGN#PBF THAT1510S08-U CMX589AD5

ADRF6821ACPZ AD630ADZ AD630ARZ AD630JNZ AD630KNZ AD8346ARUZ-REEL7 AD8339ACPZ AD8345ARE AD8345AREZ

AD8345AREZ-RL7 AD8347ARUZ AD8347ARUZ-REEL7 AD8348ARUZ AD8349AREZ AD8349AREZ-RL7 ADL5371ACPZ-R7

ADL5387ACPZ-WP ADL5387ACPZ-R7 ADL5372ACPZ-R7 ADL5373ACPZ-R7 ADA2200ARUZ-REEL7 AD8346ARUZ ADL5380

EVALZ ADL5382ACPZ-R7 AD630ARZ-RL ADL5375-15ACPZ-R7 ADL5380ACPZ-R7 ADL5375-05ACPZ-R7 AD8333ACPZ-WP

AD8341ACPZ-REEL7 ADRF6703ACPZ-R7 ADRF6750ACPZ-R7 ADRF6806ACPZ-R7 HMC1097LP4E HMC630LP3ETR

HMC500LP3ETR HMC495LP3ETR HMC500LP3E HMC630LP3E HMC631LP3E HMC795LP5E LT5516EUF LTC5598IUF