http://onsemi.com

#### **Bi-CMOS IC**

# Class-D Audio power Amplifier Power cell BTL 10W×2ch

#### Overview

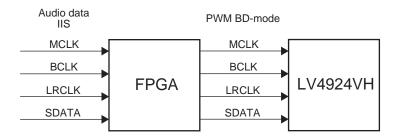

The LV4924VH is a 2-channel full-bridge driver for digital power amplifiers. It requires a PWM modulator IC in the previous stage. This IC is a power cell that takes in PWM signals as an input and is used to form a digital amplifier system for TVs, amusement equipment, and other such systems.

#### **Features**

- BTL output, class D amplifier system

- High-efficiency class D amplifier

- Muting function reduces impulse noise at power on / off

- Protection circuits incorporated for over-current, thermal, supply voltage drop, output offset detector

- Built-in bootstrap diodes

#### **Specification**

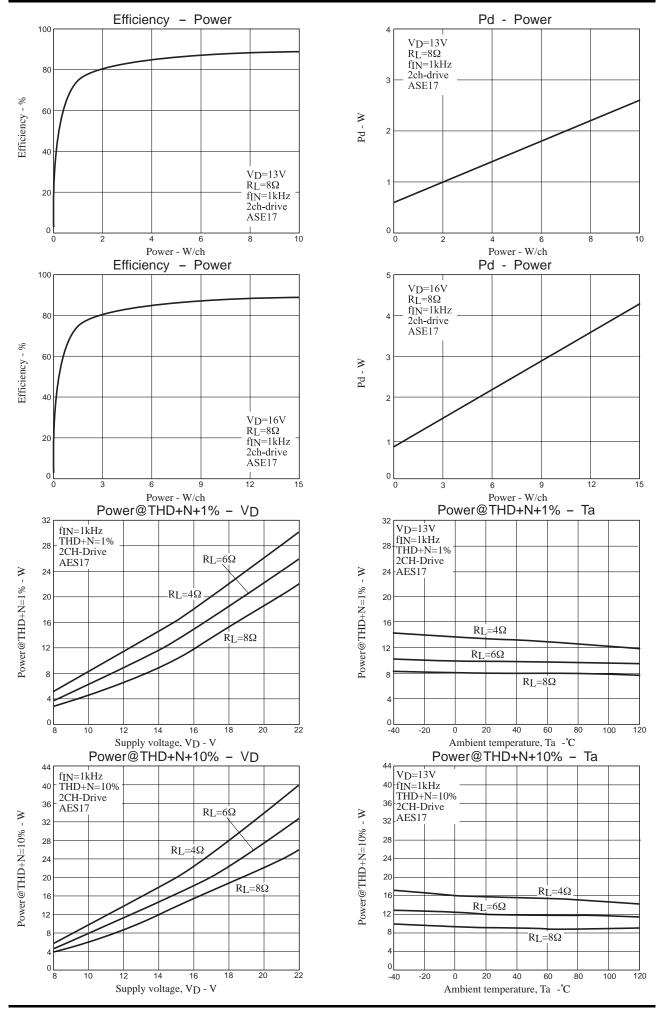

- Output 15W (V<sub>D</sub>=16V, R<sub>L</sub>=8Ω, f<sub>IN</sub>=1kHz, AES17, THD+N=10%)

- Output 10W ( $V_D$ =13V,  $R_L$ =8 $\Omega$ ,  $f_{IN}$ =1kHz, AES17, THD+N=10%)

- Efficiency : 89% (VD=13V, RL=8 $\Omega$ , f<sub>IN</sub>=1kHz, PO=10W)

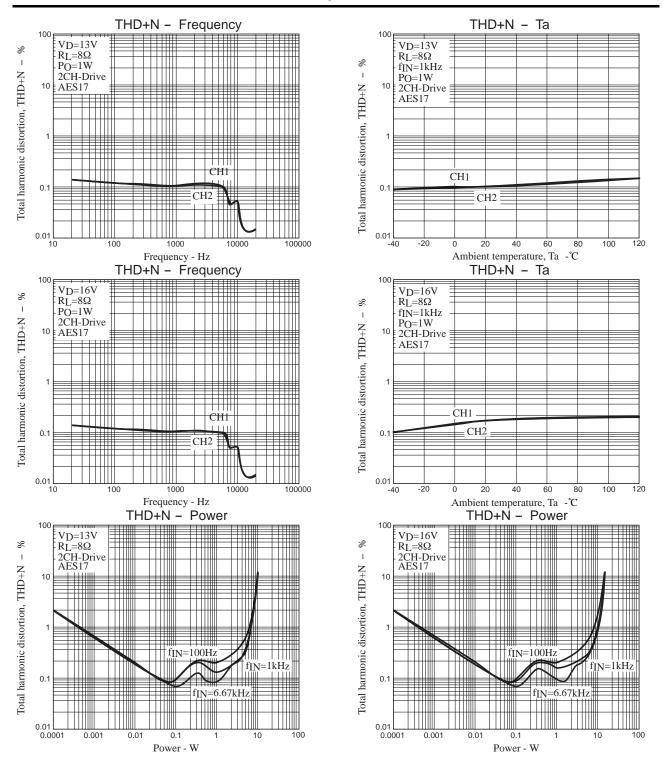

- THD+N : 0.1% (VD=13V, RL=8 $\Omega$ , f<sub>IN</sub>=1kHz, PO=1W, Filter: AES17)

#### Maximum Ratings / Absolute Maximum Ratings / Ta=25°C

| Parameter                    | Symbol   | Conditions                  | Ratings    | Unit |

|------------------------------|----------|-----------------------------|------------|------|

| Maximum supply voltage       | $v_D$    | Externally applied voltage  | 22         | V    |

| Maximum PWM pin voltage      | $V_{IN}$ | PWM_A1,PWM_A2,PWM_B1,PWM_B2 | 6          | V    |

| Maximum pull-up pin voltage  | Vpup max | NPN Open collector pin      | 20         | V    |

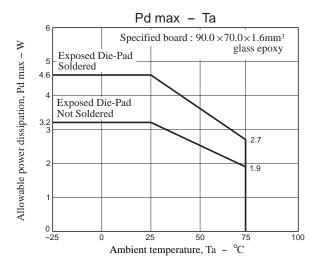

| Allowable power dissipation  | Pd max   | Exposed Die-pad Soldered *1 | 4.6        | W    |

| Maximum junction temperature | Tj max   |                             | 150        | °C   |

| Operating temperature        | Topr     |                             | -25 to 75  | °C   |

| Storage temperature          | Tstg     |                             | -50 to 150 | °C   |

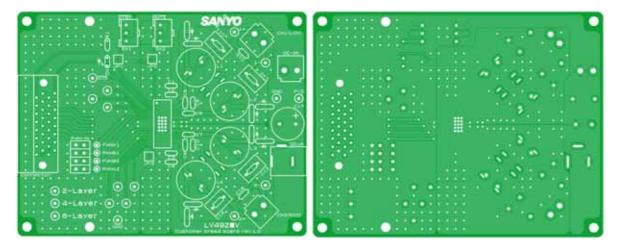

<sup>\*1</sup> Customer bread board rev.1.0: 90.0mm × 70.0 mm × 1.6 mm (two-layer) Material: glass epoxy

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Recommended Operating Range** at Ta = 25°C

| Parameter                   | Cumbal          | Conditions                  | Ratings |     |     | Unit |

|-----------------------------|-----------------|-----------------------------|---------|-----|-----|------|

| Parameter                   | Symbol          | Conditions                  | min     | typ | max | Unit |

| Recommended supply voltage  | V <sub>D</sub>  | Externally applied voltage  | 9       | 13  | 20  | V    |

| range                       |                 |                             |         |     |     |      |

| Recommended PWM pin voltage | V <sub>IN</sub> | PWM_A1,PWM_A2,PWM_B1,PWM_B2 | 0       | 3.3 | 5   | V    |

| Recommended pull-up supply  | Vpup            | NPN Open collector pin      | -       | -   | 18  | V    |

| voltage                     |                 |                             |         |     |     |      |

| Recommended load resistance | RL              | Speaker load                | 4       | 8   | -   | Ω    |

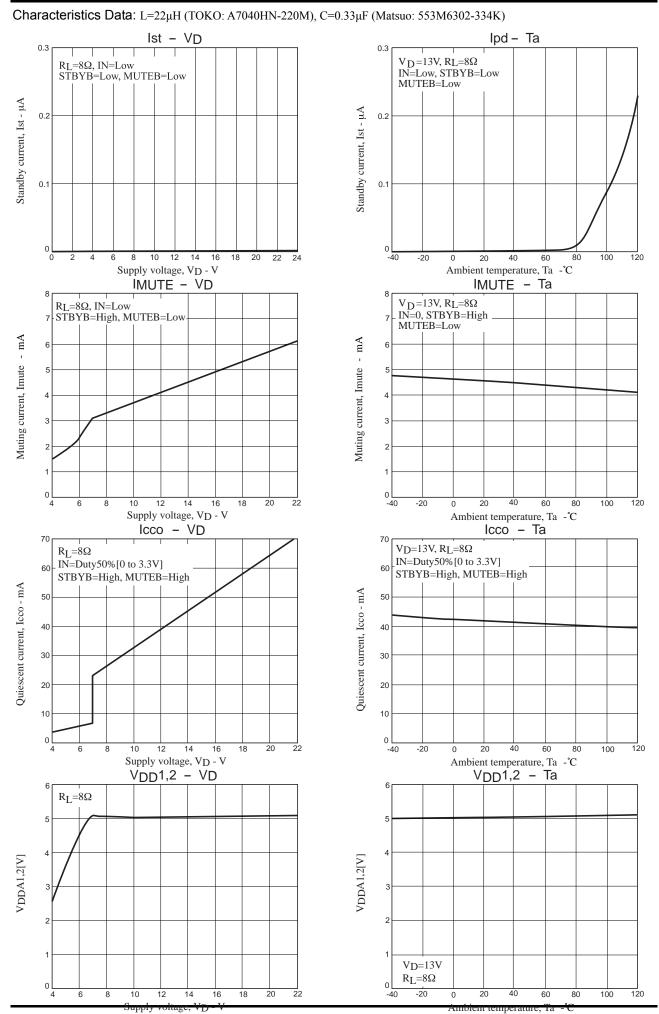

#### Electrical Characteristics Ta=25°C, VD=13V, RL=8Ω, L=22μH (ΤΟΚΟ: Α7040HN-220M), C=0.33μF (Matsuo: 553M6302-334K)

| Descriptor                 | O. wash ad       | O contitue of                                             | Ratings |     |     | 11-4 |  |

|----------------------------|------------------|-----------------------------------------------------------|---------|-----|-----|------|--|

| Parameter                  | Symbol           | Conditions                                                | min     | typ | max | Unit |  |

| Quiescent current          | Icco             | STBY=H, MUTE=H, f <sub>IN</sub> =384kHz, Duty=50%         | 30      | 38  | 45  | mA   |  |

| Current at MUTE            | Imute            | STBY=H, MUTE=L, V <sub>IN</sub> =GND                      | 2       | 4   | 6   | mA   |  |

| Standby current            | Ist              | STBY=L, MUTE=L, V <sub>IN</sub> =GND                      | -       | -   | 10  | μA   |  |

| H input voltage            | V <sub>I</sub> H | PWM_A, PWM_B, STBY, MUTE                                  | 2.3     | 1   | 5.5 | V    |  |

| L input voltage            | V <sub>I</sub> L | PWM_A, PWM_B, STBY, MUTE                                  | 0       | 1   | 1.0 | V    |  |

| H input current            | I <sub>I</sub> H | V <sub>IN</sub> =5V                                       | -       | -   | 60  | μA   |  |

| L input current            | I <sub>Ι</sub> L | V <sub>IN</sub> =GND                                      | -20     | 1   | -   | μA   |  |

| Output pin leakage current | IOFF             | NPN Open collector output OFF-stage 5.0V pull-up          | -       | -   | 1   | μA   |  |

| Output pin current         | IOL              | NPN Open collector output ON-stage, V <sub>OL</sub> =0.4V | 0.5     | -   | -   | mA   |  |

| Power Tr ON resistance *1  | Rds ON           | Id=1A                                                     | -       | 220 | -   | mΩ   |  |

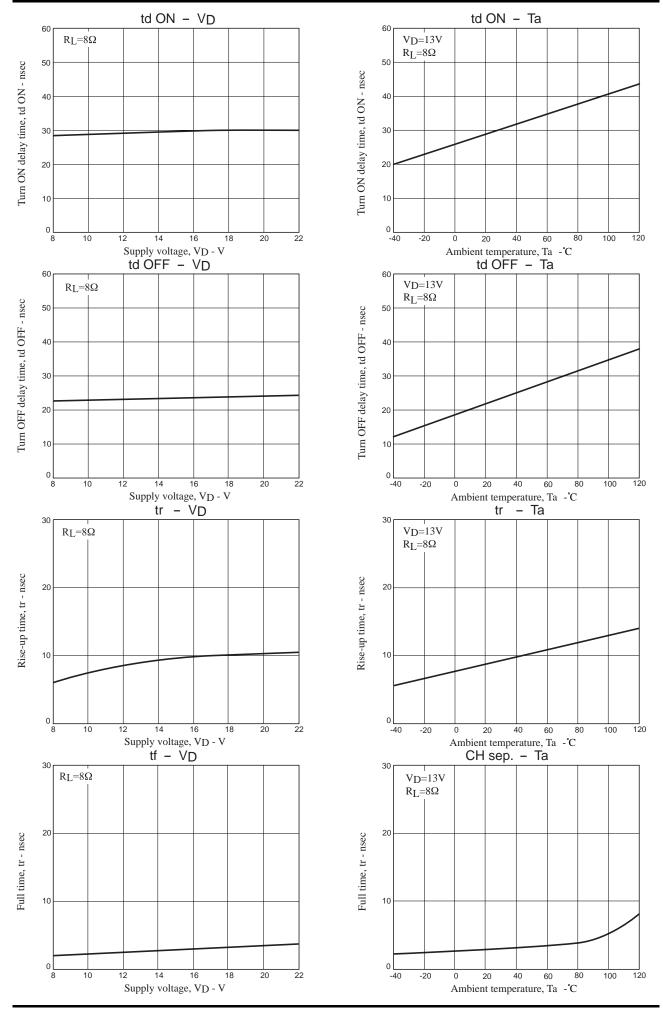

| Turn ON delay time         | td ON            | f <sub>IN</sub> =384kHz, Duty=50%                         | -       | 30  | 50  | ns   |  |

| Turn OFF delay time        | td OFF           | f <sub>IN</sub> =384kHz, Duty=50%                         | -       | 30  | 50  | ns   |  |

| Rise-up time               | tr               | f <sub>IN</sub> =384kHz, Duty=50%                         | -       | 5   | 20  | ns   |  |

| Fall time                  | tf               | f <sub>IN</sub> =384kHz, Duty=50%                         | -       | 5   | 20  | ns   |  |

<sup>\*1 :</sup> The maximum power transistor ON resistance(RDSON) is 270m $\Omega$ (design guarantee value).

Note: The value of these characteristics were measured in Our test environment. The actual value in an end system will vary depending on the printed circuit board pattern, the components used, and other factors.

#### **Electrical Characteristics**

(Reference value: The table below shows the reference value when FPGA equivalent to the Our reference model is used.)

| Descriptor                | Symbol Conditions | O a matition man                                             | Ratings |     |      | 1.1:4 |

|---------------------------|-------------------|--------------------------------------------------------------|---------|-----|------|-------|

| Parameter                 |                   | min                                                          | typ     | max | Unit |       |

| Output 1                  | P <sub>O</sub> 1  | THD+N=10%, f <sub>IN</sub> =1kHz, AES17                      | -       | 10  | -    | W     |

| Output 2                  | P <sub>O</sub> 2  | V <sub>D</sub> =16V, THD+N=10%, f <sub>IN</sub> =1kHz, AES17 | -       | 15  | -    | W     |

| Total harmonic distortion | THD+N             | P <sub>O</sub> =1W, f <sub>IN</sub> =1kHz, AES17             | -       | 0.1 | -    | %     |

Note: The value of these characteristics were measured in Our test environment. The actual value in an end system will vary depending on the printed circuit board pattern, the components used, and other factors.

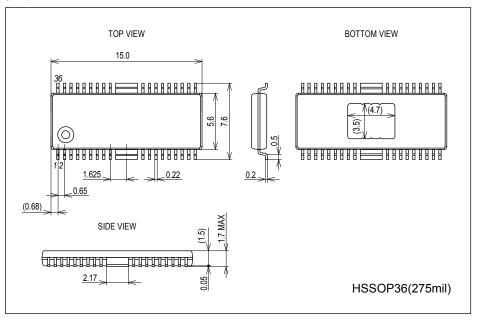

# **Package Dimensions**

unit: mm (typ)

3417

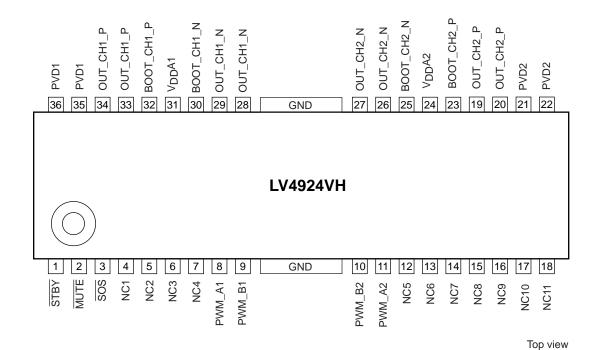

### **Pin Assignment**

#### Reference data for thermal design

#### Overall view of substrate

Mounted on a specified board (Customer bread board rev.1.0): 90.0mm × 70.0 mm × 1.6 mm (two-layer) Material: glass epoxy

Pd max-Ta

- 1. Data of the Exposed Die-Pad (heat spreader) substrate as mounted represents the value in the state where the exposed Die-Pad surface is wet for 90% or more.

- 2. For the set design, derating design should be made while ensuring allowance.

Stresses to become an object of derating are the voltage, current, junction temperature, power loss and mechanical stresses including vibration, impact and tension.

Accordingly, these stresses must be as low or small as possible in the design.

Approximate targets for general derating are as follows:

- (1) Maximum value 80% or less for the voltage rating.

- (2) Maximum value 80% or less for the current rating.

- (3) Maximum value 80% or less for the temperature rating.

- 3. After set design, be sure to verify the design with the product.

Also check the soldered state of the Exposed Die-Pad, etc. and verify the reliability of the soldered joint. If any void or deterioration is observed in these sections, thermal conduction to the substrate is deteriorated, resulting in thermal damage of IC.

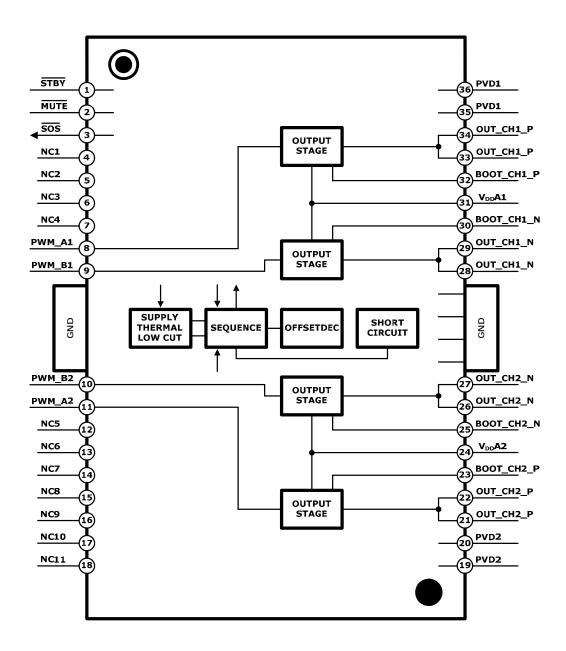

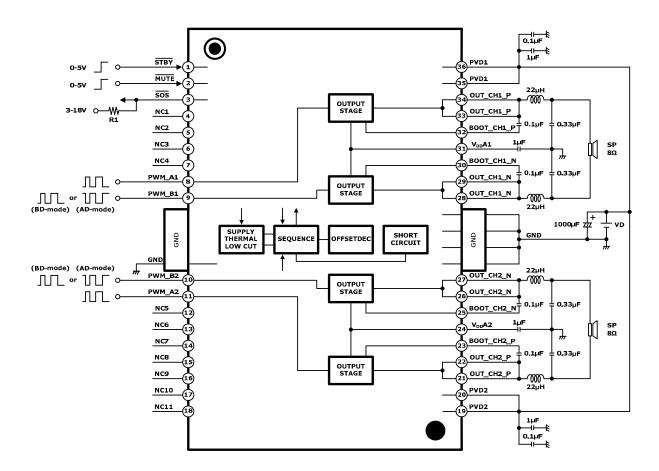

# **Block Diagram**

#### **Pin Equivalent Circuit**

| Pin No. | Pin name | I/O | Description          | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | STBY     | ı   | Standby mode control | 10kΩ (30g) |

| 2       | MUTE     | I   | Muting control       | PVD VDDA  GND  VDDA  GND  VDDA  GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Continued on next page.

Continued from preceding page.

| Continued from preceding page. |                    |     |                                                                                                                                                                                         |                     |  |  |  |  |

|--------------------------------|--------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| Pin No.                        | Pin name           | I/O | Description                                                                                                                                                                             | Equivalent Circuit  |  |  |  |  |

| 3                              | SOS                | I   | Internal protection circuit detection output (OR output of the thermal detection, over-current, voltage drop protection, offset detection circuit) of an NPN open collector output type | PVD<br>500Ω<br>GND  |  |  |  |  |

| 4                              | NC1                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 5                              | NC2                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 6                              | NC3                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 7                              | NC4                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 8                              | PWM_A1             | - 1 | PWM input (plus input) of OUT_CH1_P                                                                                                                                                     | PVD VDDA            |  |  |  |  |

| 9                              | PWM_B1             | - 1 | PWM input (negative input) of OUT_CH1_N                                                                                                                                                 | 1 10                |  |  |  |  |

| 10                             | PWM_B2             | - 1 | PWM input (negative input) of OUT_CH2_N                                                                                                                                                 | 1000                |  |  |  |  |

| 11                             | PWM_A2             | I   | PWM input (plus input) of OUT_CH2_P                                                                                                                                                     | 10kΩ<br>W C3<br>GND |  |  |  |  |

| FIN                            | GND                | -   | ground                                                                                                                                                                                  |                     |  |  |  |  |

| 12                             | NC5                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 13                             | NC6                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 14                             | NC7                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 15                             | NC8                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 16                             | NC9                | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 17                             | NC10               | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 18                             | NC11               | -   | Non connection                                                                                                                                                                          |                     |  |  |  |  |

| 19, 20                         | PVD2               | -   | Power pin                                                                                                                                                                               |                     |  |  |  |  |

| 21, 22                         | OUT_CH2_P          | 0   | Output pin, Channel 2 plus                                                                                                                                                              | PVD                 |  |  |  |  |

| 26, 27                         | OUT_CH2_N          | 0   | Output pin, Channel 2 minus                                                                                                                                                             |                     |  |  |  |  |

| 28, 29                         | OUT_CH1_N          | 0   | Output pin, Channel 1 minus                                                                                                                                                             |                     |  |  |  |  |

| 33, 34                         | OUT_CH1_P          | 0   | Output pin, Channel 1 plus                                                                                                                                                              | GND                 |  |  |  |  |

| 23                             | BOOT_CH2_P         | I/O | Bootstrap I / O pin, channel 2 plus                                                                                                                                                     |                     |  |  |  |  |

| 24                             | V <sub>DD</sub> A2 | 0   | Internal power supply decoupling capacitor connection                                                                                                                                   |                     |  |  |  |  |

| 25                             | BOOT_CH2_N         | I/O | Bootstrap I / O pin, channel 2 minus                                                                                                                                                    |                     |  |  |  |  |

| 30                             | BOOT_CH1_N         | I/O | Bootstrap I / O pin, channel 1 minus                                                                                                                                                    |                     |  |  |  |  |

| 31                             | V <sub>DD</sub> A1 | 0   | Internal power supply decoupling capacitor connection                                                                                                                                   |                     |  |  |  |  |

| 32                             | BOOT_CH1_P         | I/O | Bootstrap I / O pin, channel 1 plus                                                                                                                                                     |                     |  |  |  |  |

| 35, 36                         | PVD1               | -   | Power pin                                                                                                                                                                               |                     |  |  |  |  |

#### Description of functions

#### System Standby

The built-in 5V regulator is turned ON / OFF by changing over "H" and "L" of "STBY". The regulator is turned OFF with "STBY" at "L" and ON with "STBY" at "H".

This signal also causes initialization of the internal logic initialization with "L" and the normal mode with "H".

#### **MUTE Function**

The MUTE function is mainly for muting of the output and for reduction of pop noise at power ON.

#### Muting the output

The output PWM can be turned ON / OFF by changing over "H" and "L" of "MUTE". The PWM output is stopped (putting all of PWM outputs at high impedance) with "MUTE" at "L" and enters the normal operation mode with "MUTE" at "H".

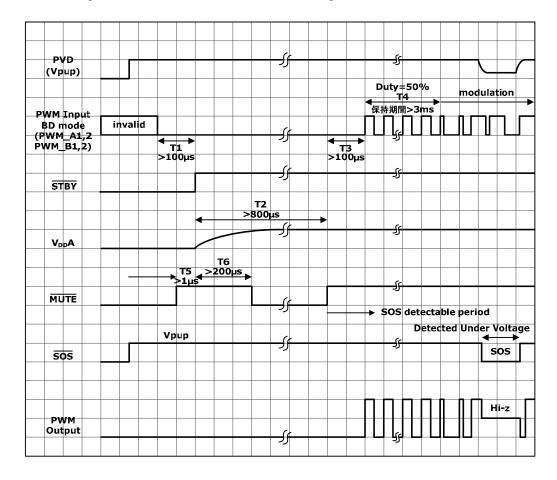

#### Sequence at power ON

To reduce the pop noise, turn ON power supply while controlling in the following timing (PWM=BD mode). In particular, all of inputs of PWM must be held at "L" at canceling of MUTE function.

<sup>\*</sup> Please observe the following items for the destruction prevention of the output transistor.

<sup>(1)</sup> Under all conditions must control the period at the "H" level about the PWM input so as not to become more than 200µs when period of the "H" level MUTE and STBY signals both.

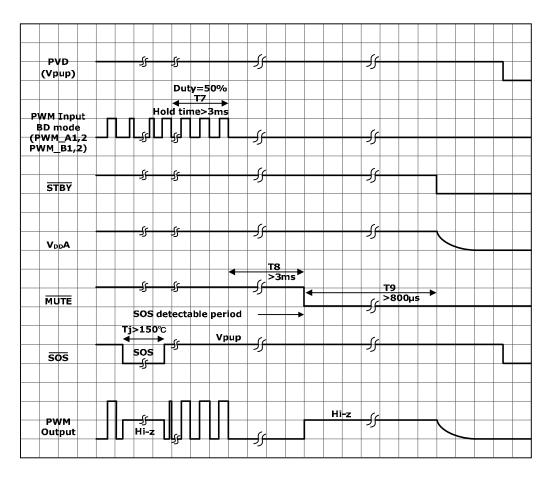

#### Sequence at power OFF

To reduce the pop noise, turn OFF power supply while controlling in the following timing (PWM=BD mode).

#### **Protection Circuit**

LV4924VH incorporates the over-current protection circuit, thermal protection circuit, supply voltage drop protection circuit and output offset detection protection circuit. Activation of any one of these circuits causes the  $\overline{SOS}$  output pin to become active and thus "L".

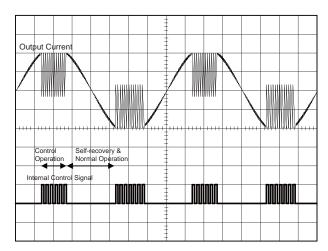

#### Over-current protection circuit

This circuit is a protection circuit\* to protect the output transistor from the over-current and compatible with any mode of lightning, ground fault, and load short-circuit.

Protection is done when the detection current value (about 6A) set inside IC is reached, forcing the output transistor to remain OFF for about 20µs. After forced OFF, the transistor returns automatically to the normal operation and performs protection again if the over-current continues to flow.

<sup>\*</sup> The over-current protection circuit functions only to avoid the abnormal state, such as output short-circuit, etc., temporarily, and does not guarantee to offer the protection to prevent damage to IC.

#### Thermal protection circuit

This circuit detects the temperature (150°C or more) inside LSI for protection. While this protection circuit is active, the output Tr is turned OFF on both high- and low-sides, putting the output in the high-impedance state. This operation is also provided with the hysteresis.

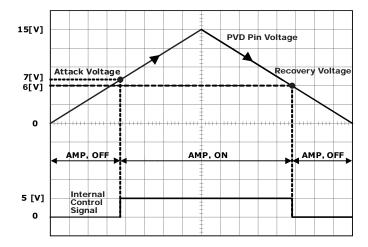

#### Supply voltage drop protection circuit

To avoid unstable operation at low voltages, this circuit monitors the PVD pin voltage and turns ON the amplifier when this voltage exceeds the Attack voltage ( $V_D = 7V$  typ.). In addition, to avoid unstable operation when the PVD pin voltage has dropped because of certain reasons, the Recover voltage ( $V_D = 6V$  typ.) is set. Both Attack and Recover voltages have the hysteresis (about 1V) to prevent continuous ON / OFF operation of the supply voltage drop protection circuit.

#### Output offset detection protection circuit

This circuit is a protection circuit intended to alleviate burn of the loudspeakers when DC outputs to the BTL output for a certain period or more.

The circuit detects the case in which each BTL input of each channel continues to disagree (for about 300ms), turns OFF the output Tr on both high- and low-sides, and puts the output in the high-impedance state.

# **Application Circuit**

<sup>\*</sup> SOS of pin 3 is the open collector output.

Therefore, to monitor this output with CPU, it is necessary to pull up (resistor: R1) at power supply of CPU, etc.

When the output is not to be used (not to be monitored), it is not necessary to pull-up the resistor.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Amplifier IC Development Tools category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

EVAL-ADCMP566BCPZ EVAL-ADCMP606BKSZ AD8013AR-14-EBZ AD8033AKS-EBZ AD8044AR-EBZ AD8225-EVALZ

ADA4859-3ACP-EBZ ADA4862-3YR-EBZ DEM-OPA-SO-2B AD744JR-EBZ AD8023AR-EBZ AD8030ARJ-EBZ AD8040ARU-EBZ

AD8073JR-EBZ AD813AR-14-EBZ AD848JR-EBZ ADA4858-3ACP-EBZ ADA4922-1ACP-EBZ 551600075-001/NOPB DEM-OPA-SO

2E THS7374EVM EVAL-ADCMP553BRMZ EVAL-ADCMP608BKSZ MIOP 42109 EVAL-ADCMP609BRMZ ADA4950-1YCP-EBZ

MAX9928EVKIT+ MAX9611EVKIT MAX9937EVKIT+ MAX9934TEVKIT+ MAX44290EVKIT# MAX2644EVKIT MAX2634EVKIT

MAX4073EVKIT+ DEM-OPA-SO-2C MAX2643EVKIT ISL28158EVAL1Z MAX40003EVKIT# MAX2470EVKIT MAX2473EVKIT

MAX2472EVKIT MAX4223EVKIT MAX9700BEVKIT MADL-011014-001SMB DC1685A DEM-OPA-SO-2D MAX2670EVKIT# DEM-OPA-SO-1E AD8137YCP-EBZ EVAL-ADA4523-1ARMZ