# **LV5725JA**

#### **Bi-CMOS LSI**

# **Step-down Switching** Regulator

http://onsemi.com

#### Overview

The LV5725JA is a step-down voltage switching regulator.

#### **Functions**

- Wide input dynamic range: 4.5V to 50V.

- Current mode type.

- Built-in pulse-by-pulse OCP circuit: detection is on resistance of an external MOS. • Over current protection: HICCUP mode.

- Thermal shutdown.

• Load-independent soft start circuit

• ON/OFF pin

• Synchronous operation by external signal.

- Power good pin

- External voltage is usable when output voltage is high.

#### **Specifications**

#### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter      |                                              | Symbol              | Conditions                      | Ratings              | Unit |

|----------------|----------------------------------------------|---------------------|---------------------------------|----------------------|------|

| Supply voltage |                                              | V <sub>IN</sub> max |                                 | 55                   | V    |

|                | V <sub>IN</sub> , SW, OUT, PGOOD             |                     |                                 | 55                   | V    |

|                | HDRV, CBOOT                                  |                     |                                 | 61                   | V    |

| tage           | LDRV                                         |                     |                                 | 6.0                  | V    |

| pin voltage    | Between CBOOT to SW<br>Between CBOOT to HDRV |                     |                                 | 6.0                  | V    |

| Allowable      | EN, ILIM                                     |                     |                                 | V <sub>IN</sub> +0.3 | V    |

| No             | Between V <sub>IN</sub> to ILIM              |                     |                                 | 1.0                  | V    |

| _              | $V_{DD}$                                     |                     |                                 | 6.0                  | V    |

|                | SS, FB, COMP,RT, SYNC                        |                     |                                 | V <sub>DD</sub> +0.3 | V    |

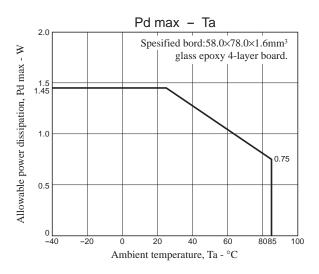

| Allo           | owable Power dissipation                     | Pd max              | Mounted on a specified board. * | 1.45                 | W    |

| Ор             | erating temperature                          | Topr                |                                 | -40 to +85           | °C   |

| Sto            | rage temperature                             | Tstg                |                                 | -55 to +150          | °C   |

|                | Parameter                                    | Symbol              | Conditions                      | Ratings              | Unit |

| Ма             | ximum junction temperature                   | Tj max              |                                 | 150                  | °C   |

<sup>\*</sup> Specified board: 58.0mm × 78.0mm × 1.6mm, fiberglass epoxy printed board.

Caution 1) Absolute maximum ratings represent the value which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# LV5725JA

## Recommended Operating Range at $Ta = 25^{\circ}C$

| Parameter                     | Parameter Symbol Conditions Ratings |  | Ratings   | Unit |

|-------------------------------|-------------------------------------|--|-----------|------|

| Supply voltage range          | V <sub>IN</sub>                     |  | 4.5 to 50 | V    |

| Error amplifier input voltage | $V_{FB}$                            |  | 0 to 1.6  | V    |

| Oscillatory frequency         | Fosc                                |  | 50 to 500 | kHz  |

### **Electrical Characteristics** at Ta = 25°C, $V_{\mbox{\footnotesize{IN}}} = 12V$

| Parameter                                                    | Symbol                | Symbol Conditions                                      |                       | Ratings |                 |      |  |

|--------------------------------------------------------------|-----------------------|--------------------------------------------------------|-----------------------|---------|-----------------|------|--|

| Parameter                                                    | Symbol                | Conditions                                             | min                   | typ     | max             | Unit |  |

| Reference voltage block                                      |                       |                                                        |                       |         |                 |      |  |

| Internal reference voltage                                   | Vref                  | Including offset of E/A                                | 0.698                 | 0.708   | 0.718           | V    |  |

| 5V power supply                                              | V <sub>DD</sub>       | I <sub>OUT</sub> = 0 to 5mA                            | 4.7                   | 5.2     | 5.7             | V    |  |

| Triangular waveform oscillator block                         |                       |                                                        |                       |         |                 |      |  |

| Oscillation frequency                                        | Fosc                  | RT= 56kΩ                                               | 317                   | 365     | 412             | kHz  |  |

| Frequency variation                                          | Fosc dv               | V <sub>IN</sub> = 4.5 to 50V                           |                       | 1       |                 | %    |  |

| Fold back detection voltage                                  | V <sub>OSC FB</sub>   | After power is supplied to SS, voltage is detected FB. |                       | 0.5     |                 | V    |  |

| Fold back oscillation frequency                              | FOSC FB               | RT= 56kΩ, V <sub>FB</sub> = 0V                         | 100                   | 130     | 160             | kHz  |  |

| ON/OFF circuit block                                         |                       |                                                        |                       |         |                 |      |  |

| IC start-up voltage                                          | V <sub>EN</sub> on    |                                                        | -                     | 2.5     | 3.0             | V    |  |

| Hysteresis of startup voltage                                | V <sub>EN</sub> hys   |                                                        | 0.3                   | 0.6     | -               | V    |  |

| Soft start circuit block                                     |                       |                                                        |                       |         |                 |      |  |

| Soft start source current                                    | I <sub>SS</sub> SC    | EN > 3.0V                                              | 4                     | 5       | 6               | μΑ   |  |

| Soft start sink current                                      | I <sub>SS</sub> SK    | EN < 1V, V <sub>DD</sub> = 5V                          |                       | 2       |                 | mA   |  |

| Soft start end voltage                                       | V <sub>SS</sub> END   |                                                        | 0.7                   | 0.9     | 1.1             | V    |  |

| UVLO circuit block                                           |                       |                                                        |                       |         |                 |      |  |

| UVLO voltage                                                 | V <sub>UVLO</sub>     |                                                        | 3.7                   | 4.0     | 4.3             | V    |  |

| Hysteresis of UVLO                                           | V <sub>UVLO</sub> H   |                                                        |                       | 0.3     |                 | V    |  |

| Error amplifier                                              |                       |                                                        |                       |         |                 |      |  |

| Input bias current                                           | I <sub>EA IN</sub>    |                                                        |                       |         | 100             | nA   |  |

| Error amplifier gain                                         | G <sub>EA</sub>       |                                                        | 1000                  | 1400    | 1800            | μA/V |  |

| Range of common-mode input voltage                           | V <sub>EA</sub> R     | V <sub>IN</sub> = 4.5 to 50V                           | 0                     |         | 1.6             | V    |  |

| Output sink current                                          | I <sub>EA</sub> OSK   | FB = 1.0V                                              |                       | -100    |                 | μΑ   |  |

| Output source current                                        | IEA OSC               | FB = 0V                                                |                       | 100     |                 | μΑ   |  |

| Current detection amplifier gain                             | GISNS                 |                                                        |                       | 2.4     |                 |      |  |

| Over current limiter circuit block                           |                       |                                                        |                       |         |                 |      |  |

| Reference current                                            | I <sub>LIM</sub>      |                                                        | -10%                  | 20      | +10%            | μΑ   |  |

| Over current detection comparator offset voltage             | V <sub>LIM_</sub> OFS |                                                        | -5                    |         | +5              | mV   |  |

| Range of over current detection comparator common mode input | V <sub>LIM_CM</sub>   |                                                        | V <sub>IN</sub> -0.45 |         | V <sub>IN</sub> | ٧    |  |

| PWM comparator                                               |                       |                                                        |                       |         |                 |      |  |

| Input threshold voltage                                      | Vt max                | Duty cycle = D <sub>MAX</sub> , SW = V <sub>IN</sub>   | 1.15                  | 1.25    | 1.35            | V    |  |

|                                                              | Vt0                   | Duty cycle = 0%, SW = V <sub>IN</sub>                  | 0.5                   | 0.6     | 0.7             | V    |  |

| Maximum ON duty                                              | D <sub>MAX</sub>      |                                                        | 92                    |         |                 | %    |  |

Continued on next page.

Continued from preceding page.

| D                                      | Complete al            | O a difference                 |     | Ratings |     |      |  |

|----------------------------------------|------------------------|--------------------------------|-----|---------|-----|------|--|

| Parameter                              | Symbol                 | Conditions                     | min | typ     | max | Unit |  |

| Power good                             |                        |                                |     |         |     |      |  |

| Power good "L" sink current            | IpgL                   | PGOOD = 5V                     |     | 5       |     | mA   |  |

| Power good "H" sink current            | I <sub>PG</sub> H      | PGOOD = 5V                     |     |         | 1   | μΑ   |  |

| Power good voltage                     | PGthresh               | When FB voltage rises          |     | 0.612   |     | V    |  |

| Hysteresis of power good               | PG <sub>hys</sub>      |                                |     | 12      |     | mV   |  |

| Output block                           |                        |                                |     |         |     |      |  |

| High side output ON resistance (upper) | R <sub>ONH</sub> _HIGH | CBOOT – HDRV = -0.1V           |     | 12      |     | Ω    |  |

| High side output ON resistance (lower) | R <sub>ONL</sub> HIGH  | HDRV – SW = +0.1V              |     | 3.3     |     | Ω    |  |

| Low side output ON resistance (upper)  | R <sub>ONH</sub> LOW   | V <sub>DD</sub> – LDRV = -0.1V |     | 7.9     |     | Ω    |  |

| Low side output ON resistance (lower)  | R <sub>ONL</sub> LOW   | LDRV – GND = +0.1V             |     | 3.8     |     | Ω    |  |

| High side output ON current (upper)    | I <sub>ONH</sub> _HIGH | CBOOT – HDRV = -4.5V           | 160 |         |     | mA   |  |

| High side output ON current (lower)    | I <sub>ONL</sub> HIGH  | HDRV – SW = +4.5V              | 330 |         |     | mA   |  |

| Low side output ON current (upper)     | I <sub>ONH</sub> _LOW  | V <sub>DD</sub> – LDRV = -5.2V | 190 |         |     | mA   |  |

| Low side output ON current (lower)     | I <sub>ONL</sub> LOW   | LDRV – GND = +5.2V             | 250 |         |     | mA   |  |

| Entire device                          | •                      | •                              |     |         |     |      |  |

| Standby current                        | Iccs                   | EN < 1V                        |     |         | 1   | μА   |  |

| Average current consumption            | ICCA                   | EN > 3.0V                      |     | 2.5     |     | mA   |  |

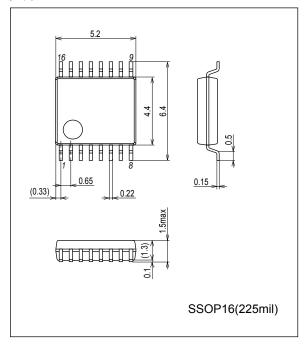

# **Package Dimensions**

unit : mm (typ)

3178B

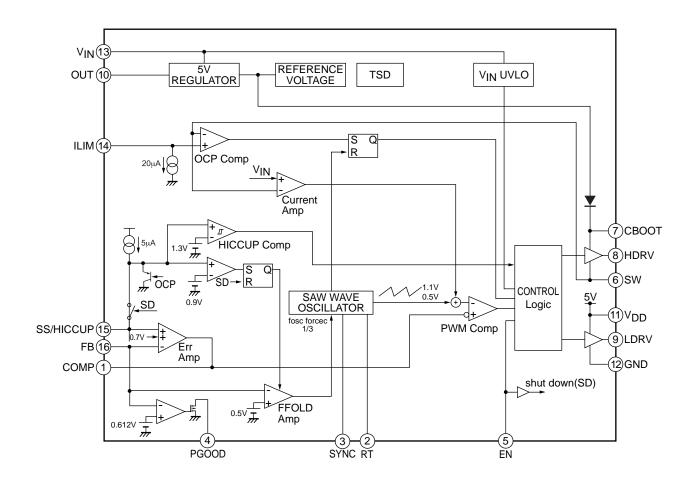

#### **Block Diagram**

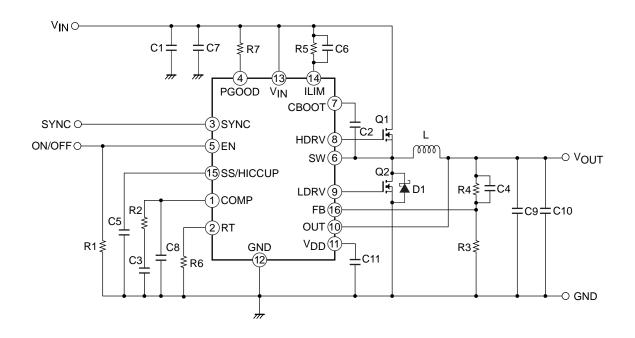

### Sample application circuit

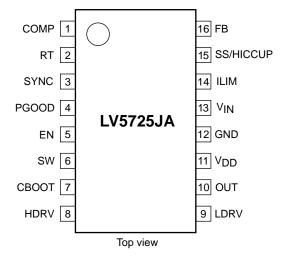

## **Pin Assignment**

### **Pin Function**

| Pin No. | Pin name        | Description                                                                                                                                                                                                                                                                                                                                                      |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | COMP            | Error amplifier output pin. Make sure to connect a phase compensation network between COMP and GND.                                                                                                                                                                                                                                                              |

| 2       | RT              | Oscillating frequency setting pin. Make sure to connect a resistor between this pin and GND.                                                                                                                                                                                                                                                                     |

| 3       | SYNC            | External synchronous signal input pin.                                                                                                                                                                                                                                                                                                                           |

| 4       | PGOOD           | Power good pin.                                                                                                                                                                                                                                                                                                                                                  |

| 5       | EN              | ON/OFF pin.                                                                                                                                                                                                                                                                                                                                                      |

| 6       | SW              | This pin is connected to switching node. Connect the source of Nch MOSFET to this pin.                                                                                                                                                                                                                                                                           |

| 7       | СВООТ           | Bootstrap capacitor connected pin. This pin is used as gate driving power supply for external Nch MOSFET. Make sure to connect a capacitor between CBOOT and SW.                                                                                                                                                                                                 |

| 8       | HDRV            | External upper MOSFET gate driving pin.                                                                                                                                                                                                                                                                                                                          |

| 9       | LDRV            | External lower MOSFET gate driving pin.                                                                                                                                                                                                                                                                                                                          |

| 10      | OUT             | Internal regulator power supply pin. This pin is connected to V <sub>OUT</sub> .                                                                                                                                                                                                                                                                                 |

| 11      | $V_{DD}$        | Power supply pin for gate drive of the external lower MOS-FET.                                                                                                                                                                                                                                                                                                   |

| 12      | GND             | Ground pin. GND pin voltage is the reference for each reference voltage.                                                                                                                                                                                                                                                                                         |

| 13      | V <sub>IN</sub> | Power supply pin. This pin is monitored by UVLO function. When the voltage of this pin becomes higher than 4.3V by UVLO function, the IC starts up and mode shifts to soft start operation.                                                                                                                                                                      |

| 14      | ILIM            | Reference current pin for current detection. The inlet current of approx. 20µA flows into this pin. Connect a resistor externally between this pin and VIN and when the voltage supplied to SW pin is lower than the pin voltage of this resistor, the upper Nch MOSFET is turned off by current limiter comparator. This operation is reset at every PWM pulse. |

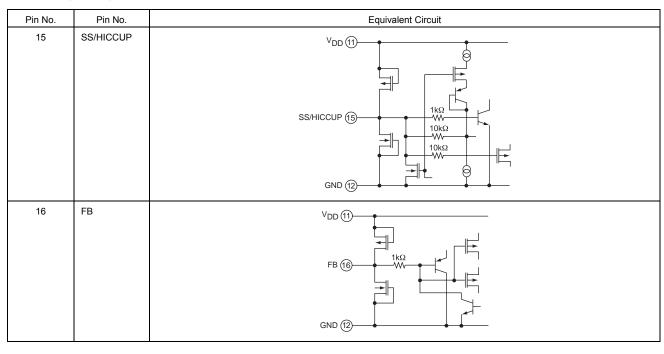

| 15      | SS/HICCUP       | Capacitor connection pin for soft start. This pin enables to charge the soft start capacitor by 5µA. (approx) When this pin turns approx. 0.9V, soft start period ends and frequency fold back function is activated.                                                                                                                                            |

| 16      | FB              | Error amplifier reverse input pin. Converter operates to set this pin to 0.708V. The output voltage divided by the external resistance is applied to this pin. After soft start, frequency fold back function operates when the voltage of this pin becomes 0.5V or lower. And oscillating frequency decreases together with FB voltage.                         |

## LV5725JA

# I/O pin equivalent circuit chart

| Pin No. | Pin No. | Equivalent Circuit                             |

|---------|---------|------------------------------------------------|

| 1       | СОМР    | V <sub>DD</sub> (1)                            |

| 2       | RT      | VDD (1) 10kΩ  RT (2)  GND (12)                 |

| 3       | SYNC    | V <sub>DD</sub> (1) SYNC (3) SYNC (3) GND (12) |

| 4       | PGOOD   | PGOOD (4)  PGOOD (2)  I kΩ  GND (12)           |

| 5       | EN      | V <sub>DD</sub> (1) 720kΩ \$ 650kΩ \$ GND (2)  |

| 6       | SW      | CBOOT 7  V <sub>IN</sub> (3)  SW 6  GND (12)   |

Continued on next page.

Continued from preceding page.

| Pin No. | Pin No.              | Equivalent Circuit                                        |

|---------|----------------------|-----------------------------------------------------------|

| 7       | СВООТ                | V <sub>DD</sub> (1)                                       |

| 8       | LDRV                 | CBOOT (7) HDRV (8) SW (6) GND (12)                        |

| 9       | HDRV                 | VDD (1) LDRV (9) GND (12)                                 |

| 10      | OUT                  | V <sub>IN</sub> (3) OUT (10) V <sub>DD</sub> (1) GND (12) |

| 11      | V <sub>DD</sub>      | V <sub>IN</sub> (13) V <sub>DD</sub> (1) GND (12)         |

| 12, 13  | GND, V <sub>IN</sub> | VIN (13) 1pF 30001                                        |

| 14      | ILIM                 | V <sub>IN</sub> (3)  ILIM (4)  GND (2)                    |

Continued on next page.

Continued from preceding page.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG

NCP81205MNTXG SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG

NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UBA2051C FSL4110LRLX MAX8778ETJ+ NTBV30N20T4G

NCP1240AD065R2G NCP1240FD065R2G NCP1361BABAYSNT1G NTC6600NF NCP1230P100G NCP1612BDR2G NX2124CSTR

SG2845M NCP81101MNTXG TEA19362T/1J IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG

NCP4308AMTTWG NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF

MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T

E/MG NCV1397ADR2G NCP1246ALD065R2G