# **PECL/TTL-TTL 1:8 Clock Distribution Chip**

#### Description

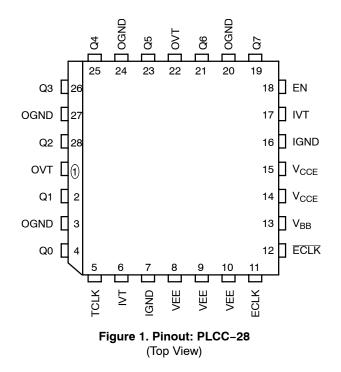

The MC10H/100H646 is a single supply, low skew translating 1:8 clock driver. Devices in the ON Semiconductor H646 translator series utilize the 28–lead PLCC for optimal power pinning, signal flow through and electrical performance. The single supply H646 is similar to the H643, which is a dual supply 1:8 version of the same function.

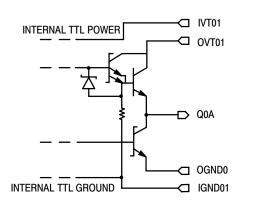

The H646 was designed specifically to drive series terminated transmission lines. Special techniques were used to match the HIGH and LOW output impedances to about 7.0  $\Omega$ . This simplifies the choice of the termination resistor for series terminated applications. To match the HIGH and LOW output impedances, it was necessary to remove the standard I<sub>OS</sub> limiting resistor. As a result, the user should take care in preventing an output short to ground as the part will be permanently damaged.

The H646 device meets all of the requirements for driving the 60 MHz and 66 MHz Intel Pentium® Microprocessor. The device has no PLL components, which greatly simplifies its implementation into a digital design. The eight copies of the clock allows for point-to-point clock distribution to simplify board layout and optimize signal integrity.

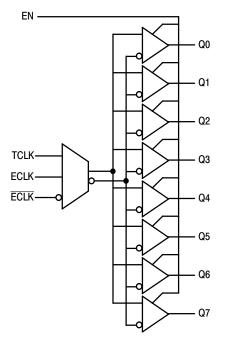

The H646 provides differential PECL inputs for picking up LOW skew PECL clocks from the backplane and distributing it to TTL loads on a daughter board. When used in conjunction with the MC10/100E111, very low skew, very wide clock trees can be designed. In addition, a TTL level clock input is provided for flexibility. Note that only one of the inputs can be used on a single chip. For correct operation, the unused input pins should be left open.

The Output Enable pin forces the outputs into a high impedance state when a logic 0 is applied.

The output buffers of the H646 can drive two series terminated, 50  $\Omega$  transmission lines each. This capability allows the H646 to drive up to 16 different point-to-point clock loads. Refer to the Applications section for a more detailed discussion in this area.

The 10H version is compatible with MECL<sup>™</sup> 10H ECL logic levels. The 100H version is compatible with 100K levels.

## Features

- PECL/TTL-TTL Version of Popular ECLinPS<sup>™</sup> E111

- Low Skew

- Guaranteed Skew Spec

- Tri-State Enable

- Differential Internal Design

- V<sub>BB</sub> Output

## **ON Semiconductor®**

http://onsemi.com

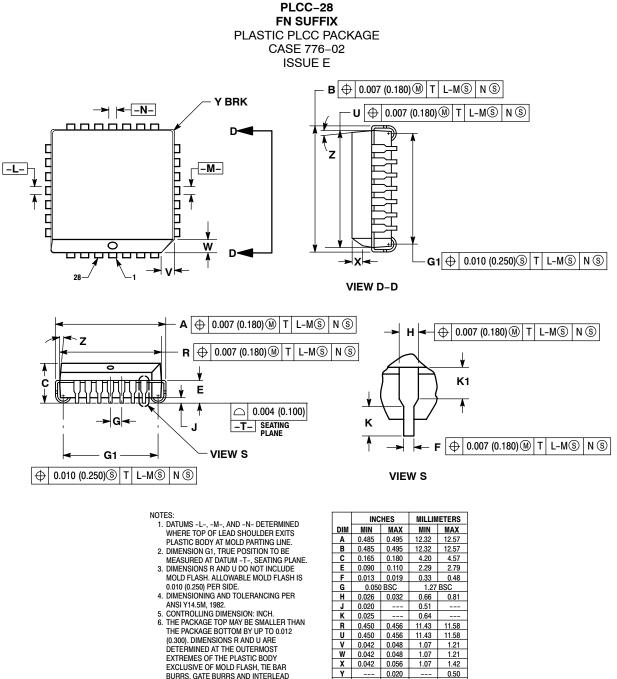

PLCC-28 FN SUFFIX CASE 776

## MARKING DIAGRAM\*

\*For additional marking information, refer to Application Note AND8002/D.

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

- Single Supply

- Extra TTL and ECL Power/Ground Pins

- Matched High and Low Output Impedance

- Meets Specifications Required to Drive Intel® Pentium® Microprocessors

- Pb-Free Packages are Available\*

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Figure 2. Logic Diagram

## Table 1. PIN DESCRIPTION

| PIN              | FUNCTION                              |

|------------------|---------------------------------------|

| OGND             | TTL Output Ground (0 V)               |

| OVT              | TTL Output V <sub>CC</sub> (+5.0 V)   |

| IGND             | Internal TTL GND (0 V)                |

| IVT              | Internal TTL V <sub>CC</sub> (+5.0 V) |

| V <sub>EE</sub>  | ECL V <sub>EE</sub> (0 V)             |

| V <sub>CCE</sub> | ECL Ground (5.0 V)                    |

| ECLK, ECLK       | Differential Signal Input             |

|                  | (PECL)                                |

| V <sub>BB</sub>  | V <sub>BB</sub> Reference Output      |

| Q0-Q7            | Signal Outputs (TTL)                  |

| EN               | Tri-State Enable Input (TTL)          |

Table 2. TRUTH TABLE

| TCLK | ECLK | ECLK | EN | Q |

|------|------|------|----|---|

| GND  | L    | Н    | Н  | L |

| GND  | Н    | L    | Н  | Н |

| Н    | GND  | GND  | Н  | Н |

| L    | GND  | GND  | Н  | L |

| Х    | Х    | Х    | L  | Z |

L = Low Voltage Level; H = High Voltage Level; Z = Tristate

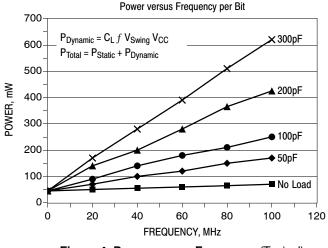

Figure 4. Power versus Frequency (Typical)

|                  |                             |                                                  |      | 0°C |      |      | 25°C |      |      | 85°C |       |      |

|------------------|-----------------------------|--------------------------------------------------|------|-----|------|------|------|------|------|------|-------|------|

| Symbol           | Characteristic              | Condition                                        | Min  | Тур | Max  | Min  | Тур  | Max  | Min  | Тур  | Max   | Unit |

| I <sub>INH</sub> | Input HIGH Current          |                                                  |      |     | 255  |      |      | 175  |      |      | 175   | μA   |

| Ι <sub>ΙL</sub>  | Input LOW Current           |                                                  | 0.5  |     |      | 0.5  |      |      | 0.5  |      |       | μA   |

| V <sub>IH</sub>  | Input HIGH Voltage          | IVT = IVO =<br>V <sub>CCE</sub> = 5.0 V (Note 1) | 3.83 |     | 4.16 | 3.87 |      | 4.19 | 3.94 |      | 4.28  | V    |

| V <sub>IL</sub>  | Input LOW Voltage           | IVT = IVO =<br>V <sub>CCE</sub> = 5.0 V (Note 1) | 3.05 |     | 3.52 | 3.05 |      | 3.52 | 3.05 |      | 3.555 | V    |

| $V_{BB}$         | Output Reference<br>Voltage | IVT = IVO =<br>V <sub>CCE</sub> = 5.0 V (Note 1) | 3.62 |     | 3.73 | 3.65 |      | 3.75 | 3.69 |      | 3.81  | V    |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

1. ECL V<sub>IH</sub>, V<sub>IL</sub> and V<sub>BB</sub> are referenced to V<sub>CCE</sub> and will vary 1:1 with the power supply. The levels shown are for IVT = IVO = V<sub>CCE</sub> = 5.0 V

|                  |                             |                                                  |       | 0°C |       |       | 25°C |       |       | 85°C |       |      |

|------------------|-----------------------------|--------------------------------------------------|-------|-----|-------|-------|------|-------|-------|------|-------|------|

| Symbol           | Characteristic              | Condition                                        | Min   | Тур | Max   | Min   | Тур  | Max   | Min   | Тур  | Max   | Unit |

| I <sub>INH</sub> | Input HIGH Current          |                                                  |       |     | 255   |       |      | 175   |       |      | 175   | μA   |

| IIL              | Input LOW Current           |                                                  | 0.5   |     |       | 0.5   |      |       | 0.5   |      |       | μA   |

| V <sub>IH</sub>  | Input HIGH Voltage          | IVT = IVO =<br>V <sub>CCE</sub> = 5.0 V (Note 2) | 3.835 |     | 4.12  | 3.835 |      | 4.12  | 3.835 |      | 3.835 | V    |

| V <sub>IL</sub>  | Input LOW Voltage           | IVT = IVO =<br>V <sub>CCE</sub> = 5.0 V (Note 2) | 3.19  |     | 3.525 | 3.19  |      | 3.525 | 3.19  |      | 3.525 | V    |

| $V_{BB}$         | Output Reference<br>Voltage | IVT = IVO =<br>V <sub>CCE</sub> = 5.0 V (Note 2) | 3.62  |     | 3.74  | 3.62  |      | 3.74  | 3.62  |      | 3.74  | V    |

## Table 4. 100H PECL DC CHARACTERISTICS (IVT = $V_{CCE} = 5.0 V \pm 5\%$ )

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

2. ECL VIH, VIL and VBB are referenced to VCCE and will vary 1:1 with the power supply. The levels shown are for IVT = IVO = VCCE = 5.0 V

## Table 5. DC CHARACTERISTICS (IVT = OVT = V<sub>CCE</sub> = 5.0 V ±∫5%)

|                 |                              |                         | 0°C |     | 25°C 85°C |     | °C  |     |      |

|-----------------|------------------------------|-------------------------|-----|-----|-----------|-----|-----|-----|------|

| Symbol          | Characteristic               | Condition               | Min | Max | Min       | Max | Min | Max | Unit |

| V <sub>OH</sub> | Output HIGH Voltage          | I <sub>OH</sub> = 24 mA | 2.6 | -   | 2.6       |     | 2.6 | -   | V    |

| V <sub>OL</sub> | Output LOW Voltage           | I <sub>OL</sub> = 48 mA | -   | 0.5 | -         | 0.5 | -   | 0.5 | V    |

| IOS             | Output Short Circuit Current | (Note 3)                | -   | -   | -         | -   | -   | -   | mA   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

3. The outputs must not be shorted to ground, as this will result in permanent damage to the device. The high drive outputs of this device do not include a limiting IOS resistor.

#### Table 6. TTL DC CHARACTERISTICS (V<sub>T</sub> = V<sub>E</sub> = 5.0 V ±[5%)

|                                    |                                         |                                                       | 0°C        |           | 25°C       |           | 85°C       |           |      |

|------------------------------------|-----------------------------------------|-------------------------------------------------------|------------|-----------|------------|-----------|------------|-----------|------|

| Symbol                             | Characteristic                          | Condition                                             | Min        | Max       | Min        | Max       | Min        | Max       | Unit |

| V <sub>IH</sub><br>V <sub>IL</sub> | Input HIGH Voltage<br>Input LOW Voltage |                                                       | 2.0        | 0.8       | 2.0        | 0.8       | 2.0        | 0.8       | V    |

| IIH                                | Input HIGH Current                      | V <sub>IN</sub> = 2.7 V<br>V <sub>IN</sub> = 7.0 V    |            | 20<br>100 |            | 20<br>100 |            | 20<br>100 | μΑ   |

| I <sub>IL</sub>                    | Input LOW Current                       | V <sub>IN</sub> = 0.5 V                               |            | -0.6      |            | -0.6      |            | -0.6      | mA   |

| V <sub>OH</sub>                    | Output HIGH Voltage                     | I <sub>OH</sub> = –3.0 mA<br>I <sub>OH</sub> = –24 mA | 2.5<br>2.0 |           | 2.5<br>2.0 |           | 2.5<br>2.0 |           | V    |

| V <sub>OL</sub>                    | Output LOW Voltage                      | I <sub>OL</sub> = 24 mA                               |            | 0.5       |            | 0.5       |            | 0.5       | V    |

| VIK                                | Input Clamp Voltage                     | I <sub>IN</sub> = -18 mA                              |            | -1.2      |            | -1.2      |            | -1.2      | V    |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

#### Table 7. DC CHARACTERISTICS (IVT = OVT = V<sub>CCE</sub> = 5.0 V ±[5%)

|                  |                      |                     | 0   | °C  |     | 25°C |     | 85  | °C  |      |

|------------------|----------------------|---------------------|-----|-----|-----|------|-----|-----|-----|------|

| Symbol           | Characteristic       | Condition           | Min | Max | Min | Тур  | Max | Min | Max | Unit |

| I <sub>CCL</sub> | Power Supply Current | Total all OVT, IVT, |     | 185 |     | 166  | 185 |     | 185 | mA   |

| I <sub>CCH</sub> |                      | and $V_{CCE}$ pins  |     | 175 |     | 154  | 175 |     | 175 | mA   |

| I <sub>CCZ</sub> |                      |                     |     | 210 |     |      | 210 |     | 210 |      |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

|                                 |                      |                                                                      |              | 0                        | °C                | 25                       | °C                | 85                       | °C                |     |

|---------------------------------|----------------------|----------------------------------------------------------------------|--------------|--------------------------|-------------------|--------------------------|-------------------|--------------------------|-------------------|-----|

| Symbol                          | Characte             | Condition                                                            | Min          | Max                      | Min               | Max                      | Min               | Max                      | Unit              |     |

| t <sub>PLH</sub>                | Propagation Delay    | ECLK to Q<br>TCLK to Q                                               |              | 4.8<br>5.1               | 5.8<br>6.4        | 5.0<br>5.3               | 6.0<br>6.4        | 5.6<br>5.7               | 6.6<br>7.0        | ns  |

| t <sub>PHL</sub>                | Propagation Delay    | ECLK to Q<br>TCLK to Q                                               |              | 4.4<br>4.7               | 5.4<br>6.0        | 4.4<br>4.8               | 5.4<br>5.9        | 4.8<br>5.2               | 5.8<br>6.5        | ns  |

| t <sub>SK(O)</sub>              | Output Skew          | Q0, Q3, Q4, Q7<br>Q1, Q2, Q5<br>Q0–Q7                                | (Notes 4, 9) |                          | 350<br>350<br>500 |                          | 350<br>350<br>500 |                          | 350<br>350<br>500 | ps  |

| t <sub>SK(PR)</sub>             | Process Skew         | ECLK to Q<br>TCLK to Q                                               | (Notes 5, 9) |                          | 1.0<br>1.3        |                          | 1.0<br>1.1        |                          | 1.0<br>1.3        | ns  |

| t <sub>SK(P)</sub>              | Pulse Skew           | $\Delta t_{PLH} - t_{PHL}$                                           |              |                          | 1.0               |                          | 1.0               |                          | 1.0               | ns  |

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Time       |                                                                      |              | 0.3                      | 1.5               | 0.3                      | 1.5               | 0.3                      | 1.5               | ns  |

| t <sub>PW</sub>                 | Output Pulse Width   | 66 MHz @ 2.0 V<br>66 MHz @ 0.8 V<br>60 MHz @ 2.0 V<br>60 MHz @ 0.8 V | (Notes 6, 9) | 5.5<br>5.5<br>6.0<br>6.0 |                   | 5.5<br>5.5<br>6.0<br>6.0 |                   | 5.5<br>5.5<br>6.0<br>6.0 |                   | ns  |

| t <sub>Stability</sub>          | Clock Stability      |                                                                      | (Notes 7, 9) |                          | ±75               |                          | ±75               |                          | ±75               | ps  |

| F <sub>MAX</sub>                | Maximum Input Freque | ency                                                                 | (Notes 8, 9) |                          | 80                |                          | 80                |                          | 80                | MHz |

#### Table 8. AC CHARACTERISTICS (IVT = OVT = V<sub>CCE</sub> = 5.0 V ±5%)

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

- 4. Output skew defined for identical output transitions.

Couput skew defined for N<sub>CC</sub> = 5.0 V ±[5%.

Process skew is valid for V<sub>CC</sub> = 5.0 V ±[5%.

Parameters guaranteed by t<sub>SK(P)</sub> and t<sub>r</sub>, t<sub>f</sub> specification limits.

Clock stability is the period variation between two successive rising edges.

8. For series terminated lines. See Applications section for F<sub>MAX</sub> enhancement techniques.

9. All AC specifications tested driving 50  $\Omega$  series terminated transmission lines at 80 MHz.

#### **ORDERING INFORMATION**

| Device         | Package              | Shipping <sup>†</sup> |

|----------------|----------------------|-----------------------|

| MC10H646FN     | PLCC-28              | 37 Units / Rail       |

| MC10H646FNG    | PLCC-28<br>(Pb-Free) | 37 Units / Rail       |

| MC10H646FNR2   | PLCC-28              | 500 / Tape & Reel     |

| MC10H646FNR2G  | PLCC-28<br>(Pb-Free) | 500 / Tape & Reel     |

| MC100H646FN    | PLCC-28              | 37 Units / Rail       |

| MC100H646FNG   | PLCC-28<br>(Pb-Free) | 37 Units / Rail       |

| MC100H646FNR2  | PLCC-28              | 500 / Tape & Reel     |

| MC100H646FNR2G | PLCC-28<br>(Pb-Free) | 500 / Tape & Reel     |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

| AN1405/D  | - | ECL Clock Distribution Techniques           |

|-----------|---|---------------------------------------------|

| AN1406/D  | - | Designing with PECL (ECL at +5.0 V)         |

| AN1503/D  | - | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |

| AN1504/D  | - | Metastability and the ECLinPS Family        |

| AN1568/D  | - | Interfacing Between LVDS and ECL            |

| AN1672/D  | - | The ECL Translator Guide                    |

| AND8001/D | - | Odd Number Counters Design                  |

| AND8002/D | - | Marking and Date Codes                      |

| AND8020/D | _ | Termination of ECL Logic Devices            |

| AND8066/D | - | Interfacing with ECLinPS                    |

| AND8090/D | _ | AC Characteristics of ECL Devices           |

|           |   |                                             |

### PACKAGE DIMENSIONS

EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.

DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037 7 (0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).

0.50

10°

2 °

1.02

2 °

K1 0.040

10 °

G1 0.410 0.430 10.42 10.92

z

ECLinPS is a trademark of Semiconductor Components Industries, LLC (SCILLC). MECL 10H is a trademark of Motorola, Inc. Pentium is a registered trademark of Intel Corporation.

ON Semiconductor and I are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Drivers & Distribution category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

8501BYLF P9090-0NLGI8 854110AKILF 83210AYLF NB6VQ572MMNG HMC6832ALP5LETR RS232-S5 6ES7390-1AF30-0AA0 CDCVF2505IDRQ1 NB7L572MNR4G SY100EP33VKG HMC7043LP7FETR ISPPAC-CLK5520V-01T100C EC4P-221-MRXD1 6EP1332-1SH71 6ES7223-1PH32-0XB0 AD246JN AD246JY AD9510BCPZ AD9510BCPZ-REEL7 AD9511BCPZ AD9511BCPZ AD9511BCPZ-REEL7 AD9512BCPZ AD9512UCPZ-EP AD9514BCPZ AD9514BCPZ-REEL7 AD9515BCPZ AD9515BCPZ-REEL7 AD9572ACPZLVD AD9572ACPZPEC AD9513BCPZ-REEL7 ADCLK950BCPZ-REEL7 ADCLK950BCPZ AD9553BCPZ HMC940LC4B HMC6832ALP5LE CSPUA877ABVG8 9P936AFLFT 49FCT3805ASOG 49FCT3805EQGI 49FCT805CTQG 74FCT3807ASOG 74FCT3807EQGI 74FCT388915TEPYG 853S012AKILF 853S013AMILF 853S058AGILF 8V79S680NLGI ISPPAC-CLK5312S-01TN48I ISPPAC-CLK5520V-01TN100I