# Micropower Undervoltage Sensing Circuits

The MC34164 series are undervoltage sensing circuits specifically designed for use as reset controllers in portable microprocessor based systems where extended battery life is required. These devices offer the designer an economical solution for low voltage detection with a single external resistor. The MC34164 series features a bandgap reference, a comparator with precise thresholds and built–in hysteresis to prevent erratic reset operation, an open collector reset output capable of sinking in excess of 6.0 mA, and guaranteed operation down to 1.0 V input with extremely low standby current. The MC devices are packaged in 3–pin TO–92 (TO–226AA), micro size TSOP–5, 8–pin SOIC–8 and Micro8™ surface mount packages. The NCV device is packaged in SOIC–8.

Applications include direct monitoring of the 3.0 V or 5.0 V MPU/logic power supply used in appliance, automotive, consumer, and industrial equipment.

### **Features**

- Temperature Compensated Reference

- Monitors 3.0 V (MC34164–3) or 5.0 V (MC34164–5) Power Supplies

- Precise Comparator Thresholds Guaranteed Over Temperature

- Comparator Hysteresis Prevents Erratic Reset

- Reset Output Capable of Sinking in Excess of 6.0 mA

- Internal Clamp Diode for Discharging Delay Capacitor

- Guaranteed Reset Operation With 1.0 V Input

- Extremely Low Standby Current: As Low as 9.0 μA

- Economical TO–92 (TO–226AA), TSOP–5, SOIC–8 and Micro8 Surface Mount Packages

- NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes

- These Devices are Pb-Free and are RoHS Compliant

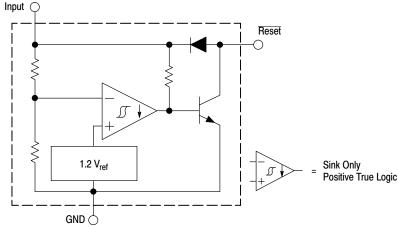

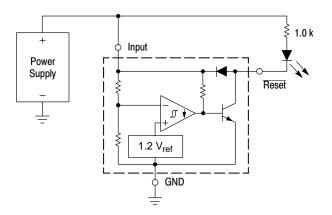

Figure 1. Representative Block Diagram

This device contains 28 active transistors.

# ON Semiconductor®

www.onsemi.com

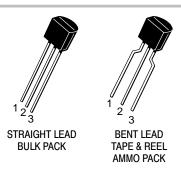

TO-92 (TO-226AA) P SUFFIX CASE 29

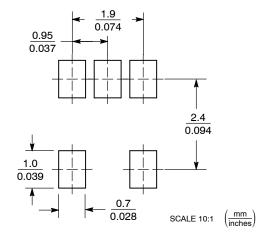

TSOP-5 SN SUFFIX CASE 483

SOIC-8 D SUFFIX CASE 751

Micro8 DM SUFFIX CASE 846A

### **PIN CONNECTIONS**

| Reset      | 1 | C | $\overline{\mathcal{C}}$ |  | 8 | N.C. |

|------------|---|---|--------------------------|--|---|------|

| Input      | 2 |   |                          |  | 7 | N.C. |

| N.C.       | 3 |   |                          |  | 6 | N.C. |

| Ground     | 4 |   |                          |  | 5 | N.C. |

| (Top View) |   |   |                          |  |   |      |

### TSOP-5

- Pin 1. Ground

- 2. Input

- Reset

- 4. NC

- 5. NC

### TO-92

- Pin 1. Reset

- 2. Input

- 3. Ground

### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.

### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 8 of this data sheet.

### **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                                                                                                                                         | Symbol                                                                                                         | Value                                  | Unit                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|

| Power Input Supply Voltage                                                                                                                                                                                                                                                                                                                                                                     | V <sub>in</sub>                                                                                                | -1.0 to 12                             | V                              |

| Reset Output Voltage                                                                                                                                                                                                                                                                                                                                                                           | Vo                                                                                                             | -1.0 to 12                             | V                              |

| Reset Output Sink Current                                                                                                                                                                                                                                                                                                                                                                      | I <sub>Sink</sub>                                                                                              | Internally<br>Limited                  | mA                             |

| Clamp Diode Forward Current, Reset to Input Pin (Note 1)                                                                                                                                                                                                                                                                                                                                       | IF                                                                                                             | 100                                    | mA                             |

| Power Dissipation and Thermal Characteristics P Suffix, Plastic Package Maximum Power Dissipation @ T <sub>A</sub> = 25°C Thermal Resistance, Junction—to—Air D Suffix, Plastic Package Maximum Power Dissipation @ T <sub>A</sub> = 25°C Thermal Resistance, Junction—to—Air DM Suffix, Plastic Package Maximum Power Dissipation @ T <sub>A</sub> = 25°C Thermal Resistance, Junction—to—Air | P <sub>D</sub><br>R <sub>θJA</sub><br>P <sub>D</sub><br>R <sub>θJA</sub><br>P <sub>D</sub><br>R <sub>θJA</sub> | 700<br>178<br>700<br>178<br>520<br>240 | mW<br>°C/W<br>mW<br>°C/W<br>mW |

| Operating Junction Temperature                                                                                                                                                                                                                                                                                                                                                                 | T <sub>J</sub>                                                                                                 | +150                                   | °C                             |

| Operating Ambient Temperature Range<br>MC34164 Series<br>MC33164 Series, NCV33164                                                                                                                                                                                                                                                                                                              | T <sub>A</sub>                                                                                                 | 0 to +70<br>- 40 to +125               | °C                             |

| Storage Temperature Range                                                                                                                                                                                                                                                                                                                                                                      | T <sub>stg</sub>                                                                                               | - 65 to +150                           | °C                             |

| Electrostatic Discharge Sensitivity (ESD) Human Body Model (HBM) Machine Model (MM)                                                                                                                                                                                                                                                                                                            | ESD                                                                                                            | 4000<br>200                            | V                              |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## MC34164-3, MC33164-3 SERIES, NCV33164-3

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_A = 25^{\circ}C$ , for min/max values  $T_A$  is the operating ambient temperature range that applies [Notes 2 & 3], unless otherwise noted.)

| Characteristic                                                                                                                                         | Symbol                                               | Min                  | Тур                  | Max               | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|----------------------|-------------------|------|

| COMPARATOR                                                                                                                                             |                                                      |                      |                      |                   |      |

| Threshold Voltage High State Output (V <sub>in</sub> Increasing) Low State Output (V <sub>in</sub> Decreasing) Hysteresis (I <sub>Sink</sub> = 100 μA) | V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>H</sub> | 2.55<br>2.55<br>0.03 | 2.71<br>2.65<br>0.06 | 2.80<br>2.80<br>– | V    |

| RESET OUTPUT                                                                                                                                           |                                                      |                      |                      |                   |      |

| Output Sink Saturation $ (V_{in} = 2.4 \text{ V}, I_{Sink} = 1.0 \text{ mA}) $ $ (V_{in} = 1.0 \text{ V}, I_{Sink} = 0.25 \text{ mA}) $                | V <sub>OL</sub>                                      |                      | 0.14<br>0.1          | 0.4<br>0.3        | V    |

| Output Sink Current (V <sub>in</sub> , Reset = 2.4 V)                                                                                                  | I <sub>Sink</sub>                                    | 6.0                  | 12                   | 30                | mA   |

| Output Off-State Leakage<br>(V <sub>in</sub> , Reset = 3.0 V)<br>(V <sub>in</sub> , Reset = 10 V)                                                      | <sup>l</sup> R(leak)                                 | -<br>-               | 0.02<br>0.02         | 0.5<br>1.0        | μΑ   |

| Clamp Diode Forward Voltage, Reset to Input Pin (I <sub>F</sub> = 5.0 mA)                                                                              | V <sub>F</sub>                                       | 0.6                  | 0.9                  | 1.2               | V    |

| TOTAL DEVICE                                                                                                                                           | •                                                    | •                    |                      |                   |      |

| Operating Input Voltage Range                                                                                                                          | V <sub>in</sub>                                      | 1.0 to 10            | -                    | _                 | V    |

| Quiescent Input Current $V_{in} = 3.0 \text{ V}$ $V_{in} = 6.0 \text{ V}$                                                                              | l <sub>in</sub>                                      | -<br>-               | 9.0<br>24            | 15<br>40          | μΑ   |

- 1. Maximum package power dissipation limits must be observed.

- 2. Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible. 3.  $T_{low} = 0^{\circ}C$  for MC34164  $T_{high} = +70^{\circ}C$  for MC34164

- - = -40°C for MC33164, NCV33164 = +125°C for MC33164, NCV33164

## MC34164-5, MC33164-5 SERIES, NCV33164-5

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_A = 25^{\circ}C$ , for min/max values  $T_A$  is the operating ambient temperature range that applies [Notes 5 & 6], unless otherwise noted.)

| Characteristic                                                                                                                                          | Symbol                                               | Min                  | Тур                  | Max               | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|----------------------|-------------------|------|

| COMPARATOR                                                                                                                                              |                                                      |                      |                      | -                 |      |

| Threshold Voltage High State Output (V <sub>in</sub> Increasing) Low State Output (V <sub>in</sub> Decreasing) Hysteresis (I <sub>Sink</sub> = 100 μA)  | V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>H</sub> | 4.15<br>4.15<br>0.02 | 4.33<br>4.27<br>0.09 | 4.45<br>4.45<br>– | V    |

| RESET OUTPUT                                                                                                                                            | •                                                    |                      |                      | •                 |      |

| Output Sink Saturation $ (V_{in} = 4.0 \text{ V}, \text{ I}_{Sink} = 1.0 \text{ mA}) $ $ (V_{in} = 1.0 \text{ V}, \text{ I}_{Sink} = 0.25 \text{ mA}) $ | V <sub>OL</sub>                                      | -<br>-               | 0.14<br>0.1          | 0.4<br>0.3        | V    |

| Output Sink Current (V <sub>in</sub> , Reset = 4.0 V)                                                                                                   | I <sub>Sink</sub>                                    | 7.0                  | 20                   | 50                | mA   |

| Output Off-State Leakage (V <sub>in</sub> , Reset = 5.0 V) (V <sub>in</sub> , Reset = 10 V)                                                             | <sup>l</sup> R(leak)                                 | -                    | 0.02<br>0.02         | 0.5<br>2.0        | μΑ   |

| Clamp Diode Forward Voltage, Reset to Input Pin (I <sub>F</sub> = 5.0 mA)                                                                               | V <sub>F</sub>                                       | 0.6                  | 0.9                  | 1.2               | V    |

| TOTAL DEVICE                                                                                                                                            |                                                      |                      |                      | -                 |      |

| Operating Input Voltage Range                                                                                                                           | V <sub>in</sub>                                      | 1.0 to 10            | _                    | -                 | V    |

| Quiescent Input Current $V_{in} = 5.0 \text{ V}$ $V_{in} = 10 \text{ V}$                                                                                | I <sub>in</sub>                                      | -                    | 12<br>32             | 20<br>50          | μΑ   |

<sup>4.</sup> Maximum package power dissipation limits must be observed.

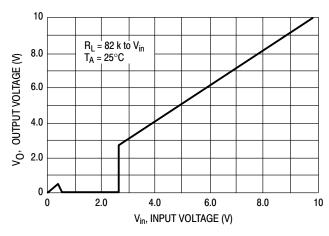

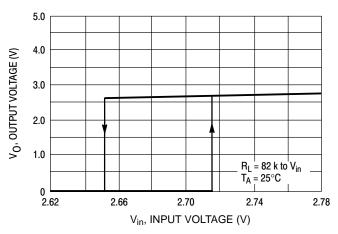

Figure 2. MC3X164-3 Reset Output Voltage versus Input Voltage

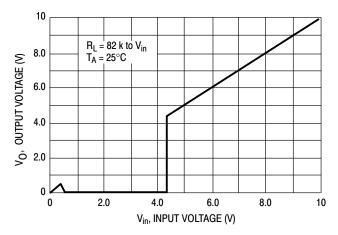

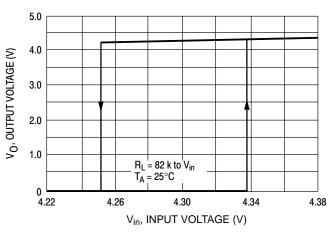

Figure 3. MC3X164-5 Reset Output Voltage versus Input Voltage

<sup>5.</sup> Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

<sup>6.</sup>  $T_{low} = 0^{\circ}\text{C for MC34164}$   $T_{high} = +70^{\circ}\text{C for MC34164}$

<sup>= -40°</sup>C for MC33164, NCV33164 = +125°C for MC33164, NCV33164

<sup>7.</sup> NCV prefix is for automotive and other applications requiring site and change control.

Figure 4. MC3X164-3 Reset Output Voltage versus Input Voltage

Figure 5. MC3X164-5 Reset Output Voltage versus Input Voltage

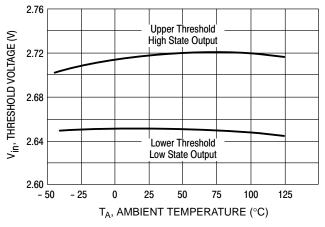

Figure 6. MC3X164-3 Comparator Threshold Voltage versus Temperature

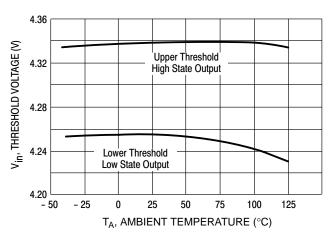

Figure 7. MC3X164–5 Comparator Threshold Voltage versus Temperature

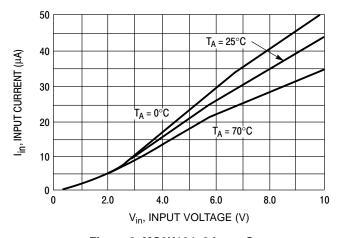

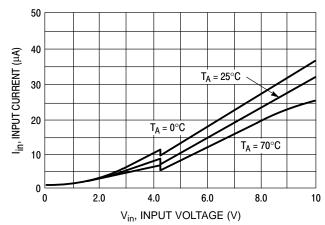

Figure 8. MC3X164-3 Input Current versus Input Voltage

Figure 9. MC3X164-5 Input Current versus Input Voltage

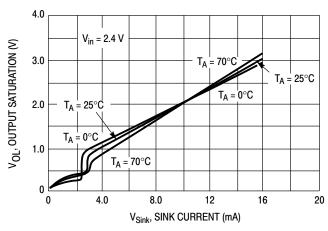

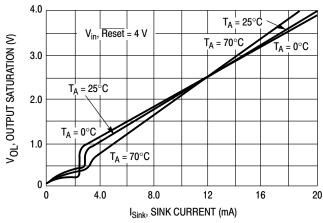

Figure 10. MC3X164-3 Reset Output Saturation versus Sink Current

Figure 11. MC3X164-5 Reset Output Saturation versus Sink Current

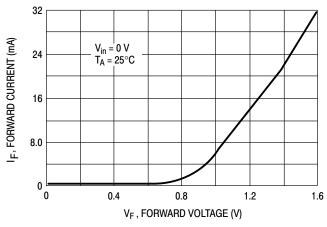

Figure 12. Clamp Diode Forward Current versus Voltage

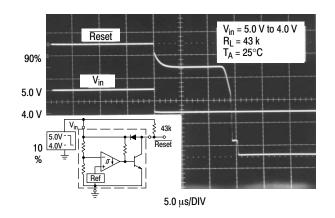

Figure 13. Reset Delay Time (MC3X164-5 Shown)

A time delayed reset can be accomplished with the addition of  $C_{DLY}$ . For systems with extremely fast power supply rise times (< 500 ns) it is recommended that the  $RC_{DLY}$  time constant be greater than 5.0  $\mu$ s.  $V_{th(MPU)}$  is the microprocessor reset input threshold.

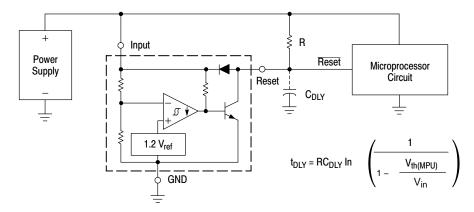

Figure 14. Low Voltage Microprocessor Reset

| Test Data              |                      |                       |                        |  |  |

|------------------------|----------------------|-----------------------|------------------------|--|--|

| V <sub>H</sub><br>(mV) | $\Delta V_{th}$ (mV) | R <sub>H</sub><br>(Ω) | R <sub>L</sub><br>(kΩ) |  |  |

| 60                     | 0                    | 0                     | 43                     |  |  |

| 103                    | 1.0                  | 100                   | 10                     |  |  |

| 123                    | 1.0                  | 100                   | 6.8                    |  |  |

| 160                    | 1.0                  | 100                   | 4.3                    |  |  |

| 155                    | 2.2                  | 220                   | 10                     |  |  |

| 199                    | 2.2                  | 220                   | 6.8                    |  |  |

| 280                    | 2.2                  | 220                   | 4.3                    |  |  |

| 262                    | 4.7                  | 470                   | 10                     |  |  |

| 306                    | 4.7                  | 470                   | 8.2                    |  |  |

| 357                    | 4.7                  | 470                   | 6.8                    |  |  |

| 421                    | 4.7                  | 470                   | 5.6                    |  |  |

| 530                    | 4.7                  | 470                   | 4.3                    |  |  |

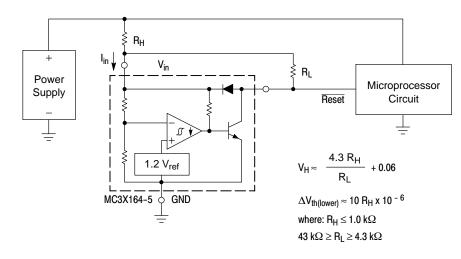

Comparator hysteresis can be increased with the addition of resistor  $R_H$ . The hysteresis equation has been simplified and does not account for the change of input current  $I_{in}$  as  $V_{in}$  crosses the comparator threshold (Figure 8). An increase of the lower threshold  $\Delta V_{th(lower)}$  will be observed due to  $I_{in}$  which is typically 10  $\mu$ A at 4.3 V. The equations are accurate to  $\pm 10\%$  with  $R_H$  less than 1.0 k $\Omega$  and  $R_L$  between 4.3 k $\Omega$  and 43 k $\Omega$ .

Figure 15. Low Voltage Microprocessor Reset With Additional Hysteresis (MC3X164–5 Shown)

Reset Solar Cells

GND

Figure 16. Voltage Monitor

Figure 17. Solar Powered Battery Charger

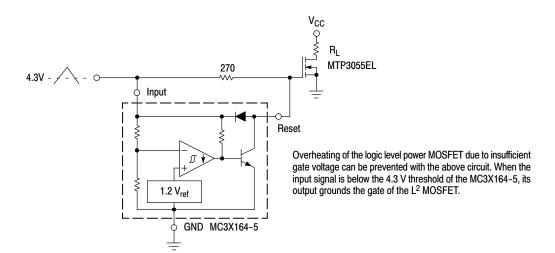

Figure 18. MOSFET Low Voltage Gate Drive Protection Using the MC3X164-5

### **ORDERING INFORMATION**

| Device          | Package             | Shipping <sup>†</sup>    |

|-----------------|---------------------|--------------------------|

| MC33164D-3G     | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |

| MC33164D-3R2G   | SOIC-8<br>(Pb-Free) | 2500 Unite / Tana & Deel |

| NCV33164D-3R2G* | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |

| MC33164DM-3R2G  | Micro8<br>(Pb-Free) | 4000 Units / Tape & Reel |

| MC33164P-3G     | TO-92<br>(Pb-Free)  | 2000 Units / Box         |

| MC33164P-3RAG   | TO-92<br>(Pb-Free)  | 2000 Units / Tape & Reel |

| MC33164P-3RPG   | TO-92<br>(Pb-Free)  | 2000 Units / Pack        |

| MC33164D-5G     | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |

| MC33164D-5R2G   | SOIC-8<br>(Pb-Free) |                          |

| NCV33164D-5R2G* | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |

| MC33164DM-5R2G  | Micro8<br>(Pb-Free) | 4000 Units / Tape & Reel |

| MC33164P-5G     | TO-92<br>(Pb-Free)  | 2000 Units / Box         |

| MC33164P-5RAG   | TO-92<br>(Pb-Free)  | 2000 Units / Tape & Reel |

| MC33164P-5RPG   | TO-92<br>(Pb-Free)  | 2000 Units / Pack        |

| MC34164D-3G     | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |

| MC34164D-3R2G   | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |

| MC34164DM-3R2G  | Micro8<br>(Pb-Free) | 4000 Units / Tape & Reel |

| MC34164P-3G     | TO-92<br>(Pb-Free)  | 2000 Units / Box         |

| MC34164P-3RPG   | TO-92<br>(Pb-Free)  | 2000 Units / Pack        |

| MC34164D-5G     | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |

| MC34164D-5R2G   | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |

| MC34164DM-5R2G  | Micro8<br>(Pb-Free) | 4000 Units / Tape & Reel |

| MC34164SN-5T1G  | TSOP-5<br>(Pb-Free) | 3000 Units / Tape & Reel |

| MC34164P-5G     | TO-92<br>(Pb-Free)  | 2000 Units / Box         |

| MC34164P-5RAG   | TO-92<br>(Pb-Free)  | 2000 Units / Tape & Reel |

| MC34164P-5RPG   | TO-92<br>(Pb-Free)  | 2000 Units / Pack        |

|                 | ( /                 |                          |

<sup>\*</sup>NCV33164:  $T_{low} = -40$ °C,  $T_{high} = +125$ °C. Guaranteed by design. NCV prefix is for automotive and other applications requiring site and change control.

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

## PIN CONNECTIONS AND MARKING DIAGRAMS

SOIC-8 D SUFFIX CASE 751

Micro8 MC33164DM CASE 846A

Micro8 MC34164DM CASE 846A

TO-92 MC3x164P-yRA MC3x164P-yRP MC3x164P-y CASE 29

SRC = Device Code

x = Device Number 3 or 4 y = Suffix Number 3 or 5 A = Assembly Location

L = Wafer Lot Y = Year W = Work Week ■ = Pb-Free

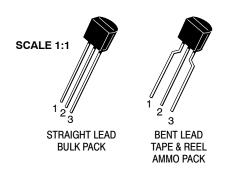

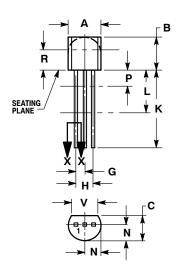

**TO-92 (TO-226)** CASE 29-11 **ISSUE AM**

**DATE 09 MAR 2007**

STRAIGHT LEAD **BULK PACK**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. CONTOUR OF PACKAGE BEYOND DIMENSION R IS UNCONTROLLED.

4. LEAD DIMENSION IS UNCONTROLLED IN P AND BEYOND DIMENSION K MINIMUM.

|     | INC   | HES   | MILLIN | IETERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   | 0.175 | 0.205 | 4.45   | 5.20   |

| В   | 0.170 | 0.210 | 4.32   | 5.33   |

| С   | 0.125 | 0.165 | 3.18   | 4.19   |

| D   | 0.016 | 0.021 | 0.407  | 0.533  |

| G   | 0.045 | 0.055 | 1.15   | 1.39   |

| Н   | 0.095 | 0.105 | 2.42   | 2.66   |

| J   | 0.015 | 0.020 | 0.39   | 0.50   |

| K   | 0.500 |       | 12.70  |        |

| L   | 0.250 |       | 6.35   |        |

| N   | 0.080 | 0.105 | 2.04   | 2.66   |

| Р   |       | 0.100 |        | 2.54   |

| R   | 0.115 |       | 2.93   |        |

| ٧   | 0.135 |       | 3.43   |        |

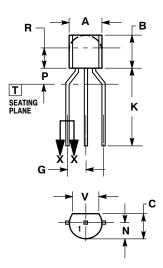

**BENT LEAD** TAPE & REEL AMMO PACK

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. CONTOUR OF PACKAGE BEYOND DIMENSION R IS UNCONTROLLED.

4. LEAD DIMENSION IS UNCONTROLLED IN P AND BEYOND DIMENSION K MINIMUM.

|     | MILLIMETERS |      |  |  |  |  |

|-----|-------------|------|--|--|--|--|

| DIM | MIN         | MAX  |  |  |  |  |

| Α   | 4.45        | 5.20 |  |  |  |  |

| В   | 4.32        | 5.33 |  |  |  |  |

| С   | 3.18        | 4.19 |  |  |  |  |

| D   | 0.40        | 0.54 |  |  |  |  |

| G   | 2.40        | 2.80 |  |  |  |  |

| J   | 0.39        | 0.50 |  |  |  |  |

| K   | 12.70       |      |  |  |  |  |

| N   | 2.04        | 2.66 |  |  |  |  |

| P   | 1.50        | 4.00 |  |  |  |  |

| R   | 2.93        |      |  |  |  |  |

| v   | 3 43        |      |  |  |  |  |

## **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42022B               | Electronic versions are uncontrolle                                  | '           |

|------------------|---------------------------|----------------------------------------------------------------------|-------------|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document versions are uncontrolled except |             |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                            |             |

| DESCRIPTION:     | TO-92 (TO-226)            |                                                                      | PAGE 1 OF 3 |

# **TO-92 (TO-226)** CASE 29-11

# ISSUE AM

# DATE 09 MAR 2007

| STYLE 1:<br>PIN 1.<br>2.<br>3. | EMITTER<br>BASE<br>COLLECTOR        | STYLE 2:<br>PIN 1.<br>2.<br>3.  | BASE<br>EMITTER<br>COLLECTOR               | STYLE 3:<br>PIN 1.<br>2.<br>3.  | ANODE<br>ANODE<br>CATHODE           | STYLE 4:<br>PIN 1.<br>2.<br>3.  | CATHODE<br>CATHODE<br>ANODE           | STYLE 5:<br>PIN 1.<br>2.<br>3.  | DRAIN         |

|--------------------------------|-------------------------------------|---------------------------------|--------------------------------------------|---------------------------------|-------------------------------------|---------------------------------|---------------------------------------|---------------------------------|---------------|

| 2.                             | GATE<br>SOURCE & SUBSTRATE<br>DRAIN | STYLE 7:<br>PIN 1.<br>2.<br>3.  | SOURCE<br>DRAIN<br>GATE                    | STYLE 8:<br>PIN 1.<br>2.<br>3.  | DRAIN<br>GATE<br>SOURCE & SUBSTRATE | PIN 1.                          | BASE 1                                |                                 | CATHODE       |

| 2.                             | ANODE<br>CATHODE & ANODE<br>CATHODE | STYLE 12:<br>PIN 1.<br>2.<br>3. | MAIN TERMINAL 1<br>GATE<br>MAIN TERMINAL 2 | PIN 1.                          | ANODE 1                             | PIN 1.                          | EMITTER<br>COLLECTOR<br>BASE          | PIN 1.<br>2.                    |               |

| 2.                             | ANODE<br>GATE                       | PIN 1.<br>2.                    | COLLECTOR<br>BASE                          | PIN 1.<br>2.                    | ANODE<br>CATHODE                    | PIN 1.<br>2.                    | GATE                                  | 2.                              | NOT CONNECTED |

| 2.                             | COLLECTOR                           | PIN 1.<br>2.                    | SOURCE<br>GATE<br>DRAIN                    | STYLE 23:<br>PIN 1.<br>2.<br>3. | GATE<br>SOURCE<br>DRAIN             | STYLE 24:<br>PIN 1.<br>2.<br>3. | EMITTER<br>COLLECTOR/ANODE<br>CATHODE | STYLE 25:<br>PIN 1.<br>2.<br>3. | MT 1<br>GATE  |

|                                | V <sub>CC</sub>                     | PIN 1.<br>2.                    | MT                                         | STYLE 28:<br>PIN 1.<br>2.       | CATHODE<br>ANODE<br>GATE            | STYLE 29:<br>PIN 1.<br>2.       |                                       | PIN 1.<br>2.                    | DRAIN         |

|                                | GATE                                | PIN 1.<br>2.                    |                                            | STYLE 33:<br>PIN 1.<br>2.<br>3. | RETURN                              | 2.                              |                                       |                                 |               |

| DOCUMENT NUMBER: | 98ASB42022B               | Electronic versions are uncontrolle                                  | '           |

|------------------|---------------------------|----------------------------------------------------------------------|-------------|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document versions are uncontrolled except | ' '         |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                            |             |

| DESCRIPTION:     | TO-92 (TO-226)            |                                                                      | PAGE 2 OF 3 |

| <b>DOCUMENT</b> | NUMBER: |

|-----------------|---------|

| 08 V S B 42022  | R       |

PAGE 3 OF 3

| ISSUE | REVISION                                                | DATE        |

|-------|---------------------------------------------------------|-------------|

| AM    | ADDED BENT-LEAD TAPE & REEL VERSION. REQ. BY J. SUPINA. | 09 MAR 2007 |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

|       |                                                         |             |

ON Semiconductor and 💵 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. arising out of the application of use of any product or circuit, and specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death. associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

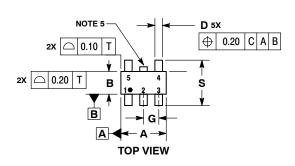

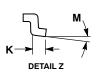

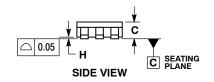

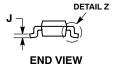

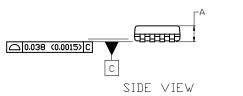

TSOP-5 **CASE 483 ISSUE N**

**DATE 12 AUG 2020**

### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME

- CONTROLLING DIMENSION: MILLIMETERS.

MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH

THICKNESS. MINIMUM LEAD THICKNESS IS THE

MINIMUM THICKNESS OF BASE MATERIAL.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION A. OPTIONAL CONSTRUCTION: AN ADDITIONAL

- TRIMMED LEAD IS ALLOWED IN THIS LOCATION. TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2 FROM BODY.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 2.85        | 3.15 |  |

| В   | 1.35        | 1.65 |  |

| C   | 0.90        | 1.10 |  |

| D   | 0.25        | 0.50 |  |

| G   | 0.95 BSC    |      |  |

| Н   | 0.01        | 0.10 |  |

| J   | 0.10        | 0.26 |  |

| K   | 0.20        | 0.60 |  |

| М   | 0 °         | 10 ° |  |

| S   | 2 50        | 3.00 |  |

### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code XXX = Specific Device Code

= Assembly Location = Date Code = Year = Pb-Free Package

= Work Week W = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: 98ARB18753C |        | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:                 | TSOP-5 |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

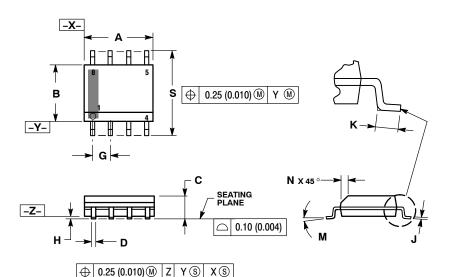

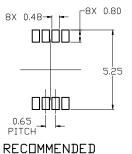

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INC       | HES   |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |

## **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week = Pb-Free Package XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α

= Year ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the I Printed versions are uncontrolled except when stamped "CONTROLLED COP" |           |  |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|-------------|

| DESCRIPTION:                                                                                                                                                                      | SOIC-8 NB |  | PAGE 1 OF 2 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

## SOIC-8 NB CASE 751-07 ISSUE AK

# DATE 16 FEB 2011

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     | 27112 101 22 2                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            |                                                                                                                                                                         |

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1                              |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | 8. DHAIN 1  STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON   | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| 6. VEE 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                   | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | a COLLECTOR/ANODE                                                                                                                                                       |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                         |

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     |                                                                                                                                                                         |

| DOCUMENT NUMBER: | 98ASB42564B Printed versions are uncontrolled except when stamped "CONTROLLED COPY" |  | ' '         |

|------------------|-------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | SOIC-8 NB                                                                           |  | PAGE 2 OF 2 |

ON Semiconductor and IN are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

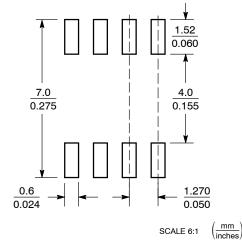

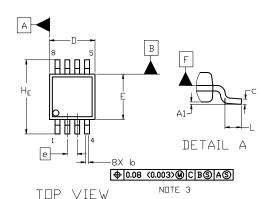

### Micro8 CASE 846A-02 ISSUE K

**DATE 16 JUL 2020**

### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10 mm IN EXCESS OF MAXIMUM MATERIAL CONDITION.

- 4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 mm PER SIDE. DIMENSION E DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 mm PER SIDE. DIMENSIONS D AND E ARE DETERMINED AT DATUM F.

- 5. DATUMS A AND B ARE TO BE DETERMINED AT DATUM F.

- 6. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

MOUNTING FOOTPRINT

| DIM   | MILLIMETERS |      |      |

|-------|-------------|------|------|

| ויונע | MIN.        | N□M. | MAX. |

| Α     |             |      | 1.10 |

| A1    | 0.05        | 0.08 | 0.15 |

| b     | 0.25        | 0.33 | 0.40 |

| С     | 0.13        | 0.18 | 0.23 |

| D     | 2.90        | 3.00 | 3.10 |

| E     | 2.90        | 3.00 | 3.10 |

| е     | 0.65 BSC    |      |      |

| HE    | 4.75        | 4.90 | 5.05 |

| L     | 0.40        | 0.55 | 0.70 |

# GENERIC MARKING DIAGRAM\*

XXXX = Specific Device Code A = Assembly Location

Y = Year W = Work Week • = Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| STYLE 1:                 | STYLE 2:                   | STYLE 3:                   |

|--------------------------|----------------------------|----------------------------|

| PIN 1. SOURCE            | PIN 1. SOURCE 1            | PIN 1. N-SOURCE            |

| <ol><li>SOURCE</li></ol> | 2. GATE 1                  | 2. N-GATE                  |

| <ol><li>SOURCE</li></ol> | <ol><li>SOURCE 2</li></ol> | <ol><li>P-SOURCE</li></ol> |

| <ol><li>GATE</li></ol>   | 4. GATE 2                  | 4. P-GATE                  |

| <ol><li>DRAIN</li></ol>  | 5. DRAIN 2                 | 5. P-DRAIN                 |

| <ol><li>DRAIN</li></ol>  | 6. DRAIN 2                 | 6. P-DRAIN                 |

| 7. DRAIN                 | 7. DRAIN 1                 | 7. N-DRAIN                 |

| 8. DRAIN                 | 8. DRAIN 1                 | 8. N-DRAIN                 |

| DOCUMENT NUMBER: | 98ASB14087C | D87C Electronic versions are uncontrolled except when accessed directly from the Document Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | MICRO8      |                                                                                                                                                                           | PAGE 1 OF 1 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Supervisory Circuits category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

CAT1161LI-25-G CAT853STBI-T3 CAT1026LI-30-G CAT1320LI-25-G TC54VN2402EMB713 MCP1316T-44NE/OT MCP1316MT-45GE/OT MCP1316MT-23LI/OT MAX8997EWW+ MAX6725AKASYD3-LF-T DS1232L NCV302HSN45T1G PT7M6130NLTA3EX PT7M7811STBEX-2017 S-1000N28-I4T1U CAT1161LI-28-G MCP1321T-29AE/OT MCP1319MT-47QE/OT S-1000N23-I4T1U S-1000N19-I4T1U CAT824UTDI-GT3 TC54VC2502ECB713 PT7M6133NLTA3EX PT7M6127NLTA3EX VDA2510NTA AP0809ES3-r HG811RM4/TR MD7030C MD7033C MD7019 MD7020 MD7021 MD7023 MD7024 MD7027 MD7030 MD7033 MD7035 MD7036 MD7039 MD7040 MD7044 MD7050 MD7015 MD7022 MD7028 MD7031 MD7042 MD7043 MD7047