# **Voltage Regulator** - Adjustable Output, Low Dropout

### 800 mA

The MC33269/NCV33269 series are low dropout, medium current, fixed and adjustable, positive voltage regulators specifically designed for use in low input voltage applications. These devices offer the circuit designer an economical solution for precision voltage regulation, while keeping power losses to a minimum.

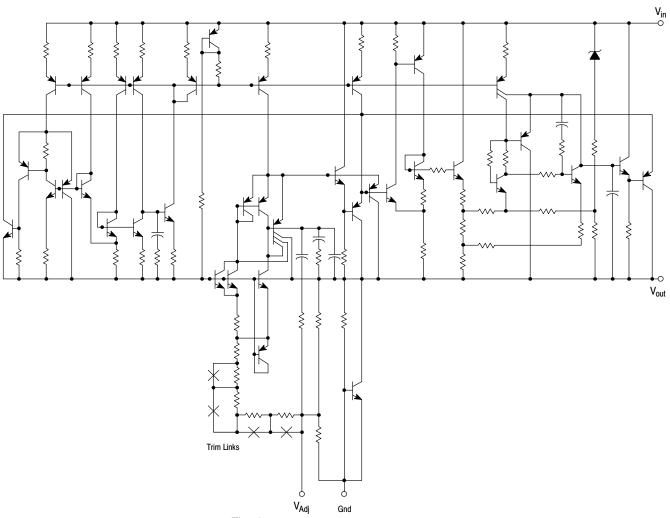

The regulator consists of a 1.0 V dropout composite PNP–NPN pass transistor, current limiting, and thermal shutdown.

### **Features**

- 3.3 V, 3.5 V, 5.0 V, 12 V and Adjustable Versions 2.85 V version available as MC34268

- Space Saving DPAK, SO-8 and SOT-223 Power Packages

- 1.0 V Dropout

- Output Current in Excess of 800 mA

- Thermal Protection

- Short Circuit Protection

- Output Trimmed to 1.0% Tolerance

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb-Free Devices

### **DEVICE TYPE/NOMINAL OUTPUT VOLTAGE**

| MC33269D          | Adj   | MC33269T-3.5      | 3.5 V |

|-------------------|-------|-------------------|-------|

| NCV33269D*        | Adj   | MC33269D-5.0      | 5.0 V |

| MC33269DT         | Adj   | MC33269DT-5.0     | 5.0 V |

| NCV33269DTRK*     | Adj   | NCV33269DT-5.0*   | 5.0 V |

| MC33269T          | Adj   | NCV33269DTRK-5.0* | 5.0 V |

| MC33269D-3.3      | 3.3 V | MC33269T-5.0      | 5.0 V |

| MC33269DT-3.3     | 3.3 V | MC33269D-012      | 12 V  |

| NCV33269DTRK-3.3* | 3.3 V | MC33269DT-012     | 12 V  |

| MC33269T-3.3      | 3.3 V | NCV33269DTRK-012* | 12 V  |

| MC33269ST-3.3     | 3.3 V | MC33269T-012      | 12 V  |

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

### ON Semiconductor®

http://onsemi.com

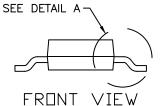

DPAK DT SUFFIX CASE 369C

SOT-223 ST SUFFIX CASE 318E

Heatsink surface (shown as terminal 4 in case outline drawing) is connected to Pin 2.

Heatsink surface (shown as terminal 4 in case outline drawing) is connected to Pin 2.

### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.

### **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 8 of this data sheet.

### **MAXIMUM RATINGS**

|                                                      | Rating                                                                                                   | Symbol                                                          | Value                           | Unit              |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|-------------------|

| Power Supply Input Voltage                           |                                                                                                          | V <sub>in</sub>                                                 | 20                              | V                 |

| Power Dissipation                                    |                                                                                                          |                                                                 |                                 |                   |

| Case 369C (DPAK)                                     | T <sub>A</sub> = 25°C<br>Thermal Resistance, Junction-to-Ambient<br>Thermal Resistance, Junction-to-Case | ${\sf P}_{\sf D} \ {\sf 	heta}_{\sf JA} \ {\sf 	heta}_{\sf JC}$ | Internally Limited<br>92<br>6.0 | °C/W              |

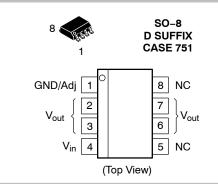

| Case 751 (SO-8)                                      | T <sub>A</sub> = 25°C<br>Thermal Resistance, Junction-to-Ambient<br>Thermal Resistance, Junction-to-Case | P <sub>D</sub><br>θ <sub>JA</sub><br>θ,IC                       | Internally Limited<br>160<br>25 | °C/W              |

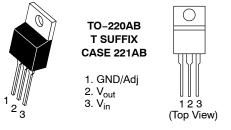

| Case 221A (TO-220)                                   | T <sub>A</sub> = 25°C<br>Thermal Resistance, Junction-to-Ambient<br>Thermal Resistance, Junction-to-Case | P <sub>D</sub><br>θJA<br>θJC                                    | Internally Limited<br>65<br>5.0 | °C/W              |

| Case 318E (SOT-223)                                  | T <sub>A</sub> = 25°C<br>Thermal Resistance, Junction-to-Ambient<br>Thermal Resistance, Junction-to-Case | P <sub>D</sub><br>θ <sub>JA</sub><br>θ <sub>JC</sub>            | Internally Limited<br>156<br>15 | W<br>°C/W<br>°C/W |

| Operating Die Junction Tem                           | perature Range                                                                                           | TJ                                                              | -40 to +150                     | °C                |

| Operating Ambient Temperature Range MC33269 NCV33269 |                                                                                                          | T <sub>A</sub>                                                  | -40 to +125<br>-40 to +125      | °C                |

| Storage Temperature                                  |                                                                                                          | T <sub>stg</sub>                                                | -55 to +150                     | °C                |

| Electrostatic Discharge Sens                         | sitivity (ESD) Human Body Model (HBM)<br>Machine Model (MM)                                              | ESD                                                             | 4000<br>400                     | V                 |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

### $\textbf{ELECTRICAL CHARACTERISTICS} \ (C_O = 10 \ \mu\text{F}, \ T_A = 25^{\circ}\text{C}, \ \text{for min/max values} \ T_A = -40^{\circ}\text{C to} \ +125^{\circ}\text{C}, \ \text{unless otherwise noted.})$

| Characteristic                                                                                                                                                                                                                                                                                                                                                        | Symbol                             | Min                            | Тур                     | Max                            | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------|-------------------------|--------------------------------|------|

| Output Voltage ( $I_{out}$ = 10 mA, $T_A$ = 25°C)<br>3.3 Suffix ( $V_{CC}$ = 5.3 V)<br>3.5 Suffix ( $V_{CC}$ = 5.5 V)<br>5.0 Suffix ( $V_{CC}$ = 7.0 V)<br>12 Suffix ( $V_{CC}$ = 14 V)                                                                                                                                                                               | Vo                                 | 3.27<br>3.465<br>4.95<br>11.88 | 3.3<br>3.5<br>5.0<br>12 | 3.33<br>3.535<br>5.05<br>12.12 | V    |

| Output Voltage (Line, Load and Temperature) (Note 1) $ (1.25 \text{ V} \leq \text{V}_{in} - \text{V}_{out} \leq 15 \text{ V}, \text{I}_{out} = 500 \text{ mA}) \\ (1.35 \text{ V} \leq \text{V}_{in} - \text{V}_{out} \leq 10 \text{ V}, \text{I}_{out} = 800 \text{ mA}) \\ 3.3 \text{ Suffix} \\ 3.5 \text{ Suffix} \\ 5.0 \text{ Suffix} \\ 12 \text{ Suffix} \\ $ | Vo                                 | 3.23<br>3.43<br>4.90<br>11.76  | 3.3<br>3.5<br>5.0<br>12 | 3.37<br>3.57<br>5.10<br>12.24  | V    |

| Reference Voltage for Adjustable Voltage (I <sub>out</sub> = 10 mA, V <sub>in</sub> – V <sub>out</sub> = 2.0 V, T <sub>A</sub> = 25°C)                                                                                                                                                                                                                                | V <sub>ref</sub>                   | 1.235                          | 1.25                    | 1.265                          | V    |

| Reference Voltage (Line, Load and Temperature) (Note 1) for Adjustable Voltage (1.25 V $\leq$ V <sub>in</sub> $-$ V <sub>out</sub> $\leq$ 15 V, I <sub>out</sub> = 500 mA) (1.35 V $\leq$ V <sub>in</sub> $-$ V <sub>out</sub> $\leq$ 10 V, I <sub>out</sub> = 800 mA)                                                                                                | V <sub>ref</sub>                   | 1.225                          | 1.25                    | 1.275                          | V    |

| Line Regulation ( $I_{out}$ = 10 mA, $V_{in}$ = [ $V_{out}$ + 1.5 V] to $V_{in}$ = 20 V, $T_A$ = 25°C)                                                                                                                                                                                                                                                                | Reg <sub>line</sub>                | -                              | _                       | 0.3                            | %    |

| Load Regulation $(V_{in} = V_{out} + 3.0 \text{ V}, I_{out} = 10 \text{ mA to } 800 \text{ mA}, T_A = 25^{\circ}\text{C})$                                                                                                                                                                                                                                            | Reg <sub>load</sub>                | -                              | _                       | 0.5                            | %    |

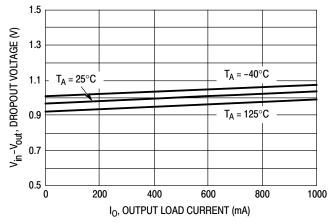

| Dropout Voltage $ \begin{aligned} \text{(I}_{\text{out}} &= 500 \text{ mA)} \\ \text{(I}_{\text{out}} &= 800 \text{ mA)} \end{aligned} $                                                                                                                                                                                                                              | V <sub>in</sub> – V <sub>out</sub> | -<br>-                         | 1.0<br>1.1              | 1.25<br>1.35                   | V    |

| Ripple Rejection (10 $V_{pp}$ , 120 Hz Sinewave; $I_{out}$ = 500 mA)                                                                                                                                                                                                                                                                                                  | RR                                 | 55                             | -                       | _                              | dB   |

| Current Limit $(V_{in} - V_{out} = 10 \text{ V})$                                                                                                                                                                                                                                                                                                                     | I <sub>Limit</sub>                 | 800                            | -                       | _                              | mA   |

| Quiescent Current (Fixed Output) $ (1.5 \text{ V} \leq \text{V}_{out} \leq 3.5 \text{ V}) \\ (5 \text{ V} \leq \text{V}_{out} \leq 12 \text{ V}) $                                                                                                                                                                                                                    | IQ                                 | -<br>-                         | 5.5<br>-                | 8.0<br>20                      | mA   |

| Minimum Required Load Current Fixed Output Voltage Adjustable Voltage                                                                                                                                                                                                                                                                                                 | I <sub>Load</sub>                  | -<br>8.0                       | -<br>-                  | 0<br>-                         | mA   |

| Adjustment Pin Current                                                                                                                                                                                                                                                                                                                                                | I <sub>Adj</sub>                   | -                              | -                       | 120                            | μΑ   |

<sup>1.</sup> The MC33269–12, V<sub>in</sub> – V<sub>out</sub> is limited to 8.0 V maximum, because of the 20 V maximum rating applied to V<sub>in</sub>.

This device contains 38 active transistors.

Figure 1. Internal Schematic

100 OUTPUT OV OUTPUT OU

Figure 2. Dropout Voltage versus

Output Load Current

Figure 3. Transient Load Regulation

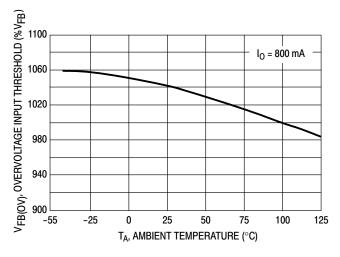

Figure 4. Dropout Voltage versus Temperature

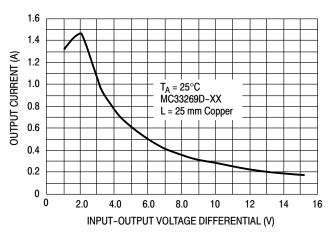

Figure 5. MC33269-XX Output DC Current versus Input-Output Differential Voltage

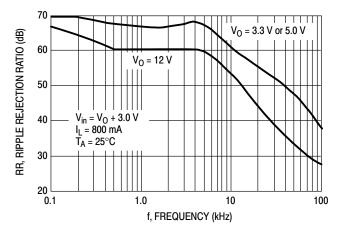

Figure 6. MC33269 Ripple Rejection versus Frequency

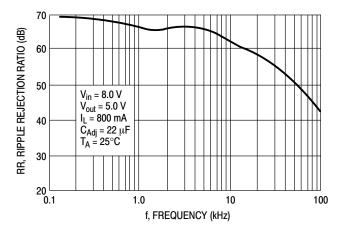

Figure 7. MC33269–ADJ Ripple Rejection versus Frequency

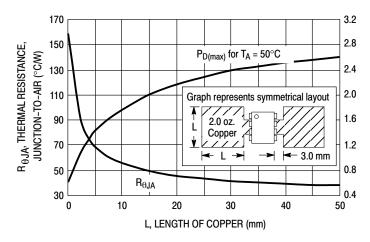

Figure 8. SOP-8 Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

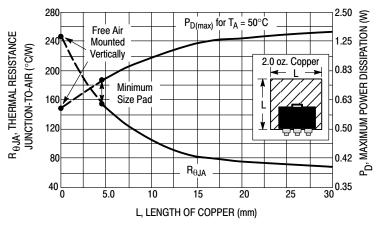

Figure 9. DPAK Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

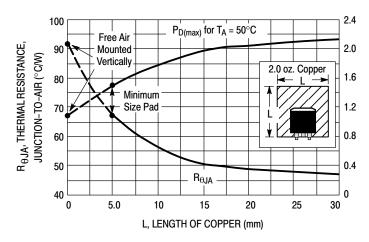

Figure 10. SOT-223 Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

### **APPLICATIONS INFORMATION**

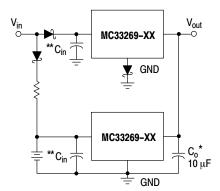

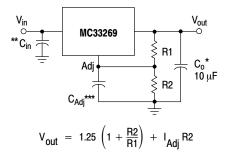

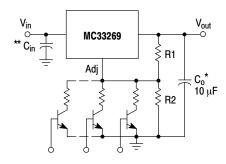

Figures 11 through 15 are typical application circuits. The output current capability of the regulator is in excess of 800 mA, with a typical dropout voltage of less than 1.0 V. Internal protective features include current and thermal limiting.

\* The MC33269 requires an external output capacitor for stability. The capacitor should be at least 10  $\mu F$  with an equivalent series resistance (ESR) of less than 10  $\Omega$  but greater than 0.2  $\Omega$  over the anticipated operating temperature range. With economical electrolytic capacitors, cold temperature operation can pose a problem. As temperature decreases, the capacitance also decreases and the ESR increases, which could cause the circuit to oscillate. Also capacitance and ESR of a solid tantalum capacitor is more stable over temperature. The use of a low ESR ceramic capacitor placed within close proximity to the output of the device could cause instability.

\*\* An input bypass capacitor is recommended to improve transient response or if the regulator is connected to the

An input capacitor is not necessary for stability, however it will improve the overall performance.

Figure 11. Typical Fixed Output Application

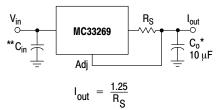

Figure 13. Current Regulator

The Schottky diode in series with the ground leg of the upper regulator shifts its output voltage higher by the forward voltage drop of the diode. This will cause the lower device to remain off until the input voltage is removed.

Figure 14. Battery Backed-Up Power Supply

supply input filter with long wire lengths. This will reduce the circuit's sensitivity to the input line impedance at high frequencies. A 0.33  $\mu F$  or larger tantalum, mylar, ceramic, or other capacitor having low internal impedance at high frequencies should be chosen. The bypass capacitor should be mounted with shortest possible lead or track length directly across the regulator's input terminals. Applications should be tested over all operating conditions to insure stability.

Internal thermal limiting circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 170°C, the output is disabled. There is no hysteresis built into the thermal limiting circuit. As a result, if the device is overheating, the output will appear to be oscillating. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heat–sinking.

\*\*\*C<sub>Adj</sub> is optional, however it will improve the ripple rejection. The MC34269 develops a 1.25 V reference voltage between the output and the adjust terminal. Resistor R1, operates with constant current to flow through it and resistor R2. This current should be set such that the Adjust Pin current causes negligible drop across resistor R2. The total current with minimum load should be greater than 8.0 mA.

Figure 12. Typical Adjustable Output Application

${\rm R}_2$  sets the maximum output voltage. Each transistor reduces the output voltage when turned on.

Figure 15. Digitally Controlled Voltage Regulator

### **ORDERING INFORMATION**

| Device            | Package              | Shipping Information <sup>†</sup> |

|-------------------|----------------------|-----------------------------------|

| MC33269DG         | SO-8<br>(Pb-Free)    | 98 Units / Rail                   |

| MC33269DR2G       | SO-8<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269DTG        | DPAK<br>(Pb-Free)    | 75 Units / Rail                   |

| MC33269DTRKG      | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269TG         | TO-220<br>(Pb-Free)  | 50 Units / Rail                   |

| MC33269D-3.3G     | SO-8<br>(Pb-Free)    | 98 Units / Rail                   |

| MC33269DR2-3.3G   | SO-8<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269DT-3.3G    | DPAK<br>(Pb-Free)    | 75 Units / Rail                   |

| MC33269DTRK-3.3G  | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269ST-3.3T3G  | SOT-223<br>(Pb-Free) | 4000 Units / Tape & Reel          |

| MC33269T-3.3G     | TO-220<br>(Pb-Free)  | 50 Units / Rail                   |

| MC33269T-3.5G     | TO-220<br>(Pb-Free)  | 50 Units / Rail                   |

| MC33269D-5.0G     | SO-8<br>(Pb-Free)    | 98 Units / Rail                   |

| MC33269DR2-5.0G   | SO-8<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269DT-5.0G    | DPAK<br>(Pb-Free)    | 75 Units / Rail                   |

| NCV33269DT-5.0G*  | DPAK<br>(Pb-Free)    | 75 Units / Rail                   |

| MC33269DTRK-5.0G  | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269T-5.0G     | TO-220<br>(Pb-Free)  | 50 Units / Rail                   |

| MC33269D-012G     | SO-8<br>(Pb-Free)    | 98 Units / Rail                   |

| MC33269DR2-012G   | SO-8<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269DT-012G    | DPAK<br>(Pb-Free)    | 75 Units / Rail                   |

| MC33269DTRK-012G  | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| MC33269T-012G     | TO-220<br>(Pb-Free)  | 50 Units / Rail                   |

| NCV33269DR2G*     | SO-8<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| NCV33269DTRKG*    | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| NCV33269DTRK3.3G* | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| NCV33269DTRK5.0G* | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

| NCV33269DTRK-12G* | DPAK<br>(Pb-Free)    | 2500 Units / Tape & Reel          |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

<sup>\*</sup>NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

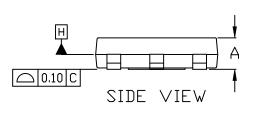

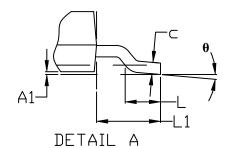

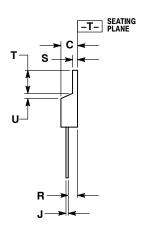

**SOT-223 (TO-261)** CASE 318E-04 ISSUE R

**DATE 02 OCT 2018**

### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSIONS D & E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.200MM PER SIDE.

- 4. DATUMS A AND B ARE DETERMINED AT DATUM H.

- 5. ALLIS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY.

- 6. POSITIONAL TOLERANCE APPLIES TO DIMENSIONS 6 AND 61.

|     | MILLIMETERS |          |      |  |

|-----|-------------|----------|------|--|

| DIM | MIN.        | N□M.     | MAX. |  |

| Α   | 1.50        | 1.63     | 1.75 |  |

| A1  | 0.02        | 0.06     | 0.10 |  |

| b   | 0.60        | 0.75     | 0.89 |  |

| b1  | 2.90        | 3.06     | 3.20 |  |

| c   | 0.24        | 0.29     | 0.35 |  |

| D   | 6.30        | 6.50     | 6.70 |  |

| E   | 3.30        | 3.50     | 3.70 |  |

| е   |             | 5'30 B2C | ,    |  |

| L   | 0.20        |          |      |  |

| L1  | 1.50        | 1.75     | 2.00 |  |

| He  | 6.70        | 7.00     | 7.30 |  |

| θ   | 0°          |          | 10°  |  |

RECOMMENDED MOUNTING FOOTPRINT

| DOCUMENT NUMBER: | 98ASB42680B      | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOT-223 (TO-261) |                                                                                                                                                                                   | PAGE 1 OF 2 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

### **SOT-223 (TO-261)** CASE 318E-04 ISSUE R

**DATE 02 OCT 2018**

| STYLE 1: PIN 1. BASE 2. COLLECTOR 3. EMITTER 4. COLLECTOR | STYLE 2: PIN 1. ANODE 2. CATHODE 3. NC 4. CATHODE            | STYLE 3:<br>PIN 1. GATE<br>2. DRAIN<br>3. SOURCE<br>4. DRAIN           | STYLE 4: PIN 1. SOURCE 2. DRAIN 3. GATE 4. DRAIN   | STYLE 5: PIN 1. DRAIN 2. GATE 3. SOURCE 4. GATE                |

|-----------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|

| STYLE 6: PIN 1. RETURN 2. INPUT 3. OUTPUT 4. INPUT        | STYLE 7: PIN 1. ANODE 1 2. CATHODE 3. ANODE 2 4. CATHODE     | STYLE 8: CANCELLED                                                     | STYLE 9: PIN 1. INPUT 2. GROUND 3. LOGIC 4. GROUND | STYLE 10:<br>PIN 1. CATHODE<br>2. ANODE<br>3. GATE<br>4. ANODE |

| STYLE 11:<br>PIN 1. MT 1<br>2. MT 2<br>3. GATE<br>4. MT 2 | STYLE 12:<br>PIN 1. INPUT<br>2. OUTPUT<br>3. NC<br>4. OUTPUT | STYLE 13:<br>PIN 1. GATE<br>2. COLLECTOR<br>3. EMITTER<br>4. COLLECTOR |                                                    |                                                                |

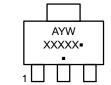

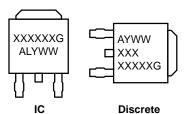

# GENERIC MARKING DIAGRAM\*

A = Assembly Location

Y = Year W = Work Week

$XXXXX \ = Specific \ Device \ Code$

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to

device data sheet for actual part marking.

Pb-Free indicator, "G" or microdot "•", may

or may not be present. Some products may

not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42680B      | Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOT-223 (TO-261) |                                                                                                                                                                                  | PAGE 2 OF 2 |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

### **MECHANICAL CASE OUTLINE PACKAGE DIMENSIONS**

ON Semiconductor®

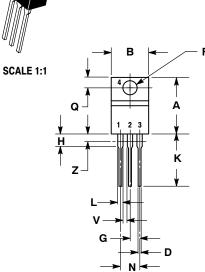

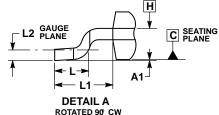

TO-220, SINGLE GAUGE CASE 221AB-01 **ISSUE A**

**DATE 16 NOV 2010**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCHES.

3. DIMENSION 2 DEFINES A ZONE WHERE ALL BODY AND LEAD INREGULARITIES ARE ALLOWED.

4. PRODUCT SHIPPED PRIOR TO 2008 HAD DIMENSIONS S = 0.045 0.055 INCHES (1.143 1.397 MM)

|     | INC   | HES   | MILLIN | IETERS |

|-----|-------|-------|--------|--------|

| DIM | MIN   | MAX   | MIN    | MAX    |

| Α   | 0.570 | 0.620 | 14.48  | 15.75  |

| В   | 0.380 | 0.405 | 9.66   | 10.28  |

| С   | 0.160 | 0.190 | 4.07   | 4.82   |

| D   | 0.025 | 0.035 | 0.64   | 0.88   |

| F   | 0.142 | 0.147 | 3.61   | 3.73   |

| G   | 0.095 | 0.105 | 2.42   | 2.66   |

| Н   | 0.110 | 0.155 | 2.80   | 3.93   |

| J   | 0.018 | 0.025 | 0.46   | 0.64   |

| K   | 0.500 | 0.562 | 12.70  | 14.27  |

| L   | 0.045 | 0.060 | 1.15   | 1.52   |

| N   | 0.190 | 0.210 | 4.83   | 5.33   |

| Q   | 0.100 | 0.120 | 2.54   | 3.04   |

| R   | 0.080 | 0.110 | 2.04   | 2.79   |

| S   | 0.020 | 0.024 | 0.508  | 0.61   |

| T   | 0.235 | 0.255 | 5.97   | 6.47   |

| U   | 0.000 | 0.050 | 0.00   | 1.27   |

| ٧   | 0.045 |       | 1.15   |        |

| Z   |       | 0.080 |        | 2.04   |

| STYLE 1: |           | STYLE 2:  |           | STYLE 3:  |         |

|----------|-----------|-----------|-----------|-----------|---------|

| PIN 1.   | BASE      | PIN 1.    | BASE      | PIN 1.    | CATHODE |

| 2.       | COLLECTOR | 2.        | EMITTER   | 2.        | ANODE   |

| 3.       | EMITTER   | 3.        | COLLECTOR | 3.        | GATE    |

| 4.       | COLLECTOR | 4.        | EMITTER   | 4.        | ANODE   |

| STYLE 5: |           | STYLE 6:  |           | STYLE 7:  |         |

| PIN 1.   | GATE      | PIN 1.    | ANODE     | PIN 1.    | CATHODE |

| 2.       | DRAIN     | 2.        | CATHODE   | 2.        | ANODE   |

| 3.       | SOURCE    | 3.        | ANODE     | 3.        | CATHODE |

| 4.       | DRAIN     | 4.        | CATHODE   | 4.        | ANODE   |

| STYLE 9: |           | STYLE 10: |           | STYLE 11: |         |

| PIN 1.   | GATE      | PIN 1.    | GATE      | PIN 1.    | DRAIN   |

| 2.       | COLLECTOR | 2.        | SOURCE    | 2.        | SOURCE  |

| 3.       | EMITTER   | 3.        | DRAIN     | 3.        | GATE    |

| 4.       | COLLECTOR | 4.        | SOURCE    | 4.        | SOURCE  |

|          |           |           |           |           |         |

| 3.       | MAIN TERMINAL 1<br>MAIN TERMINAL 2<br>GATE<br>MAIN TERMINAL 2 |

|----------|---------------------------------------------------------------|

| 2.<br>3. | CATHODE<br>ANODE<br>EXTERNAL TRIP/DELAY<br>ANODE              |

| DOCUMENT NUMBER: | 98AON23085D          | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TO-220, SINGLE GAUGE |                                                                                                                                                                                 | PAGE 1 OF 1 |  |

ON Semiconductor and III are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

**DATE 21 JUL 2015**

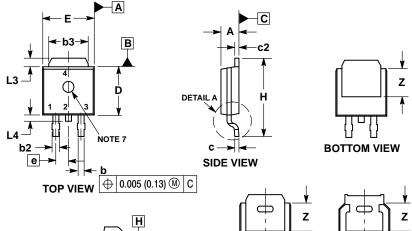

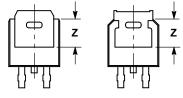

## **DPAK (SINGLE GAUGE)** CASE 369C ISSUE F SCALE 1:1 Α

**BOTTOM VIEW** ALTERNATE CONSTRUCTIONS

| STYLE 1: PIN 1. BASE 2. COLLECT 3. EMITTER 4. COLLECT | 3. SOUI      | N 2. CATH<br>RCE 3. ANO | HODE 2. ANODE<br>DE 3. GATE | STYLE 5:<br>PIN 1. GATE<br>2. ANODE<br>3. CATHODE<br>4. ANODE |

|-------------------------------------------------------|--------------|-------------------------|-----------------------------|---------------------------------------------------------------|

|                                                       | TYLE 7:      | STYLE 8:                | STYLE 9:                    | STYLE 10:                                                     |

|                                                       | PIN 1. GATE  | PIN 1. N/C              | PIN 1. ANODE                | PIN 1. CATHODE                                                |

|                                                       | 2. COLLECTOR | 2. CATHODE              | 2. CATHODE                  | 2. ANODE                                                      |

|                                                       | 3. EMITTER   | 3. ANODE                | 3. RESISTOR ADJUST          | 3. CATHODE                                                    |

|                                                       | 4. COLLECTOR | 4. CATHODE              | 4. CATHODE                  | 4. ANODE                                                      |

### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

- IOTES. 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: INCHES. 3. THERMAL PAD CONTOUR OPTIONAL WITHIN DI-

- MENSIONS b3, L3 and Z.

Jimensions b And E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.006 INCHES PER SIDE.

MENSIONS D AND E ARE DETERMINED AT THE

- OUTERMOST EXTREMES OF THE PLASTIC BODY.

6. DATUMS A AND B ARE DETERMINED AT DATUM

- 7. OPTIONAL MOLD FEATURE.

|     | INCHES      |       | MILLIM   | ETERS |

|-----|-------------|-------|----------|-------|

| DIM | MIN         | MAX   | MIN      | MAX   |

| Α   | 0.086       | 0.094 | 2.18     | 2.38  |

| A1  | 0.000       | 0.005 | 0.00     | 0.13  |

| b   | 0.025       | 0.035 | 0.63     | 0.89  |

| b2  | 0.028       | 0.045 | 0.72     | 1.14  |

| b3  | 0.180       | 0.215 | 4.57     | 5.46  |

| С   | 0.018       | 0.024 | 0.46     | 0.61  |

| c2  | 0.018       | 0.024 | 0.46     | 0.61  |

| D   | 0.235       | 0.245 | 5.97     | 6.22  |

| E   | 0.250       | 0.265 | 6.35     | 6.73  |

| е   | 0.090       | BSC   | 2.29 BSC |       |

| Н   | 0.370       | 0.410 | 9.40     | 10.41 |

| L   | 0.055       | 0.070 | 1.40     | 1.78  |

| L1  | 0.114 REF   |       | 2.90     | REF   |

| L2  | 0.020 BSC   |       | 0.51     | BSC   |

| L3  | 0.035 0.050 |       | 0.89     | 1.27  |

| L4  | 0.040       |       |          | 1.01  |

| Z   | 0.155       |       | 3.93     |       |

### **GENERIC MARKING DIAGRAM\***

XXXXXX = Device Code

= Assembly Location Α L = Wafer Lot Υ = Year

WW = Work Week G = Pb-Free Package

| DOCUMENT NUMBER:                             | 98AON10527D               | Electronic versions are uncontrolle         | • |

|----------------------------------------------|---------------------------|---------------------------------------------|---|

| STATUS:                                      | ON SEMICONDUCTOR STANDARD | versions are uncontrolled except when stamp |   |

| NEW STANDARD:                                | REF TO JEDEC TO-252       |                                             |   |

| DESCRIPTION: DPAK SINGLE GAUGE SURFACE MOUNT |                           | PAGE 1 OF 2                                 |   |

<sup>\*</sup>This information is generic. Please refer to device data sheet for actual part marking.

| <b>DOCUMENT</b> | NUMBER: |

|-----------------|---------|

| 98AON10527      | 7D      |

PAGE 2 OF 2

| ISSUE | REVISION                                                                                                                               | DATE        |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| 0     | RELEASED FOR PRODUCTION. REQ. BY L. GAN                                                                                                | 24 SEP 2001 |  |  |

| Α     | ADDED STYLE 8. REQ. BY S. ALLEN.                                                                                                       | 06 AUG 2008 |  |  |

| В     | ADDED STYLE 9. REQ. BY D. WARNER.                                                                                                      | 16 JAN 2009 |  |  |

| С     | ADDED STYLE 10. REQ. BY S. ALLEN.                                                                                                      | 09 JUN 2009 |  |  |

| D     | RELABELED DRAWING TO JEDEC STANDARDS. ADDED SIDE VIEW DETAIL A. CORRECTED MARKING INFORMATION. REQ. BY D. TRUHITTE.                    | 29 JUN 2010 |  |  |

| E     | ADDED ALTERNATE CONSTRUCTION BOTTOM VIEW. MODIFIED DIMENSIONS b2 AND L1. CORRECTED MARKING DIAGRAM FOR DISCRETE. REQ. BY I. CAMBALIZA. | 06 FEB 2014 |  |  |

| F     | ADDED SECOND ALTERNATE CONSTRUCTION BOTTOM VIEW. REQ. BY K. MUSTAFA.                                                                   | 21 JUL 2015 |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

|       |                                                                                                                                        |             |  |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

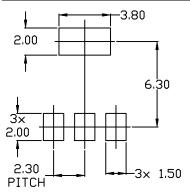

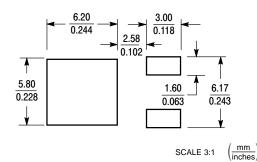

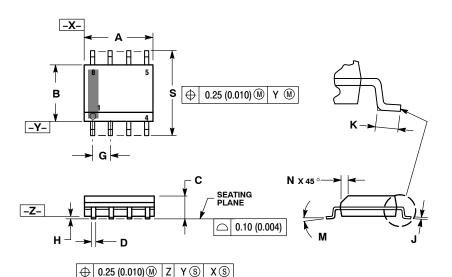

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | MILLIMETERS INCHES |       | HES |

|-----|-------------|------|--------------------|-------|-----|

| DIM | MIN         | MAX  | MIN                | MAX   |     |

| Α   | 4.80        | 5.00 | 0.189              | 0.197 |     |

| В   | 3.80        | 4.00 | 0.150              | 0.157 |     |

| С   | 1.35        | 1.75 | 0.053              | 0.069 |     |

| D   | 0.33        | 0.51 | 0.013              | 0.020 |     |

| G   | 1.27 BSC    |      | 0.050 BSC          |       |     |

| Н   | 0.10        | 0.25 | 0.004              | 0.010 |     |

| J   | 0.19        | 0.25 | 0.007              | 0.010 |     |

| K   | 0.40        | 1.27 | 0.016              | 0.050 |     |

| М   | 0 °         | 8 °  | 0 °                | 8 °   |     |

| N   | 0.25        | 0.50 | 0.010              | 0.020 |     |

| S   | 5.80        | 6.20 | 0.228              | 0.244 |     |

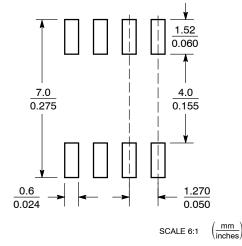

### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week = Pb-Free Package XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α

= Year ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repo<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                              | PAGE 1 OF 2 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

### SOIC-8 NB CASE 751-07 ISSUE AK

### DATE 16 FEB 2011

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     | 27112 101 22 2                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            |                                                                                                                                                                         |

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1                              |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | 8. DHAIN 1  STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON   | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| 6. VEE 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                   | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | a COLLECTOR/ANODE                                                                                                                                                       |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                         |

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     |                                                                                                                                                                         |

| DOCUMENT NUMBER: | : 98ASB42564B Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in |  | ' '         |

|------------------|------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | SOIC-8 NB                                                                                |  | PAGE 2 OF 2 |

ON Semiconductor and IN are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for ON Semiconductor manufacturer:

Other Similar products are found below:

1.5SMC82AT3G 74LCX574WM STK621-068C-E KAF-0402-ABA-CD-B2 NBXSBA017LN1TAG KAF-3200-ABA-CP-B2 STK621-728S-E AMIS30621AUA STK531U340A-E STK760-304-E FJAF6810DTU DBD250G STK621-713-E TIP115 LB11847-E NBXHBA017LN1TAG LV8736V-MPB-H NCP694H12HT1G LA4631VC-XE CAT1025WI-25-G NDF04N60ZG-001 LA78040B-S-E NGTB30N120IHLWG LA6584M-MPB-E NVB60N06T4G LA6245P-CL-TLM-E STK621-043D-E BTA30H-600CW3G NBXHBA017LNHTAG P6SMB100AT3G NCP1129AP100G LV8406T-TLM-E MC100EL13DWG NGTB30N60SWG FW217A-TL-2WX FGPF4533 MC33201DG KA78L05AZTA KA378R33TU FST3126MX LV4904V-MPB-E STK672-400 SBM30-03-TR-E NCP1398BDR2G BTA25H-600CW3G LC89057W-VF4A-E NGB8206ANTF4G NB7VQ58MMNG CPH6531-TL-E NCP4683DSQ28T1G