# 64 kb Low Power Serial **SRAMs**

# 8 k x 8 Bit Organization

#### Introduction

The ON Semiconductor serial SRAM family includes several integrated memory devices including this 64 k serially accessed Static Random Access Memory, internally organized as 8 k words by 8 bits. The devices are designed and fabricated using ON Semiconductor's advanced CMOS technology to provide both high-speed performance and low power. The devices operate with a single chip select  $(\overline{CS})$ input and use a simple Serial Peripheral Interface (SPI) serial bus. A single data in and data out line is used along with a clock to access data within the devices. The N64S818HA devices include a HOLD pin that allows communication to the device to be paused. While paused, input transitions will be ignored. The devices can operate over a wide temperature range of -40°C to +85°C and can be available in several standard package offerings.

#### **Features**

• Power Supply Range: 1.7 to 1.95 V

• Very Low Standby Current: As low as 200 nA • Very Low Operating Current: As low as 3 mA

• Simple Memory Control: Single chip select  $(\overline{CS})$ Serial input (SI) and serial output (SO)

• Flexible Operating Modes:

Word read and write Page mode (32 word page) Burst mode (full array)

• Organization: 8 k x 8 bit

• Self Timed Write Cycles

• Built-in Write Protection (CS High)

• **HOLD** Pin for Pausing Communication

• High Reliability: Unlimited write cycles

• Green SOIC and TSSOP

• These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

# ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAMS**

TSSOP-8 **T SUFFIX** CASE 948AL

SOIC-8 **S SUFFIX** CASE 751BD

XXXX = Date Code = Assembly Code ZZ = Lot Traceability

#### **ORDERING INFORMATION**

| Device         | Package              | Shipping <sup>†</sup> |

|----------------|----------------------|-----------------------|

| N64S818HAS21I  | SOIC-8<br>(Pb-Free)  | 100 Units / Tube      |

| N64S818HAT21I  | TSSOP-8<br>(Pb-Free) | 100 Units / Tube      |

| N64S818HAS21IT | SOIC-8<br>(Pb-Free)  | 3000 / Tape &<br>Reel |

| N64S818HAT21IT | TSSOP-8<br>(Pb-Free) | 3000 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

1

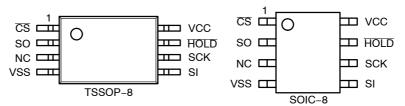

Figure 1. Pin Connections (Top View)

**Table 1. DEVICE OPTIONS**

| Part Number | Density | Power<br>Supply (V) | Speed (MHz) | Package | Typical Standby<br>Current | Read/Write<br>Operating Current |

|-------------|---------|---------------------|-------------|---------|----------------------------|---------------------------------|

| N64S818HAS2 | 64 Kb   | 1.8                 | 16          | SOIC    | 200 nA                     | 3 mA @ 1 Mhz                    |

| N64S818HAT2 | 04 ND   | 1.0                 | 10          | TSSOP   | 200 HA                     | 3 IIIA @ 1 IVIIIZ               |

**Table 2. PIN NAMES**

| Pin Name        | Pin Function       |

|-----------------|--------------------|

| CS              | Chip Select Input  |

| SCK             | Serial Clock Input |

| SI              | Serial Data Input  |

| SO              | Serial Data Output |

| HOLD            | Hold Input         |

| NC              | No Connect         |

| V <sub>CC</sub> | Power              |

| V <sub>SS</sub> | Ground             |

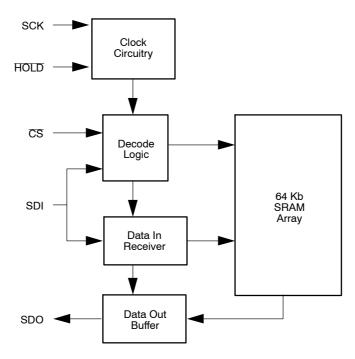

Figure 2. Functional Block Diagram

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Item                                                          | Symbol              | Rating                        | Unit |

|---------------------------------------------------------------|---------------------|-------------------------------|------|

| Voltage on any pin relative to V <sub>SS</sub>                | V <sub>IN,OUT</sub> | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> | V <sub>CC</sub>     | -0.3 to 4.5                   | V    |

| Power Dissipation                                             | P <sub>D</sub>      | 500                           | mW   |

| Storage Temperature                                           | T <sub>STG</sub>    | -40 to 125                    | °C   |

| Operating Temperature                                         | T <sub>A</sub>      | -40 to +85                    | °C   |

| Soldering Temperature and Time                                | T <sub>SOLDER</sub> | 260°C, 10 sec                 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 4. OPERATING CHARACTERISTICS (Over Specified Temperature Range)

| ltem                   | Symbol           | Test Conditions                                                                                                             | Min                   | Typ<br>(Note 1) | Max                   | Unit |

|------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-----------------------|------|

| Supply Voltage         | V <sub>CC</sub>  | 1.8 V Device                                                                                                                | 1.7                   |                 | 1.95                  | V    |

| Input High Voltage     | V <sub>IH</sub>  |                                                                                                                             | 0.7 x V <sub>CC</sub> |                 | V <sub>CC</sub> + 0.3 | V    |

| Input Low Voltage      | V <sub>IL</sub>  |                                                                                                                             | -0.3                  |                 | 0.8                   | V    |

| Output High Voltage    | V <sub>OH</sub>  | $I_{OH} = -0.4 \text{ mA}$                                                                                                  | V <sub>CC</sub> - 0.5 |                 |                       | ٧    |

| Output Low Voltage     | $V_{OL}$         | I <sub>OL</sub> = 1 mA                                                                                                      |                       |                 | 0.2                   | ٧    |

| Input Leakage Current  | l <sub>Ll</sub>  | $\overline{\text{CS}} = V_{\text{CC}}, V_{\text{IN}} = 0 \text{ to } V_{\text{CC}}$                                         |                       |                 | 0.5                   | μΑ   |

| Output Leakage Current | I <sub>LO</sub>  | $\overline{\text{CS}} = \text{V}_{\text{CC}},  \text{V}_{\text{OUT}} = 0 \text{ to V}_{\text{CC}}$                          |                       |                 | 0.5                   | μΑ   |

| Read/Write Operating   | I <sub>CC1</sub> | F = 1 MHz, I <sub>OUT</sub> = 0                                                                                             |                       |                 | 3                     | mA   |

| Current                | I <sub>CC2</sub> | F = 10 MHz, I <sub>OUT</sub> = 0                                                                                            |                       |                 | 6                     | mA   |

|                        | I <sub>CC3</sub> | F = fCLK MAX, I <sub>OUT</sub> = 0                                                                                          |                       |                 | 10                    | mA   |

| Standby Current        | I <sub>SB</sub>  | $\overline{\text{CS}} = \text{V}_{\text{CC}}, \text{V}_{\text{IN}} = \text{V}_{\text{SS}} \text{ or } \text{V}_{\text{CC}}$ |                       | 200             | 500                   | nA   |

<sup>1.</sup> Typical values are measured at Vcc = Vcc Typ.,  $T_A$  = 25°C and are not 100% tested.

# Table 5. CAPACITANCE (Note 2)

| Item              | Symbol           | Test Condition                                                        | Min | Max | Unit |

|-------------------|------------------|-----------------------------------------------------------------------|-----|-----|------|

| Input Capacitance | C <sub>IN</sub>  | $V_{IN}$ = 0 V, f = 1 MHz, $T_A$ = 25°C                               |     | 7   | pF   |

| I/O Capacitance   | C <sub>I/O</sub> | $V_{IN} = 0 \text{ V, f} = 1 \text{ MHz, T}_{A} = 25^{\circ}\text{C}$ |     | 7   | pF   |

<sup>2.</sup> These parameters are verified in device characterization and are not 100% tested

## **Table 6. TIMING TEST CONDITIONS**

| Item                                     |                                            |

|------------------------------------------|--------------------------------------------|

| Input Pulse Level                        | 0.1 V <sub>CC</sub> to 0.9 V <sub>CC</sub> |

| Input Rise and Fall Time                 | 5 ns                                       |

| Input and Output Timing Reference Levels | 0.5 V <sub>CC</sub>                        |

| Output Load                              | CL = 100 pF                                |

| Operating Temperature                    | −40 to +85°C                               |

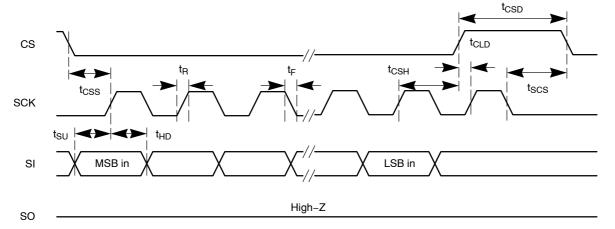

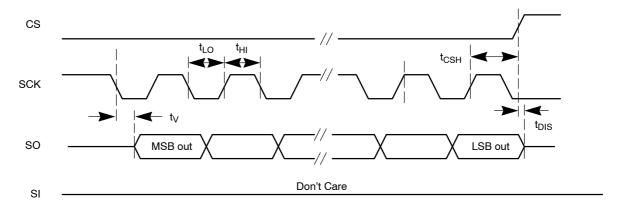

**Table 7. TIMING**

| Item                        | Symbol           | Min | Max | Units |

|-----------------------------|------------------|-----|-----|-------|

| Clock Frequency             | f <sub>CLK</sub> |     | 16  | MHz   |

| Clock Rise Time             | t <sub>R</sub>   |     | 2   | μs    |

| Clock Fall Time             | t <sub>F</sub>   |     | 2   | μs    |

| Clock High Time             | t <sub>HI</sub>  | 32  |     | ns    |

| Clock Low Time              | t <sub>LO</sub>  | 32  |     | ns    |

| Clock Delay Time            | t <sub>CLD</sub> | 32  |     | ns    |

| CS Setup Time               | t <sub>CSS</sub> | 32  |     | ns    |

| CS Hold Time                | t <sub>CSH</sub> | 50  |     | ns    |

| CS Disable Time             | t <sub>CSD</sub> | 32  |     | ns    |

| SCK to CS                   | t <sub>SCS</sub> | 5   |     | ns    |

| Data Setup Time             | t <sub>SU</sub>  | 10  |     | ns    |

| Data Hold Time              | t <sub>HD</sub>  | 10  |     | ns    |

| Output Valid From Clock Low | t <sub>V</sub>   |     | 32  | ns    |

| Output Hold Time            | t <sub>HO</sub>  | 0   |     | ns    |

| Output Disable Time         | t <sub>DIS</sub> |     | 20  | ns    |

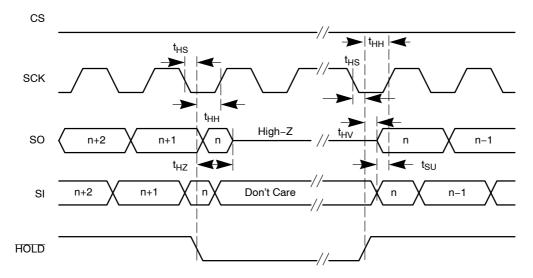

| HOLD Setup Time             | t <sub>HS</sub>  | 10  |     | ns    |

| HOLD Hold Time              | t <sub>HH</sub>  | 10  |     | ns    |

| HOLD Low to Output High-Z   | t <sub>HZ</sub>  | 10  |     | ns    |

| HOLD High to Output Valid   | t <sub>HV</sub>  |     | 50  | ns    |

Figure 3. Serial Input Timing

Figure 4. Serial Output Timing

Figure 5. Hold Timing

**Table 8. CONTROL SIGNAL DESCRIPTIONS**

| Signal | Name            | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------|-----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CS     | Chip Select     | I   | A low level selects the device and a high level puts the device in standby mode. If $\overline{\text{CS}}$ is brought high during a program cycle, the cycle will complete and then the device will enter standby mode When $\overline{\text{CS}}$ is high, SO is in high–Z. $\overline{\text{CS}}$ must be driven low after power–up prior to any sequence being started.                                                                                                                                                                                                                                                                                      |  |

| SCK    | Serial Clock    | I   | Synchronizes all activities between the memory and controller. All incoming addresses, data and instructions are latched on the rising edge of SCK. Data out is updated on SO after the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| SI     | Serial Data In  | I   | Receives instructions, addresses and data on the rising edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| SO     | Serial Data Out | 0   | Data is transferred out after the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| HOLD   | Hold            | I   | A high level is required for normal operation. Once the device is selected and a serial sequence is started, this input may be taken low to pause serial communication without resetting the serial sequence. The pin must be brought low while SCK is low for immediate use. If SCK is not low, the Hold function will not be invoked until the next SCK high to low transition. The device must remain selected during this sequence. SO is high–Z during the Hold time and SI and SCK are inputs are ignored. To resume operations, HOLD must be pulled high while the SCK pin is low. Lowering the HOLD input at any time will take to SO output to High–Z. |  |

#### **Functional Operation**

#### **Basic Operation**

The 64 Kb serial SRAM is designed to interface directly with a standard Serial Peripheral Interface (SPI) common on many standard micro-controllers. It may also interface with other non-SPI ports by programming discrete I/O lines to operate the device.

The serial SRAM contains an 8-bit instruction register and is accessed via the SI pin. The  $\overline{CS}$  pin must be low and the  $\overline{HOLD}$  pin must be high for the entire operation. Data is

sampled on the first rising edge of SCK after  $\overline{\text{CS}}$  goes low. If the clock line is shared, the user can assert the  $\overline{\text{HOLD}}$  input and place the device into a Hold mode. After releasing the  $\overline{\text{HOLD}}$  pin, the operation will resume from the point where it was held.

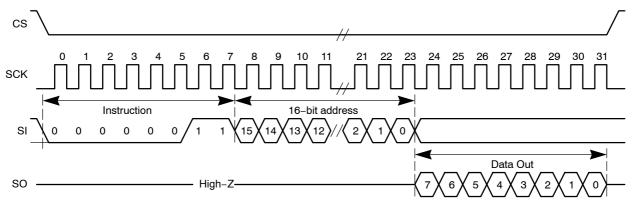

The following table contains the possible instructions and formats. All instructions, addresses and data are transferred MSB first and LSB last.

**Table 9. INSTRUCTION SET**

| Instruction | Instruction Format | Description                                        |  |  |  |  |

|-------------|--------------------|----------------------------------------------------|--|--|--|--|

| READ        | 0000 0011          | Read data from memory starting at selected address |  |  |  |  |

| WRITE       | 0000 0010          | Write data to memory starting at selected address  |  |  |  |  |

| RDSR        | 0000 0101          | Read status register                               |  |  |  |  |

| WRSR        | 0000 0001          | Write status register                              |  |  |  |  |

#### **READ Operations**

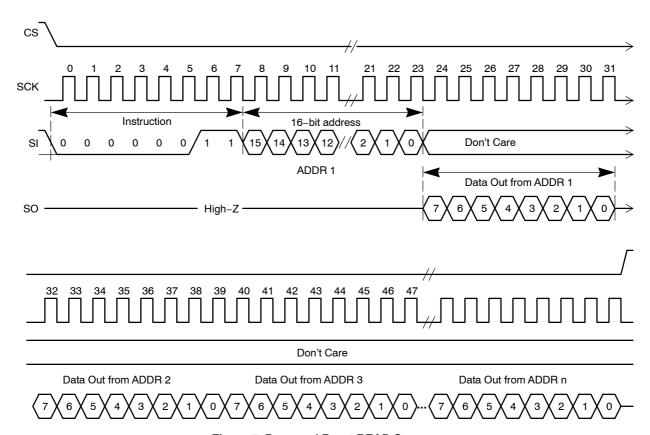

The serial SRAM READ is selected by enabling  $\overline{CS}$  low. First, the 8-bit READ instruction is transmitted to the device followed by the 16-bit address with the 3 MSBs being don't care. After the READ instruction and addresses are sent, the data stored at that address in memory is shifted out on the SO pin after the output valid time from the clock edge.

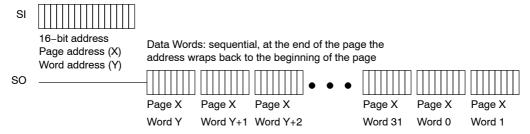

If operating in page mode, after the initial word of data is shifted out, the data stored at the next memory location on the page can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address on the page after each word of data is read out. This can be continued for the entire page length of 32 words long. At the end of the page, the

addresses pointer will be wrapped to the 0 word address within the page and the operation can be continuously looped over the 32 words of the same page.

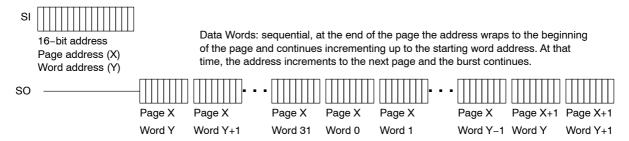

If operating in burst mode, after the initial word of data is shifted out, the data stored at the next memory location can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each word of data is read out. This can be continued for the entire array and when the highest address is reached (1FFFh), the address counter wraps to the address 0000h. This allows the burst read cycle to be continued indefinitely.

All READ operations are terminated by pulling  $\overline{\text{CS}}$  high.

Figure 6. Word READ Sequence

Figure 7. Page and Burst READ Sequence

Figure 8. Page READ Sequence

Figure 9. Burst READ Sequence

#### **WRITE Operations**

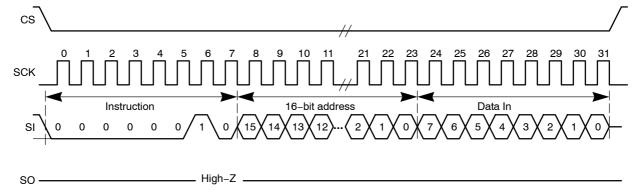

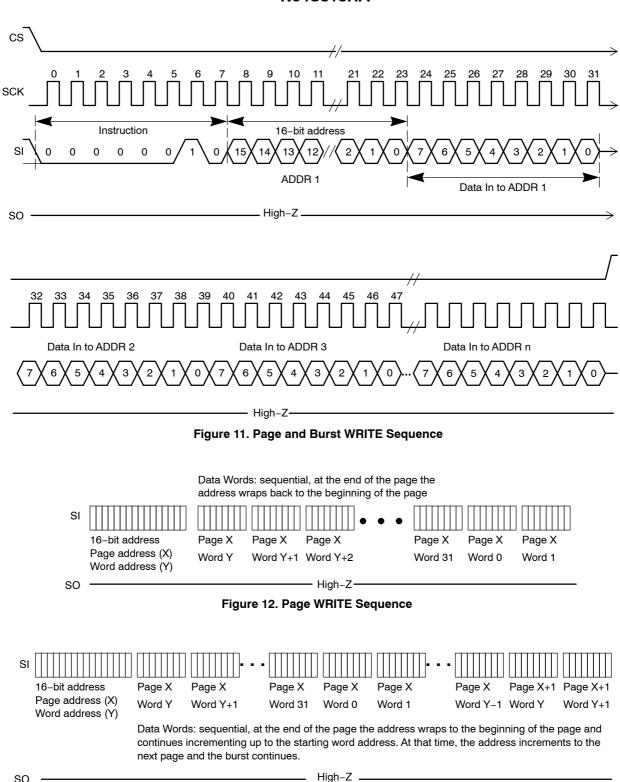

The serial SRAM WRITE is selected by enabling  $\overline{\text{CS}}$  low. First, the 8-bit WRITE instruction is transmitted to the device followed by the 16-bit address with the 3 MSBs being don't care. After the WRITE instruction and addresses are sent, the data to be stored in memory is shifted in on the SI pin.

If operating in page mode, after the initial word of data is shifted in, additional data words can be written as long as the address requested is sequential on the same page. Simply write the data on SI pin and continue to provide clock pulses. The internal address pointer is automatically incremented to the next higher address on the page after each word of data is written in. This can be continued for the entire page length of 32 words long. At the end of the page, the addresses pointer will be wrapped to the 0 word address within the

page and the operation can be continuously looped over the 32 words of the same page. The new data will replace data already stored in the memory locations.

If operating in burst mode, after the initial word of data is shifted in, additional data words can be written to the next sequential memory locations by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each word of data is read out. This can be continued for the entire array and when the highest address is reached (1FFFh), the address counter wraps to the address 0000h. This allows the burst write cycle to be continued indefinitely. Again, the new data will replace data already stored in the memory locations.

All WRITE operations are terminated by pulling  $\overline{CS}$  high.

Figure 10. Word WRITE Sequence

Figure 13. Burst WRITE Sequence

SO

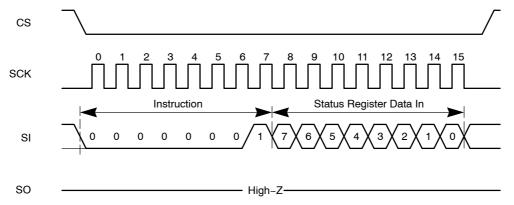

## **WRITE Status Register Instruction (WRSR)**

This instruction provides the ability to write the status register and select among several operating modes. Several of the register bits must be set to a low '0' if any of the other bits are written. The timing sequence to write to the status register is shown below, followed by the organization of the status register.

Figure 14. WRITE Status Register Sequence

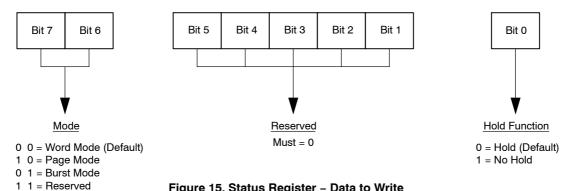

Figure 15. Status Register - Data to Write

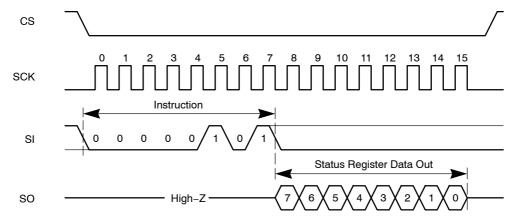

## **READ Status Register Instruction (RDSR)**

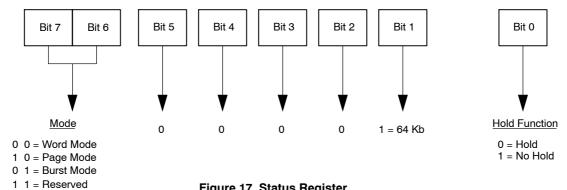

This instruction provides the ability to read the Status register. The register may be read at any time by performing the following timing sequence. Bits 0, 6 and 7 contain the data for the functional operation and Bit 1 will read data type '1' for the 64 Kb device.

Figure 16. READ Status Register Instruction (RDSR)

Figure 17. Status Register

## Power-Up State

The serial SRAM enters a know state at power-up time. The device is in low-power standby state with  $\overline{CS} = 1$ . A low level on  $\overline{CS}$  is required to enter an active state.

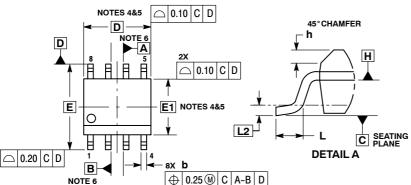

**DATE 18 MAY 2015**

NOTES 3&7

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.004 mm IN EXCESS OF MAXIMUM MATERIAL CONDITION.

- DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006 mm PER SIDE. DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.010 mm PER SIDE.

- THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM. DIMENSIONS D AND E1 ARE DETERMINED AT THE OUTER-MOST EXTREMES OF THE PLASTIC BODY AT DATUM H.

DIMENSIONS A AND B ARE TO BE DETERMINED AT DATUM H.

- DIMENSIONS 6 AND 6 APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 TO 0.25 FROM THE LEAD TIP.

- A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   |             | 1.75 |  |  |

| A1  | 0.10        | 0.25 |  |  |

| A2  | 1.25        |      |  |  |

| b   | 0.31        | 0.51 |  |  |

| С   | 0.10        | 0.25 |  |  |

| D   | 4.90 BSC    |      |  |  |

| E   | 6.00        | BSC  |  |  |

| E1  | 3.90        | BSC  |  |  |

| е   | 1.27        | BSC  |  |  |

| h   | 0.25        | 0.41 |  |  |

| L   | 0.40        | 1.27 |  |  |

| L2  | 0.25 BSC    |      |  |  |

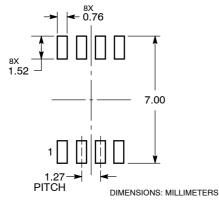

#### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC** MARKING DIAGRAM\*

XXXXX = Specific Device Code

= Assembly Location

L = Wafer Lot Υ = Year

W = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G", may or not be present.

| DOCUMENT NUMBER: | 98AON34918E | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8      |                                                                                                                                                                                 | PAGE 1 OF 1 |  |

are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor and ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

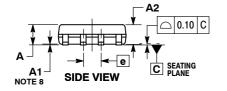

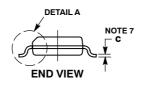

TSSOP-8 CASE 948S-01 ISSUE C

**DATE 20 JUN 2008**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI

- 714.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH.

PROTRUSIONS OR GATE BURRS. MOLD FLASH

- PROTRUSION S OF SAILE BORNES. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. 4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE

- 5. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- 6. DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIMETERS |                    | INCHES |           |  |

|-----|-------------|--------------------|--------|-----------|--|

| DIM | MIN         | MAX                | MIN    | MAX       |  |

| Α   | 2.90        | 3.10               | 0.114  | 0.122     |  |

| В   | 4.30        | 4.50               | 0.169  | 0.177     |  |

| С   |             | 1.10               |        | 0.043     |  |

| D   | 0.05        | 0.15               | 0.002  | 0.006     |  |

| F   | 0.50        | 0.70               | 0.020  | 0.028     |  |

| G   | 0.65        | 0.65 BSC           |        | 0.026 BSC |  |

| J   | 0.09        | 0.20               | 0.004  | 0.008     |  |

| J1  | 0.09        | 0.16               | 0.004  | 0.006     |  |

| K   | 0.19        | 0.30               | 0.007  | 0.012     |  |

| K1  | 0.19        | 0.25               | 0.007  | 0.010     |  |

| L   |             | 6.40 BSC 0.252 BSC |        | BSC       |  |

| М   | 0°          | 8°                 | 0°     | 8°        |  |

## **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code = Assembly Location Α

= Year WW = Work Week

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

= Pb-Free Package

| DOCUMENT NUMBER: | 98AON00697D               | Electronic versions are uncontrolled except when                                                         |

|------------------|---------------------------|----------------------------------------------------------------------------------------------------------|

| STATUS:          | ON SEMICONDUCTOR STANDARD | accessed directly from the Document Repository. Printed<br>versions are uncontrolled except when stamped |

| NEW STANDARD:    |                           | "CONTROLLED COPY" in red.                                                                                |

| DESCRIPTION:     | TSSOP-8                   | PAGE 1 OF 2                                                                                              |

**DETAIL E**

| DOCUMENT   | NUMBER: |

|------------|---------|

| 98AON00697 | 'D      |

PAGE 2 OF 2

| ISSUE | REVISION                                                                                             | DATE        |

|-------|------------------------------------------------------------------------------------------------------|-------------|

| 0     | RELEASED FOR PRODUCTION.                                                                             | 18 APR 2000 |

| Α     | ADDED MARKING DIAGRAM INFORMATION. REQ. BY V. BASS.                                                  | 13 JAN 2006 |

| В     | CORRECTED MARKING DIAGRAM PIN 1 LOCATION AND MARKING. REQ. BY C. REBELLO.                            | 13 MAR 2006 |

| С     | REMOVED EXPOSED PAD VIEW AND DIMENSIONS P AND P1. CORRECTED MARKING INFORMATION. REQ. BY C. REBELLO. | 20 JUN 2008 |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

|       |                                                                                                      |             |

ON Semiconductor and a registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for SRAM category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

CY7C13538S166BG IS64WV3216BLL-15CTLA3 IS66WVE4M16ECLL-70BLI PCF8570P K6F2008V2E-LF70000 K6T4008C1B-GB70 CY7C1353S-100AXC AS6C8016-55BIN AS7C164A-15PCN 515712X IDT71V67603S133BG IS62WV51216EBLL-45BLI IS63WV1288DBLL-10HLI IS66WVE2M16ECLL-70BLI IS66WVE4M16EALL-70BLI IS61WV102416DBLL-10TLI CY7C1381KV33-100AXC CY7C1381KVE33-133AXI 8602501XA 5962-3829425MUA 5962-3829430MUA 5962-8866201YA 5962-8866204TA 5962-8866206MA 5962-8866208UA 5962-8872502XA 5962-9062007MXA 5962-9161705MXA GS882Z18CD-150I M38510/28902BVA 8413202RA 5962-9161708MYA 5962-8871203XA 5962-8971202ZA 5962-8872501LA 5962-8866208YA 5962-8866205YA 5962-886620