# High-Voltage, Multimode Power Factor Controller

### **NCP1618**

The NCP1618 is an innovative multimode power factor controller. The circuit naturally transitions from one operation mode to another depending the switching period duration so that the efficiency is optimized over the line/load range. In very-light-load conditions, the circuit can enter the soft-SKIP mode for minimized losses.

Housed in a SO-9 package, the circuit further incorporates the features necessary for robust and compact PFC stages, with few external components.

#### **Multimode Operation**

- Multimode Operation for Optimized Operation over the Line/Load Range:

- Continuous Conduction Mode (CCM) in Heavy-Load Conditions

- Frequency-Clamped Critical Conduction Mode (FCCrM) in Medium- and Light-Load Conditions

- FCCrM: Critical Conduction Mode (CrM) when the CrM Switching Frequency is Lower than 130 kHz, Discontinuous Conduction Mode (DCM) at 130 kHz Otherwise

- DCM Frequency Reduction in Light Load Conditions

- Minimum DCM Frequency Forced above 25 kHz

- ♦ Valley Turn-On in FCCrM

- ◆ Soft-SKIP Mode in Very Light Load Conditions

- Near-Unity Power Factor in All Modes (Except Soft-SKIP Mode)

- Firm Control of the Switching Frequency between 25 kHz and 130 kHz

#### **General Features**

- High–Voltage Start–Up Current Source for V<sub>CC</sub> Capacitor Charge at Startup

- Internal Compensation of the Regulation Loop

- X2 Cap Discharge Function

- Fast Line / Load Transient Compensation (Dynamic Response Enhancer)

- Large V<sub>CC</sub> Operating Range (9.5 V to 35 V)

- Line Range Detection

- pfcOK Signal For Enabling/Disabling the Downstream Converter

- Jittering for Easing EMI Filtering

#### **Protection Features**

- Soft- and Fast-Overvoltage Protection

- Line-Sag and Brown-Out Detection

- 2-Level Over Current Detection

- Bulk Under-Voltage Detection

- OVP2: Redundant Over-Voltage Protection Using the ZCD Pin

- Thermal Shutdown

This document contains information on some products that are still under development. **onsemi** reserves the right to change or discontinue these products without notice.

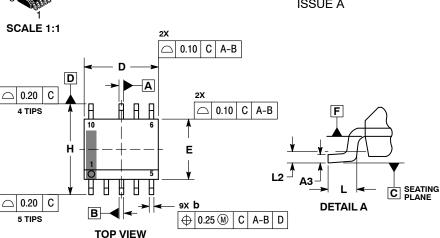

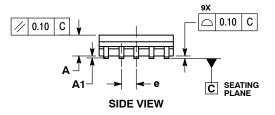

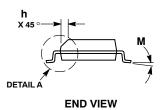

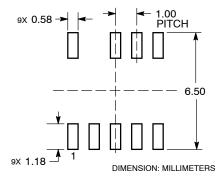

#### **MARKING DIAGRAM**

NCP1618X = Specific Device Code A = Assembly Location

L = Wafer Lot Y = Year W = Work Week

= Pb-Free Package

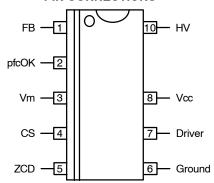

#### PIN CONNECTIONS

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 28 of this data sheet.

#### **Typical Applications**

- PC Power Supplies

- All Off-Line Appliances Requiring Power Factor Correction

**Table 1. SELECTION TABLE**

|                                                                            | NCP1618A                                          | NCP1618B                                          | NCP1618C                                          | NCP1618D                                                        | NCP1618F                                          |

|----------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------|

| f <sub>CCM</sub>                                                           | 65 kHz                                            | 65 kHz                                            | 65 kHz                                            | 65 kHz                                                          | 65 kHz                                            |

| f <sub>clamp</sub>                                                         | 130 kHz                                           | 130 kHz                                           | 130 kHz                                           | 130 kHz                                                         | 130 kHz                                           |

| OVP2                                                                       | YES                                               | NO                                                | NO                                                | NO                                                              | NO                                                |

| V <sub>CC(on)</sub>                                                        | 17.0 V                                            | 10.5 V                                            | 17.0 V                                            | 17.0 V                                                          | 17.0 V                                            |

| V <sub>BO(start)</sub> /<br>V <sub>BO(stop)</sub>                          | 111 V / 100 V                                     | 95 V / 87 V                                       | 111 V / 100 V                                     | 111 V / 100 V                                                   | 111 V / 100 V                                     |

| $\left(P_{FF,th}\right)_{LL}$                                              | $\frac{12\% \cdot V_{in,rms}^2}{L \cdot f_{CCM}}$ | $\frac{-6\% \cdot V_{in,rms^2}}{L \cdot f_{CCM}}$ | $\frac{12\% \cdot V_{in,rms^2}}{L \cdot f_{CCM}}$ | $\frac{12\% \cdot V_{\text{in,rms}}^2}{L \cdot f_{\text{CCM}}}$ | $\frac{12\% \cdot V_{in,rms^2}}{L \cdot f_{CCM}}$ |

| Current criterion for<br>CCM detection and<br>confirmation at<br>high line | YES                                               | NO                                                | YES                                               | NO                                                              | YES                                               |

| CCM operation                                                              | YES                                               | YES                                               | YES                                               | YES                                                             | FORCED                                            |

| X2 cap discharger                                                          | NO                                                | NO                                                | YES                                               | NO                                                              | NO                                                |

#### NOTES:

- f<sub>CCM</sub> is the switching frequency when the circuit operates in continuous conduction mode (CCM)

- f<sub>clamp</sub> is the maximum level to which the switching frequency is clamped when the circuit operates in FCCrM (frequency–clamped critical conduction mode). Practically, considering all modes, the circuit maintains the switching frequency above 25 kHz and below f<sub>clamp</sub>.

- V<sub>BO(start)</sub> and V<sub>BO(stop)</sub> respectively are the upper and the lower thresholds of the brown-out protection (Table 1 provides their typical value)

- V<sub>CC(on)</sub> is the V<sub>CC</sub> startup threshold, that is, the V<sub>CC</sub> voltage at which the circuit starts to operate (Table 1 provides the typical value)

- OVP2: if an image of the output voltage is provided to the ZCD pin during the off-time, the circuit can detect an overvoltage of the output voltage and provide a redundant protection

- (P<sub>FF,th</sub>)<sub>LL</sub> is the expression of the power below which the circuit enters the frequency foldback operation at low line. This threshold varies

as a function of the line rms voltage square and depends on the selected inductor value (L). In high line conditions, the power threshold

are obtained by dividing the power expression by two (see the frequency foldback section).

- See the CCM detection section for more information regarding the current criterion for CCM detection and confirmation at high line

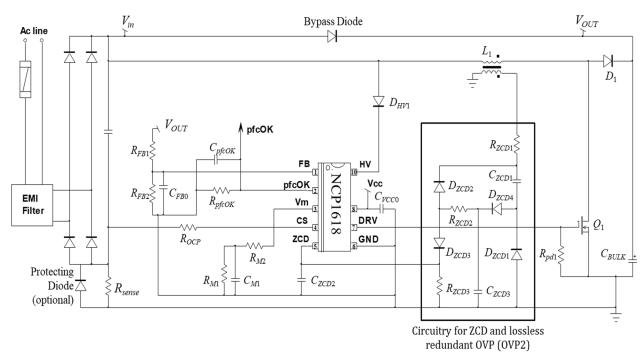

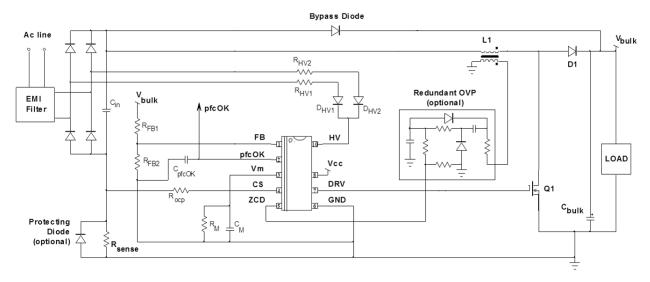

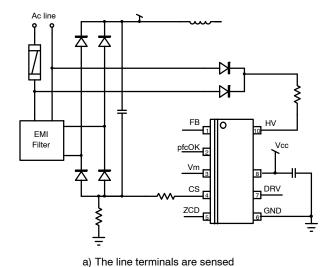

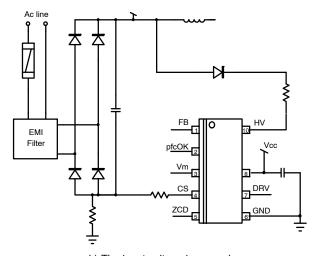

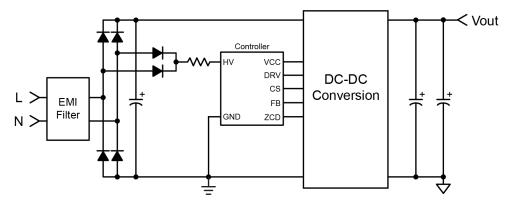

#### TYPICAL APPLICATION SCHEMATIC DIAGRAMS

Figure 1. NCP1618 with ZCD\_OVP2 Typical Application Schematic Diagram

Note that several circuitries exist for lossless redundant OVP2 as discussed in application note AND90011.

Figure 2. NCP1618 AC Start-up Typical Application Schematic Diagram

#### **PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name        | Function                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

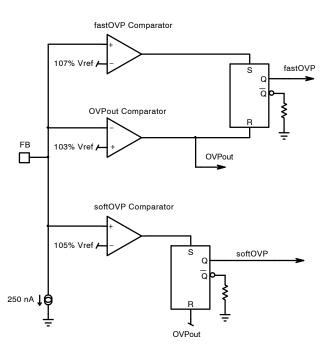

| 1       | FB              | Feedback Pin              | This pin receives a portion of the PFC output voltage for regulation and the Dynamic Response Enhancer (DRE) function which drastically speeds—up the loop response when the output voltage drops below 95.5% of the desired output level. $V_{FB}$ is also the input signal for the soft— and fast—overvoltage (OVP) and under—voltage (UVP) comparators. A 250 nA sink current is built—in to trigger the UVP protection and disable the part if the feedback pin is accidently open. |

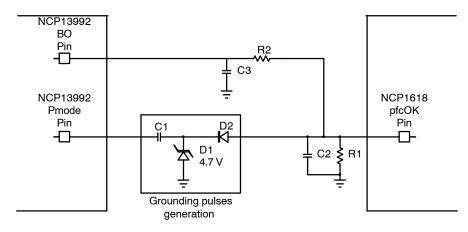

| 2       | pfcOK           | PFC OK Pin                | This pin is grounded until the PFC output has reached its nominal level. It is also grounded if the NCP1618 detects a major fault like a brown–out situation. A resistor is to be placed between the <i>pfcOK</i> pin and ground to form a voltage representative of the output voltage which can be used to enable the downstream converter and provide it with a feedforward signal.                                                                                                  |

| 3       | V <sub>M</sub>  | Multiplier<br>Output      | This pin provides a voltage $V_M$ for duty cycle modulation when the circuit operates in continuous conduction mode. The external resistor $R_M$ applied to the $V_M$ pin, adjusts the maximum power which can be delivered by the PFC stage. The device operates in average–current mode if an external capacitor $C_M$ is further connected to the pin. Otherwise, it operates in peak–current mode                                                                                   |

| 4       | CS              | Current<br>Sense Pin      | This pin sources a current $l_{CS}$ which is proportional to the inductor current. The NCP1618 uses $l_{CS}$ to adjust the PFC duty ratio in CCM operation. $l_{CS}$ is also used for protection: inrush current detection, abnormal current detection and overcurrent protection (OCP).                                                                                                                                                                                                |

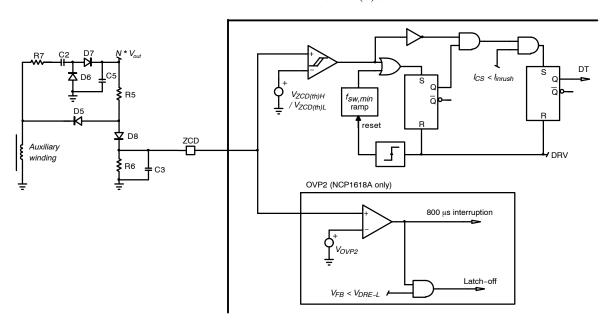

| 5       | ZCD             | Zero Current<br>Detection | This pin is designed to monitor a signal from an auxiliary winding and to detect the core reset when this voltage drops to zero. This function ensures valley turn on in discontinuous and critical conduction modes (DCM and CrM). The NCP1618 can further use the ZCD voltage to detect an over-voltage condition of the bulk voltage, reduce the power delivery and if the FB pin voltage is low, latch off the part in such an event.                                               |

| 6       | GND             | Ground Pin                | Connect this pin to the PFC stage ground.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7       | DRV             | Driver Output             | The high-current capability of the totem pole gate drive (-0.5/+0.8 A) makes it suitable to effectively drive high gate charge power MOSFETs.                                                                                                                                                                                                                                                                                                                                           |

| 8       | V <sub>CC</sub> | IC Supply<br>Pin          | This pin is the positive supply of the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 9       | -               | -                         | Removed for creepage distance.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10      | HV              | High Voltage<br>Pin       | The circuit senses the HV pin voltage for line range detection and line-sag and brownout protections. This pin is also the input for the high voltage start-up circuit.                                                                                                                                                                                                                                                                                                                 |

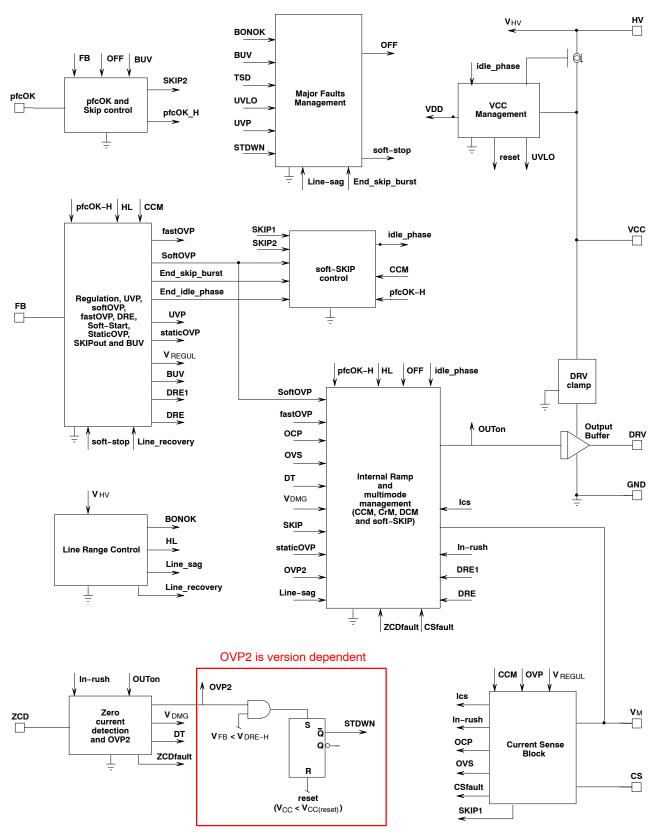

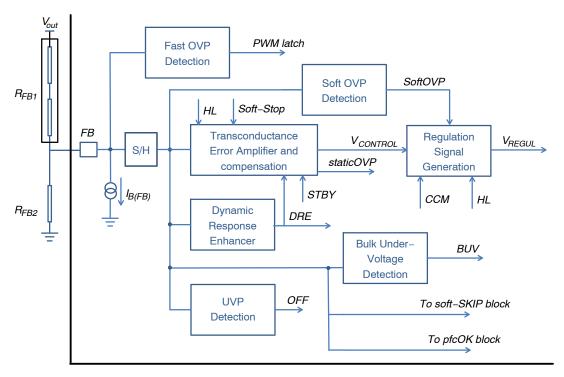

#### INTERNAL CIRCUIT ARCHITECTURE

Figure 3. Internal Circuit Architecture

#### **MAXIMUM RATINGS**

| Symbol                                         | Rating                                                                                                                               | Value                                         | Unit    |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------|

| $V_{HV(MAX)}$                                  | High Voltage Start – Up Circuit Input Voltage                                                                                        | -0.3 to 700                                   | V       |

| V <sub>CC(MAX)</sub>                           | Maximum Power Supply voltage, $V_{CC}$ pin, continuous voltage Maximum current for $V_{CC}$ pin                                      | -0.3 to 35<br>Internally limited              | V<br>mA |

| V <sub>DRV(MAX)</sub><br>I <sub>DRV(MAX)</sub> | Maximum driver pin voltage, DRV pin, continuous voltage<br>Maximum current for DRV pin                                               | -0.3, V <sub>DRV</sub> (Note 1)<br>-500, +800 | V<br>mA |

| $V_{MAX}$ $I_{MAX}$                            | Maximum voltage on low voltage pins (except DRV and $V_{CC}$ pins) Current range for low voltage pins (except DRV and $V_{CC}$ pins) | -0.3, 5.5 (Note 2)<br>-2, +5                  | V<br>mA |

| $R_{\theta J-A}$                               | Thermal Resistance Junction-to-Air                                                                                                   | 180                                           | °C/W    |

| $T_{J(MAX)}$                                   | Maximum Junction Temperature                                                                                                         | 150                                           | °C      |

| $T_J$                                          | Operating Temperature Range                                                                                                          | -40 to +125                                   | °C      |

| T <sub>S</sub>                                 | Storage Temperature Range                                                                                                            | -60 to +150                                   | °C      |

| MSL                                            | Moisture Sensitivity Level                                                                                                           | 1                                             | -       |

|                                                | ESD Capability, HBM model (Notes 3 and 4)                                                                                            | 3.5                                           | kV      |

|                                                | ESD Capability, CDM model (Note 4)                                                                                                   | 1                                             | kV      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- V<sub>DRV</sub> is the DRV clamp voltage V<sub>DRV(high)</sub> when V<sub>CC</sub> is higher than V<sub>DRV(high)</sub>. V<sub>DRV</sub> is V<sub>CC</sub> otherwise.

This level is low enough to guarantee not to exceed the internal ESD diode and 5.5 V ZENER diode. More positive and negative voltages can be applied if the pin current stays within the -2 mA / 5 mA range.

- 3. Except HV pin

- 4. This device contains ESD protection and exceeds the following tests: Human Body Model 3500 V per JEDEC Standard JESD22-A114F, Charged Device Model 1000 V per JEDEC Standard JESD22–C101F

5. This device contains latch–up protection and exceeds 100 mA per JEDEC Standard JESD78E.

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_J = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{HV} = 130$  V unless otherwise noted. For min/max values  $T_J = -40$ °C to +125°C,  $V_{CC} = 12$  V,  $V_{HV} = 130$  V unless otherwise noted)

| Symbol                                                   | Description                                                                                                                       | Test Condition                                                     | Min               | Тур                  | Max                  | Unit |  |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------|----------------------|----------------------|------|--|--|

| STARTUP AND                                              | STARTUP AND SUPPLY CIRCUITS                                                                                                       |                                                                    |                   |                      |                      |      |  |  |

| V <sub>CC(on)</sub>                                      | Startup Threshold NCP1618A, C, D, F<br>NCP1618B                                                                                   | V <sub>CC</sub> rising                                             | 15.8<br>9.75      | 17.0<br>10.5         | 18.2<br>11.25        | V    |  |  |

| V <sub>CC(off)</sub><br>V <sub>CC(HYS)</sub>             | Minimum Operating Voltage Hysteresis V <sub>CC(on)</sub> – V <sub>CC(off)</sub> NCP1618A, C, D, F NCP1618B                        | V <sub>CC</sub> decreasing<br>V <sub>CC</sub> decreasing           | 8.5<br>6.0<br>0.5 | 9.0<br>8.0<br>1.5    | 9.5<br>-<br>-        |      |  |  |

| V <sub>CC(reset)</sub>                                   | V <sub>CC</sub> level below which the circuit resets                                                                              | V <sub>CC</sub> decreasing                                         | 3.5               | 5.0                  | 6.0                  |      |  |  |

| I <sub>start1</sub><br>I <sub>HV1</sub>                  | Start–Up Current when the $V_{CC}$ Pin is Grounded Sourced by the $V_{CC}$ Pin Sunk by the HV pin                                 | V <sub>CC</sub> = 0 V, V <sub>HV</sub> = 130 V                     | 0.7               | 1.0<br>-             | 1.3<br>1.3           | mA   |  |  |

| I <sub>start1</sub><br>I <sub>HV1</sub>                  | NCP1618C Start-Up Current when the V <sub>CC</sub> Pin is<br>Grounded<br>Sourced by the V <sub>CC</sub> Pin<br>Sunk by the HV pin | V <sub>CC</sub> = 0 V, V <sub>HV</sub> = 130 V                     | 1.0<br>-          | 1.6<br>-             | 2.2<br>2.2           | mA   |  |  |

| I <sub>start2</sub><br>I <sub>HV2</sub>                  | Start – Up Current Sourced by the V <sub>CC</sub> Pin Sunk by the HV pin                                                          | $V_{CC} = V_{CC(on)} - 0.5 \text{ V},$<br>$V_{HV} = 130 \text{ V}$ | 6.5<br>-          | 12.0<br>-            | 16.5<br>18.0         | mA   |  |  |

| V <sub>CC(inhibit)</sub>                                 | $V_{CC}$ Threshold for $I_{start1}$ to $I_{start2}$ transition                                                                    | V <sub>CC</sub> increasing,<br>I <sub>HV</sub> > 6.5 mA            | 0.4               | 0.8                  | 1.2                  | V    |  |  |

| HV <sub>(MIN)</sub>                                      | Minimum Voltage for Start-Up Circuit ensuring I <sub>start2</sub> = 6.5 mA                                                        | $V_{CC} = V_{CC(on)} - 0.5 \text{ V}$                              | -                 | _                    | 38                   | V    |  |  |

| I <sub>CC1</sub><br>I <sub>CC2</sub><br>I <sub>CC3</sub> | Supply Current Device Disabled / Fault (no switching) Device Enabled (switching) / No output load on pin 5 Soft–SKIP Idle Phase   | V <sub>CC</sub> = 9.6 V, F <sub>sw</sub> = 65 kHz                  | 0.80<br>-<br>-    | 1.20<br>2.20<br>0.25 | 1.40<br>4.00<br>0.50 | mA   |  |  |

| GATE DRIVE                                               |                                                                                                                                   |                                                                    |                   |                      | •                    |      |  |  |

| t <sub>R</sub>                                           | Output voltage rise-time                                                                                                          | C <sub>L</sub> = 1 nF<br>10 – 90% of output signal                 |                   | 45                   | -                    | ns   |  |  |

| t <sub>F</sub>                                           | Output voltage fall-time                                                                                                          | C <sub>L</sub> = 1 nF<br>10 - 90% of output signal                 | ı                 | 30                   | -                    | ns   |  |  |

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_J = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{HV} = 130$  V unless otherwise noted. For min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{HV} = 130$  V unless otherwise noted) (continued)

| Symbol                                                           | Description                                                                                                                   | Test Condition                                                   | Min          | Тур          | Max          | Unit |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------|--------------|--------------|------|

| GATE DRIVE                                                       |                                                                                                                               |                                                                  |              |              |              |      |

| R <sub>OH</sub>                                                  | Source resistance                                                                                                             |                                                                  | _            | 11           | _            | Ω    |

| R <sub>OL</sub>                                                  | Sink resistance                                                                                                               |                                                                  | _            | 7            | _            | Ω    |

| I <sub>SOURCE</sub>                                              | Peak source current (Note 6)                                                                                                  | V <sub>DRV</sub> = 0 V                                           | _            | 500          | _            | mA   |

| I <sub>SINK</sub>                                                | Peak sink current (Note 6)                                                                                                    | V <sub>DRV</sub> = 12 V                                          | _            | 800          | _            | mA   |

| V <sub>DRVlow</sub>                                              | DRV pin level at $V_{CC}$ close to $V_{CC (off)}$                                                                             | $V_{CC} = V_{CC(off)} + 200 \text{ mV}$<br>10 kΩ resistor to GND | 8            | _            | -            | V    |

| $V_{DRVhigh}$                                                    | DRV pin level at $V_{CC}$ = 35 V                                                                                              | $R_L$ = 33 kΩ, $C_L$ = 220 pF                                    | 10           | 12           | 14           | V    |

| RAMP                                                             | -                                                                                                                             |                                                                  |              |              |              |      |

| f <sub>CCM</sub>                                                 | CCM switching frequency                                                                                                       |                                                                  | 60           | 65           | 70           | kHz  |

| R <sub>CCM</sub>                                                 | Ratio f <sub>CCM</sub> over Switching Frequency for CCM detection                                                             |                                                                  | -            | 112          | -            | %    |

| tCCMend                                                          | Blanking Time for CCM mode end detection                                                                                      |                                                                  | 315          | 360          | 415          | ms   |

| f <sub>clamp</sub>                                               | Clamp Frequency (DCM Frequency)                                                                                               | No frequency foldback                                            | _            | 130          | _            | kHz  |

| f <sub>clamp ratio</sub>                                         | f <sub>Clamp</sub> over f <sub>CCM</sub> ratio                                                                                | No frequency foldback                                            | 1.90         | 2.00         | 2.05         | _    |

| Gamp_ratio                                                       | On–Time below which Frequency Foldback is Engaged                                                                             | 1 3                                                              | 1            |              |              | μS   |

| (t <sub>on,FF</sub> ) <sub>LLA</sub>                             | NCP1618A, C, D, F                                                                                                             | Low line                                                         | _            | 3.75         | -            | pio  |

| (t <sub>on,FF</sub> ) <sub>HLA</sub>                             | NCP1618B                                                                                                                      | High line<br>Low line                                            | _            | 1.87<br>1.87 | _            |      |

| (t <sub>on,FF</sub> ) <sub>LLB</sub><br>(t <sub>on,FF</sub> )HLB | NOT TO TOD                                                                                                                    | High line                                                        | _            | 0.94         | _            |      |

| f <sub>min</sub>                                                 | Minimum DCM Frequency                                                                                                         |                                                                  | 25.0         | 30.5         | 36.0         | kHz  |

| t <sub>on,max</sub>                                              | Maximum On-Time (CCM)                                                                                                         |                                                                  | 13           | 15           | 17           | μs   |

| R <sub>iit</sub>                                                 | Ramp Frequency Jittering                                                                                                      |                                                                  | _            | 10           | _            | %    |

| f <sub>iit</sub>                                                 | Jittering Frequency                                                                                                           |                                                                  | _            | 119          | _            | Hz   |

| REGULATION E                                                     |                                                                                                                               |                                                                  | 1            |              |              |      |

| $V_{REF}$                                                        | Feedback Voltage Reference                                                                                                    | $T_J = 25^{\circ}C$<br>$T_J = -40^{\circ}C$ to +125°C            | 2.46<br>2.44 | 2.50<br>2.50 | 2.54<br>2.56 | V    |

| V <sub>DRE</sub> L / V <sub>REF</sub>                            | Ratio ( $V_{OUT}$ Low Detect Lower Threshold / $V_{REF}$ )                                                                    |                                                                  | 95.0         | 95.5         | 96.0         | %    |

| V <sub>DRE</sub> H / V <sub>REF</sub>                            | Ratio ( $V_{OUT}$ Low Detect Higher Threshold / $V_{REF}$ )                                                                   |                                                                  | 97.5         | 98.0         | 98.5         | %    |

| H <sub>DRE</sub> / V <sub>REF</sub>                              | Ratio (V <sub>OUT</sub> Low Detect Hysteresis / V <sub>REF</sub> )                                                            |                                                                  | 2            | _            | _            | %    |

| K <sub>DRE1</sub>                                                | Loop Gain Increase due to Dynamic Response<br>Enhancer                                                                        | pfcOK high<br>pfcOK low                                          | _<br>_       | 10<br>5      | -<br>-       | -    |

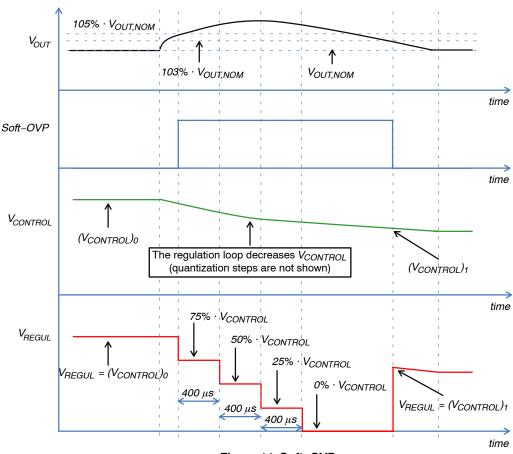

| t <sub>SSTOP,max</sub>                                           | Soft-Stop Duration for Gradual Discharge of the Control Voltage from Max to Min                                               |                                                                  | -            | 140          | -            | ms   |

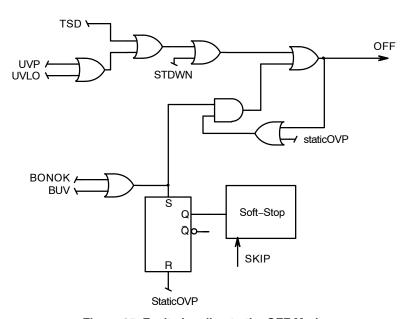

| StaticOVP                                                        |                                                                                                                               |                                                                  |              | •            |              |      |

| D <sub>MIN</sub>                                                 | Duty Ratio                                                                                                                    | V <sub>FB</sub> = 3 V                                            | _            | _            | 0            | %    |

|                                                                  | CLE MODE BLOCK                                                                                                                | . 5                                                              | I.           | ı            |              |      |

| $I_{VM}$                                                         | CrM/DCM V <sub>M</sub> pin Current Capability                                                                                 |                                                                  | 400          | _            | _            | μА   |

| V <sub>SKIP(th)</sub>                                            | V <sub>M</sub> Pin SKIP Threshold                                                                                             |                                                                  | 1.2          | 1.5          | 1.8          | V    |

| V <sub>SKIP2</sub>                                               | pfcOK SKIP Threshold                                                                                                          |                                                                  | 0.4          | 0.5          | 0.6          | V    |

| t <sub>SKIP2</sub>                                               | pfcOK Minimum Negative Pulse Duration for SKIP Detection                                                                      |                                                                  | 24           | 29           | 33           | μs   |

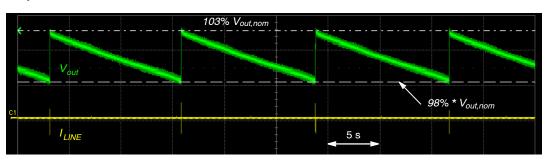

| V <sub>REFX</sub> /V <sub>REF</sub>                              | V <sub>FB</sub> Upper Value (V <sub>REFX</sub> ) During a Soft-SKIP Burst<br>Cycle (defined as a V <sub>REF</sub> percentage) |                                                                  | 102.5        | 103.0        | 103.5        | %    |

| (R <sub>FB</sub> ) <sub>recover</sub>                            | V <sub>FB</sub> Lower Value During a Soft Skip Cycle Burst (defined as a percentage of V <sub>REF</sub> )                     |                                                                  | 96.5         | 98.0         | 99.5         | %    |

| OUDDENT SET                                                      | for NCP1618C, D                                                                                                               |                                                                  | 98.5         | 100          | 101.5        |      |

| CURRENT SEN                                                      |                                                                                                                               |                                                                  | 1.5          | I            |              |      |

| V <sub>CSoff100</sub>                                            | Current Sense Voltage Offset                                                                                                  | I <sub>CS</sub> = -100 μA                                        | -10          | -            | 15           | mV   |

| V <sub>CSoff10</sub>                                             | Current Sense Voltage Offset                                                                                                  | I <sub>CS</sub> = -10 μA                                         | -10          | _            | 10           | mV   |

| I <sub>CCM-H</sub>                                               | Minimum I <sub>CS</sub> current for CCM detection                                                                             |                                                                  | 44           | 50           | 56           | μΑ   |

**ELECTRICAL CHARACTERISTICS** (For typical values  $T_J = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{HV} = 130$  V unless otherwise noted. For min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{HV} = 130$  V unless otherwise noted) (continued)

| Symbol                           | Description                                                                                                              | Test Condition          | Min   | Тур   | Max   | Unit |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|-------|-------|------|

| CURRENT SEN                      | ISE BLOCK                                                                                                                |                         |       |       |       |      |

| I <sub>CCM-L</sub>               | Minimum I <sub>CS</sub> current for CCM confirmation                                                                     |                         | 26    | 30    | 35    | μΑ   |

| I <sub>ILIMIT1 (LL)</sub>        | Low-Line Over-Current Protection Threshold                                                                               | V <sub>HV</sub> = 130 V | 185   | 200   | 215   | μΑ   |

| I <sub>ILIMIT1 (HL)</sub>        | High-Line Over-Current Protection Threshold                                                                              | V <sub>HV</sub> = 290 V | 185   | 200   | 215   | μΑ   |

| t <sub>OCP1(LL)</sub>            | Low-Line Over-current Protection Delay from (I <sub>CS</sub> > I <sub>ILIMIT1(LL)</sub> ) to DRV low                     | V <sub>HV</sub> = 130 V | -     | 40    | 100   | ns   |

| t <sub>OCP1(HL)</sub>            | High-Line Over-current Protection Delay from ( $I_{CS} > I_{ILIMIT1(HL)}$ ) to DRV low                                   | V <sub>HV</sub> = 290 V | -     | 40    | 100   | ns   |

| I <sub>ILIMIT2(LL)</sub>         | Low-Line Threshold for Abnormal Current Protection                                                                       | V <sub>HV</sub> = 130 V | 270   | 300   | 330   | μΑ   |

| I <sub>ILIMIT2(HL)</sub>         | High-Line Threshold for Abnormal Current Protection                                                                      | V <sub>HV</sub> = 290 V | 270   | 300   | 330   | μΑ   |

| t <sub>LEB,CS</sub>              | Leading Edge Blanking Time for the Over-Current and Abnormal Current Detection Comparators (Note 6)                      |                         | 150   | 260   | 350   | ns   |

| I <sub>in-rush</sub>             | Threshold for In-rush Current Detection                                                                                  |                         | 7.5   | 10.0  | 12.5  | μΑ   |

| V <sub>CS(fault)</sub>           | CS Fault Threshold                                                                                                       |                         | 180   | 250   | 320   | mV   |

| t <sub>CS(fault)</sub>           | CS Fault Blanking Time                                                                                                   |                         | 1     | 2     | 3     | μs   |

| I <sub>CS(test)</sub>            | Source Current for CS pin testing                                                                                        |                         | -     | 235   | _     | μA   |

| R <sub>OCP,min</sub>             | Minimum Impedance to apply to the CS pin not to Trig the CS Short-to-Ground Protection (Note 6)                          |                         | -     | -     | 1.5   | kΩ   |

| ERO VOLTAG                       | E DETECTION CIRCUIT                                                                                                      |                         | •     | •     |       |      |

| t <sub>LEB,ZCD</sub>             | ZCD Leading Edge Blanking Time                                                                                           |                         | 70    | 100   | 130   | ns   |

| V <sub>ZCD(th)H</sub>            | Zero Current Detection, V <sub>ZCD</sub> rising                                                                          |                         | 0.90  | 1.00  | 1.10  | V    |

| V <sub>ZCD(th)L</sub>            | Zero Current Detection, V <sub>ZCD</sub> falling                                                                         |                         | 0.40  | 0.50  | 0.60  | V    |

| V <sub>ZCD(hyst)</sub>           | Hysteresis of the Zero Current Detection Comparator                                                                      |                         | 0.35  | 0.50  | -     | V    |

| I <sub>ZCD(bias)H</sub>          | ZCD Pin Bias Current, $V_{ZCD} = V_{ZCD(th)H}$                                                                           |                         | 0.5   | -     | 2.0   | μΑ   |

| I <sub>ZCD(bias)L</sub>          | ZCD Pin Bias Current, $V_{ZCD} = V_{ZCD}(th)L$                                                                           |                         | 0.5   | -     | 2.0   | μΑ   |

| t <sub>ZCD</sub>                 | $(V_{ZCD} < V_{ZCD(th)L})$ to (DRV high)                                                                                 |                         | -     | 50    | 85    | ns   |

| t <sub>SYNC</sub>                | Minimum ZCD Pulse Width                                                                                                  |                         | -     | 50    | _     | ns   |

| t <sub>WDG(OS)</sub>             | Watch Dog Timer in "Overstress" Situation                                                                                |                         | 710   | 815   | 950   | μs   |

| I <sub>ZCD(test)</sub>           | Source Current for ZCD pin testing                                                                                       |                         | -     | 230   | -     | μΑ   |

| R <sub>ZCD,min</sub>             | Minimum Impedance to apply to the ZCD pin not to Trig the ZCD Short-to-Ground Protection (Note 6)                        |                         | -     | _     | 7.5   | kΩ   |

| JNDER- AND (                     | OVER-VOLTAGE PROTECTION                                                                                                  |                         | -     | =     | -     | =    |

| V <sub>UVP</sub>                 | UVP Threshold                                                                                                            | V <sub>FB</sub> falling | -     | 0.3   | _     | V    |

| R <sub>UVP</sub>                 | Ratio (UVP Threshold) over $V_{REF}$ ( $V_{UVP}$ / $V_{REF}$ )                                                           | V <sub>FB</sub> falling | 8     | 12    | 16    | %    |

| R <sub>UVP(HYST)</sub>           | Ratio (UVP Hysteresis) over V <sub>REF</sub>                                                                             | V <sub>FB</sub> rising  | 2     | 3     | 4     | %    |

| V <sub>softOVP</sub>             | Soft OVP Threshold                                                                                                       | V <sub>FB</sub> rising  | -     | 2.625 | _     | V    |

| R <sub>softOVP</sub>             | Ratio (Soft OVP Threshold) over $V_{REF}$ ( $V_{softOVP}$ / $V_{REF}$ )                                                  | V <sub>FB</sub> rising  | 104   | 105   | 106   | %    |

| R <sub>softOVP(H)</sub>          | Ratio (Soft OVP Hysteresis) over V <sub>REF</sub>                                                                        | V <sub>FB</sub> falling | 1.5   | 2.0   | 2.5   | %    |

| V <sub>fastOVP</sub>             | Fast OVP Threshold                                                                                                       | V <sub>FB</sub> rising  | -     | 2.7   | _     | V    |

| R <sub>fastOVP1</sub>            | Ratio (Fast OVP Threshold) over (Soft OVP Upper Threshold) ( <i>V</i> <sub>fastOVP</sub> / <i>V</i> <sub>softOVP</sub> ) | V <sub>FB</sub> rising  | 102   | 103   | 104   | %    |

| R <sub>fastOVP2</sub>            | Ratio (Fast OVP Threshold) over $V_{REF}$ ( $V_{fastOVP}$ / $V_{REF}$ )                                                  | V <sub>FB</sub> rising  | 107.0 | 108.3 | 109.5 | %    |

| V <sub>OVPrecover</sub>          | FB Threshold for Recovery from a Soft or Fast OVP                                                                        | V <sub>FB</sub> falling | -     | 2.575 | _     | V    |

| (I <sub>B</sub> ) <sub>FB1</sub> | FB bias Current @ V <sub>FB</sub> = V <sub>softOVP</sub>                                                                 |                         | 50    | 210   | 450   | nA   |

| (I <sub>B</sub> ) <sub>FB2</sub> | FB bias Current @ V <sub>FB</sub> = V <sub>UVP</sub>                                                                     |                         | 50    | 210   | 450   | nA   |

| V <sub>OVP2</sub>                | ZCD OVP2 Threshold (NCP1618A only)                                                                                       | V <sub>ZCD</sub> rising | 3.9   | 4.0   | 4.1   | V    |

| t <sub>OVP2</sub>                | OVP2 Blanking Time (NCP1618A only)                                                                                       | _                       | 70    | 100   | 130   | ns   |

$\begin{tabular}{ll} \textbf{ELECTRICAL CHARACTERISTICS} & \textbf{(For typical values $T_J=25^\circ$C, $V_{CC}=12$ V, $V_{HV}=130$ V unless otherwise noted. For min/max values $T_J=-40^\circ$C to $+125^\circ$C, $V_{CC}=12$ V, $V_{HV}=130$ V unless otherwise noted) (continued) $T_J=-40^\circ$C to $+125^\circ$C, $T_{CC}=12$ V, $T_{HV}=130$ V unless otherwise noted) (continued) $T_J=-40^\circ$C to $+125^\circ$C, $T_{CC}=12$ V, $T_{HV}=130$ V unless otherwise noted) (continued) $T_J=-40^\circ$C to $+125^\circ$C, $T_{CC}=12$ V, $T_{HV}=130$ V unless otherwise noted) (continued) $T_J=-40^\circ$C to $+125^\circ$C, $T_{CC}=12$ V, $T_{HV}=130$ V unless otherwise noted) (continued) $T_J=-40^\circ$C to $+125^\circ$C, $T_{CC}=12$ V, $T_{HV}=130$ V unless otherwise noted) (continued) $T_J=-40^\circ$C to $+125^\circ$C, $T_{CC}=12$ V, $T_{HV}=130$ V unless otherwise noted) (continued) $T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}=T_{TV}$

| Symbol                                                      | Description                                                                           | Test Condition                                    | Min       | Тур       | Max        | Unit     |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------|-----------|-----------|------------|----------|

| M PIN                                                       |                                                                                       |                                                   |           |           |            |          |

| V <sub>M,FCCrM</sub>                                        | V <sub>M</sub> Pin Voltage in FCCrM (CrM or DCM)                                      |                                                   | 2.0       | 2.5       | 3.0        | V        |

| (V <sub>ramp</sub> ) <sub>pk</sub>                          | PWM Comparator Reference Voltage for CCM Operation                                    | V <sub>M</sub> rising                             | 3.50      | 3.75      | 4.00       | V        |

| I <sub>M1(LL)</sub>                                         | V <sub>M</sub> Pin Source Current                                                     | $V_{FB}$ = 2 V, $I_{CS}$ = -100 $\mu$ A low line  | 31        | 39        | 46         | μА       |

| I <sub>M1(LL)</sub> /<br>(V <sub>ramp</sub> ) <sub>pk</sub> | I <sub>M1(LL)</sub> over (V <sub>ramp</sub> ) <sub>pk</sub> ratio                     | $V_{FB}$ = 2 V, $I_{CS}$ = -100 $\mu A$ low line  | 8.4       | 10.4      | 12.4       | μS       |

| I <sub>M2(LL)</sub>                                         | V <sub>M</sub> Pin Source Current                                                     | $V_{FB}$ = 2 V, $I_{CS}$ = -200 $\mu A$ low line  | 66        | 82        | 96         | μΑ       |

| I <sub>M2(LL)</sub> /<br>(V <sub>ramp</sub> ) <sub>pk</sub> | I <sub>M2(LL)</sub> over (V <sub>ramp</sub> ) <sub>pk</sub> ratio                     | $V_{FB}$ = 2 V, $I_{CS}$ = -200 $\mu A$ low line  | 17        | 22        | 26         | μS       |

| I <sub>M1(HL)</sub>                                         | V <sub>M</sub> Pin Source Current                                                     | $V_{FB}$ = 2 V, $I_{CS}$ = -100 $\mu A$ high line | 131       | 163       | 194        | μΑ       |

| I <sub>M1(HL)</sub> /<br>(V <sub>ramp</sub> ) <sub>pk</sub> | I <sub>M1(HL)</sub> over (V <sub>ramp</sub> ) <sub>pk</sub> ratio                     | $V_{FB}$ = 2 V, $I_{CS}$ = -100 $\mu$ A high line | 35        | 43        | 52         | μS       |

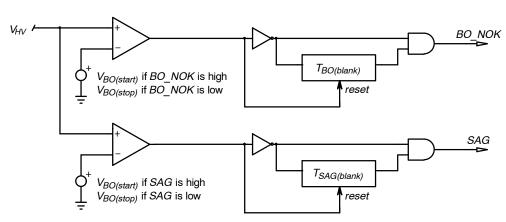

| ROWN-OUT, I                                                 | LINE SAG AND LINE RANGE DETECTION                                                     |                                                   |           |           |            |          |

| V <sub>BO(start)</sub>                                      | Upper Threshold for Line Sag and Brown-Out<br>Detection NCP1618A, C, D, F<br>NCP1618B | V <sub>HV</sub> increasing                        | 103<br>88 | 111<br>95 | 119<br>102 | V        |

| V <sub>BO(stop)</sub>                                       | Lower Threshold for Line Sag and Brown-Out<br>Detection NCP1618A, C, D, F<br>NCP1618B | V <sub>HV</sub> decreasing                        | 92<br>80  | 100<br>87 | 108<br>94  | V        |

| V <sub>BO(HYS)</sub>                                        | Hysteresis NCP1618A, C, D, F<br>NCP1618B                                              | V <sub>HV</sub> increasing                        | 7<br>3.5  | 11<br>7.5 | -<br>-     | V        |

| t <sub>BO(blank)</sub>                                      | Brown-out Detection Blanking Time                                                     | V <sub>HV</sub> decreasing                        | 550       | 650       | 750        | ms       |

| t <sub>Sag(blank)</sub>                                     | Line Sag Detection Blanking Time                                                      | V <sub>HV</sub> decreasing                        | 22.8      | 26.0      | 30.2       | ms       |

| V <sub>HL</sub>                                             | High-Line Level Detection Threshold                                                   | V <sub>HV</sub> increasing                        | 220       | 236       | 252        | V        |

| $V_{LL}$                                                    | Low-Line Level Detection Threshold                                                    | V <sub>HV</sub> decreasing                        | 207       | 222       | 237        | V        |

| V <sub>LR(HYST)</sub>                                       | Line Range Select Hysteresis                                                          | V <sub>HV</sub> increasing                        | 9         | -         | _          | V        |

| t <sub>blank(LL)</sub>                                      | High- to Low-Line Mode Selector Timer                                                 | V <sub>HV</sub> decreasing                        | 22.8      | 26.0      | 30.2       | ms       |

| t <sub>filter(HV)</sub>                                     | Low- to High-Line Mode Selector Timer Filter                                          |                                                   | 300       | 360       | 420        | μs       |

| t <sub>line(lockout)</sub>                                  | Lockout Timer for Low- to High-Line Mode Transition                                   | V <sub>HV</sub> increasing                        | 450       | 515       | 600        | ms       |

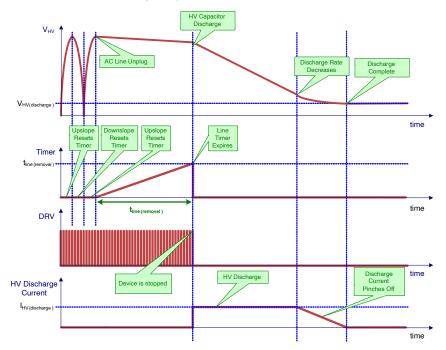

| 2 DISCHARGE                                                 |                                                                                       |                                                   |           |           |            |          |

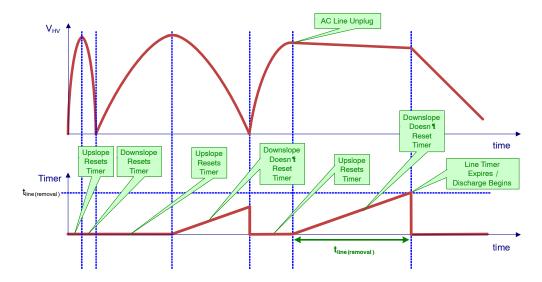

| t <sub>line(removal)</sub>                                  | Line Voltage Removal Detection Timer                                                  |                                                   | 83        | 100       | 100        | ms       |

| t <sub>HV(up)</sub>                                         | Upslope Detection Reset Timer (Note 6)                                                | HV increasing                                     | -         | 1         | 27         | V/m<br>s |

| t <sub>HV(down)</sub>                                       | Downslope Detection Reset Timer (Note 6)                                              | HV decreasing                                     | -         | 14.0      | 1.89       | V/m<br>s |

| I <sub>HV(discharge)</sub>                                  | HV Discharge Current                                                                  |                                                   | 2.5       | 4.5       | 6.5        | mA       |

| V <sub>HV(discharge)</sub>                                  | HV Discharge Stop Level                                                               |                                                   | _         | _         | 34         | V        |

|                                                             | V PROTECTION                                                                          |                                                   | 1         | 1         |            |          |

| V <sub>pfcOK-L</sub>                                        | pfcOK Voltage in OFF Mode                                                             | 1 mA being sunk by the pfcOK pin                  | -         | -         | 100        | mV       |

| I <sub>pfcOK</sub>                                          | pfcOK Current                                                                         | V <sub>FB</sub> = 2.5 V, V <sub>pfcOK</sub> = 1 V | 23        | 25        | 27         | μΑ       |

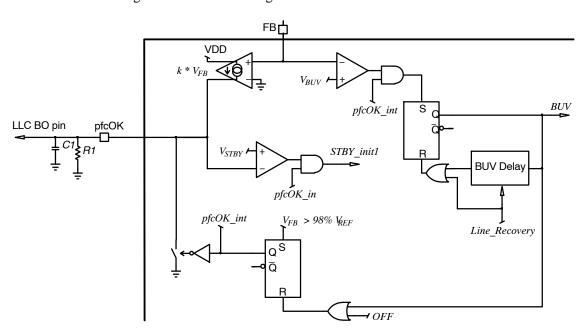

| V <sub>BUV</sub>                                            | Bulk Under-Voltage Protection (BUV) Threshold                                         | V <sub>FB</sub> falling                           | 1.71      | 1.80      | 1.89       | V        |

| t <sub>BUV</sub>                                            | BUV Delay Before Operation Recovery                                                   |                                                   | 450       | 515       | 600        | ms       |

| HERMAL SHU                                                  |                                                                                       |                                                   |           | <u> </u>  | •          |          |

|                                                             |                                                                                       |                                                   |           |           |            |          |

| T <sub>LIMIT</sub>                                          | Thermal Shutdown Threshold                                                            |                                                   | -         | 150       | _          | °C       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. Guaranteed by Design

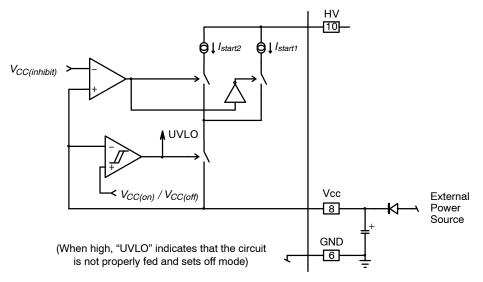

#### STARTUP SEQUENCE / $V_{CC}$ MANAGEMENT

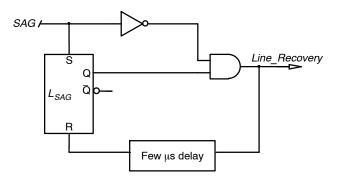

An internal high–voltage startup current source is enabled whenever  $V_{CC}$  drops below  $V_{CC(off)}$  (9 V, typically), to charge the  $V_{CC}$  capacitor, in particular when the PFC stage is plugged to the mains outlet. When  $V_{CC}$  exceeds the  $V_{CC(on)}$  level, the current source turns off and the circuit starts operating. The energy stored by the  $V_{CC}$  capacitor must be large enough to feed the controller and maintain  $V_{CC}$  above  $V_{CC(off)}$  (that is, the level below which the circuit turns off) until an auxiliary power supply takes over. The large 8–V UVLO typical hysteresis ( $V_{CC(on)}$  minus

V<sub>CC(off)</sub>) is provided to prevent erratic operation. The low V<sub>CC(on)</sub> level makes it ideal in applications where the controller is fed by an external power source (typically from an auxiliary power supply). Its maximum start-up level (11.25 V) is set low enough to be powered from traditional 12–V rails.

The startup current source being off when the PFC stage is in operation, the HV pin virtually draws no current. This helps minimize the losses in light-load conditions and hence, meet the most stringent standby requirements.

Figure 4. Internal Startup Current Source

The startup current sourced by the  $V_{CC}$  pin ( $I_{start2}$ ) is 12 mA typically. As shown by Figure 4, the startup current is limited to  $I_{start1}$  (1 mA typically) when the  $V_{CC}$  voltage is below  $V_{CC(inhibit)}$  (0.8 V typically). This feature prevents the circuit from overheating if the  $V_{CC}$  pin is accidentally grounded.

Thus, the following equation provides the  $V_{CC}$  capacitor charge time:

$$t_{ch} = \frac{C_{Vcc} \cdot V_{CC(inhibit)}}{I_{start1}} + \frac{C_{Vcc} \cdot (V_{CC(on)} - V_{CC(inhibit)})}{I_{start2}} \quad \text{(eq. 1)}$$

As an example, using 17 V for  $V_{CC(on)}$  (NCP1618A typical  $V_{CC}$  startup threshold) and their typical values for the other parameters in play ( $V_{CC(inhibit)}$ ,  $I_{start1}$  and  $I_{start2}$ ), it comes for a 100- $\mu$ F  $V_{CC}$  capacitance:

$$(t_{ch-100\mu F})_{typical} = \frac{100 \cdot 10^{-6} \cdot 0.8}{1 \cdot 10^{-3}} + \frac{100 \cdot 10^{-6} \cdot (17 - 0.8)}{12 \cdot 10^{-3}} \cong 215 \text{ ms}$$

(eq. 2)

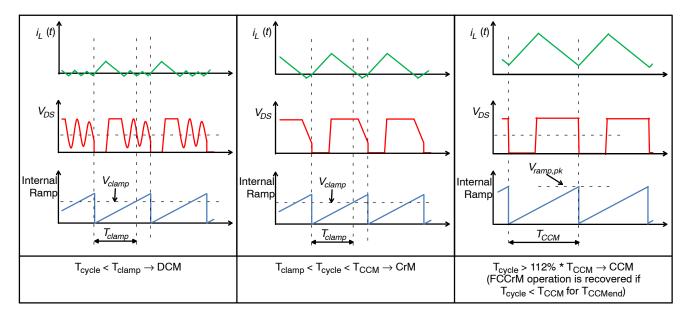

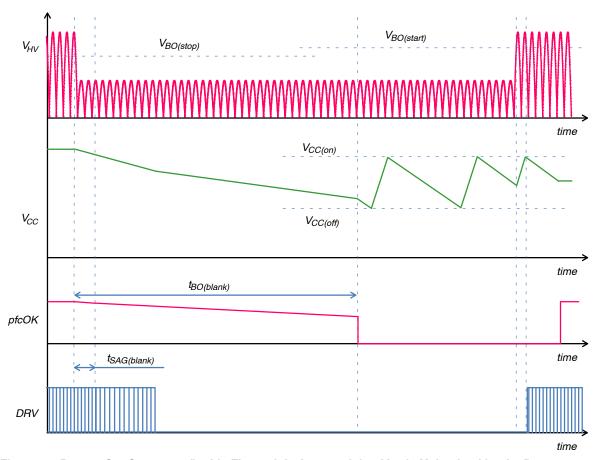

#### THREE MODES OF OPERATION

Depending on the current cycle duration, the NCP1618 operates in either FCCrM or CCM. In FCCrM (or frequency clamped critical conduction mode), the circuit operates in critical conduction mode until the switching frequency exceeds the *f*<sub>clamp</sub> clamp threshold (130 kHz typically). At

that moment, as detailed in the next paragraph, the circuit operates in discontinuous conduction mode with valley turn-on.

Note that the circuit can transition from CrM to DCM and vice versa within half-line cycles. Typically DCM is obtained near the line zero crossing where current cycles tend to be shorter and CrM, at the top of the line sinusoid where the current cycles are longer. This is because the circuit enters DCM operation when the current cycle is shorter than  $T_{clamp}$  (clamp period corresponding to  $f_{clamp}$ :  $T_{clamp} = 1 / f_{clamp}$ ) as it can easily be the case near the line zero crossing and in light-load conditions. Conversely, if the current cycle exceeds  $T_{clamp}$ , the system naturally enters the CrM operation mode. These transitions cause no discontinuity in the operation and power factor remains properly controlled.

CCM operation is obtained in heavy load conditions when the current cycle is longer than 112% of the CCM switching period. At that moment, the circuit operates as a CCM controller in all parts of the line sinusoid (no transitions to FCCrM) and remains in CCM for at least the CCM blanking time ( $T_{CCMend}$  of 360 ms typically). This is because the circuit recovers the FCCrM mode only if it cannot detect 8 consecutive current cycles longer than the CCM switching period for  $T_{CCMend}$ .

Figure 5. Three Operation Modes (MOSFET Drain-source Voltage is in Red, the Internal Ramp is in Green)

Finally, depending on the conditions, the circuit operates in CrM, DCM (with valley turn–on) or CCM.

Practically, the circuit compares the current cycle duration to two periods  $T_{clamp}$  and  $T_{CCM}$ :

- If the current cycle duration is shorter than T<sub>clamp</sub>, T<sub>clamp</sub> forces the switching frequency and the system operates in DCM

- If the current cycle duration is longer than  $T_{clamp}$  but shorter than 112% of  $T_{CCM}$ , the system operates in CrM.

- If 8 consecutive current cycles happen to be longer than 112% of  $T_{CCM}$ , the system enters CCM mode with a switching frequency set to  $f_{CCM} = 1 / T_{CCM}$ . The system remains in this mode until the circuit cannot detect 8 consecutive current cycles longer than  $T_{CCM}$  for  $T_{CCMend}$  (360 ms typically).

Figure 5 provides a simplified description of the manner the conduction mode is selected.

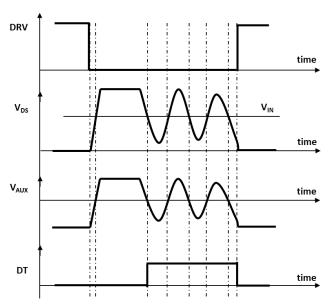

### FREQUENCY-CLAMPED CRITICAL CONDUCTION MODE

As aforementioned, the NCP1618 tends to operate in critical conduction mode as long as the current switching cycle is short enough not to enter the CCM mode. However, if the current cycle happens to be shorter than the frequency–clamp period (T<sub>clamp</sub> which is about 7.7 µs typically leading to a 130 kHz DCM frequency), the circuit

delays the next cycle until the T<sub>clamp</sub> time has elapsed. Thus, the circuit enters DCM operation. In DCM, the switching period is actually a bit longer than T<sub>clamp</sub>. This is because of the below discussed modulation method but mainly because the next cycle is further delayed until the next valley is detected (left plot of Figure 5). Doing so, valley turn–on is obtained for minimized losses.

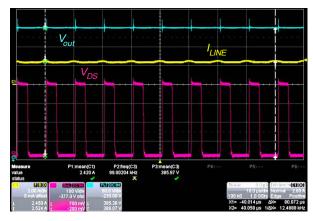

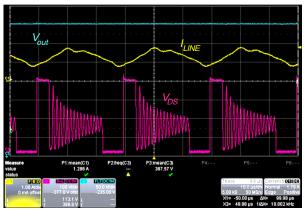

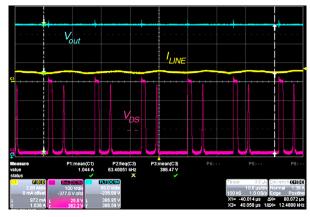

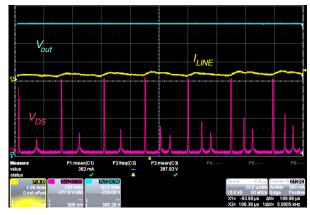

Frequency-Clamped operation is controlled by a proprietary circuitry which modulates the duty-ratio cycle-by-cycle to prevent any discontinuity in operation and ensure proper current shaping. Also, as shown by Figure 6, it automatically varies the valley at which the MOSFET turns on within the line sinusoid as necessary to maintain valley switching and clamp the frequency over the instantaneous input voltage range. For instance, DCM is more likely to occur near the line zero crossing and CrM at the top of the sinusoid. As the load further decays, current cycles become shorter and DCM operation is obtained over the entire line sinusoid. Furthermore, as detailed in the next section and illustrated by Figure 6c and Figure 6d, the DCM period clamp is increased below a certain load level for frequency foldback (a longer minimum switching period is forced causing frequency foldback). Anyway, in all cases, the NCP1618 scheme ensures a clean control preventing that repeated spurious changes in the turn-on valley possibly cause current distortion and audible noise.

a) 40% load, top of the sinusoid

c) 20% load, top of the sinusoid

b) 40% load, near the line zero crossing

d) 20% load,near the line zero crossing

Figure 6. Operation of the 500 W NCP1618 Evaluation Board @ 115 Vrms

#### FREQUENCY FOLDBACK IN DCM OPERATION

The frequency clamp (or DCM period) is gradually decreased when the power demand drops below a certain threshold. The expression of this power threshold depends on the line range (see the "Line Range Detection" section). The threshold also depends on the circuit version. Table 1 provides the equation for Low line, where  $V_{\rm in,rms}$  is the line rms voltage, L is the boost inductor of the PFC stage and  $f_{\rm CCM}$  is the switching frequency in CCM operation (65 kHz typically). The High Line power threshold is half Low Line power threshold.

The frequency clamp level linearly reduces as the power further decays to nearly reach ( $f_{clamp}$  / 10) when the power is close to zero. The circuit however forces a minimum 25–kHz operation to prevent audible noise. See next section.

#### DCM MINIMUM FREQUENCY (FOR DCM ONLY)

As aforementioned, the DCM frequency is gradually lowered in very light load conditions as a function of the load, to optimize the efficiency. This frequency foldback

function can reduce the frequency to nearly 10 kHz. However, a specific ramp ensures that the switching frequency remains above audible frequencies.

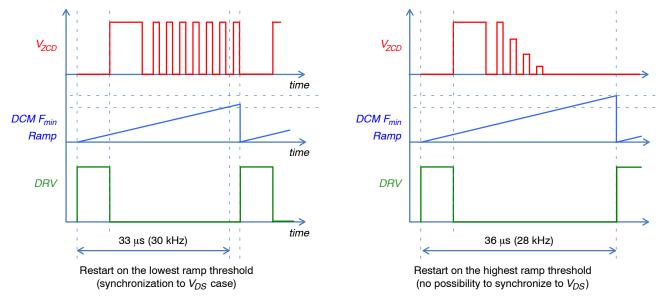

This ramp generates a clock which overrides the clock provided by the DCM ramp (it forces next DRV pulse even if the DCM ramp clock is not generated yet). However, the minimum–frequency ramp remains synchronized to the drain source voltage for valley turn–on. Practically, as shown by Figure 7, the minimum–frequency ramp typically sets the clock signal when the switching period reaches 33 µs. The DRV output will then turn on back when the next valley is detected. If no valley can be detected within a 3 µs interval, DRV is forced high whatever the drain–source voltage is. As a result, the minimum frequency is typically between 30 kHz (33 µs switching period) if a valley is immediately detected and 28 kHz (36 µs switching period) if no valley can be detected.

Note that the frequency clamp can force a new DRV pulse only if the system is in dead–time. The minimum frequency clamp cannot cause CCM operation.

Figure 7. DCM Minimum Switching Frequency Ramp

#### **JITTERING**

In CCM operation, the NCP1618 features the jittering function which is an effective method to improve the EMI signature. An internal low–frequency signal modulates the oscillator swing which helps by spreading out energy in conducted noise analysis.

Practically, the CCM switching frequency is typically varied as follows:

- Jittering frequency: 119 Hz

- Pk to pk frequency variation: 10%

Jittering is not implemented in frequency clamped critical conduction mode (FCCrM including CrM and/or DCM sequences) where valley turn-on operation naturally leads to frequency variations.

#### **CCM DETECTION**

As aforementioned, the NCP1618 measures the duration of each current cycle (the current cycle is the total duration of the on–time + the demagnetization time) and compares it to  $T_{CCM}$ , which is the CCM switching period. The circuit enters CCM mode if it consecutively detects 8 current cycles longer than 112% of  $T_{CCM}$ . Conversely, the circuit leaves the CCM mode if the circuit does not detect 8 consecutive cycles exceeding  $T_{CCM}$  for the CCM blanking time ( $T_{CCMend}$  of 360 ms typically).

The following expressions provide the typical power thresholds for:

• CCM entering:

$$(P_{in,avg})_{CCM_{in}} = \frac{0.56 \cdot V_{in,rms}^{2} \cdot (V_{out} - \sqrt{2} \cdot V_{in,rms})}{L \cdot f_{CCM} \cdot V_{out}} \quad \text{(eq. 3)}$$

• FCCrM recovery:

$$(P_{in,avg})_{CCM_{out}} = \frac{0.50 \cdot V_{in,rms}^2 \cdot (V_{out} - \sqrt{2} \cdot V_{in,rms})}{L \cdot f_{CCM} \cdot V_{out}}$$

(eq. 4)

Where L is the value of the PFC inductor,  $V_{in,rms}$  is the line rms voltage,  $V_{out}$  is the output voltage and  $f_{CCM}$  is the CCM switching frequency (65 kHz typically).

#### NOTES:

- The 8 current cycles longer than 112% of T<sub>CCM</sub> necessary to detect CCM are not validated unless the inductor current happens to exceed a minimum level within each cycle. Practically, the second criterion consists of comparing the internal current sense current (I<sub>CS</sub>) to the following internal current references:

- I<sub>CCM-H</sub> (50 μA typically) when CCM is low.

- I<sub>CCM-L</sub> (30 μA typically) when CCM is high.

- Some options (see Table 1) meet the second criterion in low line only. In high line, it validates CCM cycles regardless of the I<sub>CS</sub> current level.

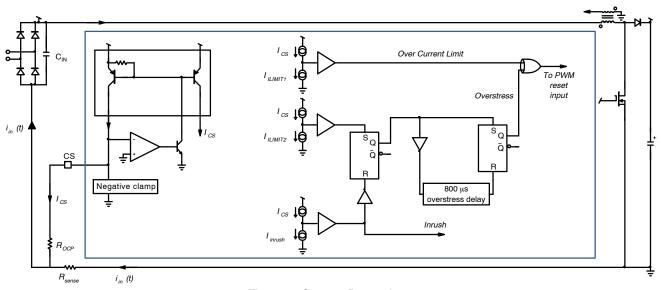

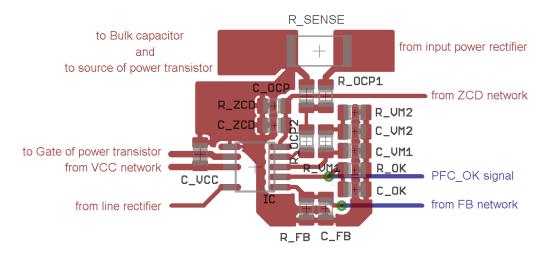

#### **CURRENT SENSE BLOCK**

The NCP1618 is designed to monitor a negative voltage proportional to inductor current ( $I_L$ ). As portrayed by Figure 8, a current sense resistor ( $R_{sense}$ ) is inserted in the return path to generate a negative voltage ( $V_{Rsense}$ ) proportional to  $I_L$ . The circuit uses  $V_{Rsense}$  to detect when  $I_L$  exceeds its maximum permissible level. To do so, the circuit incorporates an operational amplifier that sources the current necessary to maintain the CS pin at 0 V (refer to Figure 9). By inserting a resistor  $R_{OCP}$  between the CS pin and  $R_{sense}$ , we adjust the current that is sourced by the CS pin ( $I_{CS}$ ) as follows:

$$-(R_{sense} \cdot I_L) + (R_{OCP} \cdot I_{CS}) = 0$$

(eq. 5)

Which leads to:

$$I_{CS} = \frac{R_{\text{sense}}}{R_{OCP}} I_{L}$$

(eq. 6)

In other words, the CS pin current ( $I_{CS}$ ) is proportional to the inductor current. Three protection functions use  $I_{CS}$ : the over–current protection, the in–rush current detection and the overstress detection. It is also used in CCM to control the power–switch duty–ratio.

#### **IMPORTANT NOTES:**

- Resistor R<sub>OCP</sub> has to be located as close as possible to CS pin. Please see recommended layout at the end of this document

- As detailed below, two external resistors adjust the current thresholds (R<sub>sense</sub> and R<sub>OCP</sub>), thus offering some flexibility on the R<sub>sense</sub> selection which can be chosen for an optimal trade-off between noise immunity and losses.

- However the R<sub>OCP</sub> resistance must be selected higher or equal to 1.5 kΩ. If not, the protection against accidental short-to-ground failures of the CS pin may trip and thus, prevent operation of the circuit.

#### **Over-Current Protection (OCP)**

If  $I_{CS}$  exceeds the OCP threshold ( $I_{ILIMIT1}$  which is 200  $\mu$ A typically) an over-current situation is detected and the MOSFET is immediately turned off (cycle-by-cycle current limitation). The maximum inductor current can hence be limited as follows:

$$I_{L(max)} = \frac{R_{OCP}}{R_{sense}} I_{LIMIT1}$$

(eq. 7)

As an example, if  $R_{sense} = 30 \text{ m}\Omega$  and  $R_{OCP} = 2 \text{ k}\Omega$ , the maximum inductor current is typically set to:

$$I_{(L(max))} = \frac{2 \cdot 10^3}{30 \cdot 10^{-3}} \cdot 200 \cdot 10^{-6} \cong 13.3 \text{ A}$$

(eq. 8)

#### In-rush Current Detection

The NCP1618 permanently monitors the input current and when in FCCrM, can delay the MOSFET turn on until  $(I_L)$  has vanished. This is one function of the  $I_{CS}$  comparison to the  $I_{in-rush}$  threshold (10  $\mu$ A typical). This feature helps maintain proper FCCrM operation when the ZCD signal is too distorted for accurate demagnetization detection like it can happen at very high line. The inrush comparator also serves to detect that the inductor current remains at a low value, as necessary for some functions like the CS pin short–to–ground accidental protection. Re–using above example  $(R_{Sense} = 30 \text{ m}\Omega, R_{OCP} = 2 \text{ k}\Omega)$ , the inrush level of the input current is typically set to:

$$I_{\text{(L(inrush)}} = \frac{2 \cdot 10^3}{30 \cdot 10^{-3}} \cdot 10 \cdot 10^{-6} \cong 0.67 \text{ A}$$

(eq. 9)

#### **Abnormal Current Detection (Overstress)**

When the PFC stage is plugged to the mains, the bulk capacitor is abruptly charged to the line voltage. The charge current (named in–rush current) can be very huge even if an in–rush limiting circuitry is implemented. Also, if the inductor saturates, the input current can go far above the current limitation due to the reaction time of the overcurrent protection. If one of these cases leads the internal CS pin current ( $I_{CS}$ ) to exceed  $I_{ILIMIT2}$  (set to 150% of  $I_{ILIMIT1}$ ), an abnormal current situation is detected, causing the DRV output to be kept low for 800  $\mu$ s after the circuit has dropped below the in–rush level.

**Figure 8. Current Protections**

Re-using above example ( $R_{sense} = 30 \text{ m}\Omega$ ,  $R_{OCP} = 2 \text{ k}\Omega$ ), the overstress level of the input current is typically set to:

$$I_{\text{in(OVS)}} = \frac{2 \cdot 10^3}{30 \cdot 10^{-3}} \cdot 300 \cdot 10^{-6} = 20 \text{ A}$$

(eq. 10)

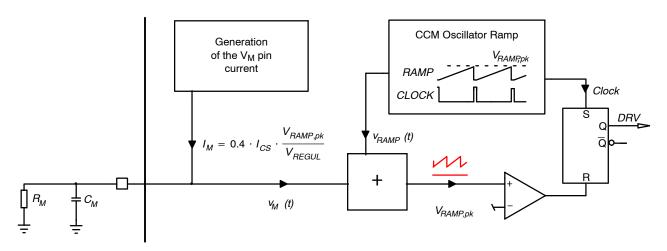

#### **Duty Ratio Control in CCM Mode**

The NCP1618 re-uses the proven "predictive method" scheme implemented in NCP1653 and NCP1654 CCM PFC controllers. In other words, it directly computes the power switch on-time as a function of the inductor current. Practically, the  $I_{CS}$  current is modulated by the control signal and sourced by the  $V_M$  pin to build the CCM current information. The  $V_M$  pin signal is:

$$V_{M} = 0.4 \cdot R_{M} \cdot \frac{V_{RAMP,pk}}{V_{REGUL}} \cdot I_{CS}$$

(eq. 11)

Where  $V_{REGUL}$ ,  $V_{RAMP,pk}$  and  $R_M$  respectively are the regulation voltage (derived from  $V_{CONTROL}$ ), the CCM oscillator peak value and the  $V_M$  pin resistor. Actually, a

capacitor  $C_M$  is to be added across  $R_M$  to filter and remove the switching frequency component of the  $V_M$  pin voltage. Hence, replacing  $I_{CS}$  by its function of the inductor current given by Equation 6, it comes:

$$V_{M} = 0.4 \cdot R_{M} \cdot \frac{V_{RAMP,pk}}{V_{REGUL}} \cdot \frac{R_{sence}}{R_{OCP}} \cdot \langle I_{L} \rangle_{T_{SW}}$$

(eq. 12)

Now,  $\langle I_L \rangle_{Tsw}$ , the inductor current averaged over the switching frequency is the input current. Thus, Equation 12 can be changed into:

$$V_{M} = 0.4 \cdot \frac{R_{M} \cdot R_{sense}}{R_{OCP}} \cdot \frac{V_{RAMP,pk}}{V_{REGUL}} \cdot i_{in} (t)$$

(eq. 13)

Figure 9. Duty Ratio Control in CCM Mode

Figure 9 sketches the manner the duty ratio is controlled in CCM.

Like in the NCP1653/4 controllers, when the power switch on–time starts, an oscillator ramp is added to the  $V_M$  pin voltage and the power switch opens when the sum reaches the oscillator upper threshold. Doing so, if  $V_{RAMPpk}$  designates the peak value of the oscillator ramp, the  $V_M$  voltage and the on–time  $(t_{on})$  are linked as follows:

$$V_{M} = V_{RAMP,pk} \cdot \left(1 - \frac{t_{on}}{T_{SW}}\right)$$

(eq. 14)

Now, the off-duty-ratio of a boost converter operated in CCM is:

$$d_{off} = 1 - \frac{t_{on}}{T_{SW}} = \frac{v_{in}(t)}{V_{out}}$$

(eq. 15)

Combining Equations 13, 14 and 15, the following expression of the input current is obtained:

$$i_{in}(t) = 2.5 \cdot \frac{R_{OCP} \cdot V_{REGUL}}{R_{M} \cdot R_{sence}} \cdot \frac{v_{in}(t)}{V_{out}}$$

(eq. 16)

The input current is as targeted proportional to the input voltage.

The CCM regulation voltage ( $V_{REGUL}$ ) is proportional to the regulation control signal provided by the "transconductance error amplifier and compensation" internal block ( $V_{CONTROL}$ ) as follows: