# 7-Bit, Programmable, 3-Phase, Mobile CPU Synchronous Buck Controller

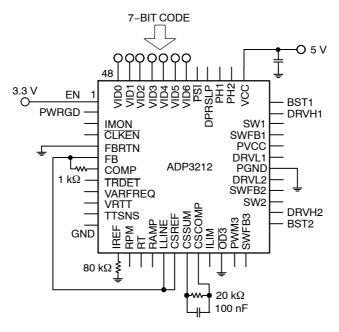

The APD3212/NCP3218/NCP3218G is a highly efficient, multi-phase, synchronous buck switching regulator controller. With its integrated drivers, the APD3212/NCP3218/NCP3218G is optimized for converting the notebook battery voltage into the core supply voltage required by high performance Intel processors. An internal 7-bit DAC is used to read a VID code directly from the processor and to set the CPU core voltage to a value within the range of 0.3 V to 1.5 V. The APD3212/NCP3218/NCP3218G is programmable for 1-, 2-, or 3-phase operation. The output signals ensure interleaved 2- or 3-phase operation.

The APD3212/NCP3218/NCP3218G uses a multimode architecture run at a programmable switching frequency and optimized for efficiency depending on the output current requirement. The APD3212/NCP3218/NCP3218G switches between single—and multi—phase operation to maximize efficiency with all load conditions. The chip includes a programmable load line slope function to adjust the output voltage as a function of the load current so that the core voltage is always optimally positioned for a load transient. The APD3212/NCP3218/NCP3218G also provides accurate and reliable short—circuit protection, adjustable current limiting, and a delayed power—good output. The IC supports On—The—Fly (OTF) output voltage changes requested by the CPU.

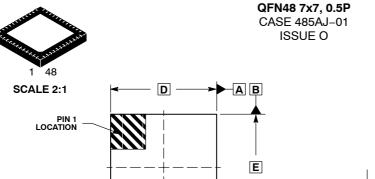

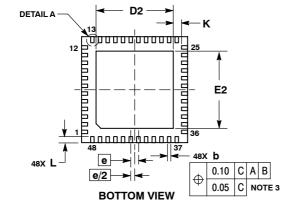

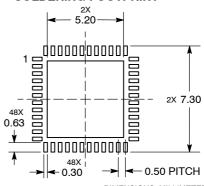

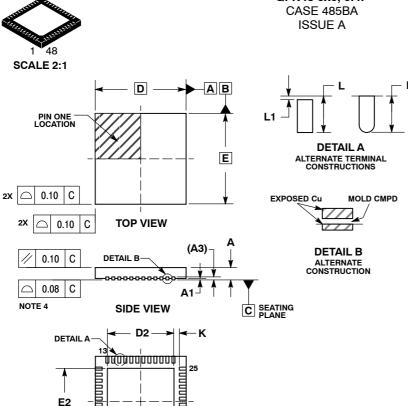

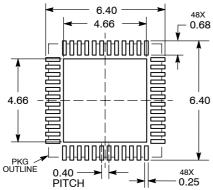

The APD3212/NCP3218/NCP3218G are specified over the extended commercial temperature range of -40°C to 100°C. The ADP3212 is available in a 48-lead QFN 7x7mm 0.5mm pitch package. The NCP3218/NCP3218G is available in a 48-lead QFN 6x6mm 0.4mm pitch package. ADP3212/NCP3218 has 1.1 V Vboot Voltage, while NCP3218G has 987.5 mV Vboot Voltage. Except for the packages and Vboot Voltages, the APD3212/NCP3218/NCP3218G are identical. APD3212/NCP3218/NCP3218G are Halogen-Free, Pb-Free and RoHS compliant.

### **Features**

- Single-Chip Solution

- Fully Compatible with the Intel<sup>®</sup> IMVP-6.5<sup>™</sup> Specifications

- Selectable 1-, 2-, or 3-Phase Operation with Up to 1

MHz per Phase Switching Frequency

- Phase 1 and Phase 2 Integrated MOSFET Drivers

- Input Voltage Range of 3.3 V to 22 V

- Guaranteed ±8 mV Worst–Case Differentially Sensed Core Voltage Error Over Temperature

- Automatic Power–Saving Mode Maximizes Efficiency with Light Load During Deeper Sleep Operation

### ON Semiconductor®

http://onsemi.com

QFN48 CASE 485AJ

QFN48 CASE 485BA

#### **MARKING DIAGRAM**

o xxP321x AWLYYWWG

xxx = Specific Device Code (ADP3212 or NCP3218/G)

A = Assembly Location

WL = Wafer Lot YY = Year

WW = Work Week

G = Pb-Free Package

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 33 of this data sheet.

- Active Current Balancing Between Output Phases

- Independent Current Limit and Load Line Setting Inputs for Additional Design Flexibility

- Built-In Power-Good Blanking Supports Voltage Identification (VID) On-The-Fly (OTF) Transients

- 7-Bit, Digitally Programmable DAC with 0.3 V to 1.5 V Output

- Short–Circuit Protection with Programmable Latchoff Delay

- Clock Enable Output Delays the CPU Clock Until the Core Voltage is Stable

- Output Power or Current Monitor Options

- 48-Lead QFN 7x7mm (ADP3212), 48-Lead QFN 6x6mm (NCP3218/NCP3218G)

- Vboot = 1.1 V (ADP3212/NCP3218)

Vboot = 987.5 mV (NCP3218G)

- These are Pb-Free Devices

- Fully RoHS Compliant

### **Applications**

1

Notebook Power Supplies for Next–Generation Intel Processors

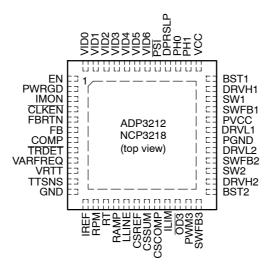

#### **PIN ASSIGNMENT**

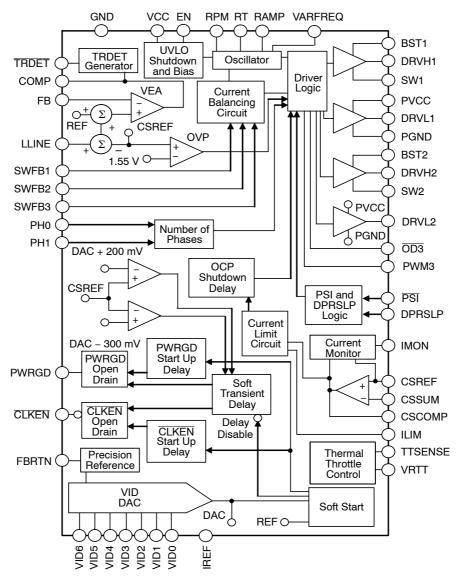

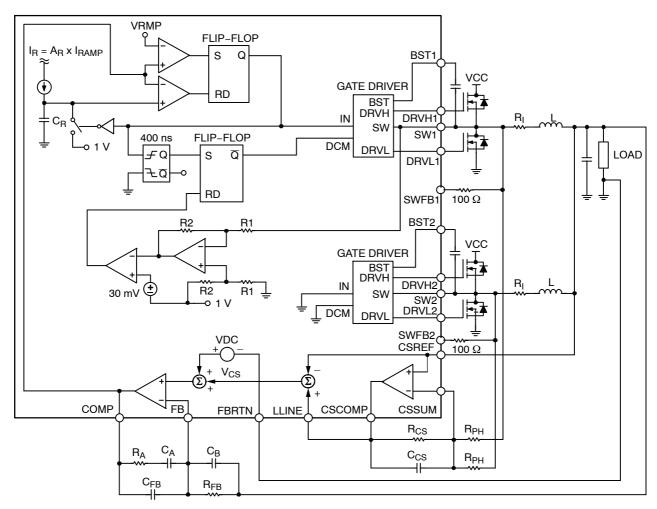

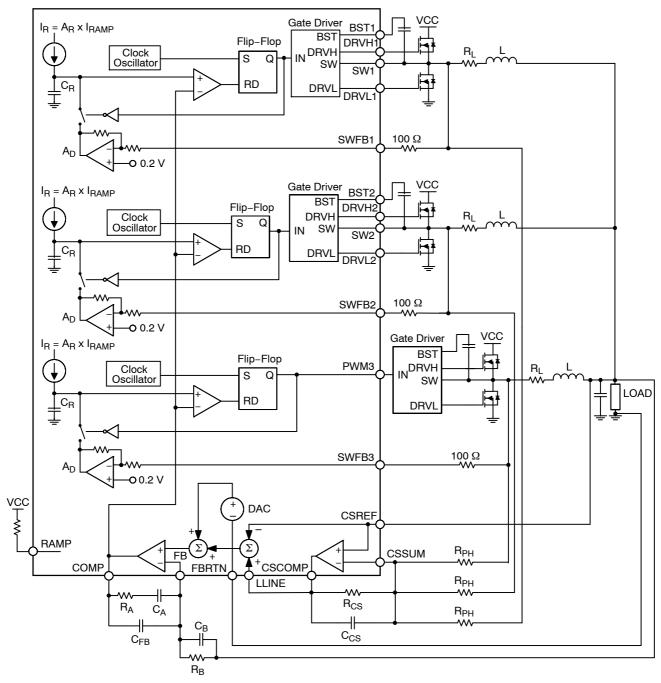

Figure 1. Functional Block Diagram

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                         | Rating                       | Unit |

|-------------------------------------------------------------------|------------------------------|------|

| V <sub>CC</sub> , PV <sub>CC1</sub> , PV <sub>CC2</sub>           | -0.3 to +6.0                 | V    |

| FBRTN, PGND1, PGND2                                               | -0.3 to +0.3                 | V    |

| BST1, BST2, DRVH1, DRVH2<br>DC<br>t < 200 ns                      | -0.3 to +28<br>-0.3 to +33   | V    |

| BST1 to PV <sub>CC</sub> , BST2 to PV <sub>CC</sub> DC t < 200 ns | -0.3 to +22<br>-0.3 to +28   | V    |

| BST1 to SW1, BST2 to SW2                                          | -0.3 to +6.0                 | V    |

| SW1, SW2<br>DC<br>t < 200 ns                                      | -1.0 to +22<br>-6.0 to +28   | V    |

| DRVH1 to SW1, DRVH2 to SW2                                        | -0.3 to +6.0                 | V    |

| DRVL1 to PGND1, DRVL2 to PGND2<br>DC<br>t < 200 ns                | -0.3 to +6.0<br>-5.0 to +6.0 | V    |

| RAMP (in Shutdown)                                                | -0.3 to +22                  | V    |

| All Other Inputs and Outputs                                      | -0.3 to +6.0                 | V    |

| Storage Temperature Range                                         | -65 to +150                  | °C   |

| Operating Ambient Temperature Range                               | -40 to +100                  | °C   |

| Operating Junction Temperature                                    | 125                          | °C   |

| Thermal Impedance (θ <sub>JA</sub> ) 2-Layer Board                | 30.5                         | °C/W |

| Lead Temperature<br>Soldering (10 sec)<br>Infrared (15 sec)       | 300<br>260                   | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

### **PIN ASSIGNMENT**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                 |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN       | Enable Input. Driving this pin low shuts down the chip, disables the driver outputs, pulls PWRGD and VRTT low, and pulls CLKEN high.                                                                                                                        |

| 2       | PWRGD    | Power–Good Output. Open–drain output. A low logic state means that the output voltage is outside of the VID DAC defined range.                                                                                                                              |

| 3       | IMON     | Current Monitor Output. This pin sources a current proportional to the output load current. A resistor to FBRTN sets the current monitor gain.                                                                                                              |

| 4       | CLKEN    | Clock Enable Output. Open-drain output. A low logic state enables the CPU internal PLL clock to lock to the external clock.                                                                                                                                 |

| 5       | FBRTN    | Feedback Return Input/Output. This pin remotely senses the CPU core voltage. It is also used as the ground return for the VID DAC and the voltage error amplifier blocks.                                                                                   |

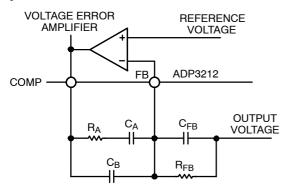

| 6       | FB       | Voltage Error Amplifier Feedback Input. The inverting input of the voltage error amplifier.                                                                                                                                                                 |

| 7       | COMP     | Voltage Error Amplifier Output and Frequency Compensation Point.                                                                                                                                                                                            |

| 8       | TRDET    | Transient Detect Output. This pin is pulled low when a load release transient is detected. During repetitive load transients at high frequencies, this circuit optimally positions the maximum and minimum output voltage into a specified loadline window. |

| 9       | VARFREQ  | Variable Frequency Enable Input. A high logic state enables the PWM clock frequency to vary with VID code.                                                                                                                                                  |

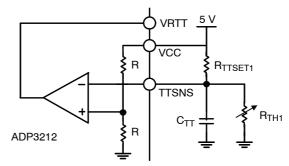

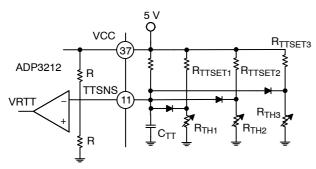

| 10      | VRTT     | Voltage Regulator Thermal Throttling Output. Logic high state indicates that the voltage regulator temperature at the remote sensing point exceeded a set alarm threshold level.                                                                            |

### **PIN ASSIGNMENT**

| Pin No.     | Mnemonic     | Description                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 11          | TTSNS        | Thermal Throttling Sense and Crowbar Disable Input. A resistor divider where the upper resistor is connected to VCC, the lower resistor (NTC thermistor) is connected to GND, and the center point is connected to this pin and acts as a temperature sensor half bridge. Connecting TTSNS to GND disables the thermal throttling function and disables the crowbar, or Overvoltage Protection (OVP), feature of the chip. |  |  |  |  |  |  |

| 12          | GND          | Analog and Digital Signal Ground.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 13          | IREF         | This pin sets the internal bias currents. A 80 $k\Omega$ resistor is connected from this pin to ground.                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 14          | RPM          | RPM Mode Timing Control Input. A resistor between this pin to ground sets the RPM mode turn-on threshold voltage.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 15          | RT           | Multi-phase Frequency Setting Input. An external resistor connected between this pin and GND sets the oscillator frequency of the device when operating in multi-phase PWM mode threshold of the converter.                                                                                                                                                                                                                |  |  |  |  |  |  |

| 16          | RAMP         | PWM Ramp Slope Setting Input. An external resistor from the converter input voltage node to this pin sets the slope of the internal PWM stabilizing ramp used for phase-current balancing.                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 17          | LLINE        | Output Load Line Programming Input. The center point of a resistor divider between CSREF and CSCOMP is connected to this pin to set the load line slope.                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

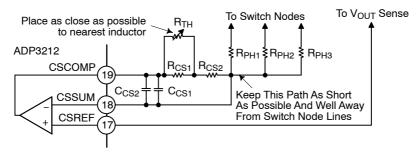

| 18          | CSREF        | Current Sense Reference Input. This pin must be connected to the common point of the output inductors. The node is shorted to GND through an internal switch when the chip is disabled to provide soft stop transient control of the converter output voltage.                                                                                                                                                             |  |  |  |  |  |  |

| 19          | CSSUM        | Current Sense Summing Input. External resistors from each switch node to this pin sum the inductor currents to provide total current information.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 20          | CSCOMP       | Current Sense Compensation Point. A resistor and capacitor from this pin to CSSUM determine the gain of the current-sense amplifier and the positioning loop response time.                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 21          | ILIM         | Current Limit Setpoint. An external resistor from this pin to CSCOMP sets the current limit threshold of the converter.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 22          | OD3          | Multi-phase Output Disable Logic Output. This pin is actively pulled low when the APD3212/NCP3218/<br>NCP3218G enters single-phase mode or during shutdown. Connect this pin to the SD inputs of the<br>Phase-3 MOSFET drivers.                                                                                                                                                                                            |  |  |  |  |  |  |

| 23          | PWM3         | Logic-Level PWM Output for phase 3. Connect to the input of an external MOSFET driver such as the ADP3611.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

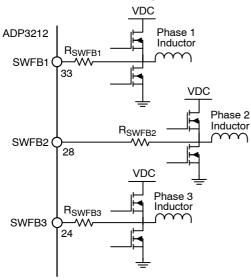

| 24          | SWFB3        | Current Balance Input for phase 3. Input for measuring the current level in phase 3. SWFB3 should be left open for 1 or 2 phase configuration.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 25          | BST2         | High-Side Bootstrap Supply for Phase 2. A capacitor from this pin to SW2 holds the bootstrapped voltage while the high-side MOSFET is on.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 26          | DRVH2        | High-Side Gate Drive Output for Phase 2.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 27          | SW2          | Current Return for High-Side Gate Drive for phase 2.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 28          | SWFB2        | Current Balance Input for phase 2. Input for measuring the current level in phase 2. SWFB2 should be left open for 1 phase configuration.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 29          | DRVL2        | Low-Side Gate Drive Output for Phase 2.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 30          | PGND         | Low-Side Driver Power Ground                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 31          | DRVL1        | Low-Side Gate Drive Output for Phase 1.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 32          | PVCC         | Power Supply Input/Output of Low-Side Gate Drivers.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 33          | SWFB1        | Current Balance Input for phase 1. Input for measuring the current level in phase 1.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 34          | SW1          | Current Return For High-Side Gate Drive for phase 1.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 35          | DRVH1        | High-Side Gate Drive Output for Phase 1.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 36          | BST1         | High-Side Bootstrap Supply for Phase 1. A capacitor from this pin to SW1 holds the bootstrapped voltage while the high-side MOSFET is on.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 37          | VCC          | Power Supply Input/Output of the Controller.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 38          | PH1          | Phase Number Configuration Input. Connect to VCC for 3 phase configuration.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 39          | PH0          | Phase Number Configuration Input. Connect to GND for 1 phase configuration. Connect to VCC for multi-phase configuration.                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 40          | DPRSLP       | Deeper Sleep Control Input.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 41          | PSI          | Power State Indicator Input. Pulling this pin to GND forces the APD3212/NCP3218/NCP3218G to operate in single-phase mode.                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 42 to<br>48 | VID6 to VID0 | Voltage Identification DAC Inputs. When in normal operation mode, the DAC output programs the FB regulation voltage from 0.3 V to 1.5 V (see Table 3).                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = PV_{CC} = 5.0 \text{ V}, \text{FBRTN} = PGND = GND = 0 \text{ V}, \text{H} = 5.0 \text{ V}, \text{L} = 0 \text{ V}, \text{EN} = \text{VARFREQ} = \text{H}, \text{DPRSLP} = \text{L}, \overline{PSI} = 1.05 \text{ V}, \text{R} = 1.05 \text{ V},$

$V_{VID} = V_{DAC} = 1.2000 \ V, \ T_{A} = -40 ^{\circ} C \ to \ 100 ^{\circ} C, \ unless \ otherwise \ noted. \ (Note \ 1) \ Current \ entering \ a \ pin \ (sink \ current) \ has \ a \ positive \ sign.$

| Parameter                                      | Symbol                                                                                  | Conditions                                                                                                                          | Min          | Тур            | Max          | Units    |

|------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|--------------|----------|

| VOLTAGE CONTROL<br>VOLTAGE ERROR AMPLIFIER (VE | EAMP)                                                                                   |                                                                                                                                     |              |                |              |          |

| FB, LLINE Voltage Range (Note 2)               | IE Voltage Range (Note 2) V <sub>FB</sub> , V <sub>LLINE</sub> Relative to CSREF = VDAC |                                                                                                                                     |              |                | +200         | mV       |

| FB, LLINE Offset Voltage (Note 2)              | V <sub>OSVEA</sub>                                                                      | Relative to CSREF = VDAC                                                                                                            | -0.5         |                | +0.5         | mV       |

| LLINE Bias Current                             | I <sub>LLINE</sub>                                                                      |                                                                                                                                     | -100         |                | +100         | nA       |

| FB Bias Current                                | I <sub>FB</sub>                                                                         |                                                                                                                                     | -1.0         |                | +1.0         | μΑ       |

| LLINE Positioning Accuracy                     | V <sub>FB</sub> – V <sub>VID</sub>                                                      | Measured on FB relative to V <sub>VID</sub> , LLINE forced 80 mV below CSREF                                                        | -77.5        | -80            | -82.5        | mV       |

| COMP Voltage Range (Note 2)                    | $V_{COMP}$                                                                              |                                                                                                                                     | 0.85         |                | 4.0          | <b>V</b> |

| COMP Current                                   | I <sub>COMP</sub>                                                                       | COMP = 2.0 V, CSREF = VDAC<br>FB forced 200 mV below CSREF<br>FB forced 200 mV above CSREF                                          |              | -0.75<br>6     |              | mA       |

| COMP Slew Rate                                 | SR <sub>COMP</sub>                                                                      | C <sub>COMP</sub> = 10 pF, CSREF = VDAC,<br>Open loop configuration<br>FB forced 200 mV below CSREF<br>FB forced 200 mV above CSREF |              | 15<br>–20      |              | V/µs     |

| Gain Bandwidth (Note 2)                        | GBW                                                                                     | Non–inverting unit gain configuration, $R_{FB}$ = 1 $k\Omega$                                                                       |              | 20             |              | MHz      |

| VID DAC VOLTAGE REFERENCE                      |                                                                                         |                                                                                                                                     |              |                |              |          |

| VDAC Voltage Range (Note 2)                    |                                                                                         | See VID table                                                                                                                       | 0            |                | 1.5          | V        |

| VDAC Accuracy                                  | V <sub>FB</sub> – V <sub>VID</sub>                                                      | Measured on FB (includes offset), relative to V <sub>VID</sub> V <sub>VID</sub> = 1.2000 V to 1.5000 V,                             |              |                |              | mV       |

|                                                |                                                                                         | T = -40°C to 100°C<br>V <sub>VID</sub> = 0.3000 V to 1.1875 V,<br>T = -40°C to 100°C                                                | -8.5<br>-7.5 |                | +8.5<br>+7.5 |          |

| VDAC Differential Non-linearity<br>(Note 2)    |                                                                                         | 1 = -40 0 to 100 0                                                                                                                  | -1.0         |                | +1.0         | LSB      |

| VDAC Line Regulation                           | ΔV <sub>FB</sub>                                                                        | VCC = 4.75 V to 5.25 V                                                                                                              |              | 0.02           |              | %        |

| VDAC Boot Voltage<br>(ADP3212, NCP3218)        | V <sub>BOOTFB</sub>                                                                     | Measured during boot delay period                                                                                                   |              | 1.100          |              | V        |

| VDAC Boot Voltage (NCP3218G)                   | V <sub>BOOTFB</sub>                                                                     | Measured during boot delay period                                                                                                   |              | 987.5          |              | mV       |

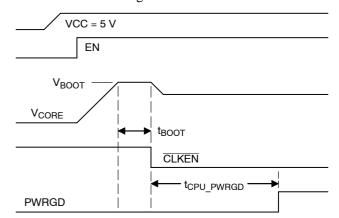

| Soft-Start Delay (Note 2)                      | t <sub>DSS</sub>                                                                        | Measured from EN pos edge to FB = 50 mV                                                                                             |              | 200            |              | μs       |

| Soft-Start Time                                | t <sub>SS</sub>                                                                         | Measured from FB = 50 mV to FB settles to 1.1 V within 5%                                                                           |              | 1.4            |              | ms       |

| Boot Delay                                     | t <sub>BOOT</sub>                                                                       | Measured from FB settling to 1.1 V within 5% to CLKEN neg edge                                                                      |              | 60             |              | μs       |

| VDAC Slew Rate (Note 2)                        |                                                                                         | Soft-Start<br>Non-LSB VID step, DPRSLP = H,<br>Slow C4 Entry/Exit                                                                   |              | 0.0625<br>0.25 |              | LSB/μs   |

|                                                |                                                                                         | Non-LSB VID step, DPRSLP = L,<br>Fast C4 Exit<br>LSB VID step, DVID transition                                                      |              | 1.0<br>0.4     |              |          |

| FBRTN Current                                  | I <sub>FBRTN</sub>                                                                      |                                                                                                                                     |              | -90            | -200         | μΑ       |

| VOLTAGE MONITORING and PRO POWER GOOD          |                                                                                         |                                                                                                                                     |              |                |              |          |

| CSREF Undervoltage Threshold                   | V <sub>UVCSREF</sub>                                                                    | Relative to nominal VDAC voltage                                                                                                    | -240         | -300           | -360         | mV       |

| CSREF Overvoltage Threshold                    | V <sub>OVCSREF</sub>                                                                    | Relative to nominal VDAC voltage                                                                                                    | 150          | 200            | 250          | mV       |

| CSREF Crowbar Voltage<br>Threshold             | V <sub>CBCSREF</sub>                                                                    | Relative to FBRTN, $V_{VID} > 1.1 \text{ V}$<br>Relative to FBRTN, $V_{VID} \le 1.1 \text{ V}$                                      | 1.5<br>1.3   | 1.55<br>1.35   | 1.6<br>1.4   | ٧        |

- 1. All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

- 2. Guaranteed by design or bench characterization, not production tested.

- 3. Based on bench characterization data.

- 4. Timing is referenced to the 90% and 10% points, unless otherwise noted.

### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = PV_{CC} = 5.0 \text{ V}, \text{ FBRTN} = PGND = GND = 0 \text{ V}, \text{ H} = 5.0 \text{ V}, \text{ L} = 0 \text{ V}, \text{ EN} = \text{VARFREQ} = \text{H}, \text{ DPRSLP} = \text{L}, \overline{\text{PSI}} = 1.05 \text{ V}, \text{ PSI} = 1.05 \text{ V}, \text{$

V<sub>VID</sub> = V<sub>DAC</sub> = 1.2000 V, T<sub>A</sub> = -40°C to 100°C, unless otherwise noted. (Note 1) Current entering a pin (sink current) has a positive sign.

| Parameter                                     | Symbol Conditions       |                                                                                                                                                                                                                                                                                                  |                                 | Тур                             | Max                                | Units |

|-----------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|------------------------------------|-------|

| VOLTAGE MONITORING and PROPOWER GOOD          | TECTION                 |                                                                                                                                                                                                                                                                                                  | •                               |                                 |                                    |       |

| CSREF Reverse Voltage<br>Threshold            | V <sub>RVCSREF</sub>    | Relative to FBRTN, latchoff mode<br>CSREF is falling<br>CSREF is rising                                                                                                                                                                                                                          | -370                            | -300<br>-75                     | -10                                | mV    |

| PWRGD Low Voltage                             | V <sub>PWRGD</sub>      | I <sub>PWRGD(SINK)</sub> = 4 mA                                                                                                                                                                                                                                                                  |                                 | 85                              | 250                                | mV    |

| PWRGD High, Leakage Current                   | I <sub>PWRGD</sub>      | V <sub>PWRDG</sub> = 5.0 V                                                                                                                                                                                                                                                                       |                                 |                                 | 1.0                                | μΑ    |

| PWRGD Startup Delay                           | T <sub>SSPWRGD</sub>    | Measured from CLKEN neg edge to PWRGD pos edge                                                                                                                                                                                                                                                   |                                 | 8.0                             |                                    | ms    |

| PWRGD Latchoff Delay                          | T <sub>LOFFPWRGD</sub>  | Measured from Out-off-Good-Window event to Latchoff (switching stops)                                                                                                                                                                                                                            |                                 | 120                             |                                    | μs    |

| PWRGD Propagation Delay (Note 3)              | T <sub>PDPWRGD</sub>    | Measured from Out-off-Good-Window event to PWRGD neg edge                                                                                                                                                                                                                                        |                                 | 200                             |                                    | ns    |

| Crowbar Latchoff Delay (Note 2)               | T <sub>LOFFCB</sub>     | Measured from Crowbar event to latchoff (switching stops)                                                                                                                                                                                                                                        |                                 | 200                             |                                    | ns    |

| PWRGD Masking Time                            |                         | Triggered by any VID change or OCP event                                                                                                                                                                                                                                                         |                                 | 100                             |                                    | μs    |

| CSREF Soft-Stop Resistance                    |                         | EN = L or latchoff condition                                                                                                                                                                                                                                                                     |                                 | 70                              |                                    | Ω     |

| CURRENT CONTROL<br>CURRENT-SENSE AMPLIFIER (C | SAMP)                   |                                                                                                                                                                                                                                                                                                  |                                 |                                 |                                    |       |

| CSSUM, CSREF Common-Mode<br>Range (Note 2)    |                         | Voltage range of interest                                                                                                                                                                                                                                                                        | 0                               |                                 | 2.0                                | V     |

| CSSUM, CSREF Offset Voltage                   | V <sub>OSCSA</sub>      | CSREF – CSSUM , T <sub>A</sub> = –40°C to 85°C                                                                                                                                                                                                                                                   | -1.2                            |                                 | +1.2                               | mV    |

| CSSUM Bias Current                            | I <sub>BCSSUM</sub>     |                                                                                                                                                                                                                                                                                                  | -20                             |                                 | +20                                | nA    |

| CSREF Bias Current                            | I <sub>BCSREF</sub>     |                                                                                                                                                                                                                                                                                                  | -3.0                            |                                 | +3.0                               | μΑ    |

| CSCOMP Voltage Range (Note 2)                 |                         | Voltage range of interest                                                                                                                                                                                                                                                                        | 0.05                            |                                 | 2.0                                | V     |

| CSCOMP Current                                | ICSCOMPsource           | CSCOMP = 2.0 V, CSSUM forced<br>200 mV below CSREF                                                                                                                                                                                                                                               |                                 | -750                            |                                    | μΑ    |

|                                               | I <sub>CSCOMPsink</sub> | CSSUM forced 200 mV above CSREF                                                                                                                                                                                                                                                                  |                                 | 1.0                             |                                    | mA    |

| CSCOMP Slew Rate (Note 2)                     |                         | C <sub>CSCOMP</sub> = 10 pF, CSREF = VDAC,<br>Open loop configuration<br>CSSUM forced 200 mV below CSREF<br>CSSUM forced 200 mV above CSREF                                                                                                                                                      |                                 | 20<br>–20                       |                                    | V/μs  |

| Gain Bandwidth (Note 2)                       | GBW <sub>CSA</sub>      | Non-inverting unit gain configuration $R_{FB} = 1 \text{ k}\Omega$                                                                                                                                                                                                                               |                                 | 20                              |                                    | MHz   |

| CURRENT MONITORING and PROCURRENT REFERENCE   | DTECTION                | ı ·-                                                                                                                                                                                                                                                                                             |                                 |                                 | 1                                  |       |

| IREF Voltage                                  | $V_{REF}$               | $R_{REF}$ = 80 kΩ to set $I_{REF}$ = 20 μA                                                                                                                                                                                                                                                       | 1.55                            | 1.6                             | 1.65                               | V     |

| CURRENT LIMITER (OCP)                         | <u> </u>                |                                                                                                                                                                                                                                                                                                  |                                 |                                 | -                                  |       |

| , camin                                       |                         | $\label{eq:measured_from_CSCOMP} \begin{tabular}{ll} Measured from CSCOMP to CSREF, \\ $R_{LIM} = 1.5 k\Omega, \\ $3$-ph configuration, $\overline{PSI}$ = H \\ $3$-ph configuration, $\overline{PSI}$ = L \\ $2$-ph configuration, $\overline{PSI}$ = L \\ $1$-ph configuration $\end{tabular}$ | -75<br>-22<br>-75<br>-36<br>-75 | -90<br>-30<br>-90<br>-45<br>-90 | -106<br>-38<br>-106<br>-54<br>-106 | mV    |

| Current Limit Latchoff Delay                  |                         | Measured from OCP event to PWRGD de-assertion                                                                                                                                                                                                                                                    |                                 | 120                             |                                    | μs    |

- 1. All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

- 2. Guaranteed by design or bench characterization, not production tested.

- 3. Based on bench characterization data.

- 4. Timing is referenced to the 90% and 10% points, unless otherwise noted.

### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = PV_{CC} = 5.0 \text{ V}, \text{ FBRTN} = PGND = GND = 0 \text{ V}, \text{ H} = 5.0 \text{ V}, \text{ L} = 0 \text{ V}, \text{ EN} = \text{VARFREQ} = \text{H}, \text{ DPRSLP} = \text{L}, \overline{PSI} = 1.05 \text{ V}, \\ V_{VID} = V_{DAC} = 1.2000 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 100^{\circ}\text{C}, \text{ unless otherwise noted.} \text{ (Note 1) Current entering a pin (sink current) has a positive sign.}$

| Parameter                              | Symbol                             | Conditions                                                                                                                                                                                                                                 | Min                | Тур                    | Max                | Units |

|----------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------|--------------------|-------|

| CURRENT MONITOR                        |                                    |                                                                                                                                                                                                                                            | •                  | •                      |                    |       |

| Current Gain Accuracy                  | I <sub>MON</sub> /I <sub>LIM</sub> | Measured from ILIM to IMON I <sub>LIM</sub> = -20 μA I <sub>LIM</sub> = -10 μA I <sub>LIM</sub> = -5 μA                                                                                                                                    | 3.7<br>3.6<br>3.5  | 4.0<br>4.0<br>4.0      | 4.3<br>4.4<br>4.5  | -     |

| IMON Clamp Voltage                     | V <sub>MAXMON</sub>                | Relative to FBRTN, ILIMP = -30 μA                                                                                                                                                                                                          | 1.0                |                        | 1.15               | ٧     |

| PULSE WIDTH MODULATOR CLOCK OSCILLATOR |                                    |                                                                                                                                                                                                                                            |                    |                        |                    |       |

| RT Voltage                             | V <sub>RT</sub>                    | $\begin{array}{l} \text{VARFREQ} = \text{high, R}_T = 125 \text{ k}\Omega, \\ \text{V}_{\text{VID}} = 1.5000 \text{ V} \\ \text{VARFREQ} = \text{low} \\ \text{See also V}_{\text{RT}}(\text{V}_{\text{VID}}) \text{ formula} \end{array}$ | 1.125<br>0.9       | 1.25<br>1.0            | 1.375<br>1.1       | V     |

| PWM Clock Frequency Range (Note 2)     | f <sub>CLK</sub>                   | Operation of interest                                                                                                                                                                                                                      | 0.3                |                        | 3.0                | MHz   |

| PWM Clock Frequency                    | f <sub>CLK</sub>                   | $\begin{array}{l} T_{A} = +25^{\circ}C, \ V_{VID} = 1.2000 \ V \\ R_{T} = 72 \ k\Omega \\ R_{T} = 120 \ k\Omega \\ R_{T} = 180 \ k\Omega \end{array}$                                                                                      | 1100<br>700<br>500 | 1257<br>800<br>550     | 1400<br>900<br>600 | kHz   |

| RAMP GENERATOR                         |                                    |                                                                                                                                                                                                                                            |                    |                        |                    |       |

| RAMP Voltage                           | $V_{RAMP}$                         | EN = high, I <sub>RAMP</sub> = 60 μA<br>EN = low                                                                                                                                                                                           | 0.9                | 1.0<br>V <sub>IN</sub> | 1.1                | V     |

| RAMP Current Range (Note 2)            | I <sub>RAMP</sub>                  | EN = high<br>EN = low, RAMP = 19 V                                                                                                                                                                                                         | 1.0<br>-1.0        |                        | 100<br>+1.0        | μΑ    |

| PWM COMPARATOR                         | •                                  | •                                                                                                                                                                                                                                          | •                  | •                      |                    |       |

| PWM Comparator Offset (Note 2)         | V <sub>OSRPM</sub>                 | V <sub>RAMP</sub> - V <sub>COMP</sub>                                                                                                                                                                                                      |                    | ±3.0                   |                    | mV    |

| RPM COMPARATOR                         |                                    |                                                                                                                                                                                                                                            |                    | •                      |                    |       |

| RPM Current                            | I <sub>RPM</sub>                   | $V_{VID}$ = 1.2 V, $R_T$ = 215 k $\Omega$<br>See also $I_{RPM}(R_T)$ formula                                                                                                                                                               |                    | -9.0                   |                    | μΑ    |

| RPM Comparator Offset (Note 2)         | V <sub>OSRPM</sub>                 | V <sub>COMP</sub> - (1 + V <sub>RPMTH</sub> )                                                                                                                                                                                              |                    | ±3.0                   |                    | mV    |

| EPWM CLOCK SYNC                        |                                    | •                                                                                                                                                                                                                                          |                    |                        |                    |       |

| Trigger Threshold (Note 2)             |                                    | Relative to COMP sampled T <sub>CLK</sub> time earlier 3-phase configuration 2-phase configuration 1-phase configuration                                                                                                                   |                    | 350<br>400<br>450      |                    | mV    |

| TRDET                                  |                                    |                                                                                                                                                                                                                                            | <b>.</b>           |                        | <u> </u>           |       |

| Trigger Threshold (Note 2)             |                                    |                                                                                                                                                                                                                                            |                    | -450<br>-500<br>-600   |                    | mV    |

| TRDET Low Voltage (Note 2)             | V <sub>LTRDET</sub>                | Logic low, I <sub>TRDETsink</sub> = 4 mA                                                                                                                                                                                                   |                    | 30                     | 300                | mV    |

| TRDET Leakage Current                  | I <sub>HTRDET</sub>                | Logic high, V <sub>TRDET</sub> = VCC                                                                                                                                                                                                       |                    |                        | 5.0                | μΑ    |

| SWITCH AMPLIFIER                       |                                    |                                                                                                                                                                                                                                            |                    |                        |                    |       |

| SW Common Mode Range<br>(Note 2)       | V <sub>SW(X)CM</sub>               | Operation of interest for current sensing                                                                                                                                                                                                  | -600               |                        | +200               | mV    |

| SWFB Input Resistance                  | R <sub>SW(X)</sub>                 | SW <sub>X</sub> = 0 V, SWFB = 0 V                                                                                                                                                                                                          | 20                 | 35                     | 50                 | kΩ    |

| ZERO CURRENT SWITCHING COI             | •                                  |                                                                                                                                                                                                                                            |                    |                        |                    |       |

| SW ZCS Threshold                       | V <sub>DCM(SW1)</sub>              | DCM mode, DPRSLP = 3.3 V                                                                                                                                                                                                                   |                    | -6.0                   |                    | mV    |

- 1. All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

- 2. Guaranteed by design or bench characterization, not production tested.

- 3. Based on bench characterization data.

- 4. Timing is referenced to the 90% and 10% points, unless otherwise noted.

### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = PV_{CC} = 5.0 \text{ V}, \text{ FBRTN} = PGND = GND = 0 \text{ V}, \text{ H} = 5.0 \text{ V}, \text{ L} = 0 \text{ V}, \text{ EN} = \text{VARFREQ} = \text{H}, \text{ DPRSLP} = \text{L}, \overline{PSI} = 1.05 \text{ V}, \\ V_{VID} = V_{DAC} = 1.2000 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 100^{\circ}\text{C}, \text{ unless otherwise noted.} \text{ (Note 1) Current entering a pin (sink current) has a positive sign.}$

| Parameter                                          | Symbol                                                       | Conditions                                                                             | Min  | Тур         | Max       | Units    |

|----------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|------|-------------|-----------|----------|

| ZERO CURRENT SWITCHING CO                          | MPARATOR                                                     |                                                                                        |      |             |           |          |

| Masked Off-Time                                    | <sup>t</sup> OFFMSKD                                         | Measured from DRVH1 neg edge to<br>DRVH1 pos edge at operation max<br>frequency        |      | 600         |           | ns       |

| SYSTEM I/O BUFFERS<br>VID[6:0], DPRSLP, PSI INPUTS |                                                              |                                                                                        |      |             |           |          |

| Input Voltage                                      | Voltage  Refers to driving signal level Logic low Logic high |                                                                                        | 0.7  |             | 0.3       | V        |

| Input Current                                      |                                                              | V = 0.2 V, VID[6:0], DPRSLP<br>(active pulldown to GND)<br>PSI (active pullup to VCC)  |      | -1.0<br>1.0 |           | μΑ       |

| VID Delay Time (Note 2)                            |                                                              | Any VID edge to FB change 10%                                                          | 200  |             |           | ns       |

| VARFREQ                                            | •                                                            | -                                                                                      | •    | •           | •         |          |

| Input Voltage                                      |                                                              | Refers to driving signal level<br>Logic low<br>Logic high                              | 4.0  |             | 0.7       | V        |

| Input Current                                      |                                                              |                                                                                        |      | 1.0         |           | μΑ       |

| EN INPUT                                           |                                                              |                                                                                        | •    | •           |           |          |

| Input Voltage                                      |                                                              | Refers to driving signal level<br>Logic low<br>Logic high                              | 1.9  |             | 0.4       | V        |

| Input Current                                      |                                                              | EN = L or EN = H (static)<br>0.8 V < EN < 1.6 V (during transition)                    |      | 10<br>–70   |           | nA<br>μA |

| PH1, PH0 INPUTS                                    |                                                              |                                                                                        |      |             |           |          |

| Input Voltage                                      |                                                              | Refers to driving signal level<br>Logic low<br>Logic high                              | 4.0  |             | 0.5       | V        |

| Input Current                                      |                                                              |                                                                                        |      | 1.0         |           | μΑ       |

| CLKEN OUTPUT                                       |                                                              |                                                                                        |      |             |           |          |

| Output Low Voltage                                 |                                                              | Logic low, I <sub>sink</sub> = 4 mA                                                    |      | 60          | 200       | mV       |

| Output High, Leakage Current                       |                                                              | Logic high, V <sub>CLKEN</sub> = VCC                                                   |      |             | 1.0       | μΑ       |

| PWM3, OD3 OUTPUTS                                  |                                                              |                                                                                        |      |             |           |          |

| Output Voltage                                     |                                                              | Logic low, $I_{SINK}$ = 400 $\mu A$<br>Logic high, $I_{SOURCE}$ = -400 $\mu A$         | 4.0  | 10<br>5.0   | 100       | mV<br>V  |

| THERMAL MONITORING and PRO                         | OTECTION                                                     |                                                                                        |      |             |           |          |

| TTSNS Voltage Range (Note 2)                       |                                                              |                                                                                        | 0    |             | 5.0       | V        |

| TTSNS Threshold                                    |                                                              | VCC = 5.0 V, TTSNS is falling                                                          | 2.45 | 2.5         | 2.55      | V        |

| TTSNS Hysteresis                                   |                                                              |                                                                                        |      | 95          |           | mV       |

| TTSNS Bias Current                                 |                                                              | TTSNS = 2.6 V                                                                          | -2.0 |             | 2.0       | μΑ       |

| VRTT Output Voltage                                | V <sub>VRTT</sub>                                            | Logic low, $I_{VRTT(SINK)} = 400 \mu A$<br>Logic high, $I_{VRTT(SOURCE)} = -400 \mu A$ | 4.5  | 10<br>5.0   | 100       | mV<br>V  |

| SUPPLY                                             | 1                                                            | <del>_</del>                                                                           |      | T           |           | 1        |

| Supply Voltage Range                               | V <sub>CC</sub>                                              |                                                                                        | 4.5  |             | 5.5       | V        |

| Supply Current                                     |                                                              | EN = high<br>EN = 0 V                                                                  |      | 7<br>10     | 10<br>150 | mA<br>μA |

| VCC OK Threshold                                   | V <sub>CCOK</sub>                                            | VCC is rising                                                                          |      | 4.4         | 4.5       | V        |

| VCC UVLO Threshold                                 | V <sub>CCUVLO</sub>                                          | VCC is falling                                                                         | 4.0  | 4.15        |           | ٧        |

- 1. All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

- 2. Guaranteed by design or bench characterization, not production tested.

- Based on bench characterization data.

Timing is referenced to the 90% and 10% points, unless otherwise noted.

### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = PV_{CC} = 5.0 \text{ V}, \text{ FBRTN} = PGND = GND = 0 \text{ V}, \text{ H} = 5.0 \text{ V}, \text{ L} = 0 \text{ V}, \text{ EN} = \text{VARFREQ} = \text{H}, \text{ DPRSLP} = \text{L}, \overline{PSI} = 1.05 \text{ V}, \\ V_{VID} = V_{DAC} = 1.2000 \text{ V}, \text{ T}_{A} = -40^{\circ}\text{C} \text{ to } 100^{\circ}\text{C}, \text{ unless otherwise noted. (Note 1) Current entering a pin (sink current) has a positive sign.}$

| Parameter                                        | Parameter Symbol Conditions              |                                                                                            |     |            | Max      | Units |

|--------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|-----|------------|----------|-------|

| SUPPLY                                           |                                          |                                                                                            |     | •          | •        |       |

| VCC Hysteresis (Note 2)                          |                                          |                                                                                            |     | 150        |          | mV    |

| HIGH-SIDE MOSFET DRIVER                          |                                          |                                                                                            |     |            |          |       |

| Pullup Resistance, Sourcing<br>Current (Note 3)  |                                          | BST = PVCC                                                                                 |     | 1.8        | 3.3      | Ω     |

| Pulldown Resistance, Sinking<br>Current (Note 3) |                                          | BST = PVCC                                                                                 |     | 1.0        | 2.0      | Ω     |

| Transition Times                                 | tr <sub>DRVH</sub><br>tf <sub>DRVH</sub> | BST = PVCC, C <sub>L</sub> = 3 nF, Figure 2<br>BST = PVCC, C <sub>L</sub> = 3 nF, Figure 2 |     | 15<br>13   | 30<br>25 | ns    |

| Dead Delay Times                                 | tpdh <sub>DRVH</sub>                     | BST = PVCC, Figure 2                                                                       | 15  | 30         | 40       | ns    |

| BST Quiescent Current                            |                                          | EN = L (Shutdown)<br>EN = H, no switching                                                  |     | 1.0<br>200 | 10       | μΑ    |

| LOW-SIDE MOSFET DRIVER                           |                                          |                                                                                            |     |            |          |       |

| Pullup Resistance, Sourcing<br>Current (Note 3)  |                                          |                                                                                            |     | 1.7        | 2.8      | Ω     |

| Pulldown Resistance, Sinking<br>Current (Note 3) |                                          |                                                                                            |     | 0.8        | 1.7      | Ω     |

| Transition Times                                 | tr <sub>DRVL</sub><br>tf <sub>DRVL</sub> | $C_L = 3$ nF, Figure 2<br>$C_L = 3$ nF, Figure 2                                           |     | 15<br>14   | 35<br>35 | ns    |

| Propagation Delay Times                          | tpdh <sub>DRVL</sub>                     | C <sub>L</sub> = 3 nF, Figure 2                                                            |     | 11         | 30       | ns    |

| SW Transition Timeout                            | t <sub>TOSW</sub>                        | DRVH = L, SW = 2.5 V                                                                       | 100 | 250        | 350      | ns    |

| SW Off Threshold                                 | V <sub>OFFSW</sub>                       |                                                                                            |     | 2.5        |          | V     |

| PVCC Quiescent Current                           |                                          | EN = L (Shutdown)<br>EN = H, no switching                                                  |     | 1.0<br>170 | 10       | μΑ    |

| BOOTSTRAP RECTIFIER SWITCH                       | <br>H                                    |                                                                                            |     |            |          | _     |

| On Resistance (Note 3)                           |                                          | EN = L or EN = H and DRVL = H                                                              | 4.0 | 6.0        | 8.0      | Ω     |

- 1. All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

- 2. Guaranteed by design or bench characterization, not production tested.

- 3. Based on bench characterization data.

- 4. Timing is referenced to the 90% and 10% points, unless otherwise noted.

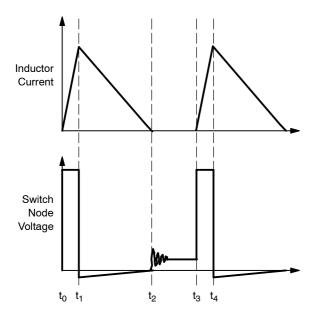

Figure 2. Timing Diagram (Note 4)

### **TEST CIRCUITS**

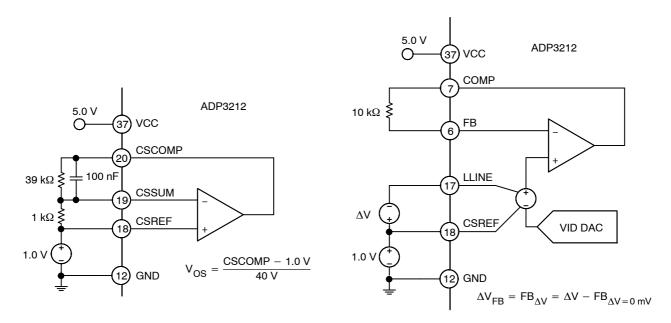

Figure 3. Closed-Loop Output Voltage Accuracy

Figure 4. Current Sense Amplifier, VOS

Figure 5. Positioning Accuracy

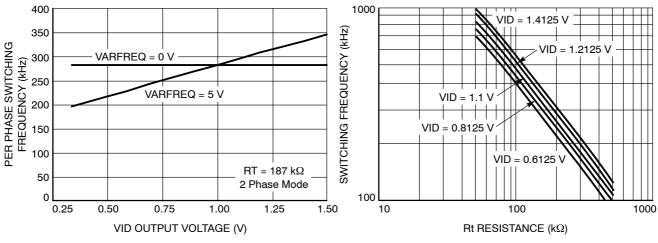

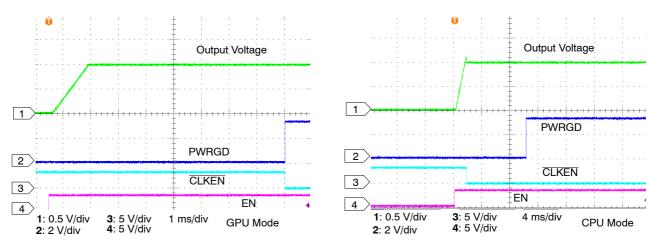

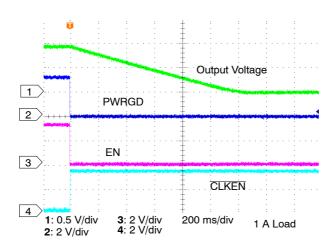

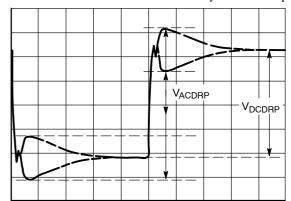

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{VID}$  = 1.5 V,  $T_A$  = 20°C to 100°C, unless otherwise noted.

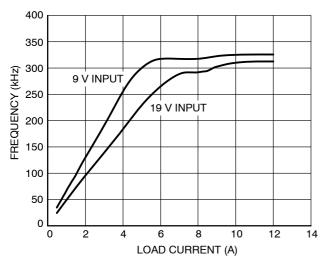

Figure 6. Switching Frequency vs. VID Output Voltage in PWM Mode

Figure 7. Per Phase Switching Frequency vs. RT Resistance

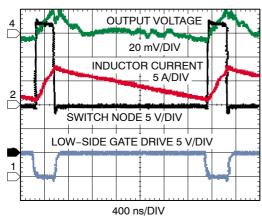

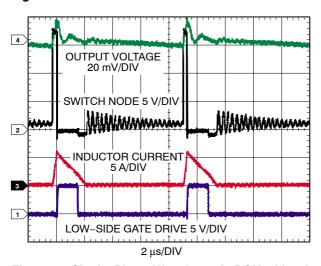

Figure 8. Startup in GPU Mode

Figure 9. Startup in CPU Mode

Figure 10. Shutdown

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{VID}$  = 1.5 V,  $T_A$  = 20°C to 100°C, unless otherwise noted.

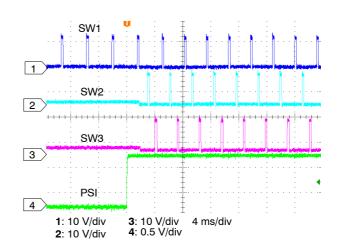

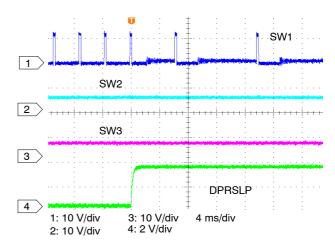

1: 10 V/div 3: 10 V/div 4 ms/div 2: 10 V/div 4: 0.5 V/div

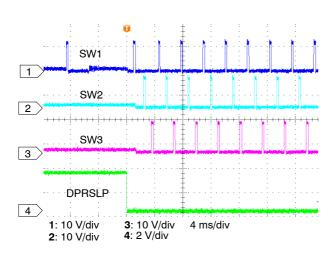

Figure 11. DPRSLP Transition with PSI = High

Figure 12. PSI Transition with DPRSLP = Low

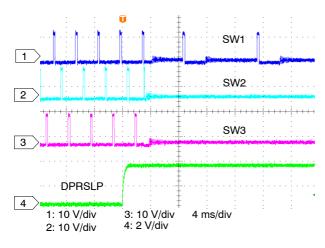

Figure 13. DPRSLP Transition with PSI = High

Figure 14. PSI Transition with DPRSLP = Low

Figure 15. DPRSLP Transition with PSI = Low

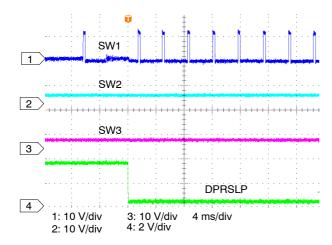

Figure 16. DPRSLP Transition with PSI = Low

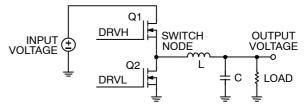

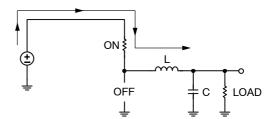

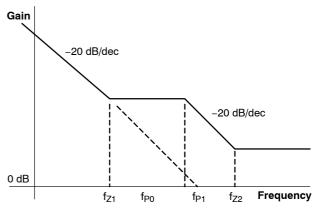

#### **Theory of Operation**

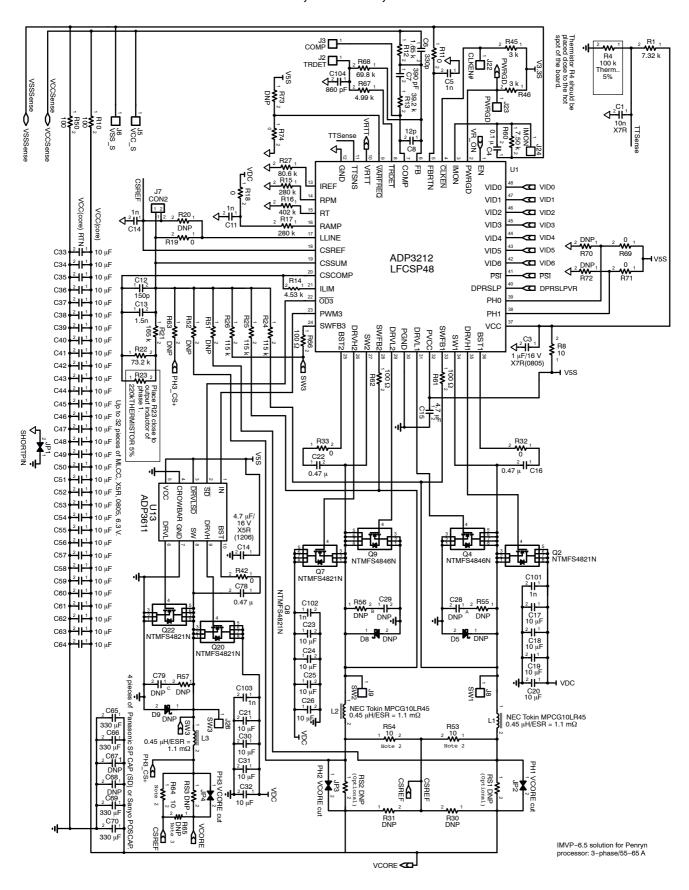

The APD3212/NCP3218/NCP3218G combines multi-mode Pulse-Width Modulated (PWM) control and Ramp-Pulse Modulated (RPM) control with multi-phase logic outputs for use in single-, dual-phase, or triple-phase synchronous buck CPU core supply power converters. The internal 7-bit VID DAC conforms to the Intel IMVP-6.5 specifications.

Multi-phase operation is important for producing the high currents and low voltages demanded by today's microprocessors. Handling high currents in a single-phase converter would put too high of a thermal stress on system components such as the inductors and MOSFETs.

The multimode control of the APD3212/NCP3218/NCP3218G is a stable, high performance architecture that includes

- Current and thermal balance between phases.

- High speed response at the lowest possible switching frequency and minimal count of output decoupling capacitors.

- Minimized thermal switching losses due to lower frequency operation.

- High accuracy load line regulation.

- High current output by supporting 2-phase or 3-phase operation.

- Reduced output ripple due to multi-phase ripple cancellation.

- High power conversion efficiency with heavy and light loads.

- Increased immunity from noise introduced by PC board layout constraints.

- Ease of use due to independent component selection.

- Flexibility in design by allowing optimization for either low cost or high performance.

#### **Number of Phases**