# **Fixed Current-Limiting Power-Distribution Switches**

# **NCP382**

The NCP382 is a single input dual outputs high side power-distribution switch designed for applications where heavy capacitive loads and short-circuits are likely to be encountered. The device includes an integrated 80 mΩ, P-channel MOSFET. The device limits the output current to a desired level by switching into a constant-current mode when the output load exceeds the current-limit threshold or a short is present. The current-limit threshold is internally fixed. The power-switches rise and fall times are controlled to minimize current ringing during switching.

The FLAG logic output asserts low during overcurrent or overtemperature conditions. The switch is controlled by a logic enable input active high or low.

#### **Features**

- 2.5 V 5.5 V Operating Range

- 80 mΩ High-Side MOSFET

- Current Limit: Fixed 500 mA, 1 A and 1.5 A

- Undervoltage Lock-Out (UVLO)

- Soft-Start Prevents Inrush Current

- Thermal Protection

- Soft Turn-Off

- Enable Active High or Low (EN or EN)

- Compliance to IEC61000-4-2 (Level 4)

- ♦ 8.0 kV (Contact)

- 15 kV (Air)

- UL Listed for SOIC package (NCP382xDxxxx) File No. E343275

- IEC60950 Edition 2 for SOIC package (NCP382xDxxxx) -Amendments 1 & 2 Certified (CB Scheme)

- These are Pb-Free Devices

### **Typical Applications**

- Laptops

- USB Ports/Hubs

- TVs

### ON Semiconductor®

www.onsemi.com

### **MARKING DIAGRAM**

XXXXX = Specific Device Code = Assembly Location

= Wafer Lot L = Year

W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

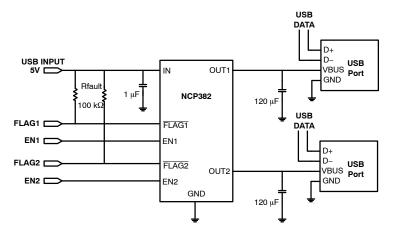

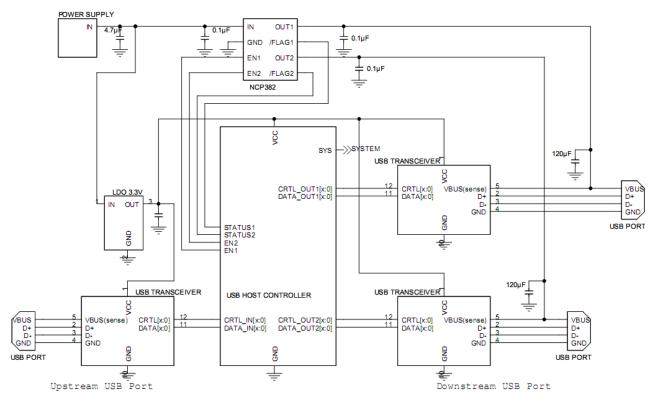

Figure 1. Typical Application Circuit

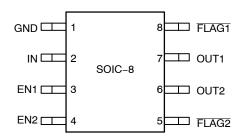

Figure 2. Pin Connections

# PIN FUNCTION DESCRIPTION

| Pin Name | Type | Description                                                                                                                                                                                                                        |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN1      | - 1  | Enable 1 input, logic low/high (i.e. $\overline{\text{EN}}$ or $\overline{\text{EN}}$ ) turns on power switch.                                                                                                                     |

| EN2      | - 1  | Enable 2 input, logic low/high (i.e. $\overline{\text{EN}}$ or $\overline{\text{EN}}$ ) turns on power switch.                                                                                                                     |

| GND      | Р    | Ground connection.                                                                                                                                                                                                                 |

| IN       | Р    | Power–switch input voltage; connect a 1 $\mu$ F or greater ceramic capacitor from IN to GND as close as possible to the IC.                                                                                                        |

| FLAG1    | 0    | Active–low open–drain output 1, asserted during overcurrent or overtemperature conditions. Connect a 10 k $\Omega$ or greater resistor pull–up, otherwise leave unconnected.                                                       |

| FLAG2    | 0    | Active–low open–drain output 2, asserted during overcurrent or overtemperature conditions. Connect a 10 k $\Omega$ or greater resistor pull–up, otherwise leave unconnected.                                                       |

| OUT1     | 0    | Power–switch output1; connect a 1 μF ceramic capacitor from OUT1 to GND, as close as possible to the IC. This minimum value is recommended for USB requirement in terms of load transient response and strong short circuits.      |

| OUT2     | 0    | Power–switch output2; connect a 1 $\mu$ F ceramic capacitor from OUT2 to GND, as close as possible to the IC. This minimum value is recommended for USB requirement in terms of load transient response and strong short circuits. |

#### **MAXIMUM RATINGS**

| Rating                                                                                                | Symbol                                                                                                                             | Value             | Unit |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|

| From IN to OUT1, From IN to OUT2 Supply Voltage (Note 1)                                              | V <sub>IN</sub> , V <sub>OUT1</sub> ,V <sub>OUT2</sub>                                                                             | -7.0 to +7.0      | V    |

| IN, OUT1,OUT2, EN1, EN2, FLAG1, FLAG2 (Note 1)                                                        | V <sub>IN,</sub> V <sub>OUT1,</sub> V <sub>OUT2,</sub> V <sub>EN1,</sub> V <sub>EN2,</sub> V <sub>FLAG1</sub> , V <sub>FLAG2</sub> | -0.3 to +7.0      | V    |

| FLAG1, FLAG2 sink current                                                                             | I <sub>SINK</sub>                                                                                                                  | 1.0               | mA   |

| ESD Withstand Voltage (IEC 61000–4–2) (output only, when bypassed with 1.0 $\mu$ F capacitor minimum) | ESD IEC                                                                                                                            | 15 Air, 8 contact | kV   |

| Human Body Model (HBM) ESD Rating are (Note 2)                                                        | ESD HBM                                                                                                                            | 2000              | V    |

| Machine Model (MM) ESD Rating are (Note 2)                                                            | ESD MM                                                                                                                             | 200               | V    |

| Latch-up protection (Note 3)  - Pins IN, OUT1, OUT2, FLAG1, FLAG2  - EN1, EN2                         | LU                                                                                                                                 | 100               | mA   |

| Maximum Junction Temperature (Note 4)                                                                 | TJ                                                                                                                                 | -40 to + TSD      | °C   |

| Storage Temperature Range                                                                             | T <sub>STG</sub>                                                                                                                   | -40 to + 150      | °C   |

| Moisture Sensitivity (Note 5)                                                                         | MSL                                                                                                                                | Level 1           |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. According to JEDEC standard JESD22-A108.

- 2. This device series contains ESD protection and passes the following tests: Human Body Model (HBM) +/-2.0 kV per JEDEC standard: JESD22-A114 for all pins. Machine Model (MM) +/-200 V per JEDEC standard: JESD22-A115 for all pins.

- 3. Latch up Current Maximum Rating: ±100 mA per JEDEC standard: JESD78 class II.

- 4. A thermal shutdown protection avoids irreversible damage on the device due to power dissipation.

- 5. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020.

#### **OPERATING CONDITIONS**

| Symbol            | Parameter                          | Conditions            | Min | Тур | Max  | Unit |

|-------------------|------------------------------------|-----------------------|-----|-----|------|------|

| V <sub>IN</sub>   | Operational Power Supply           |                       | 2.5 |     | 5.5  | V    |

| V <sub>ENX</sub>  | Enable Voltage                     |                       | 0   |     | 5.5  |      |

| T <sub>A</sub>    | Ambient Temperature Range          |                       | -40 | 25  | +85  | °C   |

| I <sub>SINK</sub> | FLAG sink current                  |                       |     |     | 1    | mA   |

| C <sub>IN</sub>   | Decoupling input capacitor         |                       | 1   |     |      | μF   |

| C <sub>OUTX</sub> | Decoupling output capacitor        | USB port per Hub      | 120 |     |      | μF   |

| $R_{\theta JA}$   | Thermal Resistance Junction-to-Air | (Notes 6 and 7)       |     | 210 |      | °C/W |

| T <sub>J</sub>    | Junction Temperature Range         |                       | -40 | 25  | +125 | °C   |

| I <sub>OUTX</sub> | Recommended Maximum DC current     |                       |     |     | 1.5  | Α    |

| P <sub>D</sub>    | Power Dissipation Rating (Note 8)  | $T_A \le 25^{\circ}C$ | 570 |     |      | mW   |

|                   |                                    | T <sub>A</sub> = 85°C | 285 |     |      | mW   |

- 6. A thermal shutdown protection avoids irreversible damage on the device due to power dissipation.

- 7. The R<sub>BJA</sub> is dependent of the PCB heat dissipation. Announced thermal resistance is the unless PCB dissipation and can be improve with final PCB layout.

- 8. The maximum power dissipation (P<sub>D</sub>) is given by the following formula:  $P_D = \frac{T_{JMAX} T_A}{R_{\theta JA}}$

**ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for  $T_A$  between  $-40^{\circ}C$  to  $+85^{\circ}C$  and  $T_J$  up to  $+125^{\circ}C$  for  $V_{IN}$  between 2.5 V to 5.5 V (Unless otherwise noted). Typical values are referenced to  $T_A = +25^{\circ}C$  and  $V_{IN} = 5$  V.

| Symbol              | Parameter                                           |                                                            | Conditions                                                            | Min  | Тур      | Max        | Unit     |

|---------------------|-----------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|------|----------|------------|----------|

| POWER S             | SWITCH                                              |                                                            |                                                                       |      |          |            |          |

| R <sub>DS(on)</sub> | Static drain-source on-state resistance             | T <sub>J</sub> = 25                                        | °C, V <sub>IN</sub> = 3.6 V to 5 V                                    |      | 80       | 110        | mΩ       |

| , ,                 |                                                     | V <sub>IN</sub> = 5 V                                      | $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}$     |      |          | 140        |          |

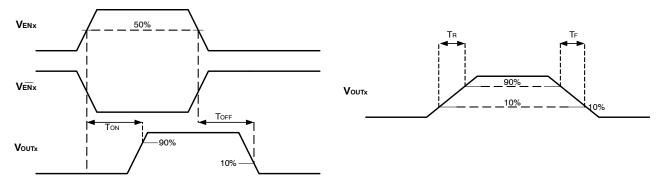

| T <sub>R</sub>      | Output rise time                                    | V <sub>IN</sub> = 5 V                                      | $C_{LOAD} = 1 \mu F$                                                  | 0.3  | 1.0      | 1.5        | ms       |

|                     |                                                     | V <sub>IN</sub> = 2.5 V                                    | $R_{LOAD} = 100 \Omega \text{ (Note 9)}$                              | 0.2  | 0.65     | 1.0        |          |

| T <sub>F</sub>      | Output fall time                                    | V <sub>IN</sub> = 5 V                                      |                                                                       | 0.1  |          | 0.5        |          |

|                     |                                                     | V <sub>IN</sub> = 2.5 V                                    |                                                                       | 0.1  |          | 0.5        |          |

| ENABLE              | INPUT ENx OR ENx                                    |                                                            |                                                                       |      |          |            |          |

| $V_{IH}$            | High-level input voltage                            |                                                            |                                                                       | 1.2  |          |            | V        |

| V <sub>IL</sub>     | Low-level input voltage                             |                                                            |                                                                       |      |          | 0.4        | V        |

| I <sub>ENx</sub>    | Input current                                       | V <sub>EN</sub>                                            | $_{c} = 0 \text{ V}, \text{ V}_{\overline{\text{ENx}}} = 5 \text{ V}$ | -0.5 |          | 0.5        | μΑ       |

| T <sub>ON</sub>     | Turn on time                                        | C <sub>LOAD</sub> = 1 μ                                    | F, R <sub>LOAD</sub> = 100 Ω (Note 9)                                 | 1.0  |          | 3.0        | ms       |

| T <sub>OFF</sub>    | Turn off time                                       |                                                            |                                                                       | 1.0  |          | 3.0        | ms       |

| CURREN'             | T LIMIT                                             |                                                            |                                                                       | -    |          |            |          |

| I <sub>OCP</sub>    | Current-limit threshold (Maximum DC                 | V <sub>IN</sub>                                            | = 5 V, Fixed 0.5 A                                                    | 0.5  | 0.6      | 0.7        | Α        |

|                     | output current I <sub>OUTX</sub> delivered to load) | V <sub>IN</sub> = 5 V, Fixed 1.0 A                         |                                                                       | 1.0  | 1.2      | 1.4        | 1        |

|                     |                                                     | V <sub>IN</sub>                                            | V <sub>IN</sub> = 5 V, Fixed 1.5 A                                    |      |          | 2.0        | 1        |

| T <sub>DET</sub>    | Response time to short circuit                      |                                                            | V <sub>IN</sub> = 5 V                                                 |      | 2.0      |            | μs       |

| T <sub>REG</sub>    | Regulation time                                     |                                                            |                                                                       |      | 3.0      | 4.0        | ms       |

| T <sub>OCP</sub>    | Over current protection time                        |                                                            |                                                                       |      | 20       | 26         | ms       |

| UNDERV              | OLTAGE LOCKOUT                                      | •                                                          |                                                                       | •    | •        | •          |          |

| V <sub>UVLO</sub>   | IN pin low-level input voltage                      |                                                            | V <sub>IN</sub> rising                                                | 2.0  | 2.35     | 2.5        | V        |

| V <sub>HYST</sub>   | IN pin hysteresis                                   |                                                            | T <sub>J</sub> = 25°C                                                 | 25   | 40       | 60         | mV       |

| T <sub>RUVLO</sub>  | Re-arming Time                                      |                                                            | V <sub>IN</sub> rising                                                | 5.0  | 10       | 15         | ms       |

|                     | CURRENT                                             |                                                            |                                                                       |      | 1        |            |          |

| I <sub>INOFF</sub>  | Low-level output supply current                     | V <sub>INI</sub> = 5 V No                                  | load on OUTX, Device OFF                                              |      | 2.0      | 3.0        | μА       |

| ·INOFF              |                                                     | V <sub>ENX</sub>                                           | $= 0 \text{ V or V}_{\overline{\text{ENX}}} = 5 \text{ V}$            |      |          | 0.0        | po t     |

| I <sub>INON</sub>   | High-level output supply current                    | 0.5 A                                                      | T <sub>J</sub> = 25°C                                                 |      |          | 95         | μΑ       |

|                     |                                                     |                                                            | T <sub>J</sub> = 85°C                                                 |      |          | 100        |          |

|                     |                                                     | 1 and 1.5 A                                                | T <sub>J</sub> = 25°C<br>T <sub>J</sub> = 85°C                        |      |          | 115<br>125 |          |

| I <sub>REV</sub>    | Reverse leakage current                             | V <sub>OUTX</sub> = 5 V,<br>V <sub>IN</sub> = 0 V          | T <sub>J</sub> = 25°C                                                 |      | 1.0      | 2.0        | μΑ       |

| FLAG PIN            |                                                     |                                                            |                                                                       | 1    | <u> </u> | <u>I</u>   | <u> </u> |

| V <sub>OL</sub>     | FLAGX output low voltage                            | 1                                                          | FLAGX = 1 mA                                                          |      |          | 400        | mV       |

| I <sub>LEAK</sub>   | Off-state leakage                                   | $V_{\text{FLAGX}} = 1 \text{ IIIA}$                        |                                                                       |      | 0.02     | 1          | μА       |

| T <sub>FLG</sub>    | FLAGX deglitch                                      | V <sub>FLAGX</sub> = 5 V<br>FLAGX de-assertion time due to |                                                                       | 4    | 6        | 9          | ms       |

| FLG                 | -                                                   | overcurrent                                                |                                                                       | 7    |          | J          | 1113     |

| T <sub>FOCP</sub>   | FLAGX deglitch                                      | FLAGX ass                                                  | sertion due to overcurrent                                            | 6    | 8        | 12         | ms       |

| THERMA              | L SHUTDOWN                                          |                                                            |                                                                       |      |          |            |          |

| $T_{SD}$            | Thermal shutdown threshold                          |                                                            |                                                                       |      | 140      |            | °C       |

| T <sub>SDOCP</sub>  | Thermal regulation threshold                        |                                                            |                                                                       |      | 125      |            | °C       |

| T <sub>RSD</sub>    | Thermal regulation rearming threshold               |                                                            |                                                                       |      | 115      |            | °C       |

<sup>9.</sup> Parameters are guaranteed for  $C_{LOAD}$  and  $R_{LOAD}$  connected to the OUTX pin with respect to the ground. 10. Guaranteed by characterization.

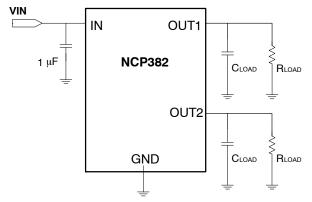

Figure 3. Test Configuration

Figure 4. Voltage Waveform

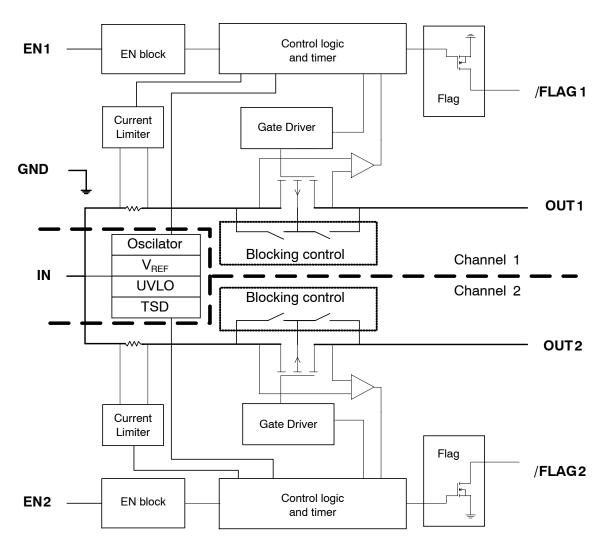

# **BLOCK DIAGRAM**

Figure 5. Block Diagram

### **FUNCTIONAL DESCRIPTION**

#### Overview

The NCP382 is a dual high side power distribution switches designed to protect the input supply voltage in case of heavy capacitive loads, short circuit or over current. In addition, the high side MOSFETs are turned off during undervoltage or thermal shutdown condition. Thanks to the soft start circuitry, NCP382 is able to limit large current and voltage surges.

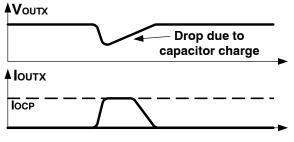

#### **Overcurrent Protection**

NCP382 switches into a constant current regulation mode when the output current is above the  $I_{OCP}$  threshold. Depending on the load, the output voltage is decreased accordingly.

In case of hot plug with heavy capacitive load, the output voltage is brought down to the capacitor voltage.

The NCP382 will limit the current to the I<sub>OCP</sub> threshold value until the charge of the capacitor is completed.

Figure 6. Heavy Capacitive Load

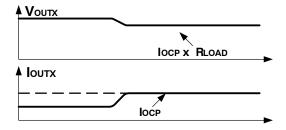

In case of overload, the current is limited to the I<sub>OCP</sub> value and the voltage value is reduced according to the load by the following relation:

$$V_{OUTX} = R_{LOAD2} \times I_{OCP}$$

(eq. 1)

Figure 7. Overload

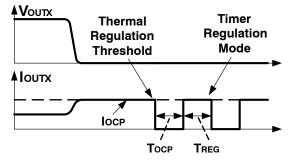

In case of short circuit or huge load, the current is limited to the I<sub>OCP</sub> value within T<sub>DET</sub> time until the short condition is removed. If the output remains shorted or tied to a very low voltage, the junction temperature of the chip exceeds T<sub>SDOCP</sub> value and the device enters in thermal shutdown (MOSFET is turned-off).

Figure 8. Short-Circuit

Then, the device enters in timer regulation mode, described in 2 phases:

- Off-phase: Power MOSFET is off during T<sub>OCP</sub> to allow the die temperature to drop.

- On-phase: regulation current mode during T<sub>REG</sub>. The current is regulated to the I<sub>OCP</sub> level.

The timer regulation mode allows the device to handle high thermal dissipation (in case of short circuit for example) within temperature operating condition.

NCP382 stays in on–phase/off–phase loop until the over current condition is removed or enable pin is toggled.

**Remark:** other regulation modes can be available for different applications. Please contact our On Semiconductor representative for availability.

### FLAG Indicator

The  $\overline{FLAG}$  pin is an open–drain MOSFET asserted low during overcurrent or overtemperature conditions. When an overcurrent fault is detected on the power path,  $\overline{FLAG}$  pin is asserted low at the end of the associate deglitch time (TFOCP). Thanks to this feature, the  $\overline{FLAG}$  pin is not tied low during the charge of a heavy capacitive load or a voltage transient on output. The  $\overline{FLAG}$  pin remains low until the fault is removed. Then, the  $\overline{FLAG}$  pin goes high at the end of  $T_{FGL}$

#### Undervoltage Lock-out

Thanks to a built–in under voltage lockout (UVLO) circuitry, the output remains disconnected from input until  $V_{IN}$  voltage is above  $V_{UVLO}$ . This circuit has a  $V_{HYST}$  hysteresis witch provides noise immunity to transient condition.

#### **Thermal Sense**

Thermal shutdown turns off the power MOSFET if the die temperature exceeds T<sub>SD</sub>. A built-in hysteresis prevents the part from turning on until the die temperature cools at TRSD.

#### **Enable Input**

Enable pin must be driven by a logic signal (CMOS or TTL compatible) or connected to the GND or VIN. A logic low on  $\overline{ENX}$  or high on ENX turns—on the device. A logic high on  $\overline{ENX}$  or low on ENX turns off device and reduces the current consumption down to  $I_{INOFF}$ .

## **Blocking Control**

The blocking control circuitry switches the bulk of the power MOS. When the part is off, the body diode limits the

leakage current  $I_{REV}$  from OUTX to IN. In this mode, anode of the body diode is connected to IN pin and cathode is connected to OUTX pin. In operating condition, anode of the body diode is connected to OUTX pin and cathode is connected to IN pin preventing the discharge of the power supply.

## **APPLICATION INFORMATION**

#### **Power Dissipation**

The junction temperature of the device depends on different contributing factors such as board layout, ambient temperature, device environment, etc... Yet, the main contributor in term of junction temperature is the power dissipation of the power MOSFET. Assuming this, the power dissipation and the junction temperature in normal mode can be calculated with the following equations:

$$P_D = R_{DS(on)} \times \left( \left( I_{OUT1} \right)^2 + \left( I_{OUT2} \right)^2 \right)$$

(eq. 2)

$P_D$  = Power dissipation (W)

$R_{DS(on)}$  = Power MOSFET on resistance ( $\Omega$ )  $I_{OUTx}$  = Output current in channel X (A)

$T_{,l} = P_{,D} \times R_{\theta,lA} + T_{,A} \qquad (eq. 3)$

$T_J$  = Junction temperature (°C)

$R_{\theta,IA}$  = Package thermal resistance (°C/W)

$T_A$  = Ambient temperature (°C)

Power dissipation in regulation mode can be calculated by taking into account the drop  $V_{IN}$  – $V_{OUTX}$  link to the load by the following relation:

$$P_{D} = ((V_{IN} - R_{LOAD1} \times I_{OCP}) + (V_{IN} - R_{LOAD2} \times I_{OCP}))$$

$$\times I_{OCP}$$

(eq. 4)

$P_D$  = Power dissipation (W)  $V_{IN}$  = Input Voltage (V)

$R_{LOADX}$  = Load Resistance on channel  $X(\Omega)$  $I_{OCP}$  = Output regulated current (A)

#### **PCB Recommendations**

The NCP382 integrates two PMOS FET rated up to 1.5 A, and the PCB design rules must be respected to properly evacuate the heat out of the silicon. By increasing PCB area, the  $R_{\theta JA}$  of the package can be decreased, allowing higher current.

Figure 9. USB Host Typical Application

# **ORDERING INFORMATION**

| Device               | Marking | Active<br>Enable<br>Level | Over<br>Current<br>Limit | Evaluation<br>Board  | UL<br>236<br>7 | IEC60950<br>Ed2 (CB<br>Scheme) | IEC60950<br>Ed2 Ad1,<br>Ad2 | Package   | Shipping <sup>†</sup> |

|----------------------|---------|---------------------------|--------------------------|----------------------|----------------|--------------------------------|-----------------------------|-----------|-----------------------|

| NCP382LD05AA-<br>R2G | 382L05  |                           | 0.5 A                    | NCP382LD<br>05AAGEVB | Y              | Y                              | Y                           |           |                       |

| NCP382LD10AA-<br>R2G | 382L10  | ENx<br>Low                | 1.0 A                    | NCP382LD<br>10AAGEVB | Y              | Y                              | Y                           |           |                       |

| NCP382LD15AA-<br>R2G | 382L15  |                           | 1.5 A                    | NCP382LD<br>15AAGEVB | Y              | Y                              | Y                           | SOIC-8    | 2500 /                |

| NCP382HD05A-<br>AR2G | 382H05  |                           | 0.5 A                    | NCP382HD<br>05AAGEVB | Y              | Y                              | Y                           | (Pb-Free) | Tape / Reel           |

| NCP382HD10A-<br>AR2G | 382H10  | ENx<br>High               | 1.0 A                    | NCP382HD<br>10AAGEVB | Y              | Y                              | Y                           |           |                       |

| NCP382HD15A-<br>AR2G | 382H15  |                           | 1.5 A                    | NCP382HD<br>15AAGEVB | Υ              | Y                              | Y                           |           |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

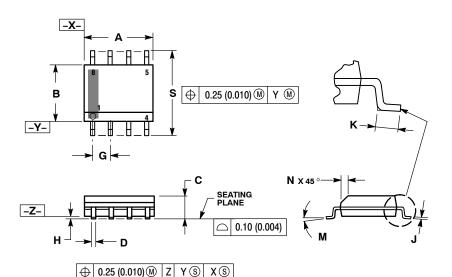

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIN | IETERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 4.80   | 5.00   | 0.189     | 0.197 |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |

| С   | 1.35   | 1.75   | 0.053     | 0.069 |  |

| D   | 0.33   | 0.51   | 0.013     | 0.020 |  |

| G   | 1.27   | 7 BSC  | 0.050 BSC |       |  |

| Н   | 0.10   | 0.25   | 0.004     | 0.010 |  |

| J   | 0.19   | 0.25   | 0.007     | 0.010 |  |

| K   | 0.40   | 1.27   | 0.016     | 0.050 |  |

| М   | 0 ° 8  |        | 0 °       | 8 °   |  |

| N   | 0.25   | 0.50   | 0.010     | 0.020 |  |

| S   | 5.80   | 6.20   | 0.228     | 0.244 |  |

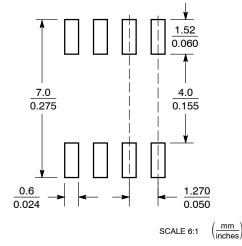

## **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week = Pb-Free Package XXXXXX AYWW AYWW H  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α

= Year ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

## SOIC-8 NB CASE 751-07 ISSUE AK

# DATE 16 FEB 2011

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     | 27112 101 22 2                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            |                                                                                                                                                                         |

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1                              |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | 8. DHAIN 1  STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON   | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| 6. VEE 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                   | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | a COLLECTOR/ANODE                                                                                                                                                       |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                         |

|                                                                                                                                                                    |                                                                                                                                                           |                                                                                                                                                     |                                                                                                                                                                         |

| DOCUMENT NUMBER: | 98ASB42564B | Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|---------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                 | PAGE 2 OF 2 |  |

ON Semiconductor and IN are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Management IC Development Tools category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

EVALZ ADP130-1.2-EVALZ ADP130-1.5-EVALZ ADP130-1.8-EVALZ ADP1712-3.3-EVALZ ADP1714-3.3-EVALZ ADP1715-3.3-EVALZ ADP1716-2.5-EVALZ ADP1740-1.5-EVALZ ADP1752-1.5-EVALZ ADP1828LC-EVALZ ADP1870-0.3-EVALZ ADP1871-0.6-EVALZ ADP1873-0.6-EVALZ ADP1874-0.3-EVALZ ADP1882-1.0-EVALZ ADP199CB-EVALZ ADP2102-1.25-EVALZ ADP2102-1.875EVALZ ADP2102-1.8-EVALZ ADP2102-2-EVALZ ADP2102-3-EVALZ ADP2102-4-EVALZ ADP2106-1.8-EVALZ ADP2147CB-110EVALZ AS3606-DB BQ24010EVM BQ24075TEVM BQ24155EVM BQ24157EVM-697 BQ24160EVM-742 BQ24296MEVM-655 BQ25010EVM BQ3055EVM NCV891330PD50GEVB ISLUSBI2CKITIZ LM2744EVAL LM2854EVAL LM3658SD-AEV/NOPB LM3658SDEV/NOPB LM4510SDEV/NOPB LM5033SD-EVAL LP38512TS-1.8EV