## Dual Input, Single Output Power Source Multiplexer

The NCP3901 integrated circuit is a dual input, single output power source multiplexer. It is optimized for multiplexing 2 different charging inputs to feed a single input battery charger. To address all types of applications, the device is able to support autonomous and slave modes of operation. Reverse USB on-the-go is fully supported.

### Features

- 3 A DC Minimum Current through Power Paths

- Reverse 5 V OTG Support through VINA Path

- Maximum 20 V Over Voltage Threshold

- 28 V Absolute Maximum Voltage on VINA

- Compliance with IEC61000-4-5 at 100 V for VINA

- Indication of Presence of Second Input

- Autonomous Priority Selection and Switch Over Lock

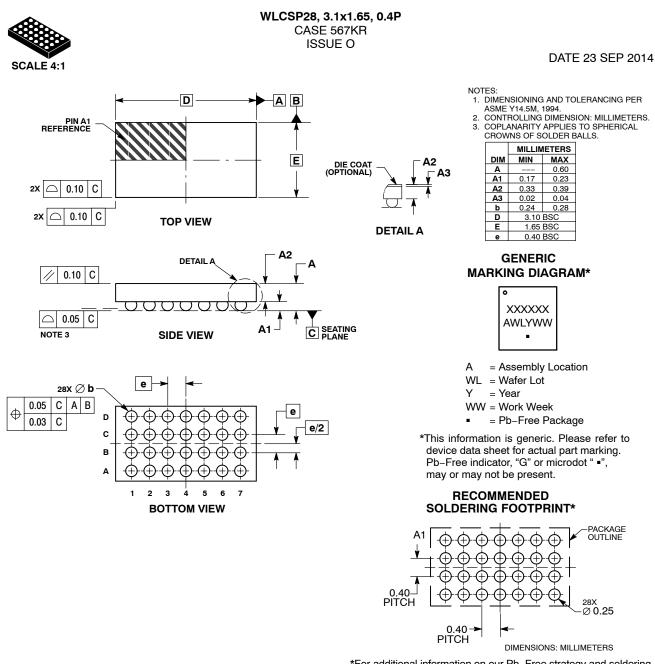

- Small Footprint: 3.1 x 1.65 mm WLCSP28 0.4 mm Pitch

- 30 ms Minimum Break–before–make Time

- This is a Pb–Free Device

### **Typical Applications**

- Handheld Devices

- Tablets

- Smart Phone

- PDAs

### **ON Semiconductor®**

#### www.onsemi.com

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 11 of this data sheet.

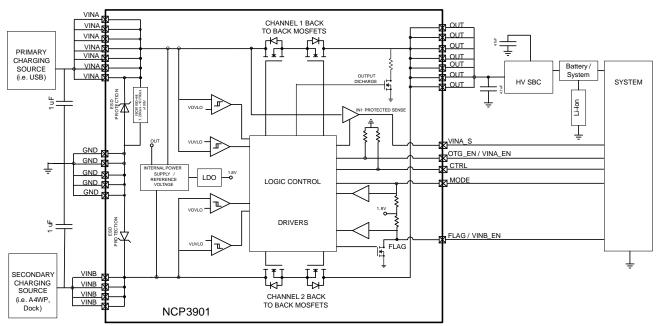

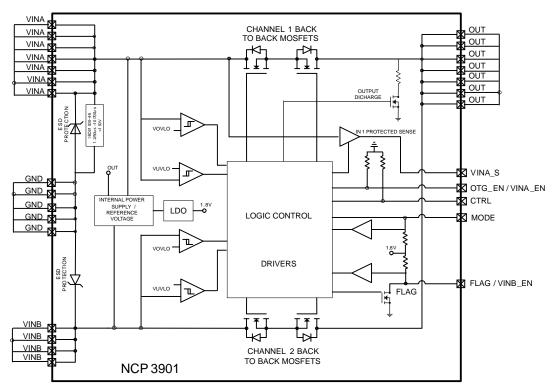

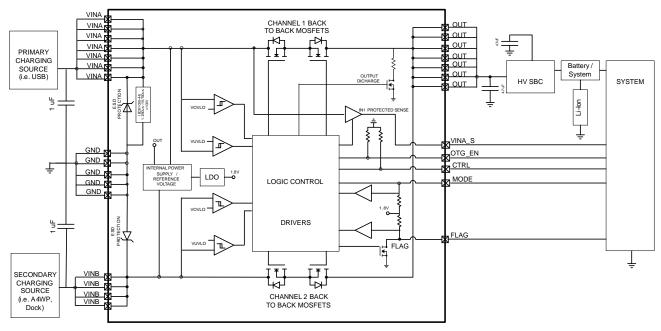

Figure 1. Typical Application Circuit

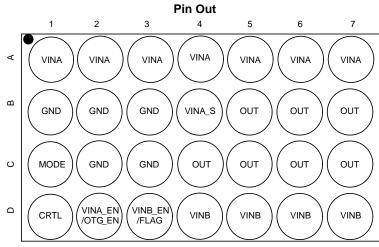

#### Table 1. PIN FUNCTIONAL DESCRIPTION

| Pin | Name           | Туре                                 | Description                                                                                                                           |  |  |  |

|-----|----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1  |                |                                      |                                                                                                                                       |  |  |  |

| A2  |                |                                      |                                                                                                                                       |  |  |  |

| A3  |                |                                      |                                                                                                                                       |  |  |  |

| A4  | VINA           | POWER                                | Channel 1 power input path. These pins must be decoupled with a 1 $\mu$ F input capacitor.                                            |  |  |  |

| A5  |                |                                      |                                                                                                                                       |  |  |  |

| A6  |                |                                      |                                                                                                                                       |  |  |  |

| A7  |                |                                      |                                                                                                                                       |  |  |  |

| C4  |                |                                      |                                                                                                                                       |  |  |  |

| B5  |                |                                      |                                                                                                                                       |  |  |  |

| B6  |                |                                      |                                                                                                                                       |  |  |  |

| B7  | OUT            | POWER                                | Output power path. Connected to battery charger. These pins must be decoupled with a 4.7 $\mu$ F input capacitor.                     |  |  |  |

| C5  |                |                                      |                                                                                                                                       |  |  |  |

| C6  |                |                                      |                                                                                                                                       |  |  |  |

| C7  |                |                                      |                                                                                                                                       |  |  |  |

| B1  |                |                                      |                                                                                                                                       |  |  |  |

| B2  |                |                                      |                                                                                                                                       |  |  |  |

| B3  | GND            | GROUND                               | Ground. Must be connected to a ground plane.                                                                                          |  |  |  |

| C2  |                |                                      |                                                                                                                                       |  |  |  |

| C3  |                |                                      |                                                                                                                                       |  |  |  |

| D4  |                |                                      |                                                                                                                                       |  |  |  |

| D5  | VINB           | POWER                                | Channel 2 power input path. These pins must be decoupled with a                                                                       |  |  |  |

| D6  |                |                                      | 1 μF input capacitor.                                                                                                                 |  |  |  |

| D7  |                |                                      |                                                                                                                                       |  |  |  |

| C1  | MODE           | DIGITAL INPUT                        | Digital Input Pin. Used to determine autonomous-or slave mode.                                                                        |  |  |  |

| D1  | CRTL           | DIGITAL INPUT                        | Digital Input Pin. Used to determine autonomous–locked or autono-<br>mous–not locked mode.                                            |  |  |  |

| B4  | VINA_S         | ANALOG OUTPUT                        | Image of VINA input when VINA is within the operating range.                                                                          |  |  |  |

| D2  | VINA_EN/OTG_EN | DIGITAL INPUT                        | Used to select USB On-The-Go mode on channel 1                                                                                        |  |  |  |

| D3  | VINB_EN/FLAG   | DIGITAL INPUT / OPEN<br>DRAIN OUTPUT | VINB valid indicator. This pin is used to indicate VINB is valid. Can also be used as an input to enable both VINA and VINB channels. |  |  |  |

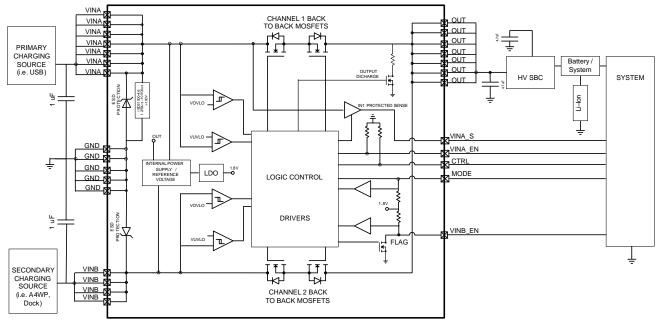

Figure 2. Package TOP VIEW

#### **Table 2. MAXIMUM RATINGS**

| Rating                                                              | Symbol            | Value       | Unit |

|---------------------------------------------------------------------|-------------------|-------------|------|

| VINA, (Note 1)                                                      | V                 | -0.3 to +29 | V    |

| VINA, (Note 2)                                                      | V <sub>INA</sub>  | 100         | V    |

| VINB, VINA_S (Note 1)                                               | V <sub>INB</sub>  | -0.3 to +21 | V    |

| OUT (Note 1)                                                        | V <sub>OUT</sub>  | –0.3 to +18 | V    |

| CTRL, MODE, VINA_EN/OTG_EN, VINB_EN/FLAG (Note 1)                   | V <sub>CTRL</sub> | –0.3 to +6  | V    |

| Storage Temperature Range                                           | T <sub>STG</sub>  | -65 to +150 | °C   |

| Maximum Junction Temperature (Note 3)                               | TJ                | -40 to +TSD | °C   |

| Moisture Sensitivity (Note 4)                                       | MSL               | Level 1     |      |

| Human Body Model (HBM) ESD Rating (JEDEC standard: JESD22–A114)     | ESD HBM           | 2500        | V    |

| Charged Device Model (CDM) ESD Rating (JEDEC standard: JESD22–A114) | ESD CDM           | 2000        | V    |

| Latch up Current (JEDEC standard: JESD78 class II):                 | ILU               | ±100        | mA   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1. With Respect to GND. According to JEDEC standard JESD22–A108.

2. With Respect to GND. According to standard IEC61000-4-5 1.2/50 μs.

3. A thermal shutdown protection avoids irreversible damage on the device due to power dissipation.

4. Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J-STD-020.

#### **Table 3. OPERATING CONDITION**

| Symbol                                                                    | Parameter                          | Conditions                     | Min | Тур | Max  | Unit |

|---------------------------------------------------------------------------|------------------------------------|--------------------------------|-----|-----|------|------|

| V <sub>INA</sub>                                                          | Operational Power Supply on VINA   |                                | 0   |     | 28   | V    |

| V <sub>INB</sub>                                                          | Operational Power Supply on VINB   |                                | 0   |     | 20   | V    |

| V <sub>CTRL</sub> ,V <sub>MODE</sub> ,<br>VINA_EN/OTG_EN,<br>VINB_EN/FLAG | Operational Supply                 |                                | 0   |     | 5.5  | V    |

| I <sub>OUT</sub>                                                          | Operational Output Current         |                                | 0   |     | 3    | А    |

| V <sub>OUT</sub>                                                          | Operational Supply on OUT          | OTG mode,<br>VINA = VINB = 0 V | 0   |     | 5.5  | V    |

|                                                                           |                                    | Charging mode                  | 0   |     | 17.3 | V    |

| C <sub>IN</sub>                                                           | Input Capacitor                    |                                |     | 1   |      | μF   |

| C <sub>OUT</sub>                                                          | Output Capacitor                   |                                |     | 4.7 |      | μF   |

| Raja                                                                      | Thermal Resistance Junction to Air | (Notes 3 and 5)                |     | 60  |      | °C/W |

| TJ                                                                        | Junction Temperature Range         |                                | -40 | 25  | +125 | °C   |

5. The  $R_{0JA}$  is dependent on the PCB heat dissipation. Board used to drive this data was a 2s2p JEDEC PCB standard.

**Table 4. ELECTRICAL CHARACTERISTICS** Min & Max Limits apply for T<sub>A</sub> between  $-40^{\circ}$ C to  $+85^{\circ}$ C and T<sub>J</sub> up to  $+125^{\circ}$ C for V<sub>IN</sub> between V<sub>UVLO</sub> to V<sub>OVLO</sub> (Unless otherwise noted) Typical values are referenced to T<sub>A</sub> =  $+25^{\circ}$ C and V<sub>IN</sub> = 5 V (Unless otherwise noted).

| Symbol             | Parameter                                          | Conditions                                              |      | Тур  | Max | Unit |

|--------------------|----------------------------------------------------|---------------------------------------------------------|------|------|-----|------|

| CORE               |                                                    |                                                         |      |      |     |      |

| V <sub>UVLO</sub>  | Under Voltage Lockout ap-                          | Rising                                                  | -    | -    | 3.0 | V    |

|                    | plied to VINA, VINB or OUT                         | Falling                                                 | 2.45 | -    | -   | V    |

| V <sub>OVLO</sub>  | Over Voltage Lockout Re-<br>ferred to VINA or VINB | Rising                                                  |      | 17   |     | V    |

|                    |                                                    | Falling                                                 |      | 16.4 |     | V    |

| I <sub>OFF</sub>   | Stand by current                                   | Measured on VOUT, VINA and VINB < UVLO,<br>OTG mode off |      | 20   |     | μΑ   |

| I <sub>ON</sub>    | Quiescent Current                                  | VINB > UVLO                                             |      |      | 100 |      |

|                    |                                                    | VINA and VINB > UVLO (including FLAG pull down)         |      |      | 200 |      |

| VINTPUP            | Internal pull up                                   | Measured on FLAG pin or MODE pin                        | 1.6  | 1.8  | 2   | V    |

| V <sub>CTRLH</sub> | CTRL High- input voltage                           |                                                         | 2.2  |      | 5.5 | V    |

6. Guaranteed by design and characterization.

| Table 4. ELECTRICAL CHARACTERISTICS Min & Max Limits apply for T <sub>A</sub> between -40°C to +85°C and T <sub>J</sub> up to + 125°C for V <sub>IN</sub>    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| between $V_{UVLO}$ to $V_{OVLO}$ (Unless otherwise noted) Typical values are referenced to $T_A = +25^{\circ}C$ and $V_{IN} = 5 V$ (Unless otherwise noted). |

| Symbol               | Parameter                                                              | Conditions                                                        | Min | Тур | Max | Unit |

|----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| CORE                 |                                                                        |                                                                   |     |     |     |      |

| VIH                  | MODE, VINA_EN/OTG_EN, VI                                               | MODE, VINA_EN/OTG_EN, VINB_EN/FLAG, CTRL High-level input voltage |     |     | 5.5 | V    |

| V <sub>IL</sub>      | MODE, VINA_EN/OTG_EN, CRTL, VINB_EN/FLAG, CTRL Low-level input voltage |                                                                   |     |     | 0.4 | V    |

| V <sub>FLGL</sub>    | VINB_EN/FLAG Low-level output voltage                                  |                                                                   |     |     | 0.4 | V    |

| R <sub>FLGPUP</sub>  | VINB_EN/FLAG pull up resistar                                          | VINB_EN/FLAG pull up resistance                                   |     |     |     | kΩ   |

| R <sub>MODEPUP</sub> | MODE pin pull up resistance                                            |                                                                   |     | 100 |     | kΩ   |

| R <sub>PULDN</sub>   | VINA_EN/OTG_EN, CRTL pins pull down resistance                         |                                                                   |     | 500 |     | kΩ   |

| R <sub>DIS</sub>     | Output Discharge Resistance                                            | During Break before make transition, measured on OUT pin          |     | 500 |     | Ω    |

POWER

| POWER                            |                            |                                                                                                                             |             |    |      |    |

|----------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|----|------|----|

| R <sub>DSONA</sub>               | On resistance input VINA   | $V_{INA} > 4 V$                                                                                                             |             | 50 | 80   | mΩ |

| R <sub>DSONB</sub>               | On resistance input VINB   | $V_{\rm INB} > 4 V$                                                                                                         |             | 50 | 80   | mΩ |

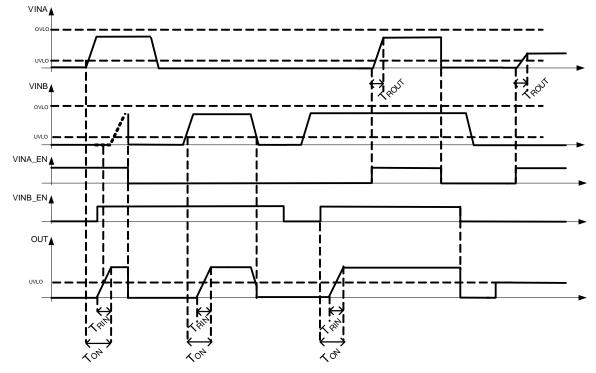

| T <sub>RIN</sub>                 | Soft Start on both channel | From 10% to 90% of VINA or VINB, CLOAD = $4.7 \ \mu$ F, RLOAD = $500 \ \Omega$ .                                            |             |    | 800  | μs |

| T <sub>ROUT</sub>                | Soft Start on both channel | VOUT = 5V. From 10% to 90% of VINA or VINB, CLOAD = 4.7 $\mu$ F, RLOAD = 500 $\Omega$ .                                     | · · · · · · |    | 800  | μS |

| I <sub>RHMX</sub> Inrush current |                            | Supply on VINA = 5 V or 10 V or VINB = 5 V or 10 V or VOUT = 5 V CLOAD = 4.7 $\mu$ F, RLOAD = 500 $\Omega$ . (Note 6)       |             |    | 800  | mA |

|                                  |                            | Total charge on C <sub>OUT</sub> during T <sub>ON</sub> time (Note 6)                                                       |             |    | 50   | μC |

|                                  |                            | Supply on VINA or VINB or VOUT CLOAD = 4.7 $\mu$ F, RLOAD = 500 $\Omega$ . (Note 6)                                         |             |    | 1    | A  |

| T <sub>ON</sub>                  | Turn–on time               | Slave Mode, from $V_{INA\_EN} = 1$ to $V_{OUT} = 90\%$ of $V_{INA}$ or $V_{INB\_EN} = 1$ to $V_{OUT} = 90\%$ of $V_{INB}$ . |             |    | 800  | μS |

| V <sub>OUTMAX</sub>              | VOUT maximum voltage       | VINA from 0 V to 28 V in 3 V/µs and COUT = 4.7 $\mu$ F                                                                      |             |    | 17.3 | V  |

|                                  |                            | VINB from 0 V to 20 V in 3 V/µs and COUT = 4.7 $\mu$ F                                                                      |             |    |      |    |

|                                  |                            | 100 V surge holdoff to support IEC 61000–4–5 on VINA. (Note 6)                                                              |             |    |      |    |

### CONTROL and TIMING

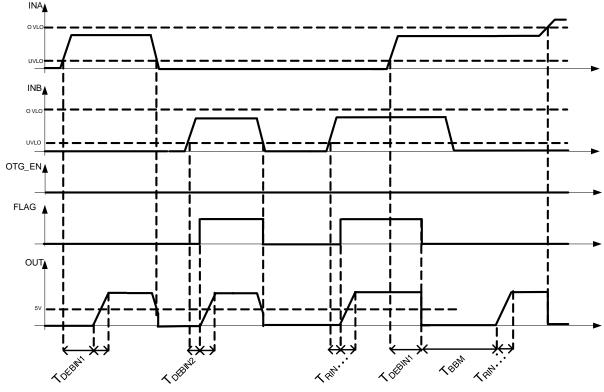

| T <sub>DEBINA</sub> | Debounce time for V <sub>INA</sub> valid | From V <sub>UVLO</sub> < V <sub>INA</sub> < V <sub>OVLO</sub> to V <sub>INA</sub> enable<br>(excluding soft start) |  | 15  | ms |

|---------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|-----|----|

| T <sub>DEBINB</sub> | Debounce time for V <sub>INB</sub> valid | From V <sub>UVLO</sub> < V <sub>INB</sub> < V <sub>OVLO</sub> to V <sub>INB</sub> enable<br>(excluding soft start) |  | 1   | ms |

| T <sub>CRTL</sub>   | CRTL pin deglitcher                      |                                                                                                                    |  | 100 | μS |

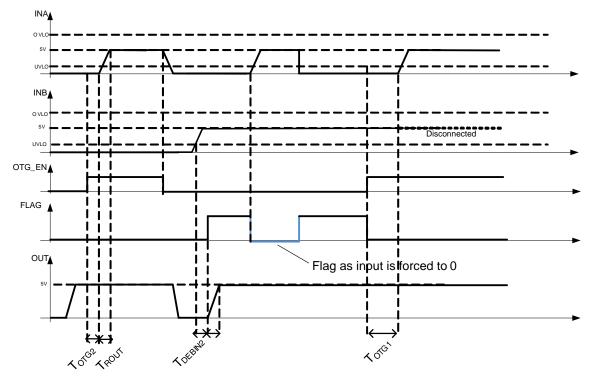

| T <sub>OTG1</sub>   | OTG wait time                            | Autonomous Mode, VINB valid, From VINA_EN/<br>OTG_EN = 1 to VINA valid (excluding soft start)                      |  | 10  | ms |

| T <sub>OTG2</sub>   |                                          | Autonomous Mode, VINB not valid, From VINA_EN/<br>OTG_EN = 1 to VINA valid (excluding soft start)                  |  | 1   | ms |

| T <sub>BBM</sub>    | Break before make time                   | Autonomous Mode, From VINA valid to VINB valid or<br>from VINB valid to VINA valid                                 |  | 30  | ms |

### INPUT SENSE PIN

| VINSDRP  | Voltage Drop VINA – VINA_S               | 20 mA sink on $V_{INA_S}$ |  | 200 | mV |

|----------|------------------------------------------|---------------------------|--|-----|----|

| VINSNSMX | Max Voltage on VINA_S volt-<br>age sense | (Note 6)                  |  | 20  | V  |

### THERMAL SHUTDOWN

| T <sub>SD</sub> | Thermal Shutdown | Temperature Rising  | 150 | °C |

|-----------------|------------------|---------------------|-----|----|

|                 |                  | Temperature Falling | 135 |    |

6. Guaranteed by design and characterization.

#### **Functional Description**

Figure 3. Block Diagram

#### Overview

The NCP3901 is a 2 to 1 flexible power source selector with arbitration logic. A primary power path (VINA) and secondary power path (VINB) are switched to a single pin (OUT) that provides power to a system (battery charger input).The two inputs (VINA and VINB) are Over Voltage protected. The Over Voltage Threshold is set in such a way that, considering pass MOSFET turn off time, the absolute highest voltage at the OUT pin with a 3 V/µs rising input voltage will be 20 V.

In addition, VINA is connected to an active clamp that protects all downstream circuitry up to a high voltage surge of 100 Vas defined by the IEC61000–4–5 1.2/50  $\mu$ s and 10/700  $\mu$ s standard. The IC is protected against reverse voltage applied to the OUT pin on both inputs by use of back to back power MOSFETs.

When a valid voltage is applied to the OUT pin, a digital input VINA\_EN/OTG\_EN pin will allow this voltage to pass through the power channel 1 from OUT to VINA.

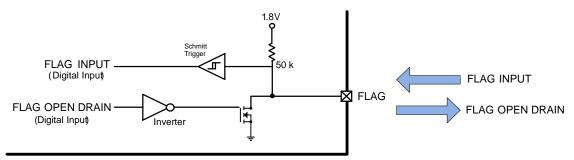

The IC contains a VINB\_EN/FLAG input that informs the controlling logic if the secondary channel is conducting or not.The VINB\_EN/FLAG pin can also be used as an input signal in order to enable both inputs at the same time.

The IC features a VINA\_S protected and current limited output as soon as the VINA voltage is valid (operating range).

Depending on the MODE pin level, the IC will operate in "Autonomous" or "Slave" mode.

- If MODE pin is high the part operates in Slave Mode

- If MODE pin is low the part operates in Autonomous Mode

In Autonomous mode, the CTRL pin will prevent, if pulled high, the part from switching from one input to the other one. MODE digital pin, if pulled high, can also be used to do this.

Finally, a thermal protection will stop the IC when exceeding the TSD threshold. The IC function will be enabled automatically when the part cools down.

### Mode Selection

Mode selection to support multiple applications is based on the CTRL and MODE pins, as depicted in the table below. If no external components are connected to the CRTL and MODE pins, the device is configured in slave mode.

| MODE Pin | CTRL Pin | PMUX behavior                |

|----------|----------|------------------------------|

| Low      | Low      | Autonomous mode – Not Locked |

| Low      | High     | Autonomous mode – Locked     |

| High     | Low      |                              |

| High     | High     | Slave mode                   |

### Mode 1 – Slave Mode

In slave mode, the NCP3901 is directly control by the host. The OTG and FLAG pins are respectively assigned to VINA\_EN and VINB\_EN, directly controlling input channel A and input channel B.

| VINA_EN       | VINB_EN        | Selected Path            |  |  |

|---------------|----------------|--------------------------|--|--|

| Low           | Low            | None                     |  |  |

| Low (default) | High (default) | VINB Conducting          |  |  |

| High          | Low            | VINA Conducting          |  |  |

| High          | High           | VINB and VINA Conducting |  |  |

Figure 4. Signal Timing in Slave Mode

### Mode 2 – Autonomous Mode

#### Autonomous Mode – Not Locked

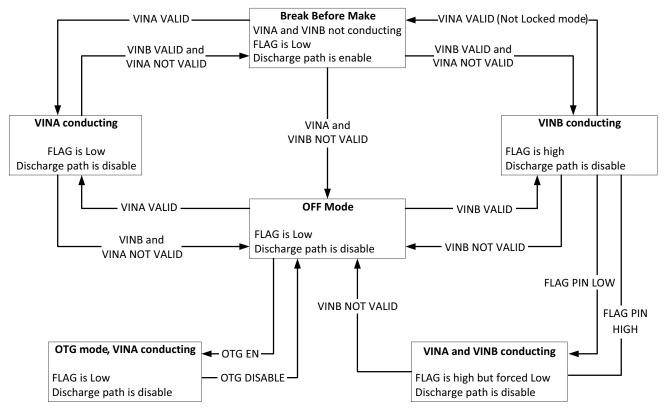

In autonomous not locked mode, the device uses its own logic to determine which input path is conducting and provides information to the system and priority is given to the VINA channel. If a VINA supply is detected valid while VINB is conducting, the PMUX will automatically switch the conducting input from VINB to VINA. During this transition, a break–before–make operation is performed within 30 ms in order to avoid cross conduction between VINA and VINB and to ensure proper operation. A 500  $\Omega$ pulldown resistor on OUT is enabled for the entire duration of the break–before–make time. As the PMUX is able to turn on channel VINA or VINB, a FLAG pin indicates to the system the active path. When the VINB path is active, FLAG pin is high. As a consequence, if a valid voltage is present on the OUT pin and if FLAG is low, VINA is active.

Figure 5. Signal Timing in Autonomous Mode – Charging Example

#### Autonomous Mode – Locked

Autonomous locked mode is set when the CTRL pin is high. In this mode, the first valid input is active till this input becomes not valid. This feature can be used to lock the VINB channel in case of a weak battery for example.

#### **OTG Mode**

5 V is applied on the output of the device during OTG mode. This 5 V will pass through the VINA path when the OTG\_EN pin is driven high. When enabling the OTG mode,

the VINA output is powered from VOUT and is soft-started for 1 ms.

For VINB to supply the OTG accessory (connected on VINA) though OUT, both channels must be activated. This can be done by asserting the FLAG pin low. Usually used as an output, the FLAG pin is also sensed by the PMUX in autonomous mode. When VINB is valid, the FLAG pin open drain is open. Thus asserting the FLAG pin low will turn on the VINA path with VINB already active.

Figure 6. FLAG Functional Diagram

Figure 7. Signal Timing in Autonomous Mode – USB On The Go Example

### Autonomous Mode Functional Diagram

### **VINA Sense Output**

The IC features a protected VINA Sense to the processor. This output is 0V when the VINA voltage level is lower than  $V_{\rm UVLO}$  and higher than  $V_{\rm OVLO}$  and equal to VINA when the VINA voltage is within the operation range.

### **Input Voltage Protection**

The device can withstand a maximum of 28 V DC on VINA and 20 V DC on VINB. Embedded OVP thresholds

will disable both VINA and VINB when the voltage applied to VINA or VINB will exceed the OVLO thresholds. The response time of the overvoltage lock out is fast enough to prevent a voltage of maximum of 20 V at VOUT.

In compliance with IEC 61000–4–5, both 1.2/50  $\mu$ s and 10/700  $\mu$ s surge waveforms up to 100 V, the PMUX clamp input voltage surges on VINA to 28 V and hold off the voltage. During these surges, the voltage at VOUT will not exceed 20 V.

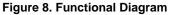

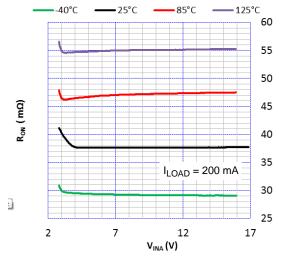

### **TYPICAL CHARACTERISTICS**

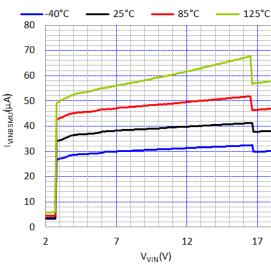

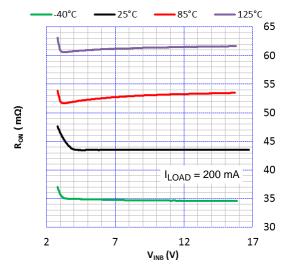

Figure 9. VINA ON Resistance vs. VINA

Figure 11. VINA ON Resistance vs. VINA

Figure 13. VINA ION vs VINA

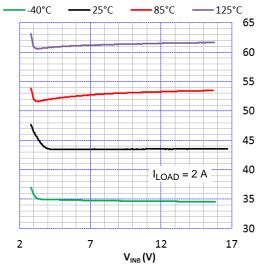

Figure 10. VINB ON Resistance vs. VINB

Figure 12. VINB ON Resistance versus VINB

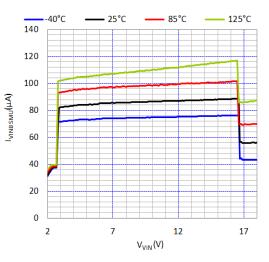

Figure 14. VINB ION vs VINB (including FLAG pull-up)

### **APPLICATION INFORMATION**

#### **Typical Application**

Figure 15. Autonomous Mode

Figure 16. Salve Mode

#### **ORDERING INFORMATION**

| Part Number   | Marking Diagram | Shipping <sup>†</sup> |

|---------------|-----------------|-----------------------|

| NCP3901FCCT1G | 3901            | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98AON91880F             | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WLCSP28, 3.1X1.65, 0.4P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

| ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                         |                                                                                                                                                                                     |             |  |  |

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Power Switch ICs - Power Distribution category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

TCK111G,LF(S\_FPF1018\_DS1222\_TCK2065G,LF\_SZNCP3712ASNT3G\_MIC2033-05BYMT-T5\_MIC2033-12AYMT-T5\_MIC2033-05BYM6-T5\_SLG5NT1437VTR\_SZNCP3712ASNT1G\_DML1008LDS-7\_KTS1670EDA-TR\_KTS1640QGDV-TR\_KTS1641QGDV-TR NCV459MNWTBG\_FPF2260ATMX\_U6513A\_MIC2012YM-TR\_NCP45780IMN24RTWG\_AP22953CW12-7\_MAX14919AUP+T MAX14919ATP+\_KTS1697AEOAB-TR\_TCK207AN,LF\_BD2227G-LBTR\_TCK126BG,LF\_XC8111AA010R-G\_MPQ5072GG-AEC1-P TCK128BG,LF\_XC8110AA018R-G\_XC8110AA010R-G\_XC8111AA018R-G\_MC33882PEP\_TPS2104DBVR\_MIC2098-1YMT-TR MIC94062YMT\_TR\_MP6231DN-LF\_MIC2015-1.2YM6\_TR\_MIC2075-2YM\_MIC94068YML-TR\_SIP32461DB-T2-GE1\_NCP335FCT2G TCK105G,LF(S\_AP2411S-13\_AP2151DSG-13\_AP2172MPG-13\_MIC94094YC6-TR\_MIC94093YC6-TR\_MIC94064YC6-TR MIC94061YMT-TR