# VR12.5 Compatible Synchronous Buck MOSFET Drivers

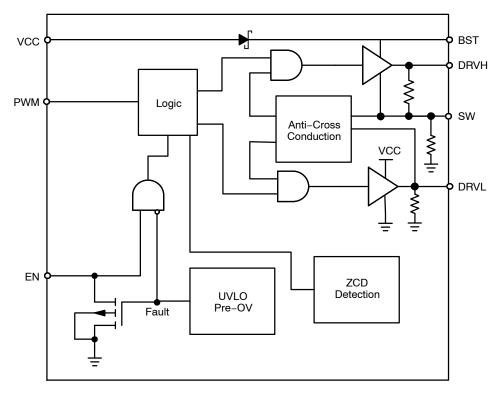

The NCP81161 is a high performance dual MOSFET gate driver optimized to drive the gates of both high-side and low-side power MOSFETs in a synchronous buck converter. It can drive up to 3 nF load with a 25 ns propagation delay and 20 ns transition time.

Adaptive anti-cross-conduction and power saving operation circuit can provide a low switching loss and high efficiency solution for notebook and desktop systems. Bidirectional EN pin can provide a fault signal to controller when the gate driver fault detect under OVP, UVLO occur. Also, an under-voltage lockout function guarantees the outputs are low when supply voltage is low.

#### **Features**

- Faster Rise and Fall Times

- Adaptive Anti-Cross-Conduction Circuit

- Integrated Bootstrap Diode

- Pre OV function

- ZCD Detect

- Floating Top Driver Accommodates Boost Voltages of up to 35 V

- Output Disable Control Turns Off Both MOSFETs

- Under-voltage Lockout

- Power Saving Operation Under Light Load Conditions

- Direct Interface to NCP6151 and Other Compatible PWM Controllers

- Thermally Enhanced Package

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

• Power Solutions for Desktop Systems

## ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAM**

1 O A4M=

A4 = Specific Device Code

M = Date Code

■ = Pb-Free Device

#### **ORDERING INFORMATION**

| Device        | Package           | Shipping <sup>†</sup> |

|---------------|-------------------|-----------------------|

| NCP81161MNTBG | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCP81161MNTWG | DFN8<br>(Pb-Free) | 3000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

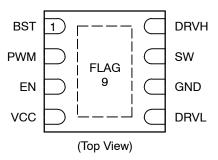

Figure 1. Pin Diagram

Figure 2. Block Diagram

**Table 1. Pin Descriptions**

| Pin No. | Symbol | Description                                                                                                                                          |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |        | 2000 Page 1                                                                                                                                          |

| 1       | BST    | Floating bootstrap supply pin for high side gate driver. Connect the bootstrap capacitor between this pin and the SW pin.                            |

| 2       | PWM    | Control input. The PWM signal has three distinctive states: Low = Low Side FET Enabled, Mid = Diode Emulation Enabled, High = High Side FET Enabled. |

| 3       | EN     | Logic input. A logic high to enable the part and a logic low to disable the part.                                                                    |

| 4       | VCC    | Power supply input. Connect a bypass capacitor (0.1 μF) from this pin to ground.                                                                     |

| 5       | DRVL   | Low side gate drive output. Connect to the gate of low side MOSFET.                                                                                  |

| 6       | GND    | Bias and reference ground. All signals are referenced to this node (QFN Flag).                                                                       |

| 7       | SW     | Switch node. Connect this pin to the source of the high side MOSFET and drain of the low side MOSFET.                                                |

| 8       | DRVH   | High side gate drive output. Connect to the gate of high side MOSFET.                                                                                |

| 9       | FLAG   | Thermal flag. There is no electrical connection to the IC. Connect to ground plane.                                                                  |

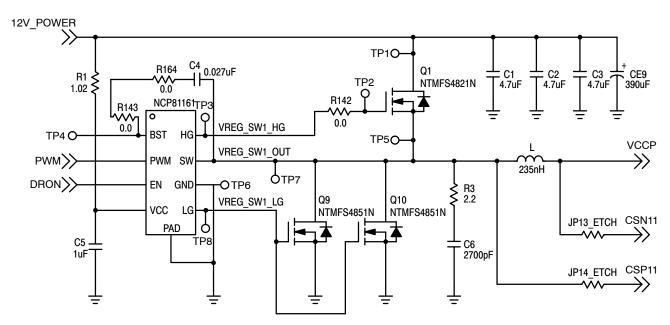

Figure 3. Application Circuit

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Pin Symbol | Pin Name                                    | V <sub>MAX</sub>                                       | V <sub>MIN</sub>                       |

|------------|---------------------------------------------|--------------------------------------------------------|----------------------------------------|

| VCC        | Main Supply Voltage Input                   | 15 V                                                   | -0.3 V                                 |

| BST        | Bootstrap Supply Voltage                    | 35 V wrt/ GND<br>40 V ≤ 50 ns wrt/ GND<br>15 V wrt/ SW | -0.3 V wrt/SW                          |

| SW         | Switching Node<br>(Bootstrap Supply Return) | 35 V<br>40 V ≤ 50 ns                                   | −5 V<br>−10 V (200 ns)                 |

| DRVH       | High Side Driver Output                     | BST+0.3 V                                              | -0.3 V wrt/SW<br>-2 V (<200 ns) wrt/SW |

| DRVL       | Low Side Driver Output                      | VCC+0.3 V                                              | −0.3 V DC<br>−5 V (<200 ns)            |

| PWM        | DRVH and DRVL Control Input                 | 6.5 V                                                  | -0.3 V                                 |

| EN         | Enable Pin                                  | 6.5 V                                                  | -0.3 V                                 |

| GND        | Ground                                      | 0 V                                                    | 0 V                                    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 3. THERMAL INFORMATION (All signals referenced to AGND unless noted otherwise)

| Symbol           | Parameter                                     | Value       | Unit |

|------------------|-----------------------------------------------|-------------|------|

| $R_{\theta JA}$  | Thermal Characteristic (Note 1)               | 74          | °C/W |

| TJ               | Operating Junction Temperature Range (Note 2) | 0 to 150    | °C   |

| T <sub>A</sub>   | Operating Ambient Temperature Range           | -10 to +125 | °C   |

| T <sub>STG</sub> | Maximum Storage Temperature Range             | −55 to +150 | °C   |

| MSL              | Moisture Sensitivity Level                    | 1           |      |

<sup>\*</sup> The maximum package power dissipation must be observed.

<sup>1.</sup> I in<sup>2</sup> Cu, 1 oz thickness.

<sup>2.</sup> Operation at -40°C to -10°C guaranteed by design, not production tested.

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL CHARACTERISTICS} & (Unless otherwise stated: $-10^{\circ}$C < $T_{A}$ < $+125^{\circ}$C; $4.5$ V < $V_{CC}$ < $13.2$ V, $4.5$ V < BST - SWN < $13.2$ V, $4.5$ V < BST < $30$ V, $0$ V < SWN < $21$ V) \\ \end{tabular}$

| Parameter                                            | Test Conditions                                                                          | Min. | Тур. | Max. | Units |

|------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|-------|

| SUPPLY VOLTAGE                                       |                                                                                          |      |      |      |       |

| VCC Operation Voltage                                |                                                                                          | 4.5  |      | 13.2 | V     |

| Power ON Reset Threshold                             |                                                                                          |      | 2.75 | 3.2  | V     |

| UNDERVOLTAGE LOCKOUT                                 |                                                                                          |      |      |      |       |

| VCC Start Threshold                                  |                                                                                          | 3.8  | 4.35 | 4.5  | V     |

| VCC UVLO Hysteresis                                  |                                                                                          | 150  | 200  | 250  | mV    |

| Output Overvoltage Trip Threshold at Startup         | Power Startup time, VCC > POR                                                            | 2.1  | 2.25 | 2.4  | V     |

| SUPPLY CURRENT                                       |                                                                                          |      |      |      |       |

| Normal Mode                                          | lcc + lbst, EN = 5 V, PWM = OSC, Fsw = 100 KHz,<br>Cload = 3 nF for DRVH, 3 nF for DRVL  |      | 10   |      | mA    |

| Standby Current                                      | Icc + Ibst, EN = GND                                                                     |      | 0.5  | 1.4  | mA    |

| Standby Current                                      | I <sub>CC</sub> + I <sub>BST</sub> , EN = HIGH, PWM = LOW,<br>No loading on DRVH & DRVL  |      | 2.0  |      | mA    |

| Standby Current                                      | I <sub>CC</sub> + I <sub>BST</sub> , EN = HIGH, PWM = HIGH,<br>No loading on DRVH & DRVL |      | 2.0  |      | mA    |

| BOOTSTRAP DIODE                                      |                                                                                          |      | •    |      |       |

| Forward Voltage                                      | V <sub>CC</sub> = 12 V, forward bias current = 2 mA                                      | 0.1  | 0.4  | 0.6  | V     |

| PWM INPUT                                            |                                                                                          |      |      |      |       |

| PWM Input High                                       |                                                                                          | 3.4  |      |      | V     |

| PWM Mid-State                                        |                                                                                          | 1.3  |      | 2.7  | V     |

| PWM Input Low                                        |                                                                                          |      |      | 0.7  | V     |

| ZCD Blanking Timer                                   |                                                                                          |      | 250  |      | ns    |

| HIGH SIDE DRIVER (VCC = 12 V)                        |                                                                                          |      |      |      |       |

| Output Impedance, Sourcing Current                   | VBST – VSW = 12 V                                                                        |      | 1.9  | 3.0  | Ω     |

| Output Impedance, Sinking Current                    | VBST – VSW = 12 V                                                                        |      | 1.0  | 1.7  | Ω     |

| DRVH Rise Time trdRVH                                | V <sub>VCC</sub> = 12 V, 3 nF load, VBST-VSW = 12 V                                      |      | 16   | 30   | ns    |

| DRVH Fall Time tfDRVH                                | V <sub>VCC</sub> = 12 V, 3 nF load, VBST-VSW = 12 V                                      |      | 11   | 25   | ns    |

| DRVH Turn-Off Propagation Delay tpdl <sub>DRVH</sub> | C <sub>LOAD</sub> = 3 nF                                                                 | 8.0  |      | 30   | ns    |

| DRVH Turn-On Propagation Delay tpdh <sub>DRVH</sub>  | C <sub>LOAD</sub> = 3 nF                                                                 |      |      | 30   | ns    |

| SW Pull Down Resistance                              | SW to PGND                                                                               |      | 45   |      | kΩ    |

| DRVH Pull Down Resistance                            | DRVH to SW, BST-SW = 0 V                                                                 |      | 45   |      | kΩ    |

| HIGH SIDE DRIVER (VCC = 5 V)                         |                                                                                          |      |      |      |       |

| Output Impedance, Sourcing Current                   | VBST – VSW = 5 V                                                                         |      | 2.5  |      | Ω     |

| Output Impedance, Sinking Current                    | VBST – VSW = 5 V                                                                         |      | 1.6  |      | Ω     |

| DRVH Rise Time tr <sub>DRVH</sub>                    | V <sub>VCC</sub> = 5 V, 3 nF load, VBST - VSW = 5 V                                      |      | 30   |      | ns    |

| DRVH Fall Time tf <sub>DRVH</sub>                    | V <sub>VCC</sub> = 5 V, 3 nF load, VBST – VSW = 5 V                                      |      | 27   |      | ns    |

| DRVH Turn-Off Propagation Delay tpdl <sub>DRVH</sub> | C <sub>LOAD</sub> = 3 nF                                                                 |      | 20   |      | ns    |

| DRVH Turn-On Propagation Delay tpdh <sub>DRVH</sub>  | C <sub>LOAD</sub> = 3 nF                                                                 |      | 27   |      | ns    |

| SW Pull Down Resistance                              | SW to PGND                                                                               |      | 45   |      | kΩ    |

$\begin{tabular}{ll} \textbf{Table 4. ELECTRICAL CHARACTERISTICS} & (Unless otherwise stated: $-10^{\circ}$C < $T_{A}$ < $+125^{\circ}$C; $4.5$ V < $V_{CC}$ < $13.2$ V, $4.5$ V < BST - SWN < $13.2$ V, $4.5$ V < BST < $30$ V, $0$ V < SWN < $21$ V) \\ \end{tabular}$

| Parameter                                            | Test Conditions                                                          | Min. | Тур. | Max. | Units |

|------------------------------------------------------|--------------------------------------------------------------------------|------|------|------|-------|

| HIGH SIDE DRIVER (VCC = 5 V)                         |                                                                          | J.   | -1   |      |       |

| DRVH Pull Down Resistance                            | DRVH to SW, BST-SW = 0 V                                                 |      | 45   |      | kΩ    |

| LOW SIDE DRIVER (VCC = 12 V)                         |                                                                          | •    |      | ı    |       |

| Output Impedance, Sourcing Current                   |                                                                          |      | 2.0  | 3.0  | Ω     |

| Output Impedance, Sinking Current                    |                                                                          |      | 0.7  | 1.5  | Ω     |

| DRVL Rise Time tr <sub>DRVL</sub>                    | C <sub>LOAD</sub> = 3 nF                                                 |      | 16   | 35   | ns    |

| DRVL Fall Time tf <sub>DRVL</sub>                    | C <sub>LOAD</sub> = 3 nF                                                 |      | 11   | 20   | ns    |

| DRVL Turn-Off Propagation Delay tpdl <sub>DRVL</sub> | C <sub>LOAD</sub> = 3 nF                                                 |      |      | 35   | ns    |

| DRVL Turn-On Propagation Delay tpdh <sub>DRVL</sub>  | C <sub>LOAD</sub> = 3 nF                                                 | 8.0  |      | 30   | ns    |

| DRVL Pull Down Resistance                            | DRVL to PGND, VCC = PGND                                                 |      | 45   |      | kΩ    |

| LOW SIDE DRIVER (VCC = 5 V)                          |                                                                          |      |      |      |       |

| Output Impedance, Sourcing Current                   |                                                                          |      | 2.5  |      | Ω     |

| Output Impedance, Sinking Current                    |                                                                          |      | 1.0  |      | Ω     |

| DRVL Rise Time tr <sub>DRVL</sub>                    | C <sub>LOAD</sub> = 3 nF                                                 |      | 30   |      | ns    |

| DRVL Fall Time tf <sub>DRVL</sub>                    | C <sub>LOAD</sub> = 3 nF                                                 |      | 22   |      | ns    |

| DRVL Turn-Off Propagation Delay tpdl <sub>DRVL</sub> | C <sub>LOAD</sub> = 3 nF                                                 |      | 27   |      | ns    |

| DRVL Turn-On Propagation Delay tpdh <sub>DRVL</sub>  | C <sub>LOAD</sub> = 3 nF                                                 |      | 12   |      | ns    |

| DRVL Pull Down Resistance                            | DRVL to PGND, VCC = PGND                                                 |      | 45   |      | kΩ    |

| EN INPUT                                             |                                                                          |      |      |      |       |

| Input Voltage High                                   |                                                                          | 2.0  |      |      | V     |

| Input Voltage Low                                    |                                                                          |      |      | 1.0  | V     |

| Hysteresis                                           |                                                                          |      | 500  |      | mV    |

| Normal Mode Bias Current                             |                                                                          | -1   |      | 1    | μΑ    |

| Enable Pin Sink Current                              |                                                                          | 4    |      | 30   | mA    |

| Propagation Delay Time                               |                                                                          |      | 20   | 40   | ns    |

| SW Node                                              |                                                                          |      |      |      |       |

| SW Node Leakage Current                              |                                                                          |      |      | 20   | μА    |

| Zero Cross Detection Threshold Voltage               | SW to -20 mV, ramp slowly until BG goes off (Start in DCM mode) (Note 3) |      | -6   |      | mV    |

## Table 5. DECODER TRUTH TABLE

| PWM INPUT | ZCD                                        | DRVL | DRVH |

|-----------|--------------------------------------------|------|------|

| PWM High  | ZCD Reset                                  | Low  |      |

| PWM Mid   | Positive current through the inductor High |      | Low  |

| PWM Mid   | Zero current through the inductor          | Low  | Low  |

| PWM Low   | ZCD Reset                                  | High | Low  |

<sup>3.</sup> Guaranteed by design; not production tested.

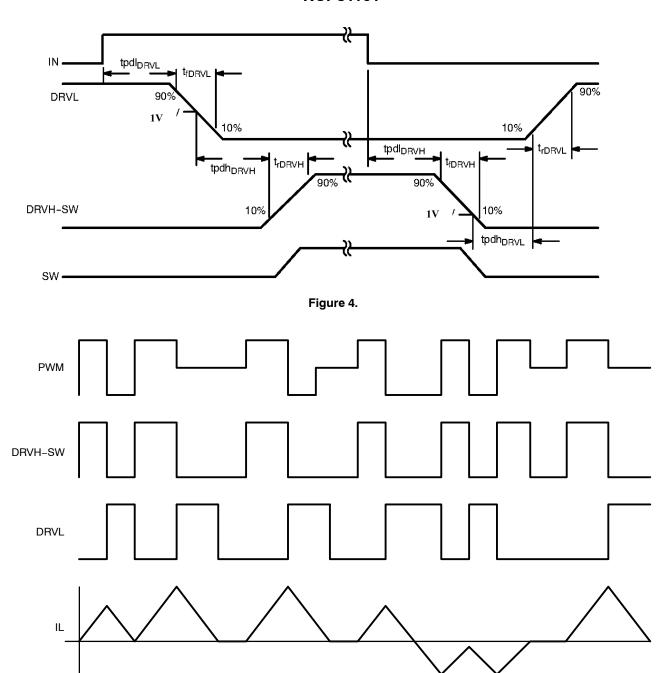

Figure 5. Timing Diagram

#### APPLICATIONS INFORMATION

The NCP81161 gate driver is a single phase MOSFET driver designed for driving N-channel MOSFETs in a synchronous buck converter topology. The NCP81161 is designed to work with ON Semiconductor's NCP6131 multi-phase controller. This gate driver is optimized for desktop applications.

## **Undervoltage Lockout**

The DRVH and DRVL are held low until VCC reaches 4.5 V during startup. The PWM signals will control the gate status when VCC threshold is exceeded. If VCC decreases to 250 mV below the threshold, the output gate will be forced low until input voltage VCC rises above the startup threshold.

#### Power-On Reset

Power-On Reset feature is used to protect a gate driver avoid abnormal status driving the startup condition. When the initial soft-start voltage is higher than 2.75 V, the gate driver will monitor the switching node SW pin. If SW pin high than 2.25 V, bottom gate will be force to high for discharge the output capacitor. The fault mode will be latch and EN pin will force to be low, unless the driver is recycle. When input voltage is higher than 4.5 V, and EN goes high, the gate driver will normal operation, top gate driver DRVH and bottom gate driver will follow the PWM signal decode to a status.

## Bi-directional EN Signal

Fault modes such as Power-On Reset and Undervoltage Lockout will de-assert the EN pin, which will pull down the DRON pin of controller as well. Thus the controller will be shut down consequently.

### **PWM Input and Zero Cross Detect (ZCD)**

The PWM input, along with EN and ZCD, control the state of DRVH and DRVL.

When PWM is set high, DRVH will be set high after the adaptive non-overlap delay. When PWM is set low, DRVL will be set high after the adaptive non-overlap delay.

When the PWM is set to the mid state, DRVH will be set low, and after the adaptive non-overlap delay, DRVL will be set high. DRVL remains high during the ZCD blanking time. When the timer is expired, the SW pin will be monitored for zero cross detection. After the detection, the DRVL will be set low.

## **Adaptive Nonoverlap**

The nonoverlap dead time control is used to avoid the shoot through damage the power MOSFETs. When the PWM signal pull high, DRVL will go low after a propagation delay, the controller will monitors the switching node (SWN) pin voltage and the gate voltage of the MOSFET to know the status of the MOSFET. When the low side MOSFET status is off an internal timer will delay

turn on of the high-side MOSFET. When the PWM pull low, gate DRVH will go low after the propagation delay (tpd DRVH).

The time to turn off the high side MOSFET is depending on the total gate charge of the high-side MOSFET. A timer will be triggered once the high side MOSFET is turn off to delay the turn on the low-side MOSFET.

#### **Low-Side Driver Timeout**

In normal operation, the DRVH signal tracks the PWM signal and turns off the Q1 high-side switch with a few 10 ns delay (t<sub>pdlDRVH</sub>) following the falling edge of the input signal. When Q1 is turned off, DRVL is allowed to go high, Q2 turns on, and the SW node voltage collapses to zero. But in a fault condition such as a high-side Q1 switch drain-source short circuit, the SW node cannot fall to zero, even when DRVH goes low. This driver has a timer circuit to address this scenario. Every time the PWM goes low, a DRVL on-time delay timer is triggered.

If the SW node voltage does not trigger a low-side turn-on, the DRVL on-time delay circuit does it instead, when it times out with t<sub>SW(TO)</sub> delay. If Q1 is still turned on, that is, its drain is shorted to the source, Q2 turns on and creates a direct short circuit across the VDCIN voltage rail. The crowbar action causes the fuse in the VDCIN current path to open. The opening of the fuse saves the load (CPU) from potential damage that the high-side switch short circuit could have caused.

#### **Layout Guidelines**

Layout for DC-DC converter is very important. The bootstrap and VCC bypass capacitors should be placed as close as to the driver IC.

Connect GND pin to local ground plane. The ground plane can provide a good return path for gate drives and reduce the ground noise. The thermal slug should be tied to the ground plane for good heat dissipation. To minimize the ground loop for low side MOSFET, the driver GND pin should be close to the low–side MOSFET source pin. The gate drive trace should be routed to minimize the length, the minimum width is 20 mils.

#### **Gate Driver Power Loss Calculation**

The gate driver power loss consists of the gate drive loss and quiescent power loss.

The equation below can be used to calculate the power dissipation of the gate driver. Where QGMF is the total gate charge for each main MOSFET and QGSF is the total gate charge for each synchronous MOSFET.

$$\mathsf{P}_{\mathsf{DRV}} = [\frac{\mathsf{f}_{\mathsf{SW}}}{2 \times \mathsf{n}} \times \left(\mathsf{n}_{\mathsf{MF}} \times \mathsf{Q}_{\mathsf{GMF}} + \mathsf{n}_{\mathsf{SF}} \times \mathsf{Q}_{\mathsf{GSF}}\right) + \mathsf{I}_{\mathsf{CC}}] \times \mathsf{V}_{\mathsf{CC}}$$

Also shown is the standby dissipation factor (ICC  $\cdot$  VCC) of the driver.

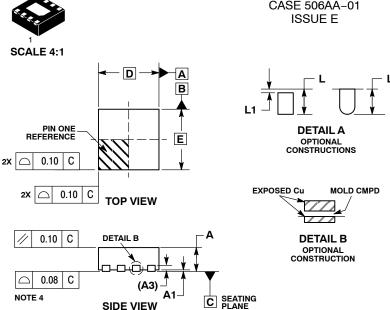

DETAIL A

е

- D2 →

**BOTTOM VIEW**

0.10 C

Ф

AB

0.05 C NOTE 3

**DATE 22 JAN 2010**

#### NOTES

- DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994 . CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN

- 0.15 AND 0.20 MM FROM TERMINAL TIP. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

| l   | MILLIMETERS |          |  |  |

|-----|-------------|----------|--|--|

|     | MILLIMETERS |          |  |  |

| DIM | MIN         | MAX      |  |  |

| Α   | 0.80        | 1.00     |  |  |

| A1  | 0.00        | 0.05     |  |  |

| A3  | 0.20        | REF      |  |  |

| b   | 0.20 0.30   |          |  |  |

| D   | 2.00        | 2.00 BSC |  |  |

| D2  | 1.10        | 1.30     |  |  |

| E   | 2.00        | BSC      |  |  |

| E2  | 0.70        | 0.90     |  |  |

| е   | 0.50 BSC    |          |  |  |

| K   | 0.30 REF    |          |  |  |

| L   | 0.25        | 0.35     |  |  |

| L1  | 0.10        |          |  |  |

## **GENERIC MARKING DIAGRAM\***

XX = Specific Device Code

= Date Code = Pb-Free Device

\*This information is generic. Please refer to device data sheet for actual part marking.

Pb-Free indicator, "G" or microdot " ■", may or may not be present.

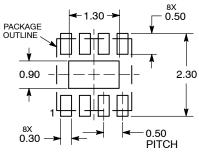

## **RECOMMENDED SOLDERING FOOTPRINT\***

**DIMENSIONS: MILLIMETERS**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON18658D                | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | DFN8, 2.0X2.0, 0.5MM PITCH |                                                                                                                                                                                    | PAGE 1 OF 1 |  |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

89076GBEST 00053P0231 56956 57.404.7355.5 LT4936 57.904.0755.0 5882900001 00600P0005 00-9050-LRPP 00-9090-RDPP

5951900000 01-1003W-10/32-15 0131700000 00-2240 LTP70N06 LVP640 5J0-1000LG-SIL LY1D-2-5S-AC120 LY2-US-AC240 LY3UA-DC24 00576P0020 00600P0010 LZN4-UA-DC12 LZNQ2M-US-DC5 LZNQ2-US-DC12 LZP40N10 00-8196-RDPP 00-8274-RDPP

00-8275-RDNP 00-8722-RDPP 00-8728-WHPP 00-8869-RDPP 00-9051-RDPP 00-9091-LRPP 00-9291-RDPP 0207100000 0207400000

01312 0134220000 60713816 M15730061 61161-90 61278-0020 6131-204-23149P 6131-205-17149P 6131-209-15149P 6131-218-17149P

6131-220-21149P 6131-260-2358P 6131-265-11149P