# LDO Linear Regulator -Micropower, DELAY, Adjustable RESET, Sense Output

# 5.0 V, 150 mA

The NCV4269C is a 5.0 V precision micropower voltage regulator with an output current capability of 150 mA.

The output voltage is accurate within  $\pm 2.0\%$  with a maximum dropout voltage of 0.5 V at 100 mA. Low quiescent current is a feature drawing only 125  $\mu$ A with a 1.0 mA load. This part is ideal for any and all battery operated microprocessor equipment.

Microprocessor control logic includes an active reset output RO with delay and a SI/SO monitor which can be used to provide an early warning signal to the microprocessor of a potential impending reset signal. The use of the SI/SO monitor allows the microprocessor to finish any signal processing before the reset shuts the microprocessor down.

The active Reset circuit operates correctly at an output voltage as low as 1.0 V. The Reset function is activated during the power up sequence or during normal operation if the output voltage drops outside the regulation limits.

The reset threshold voltage can be decreased by the connection of an external resistor divider to the  $R_{ADJ}$  lead. The regulator is protected against reverse battery, short circuit, and thermal overload conditions. The device can withstand load dump transients making it suitable for use in automotive environments. The device has also been optimized for EMC conditions.

#### Features

- 5.0 V ± 2.0% Output

- Low 125 µA Quiescent Current

- Active Reset Output Low Down to  $V_0 = 1.0 V$

- Adjustable Reset Threshold

- 150 mA Output Current Capability

- Fault Protection

- ◆ +60 V Peak Transient Voltage

- ♦ -40 V Reverse Voltage

- Short Circuit

- Thermal Overload

- Early Warning through SI/SO Leads

- Internally Fused Leads in SO-14 Package

- Integrated Pullup Resistor at Logic Outputs (To Use External Resistors, Select the NCV4279C)

- Very Low Dropout Voltage

- Electrical Parameters Guaranteed Over Entire Temperature Range

- AEC-Q100 Grade 1 Qualified and PPAP Capable

- These are Pb–Free Devices

# **ON Semiconductor®**

www.onsemi.com

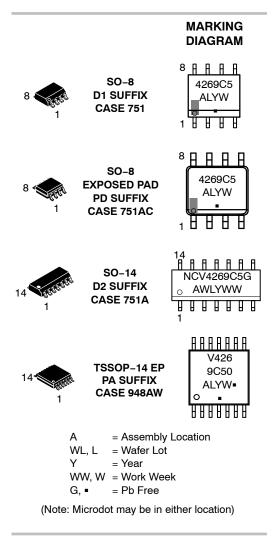

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

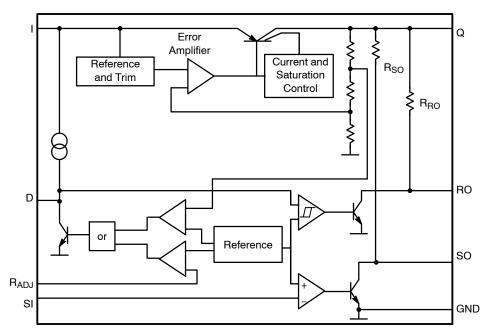

Figure 1. Block Diagram

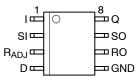

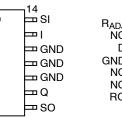

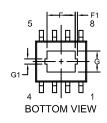

# PIN CONNECTIONS

SO-14

1

R<sub>ADJ</sub>

TSSOP-14 EP

#### PACKAGE PIN DESCRIPTION

| Package Pin Number |         | i                         |                       |                  |                                                                                                                                |

|--------------------|---------|---------------------------|-----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| SO-8               | SO-8 EP | SO-14                     | TSSOP14               | Pin<br>Symbol    | Function                                                                                                                       |

| 3                  | 3       | 1                         | 1                     | R <sub>ADJ</sub> | Reset Threshold Adjust; if not used to connect to GND.                                                                         |

| 4                  | 4       | 2                         | 3                     | D                | Reset Delay; To Set Time Delay, Connect to GND with Capacitor                                                                  |

| 5                  | 5       | 3, 4, 5, 6,<br>10, 11, 12 | 4                     | GND              | Ground                                                                                                                         |

| -                  | -       | -                         | 2, 5, 6, 9,<br>10, 12 | NC               | No connection to these pins from the IC.                                                                                       |

| 6                  | 6       | 7                         | 7                     | RO               | Reset Output; The Open–Collector Output has a 20 $k\Omega$ Pullup Resistor to Q. Leave Open if Not Used.                       |

| 7                  | 7       | 8                         | 8                     | SO               | Sense Output; This Open–Collector Output is Internally Pulled Up by 20 $k\Omega$ pullup resistor to Q. If not used, keep open. |

| 8                  | 8       | 9                         | 11                    | Q                | 5 V Output; Connect to GND with a 10 $\mu F$ Capacitor, ESR < 2.5 $\Omega.$                                                    |

| 1                  | 1       | 13                        | 13                    | I                | Input; Connect to GND Directly at the IC with Ceramic Capacitor.                                                               |

| 2                  | 2       | 14                        | 14                    | SI               | Sense Input; If not used, Connect to Q.                                                                                        |

| _                  | EPAD    | -                         | EPAD                  | EPAD             | Connect to ground potential or leave unconnected                                                                               |

#### **MAXIMUM RATINGS** ( $T_J = -40^{\circ}C$ to $150^{\circ}C$ )

| Parameter                                                             | Symbol                                 | Min                        | Max                      | Unit    |

|-----------------------------------------------------------------------|----------------------------------------|----------------------------|--------------------------|---------|

| Input to Regulator                                                    | V <sub>I</sub><br>II                   | -40<br>Internally Limited  | 45<br>Internally Limited | V       |

| Input Transient to Regulator (Note 3)                                 | VI                                     | -                          | 60                       | V       |

| Sense Input                                                           | V <sub>SI</sub><br>I <sub>SI</sub>     | -40<br>-1                  | 45<br>1                  | V<br>mA |

| Reset Threshold Adjust                                                | V <sub>RADJ</sub><br>I <sub>RADJ</sub> | -0.3<br>-10                | 7<br>10                  | V<br>mA |

| Reset Delay                                                           | V <sub>D</sub><br>I <sub>D</sub>       | -0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Ground                                                                | ۱ <sub>q</sub>                         | 50                         | -                        | mA      |

| Reset Output                                                          | V <sub>RO</sub><br>I <sub>RO</sub>     | -0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Sense Output                                                          | V <sub>SO</sub><br>I <sub>SO</sub>     | -0.3<br>Internally Limited | 7<br>Internally Limited  | V       |

| Regulated Output                                                      | V <sub>Q</sub><br>I <sub>Q</sub>       | -0.5<br>-10                | 7<br>-                   | V<br>mA |

| Junction Temperature<br>Storage Temperature                           | T <sub>J</sub><br>T <sub>STG</sub>     | _<br>_50                   | 150<br>150               | °C<br>℃ |

| Input Voltage Operating Range<br>Junction Temperature Operating Range | V <sub>I</sub><br>TJ                   | _<br>_40                   | 45<br>150                | ∨<br>°C |

#### LEAD TEMPERATURE SOLDERING AND MSL

| Parameter                                                | Symbol | Value |

|----------------------------------------------------------|--------|-------|

| MSL, 8-Lead, 14-Lead, LS Temperature 265°C Peak (Note 4) | MSL    | 1     |

| MSL, 8-Lead EP, LS Temperature 260°C                     | MSL    | 2     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. This device series incorporates ESD protection and exceeds the following ratings: Human Body Model (HBM) ≤ 4.0 kV per AEC-Q100-002. Machine Model (MM) ≤ 200 V per AEC-Q100-003.

2. Latchup tested per AEC-Q100-004.

- 3. Load Dump Test B (with centralized load dump suppression) according to ISO16750-2 standard. Guaranteed by design. Not tested in production. Passed Class A according to ISO16750–1.

+5°C/–0°C, 40 Sec Max–at–Peak, 60 – 150 Sec above 217°C.

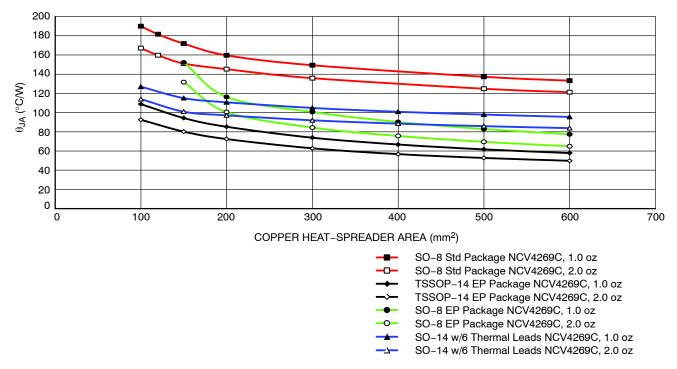

#### THERMAL CHARACTERISTICS

| Characteristic                                                          | Test Conditions (Typical Values) | Unit |

|-------------------------------------------------------------------------|----------------------------------|------|

| SO-8 Package (Note 5)                                                   |                                  |      |

| Junction–to–Pin 6 ( $\Psi$ – JL6, $\Psi$ <sub>L6</sub> )                | 58.3                             | °C/W |

| Junction-to-Ambient Thermal Resistance (R $_{\theta JA}, \theta_{JA}$ ) | 151.1                            | °C/W |

| SO-8 EP Package (Note 5)                                                |                                  |      |

| Junction–to–Pin 8 ( $\Psi$ – JL8, $\Psi$ <sub>L8</sub> )                | 47                               | °C/W |

| Junction-to-Ambient Thermal Resistance (R $_{\theta JA}, \theta_{JA}$ ) | 131.6                            | °C/W |

| Junction-to-Pad (Ψ - JPad)                                              | 16.3                             | °C/W |

| SO-14 Package (Note 5)                                                  |                                  |      |

| Junction–to–Pin 4 ( $\Psi$ – JL4, $\Psi$ <sub>L4</sub> )                | 19.5                             | °C/W |

| Junction-to-Ambient Thermal Resistance (R $_{\theta JA}, \theta_{JA}$ ) | 100.9                            | °C/W |

| TSSOP-14 EP Package (Note 5)                                            |                                  | -    |

| Junction–to–Pin 3 ( $\Psi$ – JL3, $\Psi$ <sub>L3</sub> )                | 19.3                             | °C/W |

#### THERMAL CHARACTERISTICS

| Characteristic                                                          | Test Conditions (Typical Values) | Unit |

|-------------------------------------------------------------------------|----------------------------------|------|

| TSSOP-14 EP Package (Note 5)                                            |                                  |      |

| Junction-to-Ambient Thermal Resistance (R $_{\theta JA}, \theta_{JA}$ ) | 77.3                             | °C/W |

| Junction-to-Pad (Ψ - JPad)                                              | 12.6                             | °C/W |

5. 2 oz copper, 150  $\rm mm^2$  copper area, 1.5 mm thick FR4

# **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = $-40^{\circ}C \le T_J \le 150^{\circ}C$ , V<sub>I</sub> = 13.5 V unless otherwise specified)

| Characteristic                         | Symbol               | Test Conditions                                                     | Min  | Тур  | Max  | Unit |

|----------------------------------------|----------------------|---------------------------------------------------------------------|------|------|------|------|

| REGULATOR                              |                      |                                                                     |      | •    | •    |      |

| Output Voltage                         | VQ                   | 1 mA $\leq$ $I_Q$ $\leq$ 100 mA 6 V $\leq$ V_I $\leq$ 16 V          | 4.90 | 5.00 | 5.10 | V    |

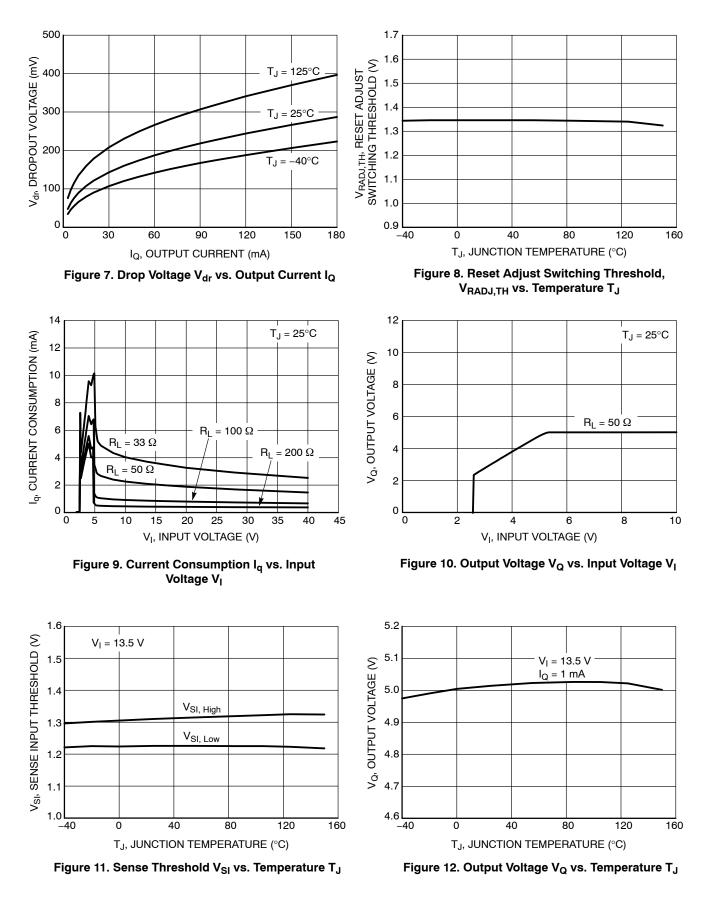

| Current Limit                          | l <sub>Q</sub>       | -                                                                   | 150  | 430  | 500  | mA   |

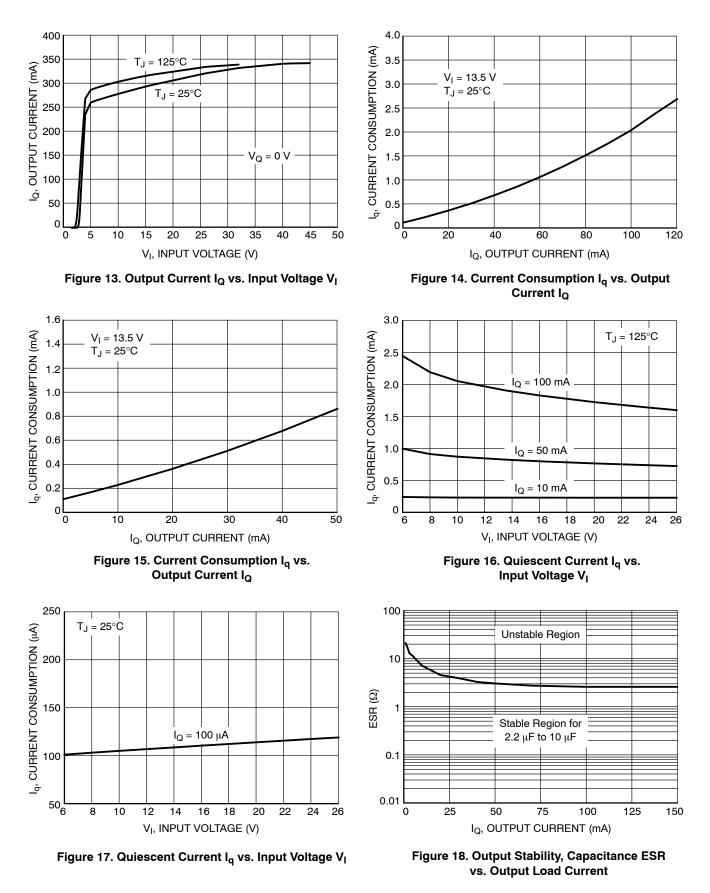

| Current Consumption; $I_q = I_I - I_Q$ | I <sub>q</sub>       | I <sub>Q</sub> = 1 mA, RO, SO High                                  | -    | 125  | 250  | μA   |

| Current Consumption; $I_q = I_I - I_Q$ | lq                   | l <sub>Q</sub> = 10 mA, RO, SO High                                 | -    | 230  | 450  | μA   |

| Current Consumption; $I_q = I_I - I_Q$ | Ιq                   | I <sub>Q</sub> = 50 mA, RO, SO High                                 | -    | 0.9  | 3.0  | mA   |

| Dropout Voltage                        | V <sub>dr</sub>      | V <sub>I</sub> = 5 V, I <sub>Q</sub> = 100 mA                       | -    | 0.23 | 0.5  | V    |

| Load Regulation                        | $\Delta V_Q$         | I <sub>Q</sub> = 5 mA to 100 mA                                     | -    | 1    | 20   | mV   |

| Line Regulation                        | $\Delta V_Q$         | $V_I = 6 V \text{ to } 26 V I_Q = 1 \text{ mA}$                     | -    | 1    | 30   | mV   |

| RESET GENERATOR                        |                      |                                                                     |      |      |      |      |

| Reset Switching Threshold              | V <sub>RT</sub>      | -                                                                   | 4.50 | 4.65 | 4.80 | V    |

| Reset Adjust Switching Threshold       | V <sub>RADJ,TH</sub> | V <sub>Q</sub> > 3.5 V                                              | 1.26 | 1.35 | 1.44 | V    |

| Reset Pullup Resistance                | R <sub>RO,INT</sub>  | -                                                                   | 10   | 20   | 40   | kΩ   |

| Reset Output Saturation Voltage        | V <sub>RO,SAT</sub>  | V <sub>Q</sub> < V <sub>RT</sub> , R <sub>RO, INT</sub>             | -    | 0.03 | 0.4  | V    |

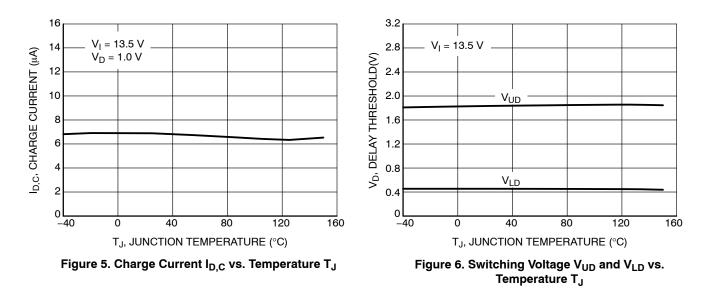

| Upper Delay Switching Threshold        | V <sub>UD</sub>      | -                                                                   | 1.4  | 1.8  | 2.2  | V    |

| Lower Delay Switching Threshold        | $V_{LD}$             | -                                                                   | 0.3  | 0.45 | 0.60 | V    |

| Saturation Voltage on Delay Capacitor  | V <sub>D,SAT</sub>   | V <sub>Q</sub> < V <sub>RT</sub>                                    | -    | -    | 0.1  | V    |

| Charge Current                         | I <sub>D,C</sub>     | V <sub>D</sub> = 1 V                                                | 3.0  | 6.5  | 9.5  | μA   |

| Delay Time L $\rightarrow$ H           | t <sub>d</sub>       | C <sub>D</sub> = 100 nF                                             | 17   | 28   | 73   | ms   |

| Delay Time H → L                       | t <sub>RR</sub>      | C <sub>D</sub> = 100 nF                                             | I    | 1.5  | -    | μs   |

| INPUT VOLTAGE SENSE                    |                      |                                                                     |      |      |      |      |

| Sense Threshold High                   | V <sub>SI,High</sub> | -                                                                   | 1.24 | 1.31 | 1.38 | V    |

| Sense Threshold Low                    | V <sub>SI,Low</sub>  | -                                                                   | 1.16 | 1.20 | 1.28 | V    |

| Sense Output Saturation Voltage        | V <sub>SO,Low</sub>  | V <sub>SI</sub> < 1.20 V; V <sub>Q</sub> > 3 V; R <sub>SO,INT</sub> | -    | 0.03 | 0.4  | V    |

| Sense Resistor Pullup                  | R <sub>SO,INT</sub>  | -                                                                   | 10   | 20   | 40   | kΩ   |

| Sense Input Current                    | I <sub>SI</sub>      | -                                                                   | -1.0 | 0.1  | 1.0  | μA   |

| THERMAL SHUTDOWN                       |                      |                                                                     |      |      |      |      |

|                                        | _                    |                                                                     |      | 1    |      |      |

Thermal Shutdown Temperature (Note 6) 150 200  $\mathsf{T}_{\mathsf{SD}}$ lout = 1 mA °C

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.6. Values based on design and/or characterization.

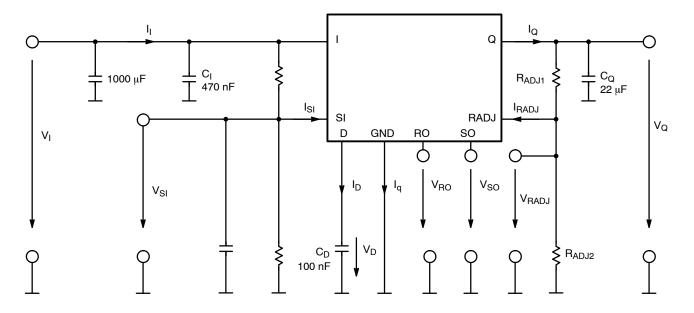

Figure 2. Measuring Circuit

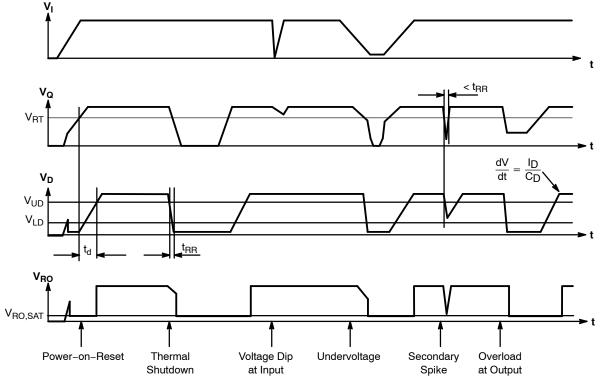

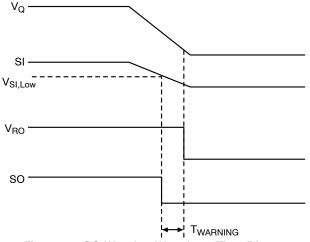

Figure 3. Reset Timing Diagram

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

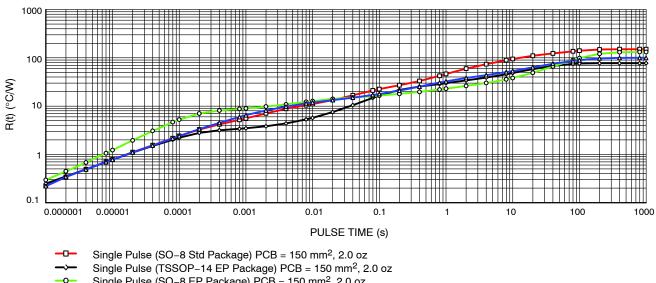

#### **TYPICAL THERMAL CHARACTERISTICS**

Figure 19. Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) vs. Heat Spreader Area

Single Pulse (SO-8 EP Package) PCB = 150 mm<sup>2</sup>, 2.0 oz

Single Pulse (SO-14 w/6 TL Package) PCB = 150 mm<sup>2</sup>, 2.0 oz 7

Figure 20. R(t) vs. Pulse Time

#### APPLICATION DESCRIPTION

#### **OUTPUT REGULATOR**

The output is controlled by a precision trimmed reference. The PNP output has base drive quiescent current control for regulation while the input voltage is low, preventing over saturation. Current limit and voltage monitors complement the regulator design to give safe operating signals to the processor and control circuits.

#### **RESET OUTPUT (RO)**

A reset signal, Reset Output, RO, (low voltage) is generated as the IC powers up. After the output voltage  $V_Q$  increases above the reset threshold voltage  $V_{RT}$ , the delay timer D is started. When the voltage on the delay timer  $V_D$  passes  $V_{UD}$ , the reset signal RO goes high. A discharge of the delay timer  $V_D$  is started when  $V_Q$  drops and stays below the reset threshold voltage  $V_{RT}$ . When the voltage of the delay timer  $V_D$  drops below the lower threshold voltage  $V_{LD}$  the reset output voltage  $V_{RO}$  is brought low to reset the processor.

The reset output RO is an open collector NPN transistor with an internal 20 k $\Omega$  pullup resistor connected to the output Q, controlled by a low voltage detection circuit. The circuit is functionally independent of the rest of the IC, thereby guaranteeing that RO is valid for V<sub>Q</sub> as low as 1.0 V.

#### RESET ADJUST (R<sub>ADJ</sub>)

The reset threshold  $V_{RT}$  can be decreased from a typical value of 4.65 V to as low as 3.5 V by using an external voltage divider connected from the Q lead to the pin  $R_{ADJ}$ , as shown in Figure 21. The resistor divider keeps the voltage above the  $V_{RADJ,TH}$  (typical 1.35 V) for the desired input voltages, and overrides the internal threshold detector. Adjust the voltage divider according to the following relationship:

```

V_{RT} = V_{RADJ,TH} \cdot (R_{ADJ1} + R_{ADJ2}) / R_{ADJ2} (eq. 1)

```

If the reset adjust option is not needed, the  $R_{ADJ}$  pin should be connected to GND causing the reset threshold to go to its default value (typically 4.65 V).

#### **RESET DELAY (D)**

The reset delay circuit provides a delay (programmable by capacitor  $C_D$ ) on the reset output lead RO. The delay lead D provides charge current  $I_{D,C}$  (typically 6.5  $\mu$ A) to the external delay capacitor  $C_D$  during the following times:

- 1. During Powerup (once the regulation threshold has been exceeded).

- 2. After a reset event has occurred and the device is back in regulation. The delay capacitor is set to discharge when the regulation ( $V_{RT}$ , reset threshold voltage) has been violated. When the delay capacitor discharges to  $V_{LD}$ , the reset signal RO pulls low.

#### SETTING THE DELAY TIME

The delay time is set by the delay capacitor  $C_D$  and the charge current  $I_D$ . The time is measured by the delay capacitor voltage charging from the low level of  $V_{DSAT}$  to the higher level  $V_{UD}$ . The time delay follows the equation:

$$t_d = [C_D (V_{UD} - V_{D, SAT})]/I_{D, C}$$

(eq. 2)

Example:

Using  $C_D = 100 \text{ nF}$ .

Use the typical value for  $V_{D,SAT} = 0.1$  V.

Use the typical value for  $V_{UD} = 1.8$  V.

Use the typical value for Delay Charge Current  $I_D = 6.5 \,\mu$ A.

$t_d = [100 \text{ nF}(1.8 - 0.1 \text{ V})]/6.5 \,\mu\text{A} = 26.2 \text{ ms}$  (eq. 3)

\*\* C<sub>Q</sub> – minimum cap required for stability is 2.2 μF while higher over/under-shoots may be expected. Cap must operate at minimum temperature expected.

Figure 21. Application Diagram

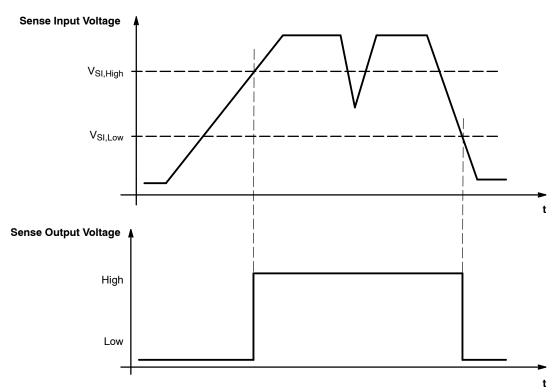

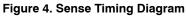

# SENSE INPUT (SI) / SENSE OUTPUT (SO) VOLTAGE MONITOR

An on-chip comparator is available to provide early warning to the microprocessor of a possible reset signal (Figure 4). The output is from an open collector driver with an internal 20 k $\Omega$  pull up resistor to output Q. The reset signal typically turns the microprocessor off instantaneously. This can cause unpredictable results with the microprocessor. The signal received from the SO pin will allow the microprocessor time to complete its present task before shutting down. This function is performed by a comparator referenced to the band gap voltage. The actual trip point can be programmed externally using a resistor divider to the input monitor SI (Figure 21). The values for R<sub>SI1</sub> and R<sub>SI2</sub> are selected for a typical threshold of 1.20 V on the SI Pin.

#### SIGNAL OUTPUT

Figure 22 shows the SO Monitor timing waveforms as a result of the circuit depicted in Figure 21. As the output voltage ( $V_Q$ ) falls, the monitor threshold ( $V_{SI,Low}$ ), is crossed. This causes the voltage on the SO output to go low sending a warning signal to the microprocessor that a reset signal may occur in a short period of time.  $T_{WARNING}$  is the time the microprocessor has to complete the function it is currently working on and get ready for the reset shutdown signal. When the voltage on the SO goes low and the RO stays high the current consumption is typically 530  $\mu$ A at 1 mA load current.

Figure 22. SO Warning Waveform Time Diagram

#### STABILITY CONSIDERATIONS

The input capacitor  $C_I$  in Figure 21 is necessary for compensating input line reactance. Possible oscillations caused by input inductance and input capacitance can be damped by using a resistor of approximately  $1.0 \Omega$  in series with  $C_I$ .

The output or compensation capacitor helps determine three main characteristics of a linear regulator: startup delay, load transient response and loop stability.

The capacitor value and type should be based on cost, availability, size and temperature constraints. The aluminum electrolytic capacitor is the least expensive solution, but, if the circuit operates at low temperatures  $(-25^{\circ}C \text{ to } -40^{\circ}C)$ , both the value and ESR of the capacitor will vary considerably. The capacitor manufacturer's data sheet usually provides this information.

The 10  $\mu$ F output capacitor C<sub>Q</sub> shown in Figure 21 should work for most applications; however, it is not necessarily the optimized solution. Stability is guaranteed at C<sub>Q</sub> is min 2.2  $\mu$ F and max ESR is 2.5  $\Omega$ . There is no min ESR limit which was proved with MURATA's ceramic caps GRM31MR71A225KA01 (2.2  $\mu$ F, 10 V, X7R, 1206) and GRM31CR71A106KA01 (10  $\mu$ F, 10 V, X7R, 1206) directly soldered between output and ground pins.

# CALCULATING POWER DISSIPATION IN A SINGLE OUTPUT LINEAR REGULATOR

The maximum power dissipation for a single output regulator (Figure 21) is:

PD(max) = [VI(max) - VQ(min)]IQ(max) + VI(max)Iq (eq. 4)where:

V<sub>I(max)</sub> is the maximum input voltage,

V<sub>Q(min)</sub> is the minimum output voltage,

$I_{Q(max)}$  is the maximum output current for the application, and  $I_q$  is the quiescent current the regulator consumes at  $I_{Q(max)}$ .

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R_{0JA}$  can be calculated:

$$R_{\theta JA} = (150^{\circ}C - T_A) / P_D$$

(eq. 5)

The value of  $R_{\theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C. In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required. The current flow and voltages are shown in the Measurement Circuit Diagram.

#### HEATSINKS

A heatsink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\text{HA}}$ :

$$R_{\theta}JA = R_{\theta}JC + R_{\theta}CS + R_{\theta}SA \qquad (eq. 6)$$

where:

$R_{\theta JC}$  = the junction-to-case thermal resistance,

$R_{\theta CS}$  = the case-to-heat sink thermal resistance, and  $R_{\theta SA}$  = the heat sink-to-ambient thermal resistance.

$R_{\theta JC}$  appears in the package section of the data sheet. Like  $R_{\theta JA}$ , it too is a function of package type.  $R_{\theta CS}$  and  $R_{\theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in data sheets of heatsink manufacturers. Thermal, mounting, and heatsinking considerations are discussed in the ON Semiconductor application note AN1040/D, available on the ON Semiconductor website.

#### **ORDERING INFORMATION**

| Device          | Output Voltage | Package               | Shipping <sup>†</sup> |

|-----------------|----------------|-----------------------|-----------------------|

| NCV4269CD150R2G |                | SO-8<br>(Pb-Free)     | 2500 / Tape & Reel    |

| NCV4269CPD50R2G | 5.0)/          | SO-8 EP<br>(Pb-Free)  | 2500 / Tape & Reel    |

| NCV4269CD250R2G | 5.0 V          | SO-14<br>(Pb-Free)    | 2500 / Tape & Reel    |

| NCV4269CPA50R2G |                | TSSOP-14<br>(Pb-Free) | 2500 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

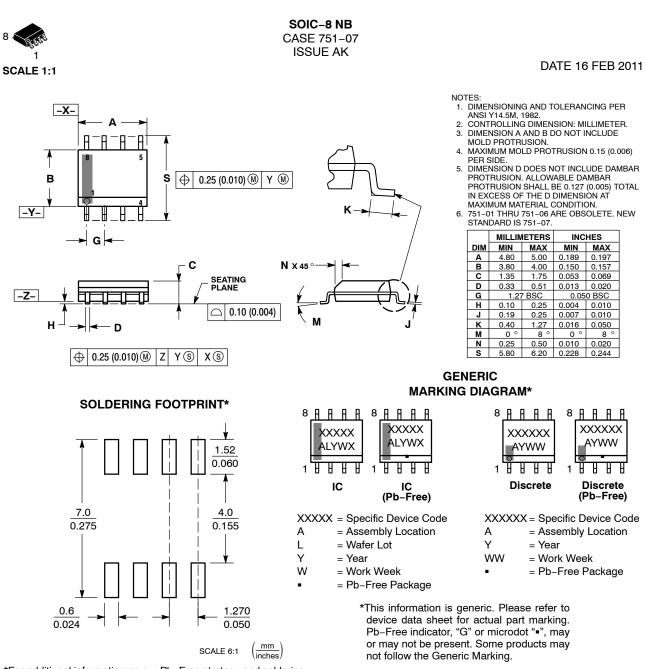

### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                  | 98ASB42564B                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Reposition<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                            |                                                       |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| DESCRIPTION: SOIC-8 NB                                                            |                                                                                             | PAGE 1 OF 2                                                                                                                                                                                                                                                                                                   |                                                       |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product on<br>acidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER EMITTER 5. BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: CATHODE 1 PIN 1. 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: PIN 1. GROUND BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC COMMON CATHODE/VCC 3 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 COMMON ANODE/GND 8. STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. 4. DRAIN, #2 GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 DRAIN 1 7. 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. SOURCE SOURCE 6. SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: ANODE ANODE PIN 1. 2. ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 3. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. 4. GATE 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER:                                                                  | 98ASB42564B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION: SOIC-8 NB PAGE 2                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE 2 OF 2                                                                                                                                                                        |  |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor and liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                                                                                                                                                                                    |  |  |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

7.

8

rights of others

COLLECTOR, #1

COLLECTOR, #1

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **STYLES ON PAGE 2**

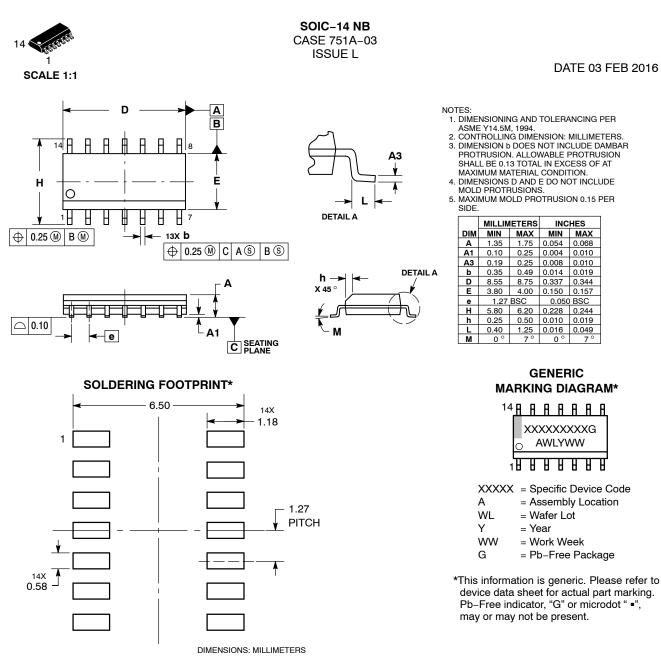

| DOCUMENT NUMBER:                                                                  | 98ASB42565B                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Reposite<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                             |                                                        |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|

| DESCRIPTION: SOIC-14 NB PAGE                                                      |                                                                                             | PAGE 1 OF 2                                                                                                                                                                                                                                                                                                  |                                                        |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product o<br>ncidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>or circuit, and specifically |  |  |

#### SOIC-14 CASE 751A-03 ISSUE L

#### DATE 03 FEB 2016

| STYLE 1:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. NO CONNECTION<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE | STYLE 2:<br>CANCELLED                                                                                                                                                                                   | STYLE 3:<br>PIN 1. NO CONNECTION<br>2. ANODE<br>3. ANODE<br>4. NO CONNECTION<br>5. ANODE<br>6. NO CONNECTION<br>7. ANODE<br>8. ANODE<br>9. ANODE<br>10. NO CONNECTION<br>11. ANODE<br>12. ANODE<br>13. NO CONNECTION<br>14. COMMON CATHODE                                            | STYLE 4:<br>PIN 1. NO CONNECTION<br>2. CATHODE<br>3. CATHODE<br>4. NO CONNECTION<br>5. CATHODE<br>6. NO CONNECTION<br>7. CATHODE<br>8. CATHODE<br>10. NO CONNECTION<br>11. CATHODE<br>12. CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. COMMON ANODE<br>8. COMMON CATHODE<br>10. ANODE/CATHODE<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                     | STYLE 6:<br>PIN 1. CATHODE<br>2. CATHODE<br>3. CATHODE<br>4. CATHODE<br>5. CATHODE<br>6. CATHODE<br>7. CATHODE<br>8. ANODE<br>9. ANODE<br>10. ANODE<br>11. ANODE<br>12. ANODE<br>13. ANODE<br>14. ANODE | STYLE 7:<br>PIN 1. ANODE/CATHODE<br>2. COMMON ANODE<br>3. COMMON CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. COMMON CATHODE<br>12. COMMON ANODE<br>13. ANODE/CATHODE<br>14. ANODE/CATHODE | STYLE 8:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>7. COMMON ANODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. NO CONNECTION<br>12. ANODE/CATHODE<br>13. ANODE/CATHODE<br>14. COMMON CATHODE |

| DOCUMENT NUMBER:                                                                                                                                                       | Electronic versions are uncontrolled except when accessed directly from the Document Re<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                           | SOIC-14 NB                                                                                                                                                                 |  | PAGE 2 OF 2 |  |  |  |

| ON Semiconductor and M are trademarks of Semiconductor Components Industries 11 C dba ON Semiconductor or its subsidiaries in the United States and/or other countries |                                                                                                                                                                            |  |             |  |  |  |

ON Semiconductor and united states and/or other countries. LC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

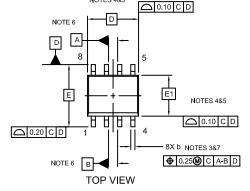

DATE 02 APR 2019

NOTES:

SOIC-8 EP CASE 751AC ISSUE D

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS

- CONTROLLING DIMENSION: MILLIMETERS

DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION & DOES NOT INCLUDE MANBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.004 IN EXCESS OF MAXIMUM MATERIAL CONDITION.

DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.006 PER SIDE. DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.010 mm PER SIDE.

THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM. DIMENSIONS D AND E1 ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY AT DATUM H.

DATUME A AND BAE TO BE TO DE DETERMINED AT DATUM H.

- 6. DATUMS A AND B ARE TO BE DETERMINED AT DATUM H.

- DIMENSIONS 5 AND C APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 TO 0.25 FROM THE LEAD TIP.

A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

NOTES 4&5

45° CHAMFER

DETAIL A NOTE 7 · c

END VIEW

|     | MILLIMETERS |      |      |

|-----|-------------|------|------|

| DIM | MIN.        | NOM  | MAX. |

| А   | 1.35        | 1.55 | 1.75 |

| A1  | 1           | 0.05 | 0.10 |

| A2  | 1.35        | 1.50 | 1.65 |

| b   | 0.31        | 0.41 | 0.51 |

| с   | 0.17        | 0.21 | 0.23 |

| D   | 4.90 BSC    |      |      |

| E   | 6.00 BSC    |      |      |

| E1  | 3.90 BSC    |      |      |

| е   | 1.27 BSC    |      |      |

| F   | 2.24        | 2.72 | 3.20 |

| F1  | 0.15        | 0.20 | 0.25 |

| G   | 1.55        | 2.03 | 2.51 |

| G1  | 0.41        | 0.46 | 0.51 |

| h   | 0.25        | 0.38 | 0.50 |

| L   | 0.40        | 0.84 | 1.27 |

| L1  | 1.04 REF    |      |      |

| L2  | 0.25 REF    |      |      |

| Ø   | 0°          | 4°   | 8°   |

**MOUNTING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D."

### GENERIC **MARKING DIAGRAM\***

AAB XXXXX AYWW=

| XXXXXX | = Specific Device Code |

|--------|------------------------|

| Α      | = Assembly Location    |

| Υ      | = Year                 |

| WW     | = Work Week            |

| •      | = Pb-Free Package      |

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " -", may or may not be present and may be in either location. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON14029D | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8 EP   |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and unarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

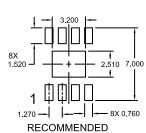

14X

0.42

DIMENSIONS: MILLIMETERS

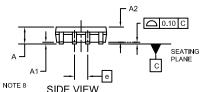

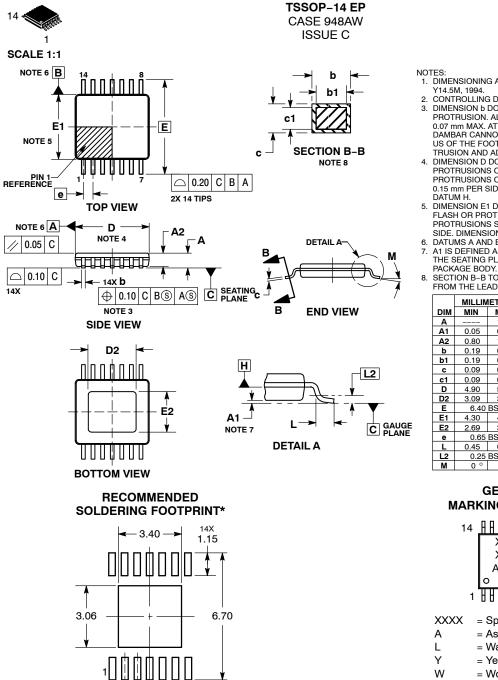

98AON66474E

TSSOP-14 EP, 5.0X4.4

ON Semiconductor and unarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

**ON Semiconductor**

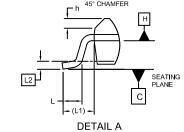

DATE 09 OCT 2012

- DIMENSIONING AND TOLERANCING PER ASME

- Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.07 mm MAX. AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADI-US OF THE FOOT. MINIMUM SPACE BETWEEN PRO-TRUSION AND ADJACENT LEAD IS 0.07.

- DIMENSION ADJOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 mm PER SIDE. DIMENSION D IS DETERMINED AT DATUM H.

- DATOM H.

DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.25 mm PER SIDE. DIMENSION E1 IS DETERMINED AT DATUM H.

- DATUMS A AND B ARE DETERMINED AT DATUM H. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE

- SECTION B-B TO BE DETERMINED AT 0.10 TO 0.25 mm FROM THE LEAD TIP.

|     | = ==        |      |  |

|-----|-------------|------|--|

|     | MILLIMETERS |      |  |

| DIM | MIN         | MAX  |  |

| Α   |             | 1.20 |  |

| A1  | 0.05        | 0.15 |  |

| A2  | 0.80        | 1.05 |  |

| b   | 0.19        | 0.30 |  |

| b1  | 0.19        | 0.25 |  |

| С   | 0.09        | 0.20 |  |

| c1  | 0.09        | 0.16 |  |

| D   | 4.90        | 5.10 |  |

| D2  | 3.09        | 3.62 |  |

| Е   | 6.40 BSC    |      |  |

| E1  | 4.30        | 4.50 |  |

| E2  | 2.69        | 3.22 |  |

| е   | 0.65 BSC    |      |  |

| L   | 0.45        | 0.75 |  |

| L2  | 0.25 BSC    |      |  |

| М   | 0 °         | 8°   |  |

#### GENERIC **MARKING DIAGRAM\***

| 14 | AAAAAA<br>xxxx<br>xxxx<br>Alyw• |

|----|---------------------------------|

| 4  | ○ •<br>                         |

|    |                                 |

|    | = Specific Device Code          |

|    | Assembly Location               |

| -  | = Wafer Lot                     |

| -  | = Year                          |

| :  | = Work Week                     |

|    |                                 |

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " .", may or may not be present.

Electronic versions are uncontrolled except when accessed directly from the Document Repository.

Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

DESCRIPTION:

0.65

PITCH

DOCUMENT NUMBER:

rights of others

PAGE 1 OF 1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

AP7363-SP-13 L79M05TL-E PT7M8202B12TA5EX TCR3DF185,LM(CT TCR3DF24,LM(CT TCR3DF285,LM(CT TCR3DF31,LM(CT TCR3DF31,LM(CT TCR3DF45,LM(CT MP2013GQ-33-Z 059985X NCP4687DH15T1G 701326R TCR2EN28,LF(S NCV8170AXV250T2G TCR3DF27,LM(CT TCR3DF19,LM(CT TCR3DF125,LM(CT TCR2EN18,LF(S AP2112R5A-3.3TRG1 AP7315-25W5-7 IFX30081LDVGRNXUMA1 NCV47411PAAJR2G AP2113KTR-G1 AP2111H-1.2TRG1 ZLD01117QK50TC AZ1117IH-1.8TRG1 AZ1117ID-ADJTRG1 TCR3DG12,LF MIC5514-3.3YMT-T5 MIC5512-1.2YMT-T5 MIC5317-2.8YM5-T5 SCD7912BTG NCP154MX180270TAG SCD33269T-5.0G NCV8170BMX330TCG NCV8170AMX120TCG NCP706ABMX300TAG NCP153MX330180TCG NCP114BMX075TCG MC33269T-3.5G CAT6243-ADJCMT5T TCR3DG33,LF AP2127N-1.0TRG1 TCR4DG35,LF LT1117CST-3.3 LT1117CST-5 TAR5S15U(TE85L,F) TAR5S18U(TE85L,F) TCR3UG19A,LF TCR4DG105,LF