# Isolated High Current IGBT Gate Driver

## NCV57001

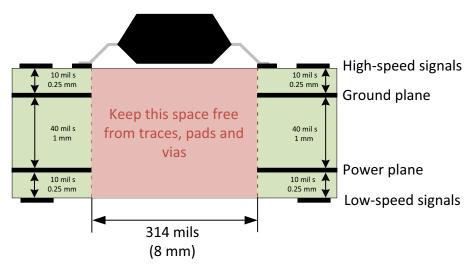

NCV57001 is a high-current single channel IGBT driver with internal galvanic isolation, designed for high system efficiency and reliability in high power applications. Its features include complementary inputs, open drain FAULT and Ready outputs, active Miller clamp, accurate UVLOs, DESAT protection, and soft turn-off at DESAT. NCV57001 accommodates both 5 V and 3.3 V signals on the input side and wide bias voltage range on the driver side including negative voltage capability. NCV57001 provides > 5 kVrms (UL1577 rating) galvanic isolation and > 1200  $V_{\rm IORM}$  (working voltage) capabilities. NCV57001 is available in the wide-body SOIC-16 package with guaranteed 8 mm creepage distance between input and output to fulfill reinforced safety insulation requirements.

#### **Features**

- High Current Output (+4/-6 A) at IGBT Miller Plateau Voltages

- Low Output Impedance for Enhanced IGBT Driving

- Short Propagation Delays with Accurate Matching

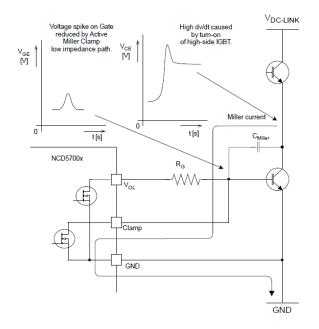

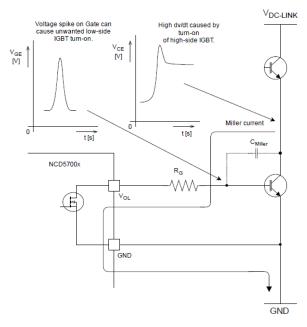

- Active Miller Clamp to Prevent Spurious Gate Turn-on

- DESAT Protection with Programmable Delay

- Negative Voltage (Down to -9 V) Capability for DESAT

- Soft Turn Off During IGBT Short Circuit

- IGBT Gate Clamping During Short Circuit

- IGBT Gate Active Pull Down

- Tight UVLO Thresholds for Bias Flexibility

- Wide Bias Voltage Range including Negative VEE2

- 3.3 V to 5 V Input Supply Voltage

- Designed for AEC-Q100 Certification

- 5000 V Galvanic Isolation (to meet UL1577 Requirements)

- 1200 V Working Voltage (per VDE0884–10 Requirements)

- High Transient Immunity

- High Electromagnetic Immunity

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant

#### **Typical Applications**

- Automotive Power Supplies

- HEV/EV Powertrain

- OBC

- BSG

- EV Charger

- PTC Heater

#### MARKING DIAGRAM

XXXXX = Specific Device Code A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

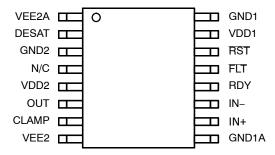

#### **PIN ASSIGNMENT**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 8 of this data sheet.

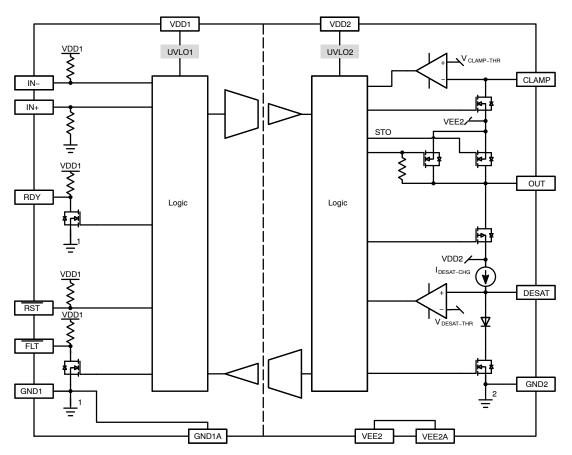

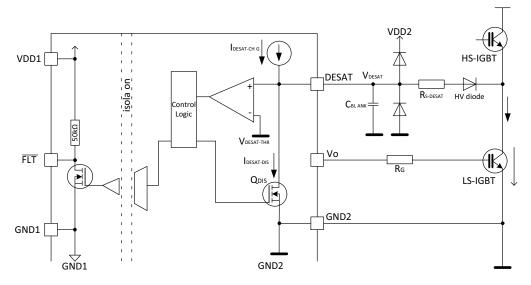

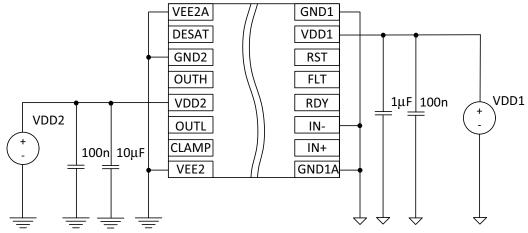

Figure 1. Simplified Block Diagram

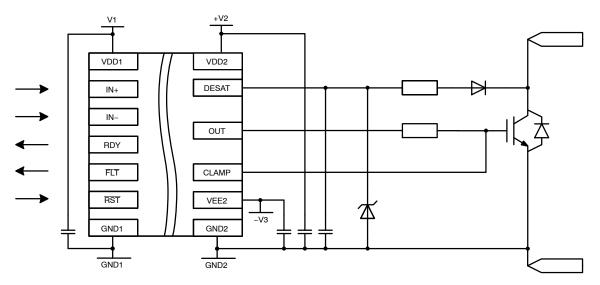

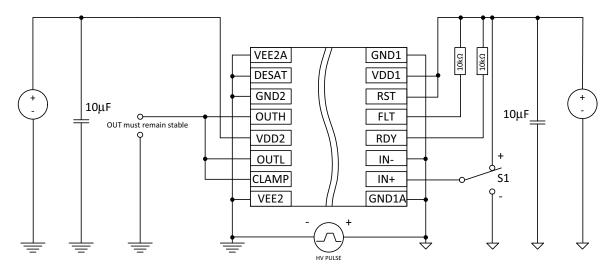

Figure 2. Simplified Application Schematics

#### **PIN DESCRIPTION**

| Pin Name           | No. | I/O   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>EE2A</sub>  | 1 8 | Power | Output side negative power supply. A good quality bypassing capacitor is required from these pins to GND2 and should be placed close to the pins for best results. Connect it to GND2 for unipolar supply application.                                                                                                                                                                                                                                                                          |

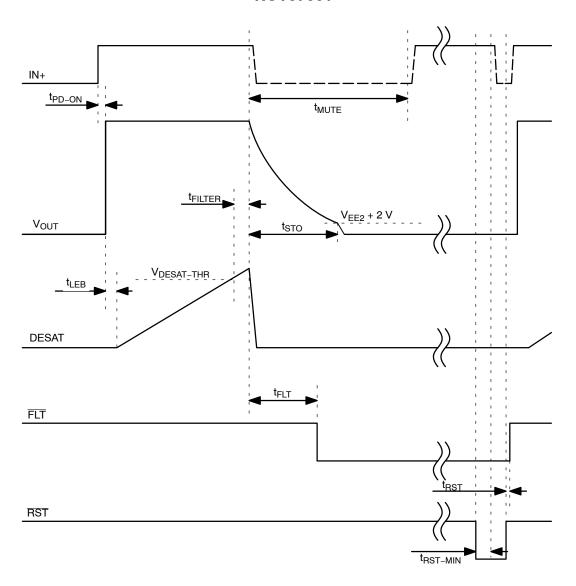

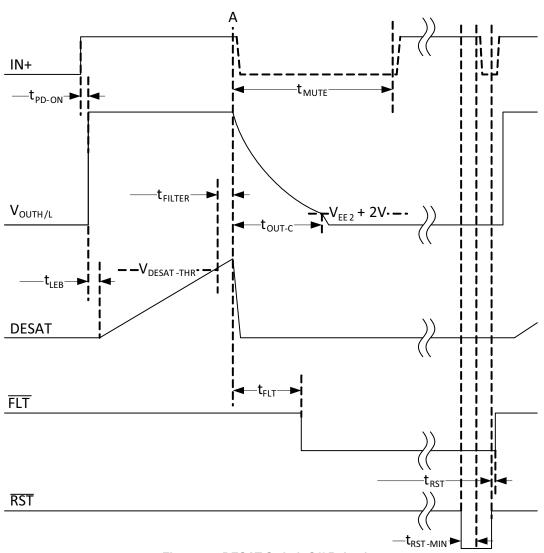

| DESAT              | 2   | I/O   | Input for detecting the desaturation of IGBT due to a short circuit condition. An internal constant current source I <sub>DESAT-CHG</sub> charging an external capacitor connected to this pin allows a programmable blanking delay every ON cycle before DESAT fault is processed, thus preventing false triggering. When the DESAT voltage goes up and reaches V <sub>DESAT-THR</sub> , the output is driven low. Further, the /FLT output is activated, please refer to Figure 5 on page 10. |

|                    |     |       | A 5 μs mute time apply to IN+ and IN- once DESAT occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GND2               | 3   | Power | Output side gate drive reference connecting to IGBT emitter or FET source.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| N/C                | 4   | _     | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{\mathrm{DD2}}$ | 5   | Power | Output side positive power supply. The operating range for this pin is from UVLO2 to its maximum allowed value. A good quality bypassing capacitor is required from this pin to GND2 and should be placed close to the pins for best results.                                                                                                                                                                                                                                                   |

| OUT                | 6   | 0     | Driver output that provides the appropriate drive voltage and source/sink current to the IGBT/FET gate. OUT is actively pulled low during start-up and under Fault conditions.                                                                                                                                                                                                                                                                                                                  |

| CLAMP              | 7   | I/O   | Provides clamping for the IGBT/FET gate during the off period to protect it from parasitic turn–on. Its internal N FET is turned on when the voltage of this pin falls below V <sub>EE2</sub> + V <sub>CLAMP-THR</sub> . It is to be tied directly to IGBT/FET gate with minimum trace length for best results.                                                                                                                                                                                 |

| GND1               | 9   | Power | Input side ground reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    | 16  |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IN+                | 10  | I     | Non inverted gate driver input. It is internally clamped to $V_{DD1}$ and has a pull–down resistor of 50 k $\Omega$ to ensure that output is low in the absence of an input signal. A minimum positive going pulse–width is required at IN+ before OUT responds.                                                                                                                                                                                                                                |

| IN-                | 11  | I     | Inverted gate driver input. It is internally clamped to $V_{DD1}$ and has a pull-up resistor of 50 k $\Omega$ to ensure that output is low in the absence of an input signal. A minimum negative going pulse-width is required at IN- before OUT responds.                                                                                                                                                                                                                                      |

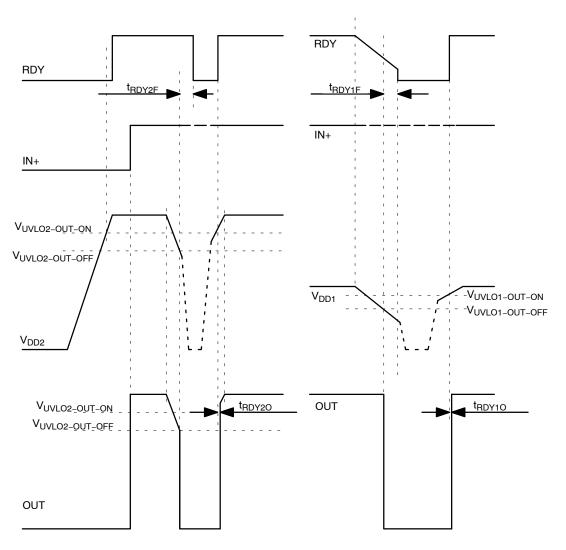

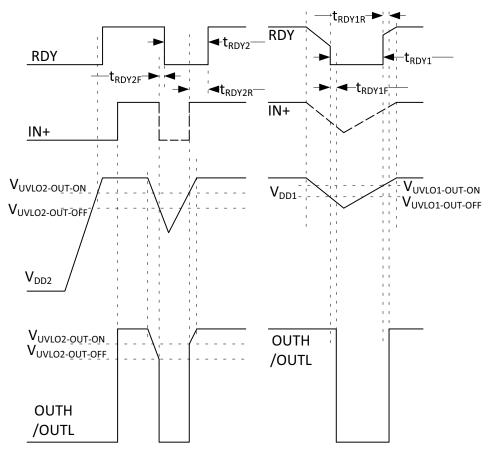

| RDY                | 12  | 0     | Power good indication output, active high when $V_{DD2}$ is good. There is an internal 50 k $\Omega$ pull–up resistor connected to this pin. Multiple of them from different drivers can be "OR"ed together. If a low RDY event is triggered by UVLO2, the maximum low duration for RDY is 200 ns. OUT remains low when RDY is low. Short time delay may apply. See Figure 4 on page 9 for details.                                                                                             |

| /FLT               | 13  | 0     | Fault output (active low) that allows communication to the main controller that the driver has encountered a desaturation condition and has deactivated the output.                                                                                                                                                                                                                                                                                                                             |

| /RST               | 14  | 1     | Reset input with an internal 50 k $\Omega$ pull-up resistor, active low to reset fault latch.                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DD1</sub>   | 15  | Power | Input side power supply (3.3 V to 5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **SAFETY AND INSULATION RATINGS**

| Symbol                | Parameter                                                                                                                                          |                         | Min       | Unit             |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|------------------|

|                       | Installation Classifications per DIN VDE 0110/1.89                                                                                                 | < 150 V <sub>RMS</sub>  | I – IV    |                  |

|                       | Table 1 Rated Mains Voltage                                                                                                                        | < 300 V <sub>RMS</sub>  | I – IV    |                  |

|                       |                                                                                                                                                    | < 450 V <sub>RMS</sub>  | I – IV    |                  |

|                       |                                                                                                                                                    | < 600 V <sub>RMS</sub>  | I – IV    |                  |

|                       |                                                                                                                                                    | < 1000 V <sub>RMS</sub> | I – III   |                  |

| CTI                   | Comparative Tracking Index (DIN IEC 112/VDE 0303 Part 1)                                                                                           | •                       | 600       |                  |

|                       | Climatic Classification                                                                                                                            |                         | 40/100/21 |                  |

|                       | Polution Degree (DIN VDE 0110/1.89)                                                                                                                |                         | 2         |                  |

| $V_{PR}$              | Input-to-Output Test Voltage, Method b, V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> , 100% Production Test with tm = 1 s, Partial Discharge < 5 pC |                         | 2250      | $V_{pk}$         |

|                       | Input-to-Output Test Voltage, Method a, V <sub>IORM</sub> x 1.6 = V <sub>PR</sub> , Type and Sample Test with tm = 10 s, Partial Discharge < 5 pC  |                         | -         | $V_{pk}$         |

| V <sub>IORM</sub>     | Maximum Repetitive Peak Voltage                                                                                                                    |                         | 1200      | $V_{pk}$         |

| $V_{IOWM}$            | Maximum Working Insulation Voltage                                                                                                                 |                         | 870       | V <sub>RMS</sub> |

| V <sub>IOTM</sub>     | Highest Allowable Over Voltage                                                                                                                     |                         | 8400      | $V_{pk}$         |

| E <sub>CR</sub>       | External Creepage                                                                                                                                  |                         | 8.0       | mm               |

| E <sub>CL</sub>       | External Clearance                                                                                                                                 |                         | 8.0       | mm               |

| DTI                   | Insulation Thickness                                                                                                                               |                         | 17.3      | um               |

| T <sub>Case</sub>     | Safety Limit Values – Maximum Values in Failure; Case Temperature                                                                                  |                         | 150       | °C               |

| P <sub>S,INPUT</sub>  | Safety Limit Values – Maximum Values in Failure; Input Power                                                                                       |                         | 36        | mW               |

| P <sub>S,OUTPUT</sub> | Safety Limit Values – Maximum Values in Failure; Output Power                                                                                      | 1364                    | mW        |                  |

| R <sub>IO</sub>       | Insulation Resistance at TS, V <sub>IO</sub> = 500 V                                                                                               | 10 <sup>9</sup>         | Ω         |                  |

#### ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature range unless otherwise noted) (Note 1)

| Symbol                               | Parameter                                                                                                             | Minimum                | Maximum                | Unit |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------|

| V <sub>DD1</sub> -GND1               | Supply voltage, input side                                                                                            | -0.3                   | 6                      | V    |

| V <sub>DD2</sub> -GND2               | Positive Power Supply, output side                                                                                    | -0.3                   | 25                     | V    |

| V <sub>EE2</sub> -GND2               | Negative Power Supply, output side                                                                                    | -10                    | 0.3                    | V    |

| $V_{DD2}$ - $V_{EE2}$ ( $V_{MAX2}$ ) | Differential Power Supply, output side                                                                                | 0                      | 25                     | V    |

| V <sub>OUT</sub>                     | Gate-driver output voltage                                                                                            | V <sub>EE2</sub> - 0.3 | V <sub>DD2</sub> + 0.3 | V    |

| I <sub>PK-SRC</sub>                  | Gate-driver output sourcing current (maximum pulse width = 10 $\mu$ s, maximum duty cycle = 0.2%, $V_{MAX2}$ = 20 V)  | -                      | 7.8                    | Α    |

| I <sub>PK-SNK</sub>                  | Gate-driver output sinking current (maximum pulse width = 10 μs, maximum duty cycle = 0.2%, V <sub>MAX2</sub> = 20 V) | -                      | 7.1                    | Α    |

| I <sub>PK-CLAMP</sub>                | Clamp sinking current (maximum pulse width = 10 $\mu$ s, maximum duty cycle = 0.2%, $V_{CLAMP}$ = 3 V)                | -                      | 2.5                    | Α    |

| t <sub>CLP</sub>                     | Maximum Short Circuit Clamping Time (I <sub>OUT_CLAMP</sub> = 500 mA)                                                 | -                      | 10                     | μs   |

| V <sub>LIM</sub> -GND1               | Voltage at IN+, IN-, /RST, /FLT, RDY                                                                                  | -0.3                   | V <sub>DD1</sub> + 0.3 | V    |

| I <sub>LIM</sub> -GND1               | Output current of /FLT, RDY                                                                                           | _                      | 10                     | mA   |

| V <sub>DESAT</sub> -GND2             | Desat Voltage (Note 2)                                                                                                | -9                     | V <sub>DD2</sub> + 0.3 | V    |

| V <sub>CLAMP</sub> -GND2             | Clamp Voltage                                                                                                         | V <sub>EE2</sub> - 0.3 | V <sub>DD2</sub> + 0.3 | V    |

| P <sub>D</sub>                       | Power Dissipation (Note 3)                                                                                            | -                      | 1400                   | mW   |

| T <sub>J(max)</sub>                  | Maximum Junction Temperature                                                                                          | -40                    | 150                    | °C   |

| T <sub>STG</sub>                     | Storage Temperature Range                                                                                             | -65                    | 150                    | °C   |

| ESD <sub>HBM</sub>                   | ESD Capability, Human Body Model (Note 4)                                                                             | _                      | ±2                     | kV   |

| ESD <sub>CDM</sub>                   | ESD Capability, Charged Device Model (Note 4)                                                                         | -                      | ±2                     | kV   |

| MSL                                  | Moisture Sensitivity Level                                                                                            | -                      | 2                      | _    |

| T <sub>SLD</sub>                     | Lead Temperature Soldering Reflow, Pb-Free Versions (Note 5)                                                          | -                      | 260                    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. The minimum value is verified by characterization with a single pulse of 100 mA for 100 µs.

- 3. The value is estimated for ambient temperature 25°C and junction temperature 150°C, 650 mm², 1 oz copper, 2 surface layers and 2 internal power plane layers. Power dissipation is affected by the PCB design and ambient temperature.

4. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Charged Device Model tested per AEC-Q100-011 (EIA/JESD22-C101)

- - Latchup Current Maximum Rating: ≤100 mA per JEDEC standard: JESD78, 125°C

- 5. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### THERMAL CHARACTERISTICS

| Symbol          | Parameter                           | Parameter Conditions                                                                     |     | Unit |

|-----------------|-------------------------------------|------------------------------------------------------------------------------------------|-----|------|

| $R_{\theta JA}$ | Thermal Resistance, Junction-to-Air | 100 mm <sup>2</sup> , 1 oz Copper, 1 Surface Layer                                       | 114 | °C/W |

|                 |                                     | 650 mm <sup>2</sup> , 1 oz Copper, 2 Surface Layers and<br>2 Internal Power Plane Layers | 62  |      |

#### **OPERATING RANGES** (Note 6)

| Symbol                                                  | Parameter                                  | Min                    | Max                    | Unit  |

|---------------------------------------------------------|--------------------------------------------|------------------------|------------------------|-------|

| V <sub>DD1</sub> -GND1                                  | Supply voltage, input side                 | UVLO1                  | 5.5                    | V     |

| V <sub>DD2</sub> -GND2                                  | Positive Power Supply, output side         | UVLO2                  | 24                     | V     |

| V <sub>EE2</sub> -GND2                                  | Negative Power Supply, output side         | -10                    | 0                      | V     |

| V <sub>DD2</sub> -V <sub>EE2</sub> (V <sub>MAX2</sub> ) | Differential Power Supply, output side     | 0                      | 24                     | V     |

| V <sub>IL</sub>                                         | Low level input voltage at IN+, IN-, /RST  | 0                      | 0.3 X V <sub>DD1</sub> | V     |

| V <sub>IH</sub>                                         | High level input voltage at IN+, IN-, /RST | 0.7 X V <sub>DD1</sub> | $V_{DD1}$              | V     |

| dV <sub>ISO</sub> /dt                                   | Common Mode Transient Immunity (1500 V)    | 100                    | -                      | kV/μs |

| T <sub>A</sub>                                          | Ambient Temperature                        | -40                    | 125                    | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

6. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

#### **ISOLATION CHARACTERISTICS**

| Symbol                         | Parameter                         | Conditions                                                                                      | Min  | Тур              | Max | Unit             |

|--------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------|------|------------------|-----|------------------|

| V <sub>ISO,</sub> input-output | Input-Output<br>Isolation Voltage | $T_A$ = 25°C, Relative Humidity < 50%, t = 1.0 minute, $I_{I-O}$ 10 A, 50 Hz (See Note 7, 8, 9) | 5000 | -                | -   | V <sub>RMS</sub> |

| R <sub>ISO</sub>               | Isolation<br>Resistance           | V <sub>I-O</sub> = 500 V (See Note 7)                                                           | -    | 10 <sup>11</sup> | -   | Ω                |

- 7. Device is considered a two-terminal device: pins 1 to 8 are shorted together and pins 9 to 16 are shorted together

- 8. 5,000  $V_{RMS}$  for 1-minute duration is equivalent to 6,000  $V_{RMS}$  for 1-second duration.

- The input-output isolation voltage is a dielectric voltage rating per UL1577. It should not be regarded as an input-output continuous voltage

rating. For the continuous working voltage rating, refer to equipment-level safety specification or DIN VDE V 0884-11 Safety and Insulation

Ratings Table

## **ELECTRICAL CHARACTERISTICS** ( $V_{DD1} = 5 \text{ V}$ , $V_{DD2} = 15 \text{ V}$ , $V_{EE2} = -8 \text{ V}$ . For typical values $T_A = 25^{\circ}\text{C}$ , for min/max values, $T_A$ is the operating ambient temperature range that applies, unless otherwise noted)

| Symbol                     | Parameter                                                | Test Condition                   | Min   | Тур  | Max  | Unit |

|----------------------------|----------------------------------------------------------|----------------------------------|-------|------|------|------|

| VOLTAGE SUPPLY             |                                                          |                                  |       |      | -    |      |

| V <sub>UVLO1-OUT-ON</sub>  | UVLO1 Output Enabled                                     |                                  | _     | -    | 3    | V    |

| V <sub>UVLO1-OUT-OFF</sub> | UVLO1 Output Disabled                                    |                                  | 2.4   | -    | -    | ٧    |

| V <sub>UVLO1-HYST</sub>    | UVLO1 Hysteresis                                         |                                  | 0.125 | -    | -    | ٧    |

| V <sub>UVLO2-OUT-ON</sub>  | UVLO2 Output Enabled                                     |                                  | 13.2  | 13.5 | 13.8 | ٧    |

| V <sub>UVLO2-OUT-OFF</sub> | UVLO2 Output Disabled                                    |                                  | 12.2  | 12.5 | 12.8 | ٧    |

| V <sub>UVLO2-HYST</sub>    | UVLO2 Hysteresis                                         |                                  | -     | 1    |      | ٧    |

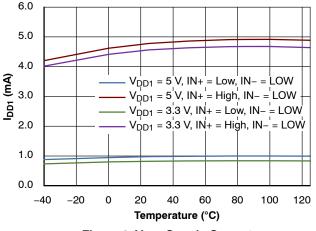

| I <sub>DD1-0</sub>         | Input Supply Quiescent Current                           | IN+ = Low, IN- = Low             | -     | 1    | 2    | mA   |

|                            | Output Low                                               | RDY = High, /FLT = High          |       |      |      |      |

| I <sub>DD1-100</sub>       | Input Supply Quiescent Current                           | IN+ = High, IN- = Low            | -     | 4.8  | 6    | mA   |

|                            | Output High                                              | RDY = High, /FLT = High          |       |      |      |      |

| I <sub>DD2-0</sub>         | Output Positive Supply Quiescent                         | IN+ = Low, IN- = Low             | -     | 3.3  | 4    | mA   |

|                            | Current, Output Low                                      | RDY = High, /FLT = High, no load |       |      |      |      |

| I <sub>DD2-100</sub>       | Output Positive Supply Quiescent                         | IN+ = High, IN- = Low            | -     | 3.6  | 6    | mA   |

|                            | Current, Output High                                     | RDY = High, /FLT = High, no load |       |      |      |      |

| I <sub>EE2-0</sub>         | Output Negative Supply<br>Quiescent Current, Output Low  | IN+ = High, IN- = Low, no load   | -     | 0.4  | 2    | mA   |

| I <sub>EE2-100</sub>       | Output Negative Supply<br>Quiescent Current, Output High | IN+ = High, IN- = Low, no load   | -     | 0.2  | 2    | mA   |

**ELECTRICAL CHARACTERISTICS** ( $V_{DD1} = 5 \text{ V}, V_{DD2} = 15 \text{ V}, V_{EE2} = -8 \text{ V}$ . For typical values  $T_A = 25^{\circ}\text{C}$ , for min/max values,  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted) (continued)

| Symbol                                  | Parameter                                                           | Test Condition                                                                                           | Min                       | Тур                        | Max                       | Unit |

|-----------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|----------------------------|---------------------------|------|

| LOGIC INPUT AND                         | ОИТРИТ                                                              |                                                                                                          |                           |                            |                           |      |

| $V_{IL}$                                | IN+, IN-, /RST Low Input Voltage                                    |                                                                                                          | _                         | _                          | 0.3 x<br>V <sub>DD1</sub> | V    |

| $V_{IH}$                                | IN+, IN-, /RST High Input Voltage                                   |                                                                                                          | 0.7 x<br>V <sub>DD1</sub> | -                          | -                         | ٧    |

| V <sub>IN-HYST</sub>                    | Input Hysteresis Voltage                                            |                                                                                                          | -                         | 0.15 x<br>V <sub>DD1</sub> | -                         | ٧    |

| I <sub>IN-L</sub> , I <sub>RST-L</sub>  | IN-, /RST Input Current<br>(50 kΩ pull-up resistor)                 | V <sub>IN</sub> -/V <sub>RST</sub> = 0 V                                                                 | -                         | -100                       | -                         | μА   |

| I <sub>IN+H</sub>                       | IN+ Input Current<br>(50 kΩ pull-down resistor)                     | V <sub>IN+</sub> = 5 V                                                                                   | -                         | 100                        | -                         | μΑ   |

| I <sub>RDY-L</sub> , I <sub>FLT-L</sub> | RDY, /FLT Pull-up Current (50 kΩ pull-up resistor)                  | $V_{RDY}/V_{FLT} = Low$                                                                                  | _                         | 100                        | -                         | μΑ   |

| V <sub>RDY-L</sub> , V <sub>FLT-L</sub> | RDY, /FLT Low Level Output Voltage                                  | I <sub>RDY</sub> /I <sub>FLT</sub> = 5 mA                                                                | -                         | -                          | 0.3                       | V    |

| t <sub>MIN1</sub>                       | Input Pulse Width of IN+, IN- for<br>No Response at Output          |                                                                                                          | -                         | -                          | 10                        | ns   |

| t <sub>MIN2</sub>                       | Input Pulse Width of IN+, IN- for<br>Guaranteed Response at Output  |                                                                                                          | 40                        | -                          | -                         | ns   |

| t <sub>RST-MIN</sub>                    | Pulse Width of /RST for Resetting /FLT                              |                                                                                                          | 800                       | -                          | -                         | ns   |

| DRIVER OUTPUT                           |                                                                     |                                                                                                          |                           |                            |                           |      |

| V <sub>OUTL1</sub>                      | Output Low State<br>(V <sub>OUT</sub> – V <sub>EE2</sub> )          | I <sub>SINK</sub> = 200 mA                                                                               | -                         | 0.1                        | 0.2                       | V    |

| V <sub>OUTL3</sub>                      |                                                                     | I <sub>SINK</sub> = 1.0 A, T <sub>A</sub> = 25°C                                                         | -                         | 0.5                        | 0.8                       | 1    |

| V <sub>OUTH1</sub>                      | Output High State                                                   | I <sub>SRC</sub> = 200 mA                                                                                | _                         | 0.3                        | 0.5                       | V    |

| V <sub>OUTH3</sub>                      | $(V_{DD2} - V_{OUT})$                                               | I <sub>SRC</sub> = 1.0 A, T <sub>A</sub> = 25°C                                                          | -                         | 0.8                        | 1                         | 1    |

| I <sub>PK-SNK1</sub>                    | Peak Driver Current, Sink (Note 10)                                 | V <sub>OUT</sub> = 7.9 V                                                                                 | -                         | 7.1                        | -                         | Α    |

| I <sub>PK</sub> -SRC1                   | Peak Driver Current, Source (Note 10)                               | V <sub>OUT</sub> = −5 V                                                                                  | _                         | 7.8                        | -                         | Α    |

| MILLER CLAMP                            |                                                                     |                                                                                                          |                           |                            |                           |      |

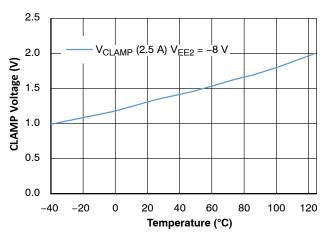

| V <sub>CLAMP</sub>                      | Clamp Voltage                                                       | I <sub>CLAMP</sub> = 2.5 A, T <sub>A</sub> = 25°C                                                        | -                         | 1.3                        | 1.7                       | V    |

|                                         | (V <sub>CLAMP</sub> – V <sub>EE2</sub> )                            | I <sub>CLAMP</sub> = 2.5 A, T <sub>A</sub> = -40°C to 125°C                                              | -                         | -                          | 3                         |      |

| V <sub>CLAMP-THR</sub>                  | Clamp Activation Threshold (V <sub>CLAMP</sub> – V <sub>EE2</sub> ) |                                                                                                          | 1.5                       | 2                          | 2.5                       | V    |

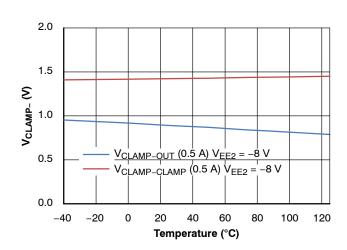

| GBT SHORT CIRC                          | UIT CLAMPING                                                        |                                                                                                          |                           |                            |                           |      |

| V <sub>CLAMP</sub> -OUT                 | Clamping Voltage, (V <sub>OUT</sub> – V <sub>DD2</sub> )            | IN+ = Low, IN- = High,<br>I <sub>OUT</sub> = 500 mA<br>(pulse test, t <sub>CLPmax</sub> = 10 μs)         | -                         | 0.9                        | 1.1                       | V    |

| V <sub>CLAMP-CLAMP</sub>                | Clamping Voltage, Clamp<br>(V <sub>CLAMP</sub> - V <sub>DD2</sub> ) | IN+ = High, IN- = Low,<br>I <sub>CLAMP-CLAMP</sub> = 500 mA<br>(pulse test, t <sub>CLPmax</sub> = 10 μs) | -                         | 1.4                        | 1.6                       | V    |

| DESAT PROTECTION                        | ON                                                                  |                                                                                                          |                           |                            |                           |      |

| V <sub>DESAT-THR</sub>                  | DESAT Threshold Voltage                                             |                                                                                                          | 8.5                       | 9                          | 9.5                       | V    |

| V <sub>DESAT-NEG</sub>                  | DESAT Negative Voltage                                              | I <sub>DESAT</sub> = 1.5 mA                                                                              | -                         | -8                         | -                         | V    |

| I <sub>DESAT-CHG</sub>                  | Blanking Charge Current                                             | V <sub>DESAT</sub> = 7 V                                                                                 | 0.45                      | 0.5                        | 0.6                       | mA   |

| I <sub>DESAT-DIS</sub>                  | Blanking Discharge Current                                          |                                                                                                          | -                         | 50                         | -                         | mA   |

**ELECTRICAL CHARACTERISTICS** ( $V_{DD1} = 5 \text{ V}$ ,  $V_{DD2} = 15 \text{ V}$ ,  $V_{EE2} = -8 \text{ V}$ . For typical values  $T_A = 25^{\circ}\text{C}$ , for min/max values,  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted) (continued)

| Symbol                   | Parameter                                     | Test Condition                                                                                                                        | Min | Тур | Max | Unit |

|--------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| YNAMIC CHARA             | CTERISTICS                                    |                                                                                                                                       |     |     | •   |      |

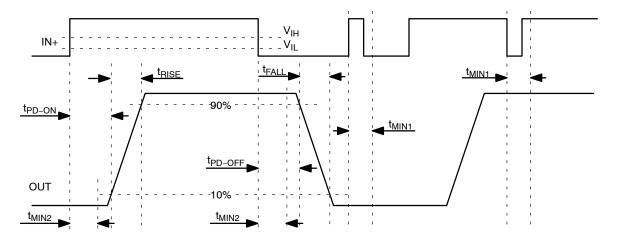

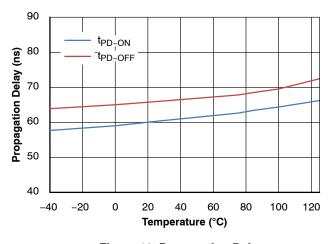

| t <sub>PD-ON</sub>       | IN+, IN- to Output High Propagation<br>Delay  | C <sub>LOAD</sub> = 10 nF<br>V <sub>IH</sub> to 10% of output change for<br>PW > 150 ns. OUT and CLAMP pins<br>are connected together | 40  | 60  | 90  | ns   |

| t <sub>PD-OFF</sub>      | IN+, IN- to Output Low Propagation<br>Delay   | C <sub>LOAD</sub> = 10 nF<br>V <sub>IL</sub> to 90% of output change for<br>PW > 150 ns. OUT and CLAMP pins<br>are connected together | 40  | 66  | 90  | ns   |

| t <sub>DISTORT</sub>     | Propagation Delay Distortion                  | T <sub>A</sub> = 25°C, PW > 150 ns                                                                                                    | -15 | -6  | 15  | ns   |

|                          | (= t <sub>PD-ON</sub> - t <sub>PD-OFF</sub> ) | $T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}, \text{ PW} > 150 \text{ ns}$                                                      | -25 | -   | 25  | ]    |

| t <sub>DISTORT_TOT</sub> | Prop Delay Distortion between Parts           | PW > 150 ns                                                                                                                           | -30 | 0   | 30  | ns   |

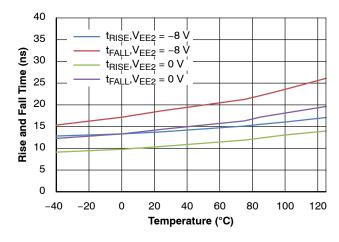

| t <sub>RISE</sub>        | Rise Time (see Fig. 3) (Note 10)              | C <sub>LOAD</sub> = 1 nF, 10% to 90% of<br>Output Change                                                                              | -   | 10  | -   | ns   |

| t <sub>FALL</sub>        | Fall Time (see Fig. 3) (Note 10)              | C <sub>LOAD</sub> = 1 nF, 90% to 10% of<br>Output Change                                                                              | -   | 15  | -   | ns   |

| t <sub>LEB</sub>         | DESAT Leading Edge Blanking Time (See Fig. 5) |                                                                                                                                       | -   | 450 | -   | ns   |

| t <sub>FILTER</sub>      | DESAT Threshold Filtering Time (see Fig. 5)   |                                                                                                                                       | -   | 320 | -   | ns   |

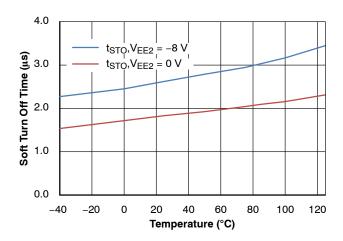

| t <sub>STO</sub>         | Soft Turn Off Time (see Fig. 5)               | $C_{LOAD}$ = 10 nF, $R_G$ = 10 $\Omega$ . $V_{EE2}$ = 0 $V$                                                                           | -   | 1.8 | -   | μs   |

|                          |                                               | $C_{LOAD}$ = 10 nF, $R_G$ = 10 $\Omega$                                                                                               | -   | 2.6 | -   | 1    |

| t <sub>FLT</sub>         | Delay after t <sub>FILTER</sub> to /FLT       |                                                                                                                                       | -   | 450 | -   | ns   |

| t <sub>RST</sub>         | /RST Rise to /FLT Rise Delay                  |                                                                                                                                       | -   | 23  | -   | ns   |

| t <sub>RDY10</sub>       | RDY High to Output High Delays                |                                                                                                                                       | -   | 55  | -   | ns   |

| t <sub>RDY20</sub>       | (see Fig. 4)                                  |                                                                                                                                       |     |     |     |      |

| t <sub>RDY1F</sub>       | V <sub>UVLO2-OUT-OFF</sub> to RDY Low         |                                                                                                                                       | -   | 8   | -   | μs   |

| t <sub>RDY2F</sub>       | Delays (see Fig. 4)                           |                                                                                                                                       |     |     |     |      |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

10. Values based on design and/or characterization.

#### **ORDERING INFORMATION**

| Device        | Package Type                   | Shipping <sup>†</sup> |

|---------------|--------------------------------|-----------------------|

| NCV57001DWR2G | SOIC-16 Wide Body<br>(Pb-Free) | 1,000 / Tape & Reel   |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

Figure 3. Propagation Delay, Rise and Fall Time

Figure 4. UVLO Waveform

Figure 5. DESAT Response Waveform

#### **TYPICAL CHARACTERISTICS**

(Conditions for the following figures are the same as stated for ELECTRICAL CHARACTERISTICS Table unless otherwise noted.

Typical and/or average values are used.)

6.0

5.0 4.0 I<sub>DD2</sub> (mA) 3.0 2.0  $V_{DD2} = 15 \text{ V}, \overline{\text{IN} + \text{ELow}, IN} - \text{ELOW}$  $V_{DD2} = 15 \text{ V}, \text{ IN}_{+} = 1 \text{ MHz}, \text{ IN}_{-} = \text{LOW}$ 1.0 V<sub>DD2</sub> = 15 V, IN+ = High, IN- = LOW 0.0 -40 -20 0 80 100 20 40 60 120 Temperature (°C)

Figure 6. V<sub>DD1</sub> Supply Current

Figure 7.  $V_{DD2}$  Supply Current

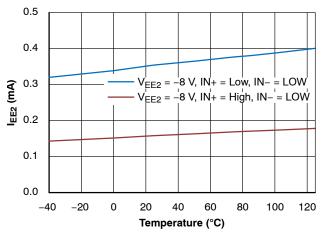

Figure 8. V<sub>EE2</sub> Supply Current

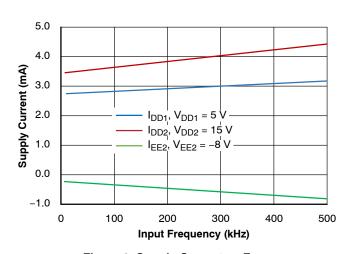

Figure 9. Supply Current vs Frequency

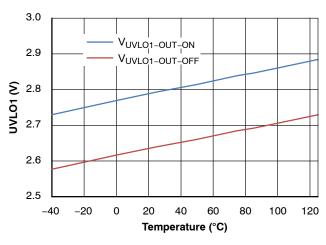

Figure 10. UVLO1 Threshold Voltage

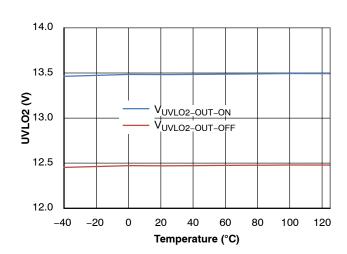

Figure 11. UVLO2 Threshold Voltage

#### **TYPICAL CHARACTERISTICS**

(Conditions for the following figures are the same as stated for ELECTRICAL CHARACTERISTICS Table unless otherwise noted.

Typical and/or average values are used.) (continued)

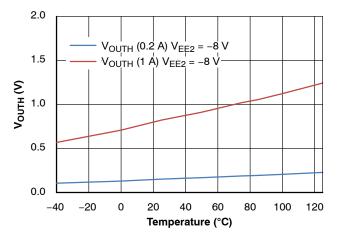

2.0  $V_{OUTL}$  (0.2 A)  $V_{EE2} = -8 V$ 1.5  $V_{OUTL}$  (1 Å)  $V_{EE2} = -8 \text{ V}$ VOUTL (V) 1.0 0.5 0.0 0 80 -40 -20 20 40 60 100 120 Temperature (°C)

Figure 12. Output Voltage Drop, Sourcing

Figure 13. Output Voltage Drop, Sinking

Figure 14. CLAMP Voltage Drop

Figure 15. IGBT Short Circuit Clamp Voltage Drop

Figure 16. Propagation Delay

Figure 17. Rise and Fall Time

Figure 18. Soft Turn Off Time

#### **FEATURE DESCRIPTIONS**

#### **Under Voltage Lockout (UVLO)**

UVLO ensures correct switching of IGBT connected to the driver output.

- The IGBT is turned-off, if the supply V<sub>CC1</sub> drops below V<sub>UVLO1-OUT-OFF</sub> and the RDY pin output goes to low.

- $\bullet$  The driver output does not start to react to the input signal on  $V_{IN}$  until the  $V_{CC1}$  rises above the  $V_{UVLO1-OUT-ON}$  again. If the supply  $V_{CC1}$  increase over  $V_{UVLO1-OUT-ON}$ , the RDY pin output goes to be open–drain and outputs continue to switch IGBT

- $\bullet$  The IGBT is turned–off, if the supply  $V_{CC2}$  drops below  $V_{UVLO2-OUT-OFF}$  and the RDY pin output goes to low.

- The driver output does not start to react to the input signal on V<sub>IN</sub> until the V<sub>CC1</sub> rises above the V<sub>UVLO1-OUT-ON</sub> again. If the supply V<sub>DD1</sub> increases over V<sub>UVLO1-OUT-ON</sub>, the RDY pin output goes to be open-drain and outputs continue to switch IGBT

- VEE2 is not monitored.

Figure 19. UVLO Diagram

#### **Active Miller Clamp Protection (CLAMP)**

NCV57001 supports both bipolar and unipolar power supply with active Miller clamp.

For operation with bipolar supplies, the IGBT is turned off with a negative voltage through OUTL with respect to its emitter. This prevents the IGBT from unintentionally turning on because of current induced from its collector to its gate due to Miller effect. In this condition it is not necessary to connect CLAMP output of the gate driver to the IGBT gate, but connecting CLAMP output to the IGBT gate is also not an issue. Typical values for bipolar operation are  $V_{DD2} = 15 \ V$  and  $V_{EE2} = -5 \ V$  with respect to GND<sub>2</sub>.

For operation with unipolar supply, typically,  $V_{DD2} = 15~V$  with respect to  $GND_2$ , and  $V_{EE2} = GND_2$ . In this case, the IGBT can turn on due to additional charge from IGBT Miller capacitance caused by a high voltage slew rate transition on the IGBT collector. To prevent IGBT to turn on, the CLAMP pin is connected directly to IGBT gate and Miller current is sinked through a low impedance CLAMP transistor. When the IGBT is turned–off and the gate voltage transitions below  $V_{CLAMP}$ , the CLAMP current output is activated.

#### Non-inverting and Inverting Input Pin (IN+, IN-)

NCV57001 has two possible input modes to control IGBT. Both inputs have defined minimum input pulse width to filter occasional glitches.

- Non-inverting input IN+ controls the driver output while inverting input IN- is set to LOW

- Inverting input IN– controls the driver output while non–inverting input IN+ is set to HIGH

Warning: When the application use an independent or separate power supply for the control unit ant the input side of the driver, all inputs should be protected by a serial resistor (In case of a power failure of the driver, the driver may be damaged due to overloading of the input protection circuits)

Figure 21. Current Path with Miler Clamp Protection

#### **Desaturation Protection (DESAT)**

Desaturation protection ensures the protection of IGBT at short circuit. When the  $V_{CESAT}$  voltage goes up and reaches the set limit, the output is driven low and /FLT output is activated. Blanking time can be set by internal current source and an external capacitor. To avoid false DESAT triggering and minimize blanking time, fast switching diodes with low internal capacitance are recommended. All DESAT protective diodes internal capacitances builds voltage divider with the blanking capacitor.

<u>Warning:</u> Both external protective diodes are recommended for the protection against voltage spikes caused by IGBT transients passing through parasitic capacitances.

#### **DESAT Circuit Parameters Specification**

$$t_{BLANK} = C_{BLANK} \cdot \frac{V_{DESAT-THR}}{I_{DESAT-CHG}}$$

$$V_{DESAT-THR} > R_{S-DESAT} \cdot I_{DESAT-CHG} + V_{F \, HV \, diode} + V_{CESAT\_IGBT}$$

Figure 22. DESAT Protection Schematic

Figure 23. DESAT Switch Off Behavior

#### Fault Output Pin (FLT)

FLT open-drain output provides feedback to the controller about driver DESAT protection conditions. The open-drain FLT outputs of multiple NCV57001 devices can be wired together forming a single, common fault bus for interfacing directly to the microcontroller. FLT output has  $50k\Omega$  internal pull-up resistor to VDD1.

#### Ready Output Pin (RDY)

RDY open-drain output provides feedback to the controller about driver UVLO and TSD protections conditions.

- If either side of device have insufficient supply (VDD1 or VDD2), the RDY pin output goes low; otherwise, RDY pin output is open drain.

- If the temperature crosses the TSD threshold, the RDY pin output goes low; otherwise, RDY pin output is open drain.

The open-drain RDY outputs of multiple NCV57001 devices can be "OR"ed together.

#### Reset Input Pin (RST)

Reset input pin has internal pull-up resistor to VDD1. In normal condition the RST pin is connected to HIGH, to reset FAULT conditions or disable output pulses connect RST pin to LOW. In applications that does not allow to control the reset, RST pin should be connected to IN+, the driver will be reset by each input pulse.

#### **RESET Input**

• FLT input is used to set back FLT output after DESAT conditions disappear

Warning: When the application use an independent or separate power supply for the control unit ant the input side of the driver, all inputs should be protected by a serial resistor (In case of a power failure of the driver, the driver may be damaged due to overloading of the input protection circuits)

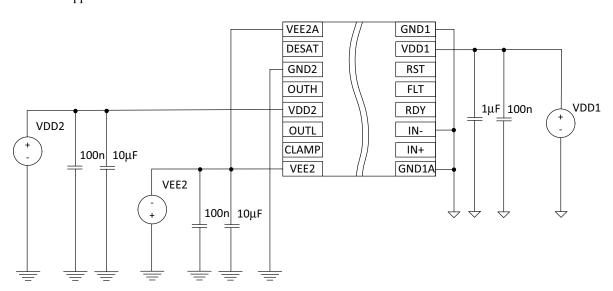

#### Power Supply (VDD1, VDD2, VEE2)

NCV57001 is designed to support two different power supply configurations, bipolar or unipolar power supply. For reliable high output current the suitable external power capacitors required. Parallel combination of  $100 \text{ nF} + 4.7 \mu\text{F}$  ceramic capacitors is optimal for a wide range of applications using IGBT. For reliable driving IGBT modules (containing several parallel IGBT's) is a higher capacity required (typically  $100 \text{ nF} + 10 \mu\text{F}$ ). Capacitors should be as close as possible to the driver's power pins.

- In bipolar power supply the driver is typically supplied with a positive voltage of 15 V at VDD2 and negative voltage –5 V at VEE2 (Figure 24). Negative power supply prevents a dynamic turn on throughout the internal IGBT input capacitance.

- In Unipolar power supply the driver is typically supplied with a positive voltage of 15 V at VDD2.

Dynamic turn on throughout the internal IGBT input capacitance could be prevented by Active Miler Clamp function. CLAMP output should be directly connected to IGBT gate (Figure 25).

Figure 24. Bipolar Power Supply

Figure 25. Unipolar Power Supply

#### **Common Mode Transient Immunity (CMTI)**

Figure 26. Common-Mode Transient Immunity Test Circuit

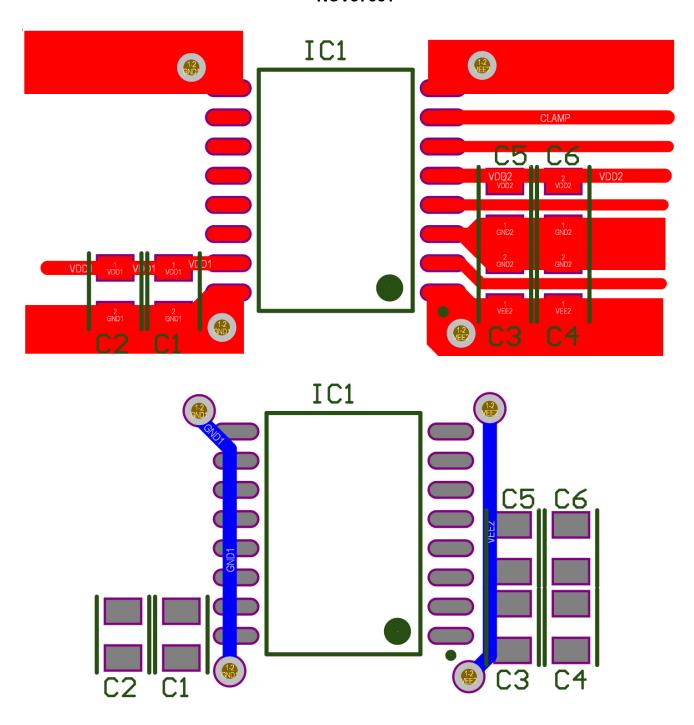

Figure 27. Recommended Basic Bipolar Power Supply PCB Design

Figure 28. Recommended Layer Stack

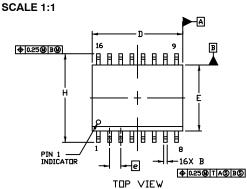

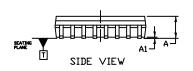

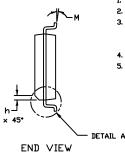

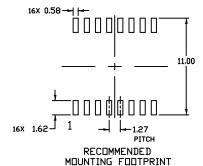

SOIC-16 WB CASE 751G ISSUE E

**DATE 08 OCT 2021**

DETAIL A

#### NOTES

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION.

- DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.

- MAXIMUM MOLD PROTRUSION OR FLASH TO BE 0.15 PER SIDE.

|     | MILLIM | IETERS |

|-----|--------|--------|

| DIM | MIN.   | MAX.   |

| Α   | 2.35   | 2.65   |

| A1  | 0.10   | 0.25   |

| В   | 0.35   | 0.49   |

| С   | 0.23   | 0.32   |

| D   | 10.15  | 10.45  |

| E   | 7.40   | 7.60   |

| е   | 1.27   | BSC    |

| Н   | 10.05  | 10.55  |

| h   | 0.53   | REF    |

| ١   | 0.50   | 0.90   |

| М   | 0*     | 7*     |

**GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location

WL = Wafer Lot YY = Year ww = Work Week = Pb-Free Package

Electronic versions are uncontrolled except when accessed directly from the Document Repository. **DOCUMENT NUMBER:** 98ASB42567B Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. **DESCRIPTION:** SOIC-16 WB **PAGE 1 OF 1**

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "=", may or may not be present. Some products may not follow the Generic Marking.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Gate Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

89076GBEST 00053P0231 56956 57.404.7355.5 LT4936 57.904.0755.0 5882900001 00600P0005 00-9050-LRPP 00-9090-RDPP

5951900000 01-1003W-10/32-15 0131700000 00-2240 LTP70N06 LVP640 5J0-1000LG-SIL LY1D-2-5S-AC120 LY2-US-AC240 LY3UA-DC24 00576P0020 00600P0010 LZN4-UA-DC12 LZNQ2M-US-DC5 LZNQ2-US-DC12 LZP40N10 00-8196-RDPP 00-8274-RDPP

00-8275-RDNP 00-8722-RDPP 00-8728-WHPP 00-8869-RDPP 00-9051-RDPP 00-9091-LRPP 00-9291-RDPP 0207100000 0207400000

01312 0134220000 60713816 M15730061 61161-90 61278-0020 6131-204-23149P 6131-205-17149P 6131-209-15149P 6131-218-17149P

6131-220-21149P 6131-260-2358P 6131-265-11149P