# Linear Voltage Regulator -Bias Rail, Low Noise, Very Low Dropout, Programmable Soft-Start

# NCV59745

### Description

The NCV59745 is very low dropout low noise dual-rail voltage regulator that is capable of providing an output current in excess of 3.0 A with a dropout voltage of 115 mV typ. at full load current. This series contains fixed output voltage devices. The high output current capability with high accuracy, broad bandwidth high PSRR and low noise makes this VLDOs ideal for powering noise sensitive high speed communication devices, high end FPGAs and microprocessors.

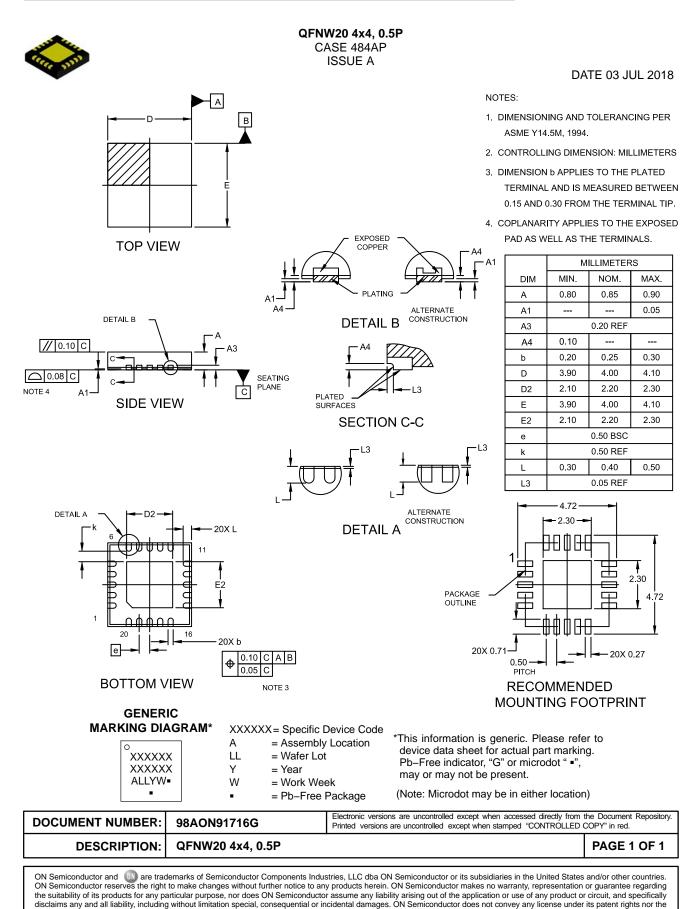

The NCV59745 is offered in QFNW20 4.0 mm x 4.0 mm package. **Features**

- Output Current in Excess of 3.0 A

- 0.25% Typical Accuracy Over Line and Load

- $V_{IN}$  Range: 0.8 V to 5.5 V

- V<sub>BIAS</sub> Range: 2.2 V to 5.5 V

- Output Voltage Range: 0.8 V to 3.6 V

- Dropout Voltage: 105 mV typ. at 3 A

- Programmable Soft Start

- Open Drain Power Good Output

- Low Noise, 6 μV<sub>RMS</sub> Typically

- Excellent Transient Response

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb-Free Devices, Wettable Flank for AOI

#### Applications

- High Speed Analog VCO, DAC, ADC

- FPGAs, DSPs, SerDes

- Imaging Sensors and ASICs

- Automotive, Telecom and Industrial Equipment Point of Load Regulation

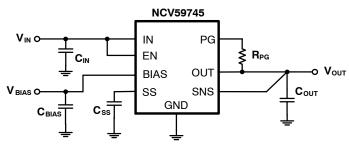

Figure 1. Typical Application Schematic

# **ON Semiconductor®**

#### www.onsemi.com

QFNW20 MW SUFFIX CASE 484AP

#### MARKING DIAGRAM

= vvater

Α

LL Y

W

- = Year

- = Work Week

- = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 10 of this data sheet.

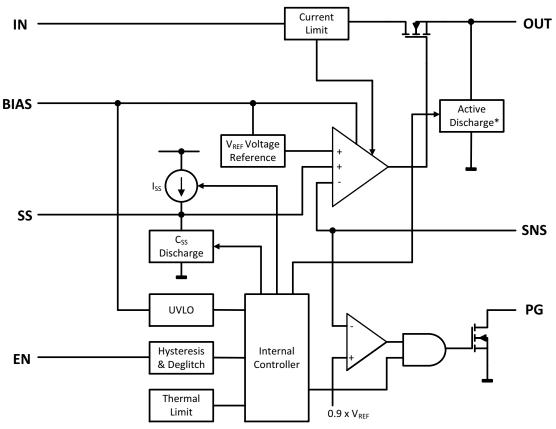

\*Active output discharge function is present only in NCV59745A option devices.

Figure 2. Simplified Schematic Block Diagram

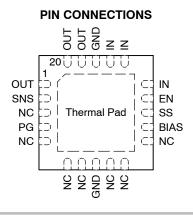

| Name    | QFNW20       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN      | 15–17        | Unregulated voltage input to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EN      | 14           | Enable pin. Driving this pin high enables the regulator. Driving this pin low puts the regulator into shut-<br>down mode. This pin must not be left floating.                                                                                                                                                                                                                                                                                                                                                                                              |

| SS      | 13           | Soft-Start pin. A capacitor connected on this pin to ground sets the Soft - Start time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BIAS    | 12           | Bias input voltage for error amplifier, reference, and internal control circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PG      | 4            | Power–Good (PG) is an open–drain, active–high output that indicates the status of V <sub>OUT</sub> . When V <sub>OUT</sub> exceeds the PG trip threshold, the PG pin goes into a high–impedance state. When V <sub>OUT</sub> is below this threshold the pin is driven to a low–impedance state. A pull–up resistor from 10 k $\Omega$ to 100 k $\Omega$ should be connected from this pin to a supply up to 5.5 V. The supply can be higher than the input voltage. Alternatively, the PG pin can be left floating if output monitoring is not necessary. |

| SNS     | 2            | Output voltage sense input pin. This pin must not be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OUT     | 1, 19, 20    | Regulated output voltage. It is recommended that the output capacitor $\ge$ 10 $\mu$ F (effective value).                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NC      | 3, 5–7, 9–11 | No connection. Each one pin is "true NC" and can be left floating or connected to GND to allow better thermal contact to the PCB top-side plane.                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND     | 8, 18        | Ground pins. Both these pins must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PAD/TAB |              | Should be soldered to the ground plane for increased thermal performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# Table 1. PIN FUNCTION DESCRIPTION

#### Table 2. ABSOLUTE MAXIMUM RATINGS

| Parameter                                     | Symbol             | Value                                         | Unit |  |

|-----------------------------------------------|--------------------|-----------------------------------------------|------|--|

| Input Voltage Range                           | V <sub>IN</sub>    | -0.3 to +6                                    | V    |  |

| Bias Voltage Range                            | V <sub>BIAS</sub>  | -0.3 to +6                                    | V    |  |

| Enable Voltage Range                          | V <sub>EN</sub>    | -0.3 to +6                                    | V    |  |

| Power-Good Voltage Range                      | V <sub>PG</sub>    | -0.3 to +6                                    | V    |  |

| PG Sink Current                               | I <sub>PG</sub>    | 0 to +1.5                                     | mA   |  |

| SS Pin Voltage Range                          | V <sub>SS</sub>    | $-0.3$ to $(V_{BIAS} + 0.3) \le 6$            | V    |  |

| Output Sense Pin Voltage Range                | V <sub>SNS</sub>   | -0.3 to +6                                    | V    |  |

| Output Voltage Range                          | V <sub>OUT</sub>   | $-0.3$ to $(V_{IN} + 0.3) \le 6$              | V    |  |

| Maximum Output Current                        | I <sub>OUT</sub>   | Internally Limited                            |      |  |

| Output Short Circuit Duration                 |                    | Indefinite                                    |      |  |

| Continuous Total Power Dissipation            | PD                 | See Thermal Characteristics Table and Formula |      |  |

| Maximum Junction Temperature                  | T <sub>JMAX</sub>  | +150                                          | °C   |  |

| Storage Junction Temperature Range            | T <sub>STG</sub>   | –55 to +150                                   | °C   |  |

| ESD Capability, Human Body Model (Note 2)     | ESD <sub>HBM</sub> | 2000                                          | V    |  |

| ESD Capability, Charged Device Model (Note 2) | ESD <sub>CDM</sub> | 1000                                          | V    |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHĂRACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002

ESD Charged Device Model tested per AEC-Q100-011

Latch-up Current Maximum Rating ±100 mA per AEC-Q100-004.

#### Table 3. THERMAL CHARACTERISTICS

| Rating                                                 | Symbol    | Value | Unit |

|--------------------------------------------------------|-----------|-------|------|

| Thermal Characteristics, QFNW20, 4.0x4.0, 0.5P package |           |       |      |

| Thermal Resistance, Junction-to-Ambient (Note 5)       | Reja      | 40    | °C/W |

| Thermal Resistance, Junction-to-Board (Note 6)         | Rөjb      | 3.6   | °C/W |

| Thermal Resistance, Junction-to-Case (top)             | RθJC(top) | 27    | °C/W |

| Thermal Resistance, Junction-to-Case (bottom) (Note 7) | RθJC(bot) | 3.6   | °C/W |

| Characterisation Parameter, Junction-to-Top            | ΤιΨ       | 1.0   | °C/W |

| Characterisation Parameter, Junction-to-Board          | Ψјв       | 3.5   | °C/W |

3. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

4. Thermal data are derived by thermal simulations based on methodology specified in the JEDEC JESD51 series standards. The following assumptions are used in the simulations:

These data were generated with only a single device at the center of a high-K (2s2p) board with 3 in x 3 in copper area which follows the JEDEC51.7 guidelines. Top and Bottom layer 2 oz. copper, inner planes 1 oz. copper.

The exposed pad is connected to the PCB ground inner layer through a 3 x 3 thermal via array. Vias are 0.3 mm diameter, plated.

5. The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a high-K board, following the JEDEC51.7 guidelines with assumptions as above, in an environment described in JESD51-2a.

6. The junction-to-board thermal resistance is simulated in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

7. The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the IC exposed pad. Test description can be found in the ANSI SEMI standard G30-88.

#### Table 4. RECOMMENDED OPERATING CONDITIONS (Note 8)

| Rating               | Symbol            | Min                                | Max | Unit |

|----------------------|-------------------|------------------------------------|-----|------|

| Input Voltage        | V <sub>IN</sub>   | V <sub>OUT</sub> + V <sub>DO</sub> | 5.5 | V    |

| Bias Voltage         | V <sub>BIAS</sub> | V <sub>OUT</sub> + 1.6             | 5.5 | V    |

| Junction Temperature | ТJ                | -40                                | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

8. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

| Table 5. ELECTRICAL CHARACTERISTICS (At $V_{EN} = 1.1 \text{ V}$ , $V_{IN} = V_{OUT(NOM)} + 0.25 \text{ V}$ , $C_{BIAS} = 1 \mu F$ , $C_{IN} = 4.7 \mu F$ , $C_{OUT} = 10 \mu F$ , |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $I_{OUT}$ = 50 mA, $V_{BIAS}$ = 5.0 V, $T_{J}$ = -40°C to +125°C, unless otherwise noted. Typical values are at $T_{J}$ = +25°C.)                                                  |

| Symbol                             | Parameter                                                          | Test Conditions                                                                                                                                  | Min                               | Тур                                             | Max  | Unit              |

|------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------|------|-------------------|

| V <sub>IN</sub>                    | Input voltage range                                                |                                                                                                                                                  | V <sub>OUT</sub> +V <sub>DO</sub> |                                                 | 5.5  | V                 |

| V <sub>BIAS</sub>                  | Bias pin voltage range                                             |                                                                                                                                                  | V <sub>OUT</sub> + 1.4            |                                                 | 5.5  | V                 |

| UVLO                               | Undervoltage Lock-out                                              | V <sub>BIAS</sub> Rising<br>Hysteresis                                                                                                           | 1.2<br>-                          | 1.5<br>0.45                                     | 2.0  | V                 |

| V <sub>OUT</sub>                   | Accuracy                                                           | 2.4 V $\leq$ V <sub>BIAS</sub> $\leq$ 5.25 V, V <sub>OUT</sub> +<br>1.6 V $\leq$ V <sub>BIAS</sub><br>50 mA $\leq$ I <sub>OUT</sub> $\leq$ 3.0 A | -1.0                              | ±0.3                                            | +1.0 | %                 |

| V <sub>OUT</sub> /V <sub>IN</sub>  | Line regulation                                                    | $V_{OUT(NOM)} + 0.25 \le V_{IN} \le 5.5 V$                                                                                                       |                                   | 0.0006                                          |      | %/V               |

| V <sub>OUT</sub> /I <sub>OUT</sub> | Load regulation                                                    | 0 mA ≤ I <sub>OUT</sub> ≤ 50 mA                                                                                                                  |                                   | 0.005                                           |      | %/mA              |

|                                    |                                                                    | $50 \text{ mA} \le I_{OUT} \le 3.0 \text{ A}$                                                                                                    |                                   | 0.01                                            |      | %/A               |

| $V_{DO}$                           | V <sub>IN</sub> dropout voltage (Note 9)                           | I <sub>OUT</sub> = 3.0 A,<br>V <sub>BIAS</sub> – V <sub>OUT(NOM)</sub> = 1.6 V                                                                   |                                   | 105                                             | 195  | mV                |

|                                    | V <sub>BIAS</sub> dropout voltage (Note 9)                         | I <sub>OUT</sub> = 3.0 A, V <sub>IN</sub> = V <sub>BIAS</sub>                                                                                    |                                   | 1.2                                             | 1.4  | V                 |

| I <sub>CL</sub>                    | Current limit                                                      | V <sub>OUT</sub> = 80% x V <sub>OUT(NOM)</sub>                                                                                                   | 3.5                               | 4.3                                             | 7    | А                 |

| I <sub>BIAS</sub>                  | Bias pin current                                                   | 0 mA ≤ I <sub>OUT</sub> ≤ 3.0 A                                                                                                                  |                                   | 1.3                                             | 2    | mA                |

| I <sub>BSHDN</sub>                 | V <sub>BIAS</sub> shutdown current                                 | V <sub>EN</sub> ≤0.4 V                                                                                                                           |                                   | 1                                               | 15   | μA                |

| IINSHDN                            | V <sub>IN</sub> shutdown current                                   | $V_{EN} \le 0.4$ V, $V_{OUT} = 0$ V                                                                                                              |                                   | 1                                               | 15   | μA                |

| I <sub>SNS</sub>                   | Sense pin current                                                  | $0 \text{ mA} \le I_{OUT} \le 3.0 \text{ A}$                                                                                                     | -250                              | 95                                              | 250  | nA                |

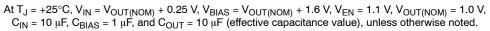

| PSRR                               | Power–supply rejection<br>(V <sub>IN</sub> to V <sub>OUT</sub> )   | 1 kHz, I <sub>OUT</sub> = 2 A,<br>V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                             |                                   | 75                                              |      | dB                |

|                                    |                                                                    | 3 MHz, I <sub>OUT</sub> = 2 A,<br>V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                             |                                   | 18                                              |      |                   |

|                                    | Power–supply rejection<br>(V <sub>BIAS</sub> to V <sub>OUT</sub> ) | 1 kHz, I <sub>OUT</sub> = 2 A,<br>V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                             |                                   | 75                                              |      | dB                |

|                                    |                                                                    | 3 MHz, I <sub>OUT</sub> = 2 A,<br>V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                                             |                                   | 18                                              |      |                   |

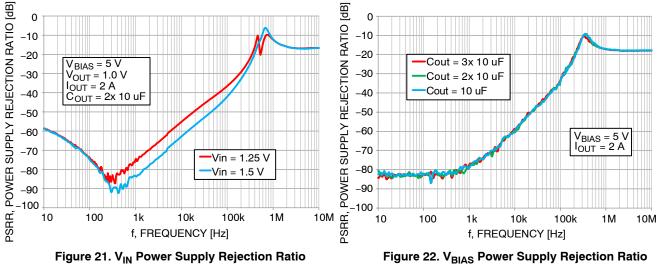

| Noise                              | Output noise voltage                                               | 10 Hz to 100 kHz, I <sub>OUT</sub> = 2 A                                                                                                         |                                   | 6                                               |      | μVrms             |

| t <sub>STRT</sub>                  | Minimum startup time                                               | I <sub>OUT</sub> = 3 A, C <sub>SS</sub> = open (Note 10)                                                                                         |                                   | 350                                             |      | μs                |

| I <sub>SS</sub>                    | Soft-start charging current                                        | V <sub>SS</sub> = 0.4 V                                                                                                                          |                                   | $6.2 \times \frac{V_{OUT(NOM)}}{0.8 \text{ V}}$ |      | μΑ                |

| VEN, HI                            | Enable input high level                                            |                                                                                                                                                  | 1.1                               |                                                 | 5.5  | V                 |

| VEN, LO                            | Enable input low level                                             |                                                                                                                                                  | 0                                 |                                                 | 0.4  | V                 |

| VEN,HYS                            | Enable pin hysteresis                                              |                                                                                                                                                  |                                   | 100                                             |      | mV                |

| Ven,dg                             | Enable pin deglitch time                                           |                                                                                                                                                  |                                   | 20                                              |      | μs                |

| I <sub>EN</sub>                    | Enable pin current                                                 | V <sub>EN</sub> = 5 V                                                                                                                            | 1                                 | 0.3                                             | 1    | μA                |

| V <sub>IT-</sub>                   | PG trip threshold                                                  | V <sub>OUT</sub> decreasing                                                                                                                      | 82                                | 88                                              | 93   | %V <sub>OUT</sub> |

| V <sub>IT+</sub>                   | PG trip threshold                                                  | V <sub>OUT</sub> increasing                                                                                                                      | 83                                | 91                                              | 96   | %V <sub>OUT</sub> |

| V <sub>HYS</sub>                   | PG trip hysteresis                                                 |                                                                                                                                                  |                                   | 3                                               |      | %V <sub>OUT</sub> |

| V <sub>PG, LO</sub>                | PG output low voltage                                              | I <sub>PG</sub> = 1 mA (sinking), V <sub>OUT</sub> < V <sub>IT</sub>                                                                             |                                   |                                                 | 0.3  | V                 |

| I <sub>PG, LKG</sub>               | PG leakage current                                                 | V <sub>PG</sub> = 5.25 V, V <sub>OUT</sub> > V <sub>IT</sub>                                                                                     |                                   | 0.03                                            | 1    | μA                |

| R <sub>AD</sub>                    | Output Active Discharge Resistance<br>(NCV59745A option only)      | V <sub>BIAS</sub> = 5.0 V, V <sub>EN</sub> = 0 V,<br>V <sub>IN</sub> = 1.25 V, V <sub>OUT</sub> = 1.0 V                                          |                                   | 600                                             |      | Ω                 |

| TSD                                | Thermal shutdown temperature                                       | Shutdown, temperature increasing<br>Reset, temperature decreasing                                                                                |                                   | +165<br>+140                                    |      | °C                |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 9. Dropout is defined as the voltage from the input to V<sub>OUT</sub> when V<sub>OUT</sub> is 3% below nominal. 10. Time from EN rising edge to 98% of V<sub>OUT(NOM)</sub>

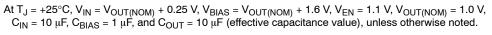

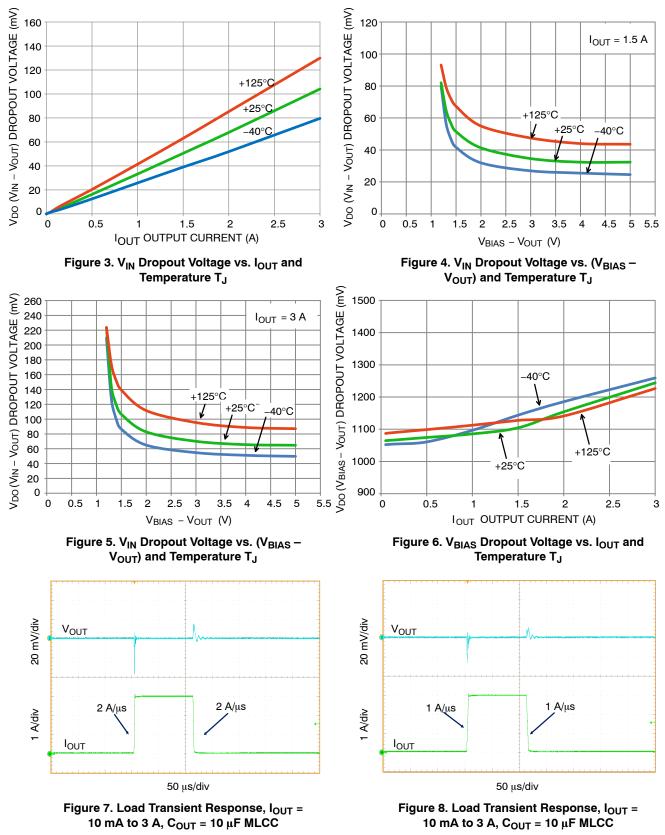

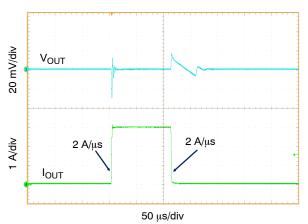

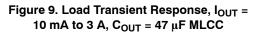

# **TYPICAL CHARACTERISTICS**

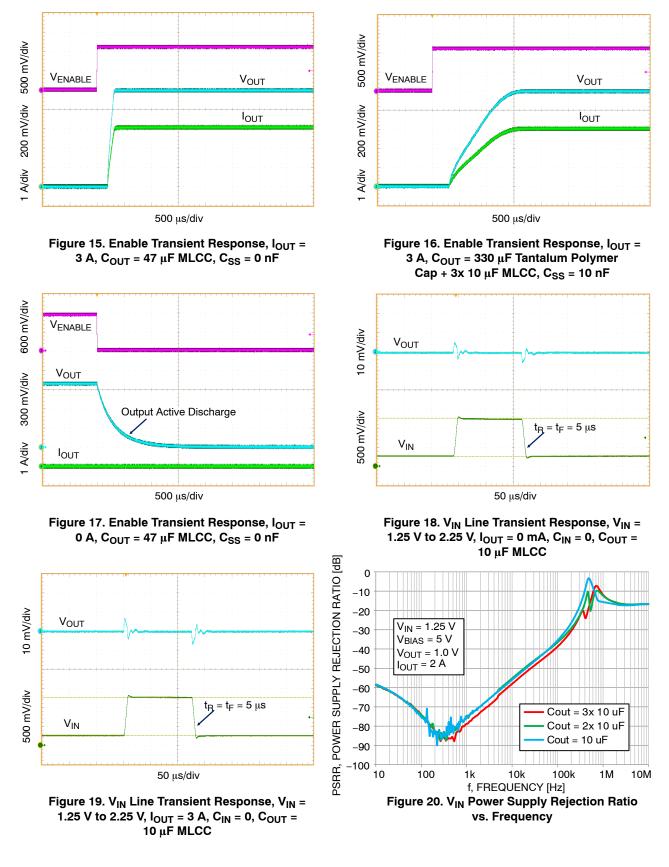

At T<sub>J</sub> = +25°C, V<sub>IN</sub> = V<sub>OUT(NOM)</sub> + 0.25 V, V<sub>BIAS</sub> = V<sub>OUT(NOM)</sub> + 1.6 V, V<sub>EN</sub> = 1.1 V, V<sub>OUT(NOM)</sub> = 1.0 V, C<sub>IN</sub> = 10  $\mu$ F, C<sub>BIAS</sub> = 1  $\mu$ F, and C<sub>OUT</sub> = 10  $\mu$ F (effective capacitance value), unless otherwise noted.

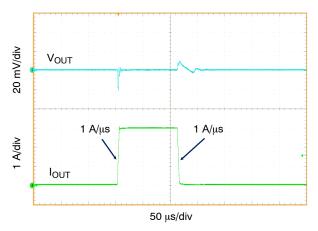

Figure 10. Load Transient Response,  $I_{OUT}$  = 10 mA to 3 A,  $C_{OUT}$  = 47  $\mu F$  MLCC

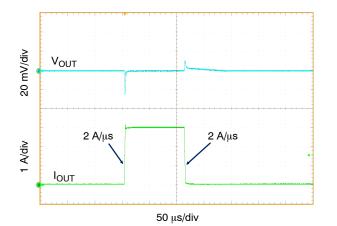

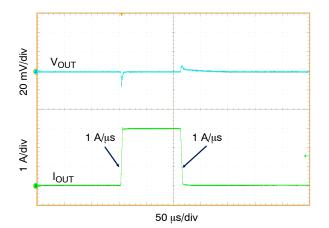

Figure 12. Load Transient Response, I<sub>OUT</sub> = 10 mA to 3 A, C<sub>OUT</sub> = 330 μF Tantalum Polymer Cap + 3x 10 μF MLCC

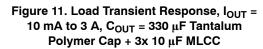

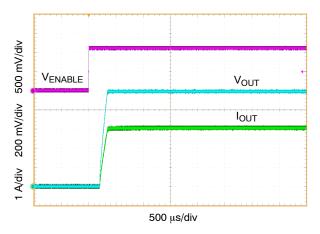

# **TYPICAL CHARACTERISTICS**

At  $T_J = +25^{\circ}C$ ,  $V_{IN} = V_{OUT(NOM)} + 0.25 V$ ,  $V_{BIAS} = V_{OUT(NOM)} + 1.6 V$ ,  $V_{EN} = 1.1 V$ ,  $V_{OUT(NOM)} = 1.0 V$ ,  $C_{IN} = 10 \mu$ F,  $C_{BIAS} = 1 \mu$ F, and  $C_{OUT} = 10 \mu$ F (effective capacitance value), unless otherwise noted.

# **TYPICAL CHARACTERISTICS**

vs. Frequency

vs. Frequency

Figure 23. Output Voltage Noise Spectral Density

#### APPLICATIONS INFORMATION

The NCV59745 very low dropout low noise dual-rail voltage regulator is using NMOS pass transistor for output voltage regulation from  $V_{IN}$  voltage. All the low current internal controll circuitry is powered from the  $V_{BIAS}$  voltage.

The use of an NMOS pass transistor offers several advantages in applications. Unlike a PMOS topology devices, the output capacitor has reduced impact on loop stability.  $V_{IN}$  to  $V_{OUT}$  operating voltage difference can be very low compared with standard PMOS regulators in very low Vin applications.

The NCV59745 offers programmable smooth monotonic start-up. The controlled voltage rising limits the inrush current what is advantageous in applications with large capacitive loads. The Voltage Controlled Soft Start time is programmable by external  $C_{\rm SS}$  capacitor value.

The Enable (EN) input is equipped with internal hysteresis and deglitch filter.

Open Drain type Power Good (PG) output is available for Vout monitoring and sequencing of other devices.

NCV59745 is a Fixed Voltage linear regulator.

#### **Dropout Voltage**

Because of two power supply inputs  $V_{IN}$  and  $V_{BIAS}$  and one  $V_{OUT}$  regulator output, there are two Dropout voltages specified.

The first, the V<sub>IN</sub> Dropout voltage is the voltage difference (V<sub>IN</sub> – V<sub>OUT</sub>) when V<sub>OUT</sub> starts to decrease by percents specified in the Electrical Characteristics table. V<sub>BIAS</sub> is high enough, specific value is published in the Electrical Characteristics table.

The second,  $V_{BIAS}$  dropout voltage is the voltage difference ( $V_{BIAS} - V_{OUT}$ ) when  $V_{IN}$  and  $V_{BIAS}$  pins are joined together and  $V_{OUT}$  starts to decrease.

#### Input and Output Capacitors

The device is designed to be stable for ceramic output capacitors with effective capacitance in the range from  $10 \ \mu\text{F}$  up to  $1000 \ \mu\text{F}$ . The device is also stable with multiple capacitors in parallel.

In applications where no low input supply impedance is available (PCB inductance in  $V_{IN}$  and/or  $V_{BIAS}$  inputs as an example) the recommended  $C_{BIAS} \ge 1 \ \mu F$  and  $C_{IN} \ge 4.7 \ \mu F$  of effective capacitance value. For the best performance all capacitors should be connected to the NCV59745 respective pins directly in the device PCB copper layer, not through vias having not negligible impedance.

#### **Enable Operation**

The enable pin will turn the regulator on or off. The threshold limits are covered in the electrical characteristics table in this data sheet. To get the full functionality of Soft Start, it is recommended to turn on the  $V_{IN}$  and  $V_{BIAS}$  supply voltages first and activate the Enable pin no sooner than  $V_{IN}$  and  $V_{BIAS}$  are on their nominal levels. If the enable function is not to be used then the pin should be connected to  $V_{IN}$  or  $V_{BIAS}$ .

#### Programmable Soft-Start

The Soft–Start time is programmable by external  $C_{SS}$  capacitor value. If  $C_{SS}$  capacitor not used, the device is starting with Minimum Start–up time specified in the Electrical Characteristics table.

The output voltage ramping time during Soft–Start depends on the Soft–Start charging current  $I_{SS}$  and Soft–Start capacitor value  $C_{SS}$ .

The Soft–Start time can be calculated using following equation:

$t_{SS} = C_{SS} \ge 0.13$

where

$t_{SS} = Soft-Start time in miliseconds$

$C_{SS}$  = Soft–Start capacitor value in nano Farads

Soft–Start time vs  $C_{SS}$  capacitor value examples can be found in the Table 6. The maximal recommended value of  $C_{SS}$  capacitor is 1  $\mu$ F.

Unlike other LDO devices with external Noise Reduction / Soft–Start capacitor, the  $C_{SS}$  capacitor value has no connection with NCV59745 noise performance. After the Soft–Start phase the SS pin voltage persists in ramping up to the  $V_{BIAS}$  supply level.

| Css    | Soft-Start Time |

|--------|-----------------|

| Open   | 0.35 ms         |

| 4.7 nF | 0.6 ms          |

| 10 nF  | 1.3 ms          |

| 47 nF  | 6 ms            |

| 100 nF | 13 ms           |

# Table 6. CAPACITOR VALUES FOR PROGRAMMING THE SOFT-START TIME

#### Output Noise

Internal Noise Reduction filter is implemented to reduce the output voltage noise. Unlike LDO devices with external noise reduction capacitor this solution is not sensitive to the external capacitor quality.

#### **Output Active Discharge**

The NCV59745A option devices are equipped with Output Active Discharge feature. When EN input level is Low and/or Thermal Shutdown is active, the Output Active Discharge transistor is On and the output voltage node  $V_{OUT}$  is pulled down to GND through a 600  $\Omega$  resistor. The C<sub>OUT</sub> output capacitor is discharged what is advantageous for applications requiring next  $V_{OUT}$  Start–Up ramping from 0 V.

#### Power Good

Power–Good (PG) is an open–drain, logic active–high output that indicates the status of the Output Voltage  $V_{OUT}$ . When  $V_{OUT}$  exceeds the PG trip threshold, the PG pin goes into a high–impedance state. When  $V_{OUT}$  is below this

threshold the pin is driven to a low-impedance state pulling the PG pin to GND. An external pull-up resistor from  $10 \text{ k}\Omega$ to  $100 \text{ k}\Omega$  should be connected from this pin to a supply up to 5.5 V. The supply voltage can be higher than the input voltage. Alternatively, the PG pin can be left floating if output monitoring is not necessary.

# **Current Limitation**

The internal Current Limitation circuitry allows the device to supply the full nominal current and surges but protects the device against Current Overload or Short.

# **Thermal Protection**

Internal thermal shutdown (TSD) circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When TSD activated, the regulator output turns off. When cooling down under the low temperature threshold, device output is activated again. This TSD feature is provided to prevent failures from accidental overheating.

# **Power Dissipation**

The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part. For reliable operation junction temperature should be limited to  $+125^{\circ}$ C.

| Device             | Output<br>Current | Output<br>Voltage | Option                     | Marking         | Wettable Flank  | Package             | Shipping <sup>†</sup> |

|--------------------|-------------------|-------------------|----------------------------|-----------------|-----------------|---------------------|-----------------------|

| NCV59745AMW100TAG  | 3.0 A             | 1.00 V            | Output Active<br>Discharge | 59745<br>V100A  | SLP<br>Step cut | QFNW20<br>(Pb-Free) | 3000 /<br>Tape & Reel |

| NCV59745AMW1015TAG | 3.0 A             | 1.015 V           | Output Active<br>Discharge | 59745<br>V1015A | SLP<br>Step cut | QFNW20<br>(Pb-Free) | 3000 /<br>Tape & Reel |

| NCV59745AMW180TAG  | 3.0 A             | 1.80 V            | Output Active<br>Discharge | 59745<br>V180A  | SLP<br>Step cut | QFNW20<br>(Pb-Free) | 3000 /<br>Tape & Reel |

| NCV59745AMW250TAG  | 3.0 A             | 2.50 V            | Output Active<br>Discharge | 59745<br>V250A  | SLP<br>Step cut | QFNW20<br>(Pb-Free) | 3000 /<br>Tape & Reel |

### Table 7. ORDERING INFORMATION

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

© Semiconductor Components Industries, LLC, 2018

rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below :

AP7363-SP-13 NCV8664CST33T3G L79M05TL-E AP7362-HA-7 PT7M8202B12TA5EX TCR3DF185,LM(CT TLF4949EJ NCP4687DH15T1G NCV8703MX30TCG LP2951CN NCV4269CPD50R2G AP7315-25W5-7 NCV47411PAAJR2G AP2111H-1.2TRG1 ZLDO1117QK50TC AZ1117ID-ADJTRG1 NCV4263-2CPD50R2G NCP706ABMX300TAG NCP114BMX075TCG MC33269T-3.5G TLE4471GXT AP7315-33SA-7 NCV4266-2CST33T3G NCP715SQ15T2G NCV8623MN-50R2G NCV563SQ18T1G NCV8664CDT33RKG NCV4299CD250R2G NCP715MX30TBG NCV8702MX25TCG TLE7270-2E NCV562SQ25T1G AP2213D-3.3TRG1 AP2202K-2.6TRE1 NCV8170BMX300TCG NCV8152MX300180TCG NCP700CMT45TBG AP7315-33W5-7 NCP154MX180300TAG AP2113AMTR-G1 NJW4104U2-33A-TE1 MP2013AGG-5-P NCV8775CDT50RKG NJM2878F3-45-TE1 S-19214B00A-V5T2U7 S-19214B50A-V5T2U7 S-19213B50A-V5T2U7 S-19214BC0A-E8T1U7\*1 S-19213B00A-V5T2U7 S-19213B33A-V5T2U7