## **ON Semiconductor**

## Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# System Basis Chip with **Integrated LIN and Voltage** Regulator

### Description

NCV7428 is a System Basis Chip (SBC) integrating functions typically found in automotive Electronic Control Units (ECUs). NCV7428 provides and monitors the low-voltage power supply for the application microcontroller and other loads and includes a LIN transceiver.

#### **Features**

- Control Logic

- Ensures safe power-up sequence and the correct reaction to different supply conditions

- Controls mode transitions including the power management and bus wakeup treatment

- · Generates reset

- 3.3 V or 5 V V<sub>OUT</sub> Supply depending on the Version from a Low-drop Voltage Regulator

- Can deliver up to 70 mA with accuracy of  $\pm 2\%$

- Supplies typically the ECU's microcontroller

- Undervoltage detector with a reset output to the supplied microcontroller

- LIN Transceiver

- ◆ LIN2.x and J2602 compliant

- TxD dominant timeout protection

- Transceiver mode controlled by dedicated input pin

- Protection and Monitoring Functions

- Thermal shutdown protection

- Load dump protection (45 V)

- LIN Bus pin protected against transients in an automotive environment

- ESD protection level for LIN and  $V_S > \pm 8 \text{ kV}$

- Wettable Flank Package for Enhanced Optical Inspection

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

### **Typical Applications**

- Automotive

- Industrial Networks

### ON Semiconductor®

www.onsemi.com

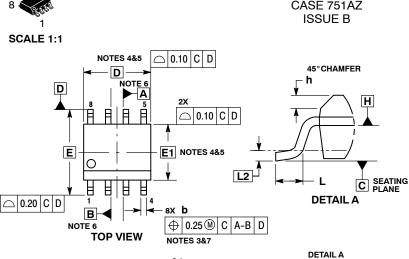

SOIC-8 **D SUFFIX** CASE 751AZ

**MW SUFFIX** CASE 506DG

### **MARKING DIAGRAMS**

Α = Assembly Location

L = Wafer Lot = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

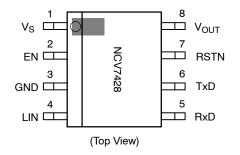

### **PIN ASSIGNMENT**

### ORDERING INFORMATION

See detailed ordering, marking and shipping information in the package dimensions section on page 17 of this data sheet.

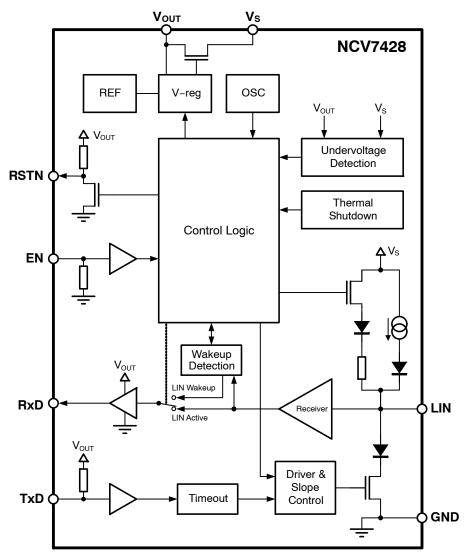

## **Block Diagram**

Figure 1. Block Diagram

**Table 1. PIN DESCRIPTION**

| Pin Number | Pin Name         | Pin Type                                           | Pin Function                                                      |

|------------|------------------|----------------------------------------------------|-------------------------------------------------------------------|

| 1          | V <sub>S</sub>   | Battery supply input                               | Principle power supply of the device                              |

| 2          | EN               | LV LIN enable input;<br>internal pull-down         | Input of the LIN block enable signal                              |

| 3          | GND              | Ground connection                                  | Ground connection                                                 |

| 4          | LIN              | LIN bus interface                                  | LIN bus line                                                      |

| 5          | RxD              | LV digital output; push-pull                       | Output of data received on LIN bus                                |

| 6          | TxD              | LV digital input; internal pull-up                 | Input of the data to be transmitted from LIN bus                  |

| 7          | RSTN             | LV digital output;<br>open drain; internal pull–up | System reset                                                      |

| 8          | V <sub>OUT</sub> | LV supply output                                   | Output of the 5 V or 3.3 V/70 mA low-drop regulator (for the MCU) |

| EP         | EP               | Exposed Pad                                        | Connect to GND or leave floating                                  |

NOTE: (LV = Low Voltage; HV = High Voltage)

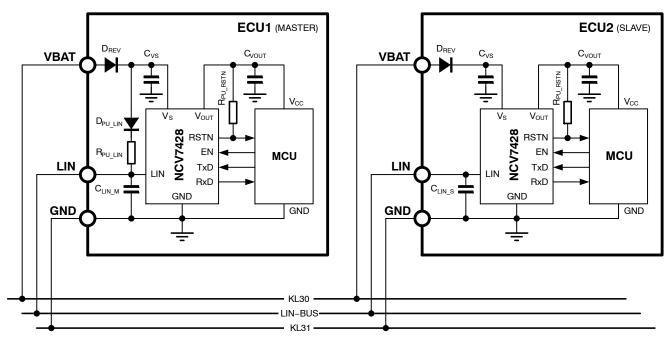

## **Application Information**

Figure 2. Example Application Diagram

### **External Components**

Overview of external components from application schematic in Figure 2 is given in Table 2 together with their recommended or required values.

**Table 2. EXTERNAL COMPONENTS OVERVIEW**

| Component<br>Name    | Description                                                       | Value                                                 | Note                                                                                          |

|----------------------|-------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| D <sub>REV</sub>     | Reverse polarity protection diode                                 | parameters application-specific;<br>e.g. 0.5 A / 50 V | required values and types<br>depend on the V <sub>OUT</sub> load<br>and the application needs |

| C <sub>VS</sub>      | Filtering capacitor for the battery input                         | recommended >100 nF ceramic                           | and the application needs                                                                     |

| C <sub>VOUT</sub>    | Voltage regulator output filtering and<br>stabilization capacitor | > 1.8 $\mu$ F, ESR < 7 $\Omega$                       |                                                                                               |

| D <sub>PU_LIN</sub>  | Master node Pull-up diode on LIN line                             |                                                       | required only for master<br>LIN node                                                          |

| R <sub>PU_LIN</sub>  | Master node Pull-up resistor on LIN line                          | 1 kΩ nominal, ≥500 mW                                 | LIN Hode                                                                                      |

| C <sub>LIN_M</sub>   | Filtering capacitor on LIN line (Master node)                     | typically 1 nF                                        | optional; is function of the entire LIN network                                               |

| C <sub>LIN_S</sub>   | Filtering capacitor on LIN line (Slave node)                      | typically 100 pF – 220 pF                             | optional; is function of the entire LIN network                                               |

| R <sub>PU_RSTN</sub> | Pull-up resistor at RSTN pin                                      | recommended 10 $k\Omega$ nominal                      | optional; depends on application needs                                                        |

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol                      | Parameter                                                                                                | Min                                       | Max                   | Units |

|-----------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|-------|

| V <sub>S</sub>              | Maximum DC voltage at V <sub>S</sub> pin                                                                 | -0.3                                      | 45                    | V     |

| V <sub>OUT</sub>            | Maximum voltage at V <sub>OUT</sub> pin                                                                  | -0.3                                      | 6                     | V     |

| V <sub>LIN</sub>            | Maximum voltage at LIN bus pin                                                                           | -45                                       | 45                    | V     |

| V <sub>Dig_IO_inputs</sub>  | Maximum voltage at digital input pins (TxD, EN)                                                          |                                           | 45                    | V     |

| V <sub>Dig_IO_outputs</sub> | Maximum voltage at digital output pins (RxD, RSTN)                                                       | -0.3                                      | V <sub>OUT</sub> +0.3 | V     |

| T <sub>AMB</sub>            | Ambient temperature range                                                                                | -40                                       | +125                  | °C    |

| TJ                          | Junction temperature range                                                                               | -40                                       | +170                  | °C    |

| T <sub>STG</sub>            | Storage temperature range                                                                                | -55                                       | +150                  | °C    |

| V <sub>ESD</sub>            | System ESD at pins VS, LIN as per IEC 61000–4–2: 330 $\Omega$ / 150 pF (Verified by external test house) | ≥ ±14                                     |                       | kV    |

|                             | Human body model at pins VS, LIN stressed towards GND with 1500 $\Omega$ / 100 pF                        |                                           | ≥ ±8                  | kV    |

|                             | Human body model at all pins as per JESD22-A114 / AEC-Q100-002                                           |                                           | ≥ ±4                  | kV    |

|                             | Charge device model at all pins as per JESD22-C101 / AEC-Q100-011                                        | 2                                         | ±500                  | V     |

|                             | Machine model; (200 pF; 0.75 $\mu$ H; 10 $\Omega$ ) as per JESD22–A115 / AEC–Q100–003                    | Ω) as per JESD22–A115 / AEC–Q100–003 ±200 |                       | V     |

| MSL                         | Moisture Sensitivity Level SOIC DFN                                                                      |                                           | 2<br>1                |       |

| T <sub>SLD</sub>            | Lead temperature Soldering - Reflow (SMD styles only), Pb-Free (Note 1)                                  |                                           | 260                   | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **Table 4. OPERATING RANGES**

| Symbol                      | Parameter                                                              | Min   | Max              | Units |

|-----------------------------|------------------------------------------------------------------------|-------|------------------|-------|

| Vs                          | VS operating voltage for parametric operation (Note 2)                 | 5.5   | 28               | V     |

|                             | VS operating voltage for limited operation (Note 2)                    | 4     | 28               | V     |

| V <sub>OUT5</sub>           | Regulated voltage at V <sub>OUT</sub> supply output for 5 V versions   | 4.9   | 5.1              | V     |

| V <sub>OUT33</sub>          | Regulated voltage at V <sub>OUT</sub> supply output for 3.3 V versions | 3.234 | 3.366            | V     |

| I <sub>VOUT</sub>           | Current delivered by the V <sub>OUT</sub> regulator                    | 70    |                  | mA    |

| $V_{LIN}$                   | Operating voltage at LIN bus pin                                       | 0     | Vs               | V     |

| V <sub>Dig_IO_inputs</sub>  | Operating voltage at digital input pins (TxD, EN)                      | 0     | 5.5              | V     |

| V <sub>Dig_IO_outputs</sub> | Operating voltage at digital output pins (RxD, RSTN)                   | 0     | V <sub>OUT</sub> | V     |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### **Table 5. THERMAL CHARACTERISTICS**

| Rating                                                                                                                                                                   | Symbol                                                 | Value     | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------|--------------|

| Thermal Characteristics, SOIC-8 (Note 3) Thermal Resistance Junction-to-Air, Free air, 1S0P PCB (Note 4) Thermal Resistance Junction-to-Air, Free air, 2S2P PCB (Note 5) | $egin{array}{l} R_{	hetaJA} \ R_{	hetaJA} \end{array}$ | 125<br>75 | °C/W<br>°C/W |

| Thermal Characteristics, DFN-8 (Note 3) Thermal Resistance Junction-to-Air, Free air, 1S0P PCB (Note 4) Thermal Resistance Junction-to-Air, Free air, 2S2P PCB (Note 5)  | $R_{	hetaJA} \ R_{	hetaJA}$                            | 133<br>55 | °C/W<br>°C/W |

- Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- 4. Values based on test board according to EIA/JEDEC Standard JESD51-3, signal layer with 10% trace coverage.

- 5. Values based on test board according to EIAJEDEC Standard JESD51-7, signal layers with 10% trace coverage for the signal layer and 4 thermal vias connected between exposed pad and first inner Cu layer.

<sup>1.</sup> For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

<sup>2.</sup> Below 5.5 V at V<sub>S</sub> pin in normal mode, the bus will either stay recessive or comply with the voltage level specifications and transition time specifications as required by SAE J2602. It is ensured by the battery monitoring circuit. Above 28 V at V<sub>S</sub> pin, LIN communication is operational (LIN pin toggling) but parameters cannot be guaranteed. For higher battery voltage operation above 28 V, LIN pull-up resistor must be selected large enough to avoid clamping of LIN pin by voltage drop over external pull-up resistor and LIN pin min current limitation.

#### **Definitions**

The characteristics defined in this section are guaranteed within the operating ranges listed in Table 4, unless stated otherwise. All voltages are referenced to GND (Pin 3). Positive currents flow into the respective pin.

**Table 6. DC CHARACTERISTICS** ( $V_S = 5.5 \text{ V}$  to 28 V;  $T_J = -40^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ ; Bus Load = 500  $\Omega$  ( $V_S$  to LIN); unless otherwise specified. Typical values are given at  $V_S = 12 \text{ V}$  and  $T_J = 25^{\circ}\text{C}$ , unless otherwise specified.)

| Symbol                         | Parameter                                                        | Conditions                                                                                                                                   | Min   | Тур  | Max   | Unit |

|--------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| SUPPLY MONITO                  | DRING                                                            |                                                                                                                                              |       |      |       |      |

| V <sub>S_PORH</sub>            | V <sub>S</sub> threshold for the power–up of the circuit         | V <sub>S</sub> rising                                                                                                                        | 3.3   |      | 4     | V    |

| V <sub>S_PORL</sub>            | V <sub>S</sub> threshold for the Shutdown of the circuit         | V <sub>S</sub> falling                                                                                                                       | 2.2   |      | 3     | V    |

| V <sub>OUT_RES_5</sub>         | V <sub>OUT</sub> monitoring threshold<br>NV7428–5                | V <sub>OUT</sub> falling                                                                                                                     | 4.55  |      | 4.75  | V    |

| V <sub>OUT_RES_33</sub>        | V <sub>OUT</sub> monitoring threshold<br>NV7428–3                | V <sub>OUT</sub> falling                                                                                                                     | 2.97  |      | 3.135 | V    |

| V <sub>OUT_RES_hys5</sub>      | V <sub>OUT</sub> monitoring threshold<br>hysteresis for NV7428–5 |                                                                                                                                              |       | 0.1  |       | V    |

| V <sub>OUT_RES_hys33</sub>     | V <sub>OUT</sub> monitoring threshold<br>hysteresis for NV7428–3 |                                                                                                                                              |       | 0.06 |       | V    |

| CURRENT CONS                   | SUMPTION                                                         |                                                                                                                                              |       |      |       |      |

| I <sub>VS_LIN_Active_rec</sub> | V <sub>S</sub> supply current                                    | LIN Active, LIN bus recessive                                                                                                                |       |      | 1.8   | mA   |

| IVS_LIN_Wakeup                 | V <sub>S</sub> supply current (Note 8)                           | Standby mode; LIN Wakeup,<br>LIN bus recessive; I <sub>VOUT</sub> = 0 mA<br>V <sub>S</sub> = 13.5 V, T <sub>J</sub> < 105°C                  |       | 25   | 33    | μΑ   |

| l <sub>VS_Sleep</sub>          | V <sub>S</sub> supply current (Note 8)                           | Sleep mode; LIN Wakeup, LIN bus recessive; $V_{OUT}$ off, $V_{OUT} < 0.5 \text{ V}$ $V_{S} = 13.5 \text{ V}$ , $T_{J} < 105^{\circ}\text{C}$ |       | 12   | 18    | μΑ   |

| V <sub>OUT</sub> REGULATO      | DR                                                               |                                                                                                                                              |       |      |       |      |

| V <sub>OUT_5</sub>             | V <sub>OUT</sub> regulator output voltage<br>(Note 6)            | $V_{OUT}$ regulator active,<br>0 < $I_{VOUT}$ < 70 mA, Static<br>regulation, $V_S$ = 5.5 V to 28 V                                           | 4.9   | 5    | 5.1   | V    |

| V <sub>OUT_33</sub>            | V <sub>OUT</sub> regulator output voltage<br>(Note 6)            | $V_{OUT}$ regulator active,<br>0 < $I_{VOUT}$ < 70 mA, Static<br>regulation, $V_S$ = 4.5 V to 28 V                                           | 3.234 | 3.3  | 3.366 | V    |

| V <sub>OUT_5</sub> _EMC        | V <sub>OUT</sub> regulator output voltage<br>under EMC (Note 8)  | DPI EMC test applied to LIN pin. No bus capacitor. SOIC8 package; (Note 7)                                                                   | 4.85  | 5    | 5.15  | V    |

| V <sub>OUT_33_EMC</sub>        | V <sub>OUT</sub> regulator output voltage<br>under EMC (Note 8)  | DPI EMC test applied to LIN pin.<br>No bus capacitor. SOIC8 package;<br>(Note 7)                                                             | 3.201 | 3.3  | 3.399 | V    |

| I <sub>LIM_VOUT</sub>          | V <sub>OUT</sub> current limitation                              | V <sub>OUT</sub> regulator active;<br>current flowing to V <sub>OUT</sub> load                                                               | 70    | 120  | 350   | mA   |

| V <sub>DROP_</sub> VOUT        | Drop-out voltage between V <sub>S</sub> and V <sub>OUT</sub>     | 5.5 V < V <sub>S</sub> < 40 V;<br>I <sub>VOUT</sub> = 70 mA                                                                                  |       |      | 0.55  | V    |

| I <sub>SINK_VOUT</sub>         | V <sub>OUT</sub> sink current                                    | V <sub>OUT</sub> regulator active, current flowing into the V <sub>OUT</sub> pin                                                             | 100   | 240  | 400   | μΑ   |

| C <sub>VOUT</sub>              | V <sub>OUT</sub> regulator filtering capacitance (Note 9)        | Equivalent series resistance < 7 $\Omega$                                                                                                    | 1.8   | 10   |       | μF   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 6. In case LIN bus capacitor of at least 82 pF is not used V<sub>OUT 5</sub> <sub>EMC</sub> and V<sub>OUT 33</sub> <sub>EMC</sub> needs to be taken into account.

7. Tested according to: LIN Conformance Test Specification Package for LIN 2.1, October 10th, 2008. Verified by external test house.

8. Values based on design and characterization. Not tested in production.

- 9. In parallel with this capacitor any other capacitor can be placed with no limit to ESR and capacitance value

- 10. The voltage drop in Normal mode between LIN and V<sub>S</sub> pin is the sum of the diode drop and the drop at serial pull-up resistor. The drop at the switch is negligible. See Figure 1.

**Table 6. DC CHARACTERISTICS** (V<sub>S</sub> = 5.5 V to 28 V;  $T_J$  = -40°C to +150°C; Bus Load = 500  $\Omega$  (V<sub>S</sub> to LIN); unless otherwise specified. Typical values are given at  $V_S = 12 \text{ V}$  and  $T_J = 25^{\circ}\text{C}$ , unless otherwise specified.)

| Symbol                        | Parameter                                     | Conditions                                                                                  | Min                  | Тур | Max   | Unit             |

|-------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|-----|-------|------------------|

| LIN TRANSMITTI                | ER                                            |                                                                                             | .1                   |     |       |                  |

| V <sub>LIN_dom_LoSup</sub>    | LIN dominant output voltage                   | TxD = Low; V <sub>S</sub> = 7.3 V                                                           |                      |     | 1.2   | V                |

| V <sub>LIN_dom_HiSup</sub>    | LIN dominant output voltage                   | TxD = Low; V <sub>S</sub> = 18 V                                                            |                      |     | 2.0   | V                |

| V <sub>LIN REC</sub>          | LIN recessive output voltage                  | TxD = High; I <sub>LIN</sub> = 10 μA (Note 10)                                              | V <sub>S</sub> – 1.5 |     | Vs    | V                |

| I <sub>LIN_lim</sub>          | Short circuit current limitation              | V <sub>LIN</sub> = V <sub>S</sub> = 18 V                                                    | 40                   |     | 200   | mA               |

| R <sub>slave</sub>            | Internal Pull-up Resistance                   | LIN Normal or Receive-only mode                                                             | 20                   | 33  | 47    | kΩ               |

| C <sub>LIN</sub>              | Capacitance at pin LIN (Note 8)               |                                                                                             |                      | 20  | 30    | pF               |

| LIN Receiver                  |                                               |                                                                                             |                      |     |       | •                |

| $V_{bus\_dom}$                | Bus voltage for Dominant state                |                                                                                             |                      |     | 0.4   | Vs               |

| V <sub>bus_rec</sub>          | Bus voltage for Recessive state               |                                                                                             | 0.6                  |     |       | Vs               |

| V <sub>rec_dom</sub>          | Receiver threshold                            | LIN bus going from Recessive to Dominant                                                    | 0.4                  |     | 0.6   | V <sub>S</sub>   |

| V <sub>rec_rec</sub>          | Receiver threshold                            | LIN bus going from Dominant to Recessive                                                    | 0.4                  |     | 0.6   | V <sub>S</sub>   |

| V <sub>rec_cnt</sub>          | Receiver center voltage                       | (V <sub>rec_dom</sub> + V <sub>rec_rec</sub> )/2                                            | 0.475                |     | 0.525 | Vs               |

| V <sub>rec_hys</sub>          | Receiver hysteresis                           | V <sub>rec_rec</sub> - V <sub>rec_dom</sub>                                                 | 0.05                 |     | 0.175 | Vs               |

| I <sub>LIN_off_dom</sub>      | LIN output current,<br>Bus in dominant state  | LIN Active Mode, Driver Off;<br>V <sub>S</sub> = 12 V, V <sub>LIN</sub> = 0 V               | -1                   |     |       | mA               |

| I <sub>LIN_off_dom_wake</sub> | LIN output current,<br>Bus in dominant state  | LIN Wakeup Mode;<br>V <sub>S</sub> = 12 V, V <sub>LIN</sub> = 0 V                           | -20                  | -15 | -2    | μΑ               |

| I <sub>LIN_off_rec</sub>      | LIN output current,<br>Bus in recessive state | Driver Off; V <sub>S</sub> < 18 V;<br>V <sub>S</sub> < V <sub>LIN</sub> < 18 V              |                      |     | 1     | μΑ               |

| I <sub>LIN_no_GND</sub>       | LIN current with missing GND                  | V <sub>S</sub> = GND = 12 V; 0 < V <sub>LIN</sub> < 18 V                                    | -1                   |     | 1     | mA               |

| I <sub>LIN_no_VBB</sub>       | LIN current with missing V <sub>S</sub>       | V <sub>S</sub> = GND = 0 V; 0 < V <sub>LIN</sub> < 18 V                                     |                      |     | 5     | μА               |

| PIN EN                        |                                               |                                                                                             |                      |     |       |                  |

| $V_{IL}EN$                    | Low-level input voltage                       |                                                                                             | -0.3                 |     | 0.8   | V                |

| V <sub>IH_EN</sub>            | High-level input voltage                      |                                                                                             | 2                    |     | 5.5   | V                |

| R <sub>pulldown_EN</sub>      | Pull-down resistance to GND                   |                                                                                             | 55                   | 100 | 185   | kΩ               |

| PIN TxD                       |                                               |                                                                                             |                      |     |       |                  |

| $V_{IL\_TxD}$                 | Low-level input voltage                       |                                                                                             | -0.3                 |     | 0.8   | V                |

| V <sub>IH_TxD</sub>           | High-level input voltage                      |                                                                                             | 2                    |     | 5.5   | V                |

| R <sub>pullup_TxD</sub>       | Pull-up resistance to V <sub>OUT</sub>        |                                                                                             | 55                   | 100 | 185   | kΩ               |

| I <sub>leak_TxD</sub>         | Leakage current                               | V <sub>TxD</sub> = V <sub>OUT</sub> = 5.5 V                                                 | -1                   | 0   | 1     | μА               |

| PIN RSTN                      |                                               |                                                                                             |                      |     |       |                  |

| I <sub>OL_RSTN</sub>          | Low-level output driving current              | V <sub>S</sub> = 4 V to 28 V; V <sub>RSTN</sub> = 0.4 V                                     | 4                    |     | 30    | mA               |

| V <sub>OL_RSTN</sub>          | Low-level output voltage                      | V <sub>S</sub> = 2 V to 4 V; V <sub>OUT</sub> = 0 V to<br>5.5 V; I <sub>RSTN</sub> = 100 μA |                      |     | 0.1   | V <sub>OUT</sub> |

|                               |                                               | $V_S$ < 2 V; $V_{OUT}$ = 1 V to 5.5 V; $I_{RSTN}$ = 100 $\mu A$                             |                      |     | 0.1   | V <sub>OUT</sub> |

| R <sub>pullup_RSTN</sub>      | Pull-up resistance to V <sub>OUT</sub>        |                                                                                             | 55                   | 100 | 185   | kΩ               |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. In case LIN bus capacitor of at least 82 pF is not used V<sub>OUT 5 EMC</sub> and V<sub>OUT 33 EMC</sub> needs to be taken into account.

7. Tested according to: LIN Conformance Test Specification Package for LIN 2.1, October 10th, 2008. Verified by external test house.

8. Values based on design and characterization. Not tested in production.

- 9. In parallel with this capacitor any other capacitor can be placed with no limit to ESR and capacitance value

- 10. The voltage drop in Normal mode between LIN and V<sub>S</sub> pin is the sum of the diode drop and the drop at serial pull-up resistor. The drop at the switch is negligible. See Figure 1.

**Table 6. DC CHARACTERISTICS** (V<sub>S</sub> = 5.5 V to 28 V;  $T_J$  = -40°C to +150°C; Bus Load = 500  $\Omega$  (V<sub>S</sub> to LIN); unless otherwise specified. Typical values are given at  $V_S = 12 \text{ V}$  and  $T_J = 25^{\circ}\text{C}$ , unless otherwise specified.)

| Symbol                    | Parameter                                               | Conditions                                                         | Min | Тур | Max   | Unit |

|---------------------------|---------------------------------------------------------|--------------------------------------------------------------------|-----|-----|-------|------|

| PIN RSTN                  |                                                         |                                                                    |     |     |       |      |

| V <sub>S_DigOut_Low</sub> | V <sub>S</sub> level guaranteeing Low level at RSTN pin | Shutdown mode; Low level guaranteed for $V_S > V_{S\_DigOut\_Low}$ |     |     | 2     | V    |

| PIN RxD                   |                                                         |                                                                    |     |     |       |      |

| I <sub>OL_RXD</sub>       | Low-level output driving current                        | V <sub>RxD</sub> = 0.4 V                                           | 0.4 |     |       | mA   |

| I <sub>OH_RXD</sub>       | High-level output driving current                       | V <sub>RXD</sub> = V <sub>OUT</sub> - 0.4 V                        |     |     | -0.16 | mA   |

| THERMAL SHUT              | rdown .                                                 |                                                                    |     |     |       |      |

| T <sub>J_SD</sub>         | Junction temperature for ther-<br>mal Shutdown          |                                                                    | 160 | 180 | 200   | °C   |

| T <sub>J SD hys</sub>     | Thermal Shutdown hysteresis                             |                                                                    |     | 10  |       | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 6. In case LIN bus capacitor of at least 82 pF is not used V<sub>OUT 5 EMC</sub> and V<sub>OUT 33 EMC</sub> needs to be taken into account.

7. Tested according to: LIN Conformance Test Specification Package for LIN 2.1, October 10th, 2008. Verified by external test house.

- 8. Values based on design and characterization. Not tested in production.

- 9. In parallel with this capacitor any other capacitor can be placed with no limit to ESR and capacitance value

- 10. The voltage drop in Normal mode between LIN and V<sub>S</sub> pin is the sum of the diode drop and the drop at serial pull-up resistor. The drop at the switch is negligible. See Figure 1.

**Table 7. AC CHARACTERISTICS** ( $V_S = 5.5 \text{ V}$  to 28 V;  $T_J = -40^{\circ}\text{C}$  to +150°C; unless otherwise specified. For the transmitter parameters, the following bus loads are considered: L1 = 1 k $\Omega$  / 1 nF; L2 = 660  $\Omega$  / 6.8 nF; L3 = 500  $\Omega$  / 10 nF)

| Symbol                     | Parameter                                                          | Conditions                                                                                                                                                                           | Min   | Тур | Max   | Unit |

|----------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| LIN TRANSMITTER            |                                                                    |                                                                                                                                                                                      |       |     |       |      |

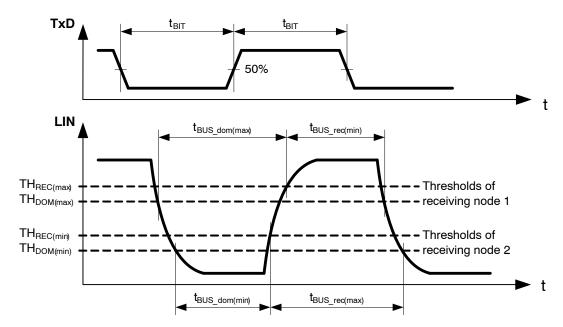

| D1                         | Duty Cycle 1 = t <sub>BUS_REC(min)</sub> / (2 x t <sub>BIT</sub> ) | $\begin{array}{l} TH_{REC(max)} = 0.744 \text{ x V}_{S} \\ TH_{DOM(max)} = 0.581 \text{ x V}_{S} \\ t_{BIT} = 50  \mu s \\ V_{S} = 7 \text{ V to } 18 \text{ V} \end{array}$         | 0.396 |     | 0.5   |      |

| D2                         | Duty Cycle 2 = t <sub>BUS_REC(max)</sub> / (2 x t <sub>BIT</sub> ) | $\begin{array}{c} TH_{REC(min)} = 0.422 \text{ x V}_S \\ TH_{DOM(min)} = 0.284 \text{ x V}_S \\ t_{BIT} = 50  \mu\text{s} \\ V_S = 7.6 \text{ V to } 18 \text{ V} \end{array}$       | 0.5   |     | 0.581 |      |

| D3                         | Duty Cycle 3 = t <sub>BUS_REC(min)</sub> / (2 x t <sub>BIT</sub> ) | $\begin{array}{c} TH_{REC(max)} = 0.778 \ x \ V_S \\ TH_{DOM(max)} = 0.616 \ x \ V_S \\ t_{BIT} = 96 \ \mu s \\ V_S = 7 \ V \ to \ 18 \ V \end{array}$                               | 0.417 |     | 0.5   |      |

| D4                         | Duty Cycle 4 = t <sub>BUS_REC(max)</sub> / (2 x t <sub>BIT</sub> ) | $\begin{array}{l} TH_{REC(min)} = 0.389 \text{ x V}_{S} \\ TH_{DOM(min)} = 0.251 \text{ x V}_{S} \\ t_{BIT} = 96  \mu\text{s} \\ V_{S} = 7.6 \text{ V to } 18 \text{ V} \end{array}$ | 0.5   |     | 0.590 |      |

| t <sub>fallNS</sub>        | LIN falling edge normal slope                                      | Normal Mode; V <sub>S</sub> = 12 V                                                                                                                                                   |       |     | 22.5  | μs   |

| t <sub>riseNS</sub>        | LIN rising edge normal slope                                       | Normal Mode; V <sub>S</sub> = 12 V                                                                                                                                                   |       |     | 22.5  | μs   |

| t <sub>symNS</sub>         | LIN slope symmetry normal slope                                    | Normal Mode; V <sub>S</sub> = 12 V                                                                                                                                                   | -4    | 0   | 4     | μs   |

| t <sub>fallLS</sub>        | LIN falling edge low slope (Note 12)                               | Normal Mode; V <sub>S</sub> = 12 V                                                                                                                                                   |       |     | 45    | μs   |

| t <sub>riseLS</sub>        | LIN rising edge low slope (Note 12)                                | Normal Mode; V <sub>S</sub> = 12 V                                                                                                                                                   |       |     | 45    | μs   |

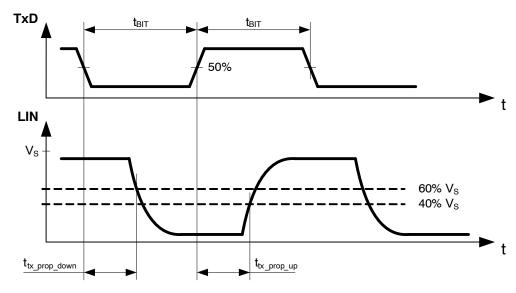

| t <sub>tx_prop_down</sub>  | Propagation Delay of TxD to LIN.<br>TxD high to low                | (Note 11)                                                                                                                                                                            |       |     | 10    | μs   |

| t <sub>tx_prop_up</sub>    | Propagation Delay of TxD to LIN.<br>TxD low to high                | (Note 11)                                                                                                                                                                            |       |     | 10    | μs   |

| t <sub>TxD_timeout</sub>   | TxD dominant timeout                                               | TxD = Low; LIN dominant timeout enabled                                                                                                                                              | 9     | 13  | 24    | ms   |

| LIN RECEIVER               |                                                                    |                                                                                                                                                                                      |       |     | •     |      |

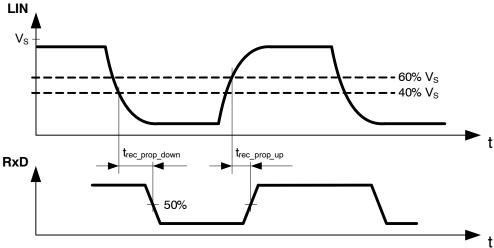

| t <sub>rec_prop_down</sub> | Propagation delay of receiver falling edge                         |                                                                                                                                                                                      | 0.1   |     | 6     | μs   |

| t <sub>rec_prop_up</sub>   | Propagation delay of receiver rising edge                          |                                                                                                                                                                                      | 0.1   |     | 6     | μs   |

| t <sub>rec_sym</sub>       | Propagation delay symmetry                                         | t <sub>rec_prop_down</sub> -<br>t <sub>rec_prop_up</sub>                                                                                                                             | -2    |     | 2     | μs   |

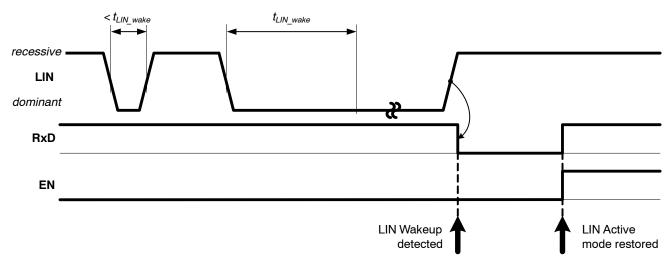

| t <sub>LIN_wake</sub>      | Dominant duration for wakeup                                       | LIN in wakeup mode                                                                                                                                                                   | 30    | 80  | 150   | μs   |

| MODE TRANSITION            | IS AND TIMEOUTS                                                    |                                                                                                                                                                                      |       |     |       |      |

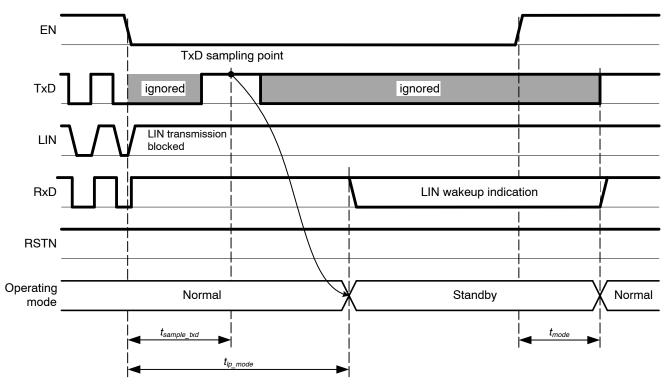

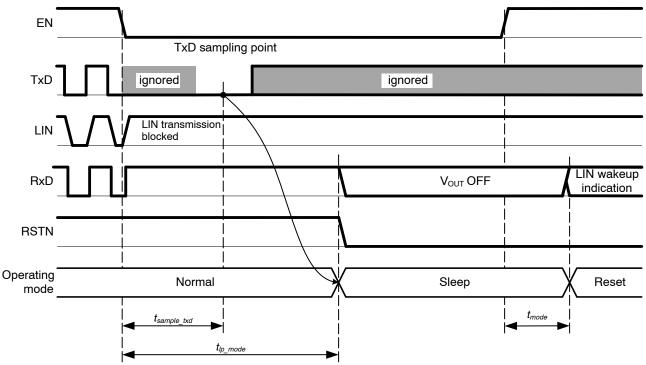

| t <sub>sample_txd</sub>    | Low power mode entry EN to TxD sampling point delay                | Normal mode:<br>Figure 9, Figure 10                                                                                                                                                  | 13    | 25  | 55    | μs   |

| t <sub>mode</sub>          | Normal mode or Reset mode transition time                          | Low power mode:<br>Figure 9, Figure 10                                                                                                                                               | 13    | 25  | 55    | μs   |

| t <sub>lp_mode</sub>       | Low power mode transition time (Standby or Sleep)                  | Normal mode:<br>Figure 9, Figure 10                                                                                                                                                  | 27    | 45  | 91    | μs   |

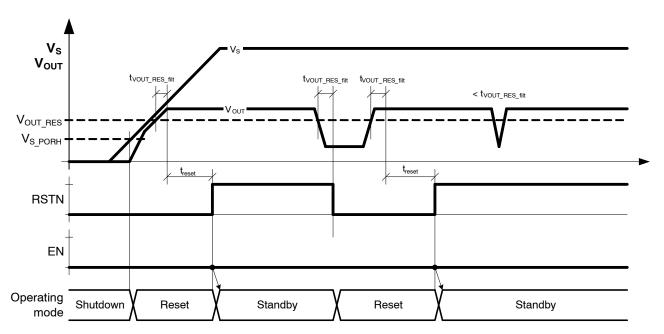

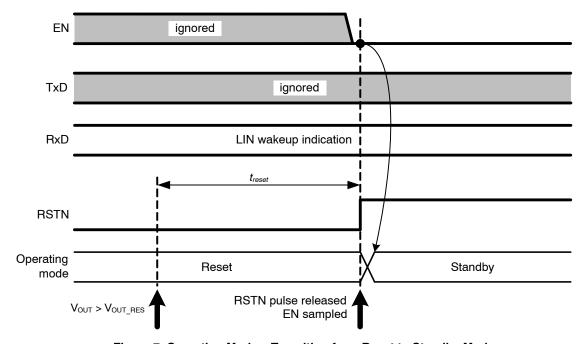

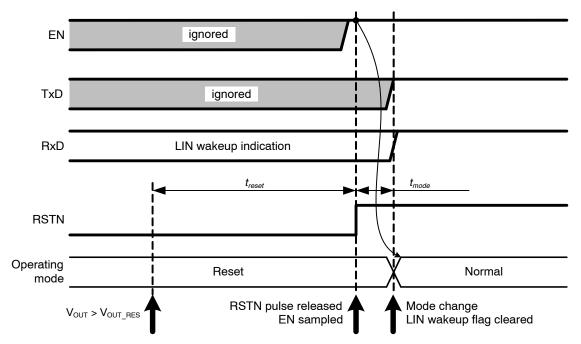

| t <sub>reset</sub>         | RSTN pulse extension                                               | Figure 6, Figure 7, Figure 8                                                                                                                                                         | 3     | 5   | 10    | ms   |

| t <sub>VOUT_RES_filt</sub> | Undervoltage detection filter time                                 | Figure 6                                                                                                                                                                             | 13    | 25  | 55    | μS   |

<sup>11.</sup> Values based on design and characterization. Not tested in production.

<sup>12.</sup> For low slope versions only (NV7428L5 and NV7428L3)

### **Functional Description**

### **VS Supply Input**

$V_S$  pin of NCV7428 is typically connected to the car battery through a reverse–protection diode and can be exposed to all relevant automotive disturbances (ISO7637 pulses, system ESD ...).  $V_S$  supplies mainly the integrated LIN transceiver. Filtering capacitors should be connected between  $V_S$  and GND.

During power–up of the battery supply,  $V_S$  pin must reach  $V_{S\_PORH}$  level in order for the circuit to become functional – the internal state machine is initiated and the  $V_{OUT}$  regulator is activated. The circuit remains functional until  $V_S$  falls back below  $V_{S\_PORL}$  level, when the device enters the Shutdown mode.

### **VOUT Low-drop Voltage Regulator**

The application low–voltage supply is provided by an integrated low–drop voltage regulator delivering a 5 V or 3.3 V output  $V_{OUT}$ . It is able to deliver up to 70 mA with given precision and is primarily intended to supply the application microcontroller unit (MCU) and related 5 V or 3.3 V loads (e.g. its own MCU–related digital inputs/outputs). An external capacitor needs to be connected on  $V_{OUT}$  pin in order to ensure the regulator's stability and to filter the disturbances caused by the connected loads.

All low-voltage digital pins are related to V<sub>OUT</sub>.

#### **LIN Transceiver**

NCV7428 integrates on-chip LIN transceiver interface between physical LIN bus and the LIN protocol controller.

This LIN physical layer is compatible to LIN2.x and J2602 specifications.

NCV7428 LIN2.2 compliant physical layer can be combined on the network with all previous LIN physical layers.

NCV7428 LIN transceiver consists of a transmitter, receiver and wakeup detector. The LIN transceiver can be connected to the bus line via LIN pin, and to the digital control through pins TxD and RxD. The functional mode of the LIN transceiver depends on the operating mode and on EN pin state – see Figure 3. The LIN transceiver is supplied directly from the  $V_S$  pin.

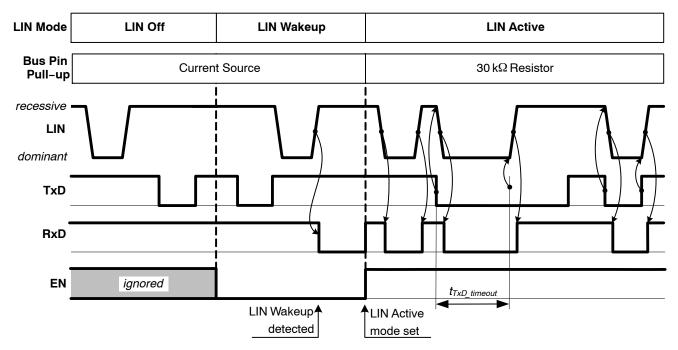

### **LIN Operating Modes**

In **LIN Active mode** the transceiver can transmit and receive data via LIN bus with speed up to 20 kBaud for normal slope mode and 10 kBaud/s for low slope version. The transmit data stream of the LIN protocol is present on the TxD pin and converted by the transmitter into a LIN bus signal with controlled slew rate to minimize EMC emission. The receiver consists of the comparator that has a threshold with hysteresis in respect to the supply voltage and an input filter to remove bus noise. The LIN output is pulled HIGH via an internal pull–up resistor (typ. 30 k $\Omega$ ). For master applications, it is needed to put an external resistor (typ.  $1 \text{ k}\Omega$ ) with a serial diode between LIN and  $V_S$ . The mode selection is done by EN = High.

The transmission is only initiated with the TxD falling edge in LIN Active mode. Entering this mode with TxD already Low will not lead to transmitting bus Dominant signal.

When leaving Normal mode (EN pin falling edge), the transmitter is deactivated immediately.

The LIN Wakeup mode can be entered if the EN pin is Low. The LIN receiver stays active to be able to detect a remote wake-up via bus. The LIN transmitter is disabled and the slave internal termination resistor of 30 k $\Omega$  between LIN and  $V_S$  is disconnected in order to minimize current consumption. Only a pull-up current source between Vs and LIN is active. The valid LIN wakeup event causes driving RxD Low until EN pin is pulled High.

A Wakeup pattern that is initiated in LIN Active mode and ends in LIN Wakeup mode is also considered a valid Wakeup event.

The LIN Wakeup mode is also forced if the device enters to the Sleep operating mode.

The **LIN Off mode** provides extreme low current consumption, LIN transceiver is fully deactivated. Pin RxD stays High (as long as V<sub>OUT</sub> is provided) and logical level on TxD is ignored.

The bus pin is internally pulled to  $V_S$  with a current source (thus limiting  $V_S$  consumption in case of a permanent LIN short to GND).

This mode is entered when NCV7428 is in Shutdown mode ( $V_S < V_{S\_PORL}$ ) or in Thermal Shutdown mode ( $T_J > T_{J-SD}$ ).

Figure 3. LIN Modes

Figure 4. LIN Wakeup Detection

### **Operating Modes**

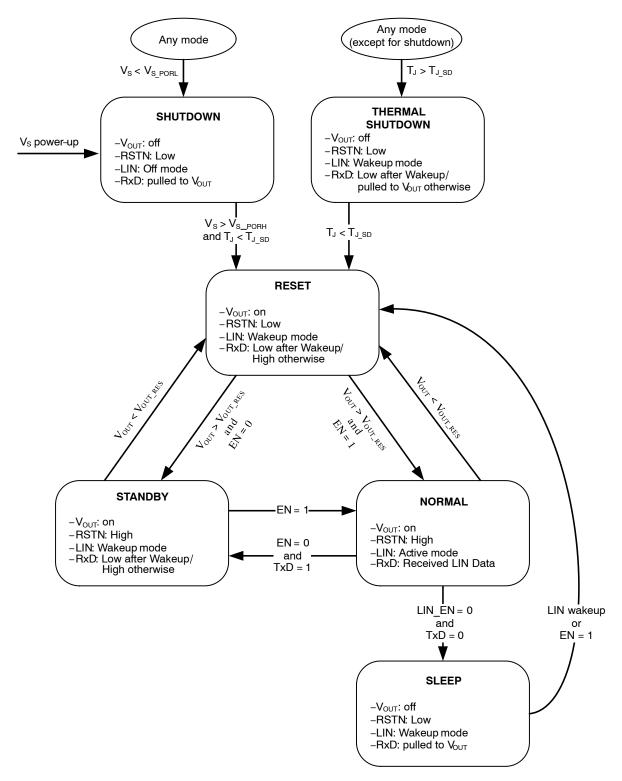

The principal operating modes of NCV7428 are shown in Figure 5 and described in the following paragraphs.

Figure 5. Operating Modes

#### **Shutdown Mode**

The Shutdown mode is a passive state, in which all NCV7428 resources are inactive. The Shutdown mode provides a defined starting point for the circuit in case of supply undervoltage, thermal Shutdown or the first supply connection.

On-chip power-supply  $V_{OUT}$  is switched off and the LIN pin remains passive so that it does not disturb the communication of other nodes connected to the LIN bus. RxD pin stays pulled to  $V_{OUT}$ . No wakeups can be detected.

RSTN pin is forced Low – RSTN Low level is guaranteed for  $V_S$  supply above  $V_{S\ DigOut\ Low}$ .

The Shutdown mode is entered asynchronously whenever the  $V_S$  level falls below the power-on-reset level  $V_{SPORL}$ .

The Shutdown mode is left only when the  $V_S$  supply exceeds the high power-on-reset level  $V_{S\_PORH}$  while junction temperature is below  $T_{J\_SD}$ . When exiting the Shutdown mode, NCV7428 always enters the Reset mode.

#### **RESET Mode**

The Reset mode is a transient mode providing a defined RSTN pulse for the application microcontroller.

$V_{OUT}$  supply is kept active. The LIN pin is passive so that it does not disturb the communication of other nodes connected to the bus. RxD pin is High if no wakeup was detected, RxD Low level indicates pending LIN wakeup. Pin RSTN is forced Low.

Reset mode will be entered as a consequence of one of the following events:

- Shutdown mode is exited

- Thermal Shutdown mode is exited

- V<sub>OUT</sub> voltage falls below V<sub>OUT RES</sub> level

- LIN wakeup or EN = High was detected in Sleep mode Normally, the Reset mode is left when V<sub>OUT</sub> voltage is above V<sub>OUT\_RES</sub> threshold and defined time t<sub>reset</sub> elapses.

The RSTN pin is internally released to High and the chip then goes to the Normal or Standby mode, depending on EN state.

### **Normal Mode**

Normal mode is entered from Standby mode after a host request – driving EN pin High (Figure 9), or if EN pin is

High when leaving Reset mode -  $t_{reset}$  time elapsed (Figure 8).

LIN transceiver is in Active mode.  $V_{OUT}$  is kept on. Pin RSTN remains High.

### **Standby Mode**

Standby mode is entered from Normal mode after host request – EN pin falling edge followed by TxD pin High. TxD is sampled  $t_{sample\_txd}$  after EN edge (Figure 9). Standby mode is also entered if EN pin is Low when leaving Reset mode –  $t_{reset}$  time elapsed (Figure 7).

LIN transceiver is in Wakeup mode – RxD pin is latched Low after valid Wakeup recognition until Normal mode is requested. V<sub>OUT</sub> is kept active. Pin RSTN remains High.

### Sleep Mode

Sleep mode can be only entered from Normal mode after a host request – EN pin falling edge followed by TxD pin Low. LIN transmitter is blocked immediately after EN pin falling edge, therefor TxD pin and EN pin can be set Low at the same moment. TxD is sampled t<sub>sample\_txd</sub> after EN pin edge (Figure 10).

V<sub>OUT</sub> regulator is switched off, LIN transceiver is in the Wakeup mode.

If LIN wakeup is detected or EN goes High, Reset mode is entered. LIN wakeup is signaled by RxD, which remains Low until Normal mode is restored (EN is High).

#### **Thermal Shutdown**

The device junction temperature is monitored in order to avoid permanent degradation or damage of the chip. Junction temperature exceeding the Shutdown level  $T_{J\_SD}$  puts the chip into Thermal Shutdown mode.

In Thermal Shutdown mode,  $V_{OUT}$  regulator is switched off. LIN transceiver is in Wakeup mode and can detect bus Wakeup. RxD pin stays pulled to  $V_{OUT}$  or is driven Low after valid Wakeup recognition. RSTN pin is pulled low. The mode is automatically left only when the junction cools down below the  $T_{J\ SD}$  threshold.

Figure 6. V<sub>OUT</sub> Regulator Voltage Monitoring

Figure 7. Operating Modes, Transition from Reset to Standby Mode

Figure 8. Operating Modes, Transition from Reset to Normal Mode

Figure 9. Operating Modes, Transition from Normal to Standby Mode

Figure 10. Operating Modes, Transition from Normal to Sleep Mode

Figure 11. Definition of LIN Duty Cycle Parameters

Figure 12. Definition of LIN Edge Parameters

Figure 13. Definition of LIN Transmitter Timing Parameters

Figure 14. Definition of LIN Receiver Timing Parameters

### **ORDERING INFORMATION**

| Part Number    | Description                                          | Marking  | Package                              | Shipping <sup>†</sup> |

|----------------|------------------------------------------------------|----------|--------------------------------------|-----------------------|

| NCV7428D15R2G  | LIN transceiver with 5 V regulator                   | NV7428-5 |                                      |                       |

| NCV7428D13R2G  | LIN transceiver with 3.3 V regulator                 | NV7428-3 | 1                                    |                       |

| NCV7428D1L5R2G | LIN transceiver with 5 V regulator,<br>low slope LIN | NV7428L5 | SOIC-8<br>(Pb-Free)                  | 3000 / Tape & Reel    |

| NCV7428D1L3R2G | LIN transceiver with 3.3 V regulator, low slope LIN  | NV7428L3 |                                      |                       |

| NCV7428MW5R2G  | LIN transceiver with 5 V regulator                   | NV7428-5 |                                      |                       |

| NCV7428MW3R2G  | LIN transceiver with 3.3 V regulator                 | NV7428-3 | DENIO                                |                       |

| NCV7428MWL5R2G | LIN transceiver with 5 V regulator,<br>low slope LIN | NV7428L5 | DFN8<br>Wettable Flanks<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCV7428MWL3R2G | LIN transceiver with 3.3 V regulator, low slope LIN  | NV7428L3 |                                      |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

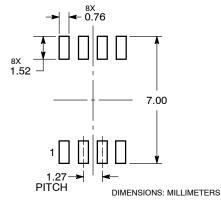

### RECOMMENDED **SOLDERING FOOTPRINT\***

**BOTTOM VIEW**

e/2

е

8X **b**

Ф

0.10 | C | A | B

0.05 C NOTE 3

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

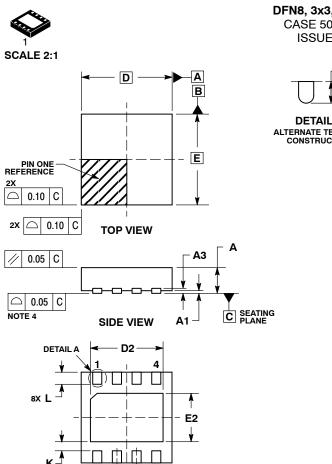

### DFN8, 3x3, 0.65P CASE 506DG **ISSUE A**

DFTΔII Δ ALTERNATE TERMINAL CONSTRUCTION

#### **DATE 28 APR 2016**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND

- 0.30mm FROM THE TERMINAL TIP.

COPLANARITY APPLIES TO THE EXPOSED

PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 0.80        | 1.00 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| A3  | 0.20 REF    |      |  |  |

| b   | 0.25        | 0.35 |  |  |

| D   | 3.00        | BSC  |  |  |

| D2  | 2.30        | 2.50 |  |  |

| E   | 3.00        | BSC  |  |  |

| E2  | 1.50        | 1.70 |  |  |

| е   | 0.65 BSC    |      |  |  |

| K   | 0.30        | TYP  |  |  |

|     | 0.35        | 0.45 |  |  |

### **GENERIC** MARKING DIAGRAM\*

XXXXXX= Specific Device Code

= Assembly Location

= Wafer Lot L Υ = Year = Work Week W

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking.

Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98AON10527G     | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | DFN8 3X3, 0.65P |                                                                                                                                                                                   | PAGE 1 OF 1 |  |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

Α1

NOTE 8

0.10 C

SEATING С

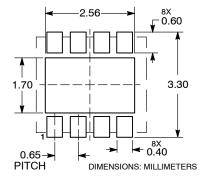

SOIC-8 CASE 751AZ

**DATE 18 MAY 2015**

#### NOTES:

NOTE 7

C

**END VIEW**

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2

- CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.004 mm IN EXCESS OF MAXIMUM MATERIAL CONDITION.

- DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006 mm PER SIDE. DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.010 mm PER SIDE.

- THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM. DIMENSIONS D AND E1 ARE DETERMINED AT THE OUTER-MOST EXTREMES OF THE PLASTIC BODY AT DATUM H. DIMENSIONS A AND B ARE TO BE DETERMINED AT DATUM H.

- DIMENSIONS b AND c APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 TO 0.25 FROM THE LEAD TIP.

- A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | i           | 1.75 |  |

| A1  | 0.10        | 0.25 |  |

| A2  | 1.25        |      |  |

| b   | 0.31        | 0.51 |  |

| С   | 0.10        | 0.25 |  |

| D   | 4.90 BSC    |      |  |

| E   | 6.00 BSC    |      |  |

| E1  | 3.90 BSC    |      |  |

| е   | 1.27 BSC    |      |  |

| h   | 0.25        | 0.41 |  |

| L   | 0.40        | 1.27 |  |

| L2  | 0.25 BSC    |      |  |

### **RECOMMENDED SOLDERING FOOTPRINT\***

**SIDE VIEW**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **GENERIC** MARKING DIAGRAM\*

XXXXX = Specific Device Code

= Assembly Location Α

= Wafer Lot L Υ = Year

W = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G", may or not be present.

| DOCUMENT NUMBER: | 98AON34918E | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8      |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LDO Voltage Regulators category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

AP7363-SP-13 L79M05TL-E PT7M8202B12TA5EX TCR3DF185,LM(CT TCR3DF24,LM(CT TCR3DF285,LM(CT TCR3DF31,LM(CT TCR3DF31,LM(CT TCR3DF45,LM(CT MP2013GQ-33-Z 059985X NCP4687DH15T1G 701326R TCR2EN28,LF(S NCV8170AXV250T2G TCR3DF27,LM(CT TCR3DF19,LM(CT TCR3DF125,LM(CT TCR2EN18,LF(S AP2112R5A-3.3TRG1 AP7315-25W5-7 IFX30081LDVGRNXUMA1 NCV47411PAAJR2G AP2113KTR-G1 AP2111H-1.2TRG1 ZLDO1117QK50TC AZ1117IH-1.8TRG1 AZ1117ID-ADJTRG1 TCR3DG12,LF MIC5514-3.3YMT-T5 MIC5512-1.2YMT-T5 MIC5317-2.8YM5-T5 SCD7912BTG NCP154MX180270TAG SCD33269T-5.0G NCV8170BMX330TCG NCV8170AMX120TCG NCP706ABMX300TAG NCP153MX330180TCG NCP114BMX075TCG MC33269T-3.5G CAT6243-ADJCMT5T TCR3DG33,LF AP2127N-1.0TRG1 TCR4DG35,LF LT1117CST-3.3 LT1117CST-5 TAR5S15U(TE85L,F) TAR5S18U(TE85L,F) TCR3UG19A,LF TCR4DG105,LF