# 12 Channels 60 mA LED Linear Current Driver I<sup>2</sup>C Controllable for Automotive Applications

# **NCV7685**

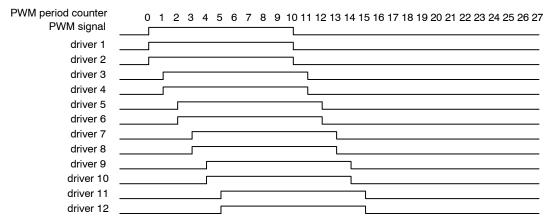

The NCV7685 consists of twelve linear programmable constant current sources with common reference. The part is designed for use in the regulation and control of LED for automotive applications. The NCV7685 allows 128 different duty cycle levels adjustable using pulse width modulation (PWM) independently for each output channel programmable via I<sup>2</sup>C serial interface. PWM frequency can be chosen in four different configurations up to 1200 Hz. The device can be used with micro–controller applications using the I<sup>2</sup>C bus or in stand–alone applications where a choice could be done in between 2 different static configuration settings. The IC also provides 3.3 V voltage reference to the application for loads up to 1 mA.

LED brightness level is easily programmed using an external resistor. Each channel has an internal circuitry to detect open-load conditions with an optional auto-recovery mode. If one driver is in open-load condition, all other channels could be turned off according to the programmable bit setting.

The device is available in small body size SSOP24-EP package.

# **Features**

- 12 Common Current Programmable Sources up to 60 mA

- Independent PWM Duty Cycle Control for each Channel via PC

- Common PWM Duty Cycle Control via I<sup>2</sup>C

- On-Chip 150, 300, 600 and 1200 Hz PWM

- Open LED String Diagnostics

- Low Dropout Operation for Pre-Regulator Applications

- Single Resistor for Current Set Point

- Voltage Reference 3.3 V/1 mA

- 8 Bits I<sup>2</sup>C Interface with CRC8 Error Detection

- OTP Bank for Stand-Alone Operation (2 Configurations)

- Output Enable Pin

- Detection and Protection Against Open Load and Under-Voltage

- Over Temperature Detection and Protection

- Low Emission with Spread Spectrum Oscillator

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- SSOP24–EP Packaging

# **Applications**

- Dashboard Applications

- Rear Combination Lamps (RCL)

- Daytime Running Lights (DRL)

- Fog Lights

- Center High Mounted Stop Lamps (CHMSL) Arrays

- Turn Signal and Other Externally Modulated Applications

# ON Semiconductor®

www.onsemi.com

SSOP24-NB EP CASE 940AQ

# **MARKING DIAGRAM**

NCV7685 AWLYYWW O •

NCV7685 = Specific Device Code

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

Pb-Free Package

(Note: Microdot may be in either location)

# **ORDERING INFORMATION**

| Device       | Package                | Shipping†            |  |  |

|--------------|------------------------|----------------------|--|--|

| NCV7685DQR2G | SSOP24-EP<br>(Pb-Free) | 2500/<br>Tape & Reel |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

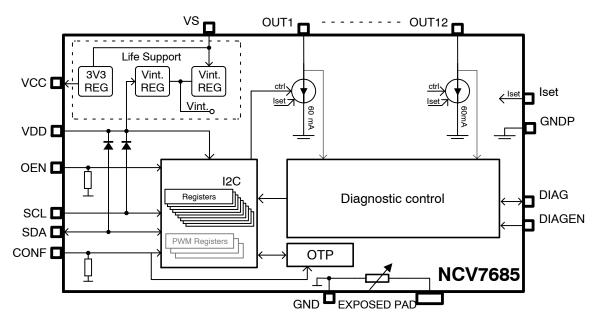

Figure 1. Block Diagram

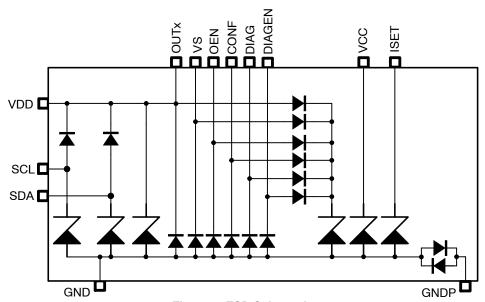

Figure 2. ESD Schematic

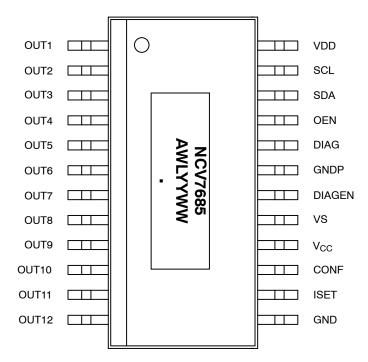

Figure 3. Pinout Diagram

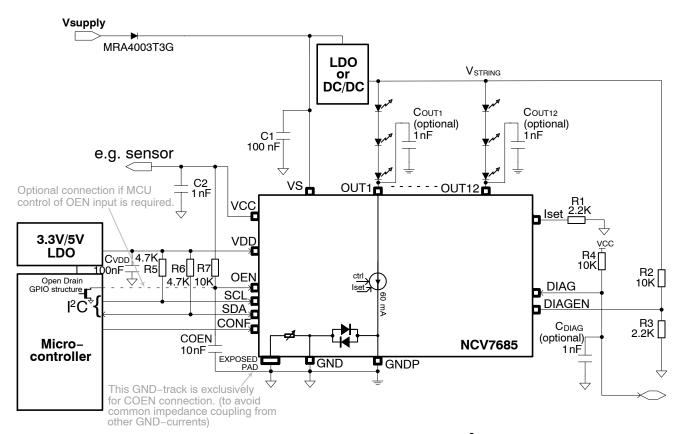

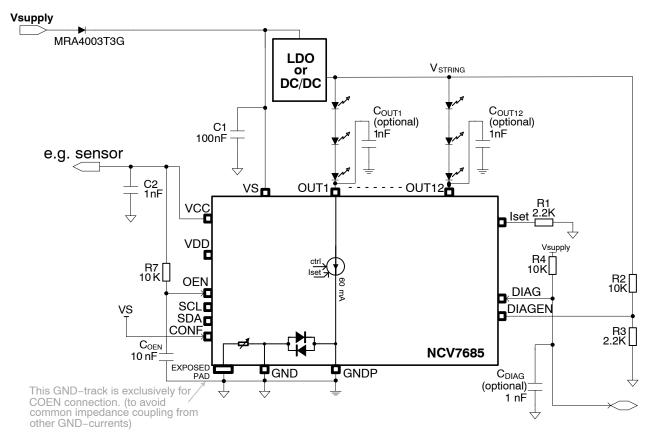

Figure 4. Application Diagram with Micro-controller (I<sup>2</sup>C Mode)

Figure 5. Application Diagram without Micro-controller (Stand Alone Mode)

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin # | Label  | Description                                                                                              |

|-------|--------|----------------------------------------------------------------------------------------------------------|

| 1     | OUT1   | Channel 1 Current Output to LED                                                                          |

| 2     | OUT2   | Channel 2 Current Output to LED                                                                          |

| 3     | OUT3   | Channel 3 Current Output to LED                                                                          |

| 4     | OUT4   | Channel 4 Current Output to LED                                                                          |

| 5     | OUT5   | Channel 5 Current Output to LED                                                                          |

| 6     | OUT6   | Channel 6 Current Output to LED                                                                          |

| 7     | OUT7   | Channel 7 Current Output to LED                                                                          |

| 8     | OUT8   | Channel 8 Current Output to LED                                                                          |

| 9     | OUT9   | Channel 9 Current Output to LED                                                                          |

| 10    | OUT10  | Channel 10 Current Output to LED                                                                         |

| 11    | OUT11  | Channel 11 Current Output to LED                                                                         |

| 12    | OUT12  | Channel 12 Current Output to LED                                                                         |

| 13    | GND    | Signal Ground                                                                                            |

| 14    | ISET   | Current Setting/EoL Enable Pin                                                                           |

| 15    | CONF   | Stand Alone Mode Selection Bank                                                                          |

| 16    | VCC    | 3.3 V Voltage Reference Output (Needs External Decoupling Capacitor)                                     |

| 17    | VS     | Supply Voltage Input                                                                                     |

| 18    | DIAGEN | Diagnostic Voltage Sensing Node for V <sub>STRING</sub> Via Resistor Divider                             |

| 19    | GNDP   | Power Ground for output drivers                                                                          |

| 20    | DIAG   | Open-drain diagnostic input/output. Reporting Open Circuit and thermal shutdown. Normal Operation = HIGH |

Table 1. PIN FUNCTION DESCRIPTION (continued)

| Pin # | Label | Description                                             |

|-------|-------|---------------------------------------------------------|

| 21    | OEN   | Output Enable Input                                     |

| 22    | SDA   | I <sup>2</sup> C Serial Data                            |

| 23    | SCL   | I <sup>2</sup> C Serial Clock                           |

| 24    | VDD   | Digital Supply Voltage Input                            |

| epad  | epad  | True Ground Do NOT Connect to PCB Traces other than GND |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Symbol                 | Parameter                                                                                         | Min          | Max      | Unit   |

|------------------------|---------------------------------------------------------------------------------------------------|--------------|----------|--------|

| V <sub>MAX</sub> _VS   | Power supply voltage:<br>Continuous supply voltage<br>Transient Voltage (t < 500 ms, "load dump") | -0.3<br>-0.3 | 28<br>40 | V<br>V |

| V <sub>MAX</sub> INx   | Input pin voltage (DIAGEN, DIAG, CONF, OEN)                                                       | -0.3         | 40       | V      |

| V <sub>MAX</sub> OUTx  | Continuous Output Pin voltage                                                                     | -0.3         | 28       | V      |

|                        | Transient Voltage (t < 500 ms, "load dump") or during PWM period = OFF                            | -0.3         | 40       | V      |

| V <sub>MAX</sub> _VCC  | Stabilized supply voltage                                                                         | -0.3         | 3.6      | V      |

| $V_{MAX}VDD$           | Digital input supply voltage                                                                      | -0.3         | 5.5      | V      |

| V <sub>MAX</sub> _IO   | DC voltage at pins (VDD, SCL, SDA)                                                                | -0.3         | 5.5      | V      |

| V <sub>MAX</sub> ISET  | DC voltage at pin ISET                                                                            | -0.3         | 3.6      | V      |

| I <sub>MAX</sub> _GNDP | Maximum Ground Current                                                                            | -            | 750      | mA     |

| T <sub>JMAX</sub>      | Junction Temperature, T <sub>J</sub>                                                              | -40          | 150      | °C     |

| T <sub>A_zap</sub>     | OTP Zap Ambient Temperature                                                                       | 10           | 30       | °C     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

**Table 3. ATTRIBUTES**

| Parameter                                                  | Value      | Unit     |

|------------------------------------------------------------|------------|----------|

| ESD Capability (Note 2)                                    |            |          |

| ESD Voltage, HBM (Human Body Model); (100 pF, 1500 Ω)      |            | 137      |

| <ul><li>All pins</li><li>Output pins OUTx to GND</li></ul> | ±2<br>±4   | kV<br>kV |

| ESD according to CDM (Charge Device Model)                 | 14         | N.V      |

| - All pins                                                 | ±500       | V        |

| - Comer pins                                               | ±750       | V        |

| ESD according to MM (Machine Mode)                         |            | .,       |

| – All pins                                                 | ±150       | V        |

| Moisture sensitivity (SSOP24-EP) (Note 3)                  | MSL2       |          |

| Storage Temperature                                        | -55 to 150 | °C       |

| Package Thermal Resistance (SSOP24-EP) (Note 4)            |            |          |

| – Junction to Ambient, R <sub>0JA</sub>                    | 45.8       | °C/W     |

| – Junction to Board, R <sub>0,JB</sub>                     | 8.8        | °C/W     |

| – Junction to Case (Top), R <sub>θJC</sub>                 | 10.1       | °C/W     |

<sup>2.</sup> This device series incorporates ESD protection and is tested by the following methods:

ESD HBM tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD MM according to AEC-Q100

<sup>1.</sup> Integrated protection functions are designed to prevent IC destruction under fault conditions described in the datasheet. Fault conditions are considered as outside normal operating range. Protection functions are not designed for continuous repetitive operation.

ESD CDM tested per EIA/JES D22/C101, Field Induced Charge Model

<sup>3.</sup> For additional information, see or download ON Semiconductor's Soldering and Mounting Techniques Reference Manual, SOLDERRM/D, and Application Note AND8003/D.

<sup>4.</sup> Values represent thermal resistances under natural convection are obtained in a simulation on a JEDEC-standard, 2S2P; High Effective Thermal Conductivity Test Board as specified in JESD51-7, in an environment described in JESD51-2a.

# **Table 4. ELECTRICAL CHARACTERISTICS**

(5 V < VS < 18 V, 3.15 V < VDD < 5.5 V, R1 = 1.82 k $\Omega$ ,  $-40^{\circ}C \le T_{J} \le 150^{\circ}C$ , unless otherwise specified)

| Characteristic                           | Symbol         | Test Conditions                                                          | Min | Тур  | Max | Unit                |

|------------------------------------------|----------------|--------------------------------------------------------------------------|-----|------|-----|---------------------|

| GENERAL                                  |                |                                                                          |     |      |     |                     |

| Supply Voltage                           | VS_EXT         | Functional extended range (limited temperature)                          | 5   | -    | 28  | V                   |

|                                          | VS_OP          | Parametric operation                                                     | 5   | -    | 18  | V                   |

| Supply Under-Voltage                     | VSUV           | VS rising                                                                | 3.8 | 4.1  | 4.4 | V                   |

| Supply range during<br>OTP zapping       | VS_OTPzap      | 2.5 V ≤ ISET ≤ 3.3 V;<br>VS current peak capability ≥ 70 mA              | 13  | -    | 18  | V                   |

| Supply Under-Voltage hysteresis          | VSUVhys        |                                                                          | -   | 200  | -   | mV                  |

| Supply Current (Vs)                      | Is(error mode) | all OUTx OFF except channel in open load SCL = SDA = 0                   |     |      |     |                     |

|                                          |                | lout_VCC = 0 mA                                                          | _   | 1.2  | 1.5 | mA                  |

|                                          |                | lout_VCC = 1 mA                                                          | _   | 2.2  | 2.5 | mA                  |

|                                          | Is(active)     | Active Mode VS = 16 V, Vcc unloaded OUTx = 1 V, R1 = $2 \text{ k}\Omega$ | -   | 7    | 10  | mA                  |

| Digital supply current                   | IDD            | I <sup>2</sup> C mode, VS = 12 V                                         | -   | 0.24 | 2   | mA                  |

| VDD Under Voltage                        | VDDUV_R        | VDD rising                                                               | _   | -    | 2.9 | V                   |

| detection                                | VDDUV_F        | VDD falling                                                              | 2   | -    | -   | V                   |

| CURRENT SOURCE OU                        | TPUTS          |                                                                          |     |      |     |                     |

| Output current                           | IOUThot        | OUTx = 1 V, Tj = 150°C                                                   | 50  | 55   | 60  | mA                  |

|                                          | IOUTcold       | OUTx = 0.5 V, Tj = -40°C                                                 | 50  | 55   | 60  | mA                  |

| Current Matching from                    | ImatchCold     | Tj = -40°C (Note 5)                                                      | -7  | 0    | 7   | %                   |

| channel to channel                       | Imatch         | Tj = 25°C (Note 5)                                                       | -6  | 0    | 6   | %                   |

|                                          | ImatchHot      | Tj = 150°C (Note 5)                                                      | -5  | 0    | 5   | %                   |

| Current Slew Rate                        | ISRx           | 10% to 90%                                                               | -   | 30   | -   | mA/μs               |

| Open Circuit Detection<br>Threshold      | OLDT           | IOUTx > 20mA                                                             | 30  | 50   | 70  | % of output current |

| Open load recovery in auto-recovery mode | OLR            |                                                                          | 5   | 10   | 15  | mA                  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 5. Matching formulas:

$$\left[\frac{2IOUTx(min)}{IOUTx(min) + IOUTx(max)} - 1\right] \times 100 \text{ and } \left[\frac{2IOUTx(max)}{IOUTx(min) + IOUTx(max)} - 1\right] \times 100$$

**Table 5. ELECTRICAL CHARACTERISTICS** (5 V < VS < 18 V, 3.15 V < V $_{DD}$  < 5.5 V, R1 = 1.82 k $_{\Omega}$ , -40°C  $\leq$  T $_{J}$   $\leq$  150°C, unless otherwise specified)

| Symbol                                      | Parameter                | Test Conditions | Min  | Тур  | Max     | Unit |  |  |  |  |

|---------------------------------------------|--------------------------|-----------------|------|------|---------|------|--|--|--|--|

| VOLTAGE REFE                                | VOLTAGE REFERENCE        |                 |      |      |         |      |  |  |  |  |

| V_VCC                                       | Output Voltage Tolerance | I_VCC ≤ 1 mA    | 3.20 | 3.30 | 3.45    | V    |  |  |  |  |

| lout_VCC                                    | Output Current           |                 | -    | -    | -1      | mA   |  |  |  |  |

| Cload_VCC                                   | Load Capacitor           | ESR < 200 mΩ    | 0.9  | 1.0  | 2.5     | nF   |  |  |  |  |

| INPUTS: OEN, CONF                           |                          |                 |      |      |         |      |  |  |  |  |

| VinL                                        | Input Low Level          |                 | 0.7  | 1.0  | -       | V    |  |  |  |  |

| VinH                                        | Input High Level         |                 | -    | 1.25 | 1.66    | V    |  |  |  |  |

| Vin_hyst                                    | Input Hysteresis         |                 | 100  | 250  | 400     | mV   |  |  |  |  |

| Rin_pd Input Pull-down Resistor 120 200 280 |                          |                 |      |      |         |      |  |  |  |  |

| INPUTS: SCL, SDA                            |                          |                 |      |      |         |      |  |  |  |  |

| VinL                                        | Input Low Level          |                 | -    | -    | 0.3×VDD | V    |  |  |  |  |

Table 5. ELECTRICAL CHARACTERISTICS (continued)

$(5 \text{ V} < \text{VS} < 18 \text{ V}, 3.15 \text{ V} < \text{V}_{DD} < 5.5 \text{ V}, \text{R1} = 1.82 \text{ k}\Omega, -40^{\circ}\text{C} \le \text{T}_{J} \le 150^{\circ}\text{C}, \text{ unless otherwise specified})$

| Symbol          | Parameter                                            | Test Conditions                       | Min      | Тур  | Max  | Unit |  |

|-----------------|------------------------------------------------------|---------------------------------------|----------|------|------|------|--|

| INPUTS: SCL, SE | )A                                                   | •                                     | •        |      | •    | •    |  |

| VinH            | Input High Level                                     |                                       | 0.7×VDD  | -    | -    | V    |  |

| Vin_hyst        | Input Hysteresis                                     |                                       | 0.05×VDD | -    | -    | V    |  |

| lout_SDA        | Output Current                                       | V (SDA) = 0.4 V                       | 3        | -    | -    | mA   |  |

| DIAGEN PIN      |                                                      |                                       |          |      |      |      |  |

| VDiagenTH       | VS Diagnostic Enable Threshold                       |                                       | 1.9      | 2.0  | 2.1  | V    |  |

| Rdiagen_pd      | Input Pull-down Resistor                             |                                       | 120      | 200  | 280  | kΩ   |  |

| DIAG PIN        |                                                      |                                       |          |      |      |      |  |

| VoutL           | Output Low Level                                     | Diagnostic Activated,<br>Idiag = 1 mA | -        | 0.2  | 0.4  | V    |  |

| DiagRes         | Diagnostic Reset Voltage                             |                                       | 1.65     | 1.80 | 1.95 | V    |  |

| tp_DIAG         | Filter Time to Set the DIAG Fail Pin in Failure Mode | Idiag = 1 mA                          | -        | 10   | 20   | μs   |  |

| DIAG_leak       | DIAG Output Leakage                                  | VDIAG = 5 V                           | _        | -    | 10   | μΑ   |  |

| ISET INPUT PIN  |                                                      |                                       |          |      |      |      |  |

| VISET           | Global Current Setting                               |                                       | 0.94     | 1.0  | 1.06 | V    |  |

| K               | IOUT ISET Factor                                     |                                       | _        | 100  | -    | -    |  |

| tsetupISET      | Setup-up Time to 90% of the ISET<br>Regulated Value  | VS > 5 V                              | -        | -    | 50   | μs   |  |

| INTERNAL PWM    | CONTROL UNIT (OUT1- OUT12)                           |                                       |          |      |      |      |  |

| Symbol          | Parameter                                            | Test Conditions                       | Min      | Тур  | Max  | Unit |  |

| PWM1            | PWM1 Frequency, I <sup>2</sup> C Mode                | Configuration Via I <sup>2</sup> C    | 132      | 150  | 168  | Hz   |  |

| PWM2            | PWM2 Frequency, I <sup>2</sup> C Mode                | Configuration Via I <sup>2</sup> C    | 264      | 300  | 336  | Hz   |  |

| PWM3            | PWM3 Frequency, I <sup>2</sup> C Mode                | Configuration Via I <sup>2</sup> C    | 528      | 600  | 672  | Hz   |  |

| PWM4            | PWM4 Frequency, I <sup>2</sup> C Mode                | Configuration Via I <sup>2</sup> C    | 1056     | 1200 | 1344 | Hz   |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Table 6. THERMAL WARNING AND THERMAL SHUTDOWN PROTECTION

| Symbol   | Parameter                                                          | Min | Тур    | Max | Unit |

|----------|--------------------------------------------------------------------|-----|--------|-----|------|

| Tjwar_on | Thermal Warning Threshold (Junction Temperature)                   | -   | TSD-30 | 1   | °C   |

| TSD      | Thermal Shutdown Threshold (Junction Temperature) $T_J$ Increasing | 160 | 1      | 180 | °C   |

| Tjsd_hys | Thermal Shutdown Hysteresis                                        | 10  | -      | 15  | °C   |

# General

The NCV7685 is a twelve channel LED driver. Each output can drive currents up to 60 mA/channel and are programmable via an external resistor. The target applications for the device are in automotive rear lighting systems and dashboard applications. The device can be used with micro-controller applications using the I<sup>2</sup>C bus or in stand-alone applications. In both cases it is mandatory to supply the LED channels by an external ballast transistor, or by an LDO or a DC/DC to have low voltage drop on the outputs which will lead to a decrease in power dissipation in the device. In order to have very low electromagnetic emission, this device has an embedded spread spectrum oscillator.

# Output Current Programming (I<sub>SET</sub>/I<sub>OUTx</sub>)

The maximum current can be defined with the Iset input pin. The equations below can be used to calculate this maximum output current:

$$lset = 1 V/R1 (eq. 1)$$

$$IOUTx = K \times Iset$$

(eq. 2)

Example:

$R1 = 2 k\Omega$

using eq. 1  $\rightarrow$  Iset = 500  $\mu$ A

and using eq.  $2 \rightarrow IOUTx = 50 \text{ mA}$

To avoid potential disturbances when all drivers are activated at the same time, a typical activation delay of 400 ns between groups of 2 consecutive outputs is implemented (see Figure 6).

Figure 6.

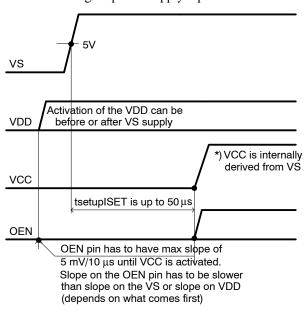

# Power Supply and Voltage Reference (VS, V<sub>CC</sub>, V<sub>DD</sub>)

VS is the analog power supply input of the device. VS supply is monitored with respect to the crossing of VSUV level (typ. 4.1 V). When VS rises above VSUV, the device starts the power–up state. When VS is above the VS\_OP minimum level (typ. 5 V), the device can work properly.

VCC is a voltage reference providing 3.3 V derived from the VS main supply. It is able to deliver up to 1 mA and is primarily intended to supply 3.3 V loads. If VCC output reference is not used, then the VCC capacitor can be omitted. VDD is the digital power supply input of the device.

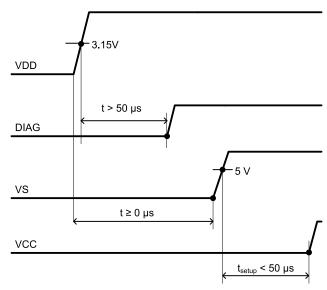

Figure 7. Power-up Sequence for OEN pin

# Ground Connections (GND: Pin 13 and GNDP Pin 19)

The device ground connection is split to two pins called GND and GNDP. Both pins have to be connected on the application PCB.

# Chip Select for OTP Programing (Using I<sub>SET</sub>)

The device can be programmed using the I<sup>2</sup>C bus in End of Line cases. When the voltage on the ISET pin is pulled higher than 2.5 V, the device can be set in OTP control mode via the I<sup>2</sup>C bus. During normal mode where only an external

ISET resistor is connected to the I<sub>SET</sub> pin, the access to the OTP registers is not possible. Zapping is only possible with VS above 13 V. The outputs are disabled as soon as 2.5 V is applied to the ISET pin. After the ID\_LOCK\_OTP I2C message is properly received, no further OTP zapping is possible.

# **Output Enable (OEN)**

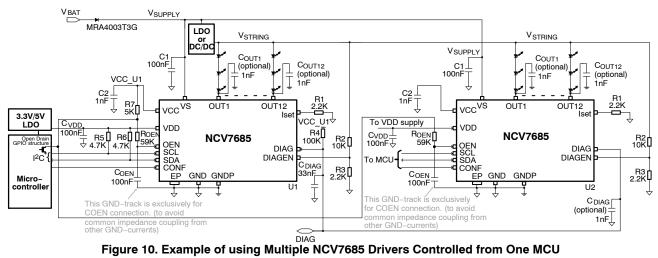

When the OEN input voltage is high, all output channels are programmed according to the I2C or SAM configuration. When OEN voltage is below 0.7 V, all outputs are disabled in the SAM or I2C mode regardless on the registers setting. If the OEN pin is left floating, the internal pull down resistor will cause switching off all channels. The OEN pin has to have max slope of 5 mV for first 10  $\mu s$  until VCC is activated. The recommended examples are shown in Figure 4 and Figure 5. The Figure 11 shows the example of the driving multiple NCV7685 drivers from one MCU.

# Configuration (CONF)

When the CONF input voltage will be below 0.7 V the configuration 1 will be selected (One Time Programmable OTP 1 register called SAM\_CONF\_1) and when the CONF input voltage will be above 1.66 V the configuration 2 will be selected (OTP 2 register called SAM\_CONF\_2). There is ability to change the configuration in error mode (either with CONF in SAM or through I<sup>2</sup>C in I2C mode).

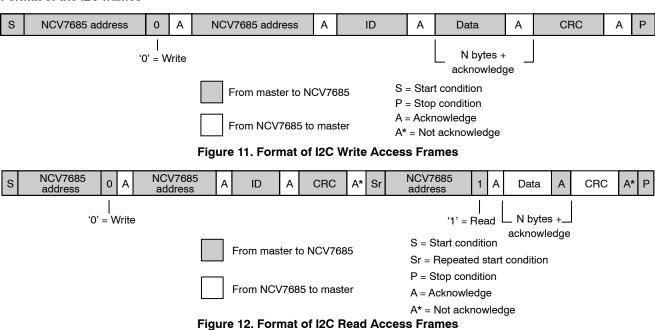

# I<sup>2</sup>C Bus (SCL, SDA)

The I<sup>2</sup>C bus consists of two wires, Serial Data (SDA) and Serial Clock (SCL), carrying information between the devices connected on the bus. Each device connected to the bus is recognized by a unique address and operates as either a transmitter or receiver, depending on the function of the device. The NCV7685 can both receive and transmit data with CRC8 error detection algorithm. The NCV7685 is a slave device.

SDA is a bi-directional line connected to a positive supply voltage via an external pull-up resistor. When the bus is free both lines are HIGH. The output stages of the devices connected to the bus must have an open drain to perform the wired-AND function. Data on the I<sup>2</sup>C bus can be transferred up to 400 kb/s.

# **Diagnostic Enabling (DIAGEN)**

The device is capable to detect for each independent channel an open load condition. Versus the number of LEDs and the Vstring voltage supply, a wrong open load condition can be detected if the fault detection is activated when there is not enough voltage across the LEDs. This threshold can be programmable thanks to an external divider connected to the DIAGEN pin. When the divided voltage is below a typical value of 2 V, the LED diagnostic is disabled. When the divided voltage is above the typical value of 2 V, the LED diagnostic is enabled.

# Diagnostic Feedback (DIAG)

The DIAG is an open drain output pin who can alert a microcontroller as soon as one of the outputs is in error mode (DIAG Low = open load or thermal shut–down or  $I_{SET}$  shorted). Forcing the DIAG pin below 1.8 V will force a fault condition if the DIAGEN input pin is above a typical value of 2 V. If the DIAGEN input pin is below the typical value of 2 V then forcing the DIAG input pin will not have any effect.

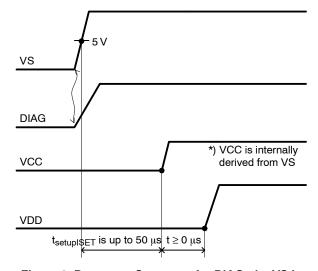

Due to certain sensitivity on the DIAG pin during the startup, it is recommended to have the pull-up resistor connected to the VCC supply. In case if the application deviate from the proposal mentioned in the Figure 4 or Figure 5, the power-up sequence has to follow the timing diagrams in the Figure 8 or Figure 9.

Figure 8. Power-up Sequence for DIAG pin. VS is supplied first, VDD comes up later.

Figure 9. Power-up Sequence for DIAG pin. VDD is supplied first, VS comes up later or equal.

# **Parallel Outputs**

The maximum rating per output is 60 mA. In order to increase system level LED string current, parallel combinations of any number of outputs is allowed. Combining all 12 outputs will allow for a maximum system level string current design of 720 mA.

# **Required Time Delay for OTP Zapping**

As soon as the ID\_LOCK\_OTP message is received, the I<sup>2</sup>C acknowledge is immediately sent out to the MCU. However, the internal circuitries still requires 500 µs time delay to complete the OTP zapping of one OTP bit. Therefore, no I<sup>2</sup>C confirmation is send. The number of OTP bits that are zapped corresponds with each change from the default values. It is needed 16.5 ms in total to successfully finish the zapping sequence of all 32 customer bits + one internal bit. The verification of the OTP banks can be done by readout of the ID\_READ\_OTP I<sup>2</sup>C message after zapping delay.

# **DIGITAL PART AND 12C REGISTERS**

The I<sup>2</sup>C bus consists of two wires, serial data (SDA) and serial clock (SCL), carrying information between the devices connected on the bus. Each device connected to the bus is recognized by a unique address. The NCV7685 can both receive and transmit data with CRC8 error detection

algorithm. The NCV7685 is a slave device only. Generation of the signals on the  $I^2C$  bus is always the responsibility of the master device.

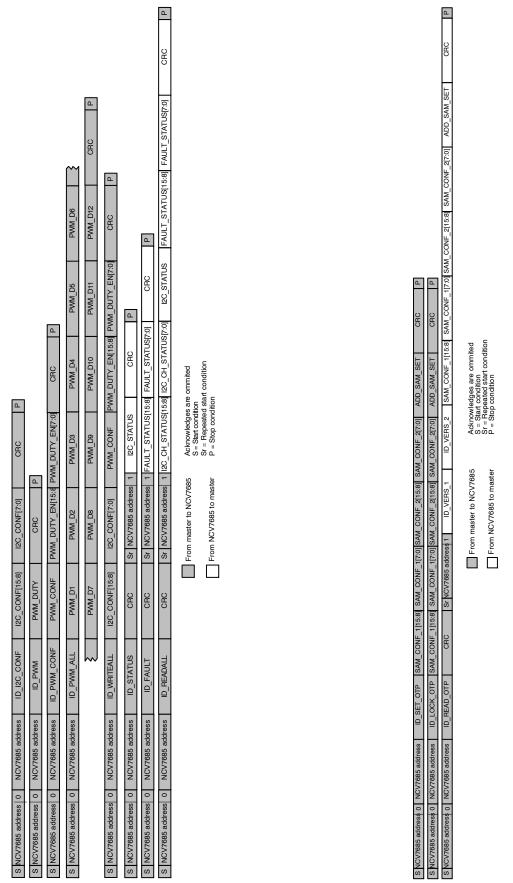

They are multiple kinds of message structure possible versus ID code received.

Table 7. IDENTIFIER ADDRESSING (ID) MESSAGE

| Name        | ID | Access type | Name of Register Addressed                                                                        |

|-------------|----|-------------|---------------------------------------------------------------------------------------------------|

| ID_I2C_CONF | 00 | W           | I2C_CONF                                                                                          |

| ID_PWM      | 01 | W           | PWM_DUTY                                                                                          |

| ID_PWM_CONF | 02 | W           | PWM_CONF, PWM_DUTY_EN                                                                             |

| ID_PWM_ALL  | 03 | W           | PWM_D1, PWM_D2, PWM_D3, PWM_D4, PWM_D5, PWM_D6, PWM_D7, PWM_D8, PWM_D9, PWM_D10, PWM_D11, PWM_D12 |

| ID_WRITEALL | 04 | W           | I2C_CONF, PWM_CONF, PWM_DUTY_EN                                                                   |

| ID_STATUS   | 08 | R           | I2C_STATUS                                                                                        |

| ID_FAULT    | 09 | R           | FAULT_STATUS                                                                                      |

| ID_READALL  | 0A | R           | I2C_CH_STATUS, I2C_STATUS, FAULT_STATUS                                                           |

| ID_SET_OTP  | 20 | W           | SAM_CONF_1, SAM_CONF_2, ADD_SAM_SET                                                               |

| ID_LOCK_OTP | 21 | W           | SAM_CONF_1, SAM_CONF_2, ADD_SAM_SET                                                               |

| ID_READ_OTP | 28 | R           | ID_VERS_1, ID_VERS_2, SAM_CONF_1, SAM_CONF_2, ADD_SAM_SET                                         |

There are 3 kinds of registers, Hard Coding, OTP and volatile registers.

Remark: CRC byte is not transmitted when CRC

protection is turned off (ERREN = 0)

**Hard Coding Registers:**

ID\_VERS\_1 ID\_VERS\_2

**OTP Registers:**

ADD\_SAM\_SET SAM\_CONF\_1 SAM\_CONF\_2 Volatile Registers:

I2C\_CONF I2C\_STATUS I2C\_CH\_STATUS FAULT\_STATUS PWM\_DUTY PWM\_D1 - PWM\_D12 PWM\_DUTY\_EN PWM\_CONF

# Format of the I2C frames

Figure 13. Format of I2C Frames

Figure 14. Format of I2C OTP Frames

There is a safety mechanism implemented by repeating the address. Since the I<sup>2</sup>C address is 7 bits long, first bit of

the second address byte starts with a "0" in the repeated byte (see tables below).

Table 8.

|                                 | 1 <sup>st</sup> byte            |   |                 |      |   |   |   |  |  |  |  |

|---------------------------------|---------------------------------|---|-----------------|------|---|---|---|--|--|--|--|

| 7                               | 7 6 5 4 3 2 1                   |   |                 |      |   |   | 0 |  |  |  |  |

|                                 | I <sup>2</sup> C device Address |   |                 |      |   |   |   |  |  |  |  |

|                                 |                                 |   | 2 <sup>nd</sup> | byte |   |   |   |  |  |  |  |

| 7                               | 6                               | 5 | 4               | 3    | 2 | 1 | 0 |  |  |  |  |

| I <sup>2</sup> C device Address |                                 |   |                 |      |   |   |   |  |  |  |  |

# **CRC ERROR DETECTION ALGORITHM**

The CRC protection is turned off by default. It can be enabled by activation of the OTP ERREN bit (ERREN = 1). The every  $I^2C$  byte including both addresses with R/W flag are calculated using CRC8 algorithms. The CRC polynomial is following:  $x^8 + x^5 + x^3 + x^2 + x + 1$ .

Example of the CRC used in the  $I^2C$  message with  $I2C\_CONF$  byte = 0xCFFF and with  $I^2C$  address 0x60 (0xC0) is 0x2E.

# HARD CODING REGISTERS

**Table 9. HARD CODING REGISTERS**

| Bit         | D7       | D6 | D5 | D4   | D3   | D2 | D1 | D0 |  |  |

|-------------|----------|----|----|------|------|----|----|----|--|--|

| ID_VERS_1   |          |    |    |      |      |    |    |    |  |  |

| Access type | R        | R  | R  | R    | R    | R  | R  | R  |  |  |

| Bit name    |          |    |    | ID1[ | 7:0] |    |    |    |  |  |

| Reset value | 0        | 1  | 0  | 0    | 0    | 0  | 1  | 1  |  |  |

| ID_VERS_2   |          |    |    |      |      |    |    |    |  |  |

| Access type | R        | R  | R  | R    | R    | R  | R  | R  |  |  |

| Bit name    | ID2[7:0] |    |    |      |      |    |    |    |  |  |

| Reset value | 0        | 0  | 0  | 0    | 0    | 1  | 0  | 0  |  |  |

<sup>1.</sup> ID1[7:0] = 43h (ON Semiconductor device identifier)

# **OTP REGISTERS**

Table 10. ADD\_SAM\_SET

| Bit         | D7    | D6      | D5    | D4  | D3  | D2       | D1  | D0  |

|-------------|-------|---------|-------|-----|-----|----------|-----|-----|

| Access type | R/W   | R/W     | R/W   | R/W | R/W | R/W      | R/W | R/W |

| Bit name    | AUTOR | DETONLY | ERREN |     |     | ADD[4:0] |     |     |

| Reset value | 0     | 1       | 0     | 0   | 0   | 0        | 0   | 0   |

ADD[4:0] are the programmable BUS address registers (in I2C mode ADD[6:5] = 11).

AUTOR: When AUTOR=1 (and DIAGEN is high), open load diagnosis is performed. When a fault is detected, the DIAG pin is set and LED driver imposes a low current on the faulty branch alone, switching off the others. When fault is recovered, LED driver returns to normal operation after resetting the DIAG pin. If the DIAG pin is triggered externally, LED driver outputs are switched off and the low power mode is entered.

DETONLY: When DETONLY=1, open load diagnostic is performed. When a fault is detected, the DIAG pin is set without taking any action on the current regulation. When fault is recovered, DIAG is reset. If the DIAG pin is triggered externally, no action is taken.

When AUTOR = DETONLY = 0, no diagnostic performed When AUTOR = DETONLY = 1, no change (same as previously setting).

*ERREN:* When ERREN = 1, CRC error detection algorithm is activated for  $I^2C$  communication.

ID2[7:0] = 04h (The actual version)

Table 11. SAM CONF

| Table 11. SA | AIVI_CC | INF |     |     |     |     |     |     |     |        |           |     |     |     |     |     |

|--------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|--------|-----------|-----|-----|-----|-----|-----|

| Bit          | D15     | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6     | D5        | D4  | D3  | D2  | D1  | D0  |

| SAM_CONF_    | 1       |     |     |     |     |     |     |     |     |        |           |     |     |     |     |     |

| Access type  | R       | R   | R   | R   | R/W | R/W | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W | R/W | R/W |

| Bit name     | _       | _   | _   | -   |     |     |     |     |     | SAM1cc | onf[11:0] |     |     |     |     |     |

| Reset value  | 0       | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   | 0   | 0   |

| SAM_CONF_    | 2       |     |     |     |     |     |     |     |     |        |           |     |     |     |     |     |

| Access type  | R       | R   | R   | R   | R/W | R/W | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W | R/W | R/W |

| Bit name     | _       | _   | -   | -   |     |     |     |     |     | SAM2cc | onf[11:0] |     |     |     |     |     |

| Reset value  | 0       | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1      | 1         | 1   | 1   | 1   | 1   | 1   |

SAM1conf[x] = 0 means channel is OFF and SAM1conf[x] = 1 means channel is ON SAM2conf[x] = 0 means channel is OFF and SAM2conf[x] = 1 means channel is ON

# **VOLATILE REGISTERS**

Table 12. I2C\_CONF

| Bit         | D15     | D14      | D13      | D12   | D11 | D10 | D9 | D8 | D7  | D6     | D5    | D4 | D3 | D2 | D1 | D0 |

|-------------|---------|----------|----------|-------|-----|-----|----|----|-----|--------|-------|----|----|----|----|----|

| Access type | W       | W        | W        | W     | W   | W   | W  | W  | W   | W      | W     | W  | W  | W  | W  | W  |

| Bit name    | I2CFLAG | I2CautoR | I2CdOnly | PWMEN |     |     |    |    | 120 | Cconf[ | 11:0] |    |    |    |    |    |

| Reset value | 0       | 0        | 0        | 0     | 0   | 0   | 0  | 0  | 0   | 0      | 0     | 0  | 0  | 0  | 0  | 0  |

*I2CFLAG:* the I2CFLAG should be reset whenever standalone mode is entered. When I2CFLAG=1 and when VDD is high, the I2C mode is activated, in all other conditions the device is in Stand Alone Mode.

*12CautoR:* When I2CautoR=1 (and DIAGEN is high), open load diagnosis is performed. When a fault is detected, the DIAG pin is set and LED driver imposes a low current on the faulty branch alone, switching off the others. When fault is recovered, LED driver returns to normal operation after resetting the DIAG pin. If the DIAG pin is triggered externally, LED driver outputs are switched off and the low power mode is entered. Whenever the device is configured in autorecovery (AUTOR in standalone mode or I2CautoR in I2C mode), it is not allowed to put PWMDUTY = 0 or PWMDx = 0 to a channel which has detected an open load.

*12CdOnly:* When I2CdOnly =1, open load diagnostic is performed. When a fault is detected, the DIAG pin is set without taking any action on the current regulation. When fault is recovered, DIAG is reset. If the DIAG pin is triggered externally, no action is taken.

When I2CautoR = I2CdOnly = 0, no diagnostic performed.

When I2CautoR = I2CdOnly = 1, no change (same as previously setting).

PWMEN: When PWMEN = 1, PWM is activated, when PWMEN = 0 the content of the complete register PWM\_DUTY\_EN is not reset and PWM is disabled.

I2Cconf[x] = 0 means channel is OFF and I2Cconf[x] = 1 means channel is ON.

Table 13. I2C\_STATUS

| Bit         | D7      | D6     | D5 | D4        | D3 | D2  | D1      | D0 |

|-------------|---------|--------|----|-----------|----|-----|---------|----|

| Access type | R       | R      | R  | R         | R  | R   | R       | R  |

| Bit name    | SC_Iset | I2Cerr | UV | diagRange | TW | TSD | DIAGERR | OL |

| Reset value | 0       | 0      | 0  | 0         | 0  | 0   | 0       | 0  |

*SC\_Iset:* SC\_Iset = 1 means there is short-circuit on the external resistor on I<sub>SET</sub> pin and drivers are switched OFF and DIAG pin is set. SC\_Iset=0 no short-circuit.

*I2Cerr:* I2Cerr=1 means an error has been detected during the I2C communication, I2Cerr=0 means no error during I2C communication has been detected.

*UV*: the device is in under voltage condition (VS is below VSUV threshold, all channels OFF).

diagRange: when diagRange = 1 the divided voltage is above the typical value of 2 V (LED diagnostic is enabled), diagRange = 0 means the divided voltage is below the typical value of 2 V (LED diagnostic is disabled).

TW: when TW=1 the device is in the thermal warning range (typ 140°C), this flag is just a warning no action is foreseen on the output drivers. TW=0 means the device is below the thermal warning range.

TSD: when TSD = 1 the device is in the Thermal shutdown range, TSD = 0 means the device is below the thermal shutdown range.

*DIAGERR*: DIAGERR = 1 means an error is detected by DIAG pin forced externally.

OL: OL = 1 means at least one channel is in Open Load condition, OL = 0 no Open Load.

# Table 14.

| SC_lset   | set when a short-circuit on the external resistor on I <sub>SET</sub> pin, latched if permanent after 10 µs. Reset in case of short-circuit disappear permanently for at least 10µs.                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2Cerr    | set if an error has been detected during the I2C communication. Reset on register reading.                                                                                                                         |

| UV        | set when device is in under voltage condition (VS is below VSUV, all channels OFF).                                                                                                                                |

| diagRange | set when divided voltage is above the VDiagenTH threshold. Reset when the divided voltage is below the VDiagenTH threshold.                                                                                        |

| TW        | set when junction temperature is above the Tjwar_on threshold.  Reset on register reading AND temperature is below the (Tjwar_on - Tjsd_hys) threshold                                                             |

| TSD       | set when junction temperature is above the TSD threshold. Reset on register reading AND temperature is below the TSD – Tjsd_hys) threshold                                                                         |

| DIAGERR   | set by DIAG pin forced low externally, latched if permanent after 10 µs. Reset in case DIAG pin is not forced permanently for at least 10 µs.                                                                      |

| OL        | set in Open Load condition and DIAGEN is high, latched if permanent after 10 µs. Reset if Open Load disappear permanently for at least 10 µs. Fault information is maintained on falling DIAGEN threshold exceeded |

# Table 15. I2C\_CH\_STATUS

| Bit         | D15     | D14      | D13      | D12   | D11 | D10 | D9 | D8 | D7   | D6    | D5     | D4    | D3 | D2 | D1 | D0 |

|-------------|---------|----------|----------|-------|-----|-----|----|----|------|-------|--------|-------|----|----|----|----|

| Access type | R       | R        | R        | R     | R   | R   | R  | R  | R    | R     | R      | R     | R  | R  | R  | R  |

| Bit name    | I2CFLAG | I2CautoR | I2CdOnly | PWMEN |     |     |    |    | I2C_ | CH_ST | ATUS[1 | 11:0] |    |    |    |    |

| Reset value | 0       | 0        | 0        | 0     | 0   | 0   | 0  | 0  | 0    | 0     | 0      | 0     | 0  | 0  | 0  | 0  |

I2CFLAG: same as I2C\_CONF register I2CautoR: same as I2C\_CONF register I2CdOnly: same as I2C\_CONF register PWMEN: same as I2C\_CONF register

*I2C\_CH\_STATUS[11:0]:* same as I2C\_CONF[11:0] bits in I2C mode or same as SAM\_CONF\_1[11:0], SAM\_CONF\_2[11:0] bits in Standalone mode.

Remark: When NCV7685 is configured in I2C mode and output channel OUTx is configured to operate in PWM mode, I2C\_CH\_STATUS[x] shall contain value '1'.

# Table 16. FAULT\_STATUS

| Bit         | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6    | D5     | D4 | D3 | D2 | D1 | D0 |

|-------------|-----|-----|-----|-----|-----|-----|----|----|----|-------|--------|----|----|----|----|----|

| Access type | R   | R   | R   | R   | R   | R   | R  | R  | R  | R     | R      | R  | R  | R  | R  | R  |

| Bit name    | -   | -   | -   | _   |     |     |    |    |    | FAULT | [11:0] |    |    |    |    |    |

| Reset value | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  | 0  | 0  |

FAULT[11:0]: when FAULT[x] = 1 the OUTx channel is in fault mode (Open Load latched when the duration is longer than 10  $\mu$ s), when FAULT[x] = 0 the OUTx channel

is working properly. The register is reset on each read operation.

Table 17. PWM DUTY

| Bit         | D7 | D6 | D5 | D4 | D3           | D2 | D1 | D0 |

|-------------|----|----|----|----|--------------|----|----|----|

| Access type | -  | W  | W  | W  | W            | W  | W  | W  |

| Bit Name    | -  |    |    | I  | PWMDUTY[6:0] |    |    |    |

| Reset Value | 0  | 0  | 0  | 0  | 0            | 0  | 0  | 0  |

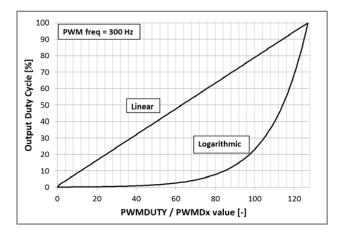

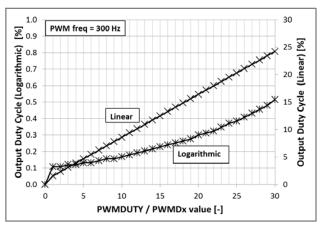

*PWMDUTY*[6:0]: logarithmic (or linear) common dimming for all channels via embedded PWM generator (128 steps). Following formula applies when logarithmic dimming is selected: Duty\_Cycle\_Percent =  $100 \times \alpha^{(N-i)}$  where  $\alpha = 0.9471$  and N = 127 rounded with an accuracy of 400 ns.

When PWMDUTY = 127 all channels ar fully switched on.

When PWMDUTY = 0 all channels are switched off.

Whenever the device is configured in autorecovery (AUTOR in standalone mode or I2CautoR in I2C mode), it is not allowed to put PWMDUTY = 0 or PWMDx = 0 to a channel which has detected an open load.

Transmitting PWM\_DUTY via I<sup>2</sup>C will cause setting the value to all channels.

Table 18. PWM\_Dx

| Bit         | D7 | D6 | D5 | D4 | D3         | D2 | D1 | D0 |

|-------------|----|----|----|----|------------|----|----|----|

| Access type | -  | W  | W  | W  | W          | W  | W  | W  |

| Bit Name    | -  |    |    |    | PWMDx[6:0] |    |    |    |

| Reset Value | 0  | 0  | 0  | 0  | 0          | 0  | 0  | 0  |

*PWMDx[6:0]:* logarithmic (or linear) independent PWM dimming for each OUTx channel via embedded PWM generator (128 steps). Following formula applies when logarithmic dimming is selected: Duty\_Cycle\_Percent =  $100 \times \alpha^{(N-i)}$  where  $\alpha = 0.9471$  and N = 127 rounded with an accuracy of 400 ns.

When PWMDx = 127 the OUTx channel is fully switched on.

When PWMDx = 0 the OUTx channel is switched off.

Whenever the device is configured in autorecovery (AUTOR in standalone mode or I2CautoR in I2C mode), it is not allowed to put PWMDUTY = 0 or PWMDx = 0 to a channel which has detected an open load.

To set independent PWM Duty Cycle value to each channel simultaneously, all twelve PWM\_Dx bytes has to be transferred via I<sup>2</sup>C bus in ID\_PWM\_ALL message. If PWM\_DUTY register is updated, all PWM\_Dx bytes will be overwritten by the same value from PWM\_DUTY register.

Table 19. PWM\_DUTY\_EN

| Bit         | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6    | D5      | D4 | D3 | D2 | D1 | D0 |

|-------------|-----|-----|-----|-----|-----|-----|----|----|----|-------|---------|----|----|----|----|----|

| Access type | -   | _   | _   | _   | W   | W   | W  | W  | W  | W     | W       | W  | W  | W  | W  | W  |

| Bit name    | -   | _   | _   | _   |     |     |    |    | P\ | WMDUT | Yen[11: | 0] |    |    |    |    |

| Reset value | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0     | 0       | 0  | 0  | 0  | 0  | 0  |

PWMDUTYen[11:0]: when PWMDUTYen[x] = 1, PWM dimming is enabled for OUTx channel, when PWMGAINen[x] = 0 means PWM dimming is disabled for

OUTx channel. When the PWM dimming is disabled, the output channel is programmed according to the I2Cconf[x] settings.

Table 20. PWM\_CONF

| Bit         | D7 | D6 | D5 | D4 | D3 | D2     | D1    | D0    |

|-------------|----|----|----|----|----|--------|-------|-------|

| Access type | W  | W  | W  | W  | W  | W      | W     | W     |

| Bit Name    | -  | -  | -  | -  | -  | PWMLIN | PWMF2 | PWMF1 |

| Reset Value | 0  | 0  | 0  | 0  | 0  | 0      | 0     | 0     |

PWMLIN bit shall select between between logarithmic (PWMLIN=0) and linear (PWMLIN=1) translation of PWMDUTY bits to duty cycle of internal PWM signal.

*PWMF2* and *PWMF1* bits set typical PWM frequency settings according to the Table 21.

**Table 21. TYPICAL PWM FREQUENCY SETTINGS**

| PWMF2 | PWMF1 | typ. PWM frequency [Hz] |

|-------|-------|-------------------------|

| 0     | 0     | 150                     |

| 0     | 1     | 300                     |

| 1     | 0     | 600                     |

| 1     | 1     | 1200                    |

Figure 15. Output Duty Cycle vs. Register Setting

Figure 16. Output Duty Cycle vs. Register Setting

- Detail

ON Semiconductor is licensed by Philips Corporation to carry the  $I^2C$  Bus Protocol.

NOTE 4 D

NOTE 6

Α

В

**TOP VIEW**

SIDE VIEW

H H H H H H H H H H

**BOTTOM VIEW**

RECOMMENDED

SOLDERING FOOTPRINT\*

**←**3.00→

NOTE 8 D2 3

NOTE 6

E1

PIN 1— REFERENCE

е

$\oplus$  0.15  $\oplus$  C A-B D

0.20

NOTE 5

0.10 C

0.10 C

# SSOP-24 NB EP CASE 940AQ **ISSUE 0**

0.20 C A-B

Н

Α1

△ 0.20 C

2X 12 TIPS

⊕ 0.12 M C A-B D

**A2**

C SEATING PLANE

⊕ 0.15 M C A-B

D

Ε

24X **b**

Α1

2.20 6.40

**DIMENSIONS: MILLIMETERS**

**DATE 18 AUG 2017**

L2

GAUGE

PLANE

C SEATING PLANE

**DETAIL A**

**DETAIL A**

**END VIEW**

NOTF 7

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. DAMBAR PROTRUSION SHALL BE 0.10 MAX. AT MMC. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT. DIMENSION & APPLIES TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 TO 0.25 FROM THE LEAD TIP.

- DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION D IS DETERMINED AT DATUM PLANE H.

5. DIMENSION E1 DOES NOT INCLUDE INTERLEAD

- FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE. DIMENSION E1 IS DETERMINED AT DA-TUM PLANE H.

- 6. DATUMS A AND B ARE DETERMINED AT DATUM PLANE H.

A1 IS DEFINED AS THE VERTICAL DISTANCE

- FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

- CONTOURS OF THE THERMAL PAD ARE UN-CONTROLLED WITHIN THE REGION DEFINED BY DIMENSIONS D2 AND E2.

|     | MILLIMETERS |      |

|-----|-------------|------|

| DIM | MIN         | MAX  |

| Α   | -           | 1.75 |

| A1  | 0.00        | 0.10 |

| A2  | 1.10        | 1.65 |

| b   | 0.19        | 0.30 |

| С   | 0.09        | 0.20 |

| D   | 8.64 BSC    |      |

| D2  | 2.50        | 2.70 |

| Е   | 6.00 BSC    |      |

| E1  | 3.90 BSC    |      |

| E2  | 1.80        | 2.00 |

| е   | 0.65 BSC    |      |

| h   | 0.25        | 0.50 |

| L   | 0.40        | 0.85 |

| L1  | 1.00 REF    |      |

| L2  | 0.25 BSC    |      |

| M   | 0°          | 8°   |

# **GENERIC MARKING DIAGRAM\***

XXXX = Specific Device Code

= Assembly Location

WL = Wafer Lot YY = Year WW = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present. Some products may not follow the Generic Marking.

# SCALE 1:1

| #Encodelline of afficient to a complete the Encoded of a condition of a first term of a first |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *For additional information on our Pb-Free strategy and soldering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| details, please download the ON Semiconductor Soldering and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mounting Techniques Reference Manual, SOLDERRM/D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

0.65

**PITCH**

Electronic versions are uncontrolled except when accessed directly from the Document Repository. **DOCUMENT NUMBER:** 98AON73645G Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

**DESCRIPTION:** SSOP-24 NB EP **PAGE 1 OF 1**

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

## **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LED Lighting Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

LV5235V-MPB-H MB39C602PNF-G-JNEFE1 MIC2871YMK-T5 AL1676-10BS7-13 AL1676-20AS7-13 AP5726WUG-7 ICL8201

IS31BL3228B-UTLS2-TR IS31BL3506B-TTLS2-TR AL3157F-7 AP5725FDCG-7 AP5726FDCG-7 LV52204MTTBG AP5725WUG-7

STP4CMPQTR NCL30086BDR2G CAT4004BHU2-GT3 LV52207AXA-VH AP1694AS-13 TLE4242EJ AS3688 IS31LT3172-GRLS4-TR

TLD2311EL KTD2694EDQ-TR KTZ8864EJAA-TR IS32LT3174-GRLA3-TR MP2488DN-LF-Z NLM0010XTSA1 AL1676-20BS7-13

ZXLD1370QESTTC MPQ7220GF-AEC1-P MPQ7220GR-AEC1-P MPQ4425BGJ-AEC1-P MPQ7220GF-AEC1-Z MPQ7220GR-AEC1-Z

MPQ4425BGJ-AEC1-Z NCL30486A2DR2G IS31FL3737B-QFLS4-TR IS31FL3239-QFLS4-TR KTD2058EUAC-TR KTD2037EWE-TR

DIO5662ST6 IS31BL3508A-TTLS2-TR KTD2026BEWE-TR MAX20052CATC/V+ MAX25606AUP/V+ BD6586MUV-E2 BD9206EFV-E2 BD9416FS-E2 LYT4227E