# Serial (SPI) Tri-Color LED Driver

The NLSF595 is advanced CMOS shift register with open drain outputs fabricated with 0.6  $\mu m$  silicon gate CMOS technology. This device is used in conjunction with a microcontroller, with only one dedicated line. All pins have Overvoltage Protection that allows voltages above  $V_{CC}$  up to 7.0 V to be present on the pins without damage or disruption of operation of the part, regardless of the operating voltage. This device may be used between 2.0 and 5.5 volts, the output driver level may be independent of supply voltage: 0–7.0 volts.

#### **Features**

- Parallel Outputs are Open Drain Capable of Sinking > 12 mA

- ullet Output Withstands up to +7.0 Regardless of  $V_{CC}$

- Standard Serial (SPI) Interface, Data, Clock, Enable (Low)

- All Inputs CMOS Level Compatible

- Frees up I/O around a Microcontroller

- Only One Pin Dedicated to this Device (Latch Enable)

- Output Enable may be Permanently Pulled Low

- High Speed Clocking, Fmax > 25 MHz (Shift Clock)

- Eight Bits Parallel Output

- Double Buffered Outputs, so Register may Fill without Affecting Output

- STD CMOS Serial Output, may be used to Cascade more than One Device

- Each Part Controls Two Tri-Color LEDs

- Two Devices can Control 5 Tri-Color LEDs

- Low Leakage:  $I_{CC} = 2.0 \mu A$  (Max) at  $T_A = 25^{\circ}C$

- Latchup Performance Exceeds 100 mA

- QFN-16/TSSOP-16 Packages

- ESD Performance:

- ♦ Human Body Model; > 2000 V

- Machine Model; > 200 V

- Functionally Similar to the Popular 74VHC595

- These Devices are Pb-Free and are RoHS Compliant

## ON Semiconductor®

http://onsemi.com

#### MARKING DIAGRAMS

QFN-16 MN SUFFIX CASE 485G

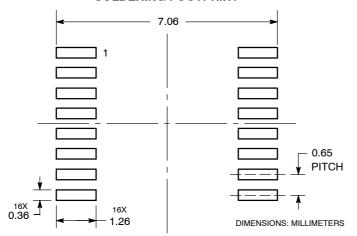

TSSOP-16 DT SUFFIX CASE 948F

A = Assembly Location

L = Wafer Lot Y = Year W = Work Week ■ Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

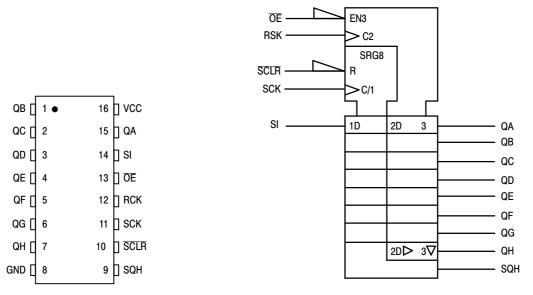

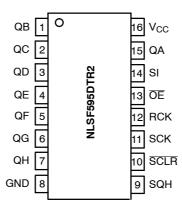

Figure 1. Pin Assignment (TSSOP-16)

Figure 2. IEC Logic Symbol

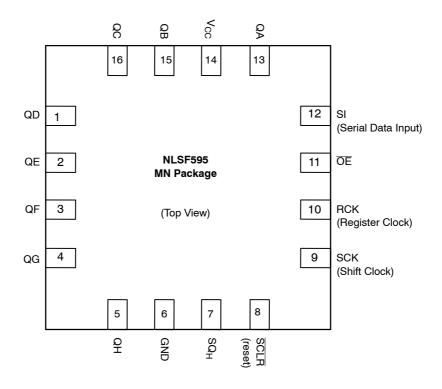

Figure 3. Pin Assignment (QFN-16)

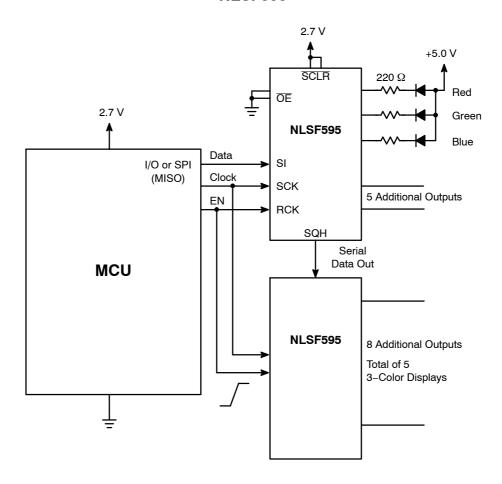

Figure 4. Expanded Logic Diagram

#### **MAXIMUM RATINGS**

| Symbol               | Parameter                                                                 | Value                        | Units |

|----------------------|---------------------------------------------------------------------------|------------------------------|-------|

| V <sub>CC</sub>      | Positive DC Supply Voltage                                                | -0.5 to +7.0                 | V     |

| V <sub>IN</sub>      | Digital Input Voltage                                                     | -0.5 to +7.0                 | V     |

| V <sub>OUT</sub>     | DC Output Voltage                                                         | -0.5 to V <sub>CC</sub> +7.0 | V     |

| I <sub>IK</sub>      | Input Diode Current                                                       | -20                          | mA    |

| I <sub>OK</sub>      | Output Diode Current                                                      | ±50                          | mA    |

| I <sub>OUT</sub>     | DC Output Current, per Pin                                                | +50                          | mA    |

| I <sub>CC</sub>      | DC Supply Current, V <sub>CC</sub> and GND Pins                           | ±75                          | mA    |

| P <sub>D</sub>       | Power Dissipation in Still Air                                            | 450                          | mW    |

| T <sub>STG</sub>     | Storage Temperature Range                                                 | -65 to +150                  | °C    |

| I <sub>LATCHUP</sub> | Latchup Performance Above V <sub>CC</sub> and Below GND at 125°C (Note 1) | ±300                         | mA    |

| $\theta_{\sf JA}$    | Thermal Resistance, Junction-to-Ambient                                   | 128                          | °C/W  |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

1. Tested to EIA/JESD78

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                          | Characteristics                                                                                               | Min | Max             | Units |

|---------------------------------|---------------------------------------------------------------------------------------------------------------|-----|-----------------|-------|

| V <sub>CC</sub>                 | DC Supply Voltage                                                                                             | 2.0 | 5.5             | V     |

| V <sub>IN</sub>                 | DC Input Voltage                                                                                              | 0   | 5.5             | V     |

| V <sub>OUT</sub>                | DC Output Voltage                                                                                             | 0   | V <sub>CC</sub> | V     |

| T <sub>A</sub>                  | Operating Temperature Range, all Package Types                                                                | -55 | 125             | °C    |

| t <sub>r</sub> , t <sub>f</sub> | Input Rise or Fall Time $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ $V_{CC} = 5.0 \text{ V} \pm 0.5 \text{ V}$ | 0   | 50<br>15        | ns/V  |

## **FUNCTION TABLE**

|                                                      |                 |                         | Inputs                  |                       |                          |                                                      | Resulting F                       | unction                          |                                  |

|------------------------------------------------------|-----------------|-------------------------|-------------------------|-----------------------|--------------------------|------------------------------------------------------|-----------------------------------|----------------------------------|----------------------------------|

| Operation                                            | Reset<br>(SCLR) | Serial<br>Input<br>(SI) | Shift<br>Clock<br>(SCK) | Reg<br>Clock<br>(RCK) | Output<br>Enable<br>(OE) | Shift<br>Register<br>Contents                        | Storage<br>Register<br>Contents   | Serial<br>Output<br>(SQH)        | Parallel<br>Outputs<br>(QA – QH) |

| Clear shift register                                 | L               | Х                       | Х                       | L, H, ↓               | L                        | L                                                    | U                                 | L                                | U                                |

| Shift data into shift register                       | Н               | D                       | 1                       | L, H, ↓               | L                        | $D \rightarrow SR_A;$<br>$SR_N \rightarrow SR_{N+1}$ | U                                 | SR <sub>G</sub> →SR <sub>H</sub> | U                                |

| Registers remains unchanged                          | Н               | Х                       | L, H, ↓                 | Х                     | L                        | U                                                    | **                                | U                                | **                               |

| Transfer shift register contents to storage register | Н               | Х                       | L, H, ↓                 | 1                     | L                        | U                                                    | SR <sub>N</sub> →STR <sub>N</sub> | *                                | SR <sub>N</sub>                  |

| Storage register remains unchanged                   | Х               | Х                       | Х                       | L, H, ↓               | L                        | *                                                    | U                                 | *                                | U                                |

| Enable parallel outputs                              | Х               | Х                       | Х                       | Х                     | L                        | *                                                    | **                                | *                                | Enabled                          |

| Force outputs into high impedance state              | Х               | Х                       | Х                       | Х                     | Н                        | *                                                    | **                                | *                                | Z                                |

SR = shift register contents

D = data (L, H) logic level

<sup>↓ =</sup> High-to-Low

<sup>\* =</sup> depends on Reset and Shift Clock inputs

U = remains unchanged STR = storage register contents

<sup>↑ =</sup> Low-to-High

<sup>\*\* =</sup> depends on Register Clock input

## DC ELECTRICAL CHARACTERISTICS

|                               |                                                                                                            |                                                                                              | v <sub>cc</sub>          | 1                          | Γ <sub>A</sub> = 25 | °C                          | T <sub>A</sub> ≤           | 85°C                        | T <sub>A</sub> ≤           | 125°C                       |       |

|-------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------|----------------------------|---------------------|-----------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------|-------|

| Symbol                        | Parameter                                                                                                  | Test Conditions                                                                              | (V)                      | Min                        | Тур                 | Max                         | Min                        | Max                         | Min                        | Max                         | Units |

| V <sub>IH</sub>               | Minimum High-Level Input<br>Voltage                                                                        |                                                                                              | 2.0<br>3.0<br>4.5<br>5.5 | 1.5<br>2.1<br>3.15<br>3.85 |                     |                             | 1.5<br>2.1<br>3.15<br>3.85 |                             | 1.5<br>2.1<br>3.15<br>3.85 |                             | V     |

| V <sub>IL</sub>               | Maximum Low-Level Input<br>Voltage                                                                         |                                                                                              | 2.0<br>3.0<br>4.5<br>5.5 |                            |                     | 0.59<br>0.9<br>1.35<br>1.65 |                            | 0.59<br>0.9<br>1.35<br>1.65 |                            | 0.59<br>0.9<br>1.35<br>1.65 | V     |

| V <sub>OH</sub>               | Minimum High-Level<br>Serial Output Only<br>Output Voltage                                                 | $V_{IN} = V_{IH} \text{ or } V_{IL}$ $I_{OH} = -50  \mu\text{A}$                             | 2.0<br>3.0<br>4.5        | 1.9<br>2.9<br>4.4          | 2.0<br>3.0<br>4.5   |                             | 1.9<br>2.9<br>4.4          |                             | 1.9<br>2.9<br>4.4          |                             | V     |

| $V_{IN} = V_{IH}$ or $V_{IL}$ |                                                                                                            | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$I_{OH} = -4 \text{ mA}$<br>$I_{OH} = -8 \text{ mA}$ | 3.0<br>4.5               | 2.58<br>3.94               |                     |                             | 2.48<br>3.80               |                             | 2.34<br>3.66               |                             |       |

| V <sub>OL</sub>               | Maximum Low-Level Output<br>Voltage<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                | I <sub>OL</sub> = 50 μA                                                                      | 2.0<br>3.0<br>4.5        |                            | 0.0<br>0.0<br>0.0   | 0.1<br>0.1<br>0.1           |                            | 0.1<br>0.1<br>0.1           |                            | 0.1<br>0.1<br>0.1           | V     |

|                               |                                                                                                            | I <sub>OL</sub> = 4 mA<br>I <sub>OL</sub> = 8 mA                                             | 3.0<br>4.5               |                            |                     | 0.36<br>0.36                |                            | 0.44<br>0.44                |                            | 0.52<br>0.52                |       |

| V <sub>OL2</sub>              | Maximum Low-Level Output<br>Voltage with Max. Load<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OL</sub> = 20 mA<br>I <sub>OL</sub> = 25 mA                                           | 3.0<br>4.5               |                            | 0.8<br>0.5          | 1.0<br>0.6                  |                            | 1.1<br>0.7                  |                            | 1.25<br>0.8                 | V     |

| I <sub>IN</sub>               | Maximum Input Leakage<br>Current                                                                           | V <sub>IN</sub> = 5.5 V or<br>GND                                                            | 0 to 5.5                 |                            |                     | ±0.1                        |                            | ±1.0                        |                            | ±1.0                        | μΑ    |

| I <sub>CC</sub>               | Maximum Quiescent Supply Current                                                                           | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                     | 5.5                      |                            |                     | 4.0                         |                            | 40.0                        |                            | 40.0                        | μΑ    |

| l <sub>OZ</sub>               | Three-State Output Off-State<br>Current<br>QA-QH                                                           | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$V_{OUT} = V_{CC} \text{ or }$<br>GND                | 5.5                      |                            |                     | ±0.25                       |                            | ±2.5                        |                            | ±2.5                        | μΑ    |

| I <sub>LKG</sub>              | Active (2) State Off Output<br>Leakage Current<br>QA-QH                                                    | $V_{IN} = V_{IH} \text{ or } V_{IL}$<br>$V_{OUT} = V_{CC} \text{ or }$<br>GND                | 5.5                      |                            |                     | ±0.25                       |                            | ±2.5                        |                            | ±2.5                        | μΑ    |

| I <sub>OFF</sub>              | Power Off<br>Output Leakage<br>All Outputs                                                                 | V <sub>IN</sub> = 0 or 5.5 V<br>V <sub>OUT</sub> = 5.5 V                                     | 0                        |                            |                     | ±0.25                       |                            | ±2.5                        |                            | ±2.5                        | μΑ    |

## AC ELECTRICAL CHARACTERISTICS (Input $t_r = t_f = 3.0 \text{ ns}$ )

|                                        |                                                                           |                                                                   |                                                                  | 1   | A = 25°                   | С                          | T <sub>A</sub> ≤         | 85°C                        | T <sub>A</sub> ≤ 125°C   |                             |       |

|----------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|-----|---------------------------|----------------------------|--------------------------|-----------------------------|--------------------------|-----------------------------|-------|

| Symbol                                 | Parameter                                                                 | Test Condi                                                        | tions                                                            | Min | Тур                       | Max                        | Min                      | Max                         | Min                      | Max                         | Units |

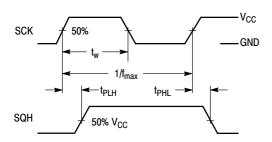

| f <sub>max</sub>                       | Maximum Clock Frequency                                                   | $V_{CC} = 3.3 \pm 0.3 \text{ V}$                                  |                                                                  | 80  | 150                       |                            | 70                       |                             | 70                       |                             | MHz   |

|                                        | (50% Duty Cycle)                                                          | $V_{CC} = 5.0 \pm 0.5 \text{ V}$                                  |                                                                  | 135 | 185                       |                            | 115                      |                             | 115                      |                             |       |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay, SCK to SQH                                             | $V_{CC} = 3.3 \pm 0.3 \text{ V}$                                  | $C_L = 15 \text{ pF}$<br>$C_L = 50 \text{ pF}$                   |     | 8.8<br>11.3               | 13.0<br>16.5               | 1.0<br>1.0               | 15.0<br>18.5                | 1.0<br>1.0               | 15.0<br>18.5                | ns    |

|                                        |                                                                           | $V_{CC} = 5.0 \pm 0.5 \text{ V}$                                  | $C_L = 15 pF$<br>$C_L = 50 pF$                                   |     | 6.2<br>7.7                | 8.2<br>10.2                | 1.0<br>1.0               | 9.4<br>11.4                 | 1.0<br>1.0               | 9.4<br>11.4                 |       |

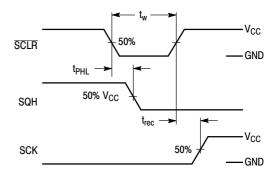

| t <sub>PHL</sub>                       | Propagation Delay,<br>SCLR to SQH                                         | $V_{CC} = 3.3 \pm 0.3 \text{ V}$                                  | C <sub>L</sub> = 15 pF<br>C <sub>L</sub> = 50 pF                 |     | 8.4<br>10.9               | 12.8<br>16.3               | 1.0<br>1.0               | 13.7<br>17.2                | 1.0<br>1.0               | 13.7<br>17.2                | ns    |

|                                        |                                                                           | $V_{CC} = 5.0 \pm 0.5 \text{ V}$                                  | $C_L = 15 pF$<br>$C_L = 50 pF$                                   |     | 5.9<br>7.4                | 8.0<br>10.0                | 1.0<br>1.0               | 9.1<br>11.1                 | 1.0<br>1.0               | 9.1<br>11.1                 |       |

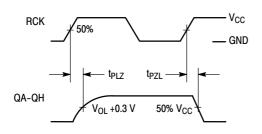

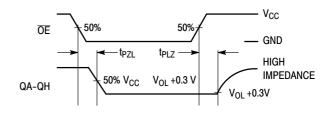

| t <sub>PLZ</sub>                       | Output Disable Time<br>RCK to QA-QH<br>Output Enable Time<br>RCK to QA-QH | $V_{CC} = 3.3 \pm 0.3 \text{ V}$ $V_{CC} = 5.0 \pm 0.5 \text{ V}$ | $C_L$ = 15 pF<br>$C_L$ = 50 pF<br>$C_L$ = 15 pF<br>$C_L$ = 50 pF |     | 7.7<br>10.2<br>5.4<br>6.9 | 11.9<br>15.4<br>7.4<br>9.4 | 1.0<br>1.0<br>1.0<br>1.0 | 13.5<br>17.0<br>8.5<br>10.5 | 1.0<br>1.0<br>1.0<br>1.0 | 13.5<br>17.0<br>8.5<br>10.5 | ns    |

| t <sub>PZL</sub>                       | Output Disable Time<br>RCK to QA-QH<br>Output Enable Time<br>RCK to QA-QH | $V_{CC} = 3.3 \pm 0.3 \text{ V}$ $V_{CC} = 5.0 \pm 0.5 \text{ V}$ | $C_L$ = 15 pF<br>$C_L$ = 50 pF<br>$C_L$ = 15 pF<br>$C_L$ = 50 pF |     | 7.7<br>10.2<br>5.4<br>6.9 | 11.9<br>15.4<br>7.4<br>9.4 | 1.0<br>1.0<br>1.0<br>1.0 | 13.5<br>17.0<br>8.5<br>10.5 | 1.0<br>1.0<br>1.0<br>1.0 | 13.5<br>17.0<br>8.5<br>10.5 | ns    |

| t <sub>PZL</sub>                       | Output Enable Time,<br>OE to QA-QH                                        | $V_{CC}$ = 3.3 ± 0.3 V $R_L$ = 1 k $\Omega$                       | C <sub>L</sub> = 15 pF<br>C <sub>L</sub> = 50 pF                 |     | 7.5<br>9.0                | 11.5<br>15.0               | 1.0<br>1.0               | 13.5<br>17.0                | 1.0<br>1.0               | 13.5<br>17.0                | ns    |

|                                        |                                                                           | $V_{CC} = 5.0 \pm 0.5 \text{ V}$ $R_L = 1 \text{ k}\Omega$        | $C_L = 15 pF$<br>$C_L = 50 pF$                                   |     | 4.8<br>8.3                | 8.6<br>10.6                | 1.0<br>1.0               | 10.0<br>12.0                | 1.0<br>1.0               | 10.0<br>12.0                |       |

| t <sub>PLZ</sub>                       | Output Disable Time,<br>OE to QA-QH                                       | $V_{CC} = 3.3 \pm 0.3 \text{ V}$ $R_L = 1 \text{ k}\Omega$        | C <sub>L</sub> = 50 pF                                           |     | 12.1                      | 15.7                       | 1.0                      | 16.2                        | 1.0                      | 16.2                        | ns    |

|                                        |                                                                           | $V_{CC}$ = 5.0 ± 0.5 V $R_L$ = 1 k $\Omega$                       | C <sub>L</sub> = 50 pF                                           |     | 7.6                       | 10.3                       | 1.0                      | 11.0                        | 1.0                      | 11.0                        |       |

| C <sub>IN</sub>                        | Input Capacitance                                                         |                                                                   |                                                                  |     | 4                         | 10                         |                          | 10                          |                          | 10                          | pF    |

| C <sub>OUT</sub>                       | Three-State Output Capacitance (Output in High-Impedance State), QA-QH    |                                                                   |                                                                  |     | 6                         |                            |                          | 10                          |                          | 10                          | pF    |

|          |                                        | Typical @ 25°C, V <sub>CC</sub> = 5.0 V |    |

|----------|----------------------------------------|-----------------------------------------|----|

| $C_{PD}$ | Power Dissipation Capacitance (Note 2) | 87                                      | pF |

<sup>2.</sup> C<sub>PD</sub> is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load. Average operating current can be obtained by the equation: I<sub>CC(OPR)</sub> = C<sub>PD</sub> • V<sub>CC</sub> • f<sub>in</sub> + I<sub>CC</sub>. C<sub>PD</sub> is used to determine the no–load dynamic power consumption; P<sub>D</sub> = C<sub>PD</sub> • V<sub>CC</sub><sup>2</sup> • f<sub>in</sub> + I<sub>CC</sub> • V<sub>CC</sub>.

## NOISE CHARACTERISTICS (Input $t_{\text{f}}$ = $t_{\text{f}}$ = 3.0 ns, $C_{\text{L}}$ = 50 pF, $V_{\text{CC}}$ = 5.0 V)

|                  |                                              | T <sub>A</sub> = 25°C |      |       |

|------------------|----------------------------------------------|-----------------------|------|-------|

| Symbol           | Characteristic                               | Тур                   | Max  | Units |

| V <sub>OLP</sub> | Quiet Output Maximum Dynamic V <sub>OL</sub> | 0.8                   | 1.0  | V     |

| V <sub>OLV</sub> | Quiet Output Minimum Dynamic V <sub>OL</sub> | -0.8                  | -1.0 | V     |

| $V_{IHD}$        | Minimum High Level Dynamic Input Voltage     |                       | 3.5  | V     |

| V <sub>ILD</sub> | Maximum Low Level Dynamic Input Voltage      |                       | 1.5  | V     |

## **TIMING REQUIREMENTS** (Input $t_r = t_f = 3.0$ ns)

|                    |                            | V <sub>CC</sub> | T <sub>A</sub> = | = 25°C     | T <sub>A</sub> = - 40 to 85°C | T <sub>A</sub> = - 55 to 125°C |       |

|--------------------|----------------------------|-----------------|------------------|------------|-------------------------------|--------------------------------|-------|

| Symbol             | Parameter                  | v               | Тур              | Limit      | Limit                         | Limit                          | Units |

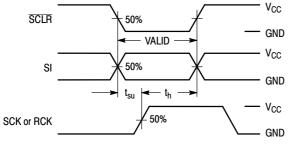

| t <sub>su</sub>    | Setup Time, SI to SCK      | 3.3<br>5.0      |                  | 3.5<br>3.0 | 3.5<br>3.0                    | 3.5<br>3.0                     | ns    |

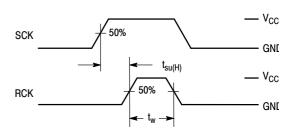

| t <sub>su(H)</sub> | Setup Time, SCK to RCK     | 3.3<br>5.0      |                  | 8.0<br>5.0 | 8.5<br>5.0                    | 8.5<br>5.0                     | ns    |

| t <sub>su(L)</sub> | Setup Time, SCLR to RCK    | 3.3<br>5.0      |                  | 8.0<br>5.0 | 9.0<br>5.0                    | 9.0<br>5.0                     | ns    |

| t <sub>h</sub>     | Hold Time, SI to SCK       | 3.3<br>5.0      |                  | 1.5<br>2.0 | 1.5<br>2.0                    | 1.5<br>2.0                     | ns    |

| t <sub>h(L)</sub>  | Hold Time, SCLR to RCK     | 3.3<br>5.0      |                  | 0          | 0<br>0                        | 1.0<br>1.0                     | ns    |

| t <sub>rec</sub>   | Recovery Time, SCLR to SCK | 3.3<br>5.0      |                  | 3.0<br>2.5 | 3.0<br>2.5                    | 3.0<br>2.5                     | ns    |

| t <sub>w</sub>     | Pulse Width, SCK or RCK    | 3.3<br>5.0      |                  | 5.0<br>5.0 | 5.0<br>5.0                    | 5.0<br>5.0                     | ns    |

| t <sub>w(L)</sub>  | Pulse Width, SCLR          | 3.3<br>5.0      |                  | 5.0<br>5.0 | 5.0<br>5.0                    | 5.0<br>5.0                     | ns    |

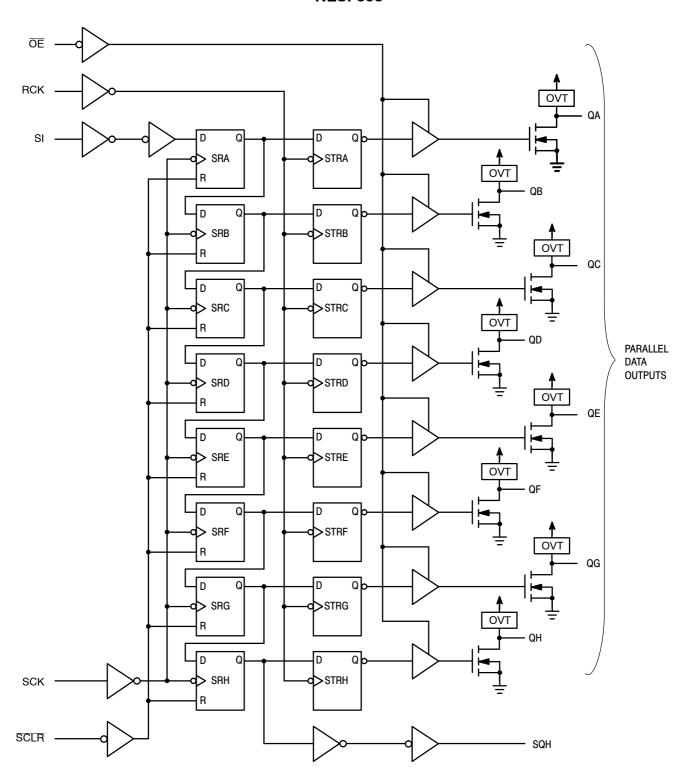

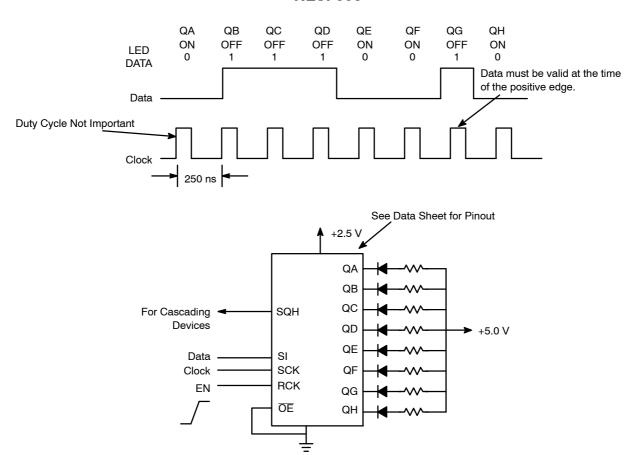

Figure 5. NLSF595 Shown Driving 5 3-Color LEDs

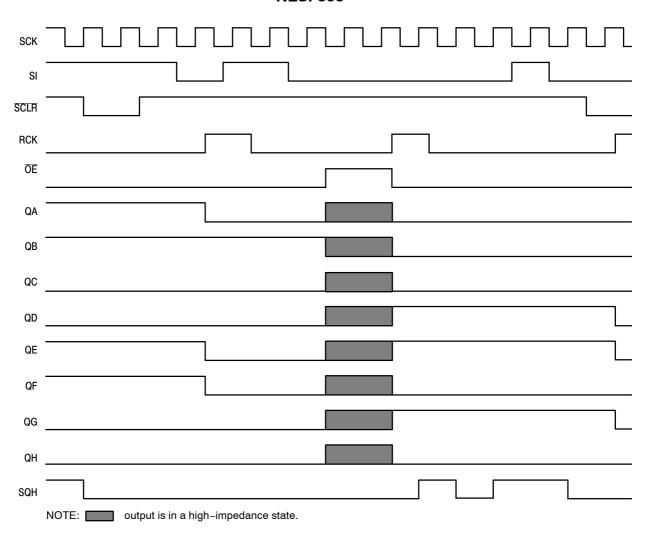

## **SWITCHING WAVEFORMS**

Figure 6.

Figure 7.

Figure 8.

Figure 9.

Figure 10.

Figure 11.

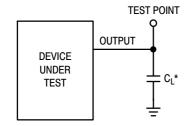

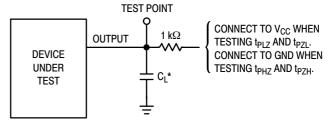

#### **TEST CIRCUITS**

\*Includes all probe and jig capacitance

Figure 12.

\*Includes all probe and jig capacitance

Figure 13.

Figure 14. Timing Diagram

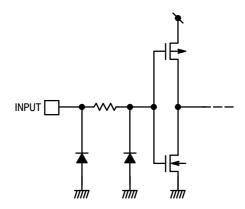

Figure 15. Input Equivalent Circuit

Figure 16. NLSF595 Example

## **ORDERING INFORMATION**

|                        |                      | Devi       | ce Nomenc          | lature            |                       |                     |                       |  |

|------------------------|----------------------|------------|--------------------|-------------------|-----------------------|---------------------|-----------------------|--|

| Device Order<br>Number | Circuit<br>Indicator | Technology | Device<br>Function | Package<br>Suffix | Tape & Reel<br>Suffix | Package             | Shipping <sup>†</sup> |  |

| NLSF595MNR2G           | NL                   | SF         | 595                | MN                | R2                    | QFN<br>(Pb-Free)    | 13-inch/3000 Unit     |  |

| NLSF595DTR2G           | NL                   | SF         | 595                | DT                | R2                    | TSSOP*<br>(Pb-Free) | 13-inch/2500 Unit     |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*This package is inherently Pb–Free.

PIN ONE LOCATION

2X 0.10 C

2X 0.10 C

// 0.05 C

0.05 C

**DATE 08 OCT 2021**

## NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30 MM FROM THE TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS.

THE TERMINALS.

DETAIL B

ALTERNATE

CONSTRUCTIONS

DETAIL A

ALTERNATE TERMINAL

CONSTRUCTIONS

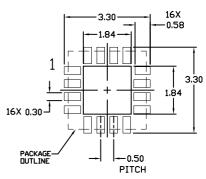

|     | MILLIME  |          |      |  |  |

|-----|----------|----------|------|--|--|

| DIM | MIN.     | N□M.     | MAX. |  |  |

| Α   | 0.80     | 0.90     | 1.00 |  |  |

| A1  | 0.00     | 0.03     | 0.05 |  |  |

| A3  |          | 0.20 REF |      |  |  |

| b   | 0.18     | 0.30     |      |  |  |

| D   | 3.00 BSC |          |      |  |  |

| D2  | 1.65     | 1.75     | 1.85 |  |  |

| E   |          | 3.00 BSC | ;    |  |  |

| E2  | 1.65     | 1.75     | 1.85 |  |  |

| e   |          | 0.50 BSC | ;    |  |  |

| k   | 0.18 TYP |          |      |  |  |

| L   | 0.30     | 0.50     |      |  |  |

| L1  | 0.00     | 0.08     | 0.15 |  |  |

|     |          |          |      |  |  |

## MOUNTING FOOTPRINT

| DETAIL A         |

|------------------|

| ⊕ 0.10 CAB 9  E2 |

BOTTOM VIEW

TOP VIEW

□(□)□

SIDE VIEW

DETAIL B

SEATING PLANE

Ċ

GENERIC

MARKING DIAGRAM\*

XXXXX = Specific Device Code A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98AON04795D     | Electronic versions are uncontrolled except when accessed directly from the Document Repositive Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |  |

|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| DESCRIPTION:     | QFN16 3X3, 0.5P |                                                                                                                                                                                 | PAGE 1 OF 1 |  |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

0.10 (0.004)

D

-T- SEATING PLANE

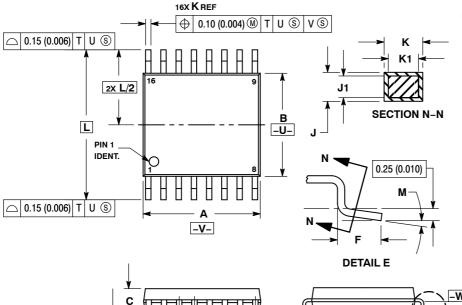

TSSOP-16 CASE 948F-01 **ISSUE B**

**DATE 19 OCT 2006**

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR

- PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.

- TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

- DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-

|     | MILLIN   | IETERS   | INC       | HES       |  |

|-----|----------|----------|-----------|-----------|--|

| DIM | MIN      | MAX      | MIN       | MAX       |  |

| Α   | 4.90     | 5.10     | 0.193     | 0.200     |  |

| В   | 4.30     | 4.50     | 0.169     | 0.177     |  |

| С   |          | 1.20     |           | 0.047     |  |

| D   | 0.05     | 0.15     | 0.002     | 0.006     |  |

| F   | 0.50     | 0.75     | 0.020     | 0.030     |  |

| G   | 0.65 BSC |          | 0.026 BSC |           |  |

| Н   | 0.18     | 0.28     | 0.007     | 0.011     |  |

| J   | 0.09     | 0.20     | 0.004     | 0.008     |  |

| J1  | 0.09     | 0.16     | 0.004     | 0.006     |  |

| Κ   | 0.19     | 0.30     | 0.007     | 0.012     |  |

| K1  | 0.19     | 0.25     | 0.007     | 0.010     |  |

| Г   |          | 6.40 BSC |           | 0.252 BSC |  |

| М   | 0 0      | 0 0      | 0 °       | 0         |  |

## **SOLDERING FOOTPRINT**

G

## **GENERIC MARKING DIAGRAM\***

168888888 XXXX XXXX o ALYW 188888888

XXXX = Specific Device Code Α = Assembly Location = Wafer Lot L

Υ = Year W = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

| DOCUMENT NUMBER: | 98ASH70247A | Electronic versions are uncontrolled except when accessed directly from the Document Repositor Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSSOP-16    |                                                                                                                                                                                | PAGE 1 OF 1 |

**DETAIL E**

🕠 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for LED Lighting Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

LV5235V-MPB-H MB39C602PNF-G-JNEFE1 MIC2871YMK-T5 AL1676-10BS7-13 AL1676-20AS7-13 AP5726WUG-7 ICL8201

IS31BL3228B-UTLS2-TR IS31BL3506B-TTLS2-TR AL3157F-7 AP5725FDCG-7 AP5726FDCG-7 LV52204MTTBG AP5725WUG-7

STP4CMPQTR NCL30086BDR2G CAT4004BHU2-GT3 LV52207AXA-VH AP1694AS-13 TLE4242EJ AS3688 IS31LT3172-GRLS4-TR

TLD2311EL KTD2694EDQ-TR KTZ8864EJAA-TR IS32LT3174-GRLA3-TR MP2488DN-LF-Z NLM0010XTSA1 AL1676-20BS7-13

ZXLD1370QESTTC MPQ7220GF-AEC1-P MPQ7220GR-AEC1-P MPQ4425BGJ-AEC1-P MPQ7220GF-AEC1-Z MPQ7220GR-AEC1-Z

MPQ4425BGJ-AEC1-Z NCL30486A2DR2G IS31FL3737B-QFLS4-TR IS31FL3239-QFLS4-TR KTD2058EUAC-TR KTD2037EWE-TR

DIO5662ST6 IS31BL3508A-TTLS2-TR KTD2026BEWE-TR MAX20052CATC/V+ MAX25606AUP/V+ BD6586MUV-E2 BD9206EFV-E2 BD9416FS-E2 LYT4227E