# **SRV05-4**

# **ESD Protection Diode Array**Low Clamping Voltage

The SRV05-4MR6 surge protection is designed to protect high speed data lines from ESD, EFT, and lighting.

#### **Features**

- Protects 4 I/O Lines

- Low Working Voltage: 5 V

- Low Clamping Voltage

- Low Capacitance (<5 pF) for High Speed Interfaces

- Transient Protection for High Speed Lines to:

IEC61000-4-2 (ESD) ±15 kV (air), ±8 kV (contact)

IEC61000-4-4 (EFT) 40 A

IEC61000-4-5 (Lightning) 12 A

- TSOP-6 is Footprint Compatible with SOT-23 6 Lead, SC-59 6 Lead and SC-74

- UL Flammability Rating of 94 V-0

- This is a Pb-Free Device

# **Typical Applications**

- High Speed Communication Line Protection

- USB 1.1 and 2.0 Power and Data Line Protection

- Digital Video Interface (DVI)

- Monitors and Flat Panel Displays

#### MAXIMUM RATINGS (T<sub>J</sub> = 25°C unless otherwise noted)

| Rating                                                                                                 | Symbol           | Value                          | Unit |

|--------------------------------------------------------------------------------------------------------|------------------|--------------------------------|------|

| Peak Power Dissipation<br>8 x 20 μs @ T <sub>A</sub> = 25°C (Note 1)                                   | $P_{pk}$         | 300                            | W    |

| Operating Junction Temperature Range                                                                   | T <sub>J</sub>   | -55 to +125                    | °C   |

| Storage Temperature Range                                                                              | T <sub>stg</sub> | -55 to +150                    | °C   |

| Lead Solder Temperature –<br>Maximum (10 Seconds)                                                      | T <sub>L</sub>   | 260                            | °C   |

| Human Body Model (HBM)<br>Machine Model (MM)<br>IEC 61000-4-2 Air (ESD)<br>IEC 61000-4-2 Contact (ESD) | ESD              | 16000<br>400<br>30000<br>30000 | V    |

| IEC 61000-4-4 (5/50 ns)                                                                                | EFT              | 40                             | Α    |

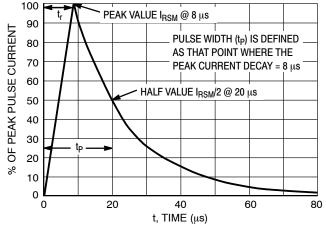

| IEC 61000-4-5 (8 x 20 μs)                                                                              | -                | 12                             | Α    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Non-repetitive current pulse per Figure 5 (Pin 5 to Pin 2)

See Application Note AND8308/D for further description of survivability specs.

# ON Semiconductor®

www.onsemi.com

# LOW CAPACITANCE SURGE PROTECTION ARRAY 300 WATTS PEAK POWER 6 VOLTS

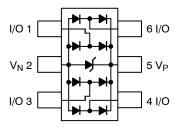

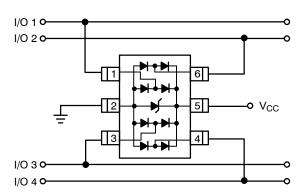

# PIN CONFIGURATION AND SCHEMATIC

TSOP-6 CASE 318G PLASTIC

# MARKING DIAGRAM

63 = Specific Device Code

M = Date Code

■ = Pb-Free Package

(Note: Microdot may be in either location)

\*Date Code orientation may vary depending upon manufacturing location.

# **ORDERING INFORMATION**

| Device        | Package             | Shipping         |

|---------------|---------------------|------------------|

| SRV05-4MR6T1G | TSOP-6<br>(Pb-Free) | 3000/Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

1

#### **ELECTRICAL CHARACTERISTICS**

(T<sub>A</sub> = 25°C unless otherwise noted)

| Symbol          | Parameter                                          |

|-----------------|----------------------------------------------------|

| I <sub>PP</sub> | Maximum Reverse Peak Pulse Current                 |

| V <sub>C</sub>  | Clamping Voltage @ I <sub>PP</sub>                 |

| $V_{RWM}$       | Working Peak Reverse Voltage                       |

| I <sub>R</sub>  | Maximum Reverse Leakage Current @ V <sub>RWM</sub> |

| $V_{BR}$        | Breakdown Voltage @ I <sub>T</sub>                 |

| I <sub>T</sub>  | Test Current                                       |

| I <sub>F</sub>  | Forward Current                                    |

| V <sub>F</sub>  | Forward Voltage @ I <sub>F</sub>                   |

| P <sub>pk</sub> | Peak Power Dissipation                             |

| С               | Capacitance @ V <sub>R</sub> = 0 and f = 1.0 MHz   |

<sup>\*</sup>See Application Note AND8308/D for detailed explanations of datasheet parameters.

# ELECTRICAL CHARACTERISTICS (T<sub>J</sub>=25°C unless otherwise specified)

| Parameter               | Symbol           | Conditions                                             | Min | Тур         | Max  | Unit |

|-------------------------|------------------|--------------------------------------------------------|-----|-------------|------|------|

| Reverse Working Voltage | V <sub>RWM</sub> | (Note 2)                                               |     |             | 5.0  | V    |

| Breakdown Voltage       | V <sub>BR</sub>  | I <sub>T</sub> =1 mA, (Note 3)                         | 6.0 |             |      | V    |

| Reverse Leakage Current | I <sub>R</sub>   | V <sub>RWM</sub> = 5 V                                 |     |             | 5.0  | μΑ   |

| Clamping Voltage        | V <sub>C</sub>   | I <sub>PP</sub> = 1 A (Note 4)                         |     |             | 12.5 | V    |

| Clamping Voltage        | V <sub>C</sub>   | I <sub>PP</sub> = 5 A (Note 4)                         |     |             | 17.5 | V    |

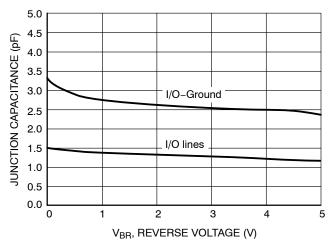

| Junction Capacitance    | CJ               | V <sub>R</sub> = 0 V, f=1 MHz between I/O Pins and GND |     | 3.0         | 5.0  | pF   |

| Junction Capacitance    | CJ               | V <sub>R</sub> = 0 V, f=1 MHz between I/O Pins         |     | 1.5         | 3.0  | pF   |

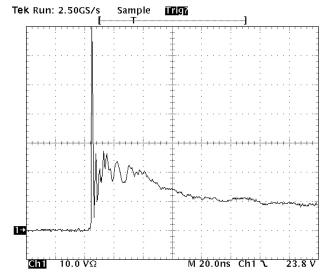

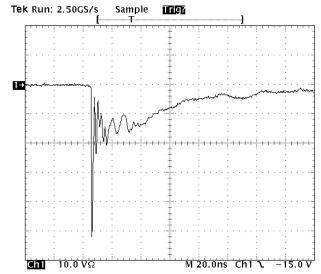

| Clamping Voltage        | V <sub>C</sub>   | Per IEC 61000-4-2 (Note 5)                             | F   | igure 1 and | 2    | V    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 2. Surge protection devices are normally selected according to the working peak reverse voltage (V<sub>RWM</sub>), which should be equal or greater than the DC or continuous peak operating voltage level.

- 3. V<sub>BR</sub> is measured at pulse test current I<sub>T</sub>.

4. Non-repetitive current pulse per Figure 5 (Any I/O Pin to Ground)

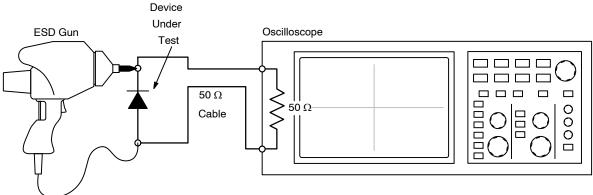

- 5. For test procedure see Figures 3 and 4 and Application Note AND8307/D.

Figure 1. ESD Clamping Voltage Screenshot Positive 8 kV Contact per IEC61000-4-2

Figure 2. ESD Clamping Voltage Screenshot Negative 8 kV Contact per IEC61000-4-2

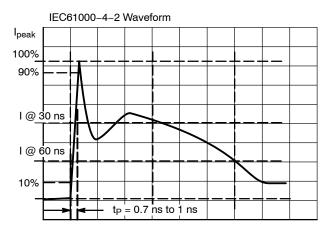

#### IEC 61000-4-2 Spec.

|       | -                      |                              |                         |                         |

|-------|------------------------|------------------------------|-------------------------|-------------------------|

| Level | Test Volt-<br>age (kV) | First Peak<br>Current<br>(A) | Current at<br>30 ns (A) | Current at<br>60 ns (A) |

| 1     | 2                      | 7.5                          | 4                       | 2                       |

| 2     | 4                      | 15                           | 8                       | 4                       |

| 3     | 6                      | 22.5                         | 12                      | 6                       |

| 4     | 8                      | 30                           | 16                      | 8                       |

Figure 3. IEC61000-4-2 Spec

Figure 4. Diagram of ESD Test Setup

The following is taken from Application Note AND8308/D – Interpretation of Datasheet Parameters for ESD Devices.

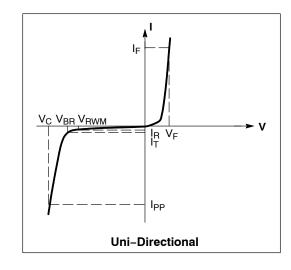

#### **ESD Voltage Clamping**

For sensitive circuit elements it is important to limit the voltage that an IC will be exposed to during an ESD event to as low a voltage as possible. The ESD clamping voltage is the voltage drop across the ESD protection diode during an ESD event per the IEC61000-4-2 waveform. Since the IEC61000-4-2 was written as a pass/fail spec for larger

systems such as cell phones or laptop computers it is not clearly defined in the spec how to specify a clamping voltage at the device level. ON Semiconductor has developed a way to examine the entire voltage waveform across the ESD protection diode over the time domain of an ESD pulse in the form of an oscilloscope screenshot, which can be found on the datasheets for all ESD protection diodes. For more information on how ON Semiconductor creates these screenshots and how to interpret them please refer to AND8307/D.

Figure 5. 8 x 20 μs Pulse Waveform

# SRV05-4

# **TYPICAL PERFORMANCE CURVES**

$(T_J = 25^{\circ}C \text{ unless otherwise noted})$

30

25 20 15 0 0 2 4 6 8 10 12 PEAK PULSE CURRENT (A)

Figure 6. Junction Capacitance vs Reverse Voltage

Figure 7. Clamping Voltage vs. Peak Pulse Current (8 x 20  $\mu$ s Waveform)

#### APPLICATIONS INFORMATION

The new SRV05-4MR6 is a low capacitance surge protection diode array designed to protect sensitive electronics such as communications systems, computers, and computer peripherals against damage due to ESD events or transient overvoltage conditions. Because of its low capacitance, it can be used in high speed I/O data lines. The integrated design of the SRV05-4MR6 offers surge rated, low capacitance steering diodes and a surge protection diode integrated in a single package (TSOP-6). If a transient condition occurs, the steering diodes will drive the transient to the positive rail of the power supply or to ground. The surge protection device protects the power line against overvoltage conditions to avoid damage to the power supply and any downstream components.

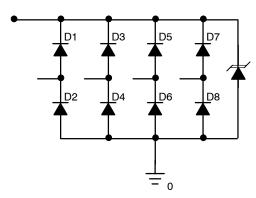

# SRV05-4MR6 Configuration Options

The SRV05–4MR6 is able to protect up to four data lines against transient overvoltage conditions by driving them to a fixed reference point for clamping purposes. The steering diodes will be forward biased whenever the voltage on the protected line exceeds the reference voltage (Vf or  $V_{CC}$  + Vf). The diodes will force the transient current to bypass the sensitive circuit.

Data lines are connected at pins 1, 3, 4 and 6. The negative reference is connected at pin 2. These pins must be connected directly to ground by using a ground plane to minimize the PCB's ground inductance. It is very important to reduce the PCB trace lengths as much as possible to minimize parasitic inductances.

#### Option 1

Protection of four data lines and the power supply using  $V_{CC}$  as reference.

For this configuration, connect pin 5 directly to the positive supply rail ( $V_{CC}$ ), the data lines are referenced to the supply voltage. The internal surge protection diode prevents overvoltage on the supply rail. Biasing of the steering diodes reduces their capacitance.

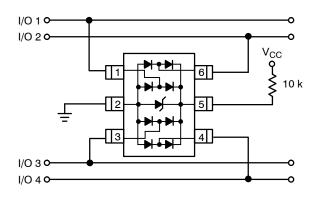

# Option 2

Protection of four data lines with bias and power supply isolation resistor.

The SRV05–4MR6 can be isolated from the power supply by connecting a series resistor between pin 5 and  $V_{CC}$ . A 10 k $\Omega$  resistor is recommended for this application. This will maintain a bias on the internal surge protection and steering diodes, reducing their capacitance.

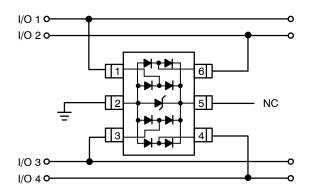

# Option 3

Protection of four data lines using the internal surge protection diode as reference.

In applications lacking a positive supply reference or those cases in which a fully isolated power supply is required, the internal surge protection can be used as the reference. For these applications, pin 5 is not connected. In this configuration, the steering diodes will conduct whenever the voltage on the protected line exceeds the working voltage of the surge protection plus one diode drop  $(Vc = Vf + V_{RWM})$ .

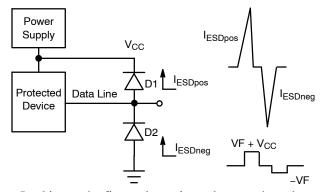

#### **ESD Protection of Power Supply Lines**

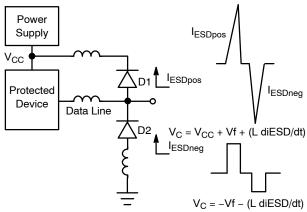

When using diodes for data line protection, referencing to a supply rail provides advantages. Biasing the diodes reduces their capacitance and minimizes signal distortion. Implementing this topology with discrete devices does have disadvantages. This configuration is shown below:

Looking at the figure above, it can be seen that when a positive ESD condition occurs, diode D1 will be forward biased while diode D2 will be forward biased when a negative ESD condition occurs. For slower transient conditions, this system may be approximated as follows:

For positive pulse conditions:

$$Vc = V_{CC} + Vf_{D1}$$

For negative pulse conditions:

$$Vc = -Vf_{D2}$$

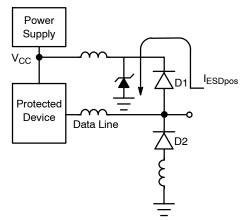

ESD events can have rise times on the order of some number of nanoseconds. Under these conditions, the effect of parasitic inductance must be considered. A pictorial representation of this is shown below.

An approximation of the clamping voltage for these fast transients would be:

For positive pulse conditions:

$$Vc = V_{CC} + Vf + (L di_{ESD}/dt)$$

For negative pulse conditions:

$$Vc = -Vf - (L di_{ESD}/dt)$$

As shown in the formulas, the clamping voltage (Vc) not only depends on the Vf of the steering diodes but also on the L  $d_{iESD}$ /dt factor. A relatively small trace inductance can result in hundreds of volts appearing on the supply rail. This endangers both the power supply and anything attached to that rail. This highlights the importance of good board layout. Taking care to minimize the effects of parasitic inductance will provide significant benefits in transient immunity.

Even with good board layout, some disadvantages are still present when discrete diodes are used to suppress ESD events across datalines and the supply rail. Discrete diodes with good transient power capability will have larger die and therefore higher capacitance. This capacitance becomes problematic as transmission frequencies increase. Reducing capacitance generally requires reducing die size. These small die will have higher forward voltage characteristics at typical ESD transient current levels. This voltage combined with the smaller die can result in device failure.

The ON Semiconductor SRV05-4MR6 was developed to overcome the disadvantages encountered when using discrete diodes for ESD protection. This device integrates a surge protection diode within a network of steering diodes.

Figure 8. SRV05-4MR6 Equivalent Circuit

During an ESD condition, the ESD current will be driven to ground through the surge protection diode as shown below.

The resulting clamping voltage on the protected IC will be:  $Vc = VF + V_{RWM}$ .

The clamping voltage of the surge protection diode is provided in Figure 7 and depends on the magnitude of the ESD current. The steering diodes are fast switching devices with unique forward voltage and low capacitance characteristics.

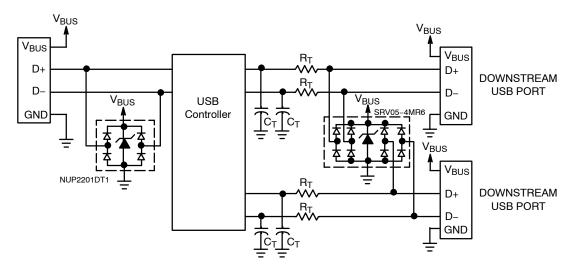

# **TYPICAL APPLICATIONS**

UPSTREAM USB PORT

Figure 9. ESD Protection for USB Port

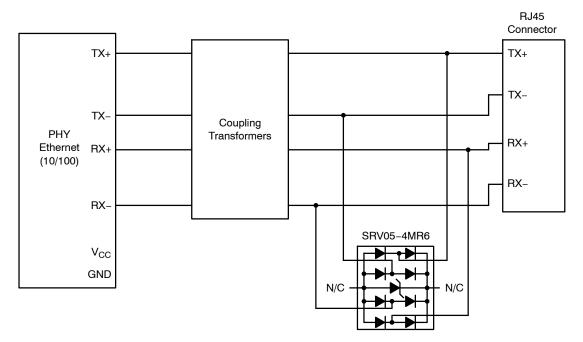

Figure 10. Protection for Ethernet 10/100 (Differential mode)

# SRV05-4

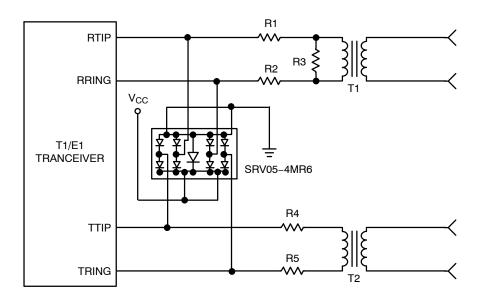

Figure 11. TI/E1 Interface Protection

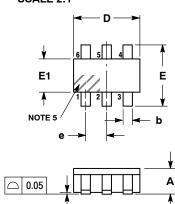

### TSOP-6 CASE 318G-02 **ISSUE V**

12

C SEATING PLANE

**DATE 12 JUN 2012**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM

- LEAD THIORNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D

- AND E1 ARE DETERMINED AT DATUM H.

PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE.

|     | MILLIMETERS |          |      |

|-----|-------------|----------|------|

| DIM | MIN         | NOM      | MAX  |

| Α   | 0.90        | 1.00     | 1.10 |

| A1  | 0.01        | 0.06     | 0.10 |

| b   | 0.25        | 0.38     | 0.50 |

| С   | 0.10        | 0.18     | 0.26 |

| D   | 2.90        | 3.00     | 3.10 |

| E   | 2.50        | 2.75     | 3.00 |

| E1  | 1.30        | 1.50     | 1.70 |

| е   | 0.85        | 0.95     | 1.05 |

| L   | 0.20        | 0.40     | 0.60 |

| L2  |             | 0.25 BSC |      |

| M   | 00          |          | 100  |

**DETAIL Z**

Н

| , , ,                                                                         |                                                                                                            |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| STYLE 1: PIN 1. DRAIN 2. DRAIN 3. GATE 4. SOURCE 5. DRAIN 6. DRAIN            | STYLE 2:<br>PIN 1. EMITTER 2<br>2. BASE 1<br>3. COLLECTOR 1<br>4. EMITTER 1<br>5. BASE 2<br>6. COLLECTOR 2 |

| STYLE 7: PIN 1. COLLECTOR 2. COLLECTOR 3. BASE 4. N/C 5. COLLECTOR 6. EMITTER | STYLE 8: PIN 1. Vbus 2. D(in) 3. D(in)+ 4. D(out)+ 5. D(out) 6. GND                                        |

Δ1

STYLE 13: PIN 1. GATE 1

5. SOURCE 1

2. SOURCE 2

DRAIN 2

3. GATE 2

| 2<br>OR 1 | STYLE 3:<br>PIN 1. ENABLE<br>2. N/C<br>3. R BOOST |  |

|-----------|---------------------------------------------------|--|

| 1         | 4. Vz                                             |  |

|           | 5. V in                                           |  |

| OR 2      | 6. V out                                          |  |

|           |                                                   |  |

|           | CTVI E O:                                         |  |

|         | V in             |

|---------|------------------|

| ъ.      | V out            |

| STYLE 9 | ٥٠               |

|         | LOW VOLTAGE GATE |

|         |                  |

| 2.      | DRAIN            |

| 3       | SOURCE           |

| 6. HIGH VO                            | LTAGE GATE  |

|---------------------------------------|-------------|

| TYLE 15:<br>PIN 1. ANODE<br>2. SOURCE | STY!<br>PIN |

| 3. GATE<br>4. DRAIN                   |             |

4. DRAIN

| YLE 15:                  |

|--------------------------|

| PIN 1. ANODE             |

| <ol><li>SOURCE</li></ol> |

| <ol><li>GATE</li></ol>   |

| <ol><li>DRAIN</li></ol>  |

| 5. N/C                   |

| 6. CATHODE               |

|                          |

|                          |

STYLE 16: PIN 1. ANODE/CATHODE

FMITTER

CATHODE

COLLECTOR

2. BASE

3.

5. ANODE

| E 10:                     | STYL |

|---------------------------|------|

| 1. D(OUT)+                | PIN  |

| 2. GND                    |      |

| <ol><li>D(OUT)-</li></ol> |      |

| 4. D(IN)-                 |      |

| 5. VBUS                   |      |

| <ol><li>D(IN)+</li></ol>  |      |

LE 11: N 1. SOURCE 1 2. DRAIN 2 DRAIN 2 SOURCE 2 5. GATE 1 6. DRAIN 1/GATE 2

STYLE 17: PIN 1. EMITTER

BASE

CATHODE

COLLECTOR

3 ANODE/CATHODE

3. COLLECTOR 1 4. EMITTER 1

BASE 1 6. COLLECTOR 2

STYLE 12: 2. GROUND 3. I/O 4. I/O 6. I/O

STYLE 6: PIN 1. COLLECTOR 2. COLLECTOR

5. COLLECTOR 6. COLLECTOR

3 BASE 4. EMITTER

| 9       | RECOMMENDED<br>SOLDERING FOOTPRI | NT* |

|---------|----------------------------------|-----|

| DRAIN 1 | 6. CATHODE/DRAIN                 | 6.  |

|         | 0. 0                             | ٠.  |

SOURCE

CATHODE/DRAIN

CATHODE/DRAIN

STYLE 14: PIN 1. ANODE

5.

3. GATE

**DIMENSIONS: MILLIMETERS**

# **GENERIC** MARKING DIAGRAM\*

XXX = Specific Device Code Α =Assembly Location

Υ = Year

W = Work Week = Pb-Free Package XXX = Specific Device Code M = Date Code

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present.

| DOCUMENT NUMBER: | 98ASB14888C | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TSOP-6      |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for ESD Suppressors / TVS Diodes category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

60KS200C D12V0H1U2WS-7 D18V0L1B2LP-7B 82356050220 D5V0M5U6V-7 NTE4902 P4KE27CA P6KE11CA P6KE39CA-TP

P6KE8.2A SA110CA SA60CA SA64CA SMBJ12CATR SMBJ8.0A SMLJ30CA-TP ESD101-B1-02ELS E6327 ESD112-B1-02EL E6327

ESD119B1W01005E6327XTSA1 ESD5V0J4-TP ESD5V0L1B02VH6327XTSA1 ESD7451N2T5G 19180-510 CPDT-5V0USP-HF

3.0SMCJ33CA-F 3.0SMCJ36A-F HSPC16701B02TP D3V3Q1B2DLP3-7 D55V0M1B2WS-7 DESD5V0U1BL-7B DRTR5V0U4SL-7

SCM1293A-04SO ESD200-B1-CSP0201 E6327 ESD203-B1-02EL E6327 SM12-7 SMF8.0A-TP SMLJ45CA-TP CEN955 W/DATA

82350120560 82356240030 VESD12A1A-HD1-GS08 CPDUR5V0R-HF CPDUR24V-HF CPDQC5V0U-HF CPDQC5V0USP-HF

CPDQC5V0-HF D1213A-01LP4-7B D1213A-02WL-7 ESDLIN1524BJ-HQ 5KP100A