# STK672-520

# ON Semiconductor®

#### Thick-Film Hybrid IC

# 2-phase Stepping Motor Driver

http://onsemi.com

#### Overview

The STK672-520 is a hybrid IC for use as a unipolar, 2-phase stepping motor driver with PWM current control.

# **Applications**

• Office photocopiers, printers, etc.

#### **Features**

- The motor speed can be controlled by the frequency of an external clock signal.

- 2-phase excitation or 1-2 phase excitation is selected according to switching the state of the MODE pin (low or high).

- The phase is maintained even if the excitation mode is switched in the middle of operation.

- The direction of rotation can be changed by applying a high or low signal to the CWB pin used to select the direction of rotation.

- Supports schmitt input for 2.5V high level input.

- Incorporating a current detection resistor (0.33 $\Omega$ : resistor tolerance  $\pm 2\%$ ), motor current can be set using two external resistors.

- Equipped with an ENABLE pin that, during clock input, allows motor output to be cut-off and resumed later while maintaining the same excitation timing.

# **Specifications**

# Absolute Maximum Ratings at Tc = 25°C

| Parameter                       | Symbol              | Conditions Ratings                              |              | unit |

|---------------------------------|---------------------|-------------------------------------------------|--------------|------|

| Maximum supply voltage 1        | V <sub>CC</sub> max | No signal                                       | 52           | V    |

| Maximum supply voltage 2        | V <sub>DD</sub> max | No signal                                       | -0.3 to +7.0 | V    |

| Input voltage                   | V <sub>IN</sub> max | Logic input pins                                | -0.3 to +7.0 | V    |

| Output current 1                | I <sub>OP</sub> max | 10μA 1 pulse (resistance load)                  | 5            | А    |

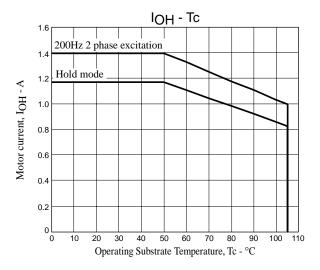

| Output current 2                | I <sub>OH</sub> max | V <sub>DD</sub> =5V, CLOCK≥200Hz                | 1.4          | Α    |

| Allowable power dissipation     | Pd max              | With an arbitrarily large heat sink. Per MOSFET | 10.2         | W    |

| Operating substrate temperature | Tc max              |                                                 | 105          | °C   |

| Junction temperature            | Tj max              |                                                 | 150          | °C   |

| Storage temperature             | Tstg                |                                                 | -40 to +125  | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# Allowable Operating Ranges at Ta=25°C

| Parameter                                   | Symbol            | Conditions                                                                                                     | Ratings                | unit |

|---------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------|------------------------|------|

| Operating supply voltage 1                  | VCC               | With signals applied                                                                                           | 10 to 42               | V    |

| Operating supply voltage 2                  | $V_{DD}$          | With signals applied                                                                                           | 5±5%                   | V    |

| Input high voltage                          | V <sub>IH</sub>   | Pins 8, 9, 10, 11, 12                                                                                          | 2.5 to V <sub>DD</sub> | V    |

| Input low voltage                           | $V_{IL}$          | Pins 8, 9, 10, 11, 12                                                                                          | 0 to 0.6               | V    |

| Output current 1                            | I <sub>OH</sub> 1 | Tc=105°C, CLOCK≥200Hz, Continuous operation, duty=100%                                                         | 1.0                    | А    |

| Output current 2                            | I <sub>OH</sub> 2 | Tc=80°C, CLOCK≥200Hz, Continuous operation, duty=100%, See the motor current (I <sub>OH</sub> ) derating curve | 1.1                    | Α    |

| CLOCK frequency                             | f <sub>CL</sub>   | Minimum pulse width: at least 10μs                                                                             | 0 to 50                | kHz  |

| Phase driver withstand voltage              | V <sub>DSS</sub>  | I <sub>D</sub> =1mA (Tc=25°C)                                                                                  | 100min                 | V    |

| Recommended operating substrate temperature | Тс                | No condensation                                                                                                | 0 to 105               | °C   |

| Recommended Vref range                      | Vref              | Tc=105°C                                                                                                       | 0.14 to 1.62           | V    |

# Electrical Characteristics at Tc=25°C, $V_{CC}$ =24V, $V_{DD}$ =5.0V

| Parameter                      | Symbol          | Conditions                       | min   | typ   | max   | unit |

|--------------------------------|-----------------|----------------------------------|-------|-------|-------|------|

| V <sub>DD</sub> supply current | Icco            | Pin 6 current CLOCK=GND          |       | 3.1   | 7     | mA   |

| Output average current         | loave           | R/L=3Ω/3.8mH in each phase       | 0.148 | 0.164 | 0.180 | Α    |

| FET diode forward voltage      | Vdf             | If=1A (R <sub>L</sub> =23Ω)      |       | 1.2   | 1.8   | V    |

| Output saturation voltage      | Vsat            | $R_L=23\Omega$                   |       | 0.61  | 0.85  | V    |

| Input high voltage             | VIH             | Pins 8, 9, 10, 11, 12            | 2.5   |       |       | V    |

| Input low voltage              | V <sub>IL</sub> | Pins 8, 9, 10, 11, 12            |       |       | 0.6   | V    |

| Input leak current             | IIL             | Pins 8, 9, 10, 11, 12=GND and 5V |       |       | ±10   | μА   |

| Vref input bias current        | I <sub>IB</sub> | Pin 7 =1.0V                      |       | 204   | 216   | μΑ   |

| PWM frequency                  | fc              |                                  | 35    | 45    | 55    | kHz  |

Notes: A fixed-voltage power supply must be used.

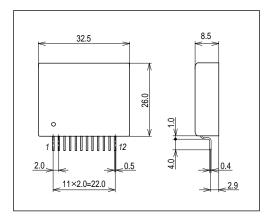

# **Package Dimensions**

unit:mm (typ)

Derating Curve of Motor Current, IOH, vs. STK672-520 Operating Substrate Temperature, Tc

#### Notes

- The current range given above represents conditions when output voltage is not in the avalanche state.

- If the output voltage is in the avalanche state, see the allowable avalanche energy for STK672-5\*\* series hybrid ICs given in a separate document.

- The operating substrate temperature, Tc, given above is measured while the motor is operating. Because Tc varies depending on the ambient temperature, Ta, the value of IOH, and the continuous or intermittent operation of IOH, always verify this value using an actual set.

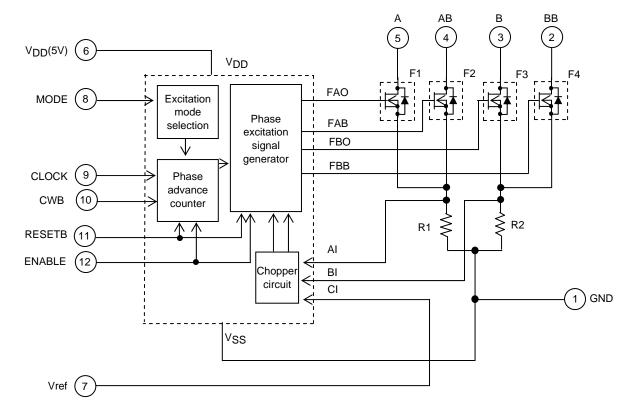

# **Block Diagram**

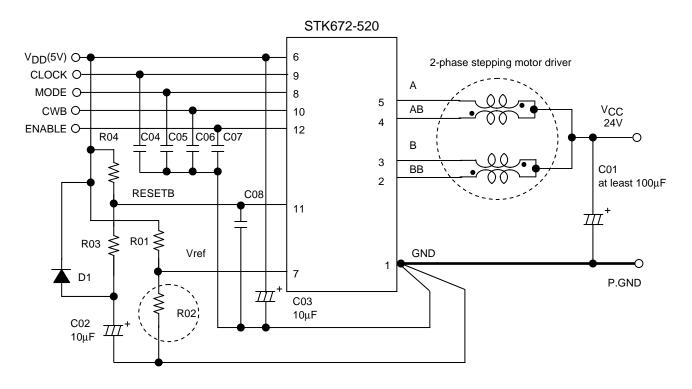

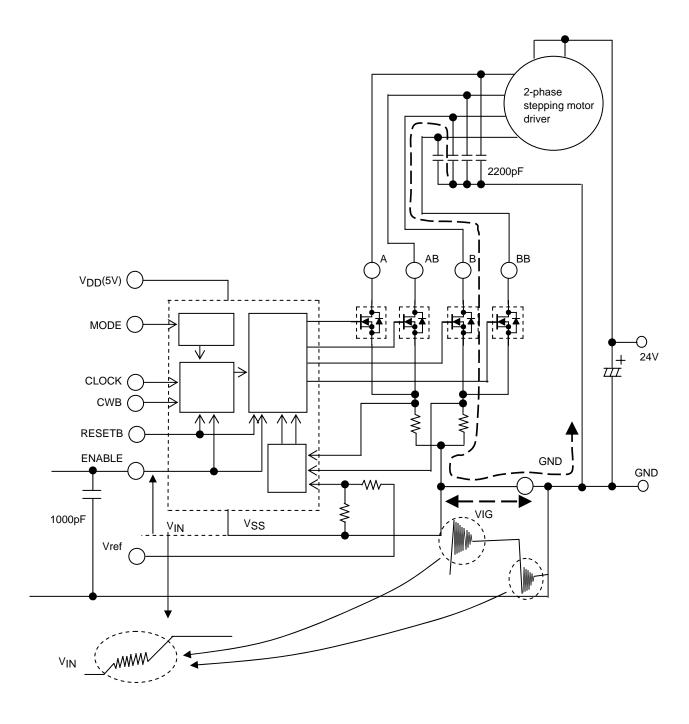

# **Sample Application Circuit**

R02 is normally open.

#### **Precautions**

#### [GND wiring]

• To reduce noise on the 5V system, be sure to place the GND of C01 in the circuit given above as close as possible to Pin 1 of the hybrid IC. Also, the GND side of RO2 must be directly wired from P.GND terminal Pin 1 in order to accurately set the current.

#### [Input pins]

- Insert resistor RO3 (47 to  $100\Omega$ ) so that the discharge energy from capacitor CO2 is not directly applied to the CMOS IC in this hybrid device. If the diode D1 has Vf characteristics with Vf less than or equal to 0.6V (when If = 0.1A), this will be smaller than the CMOS IC input pin diode Vf. If this is the case RO3 may be replaced with a short without problem.

- Apply 2.5V High level input to pins 8, 9, 10, 11, and 12.

- If V<sub>DD</sub> is being applied, use care that each input pin does not apply a negative voltage less than -0.3V to P.GND, Pin 1, and do not apply a voltage greater than or equal to V<sub>DD</sub> voltage.

- Since the input pins do not have built-in pull-up resistors, when the open-collector type pins 8, 9, 10, 11, and 12 are used as inputs, a 10 to  $47k\Omega$  pull-up resistor (to  $V_{DD}$ ) must be used. At this time, use a device for the open collector driver that has output current specifications that pull the voltage down to less than 0.6V at Low level.

- To prevent malfunction due to chopping noise, we recommend that you mount a 1000pF capacitor between Pin 1 and each of the input Pins 8, 9, 10, 11, and 12. Be sure to mount the capacitor as close as possible to the pins of hybrid IC. If input is fixed Low, directly connect to Pin 1.

If input is fixed High, directly connect to the 5V power line.

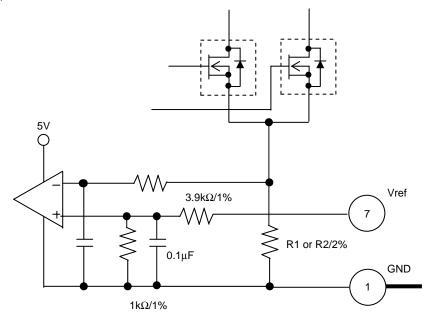

#### [Current setting Vref]

- In consideration of the specifications of the Vref input bias current, I<sub>IB</sub>, a resistance from several  $k\Omega$  to  $100k\Omega$  is recommended for RO1.

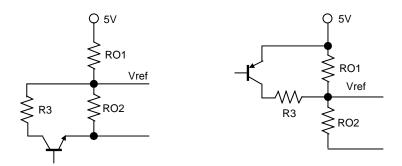

- If the motor current is temporarily reduced, the circuit given below (STK672-520: IOH>0.09A) is recommended.

- Although the driver is equipped with a fixed current control function, it is not equipped with an overcurrent protection

function to ensure that the current does not exceed the maximum output current, I<sub>OH</sub> max. If Vref is mistakenly set to

a voltage that exceeds I<sub>OH</sub> max, the driver will be damaged by overcurrent.

#### • Motor current peak value IOH setting

#### • When RO2 is open

$I_{OH} = [V_{ref} \times 1k/(1k+3.9k)] \div Rs = (V_{ref} \div 4.9) \div Rs$

The values 1k and 3.9k represent internal driver resistance values, while Rs represents the internal driver current detection resistance.

$Vref = (4.9k \div (4.9k + RO1)) \times 5V \text{ (or } 3.3V) = I_{OH} \times 4.9 \times Rs$

The value 4.9k represents the series resistance value of the internal driver values of 1k and 3.9k.

#### • If RO2 is connected

$IOH = [Vref \times 1k/(1k+3.9k)] \div Rs = (Vref \div 4.9) \div Rs$

The values 1k and 3.9k represent the internal driver resistance values, while Rs represents the internal driver current detection resistance.

$Vref = (R0x \div (RO1 + R0x)) \times 5V \text{ (or } 3.3V) = I_{OH} \times 4.9 \times Rs$

=  $[(4.9k\times RO2) \div ((4.9k\times RO2) + RO1\times (4.9k+RO2))] \times 5V(\text{or } 3.3V)$

$R0x = (4.9k \times RO2) \div (4.9k + RO2)$

Rs represents the current detection resistance inside the HIC, while the value 4.9k in the formula above represents the internal resistance value of the Vref pin.

Rs= $0.33\Omega$  when using the STK672-520

Rs= $0.165\Omega$  when using the STK672-530

Rs= $0.11\Omega$  when using the STK672-540

#### [Smoke Emission Precuations]

If any of the output pins 2, 3, 4, and 5 is held open, the electrical stress onto the driver due to the inductive energy accumulated in the motor could cause short-circuit followed by permanent damage to the internal MOSFET. As a result, the STK672-520 may give rise to emit smoke.

#### **Input Pin Functions**

| Pin Name | Pin No. | Function                                                 | Input Conditions When Operating                       |

|----------|---------|----------------------------------------------------------|-------------------------------------------------------|

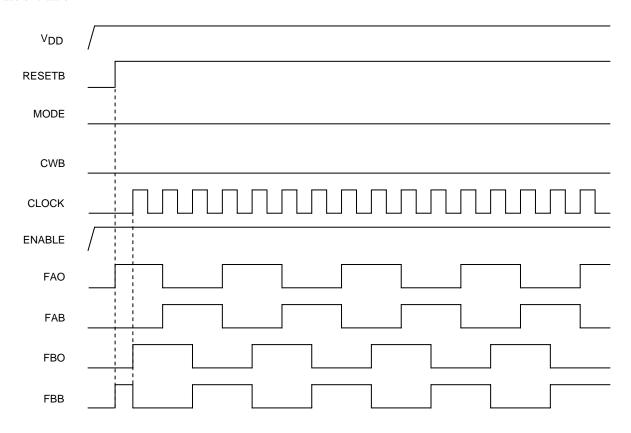

| CLOCK    | 9       | Reference clock for motor phase current switching        | Operates on the rising edge of the signal             |

| MODE     | 8       | Excitation mode selection                                | Low: 2-phase excitation                               |

|          |         |                                                          | High: 1-2 phase excitation                            |

| CWB      | 10      | Motor direction switching                                | Low: CW (forward)                                     |

|          |         |                                                          | High: CCW (reverse)                                   |

| RESETB   | 11      | System reset and A, AB, B, and BB outputs cutoff.        | A reset is applied by a low level                     |

|          |         | Applications must apply a reset signal for at least 10µs |                                                       |

|          |         | when V <sub>DD</sub> is first applied.                   |                                                       |

| ENABLE   | 12      | The A, AB, B, and BB outputs are turned off, and after   | The A, AB, B, and BB outputs are turned off by a low- |

|          |         | operation is restored by returning the ENABLE pin to the | level input.                                          |

|          |         | high level, operation continues with the same excitation |                                                       |

|          |         | timing as before the low-level input.                    |                                                       |

- (1) A simple reset function is formed from D1, CO2, RO3, and RO4 in this application circuit. With the CLOCK input held low, when the 5V supply voltage is brought up a reset is applied if the motor output phases A and BB are driven. If the 5V supply voltage rise time is slow (over 50ms), the motor output phases A and BB may not be driven. Increase the value of the capacitor CO2 and check circuit operation again.

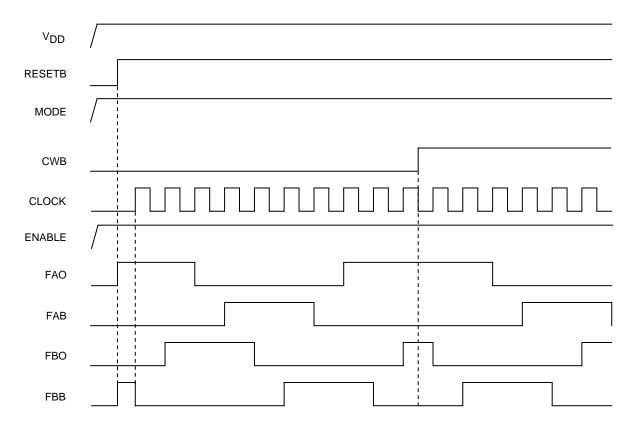

- (2) See the timing chart for the concrete details on circuit operation.

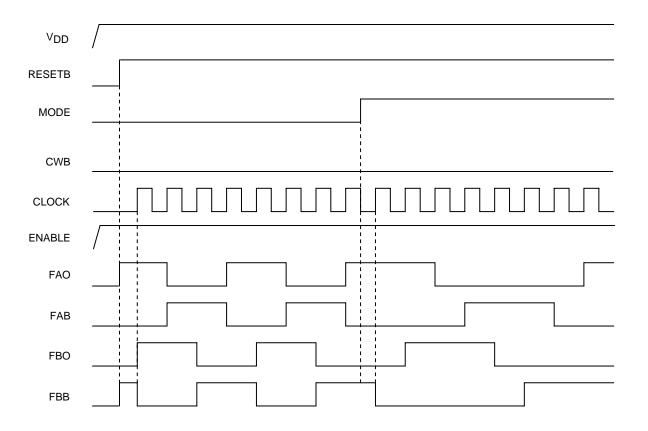

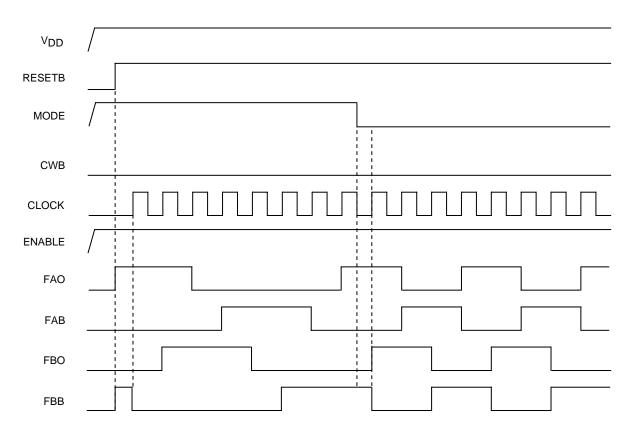

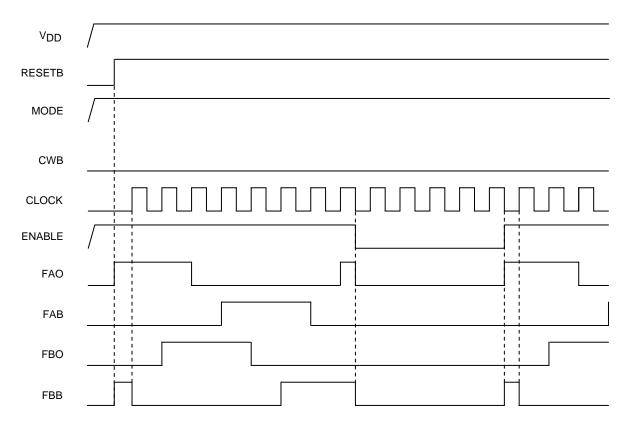

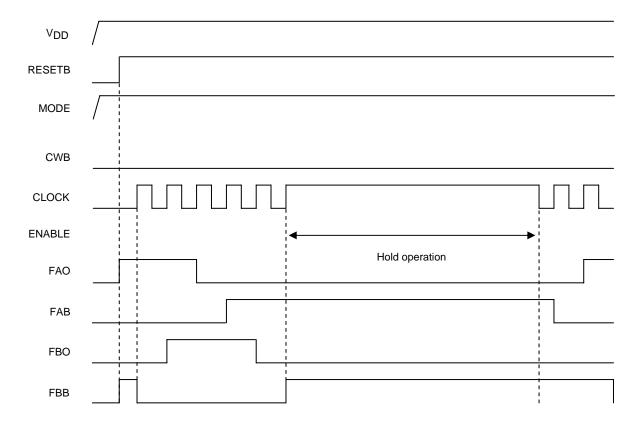

# **Timing Charts**

2-phase excitation

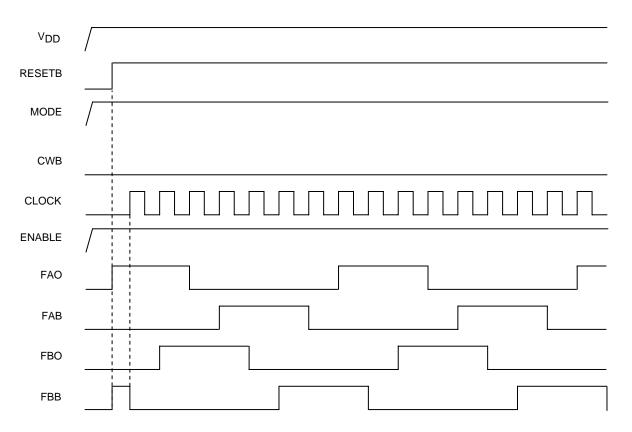

# 1-2 phase excitation

#### 1-2 phase excitation

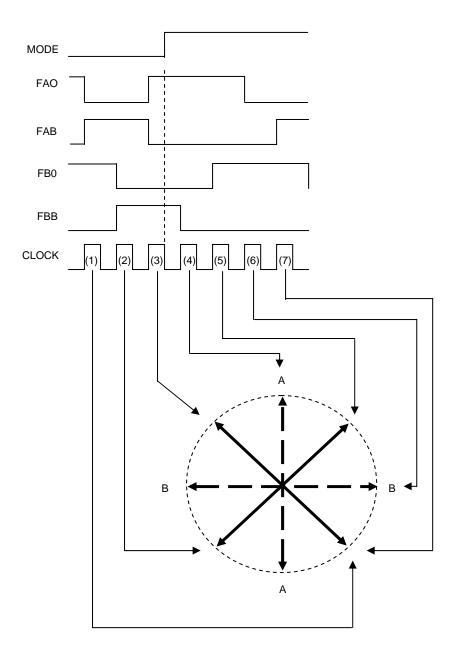

# 2-phase excitation→Switch to 1-2 phase excitation

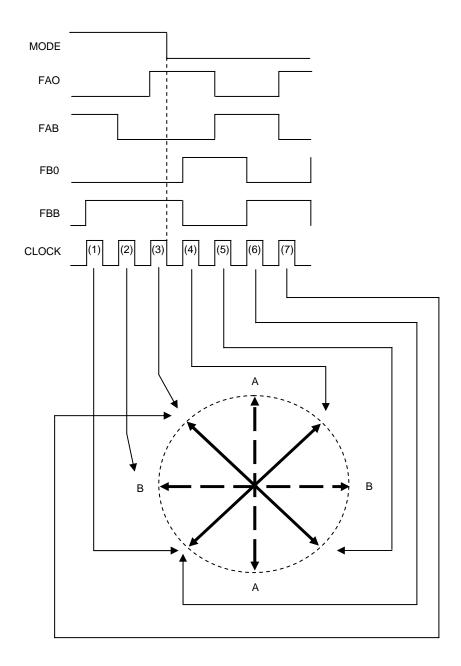

1-2-phase excitation→Switch to 2 phase excitation

#### 1-2 phase excitation (ENABLE)

# 1-2 phase excitation (Hold operation results during fixed CLOCK)

#### **Usage Notes**

1. STK672-520, STK672-530 and STK672-540 input signal functions and timing (All inputs have no internal pull-up resistor.)

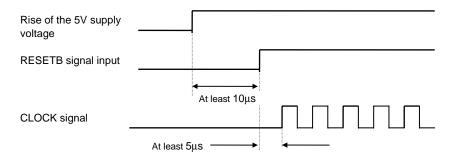

#### [RESETB and CLOCK (Input signal timing when power is first applied)]

As shown in the timing chart, a RESETB signal input is required by the driver to operate with the timing in which the F1 gate is turned on first. The RESETB signal timing must be set up to have a width of at least 10µs, as shown below. The capacitor CO2, and the resistors RO3 and RO4 in the application circuit form simple reset circuit that uses the RC time constant rising time. However, when designing the RESETB input based on VIH levels, the application must have the timing shown in figure.

Figure 1 RESETB and CLOCK Signals Input Timing

#### [CLOCK (Phase switching clock)]

• Input frequency: DC to 50kHz

• Minimum pulse width: 10µs

• Signals are read on the rising edge.

#### [CWB (Motor direction setting)]

The direction of rotation is switched by setting CWB to 1 (high) or 0 (low).

See the timing charts for details on the operation of the outputs.

Note: The state of the CWB input must not be changed during the  $6.25\mu s$  period before and after the rising edge of the CLOCK input.

[ENABLE (Controls forced OFF for A, AB, B, and selects BB and selects operation/hold mode of the hybrid IC)]

ENABLE=1: Normal operation

ENABLE=0: Outputs A, AB, B, and BB forced to the off state.

If, during the state where CLOCK signal input is provided, the ENABLE pin is set to 0 and then is later restored to the 1 state, the IC will resume operation with the excitation timing continued from before the point ENABLE was set to 0.

Enable must be initially set high for input as shown in the timing chart.

[MODE (Excitation mode selection)]

MODE=0: 2-phase excitation MODE=1: 1-2 phase excitation

See the timing charts for details on output operation in these modes.

Note: The state of the MODE input must not be changed during the 5µs period before and after the rising edge of the CLOCK input.

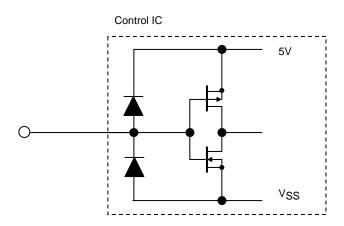

[Configuration of Each Input Pin]

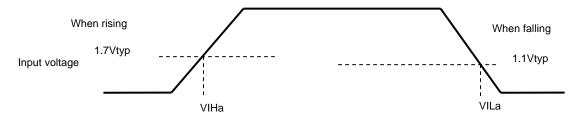

<Configuration of the MODE, CLOCK, CWB, RESETB, and ENABLE input pins> Input pins: Pin 8, 9, 10, 11, and 12

All input pins of this driver support schmitt input. Typ specifications at Tc = 25°C are given below. Hysteresis voltage is 0.6V (VIHa-VILa).

Input voltage specifications are as follows.

$V_{IH}=2.5V min$

V<sub>IL</sub>=0.6V max

<Configuration of the Vref Input Pin>

Input pin: Pin 7

#### <Pre><Precautions for Input Signal>

Because the ringing voltage VIG of the GND line is added to the input signals inside the hybrid IC, the greater the through rate of input signals, the more opportunities there are to input a ringing signal at the rising or falling edge. Particularly in cases where a capacitor is added to output pins 2, 3, 4, and 5 as shown in the figure below to suppress electromagnetic noise, the ringing voltage increases even further due to charge/discharge of the capacitor. The ringing voltage amplitude of this type may exceed 0.6V input Hysteresis voltage. Because the ringing signal can cause a malfunction leading to failure due to over-current, be sure to apply input signals with the highest through rate possible. Direct input with HC type CMOS ICs is recommended.

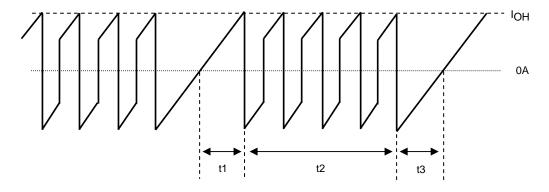

#### 2. Calculating STK672-520 HIC Internal Power Loss

The average internal power loss in each excitation mode of the STK672-520 can be calculated from the following formulas.

Each excitation mode

2-phase excitation mode

2PdAVex= (Vsat+Vdf) ×0.5×CLOCK×I<sub>OH</sub>×t2+0.5×CLOCK×I<sub>OH</sub>× (Vsat×t1+Vdf×t3)

1-2 phase excitation mode

1-2PdAVex= (Vsat+Vdf) ×0.25×CLOCK×I<sub>OH</sub>×t2+0.25×CLOCK×I<sub>OH</sub>× (Vsat×t1+Vdf×t3)

Motor hold mode

$HoldPdAVex = (Vsat + Vdf) \times IOH$

Vsat: Combined voltage represented by the Ron voltage drop+shunt resistor

Vdf: Combined voltage represented by the MOSFET body diode+shunt resistor

CLOCK: Input CLOCK (CLOCK pin signal frequency)

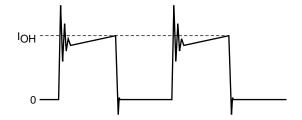

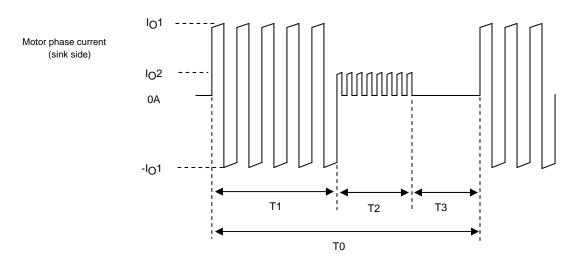

- t1, t2, and t3 represent the waveforms shown in the figure below.

- t1: Time required for the winding current to reach the set current (IOH)

- t2: Time in the constant current control (PWM) region

- t3: Time from end of phase input signal until inverse current regeneration is complete

Motor COM Current Waveform Model

$t1 = (-L/(R+0.61)) \ln (1-((R+0.61)/V_{CC}) \times I_{OH})$

$t3 = (-L/R) ln ((V_{CC}+0.61)/(I_{OH} \times R + V_{CC}+0.61))$

V<sub>CC</sub>: Motor supply voltage (V)

L: Motor inductance (H)

R: Motor winding resistance ( $\Omega$ )

IOH: Motor set output current crest value (A)

Relationship of CLOCK, t1, t2, and t3 in each excitation mode

2-phase excitation mode: t2=(2/CLOCK) - (t1+t3)

1-2 phase excitation mode: t2= (3/CLOCK) -t1

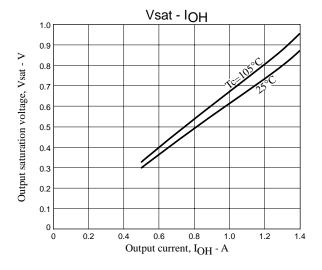

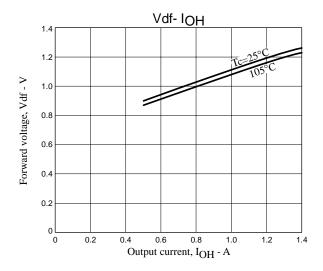

For Vsat and Vdf, be sure to substitute values from the graphs of Vsat vs. I<sub>OH</sub> and Vdf vs. I<sub>OH</sub> while the set current value is I<sub>OH</sub>.

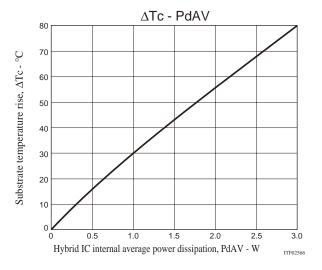

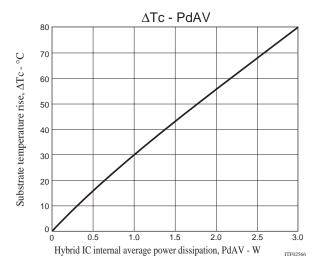

Then, determine whether a heat sink is required by comparing with the graph of  $\Delta Tc$  vs. Pd based on the average HIC power loss calculated.

When designing a heat sink, refer to the section "Thermal design" found on the next page. The average HIC power loss, PdAV, described above does not have the avalanche's loss. To include the avalanche's loss, be sure to add Equation (2), "STK672-5\*\* Allowable Avalanche Energy Value" to PdAV above. When using this IC without a fin always check for temperature increases in the set, because the HIC substrate temperature, Tc, varies due to effects of convection around the HIC.

STK672-520 Output saturation voltage, Vsat - Output current, IOH

STK672-520 Forward voltage, Vdf -Output current, IOH

Substrate temperature rise ,  $\Delta Tc$  (no heat sink) - Internal average power dissipation, PdAV

#### 3. STK672-520 Allowable Avalanche Energy Value

#### (1) Allowable Range in Avalanche Mode

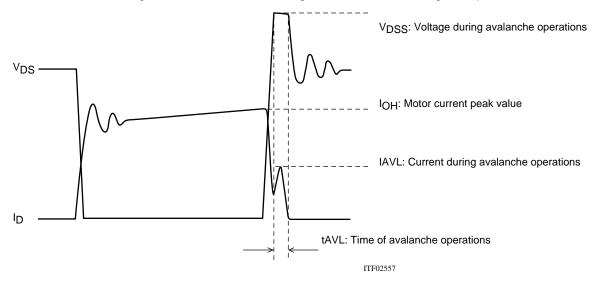

When driving a 2-phase stepping motor with constant current chopping using an STK672-5\*\* Series hybrid IC, the waveforms shown in Figure 1 below result for the output current, ID, and voltage, VDS.

Figure 1 Output Current, I<sub>D</sub>, and Voltage, V<sub>DS</sub>, Waveforms 1 of the STK672-5\*\* Series when Driving a 2-Phase Stepping Motor with Constant Current Chopping

When operations of the MOSFET built into STK672-5\*\* Series ICs is turned off for constant current chopping, the I<sub>D</sub> signal falls like the waveform shown in the figure above. At this time, the output voltage, V<sub>DS</sub>, suddenly rises due to electromagnetic induction generated by the motor coil.

In the case of voltage that rises suddenly, voltage is restricted by the MOSFET V<sub>DSS</sub>. Voltage restriction by V<sub>DSS</sub> results in a MOSFET avalanche. During avalanche operations, I<sub>D</sub> flows and the instantaneous energy at this time, EAVL1, is represented by Equation (1).

$$EAVL1 = V_{DSS} \times IAVL \times 0.5 \times tAVL ------(1)$$

VDSS: V units, IAVL: A units, tAVL: sec units

The coefficient 0.5 in Equation (1) is a constant required to convert the IAVL triangle wave to a square wave.

During STK672-5\*\* Series operations, the waveforms in the figure above repeat due to the constant current chopping operation. The allowable avalanche energy, EAVL, is therefore represented by Equation (2) used to find the average power loss, PAVL, during avalanche mode multiplied by the chopping frequency in Equation (1).

For V<sub>DSS</sub>, IAVL, and tAVL, be sure to actually operate the STK672-5\*\* Series and substitute values when operations are observed using an oscilloscope.

Ex. If  $V_{DSS}$ =110V, IAVL=1A, tAVL=0.2 $\mu$ s when using a STK672-520 driver, the result is:

PAVL=110×1×0.5×0.2×10<sup>-6</sup>×50×10<sup>3</sup>=0.55W

$V_{\mbox{DSS}}$ =110V is a value actually measured using an oscilloscope.

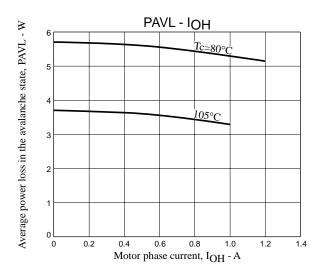

The allowable loss range for the allowable avalanche energy value, PAVL, is shown in the graph in Figure 3. When examining the avalanche energy, be sure to actually drive a motor and observe the  $I_D$ ,  $V_{DSS}$ , and  $t_AVL$  waveforms during operation, and then check that the result of calculating Equation (2) falls within the allowable range for avalanche operations.

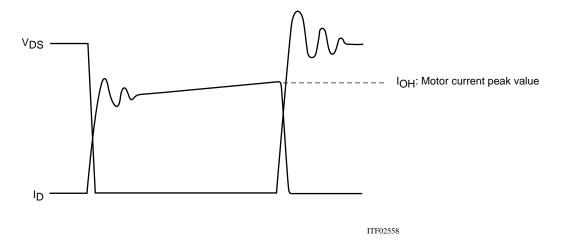

(2) ID and VDSS Operating Waveforms in Non-avalanche Mode

Although the waveforms during avalanche mode are given in Figure 1, sometimes an avalanche does not result during actual operations.

Factors causing avalanche are listed below.

- Poor coupling of the motor's phase coils (electromagnetic coupling of A phase and AB phase, B phase and BB phase).

- Increase in the lead inductance of the harness caused by the circuit pattern of the P.C. board and motor.

- Increases in V<sub>DSS</sub>, tAVL, and IAVL in Figure 1 due to an increase in the supply voltage from 24V to 36V. If the factors above are negligible, the waveforms shown in Figure 1 become waveforms without avalanche as shown in Figure 2.

Under operations shown in Figure 2, avalanche does not occur and there is no need to consider the allowable loss range of PAVL shown in Figure 3.

Figure 2 Output Current, I<sub>D</sub>, and Voltage, V<sub>DS</sub>, Waveforms 2 of the STK672-5\*\* Series when Driving a 2-Phase Stepping Motor with Constant Current Chopping

Figure 3 Allowable Loss Range, PAVL-IOH During STK672-520 Avalanche Operations

#### Note:

The operating conditions given above represent a loss when driving a 2-phase stepping motor with constant current chopping.

Because it is possible to apply 3.7W or more at  $I_{OH}$ =0A, be sure to avoid using the MOSFET body diode that is used to drive the motor as a zener diode.

#### 4. Thermal design

[Operating range in which a heat sink is not used]

Use of a heat sink to lower the operating substrate temperature of the HIC (Hybrid IC) is effective in increasing the quality of the HIC.

The size of heat sink for the HIC varies depending on the magnitude of the average power loss, PdAV, within the HIC. The value of PdAV increases as the output current increases. To calculate PdAV, refer to "Calculating Internal HIC Loss for the STK672-520" in the specification document.

Calculate the internal HIC loss, PdAV, assuming repeat operation such as shown in Figure 1 below, since conduction during motor rotation and off time both exist during actual motor operations.

Figure 1 Motor Current Timing

T1: Motor rotation operation time

T2: Motor hold operation time

T3: Motor current off time

T2 may be reduced, depending on the application.

T0: Single repeated motor operating cycle

IO1 and IO2: Motor current peak values

Due to the structure of motor windings, the phase current is a positive and negative current with a pulse form.

Note that figure 1 presents the concepts here, and that the on/off duty of the actual signals will differ.

The hybrid IC internal average power dissipation PdAV can be calculated from the following formula.

PdAV=

$$(T1\times P1+T2\times P2+T3\times 0) \div T0$$

----- (I)

(Here, P1 is the PdAV for I<sub>O</sub>1 and P2 is the PdAV for I<sub>O</sub>2)

If the value calculated using Equation (I) is 1.5W or less, and the ambient temperature, Ta, is 60°C or less, there is no need to attach a heat sink. Refer to Figure 2 for operating substrate temperature data when no heat sink is used.

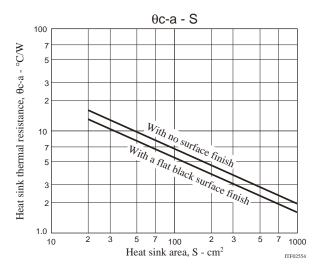

[Operating range in which a heat sink is used]

Although a heat sink is attached to lower Tc if PdAV increases, the resulting size can be found using the value of  $\theta$ c-a in Equation (II) below and the graph depicted in Figure 3.

$\theta c$ -a= (Tc max-Ta)  $\div$ PdAV ------ (II)

Tc max: Maximum operating substrate temperature =105°C

Ta: HIC ambient temperature

Although a heat sink can be designed based on equations (I) and (II) above, be sure to mount the HIC in a set and confirm that the substrate temperature, Tc, is 105°C or less.

The average HIC power loss, PdAV, described above represents the power loss when there is no avalanche operation. To add the loss during avalanche operations, be sure to add Equation (2), "Allowable STK672-5\*\* Avalanche Energy Value", to PdAV.

Figure 2 Substrate temperature rise,  $\Delta Tc$  - Internal average power dissipation, PdAV

Figure 3 Heat sink area (Board thickness: 2mm) -  $\theta$ c-a

5. Changes in motor state when switching excitation with STK672-5\*\* Series

#### Example 1: Switching from 2-phase to 1-2 phase excitation

Motor status is maintained when the excitation mode (MODE) is switched during motor rotation.

Because CLOCK cannot be detected when the interval between the rise in the MODE and CLOCK signals is  $5\mu s$  or less, the mode may not change for one CLOCK cycle.

The solid arrows indicate 2-phase excitation, and dashed arrows indicate 1-phase excitation.

Example 2: Switching from 1-2 phase to 2-phase excitation

Motor status is maintained when the excitation mode (MODE) is switched during motor rotation.

Because CLOCK cannot be detected when the interval between the rise in the MODE signal and CLOCK signal is  $5\mu s$  or less, the mode may not change for one CLOCK cycle.

The solid arrows indicate 2-phase excitation, and dashed arrows indicate 1-phase excitation.

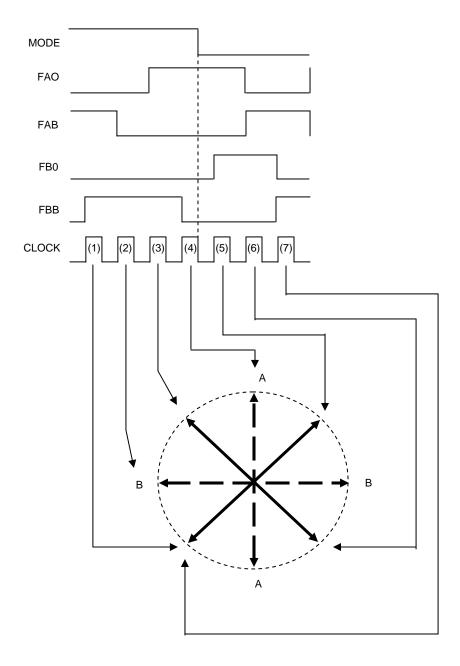

Ex.3: Changeover from 1-2 phase to 2-phase excitation

This driver stabilizes motor phase performance at changeover excitation mode during motor motion.

This driver is not able to detect CLOCK rising edge, if the time between CLOCK and MODE rising edge was less than  $5\mu s$ .

Therefore, motor phase performance doesn't change in 1 CLOCK cycle.

The solid arrows indicate 2-phase excitation, and dashed arrows indicate 1-phase excitation.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

FSB50550TB2 FSBF15CH60BTH MSVCPM2-63-12 MSVGW45-14-2 MSVGW54-14-3 MSVGW54-14-5 NTE7043 LA6565VR-TLM-E LB11650-E LB1837M-TLM-E LB1845DAZ-XE LC898300XA-MH SS30-TE-L-E 26700 LV8281VR-TLM-H BA5839FP-E2 IRAM236-1067A LA6584JA-AH LB11847L-E NCV70501DW002R2G AH293-PL-B STK672-630CN-E TND315S-TL-2H FNA23060 FSB50250AB FNA41060 MSVB54 MSVBTC50E MSVCPM3-54-12 MSVCPM3-63-12 MSVCPM4-63-12 MSVTA120 FSB50550AB NCV70501DW002G LC898301XA-MH LV8413GP-TE-L-E MSVGW45-14-3 MSVGW45-14-4 MSVGW45-14-5 MSVGW54-14-4 STK984-091A-E MP6519GQ-Z LB11651-E IRSM515-025DA4 LV8127T-TLM-H MC33812EKR2 NCP81382MNTXG TDA21801 LB11851FA-BH NCV70627DQ001R2G