| To | : Digi-Key | Issue No.      | : | ECJ08082910     |

|----|------------|----------------|---|-----------------|

|    |            | Date of Issue  | : | August 29.2008  |

|    |            | Classification | : | ■ New □ Changed |

## PRODUCT SPECIFICATION FOR APPROVAL

Product Description : Multilayer Ceramic Chip Capacitors

Product Part Number : ECJHVB1C475K

(1206 / X5R / 16 V / 4.7 uF / Thickness: 0.95 mm max.)

Customers Part Number:

Country of Origin : Japan

Applications : Consumer Type Electric Equipment

| 4 131                        |             |  |

|------------------------------|-------------|--|

| Approval No                  |             |  |

| Approval Date                |             |  |

| <b>.</b>                     |             |  |

| Excecuted by                 | :           |  |

|                              | (signature) |  |

| Title                        | :           |  |

| Dept.                        | :           |  |

| _ <b>- - - - - - - - - -</b> |             |  |

Prepared by : Engineering Section

Capacitor Business Unit Phone: +81-123-23-8149 (Direct)

Panasonic Electronic Devices Co.,Ltd. Fax: +81-123-22-4191 (Direct)

25.Kohata-nishinaka..Uji City, Kyoto, Japan

Phone: +81-774-32-1111(Representative)

Contact Person

Title

Authorized by

Title: Manager of Engineering

If there is a question, please ask the engineering section about it directly

**Panasonic**

# CLASSIFICATION SPECIFACATION No. 151S-ECJ-KMS45E SUBJECT Multilayer Ceramic Chip Capacitors (EIA 1206) Low Profile type (P/N:ECJHVB1C475K) Individual Specification PAGE 1 of 1 DATE Aug 28, 2008

#### 1. Scope

This specification applies to Low Profile type Multilayer Ceramic Chip Capacitors (EIA 1206), Temp. Char:X5R, Rated voltage DC16 V , Nominal Capacitance 4.7  $\mu$ F.

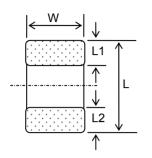

#### 2. Style and Dimensions

|        | Table 1        |

|--------|----------------|

| Symbol | Dimensions(mm) |

| L      | 3.2 +/- 0.2    |

| W      | 1.6 +/- 0.2    |

| Т      | 0.85 +/- 0.10  |

| L1,L2  | 0.6 +/- 0.3    |

#### 3. Operating Temperature Range / Storage Temperature Range

Table 2

|        | Temperature Characteristics | Operating Temp. Range. | Storage Temperature Range |

|--------|-----------------------------|------------------------|---------------------------|

| Class2 | X5R                         | -55 to 85 °C           | -55 to 85 °C              |

#### 4. Individual Specification

Table 3

| Part Number  | Rated<br>Voltage | Temp. Char. | Nominal<br>Capacitance | Cap. Tolerance |

|--------------|------------------|-------------|------------------------|----------------|

| ECJHVB1C475K | DC 16 V          | X5R         | 4.7 μF                 | +/-10 %        |

#### 5. Explanation of Part Numbers

#### 6. Temperature Characteristics

Table 4

| Temp. Char. | Capacitance Change rate from Temperature |                             | Measurement       | Reference   |

|-------------|------------------------------------------|-----------------------------|-------------------|-------------|

| Code        | Temp. Char.                              | Without voltage application | Temperature Range | Temperature |

| В           | X5R                                      | +/-15 %                     | -55 to 85 °C      | 25 °C       |

#### 7. Soldering method

Flow soldering shall not be applied.

|                                        | APPROVAL   | CHECK      | DESIGN    |

|----------------------------------------|------------|------------|-----------|

| Panasonic Electronic Devices Co., Ltd. | T.Kawamura | T.Shinriki | A.Konishi |

| CLASSIFICATION SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No.<br>151S-ECJ-KGS45E                                                                                |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| SUBJECT Multilayer Ceramic Chip Capacitors (EIA 1206)  PAGE 1 of 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |  |  |  |  |

| Low Profile type (P/N : ECJHVB1C475K) Common Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DATE Aug 28, 2008                                                                                     |  |  |  |  |

| <ol> <li>Information</li> <li>1- 1.Applicable laws and regulations         <ul> <li>(1) Any ozone-depleting substances listed in the Montreal Protocol are not used in the manufacturing processes for parts and materials used in this product.</li> <li>(2) PBB and PBDE are intentionally excluded from materials used in this product.</li> <li>(3) All the materials used in this product are registered materials under the Law Concerning Examination and Regulation of Manufacture and Handling of Chemical Substances.</li> <li>(4) This product complies with the RoHS, DIRECTIVE 2002/95/EC on the Restriction of the use of certain Hazard-ous Substances in electrical and electronic equipment.</li> <li>(5) This product is exported with export procedures under export related laws and regulations such as the Foreign Exchange and Foreign Trade Law.</li> </ul> </li> </ol> |                                                                                                       |  |  |  |  |

| <ul> <li>1- 2.Limitation in Applications         This product was designed and manufactured for general-purpose electronic equipinformation &amp; communication equipment. When the following applications, which a safety because the trouble or malfunction of this product may threaten the lives a separate specifications suitable for the application should be exchanged.         •Aerospace / Aircraft equipment, Warning / Antitheft equipment, Medical equipment, Vehicles, Trains, Ship and Vessel ), Highly public information processing equipment.     </li> </ul>                                                                                                                                                                                                                                                                                                                | are required higher reliability and and/or properties, are examined, nent, Transport equipment (Motor |  |  |  |  |

| 1- 3.Production factory (1) Panasonic Electronic Devices Japan Co., Ltd. (2) Panasonic Electronic Devices (Tianjin) Co., Ltd. (PEDTJ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |  |  |  |  |

| <ol> <li>Scope</li> <li>1.This specification applies to Low Profile type Multilayer Ceramic Chip Capacitors (P/ If there is a difference between this common specification and any individual specif the individual specifications.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |  |  |  |  |

| <ul> <li>2- 2. This product shall be used for general-purpose electronic equipment such as audiov tion &amp; communication equipment.</li> <li>Unreasonable applications may accelerate performance deterioration or short/oper ing the life end.</li> <li>Adequate safety shall be ensured especially for product design required a high I considerations.</li> <li>1)Previously examine how a single trouble in this product affects the end product 2)Design a protection circuit as Failsafe-design to avoid unsafe system resulting</li> </ul>                                                                                                                                                                                                                                                                                                                                             | n circuits as failure modes affect-<br>level of safety with the following                             |  |  |  |  |

| product. Whenever a doubt about safety arises from this product, immediately inform us for please.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | technical consultation without fail,                                                                  |  |  |  |  |

| 2- 3. This specification is a part of contract documents pertaining to the trade made by Matsushita Electric Industrial Co., Ltd.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | and between your company and                                                                          |  |  |  |  |

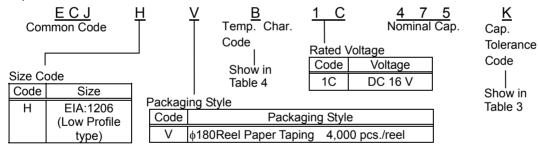

| 3. Part Number Code<br>ECJ H V B 1C 475 K<br>(1) (2) (3) (4) (5) (6) (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                       |  |  |  |  |

| <ul> <li>3- 1.Common Code (1)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                       |  |  |  |  |

| Note ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |  |  |  |  |

| Panasonic Electronic Devices Co., Ltd.  T.Kaw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OVAL CHECK DESIGN vamura T.Shinriki A.Konishi                                                         |  |  |  |  |

| CLASSIFICATION | SPECIFICATION                                        | No.<br>151S-ECJ-KGS45E |

|----------------|------------------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitors (EIA 1206)        | PAGE 2 of 7            |

| Low Pro        | ofile type (P/N : ECJHVB1C475K) Common Specification | DATE Aug 28, 2008      |

#### 3-3.Nominal Capacitance (6)

The Nominal Capacitance value is expressed in pico farads(pF) and is identified by a three-digit number; the first two digit represent significant figures and the last digit specifies the number of zero to follow.

| Symbol (Ex.) | Nominal Cap. |          |

|--------------|--------------|----------|

| 105          | 1000000pF    | (1 μF)   |

| 475          | 4700000pF    | (4.7 μF) |

| 106          | 10000000pF   | (10 μF)  |

#### 4. Operating Temperature Range

Shown in Individual Specification.

#### 5. Performance

The performance of the capacitor and its test condition shall be specified in Table 2.

#### 5- 1.Pretreatment

Before test and measurements, the following pretreatment shall be applied when necessary.

#### 5-1-1. Heat Treatment

The capacitors shall be kept in a temperature of 150+0/-10°C for 1 hour and then shall be stored in a room temperature for 48±4 hours, before initial measurement.

#### 5-1-2. Voltage Treatment

D.C. voltage shall be applied for 1 hour in the specified test condition and then shall be stored in a room temperature for 48 +/- 4 hours, before initial measurement.

#### 6. Test

Unless otherwise specified, all test and measurements shall be made at a temperature of 15 to 35°C and at a relative humidity of 45 to 75%.

If results obtained are doubted a further test should be carried out at a temperature of  $20\pm2^{\circ}$ C and a relative humidity of 60 to 70%.

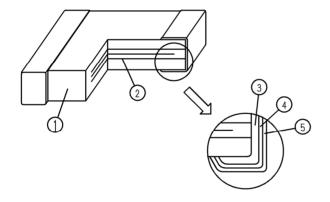

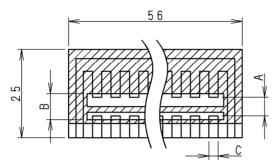

#### 7. Structure

The structure shall be in a monolithic form as shown in Fig. 1.

Fig. 1 Table 1

| No. | Name                   |

|-----|------------------------|

| 1   | Dielectric             |

| 2   | Inner electrode        |

| 3   | Substrate electrode    |

| 4   | Intermediate electrode |

| (5) | External electrode     |

| CLASSIFICATION | SPECIFICATION                                       | No.<br>151S-ECJ-KGS45E |

|----------------|-----------------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitors (EIA 1206)       | PAGE 3 of 7            |

| Low Pro        | file type (P/N : ECJHVB1C475K) Common Specification | DATE Aug 28, 2008      |

Table 2 No Contents Performance Test Method There shall be no defects which affect With a magnifying glass (3 times). 1 Appearance the life and use. Shown in Individual Specification. 2 Dimensions With slide calipers and a micrometer. Dielectric Withstand-3 There shall be no dielectric break-Test voltage: 250 % of rated voltage Apply a DC voltage of the above value for 1 to ing voltage down or damage. 5 seconds. Charge/discharge current shall be within 50mA Insulation 500/C  $M\Omega$  min. Measuring voltage: Rated voltage 4 Resistance(I.R.) Measuring voltage time: 60+/-5s (C: Nominal Cap. in µF) Charge/discharge current shall be within 50mA. 5 Capacitance Shall be within the specified tolerance. Measuring Measuring Frequency 6 Dissipation Factor 0.1 max. Voltage (tan  $\delta$ ) 1 kHz+/-10 % 1.0+/-0.2 Vrms For the class2 Capacitors, perform the heat treatment in par. 5-1-1. Our Measurement instrument is shown in the Table 3. Without 7 Temperature Temp. Char. Measure the capacitance at each stage by Coefficient Voltage X5R : Within +/- 15 % changing the temperature in the order of step 1 Applito 4 shown in the table below. Calculate the cation rate of change regarding the capacitance at stage 3 as the reference. (Unit: °C) Temp. Stage Char. 2 4 5 3 X5R 25+/-2 -55+/-3 | 25+/-2 | 85+/-2 | 25+/-2 Measuring Measuring Frequency Voltage 1 kHz+/-10 % 1.0+/-0.2 Vrms Adhesion The terminal electrode shall be free Solder the specimen to the testing jig shown in from peeling or signs of peeling. the figure., and apply a 5N force in the arrow direction for 10 seconds. Sample Material: Alumina board (95% min.) or glass epoxy board.

(continue)

Thickness: 1.0mm min.

| Note; |  |  |

|-------|--|--|

|       |  |  |

|       |  |  |

| CLASSIFICATION | SPECIFICATION                                       | No.<br>151S-ECJ-KGS45E |

|----------------|-----------------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitors (EIA 1206)       | PAGE 4 of 7            |

| Low Pro        | file type (P/N : ECJHVB1C475K) Common Specification | DATE Aug 28, 2008      |

Table 2

|    | Table 2                              |                                                                               |                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----|--------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No | Con                                  | Contents Performance                                                          |                                        | Performance                                                                                                                                                                                              | Test Method                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 9  | Bending<br>Strength                  | Appear-<br>ance<br>Capaci-<br>tance                                           |                                        | shall be no cracks and other nical damage.  Change from the value before test.  Within +/- 12.5 %                                                                                                        | After soldering capacitor on the substrate 1 mm of bending shall be applied for 5 seconds. Bending speed: 1mm/s (shown in Fig. 3)                                                                                                                                                                                                                                                                                                   |  |  |

| 10 | Vibration<br>Proof                   | Appearance Capacitance tan δ                                                  | mechar<br>Shall be                     | hall be no cracks and other nical damage.  e within the specified tolerance.  eet the specified initial value.                                                                                           | Solder the specimen to the testing jig shown in Fig. 2. Apply a variable vibration of 1.5 mm total amplitude in the 10 to 55 to10Hz vibration frequency range swept in 1 min. in 3 mutually perpendicular directions for 2 hours each, a total of 6 hours.                                                                                                                                                                          |  |  |

| 11 | Resis-<br>tance to<br>Solder<br>Heat | Appear-<br>ance<br>Capaci-<br>tance<br>tan δ<br>I.R.<br>With-stand<br>voltage | mechar Temp. Char. X5R Shall m Shall m | hall be no cracks and other nical damage.  Change from the value before test.  Within +/- 7.5 %  eet the specified initial value. eet the specified initial value. hall be no dielectric break-r damage. | Solder both method Preconditioning: Heat Temperature (See 5.1.1)/Class2 Solder temperature: 270+/-5 °C Dipping period: 3+/-0.5 s Preheat condition:  Order Temp.(°C) Period(s)  1 80 to 100 120 to 180 2 150 to 200 120 to 180 Use solder H63A(JIS-Z-3282).For the flux, use rosin (JIS-K-5902) ethanol solution of a concentration of about 25% by weight. Use tweezers for the holder to dip the specimen. Recovery: 48+/-4 hours |  |  |

| 12 | 12 Solderability                     |                                                                               | of both                                | nan 95% of the soldered area terminal electrodes shall be with fresh solder.                                                                                                                             | Solder temperature: 230+/-5 °C Dipping period: 4+/-1 s Dip the specimen in solder so that both terminal electrodes are completely submerged. Use solder H63A(JIS-Z-3282). For the flux use rosin (JIS-K-5902) of ethanol solution of a concentration of about 25 % by weight. Use tweezers for the holder to dip the specimen.                                                                                                      |  |  |

(continue)

| Note |

|------|

|------|

| CLASSIFICATION | SPECIFICATION                                        | No.<br>151S-ECJ-KGS45E |

|----------------|------------------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitors (EIA 1206)        | PAGE 5 of 7            |

| Low Pro        | ofile type (P/N : ECJHVB1C475K) Common Specification | DATE Aug 28, 2008      |

| T۶ | ab | le | 2 |

|----|----|----|---|

|    |    |    |   |

|    |                                  |                  | 1                 | Table 2                                    |                                                                                                                                                                                                                                                                          |                                                                                           |              |  |

|----|----------------------------------|------------------|-------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|--|

| No | Conter                           | nts              |                   | Performance                                |                                                                                                                                                                                                                                                                          | Test Method                                                                               |              |  |

| 13 | Temperature cycle                | Appear-<br>ance  |                   | shall be no cracks and other nical damage. | in Fig. 2                                                                                                                                                                                                                                                                | Solder the specimen to the testing jig show in Fig. 2. Condition the specimen to each     |              |  |

|    |                                  | Capaci-<br>tance | Temp.<br>Char.    | Change from the value before test.         | the peri                                                                                                                                                                                                                                                                 | temperature from step 1 to 4 in this order for the period shown in the table below. Regar |              |  |

|    |                                  |                  | X5R               | Within +/- 7.5 %                           |                                                                                                                                                                                                                                                                          | conditioning as one cycle<br>continuously.                                                | , perform    |  |

|    |                                  | tan δ            |                   | eet the specified initial value.           |                                                                                                                                                                                                                                                                          | Temperature                                                                               | Period       |  |

|    |                                  | I.R.             |                   | eet the specified initial value.           | Step                                                                                                                                                                                                                                                                     | (°C)                                                                                      | (min.)       |  |

|    |                                  | With-<br>stand   |                   | shall be no dielectric break-<br>r damage. | 1                                                                                                                                                                                                                                                                        | Minimum operation temperature +/- 3                                                       | 30+/-3       |  |

|    |                                  | voltage          |                   |                                            | 2                                                                                                                                                                                                                                                                        | Room temperature                                                                          | 3 max.       |  |

|    |                                  |                  |                   |                                            | 3                                                                                                                                                                                                                                                                        | Maximum operation temperature +/-5                                                        | 30+/-3       |  |

|    |                                  |                  |                   |                                            | 4                                                                                                                                                                                                                                                                        | Room temperature                                                                          | 3 max.       |  |

|    |                                  |                  |                   |                                            | For the class2 capacitors, perform the hoteratment in par. 5-1-1.  Before the measurement after test, the specimen shall be left to stand at room temperature for the following period:  48+/-4 h                                                                        |                                                                                           | st, the room |  |

| 14 | Moisture                         | Appear-          | There s           | shall be no cracks and other               | For the class2 capacitors, perform the he                                                                                                                                                                                                                                |                                                                                           | m the heat   |  |

|    | Resistance                       | ance             | mechar            | nical damage.                              | treatment in par. 5-1-1.                                                                                                                                                                                                                                                 |                                                                                           |              |  |

|    |                                  | Capaci-<br>tance | Temp.<br>Char.    | Change from the value before test.         |                                                                                                                                                                                                                                                                          | Solder the specimen to the testing jig shown in Fig. 2.  Test temperature: 40+/-2 °C      |              |  |

|    |                                  |                  | X5R               | Within +/- 12.5 %                          | Test t                                                                                                                                                                                                                                                                   |                                                                                           |              |  |

|    |                                  | tan δ            | 0.15 ma           | ax.                                        | Relative humidity : 90 to 95 % Test period : 500+24/0 h                                                                                                                                                                                                                  |                                                                                           |              |  |

|    |                                  | I.R.             | 50/C M<br>(C : No | $\Omega$ min. minal Cap. in μF)            | Before the measurement after test, the specimen shall be left to stand at room temperature for the following period :  48+/-4 h                                                                                                                                          |                                                                                           |              |  |

| 15 | Moisture<br>Resistant<br>Loading | Appear-<br>ance  |                   | shall be no cracks and other nical damage. | For the class2 capacitors, perform the heat treatment in par. 5-1-2.                                                                                                                                                                                                     |                                                                                           |              |  |

|    | Loading                          | Capaci-<br>tance | Temp.<br>Char.    | Change from the value before test.         |                                                                                                                                                                                                                                                                          | Solder the specimen to the testing jig shown in Fig. 2.                                   |              |  |

|    |                                  |                  | X5R               | Within +/- 12.5 %                          |                                                                                                                                                                                                                                                                          | emperature : 40+/-2 °C                                                                    |              |  |

|    |                                  | tan δ            | 0.15 ma           | ax.                                        | Relative humidity: 90 to 95 % Applied voltage: Rated voltage (DC Voltage) Charge/discharge current: within 50 mA. Test period: 500+24/0 h  Before the measurement after test, the specimen shall be left to stand at room temperature for the following period: 48+/-4 h |                                                                                           |              |  |

|    |                                  | I.R.             | 25/C M<br>(C : No | $\Omega$ min. minal Cap. in μF)            |                                                                                                                                                                                                                                                                          |                                                                                           |              |  |

|    |                                  |                  |                   | (continue)                                 |                                                                                                                                                                                                                                                                          |                                                                                           |              |  |

(continue)

| CLASSIFICATION | SPECIFICATION                                        | No.<br>151S-ECJ-KGS45E |

|----------------|------------------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitors (EIA 1206)        | PAGE 6 of 7            |

| Low Pro        | ofile type (P/N : ECJHVB1C475K) Common Specification | DATE Aug 28, 2008      |

Table 2

| No | Conten                               | ts               | Performance                                           |                                                            | Performance Test Method                                                                                                          |  | Test Method |

|----|--------------------------------------|------------------|-------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| 16 | High Tem-<br>perature Re-<br>sistant | Appear-<br>ance  | There shall be no cracks and other mechanical damage. |                                                            | For the class2 capacitors, perform the vo<br>age<br>treatment in par. 5-1-2.                                                     |  |             |

|    | Loading                              | Capaci-<br>tance | Temp.<br>Char.<br>X5R                                 | Change from the value be-<br>fore test.  Within +/- 12.5 % | Solder the specimen to the testing jig shown in Fig. 2.                                                                          |  |             |

|    |                                      | tan δ            | 0.15 ma                                               | ax.                                                        | Test temperature :  Max. Rated temp. +/-3°C                                                                                      |  |             |

|    |                                      | I.R.             | 50/C M:<br>(C : Noi                                   | $\Omega$ min.<br>minal Cap. in μF)                         | Applied voltage : 200% of Rated voltage<br>(DC Voltage)<br>Charge/discharge current : within 50 mA.<br>Test period : 1000+48/0 h |  |             |

|    |                                      |                  |                                                       |                                                            | Before the measurement after test, the specimen shall be left to stand at room temperature for the following period : 48+/-4 h   |  |             |

When uncertainty occurs in the weather resistance characteristic tests (temperature cycle, moisture resistance, moisture resistant loading, high temperature resistant loading), the same tests shall be performed for the capacitor itself.

#### Table 3

|                              | Our Standard Measuring Instrument                        |

|------------------------------|----------------------------------------------------------|

| Measuring Instrument         | 4278A 1kHz/1MHz Capacitance Meter (Agilent Technologies) |

| Measuring Mode               | Parallel Mode                                            |

| Recommended<br>Measuring Jig | 16034E Test Fixture (Agilent Technologies)               |

For High Cap Type, signal voltage may be unable to be applied to depending on conditions of measuring instruments. We would appreciate it if you would confirm whether High Cap Type is under the measurable environment or not by checking that the fixed signal voltage is applied or not. (For example, ALC function is ON, HPA is expanded.)

| Note ; |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

| CLASSIFICATION | SPECIFICATION                                       | No.<br>151S-ECJ-KGS45E |

|----------------|-----------------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitors (EIA 1206)       | PAGE 7 of 7            |

| Low Pro        | ofile type (P/N: ECJHVB1C475K) Common Specification | DATE Aug 28, 2008      |

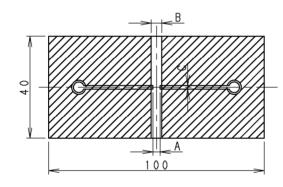

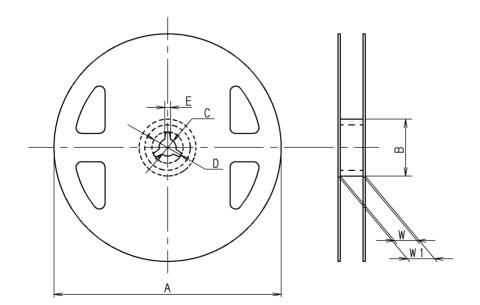

Fig. 2 Testing jig

Table 4 Size(EIA) Α В С 1206 2.2 5.0 2.0

Unit: mm

Material: Glass epoxy board

Thickness: 1.6 mm

:Copper foil (0.035 mm thick)

:Solder resist

Fig. 3 Testing jig

Table 5

| Size(EIA) | Α   | В   | С   |

|-----------|-----|-----|-----|

| 1206      | 2.2 | 5.0 | 2.0 |

Unit : mm

Material: Glass epoxy board

Thickness: 1.6 mm

:Copper foil (0.035 mm thick)

:Solder resist

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-ECJ-SS018E |

|----------------|---------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor           | PAGE 1 of 9            |

|                | Common Specification ( Precautions for Use) | DATE Apr. 1, 2008      |

#### 1. Precautions for Use

The Multilayer Ceramic Chip Capacitors (hereafter referred to as "Capacitors") may fail in a short circuit mode in an open-circuit mode when subjected to severe conditions of electrical, environmental and/or mechanical stress beyond the specified "Rating and specified "Conditions" in the Specifications, resulting in burn out, flaming or glowing in the worst case. The following "Precautions for Safety" and "Application Notes" shall be taken in your major consideration for use.

#### 2. Operating Conditions and Circuit Design

#### 2- 1. Circuit Design

2-1-1. Operating Temperature and Storage Temperature

The specified "Operating Temperature Range" in the Specifications is the absolute maximum and minimum temperature rating. Every circuit mounting a Capacitor shall be operated within the specified "Operating Temperature Range". The Capacitors mounted on PCB shall be stored without operating within the specified "Storage Temperature Range" in the Specifications.

#### 2-1-2. Design of Voltage application

The Capacitors shall not be operated exceeding the specified "Rated Voltage" in the Specification. If voltage ratings are exceeded, the Capacitors could result in failure or damage. In case of application of DC and AC voltages to the Capacitors, the designed peak voltage shall be within the specified "Rated Voltage". In case of AC of pulse voltage, the peak voltage shall be within the specified "Rated Voltage". If high frequency voltage or fast rising pulse voltage is applied continuously even within the "Rated Voltage", contact our engineering section before use. Such continuous application affects the life of the Capacitors.

#### 2-1-3. Working Current

It is recommended to equip the Capacitors with protection circuits for safety reasons, as should the Capacitors short circuit with voltages such as secondary voltage, there will be a serious risk that the Capacitors might self-heat or circuit boards might burn out.

#### 2-1-4. Self-Heating of Capacitors

When the Capacitors self-heat as a result of using AC or pulse voltage circuits and operate at room temperatures (25deg.C max.), make sure that the Capacitors' surface temperature does not exceed the ambient temperature plus 20 deg.C (max.), or the maximum operating temperature specified in product specification for approval. Also, the temperature of the Capacitors' surface which varies with circuit types used should be measured under the operational mode of devices mounted on by the Capacitors.

#### 2-1-5. Restriction on Environmental Conditions

The Capacitors shall not be operated and / or stored under the following environmental conditions.

- (1) Environmental conditions

- (a) To be exposed directly to water or salt water

- (b) To be dew formation

- (c) Under conditions of corrosive gases such as hydrogen sulfide, sulfurous acid, chlorine and ammonia

- (2) Under severe conditions of vibration or impact beyond the specified conditions in the Specifications

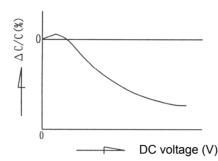

#### 2-1-6. DC voltage characteristics

The capacitance of Class 2 Capacitors has voltage dependency, contributing to big capacitance fluctuations in high DC voltage application. To secure specified capacitance, the following should be confirmed.

- (1) That the capacitance fluctuations caused by voltage application are within the capacitance range of a circuit used, or if the capacitance range of a circuit used is broad enough to maintain the Capacitors' functions.

- (2) DC voltage characteristics demonstrate, even if applied voltage is under the rated voltage, capacitance change rate increases with higher voltage (Capacitance down). Accordingly, when the Capacitors are used for circuits with narrow capacitance allowable range such as time constant circuits, we recommend to apply lower voltage upon due consideration on capacitance aging in addition to the above.

| Note ;                                 |            |            |           |

|----------------------------------------|------------|------------|-----------|

|                                        | APPROVAL   | CHECK      | DESIGN    |

| Panasonic Electronic Devices Co., Ltd. | T.Kawamura | T.Shinriki | A.Konishi |

| CLASSIFICATION | SPECIFICATIONS                    | No.<br>151S-ECJ-SS018E |

|----------------|-----------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor | PAGE 2 of 9            |

|                | DATE Apr. 1, 2008                 |                        |

#### Capacitance change vs. DC voltage

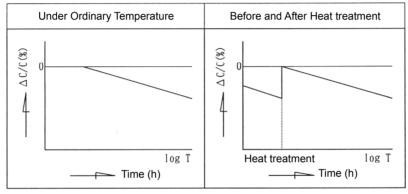

#### 2-1-7. Capacitance aging

The ceramic dielectrics of the Capacitors (Class 2) have capacitance aging. Accordingly, when the Capacitors are used for the circuits, which require a narrow capacitance allowable range, such as time constant circuits, pay due consideration to capacitance aging for use.

#### 2-1-8. Piezoelectricity

Dielectrics used for the Capacitors (Class 2) may cause the following Piezoelectricity (or Electrostriction).

(1) If the signal of a specific frequency is applied to the Capacitors, electric and acoustic noise may be generated by resonating the characteristic frequency which is determined by the dimensions of the Capacitor.

As a measure to prevent this phenomenon, changing the size of the Capacitor is effective to change its resonance frequency.

Also there is another measure changing the materials of the Capacitors to the Low-loss type, which has no (or less) piezoelectricity, or to Class1.

which has no (or less) piezoelectricity, or to Class1 is also available.

- (2) Vibration or impact applied to the Capacitors may cause noise because mechanical force is converted to electrical signals (Especially, application to around the amplifier unit).

- As a measure to prevent this phenomenon, changing the materials of the Capacitor to the Low-loss type, which has no (or less) piezoelectricity, or to Class1 is also available.

- (3) Even if a whining sound is generated, there is no problem in product performance and reliability, however, check the worrisome phenomenon which may generate noise in your equipment.

As a measure to prevent this phenomenon, changing to the Capacitor different in characteristics, size and shape as shown in the (1), (2) above is effective.

As the other measures, changing the mounting direction of the Capacitors to bring under control the resonance with equipment bodies such as printed circuit board, or the Capacitors are fixed with equipment bodies such as printed circuit board by adhesive may be effective.

#### 2- 2.Design of Printed Circuit Board

#### 2-2-1. Selection of Printed Circuit Board

When the Capacitors are mounted and soldered on an Aluminum Substrate, the substrate has influences on Capacitor's reliabilities against "Temperature Cycles" and "Heat shock" because of difference in thermal expansion coefficient between them.

It shall be carefully confirmed that the actual board applied does not deteriorate the characteristics of the Capacitors.

| CLASSIFICATION | SPECIFICATIONS                    | No.<br>151S-ECJ-SS018E |

|----------------|-----------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor | PAGE 3 of 9            |

|                | DATE Apr. 1, 2008                 |                        |

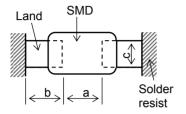

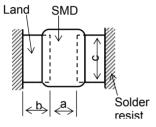

#### 2-2-2. Design of Land Pattern

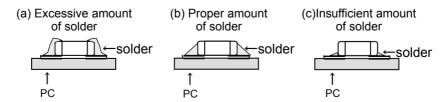

(1) Recommended land dimensions are shown below for proper amount of solder to prevent cracking at the time of excessive stress to the Capacitors due to increased amount of solder.

#### { Recommended land dimensions (Ex.) }

[ For High Capacitance, General Electronic Equipment, Low ProfileType, 100V·200V series, 630V series, High-Q Capacitors ]

|       |     |        |             |            |              | Unit in mm |  |

|-------|-----|--------|-------------|------------|--------------|------------|--|

| Size  | Con | ponent | Dimension   |            | h            |            |  |

| (EIA) | L   | W      | T           | а          | b            | С          |  |

| 0201  | 0.6 | 0.3    | 0.3         | 0.2 to 0.3 | 0.25 to 0.30 | 0.2 to 0.3 |  |

| 0402  | 1.0 | 0.5    | 0.5         | 0.4 to 0.5 | 0.4 to 0.5   | 0.4 to 0.5 |  |

| 0603  | 1.6 | 0.8    | 0.8         | 0.8 to 1.0 | 0.6 to 0.8   | 0.6 to 0.8 |  |

| 0805  | 2.0 | 1.25   | 0.6 to 1.25 | 0.8 to 1.2 | 0.8 to 1.0   | 0.8 to 1.0 |  |

| 1206  | 3.2 | 1.6    | 0.6 to 1.6  | 1.8 to 2.2 | 1.0 to 1.2   | 1.0 to 1.3 |  |

| 1210  | 3.2 | 2.5    | 0.8 to 2.5  | 1.8 to 2.2 | 1.0 to 1.2   | 1.8 to 2.3 |  |

#### [ Wide-width Type ]

|       |       |          |         |            |            | Unit in mm |

|-------|-------|----------|---------|------------|------------|------------|

| Size  | Compo | onent Di | mension | _          | L          | _          |

| (EIA) | L     | W        | Т       | а          | b          | С          |

| 0508  | 1.25  | 2.0      | 0.85    | 0.5 to 0.7 | 0.5 to 0.6 | 1.4 to 1.9 |

| 0612  | 1.6   | 3.2      | 0.85    | 0.8 to 1.0 | 0.6 to 0.7 | 2.5 to 3.0 |

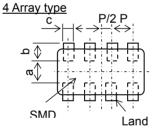

[Array Type]

|         |       |           |         |         |        |         | Unit in mm |

|---------|-------|-----------|---------|---------|--------|---------|------------|

| Size    | Compo | onent Din | nension | 0       | b      |         | Р          |

| (EIA)   | L     | W         | Т       | а       | D      | С       |            |

| 0805    | 2.0   | 1.25      | 0.85    | 0.55    | 0.5    | 0.2     | 0.4        |

| 4 Array | 2.0   | 1.23      | 0.65    | to 0.75 | to 0.6 | to 0.3  | to 0.6     |

| 1206    | 3.2   | 1.6       | 0.85    | 0.9     | 0.7    | 0.35    | 0.7        |

| 4 Array | 3.2   | 1.0       | 0.65    | to 1.1  | to 0.9 | to 0.45 | to 0.9     |

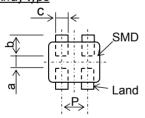

#### 2 Array type

|               |                        |     |     |        |         | U       | mit in mm |

|---------------|------------------------|-----|-----|--------|---------|---------|-----------|

| Size<br>(EIA) | Component<br>Dimension |     |     | а      | b       | С       | Р         |

| (LIA)         | L                      | W   | Т   |        |         |         |           |

|               |                        |     | 0.6 | 0.3    | 0.45    | 0.3     | 0.54      |

| 0504          | 1.37                   | 1.0 | 0.6 | to 0.4 | to 0.55 | to 0.4  | to 0.74   |

| 2 Array       | 1.57                   | 1.0 | 0.8 | 0.3    | 0.4     | 0.46    | 0.71      |

|               |                        |     | 0.6 | to 0.6 | to 0.7  | to 0.56 | to 0.91   |

(2) The size of lands shall be designed to be equal between the right and left sides. If the amount of solder on the right land is different from that on the left land, the component may be cracked by stress to one side of the component since the side with a larger amount of solder solidifies later at the time of cooling.

#### Recommended Amount of Solder

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-ECJ-SS018E |

|----------------|---------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor           | PAGE<br>4 of 9         |

|                | Common Specification ( Precautions for Use) | DATE Apr. 1, 2008      |

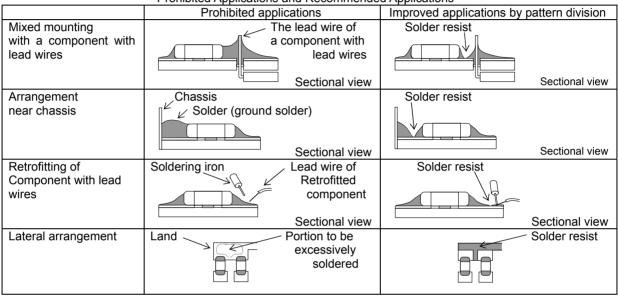

#### 2-2-3. Utilization of Solder Resist

The application of solder resist is effective in preventing solder bridges and controlling the amount of solder on PC boards.

- (1)Solder resist shall be utilized to equalize the amounts of solder on both sides.

- (2) Solder resist shall be used to divide the pattern for the following cases;

- ·Components are arranged closely.

- •The Capacitor is mounted near a component with lead wires.

- ·The Capacitor is placed near a chassis.

See the table below.

Prohibited Applications and Recommended Applications

#### 2-2-4. Component Layout

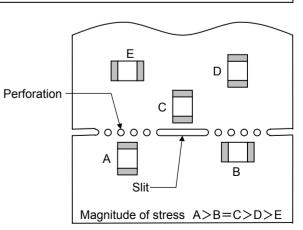

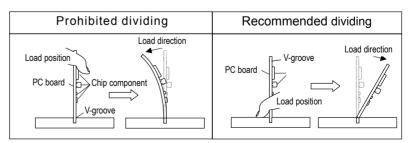

The Capacitors / components shall be placed on the PC board such that both electrodes are subjected to uniform stresses, or to position the component electrodes at right angles to the grid glove or bending line. This should be done to avoid cracking the Capacitors from bending the PC board after or during placing/mounting on the PC board.

(1) To minimize mechanical stress caused by warp or bending of a PC board, please follow the recommended Capacitor layout below.

|                          | Prohibited layout | Recommended layout                                             |

|--------------------------|-------------------|----------------------------------------------------------------|

| Warp of<br>Circuit board |                   | Lay out the Capacitor sideways against the stressing direction |

- (2) The following drawing is for your reference since mechanical stress near the dividing/breaking position of a PC board varies depending on the mounting position of the Capacitors.

- (3) The magnitude of mechanical stress applied to the Capacitors when the circuit board is divided is in the order of push back < slit < V-groove < perforation.

Also take into account the layout of the Capacitors and the dividing/breaking method.

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-ECJ-SS018E |

|----------------|---------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor           | PAGE 5 of 9            |

|                | Common Specification ( Precautions for Use) | DATE Apr. 1, 2008      |

#### 2-2-5. Mounting Density and Spaces

If components are arranged in too narrow spaces, the components are affected by Solder bridges and Solder balls. Each space between components should be carefully determined.

#### 3. Precautions for Assembly

#### 3-1.Storage

- (1) The Capacitors before mounting on PCB shall be stored between 5 40°C and 20 70% RH, not under severe conditions of high temperature and humidity.

- (2) If stored in a place that is humid, dusty, or contains corrosive gasses (hydrogen sulfide, sulfurous acid, hydrogen chloride and ammonia, etc.), the solderability of terminal electrodes may deteriorate. In addition, storage in a place subjected to heating and/or exposed to direct sunlight will cause deformed tapes and reels, and component sticking to tapes, both of which can result in mounting problems.

- (3) Do not store components longer than 6 months. Check the solderability of products that have been stored for more than 6 months before use.

- (4) The Capacitors of high dielectric constant series (Class 2, Characteristic B,X7R,X5R and F,Y5V) change in capacitance with the passage of time, "Capacitance aging", due to the inherent characteristics of ceramic dielectric materials. The changed capacitance can be recovered by heat treatment to each initial value at the time of shipping. (See 2. Operating Condition and Circuit Design, 2-1-7. Capacitance aging)

- (5) When the initial capacitance is measured, the Capacitors shall be heat-treated at 150+0/-10°C for 1 hour and then subjected to ordinary temperature and humidity for 48±4 hours before measuring the initial value.

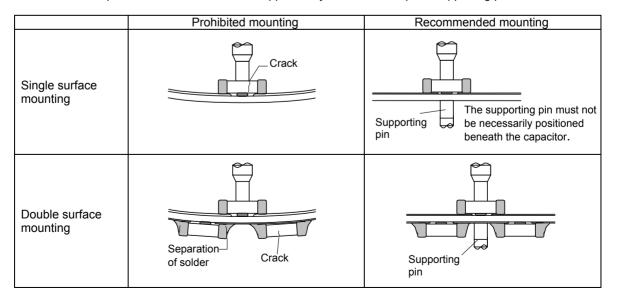

#### 3- 2. Chip Mounting Consideration

- (1) When mounting the Capacitors/components on a PC board, the capacitor bodies shall be free from excessive impact loads such as mechanical impact or stress in the positioning, pushing force and displacement of vacuum nozzles at the time of mounting.

- (2) Maintenance and inspections for Chip Mounter must be performed regularly.

- (3) If the bottom dead center of the vacuum nozzle is too low, the Capacitor is cracked by an excessive force at the time of mounting.

- The following precautions and recommendations are for your reference in use.

- (a) Set and adjust the bottom dead center of the vacuum nozzles to the upper surface of the PC board after correcting the warp of the PC board.

- (b) Set the pushing force of the vacuum nozzle at the time of mounting to 1 to 3 N in static load.

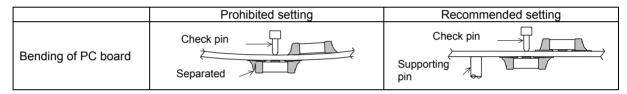

- (c) For double surface mounting, apply a supporting pin on the rear surface of the PC board to suppress the bending of the PC board in order to minimize the impact of the vacuum nozzles. The typical examples are shown in the table below.

- (d) Adjust the vacuum nozzles so that their bottom dead center at the time of mounting is not too low.

- (4) The closing dimensions of positioning chucks shall be controlled and the maintenance, checks and replacement of positioning chucks shall be regularly performed to prevent chipping or cracking of the Capacitors caused by mechanical impact at the time of positioning due to worn positioning chucks.

- (5) Maximum stroke of the nozzle shall be adjusted so that the maximum bending of PC board does not exceed 0.5mm at 90mm span. The PC board shall be supported by means of adequate supporting pins.

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-ECJ-SS018E |

|----------------|---------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor           | PAGE 6 of 9            |

|                | Common Specification ( Precautions for Use) | DATE Apr. 1, 2008      |

#### 3-3. Selection of Soldering Flux

Soldering flux may seriously affect the performance of the Capacitors. The following shall be confirmed before use.

- (1) The soldering flux should have a halogen based content of 0.1 wt. % (converted to chlorine) or below. Do not use soldering flux with strong acid.

- (2) When applying water-soluble soldering flux, wash the Capacitors sufficiently because the soldering flux residue on the surface of PC boards may deteriorate the insulation resistance on the Capacitor's surface.

#### 3-4. Soldering

#### 3-4-1. Reflow soldering

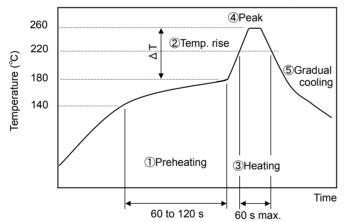

The reflow soldering temperature conditions are each temperature curves of Preheating, Temp. rise, Heating, Peak and Gradual cooling. Large temperature difference caused by rapid heat application to the Capacitors may lead to excessive thermal stresses, contributing to the thermal cracks. The Preheating temperature requires controlling with great care so that tombstone phenomenon may be prevented.

|                                            | Temperature                                                                                          | Period or Speed |

|--------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|

| ①Preheating 140 to 180 $^{\circ}$ C        |                                                                                                      | 60 to 120 s     |

| ②Temp. rise Preheating temp. to Peak temp. |                                                                                                      | 2 to 5 ℃/s      |

| ③Heating                                   | 220 ℃ min.                                                                                           | 60 s max.       |

| <pre>④Peak</pre>                           | 260 °C max.                                                                                          | 10 s max.       |

| ⑤Gradual cooling                           | Peak temp. to 140 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 1 to 4 ℃/s      |

The rapid cooling (forced cooling) during Gradual cooling part should be avoided, because this may cause defects such as the thermal cracks, etc.

When the Capacitors are immersed into a cleaning solvent, confirm that the surface temperature of the devices does not exceed 100°C.

Performing reflow soldering twice under the conditions shown in the figure above [Recommended profile of Reflow soldering (EX)] will not cause any problems. However, pay attention to the possible warp and bending of the PC board.

#### Recommended profile of Reflow soldering (Ex.)

# ⟨ Allowable temperature difference ΔT⟩ Size Temp. Tol.

| Size             | remp. roi.                     |  |

|------------------|--------------------------------|--|

| 0201 to 1206     | ΔΤ≦ 150 °C                     |  |

| 0508, 0612, 0504 | $\Delta I \cong 130 \text{ C}$ |  |

| 1210             | ΔT≦ 130 °C                     |  |

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-ECJ-SS018E |

|----------------|---------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor           | PAGE 7 of 9            |

|                | Common Specification ( Precautions for Use) | DATE Apr. 1, 2008      |

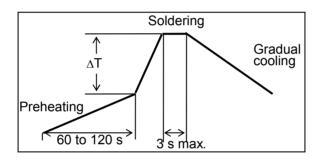

#### 3-4-2. Hand soldering

Hand soldering typically causes significant temperature change, which may induce excessive thermal stresses inside the Capacitors, resulting in the thermal cracks, etc.

In order to prevent any defects, the following should be observed;

- •The temperature of the soldering tips should be controlled with special care.

- •The direct contact of soldering tips with the Capacitors and/or terminal electrodes should be avoided.

- ·Dismounted Capacitors shall not be reused.

#### (1) Condition 1 (with preheating)

#### (a) Soldering:

*ϕ*1.0mm or below Thread eutectic solder with soldering flux\* in the core.

\*Rosin-based and non-activated flux is recommended.

#### (b) Preheating:

The Capacitors shall be preheated so that the "Temperature Gradient" between the devices and the tip of soldering iron is 150°C or below.

(c) Temperature of Iron tip: 300°C max.

(The required amount of solder shall be melted in advance on the soldering tip.)

(d) Gradual Cooling:

After soldering, the Capacitors shall be cooled gradually at room ambient temperature.

#### Recommended profile of Hand Soldering [Ex.]

| ⟨Allowable temperature difference ∆ I ⟩ |            |  |

|-----------------------------------------|------------|--|

| Size Temp. Tol.                         |            |  |

| 0201 to 1206                            | ΔT≦ 150 °C |  |

| 0508, 0612, 0504 △1 ≦ 150 C             |            |  |

| 1210 ΔT≦ 130 °C                         |            |  |

#### (2) Condition 2 (without preheating)

Hand soldering can be performed without preheating, by following the conditions below:

- (a) Soldering iron tip shall never directly touch the ceramic dielectrics and terminal electrodes of the Capacitors.

- (b) The lands are sufficiently preheated with a soldering iron tip before sliding the soldering iron tip to the terminal electrodes of the Capacitor for soldering.

|                                    | Condition                              |             |  |

|------------------------------------|----------------------------------------|-------------|--|

| Chip size                          | 0201 to 0805, 0508, 0504 1206 to 1210, |             |  |

| Temperature of soldering iron      | 270 °C max.                            | 250 °C max. |  |

| Wattage                            | 20W max.                               |             |  |

| Shape of soldering iron tip        | on tip #3mm max.                       |             |  |

| Soldering time with soldering iron | 3s max.                                |             |  |

#### 3- 5.Post Soldering Cleaning

#### 3-5-1. Cleaning solvent

Soldering flux residue may remain on the PC board if cleaned with an inappropriate solvent. This may deteriorate the electrical characteristics and reliability of the Capacitors.

#### 3-5-2. Cleaning conditions

Inappropriate cleaning conditions such as insufficient cleaning or excessive cleaning may impair the electrical characteristics and reliability of the Capacitors.

- (1) Insufficient cleaning can lead to:

- (a) The halogen substance in the residues of the soldering flux to cause the metal of terminal electrodes to corrode.

- (b) The halogen substance in the residue of the soldering flux on the surface of the Capacitors may change resistance values.

| Note |

|------|

|------|

| CLASSIFICATION | SPECIFICATIONS                              | No.<br>151S-ECJ-SS018E |

|----------------|---------------------------------------------|------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor           | PAGE 8 of 9            |

|                | Common Specification ( Precautions for Use) | DATE Apr. 1, 2008      |

(c) Water-soluble soldering flux may have more remarkable tendencies of (a) and (b) above compared to those of rosin soldering flux.

#### (2) Excessive cleaning can lead to:

(a) Overuse of ultrasonic cleaning may deteriorate the strength of the terminal electrodes or cause cracking in the solder and/or ceramic bodies of the Capacitors due to vibration of the PC boards.

Please follow these conditions for Ultrasonic cleaning:

Ultrasonic wave output : 20 W/L max.

Ultrasonic wave frequency : 40 kHz max.

Ultrasonic wave cleaning time : 5 minutes max.

#### 3-5-3. Contamination of Cleaning solvent

Cleaning with contaminated cleaning solvent may cause the same results as insufficient cleaning due to the high density of liberated halogen.

#### 3- 6.Inspection Process

When mounted PC boards are inspected with measuring terminal pins, abnormal and excess mechanical stress shall not be applied to the PC board or mounted components, to prevent failure or damage to the devices.

- (1) Mounted PC boards shall be supported by an adequate number of supporting pins with bend settings of 90 mm span 0.5mm max.

- (2) Confirm that the measuring pins have the right tip shape, are equal in height and are set in the correct positions. The following figures are for your reference to avoid bending the PC board.

#### 3-7. Protective Coating

When the surface of a PC board on which the Capacitors have been mounted is coated with resin to protect against moisture and dust, it shall be confirmed that the protective coating which is corrosive or chemically active is not used, in order that the reliability of the Capacitors in the actual equipment may not be influenced. Coating materials that expand or shrink also may lead to damage to the Capacitor during the curing process.

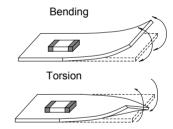

#### 3-8.Dividing/Breaking of PC Boards

- (1) Abnormal and excessive mechanical stress such as bending or torsion shown below can cause cracking in the Capacitors.

- (2) Dividing/Breaking of the PC boards shall be done carefully at moderate speed by using a jig or apparatus to prevent the Capacitors on the boards from mechanical damage.

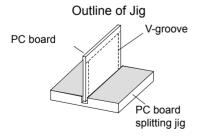

#### (3) Examples of PCB dividing/breaking jigs:

When PC boards are broken or divided, loading points should be close to the jig to minimize the extent of the bending

Also, planes with no parts mounted on should be used as plane of loading, which generates a compressive stress on the mounted plane, in order to prevent tensile stress induced by the bending, which may cause cracks of the Capacitors or other parts mounted on the PC boards.

| CLASSIFICATION | SPECIFICATIONS                                                                                                          | No.<br>151S-ECJ-SS018E        |

|----------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| SUBJECT        | Multilayer Ceramic Chip Capacitor Common Specification ( Precautions for Use)                                           | PAGE 9 of 9 DATE Apr. 1, 2008 |

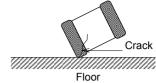

|                | citors shall be free from any excessive mechanical impact. citor body is made of ceramics and may be damaged or cracked |                               |

Never use a Capacitor which has been dropped; their quality may be impaired and failure rate increased.

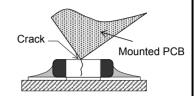

(2) When handling PC boards with Capacitors mounted on them, do not allow the Capacitors to collide with another PC board.

When mounted PC boards are handled or stored in a stacked state, impact between the corner of a PC board and the Capacitor may cause damage or cracking and can deteriorate the withstand voltage and insulation resistance of the Capacitor.

#### 4. Other

For special mounting conditions, please contact us.

Precautions for Use above are from

The Technical Report EIAJ RCR-2335 Caution Guide Line for Operation of Fixed Multilayer Ceramic Capacitors for Electronic Equipment by Japan Electronics and Information Technology Industries Association (March 2002 issued)

Please refer to above technical report for details.

| Note : |  |  |

|--------|--|--|

| Note;  |  |  |

|        |  |  |

|        |  |  |

| CLASSFICATION | N SPECIFICATIONS                                         | No.  | 151S-ECJ-SV037E |

|---------------|----------------------------------------------------------|------|-----------------|

| SUBJECT       | Multilayer Ceramic Chip Capacitor                        | PAGE | 1 of 4          |

| Tape          | d and Reeled Packaging Specifications (Low Profile Type) | DATE | 28 Apr, 2004    |

#### 1. Scope

This specification applies to taped and reeled packing for Multilayer Ceramic Chip Capacitors (Low Profile Type).

#### 2. Applicable Standards

EIAJ (Electric Industries Association of Japan) Standard EIAJ RC-1009B

JIS (Japanese Industrial Standard) Standard JIS C 0806

#### 3. Packing Specification

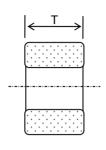

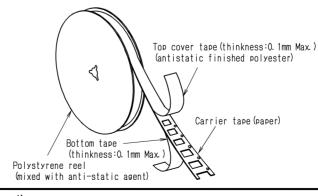

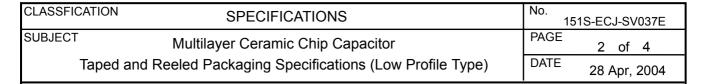

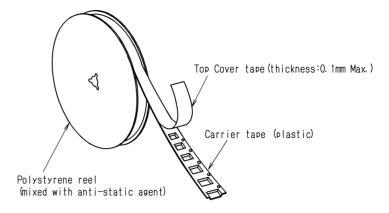

#### 3- 1. Structure and Dimensions

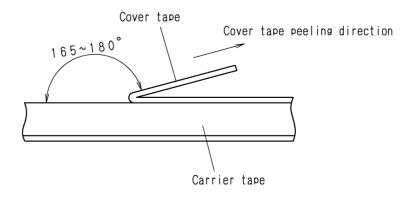

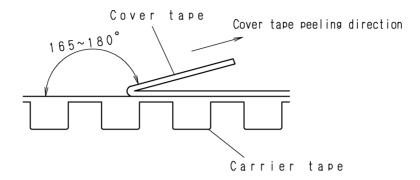

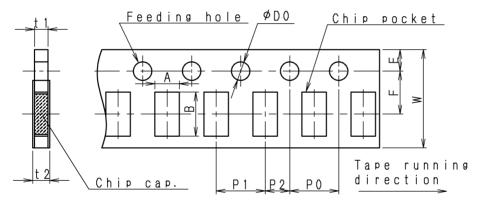

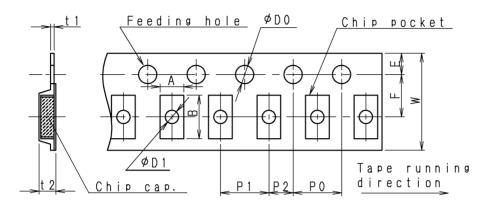

Paper taping packaging is carried out according the following diagram

(1)Carrier tape : Shown in Fig. 4.(2)Reel : Shown in Fig. 5.

(3)Packaging : We shall pack suitably in order prevent damage during transportation or storage.

3- 2.Packing Quantity

|               |               | Carrier-Tape    |              | Quantity (        | (pcs./reel) |

|---------------|---------------|-----------------|--------------|-------------------|-------------|

| Туре          | Thickness of  |                 |              | <i>ϕ</i> 180m     | m Reel      |

| (EIA)         | Capacitor(mm) | Material        | Taping Pitch | Packaging<br>Code | Quantity    |

| 12type (0805) | 0.85+/-0.10   | Paper Taping    | 4mm          | V                 | 4000        |

| 401 (4000)    | 0.85+/-0.10   | Paper Taping    | 4mm          | V                 | 4000        |

| 13type (1206) | 1.15+/-0.10   | Embossed Taping | 4mm          | F                 | 3000        |

| 23type (1210) | 0.85+/-0.10   | Embossed Taping | 4mm          | F                 | 3000        |

#### Explanation of Part Numbers (Example)

ECJ G V B 1C 105 K

Packaging Code

#### 3- 3. Marking on the Reel

The following items are described in the side of a reel in English at least.

- (1)Part Number

- (2)Quantity

- (3)Lot Number