Application Manual

**RV-3028-C7**

**Application Manual**

# **RV-3028-C7**

# Extreme Low Power Real-Time Clock Module with I<sup>2</sup>C-Bus Interface

# **TABLE OF CONTENTS**

| 1. | OV    | ERVIEW                                         | 6  |

|----|-------|------------------------------------------------|----|

|    | 1.1.  | GENERAL DESCRIPTION                            | 6  |

|    | 1.2.  | APPLICATIONS                                   | 7  |

|    | 1.3.  | ORDERING INFORMATION                           | 7  |

| 2. | BLC   | DCK DIAGRAM                                    | 8  |

|    | 2.1.  | PINOUT                                         | 9  |

|    | 2.2.  | PIN DESCRIPTION                                | 9  |

|    | 2.3.  | FUNCTIONAL DESCRIPTION                         | 10 |

|    | 2.4.  | DEVICE PROTECTION DIAGRAM                      | 10 |

| 3. | RE    | GISTER ORGANIZATION                            | 11 |

|    | 3.1.  | REGISTER CONVENTIONS                           | 11 |

|    | 3.2.  | REGISTER OVERVIEW                              | 12 |

|    | 3.3.  | CLOCK REGISTERS                                | 14 |

|    | 3.4.  | CALENDAR REGISTERS                             | 16 |

|    | 3.5.  | ALARM REGISTERS                                | 18 |

|    | 3.6.  | PERIODIC COUNTDOWN TIMER CONTROL REGISTERS     | 20 |

|    |       | STATUS AND CONTROL REGISTERS                   |    |

|    | 3.8.  | EVENT CONTROL REGISTER                         | 26 |

|    | 3.9.  | TIME STAMP REGISTERS                           | 27 |

|    | 3.10. | UNIX TIME REGISTERS                            | 30 |

|    |       | RAM REGISTERS                                  |    |

|    |       | PASSWORD REGISTERS                             |    |

|    |       | EEPROM MEMORY CONTROL REGISTERS                |    |

|    | 3.14. | ID REGISTER                                    | 35 |

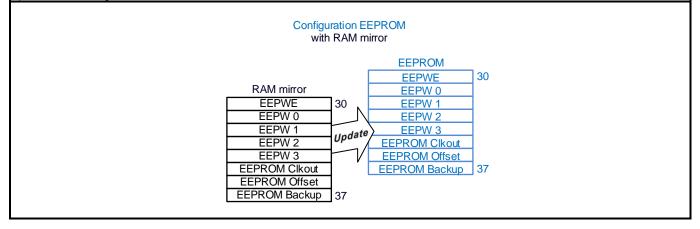

|    | 3.15. | CONFIGURATION EEPROM WITH RAM MIRROR REGISTERS | 35 |

|    | 3.    | 15.1. EEPROM RESERVED                          | 35 |

|    | 3.    | 15.2. EEPROM PASSWORD ENABLE REGISTER          | 35 |

|    | 3.    | 15.3. EEPROM PASSWORD REGISTERS                | 36 |

|    | -     | 15.4. EEPROM CLKOUT REGISTER                   | -  |

|    |       | 15.5. EEPROM OFFSET REGISTER                   |    |

|    |       | 15.6. EEPROM BACKUP REGISTER                   |    |

|    |       | USER EEPROM                                    | -  |

|    |       | RESERVED EEPROM                                |    |

|    |       | REGISTER RESET VALUES SUMMARY                  |    |

| 4. |       | TAILED FUNCTIONAL DESCRIPTION                  |    |

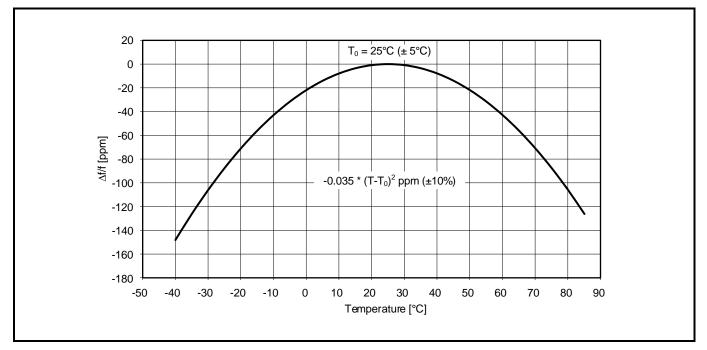

|    |       | POWER ON RESET (POR)                           |    |

|    |       | AUTOMATIC BACKUP SWITCHOVER FUNCTION           |    |

|    | 4.    | 2.1. SWITCHOVER DISABLED                       | 46 |

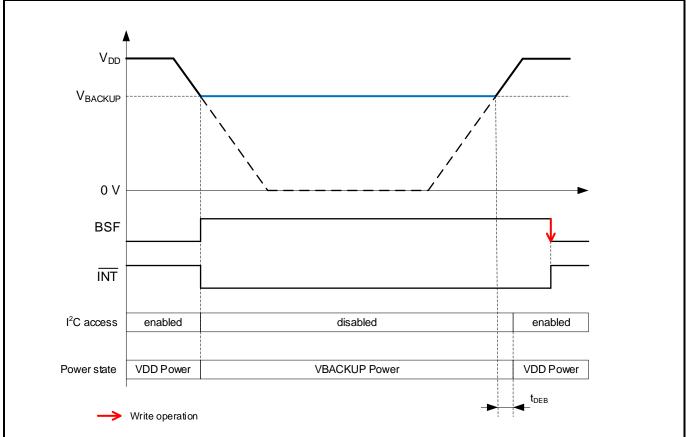

| 4.2.2. DIRECT SWITCHING MODE (DSM)                                    |    |

|-----------------------------------------------------------------------|----|

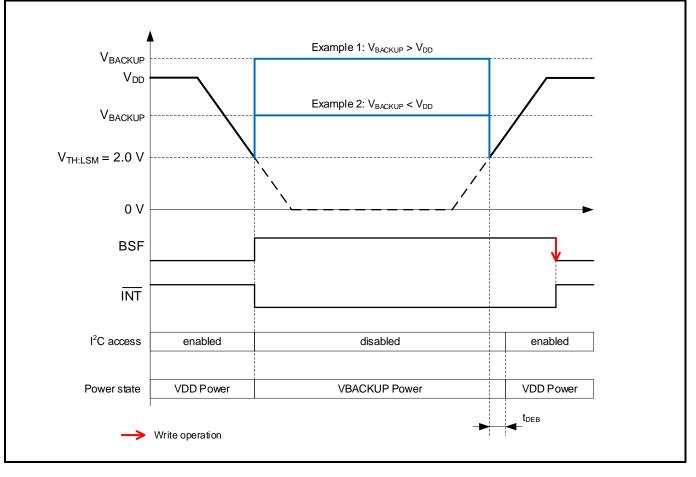

| 4.2.3. LEVEL SWITCHING MODE (LSM)                                     |    |

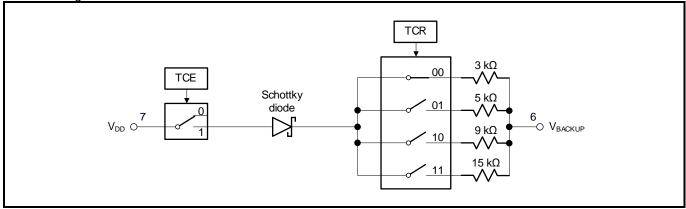

| 4.3. TRICKLE CHARGER                                                  |    |

| 4.4. PROGRAMMABLE CLOCK OUTPUT                                        |    |

| 4.4.1. CLKOUT FREQUENCY SELECTION                                     |    |

| 4.4.2. NORMAL CLOCK OUTPUT                                            |    |

| 4.4.3. INTERRUPT CONTROLLED CLOCK OUTPUT                              |    |

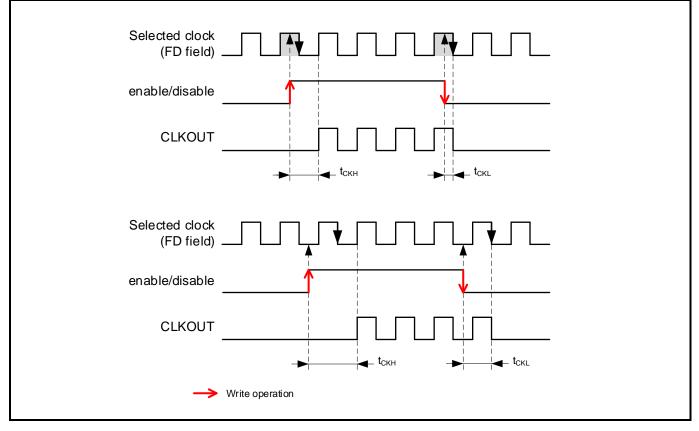

| 4.4.4. SYNCHRONIZED ENABLE/DISABLE                                    |    |

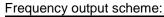

| 4.4.5. CLOCK OUTPUT SCHEME                                            | 51 |

| 4.5. SETTING AND READING THE TIME                                     |    |

| 4.5.1. SETTING THE TIME                                               | 53 |

| 4.5.2. READING THE TIME                                               | 53 |

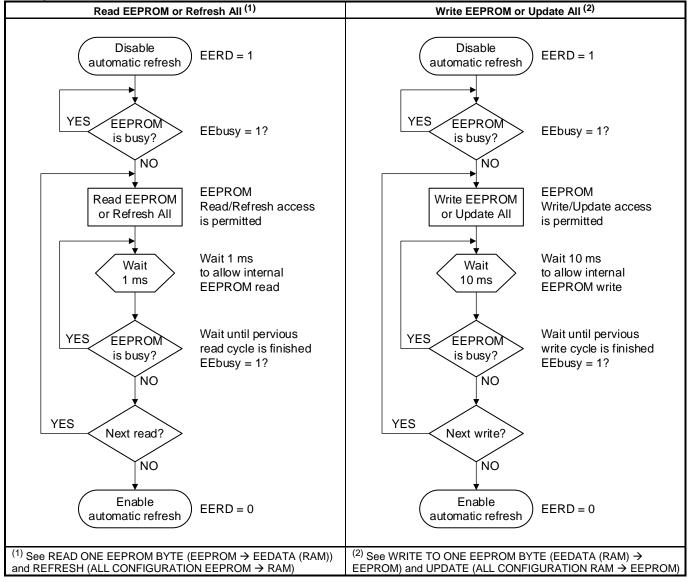

| 4.6. EEPROM READ/WRITE                                                | 54 |

| 4.6.1. POR REFRESH (ALL CONFIGURATION EEPROM $\rightarrow$ RAM)       | 54 |

| 4.6.2. AUTOMATIC REFRESH (ALL CONFIGURATION EEPROM $\rightarrow$ RAM) | 54 |

| 4.6.3. UPDATE (ALL CONFIGURATION RAM $\rightarrow$ EEPROM)            | 54 |

| 4.6.4. REFRESH (ALL CONFIGURATION EEPROM $\rightarrow$ RAM)           | 54 |

| 4.6.5. WRITE TO ONE EEPROM BYTE (EEDATA (RAM) → EEPROM)               |    |

| 4.6.6. READ ONE EEPROM BYTE (EEPROM → EEDATA (RAM))                   |    |

| 4.6.7. EEBUSY BIT                                                     |    |

| 4.6.8. EEPROM READ/WRITE CONDITIONS                                   | 57 |

| 4.6.9. USE OF THE CONFIGURATION REGISTERS                             | 57 |

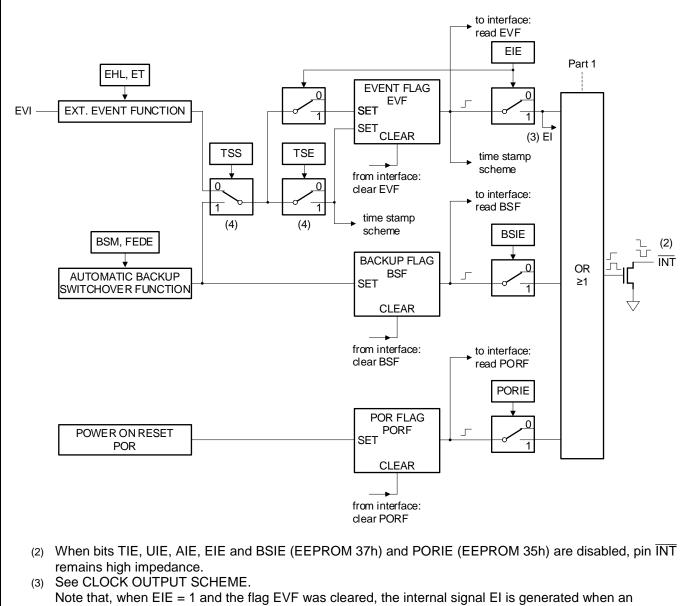

| 4.7. INTERRUPT OUTPUT                                                 |    |

| 4.7.1. SERVICING INTERRUPTS                                           |    |

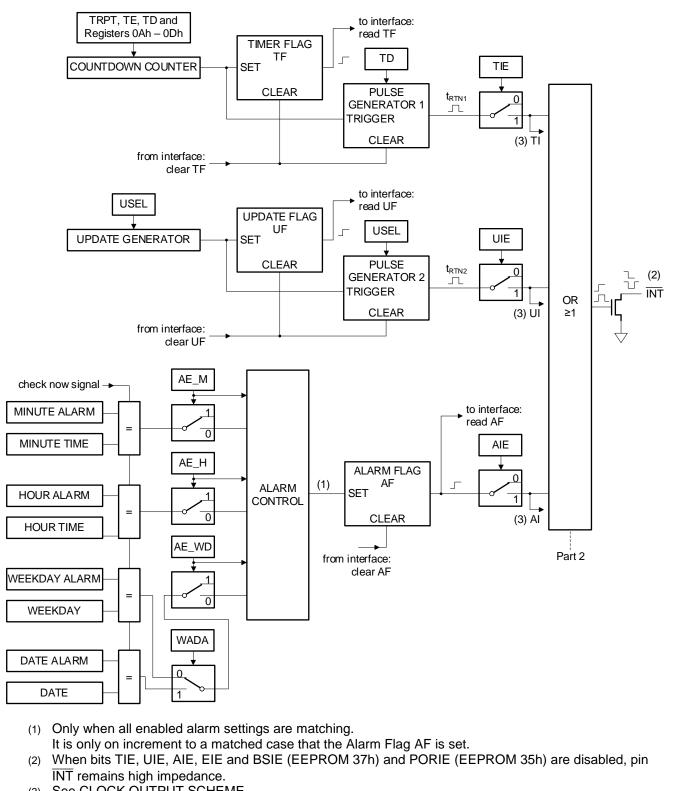

| 4.7.2. INTERRUPT SCHEME                                               | 59 |

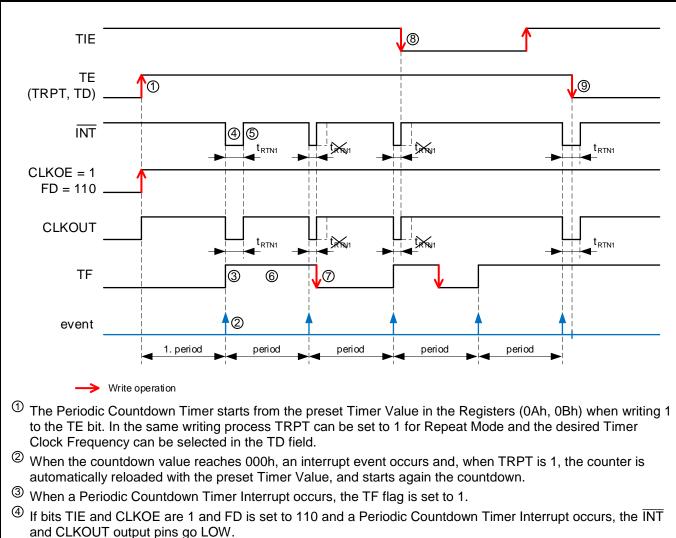

| 4.8. PERIODIC COUNTDOWN TIMER INTERRUPT FUNCTION                      |    |

| 4.8.1. PERIODIC COUNTDOWN TIMER DIAGRAM                               | 62 |

| 4.8.2. USE OF THE PERIODIC COUNTDOWN TIMER INTERRUPT                  | 63 |

| 4.8.3. FIRST PERIOD DURATION                                          | 65 |

| 4.8.4. SINGLE MODE (TRPT = 0)                                         |    |

| 4.8.5. REPEAT MODE (TRPT = 1)                                         |    |

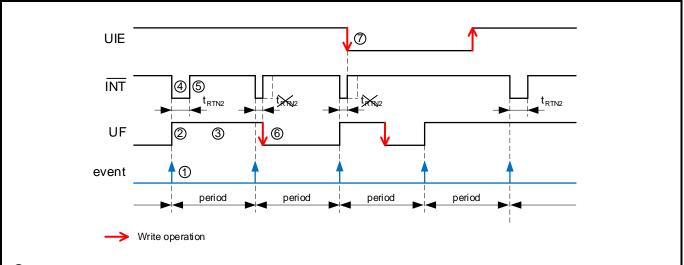

| 4.9. PERIODIC TIME UPDATE INTERRUPT FUNCTION                          | 66 |

| 4.9.1. PERIODIC TIME UPDATE DIAGRAM                                   |    |

| 4.9.2. USE OF THE PERIODIC TIME UPDATE INTERRUPT                      | 67 |

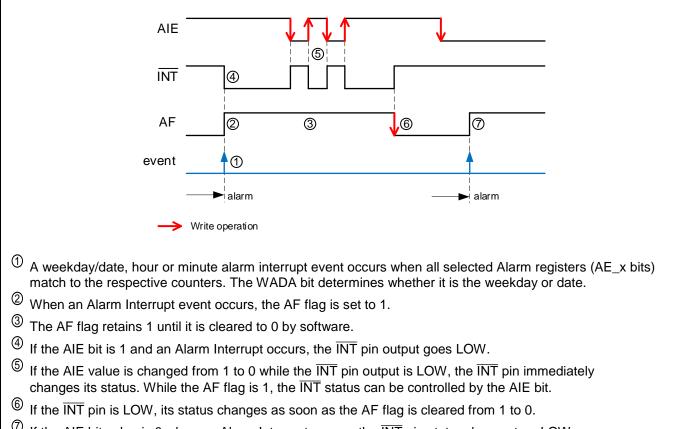

| 4.10. ALARM INTERRUPT FUNCTION                                        | 68 |

| 4.10.1. ALARM DIAGRAM                                                 |    |

| 4.10.2. USE OF THE ALARM INTERRUPT                                    |    |

| 4.11. EXTERNAL EVENT INTERRUPT FUNCTION                               |    |

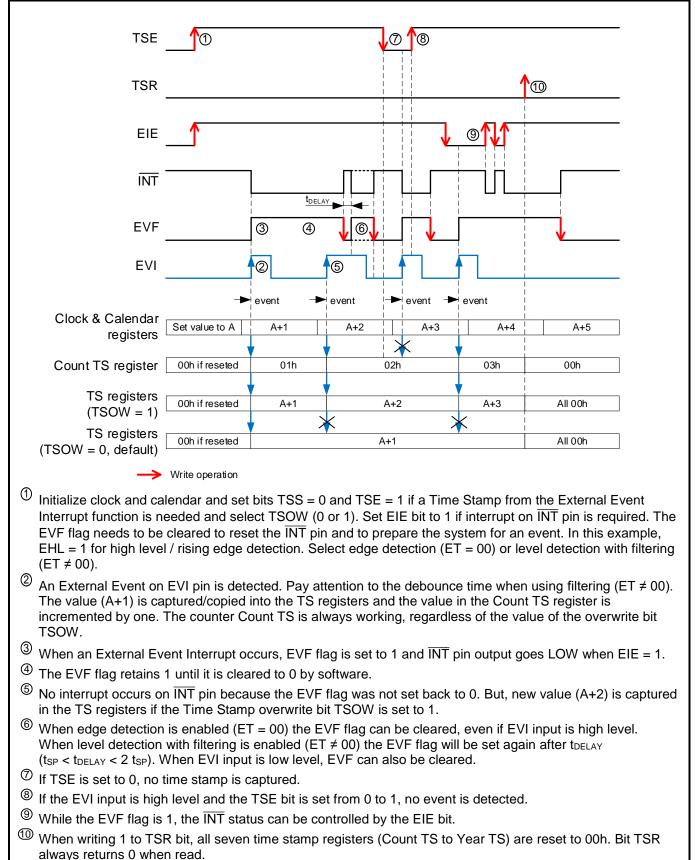

| 4.11.1. EXTERNAL EVENT DIAGRAM                                        | 71 |

|    | 4.11.2. USE OF THE EXTERNAL EVENT INTERRUPT              |     |

|----|----------------------------------------------------------|-----|

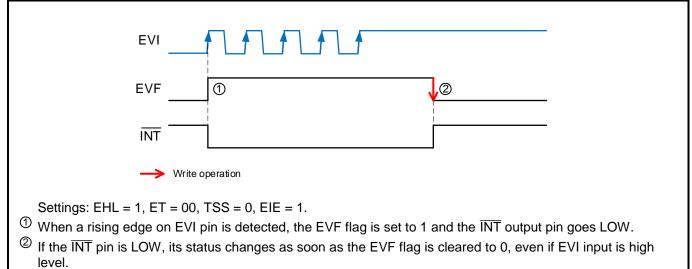

|    | 4.11.3. EDGE DETECTION (ET = 00)                         | 73  |

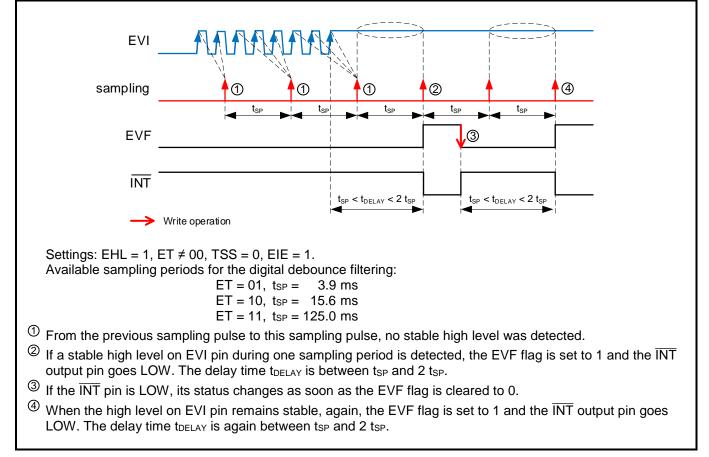

|    | 4.11.4. LEVEL DETECTION WITH FILTERING (ET ≠ 00)         |     |

| 4  | I.12. AUTOMATIC BACKUP SWITCHOVER INTERRUPT FUNCTION     | 74  |

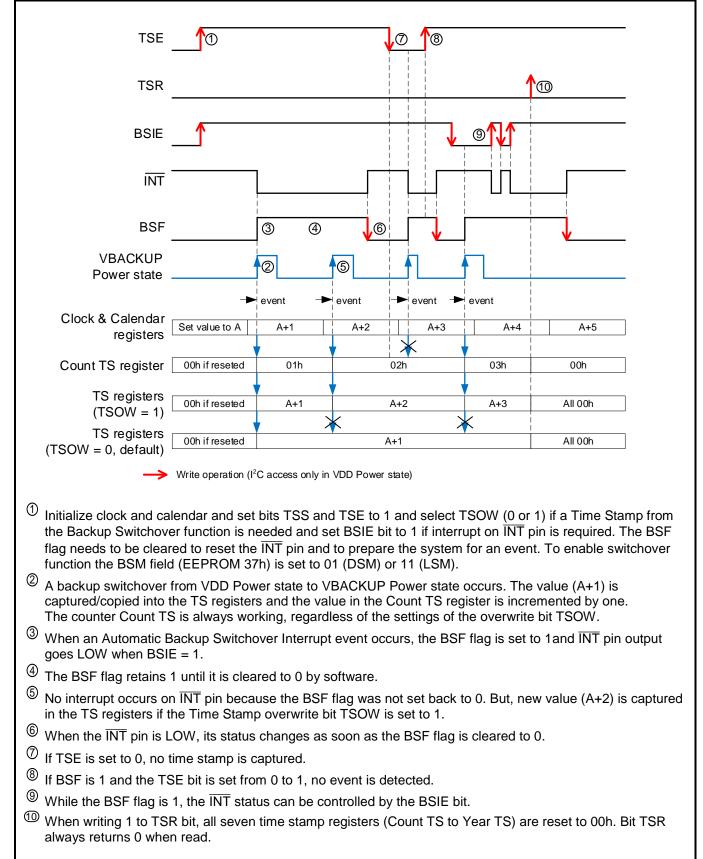

|    | 4.12.1. AUTOMATIC BACKUP SWITCHOVER DIAGRAM              | 75  |

|    | 4.12.2. USE OF THE AUTOMATIC BACKUP SWITCHOVER INTERRUPT | 76  |

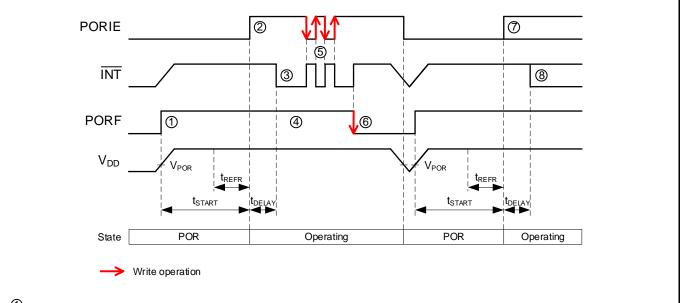

| 4  | 1.13. POWER ON RESET INTERRUPT FUNCTION                  |     |

|    | 4.13.1. POWER ON RESET DIAGRAM                           | 77  |

|    | 4.13.2. USE OF THE POWER ON RESET INTERRUPT              | 78  |

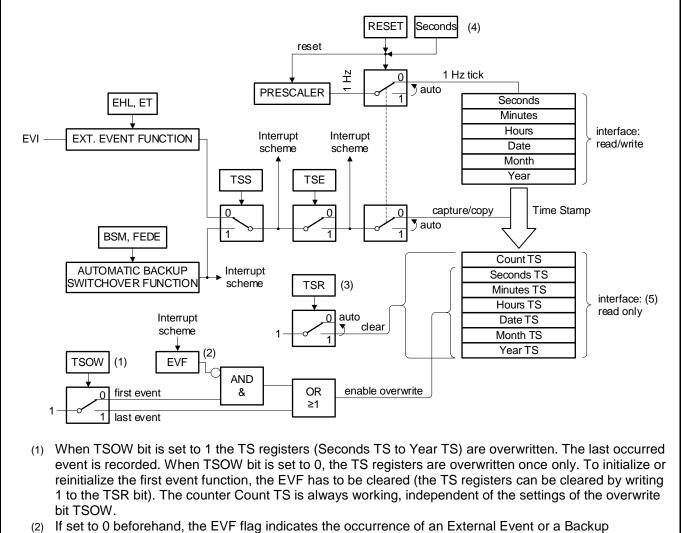

| 4  | 9.14. TIME STAMP FUNCTION                                | 79  |

| 4  | I.15. FREQUENCY OFFSET CORRECTION                        | 81  |

|    | 4.15.1. EEOFFSET VALUE DETERMINATION                     | 81  |

|    | 4.15.2. VERIFICATION OF THE CORRECTED TIME ACCURACY      | 81  |

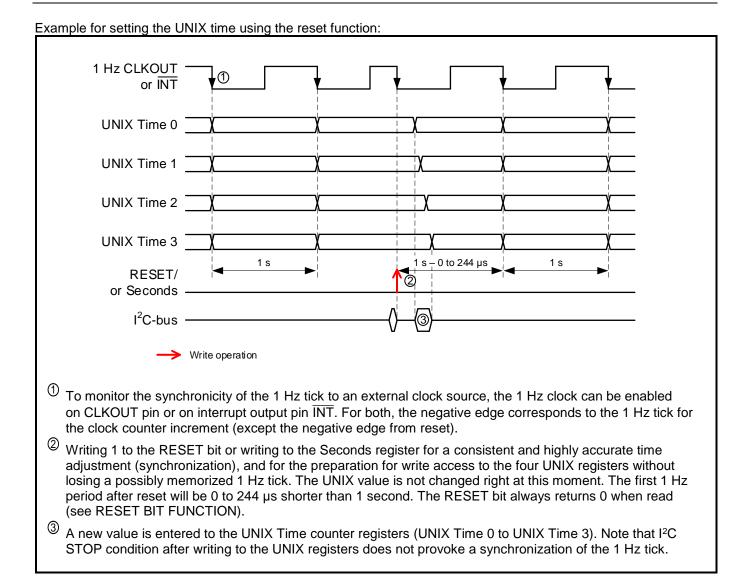

| 4  | I.16. UNIX TIME COUNTER                                  |     |

|    | 4.16.1. SETTING THE UNIX TIME                            |     |

|    | 4.16.2. READING THE UNIX TIME                            |     |

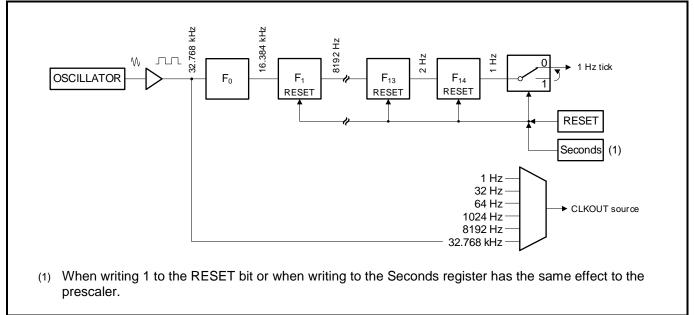

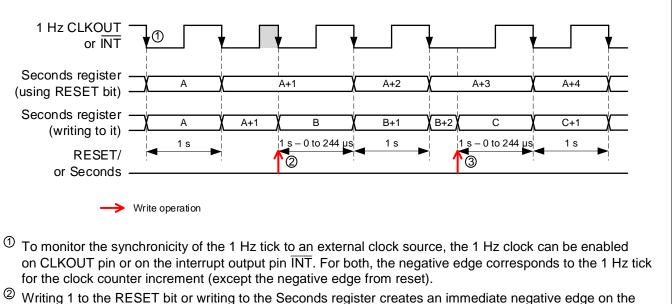

| 4  | I.17. RESET BIT FUNCTION                                 | 85  |

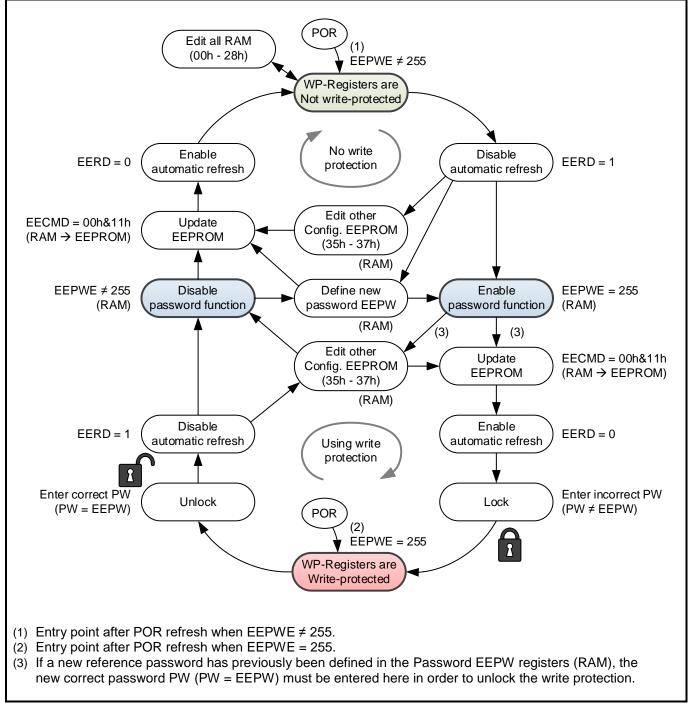

| 4  | 9.18. USER PROGRAMMABLE PASSWORD                         | 87  |

|    | 4.18.1. ENABLE/DISABLE WRITE PROTECTION                  | 87  |

|    | 4.18.2. CHANGING PASSWORD                                |     |

|    | 4.18.3. FLOWCHART                                        |     |

| 5. | I <sup>2</sup> C INTERFACE                               | 90  |

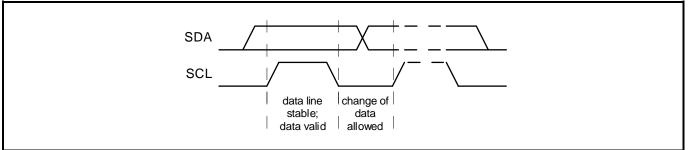

| -  | 5.1. BIT TRANSFER                                        |     |

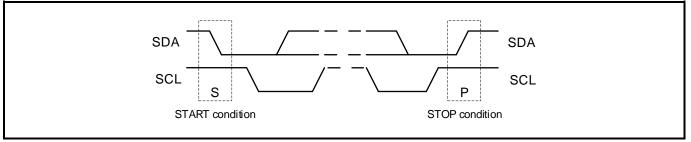

|    | 5.2. START AND STOP CONDITIONS                           |     |

| 5  | 5.3. DATA VALID                                          | 91  |

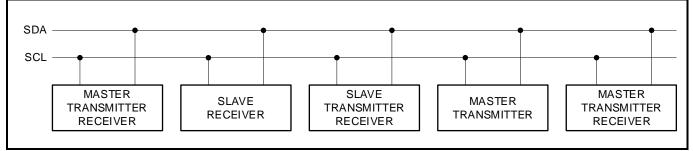

| 5  | 5.4. SYSTEM CONFIGURATION                                | 91  |

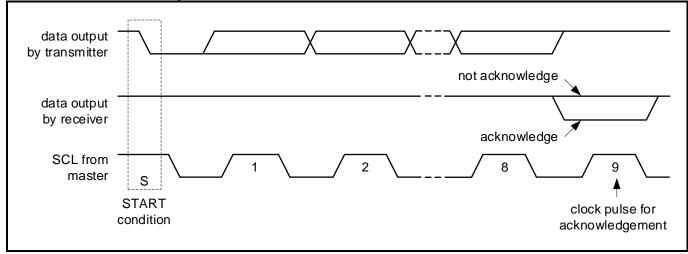

| 5  | 5.5. ACKNOWLEDGE                                         | 92  |

| 5  | 5.6. SLAVE ADDRESS                                       | 93  |

| 5  | 5.7. WRITE OPERATION                                     | 93  |

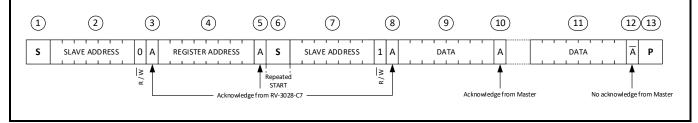

| 5  | 5.8. READ OPERATION AT SPECIFIC ADDRESS                  | 94  |

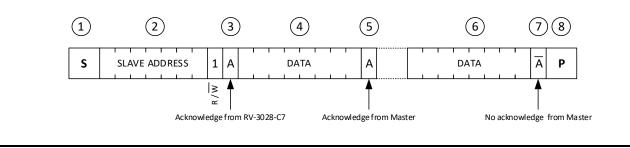

| 5  | 5.9. READ OPERATION                                      | 94  |

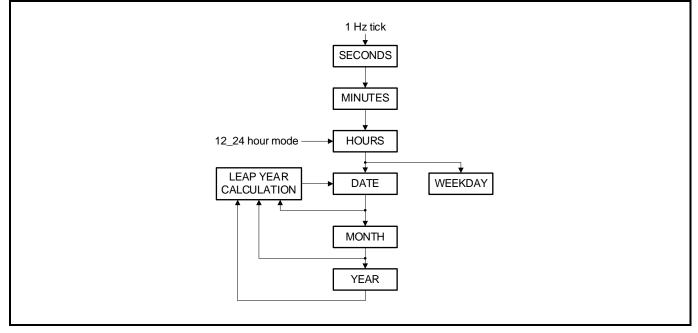

| 5  | 5.10. PC-BUS IN SWITCHOVER CONDITION                     | 95  |

| 6. | ELECTRICAL SPECIFICATIONS                                | 96  |

| 6  | 6.1. ABSOLUTE MAXIMUM RATINGS                            | 96  |

| 6  | 6.2. OPERATING PARAMETERS                                | 97  |

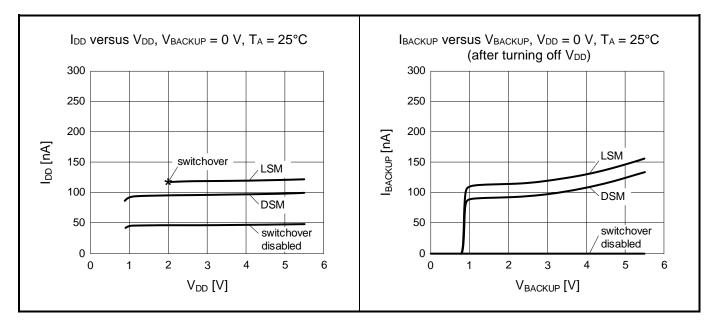

|    | 6.2.1. TYPICAL CHARACTERISTICS                           | 99  |

| 6  | 6.3. OSCILLATOR PARAMETERS                               |     |

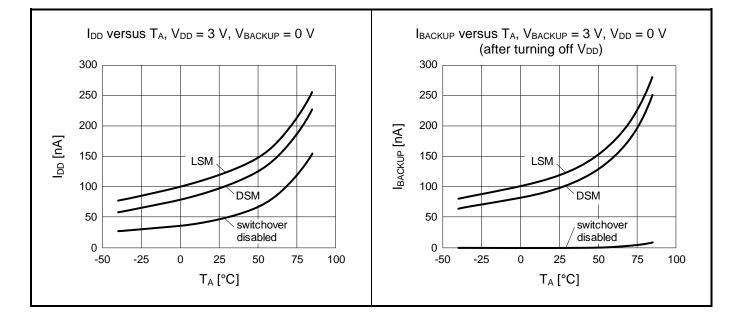

|    | 6.3.1. XTAL FREQUENCY VS. TEMPERATURE CHARACTERISTICS    | 100 |

| 6  | 6.4. POWER ON AC ELECTRICAL CHARACTERISTICS              | 101 |

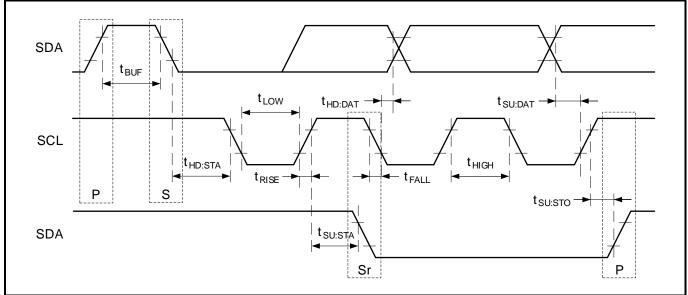

|    | 6.5.        | PC-BUS CHARACTERISTICS                                          | 102 |

|----|-------------|-----------------------------------------------------------------|-----|

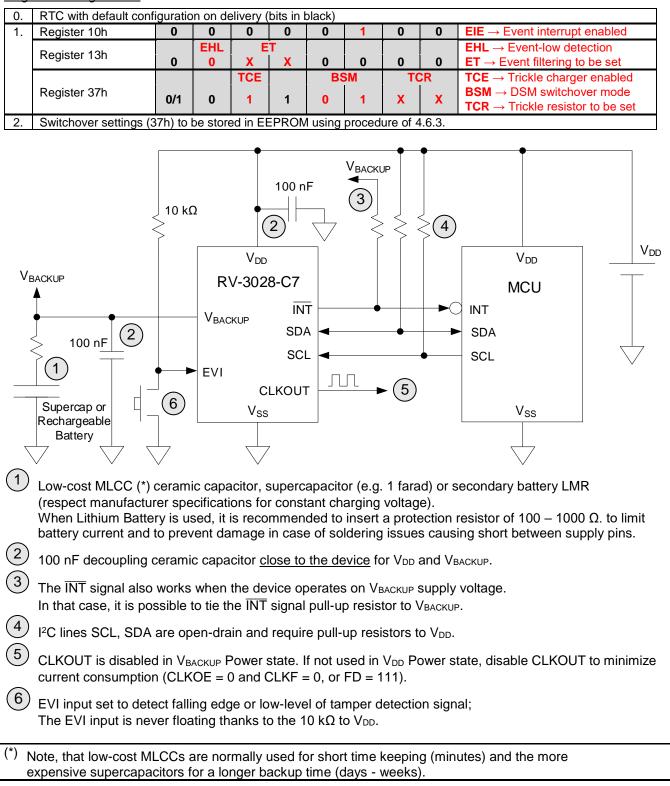

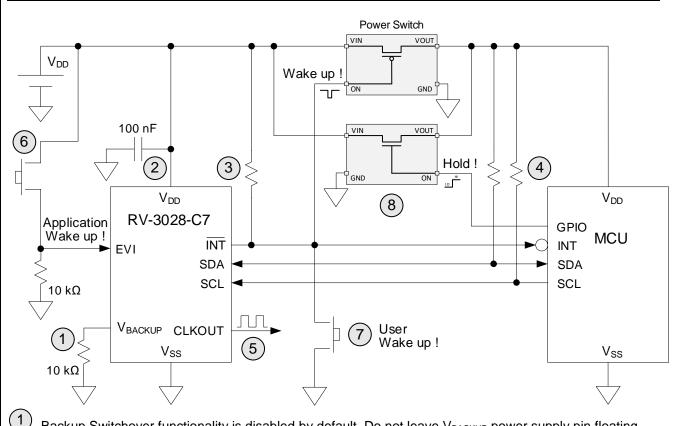

| 7. | TY          | PICAL APPLICATION CIRCUITS                                      | 03  |

|    | 7.1.        | NO BACKUP SOURCE / EVENT INPUT NOT USED                         | 103 |

|    | 7.2.        | NON-RECHARGEABLE BACKUP SOURCE / EVENT INPUT USED (ACTIVE HIGH) | 104 |

|    | 7.3.        | RECHARGEABLE BACKUP SOURCE / EVENT INPUT USED (ACTIVE LOW)      | 105 |

|    | 7.4.        | NO BACKUP SOURCE / EVENT INPUT USED ("WAKE-UP"& "POWER SWITCH") | 106 |

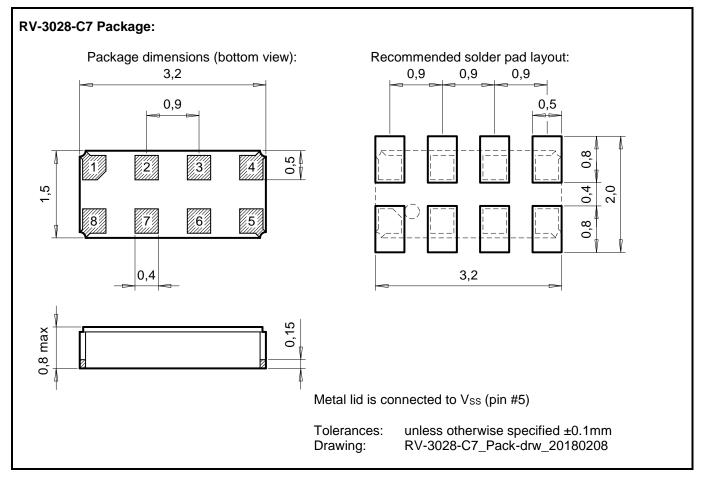

| 8. | PA          | CKAGE1                                                          | 07  |

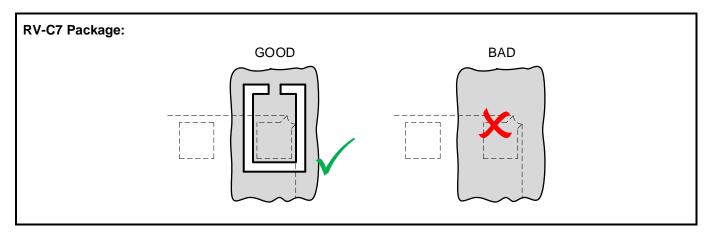

|    | 8.1.        | DIMENSIONS AND SOLDER PAD LAYOUT                                | 107 |

|    | 8.          | 1.1. RECOMMENDED THERMAL RELIEF                                 | 07  |

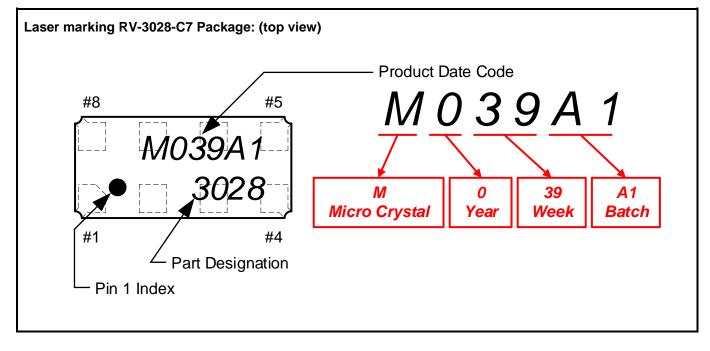

|    | 8.2.        | MARKING AND PIN #1 INDEX                                        | 108 |

| 9. | MA          | TERIAL COMPOSITION DECLARATION & ENVIRONMENTAL INFORMATION      | 09  |

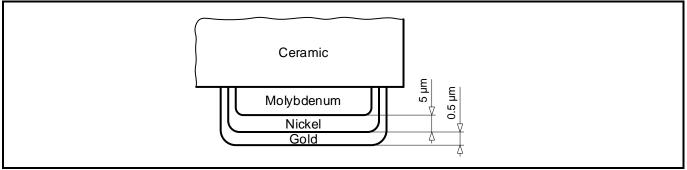

|    | 9.1.        | HOMOGENOUS MATERIAL COMPOSITION DECLARATION                     | 109 |

|    | 9.2.        | MATERIAL ANALYSIS & TEST RESULTS                                | 110 |

|    | 9.3.        | RECYCLING MATERIAL INFORMATION                                  | 111 |

|    | 9.4.        | ENVIRONMENTAL PROPERTIES & ABSOLUTE MAXIMUM RATINGS             | 112 |

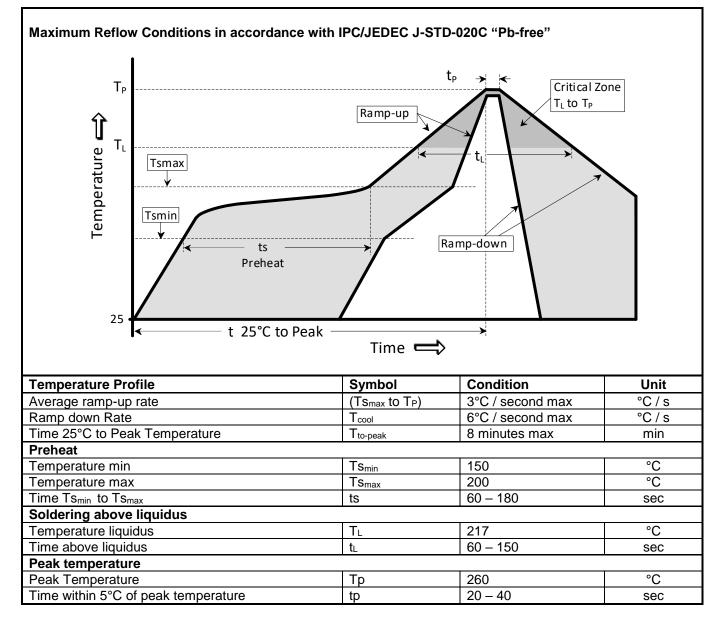

| 10 | ). SO       | LDERING INFORMATION                                             | 13  |

| 11 | . <b>HA</b> | NDLING PRECAUTIONS FOR MODULES WITH EMBEDDED CRYSTALS           | 14  |

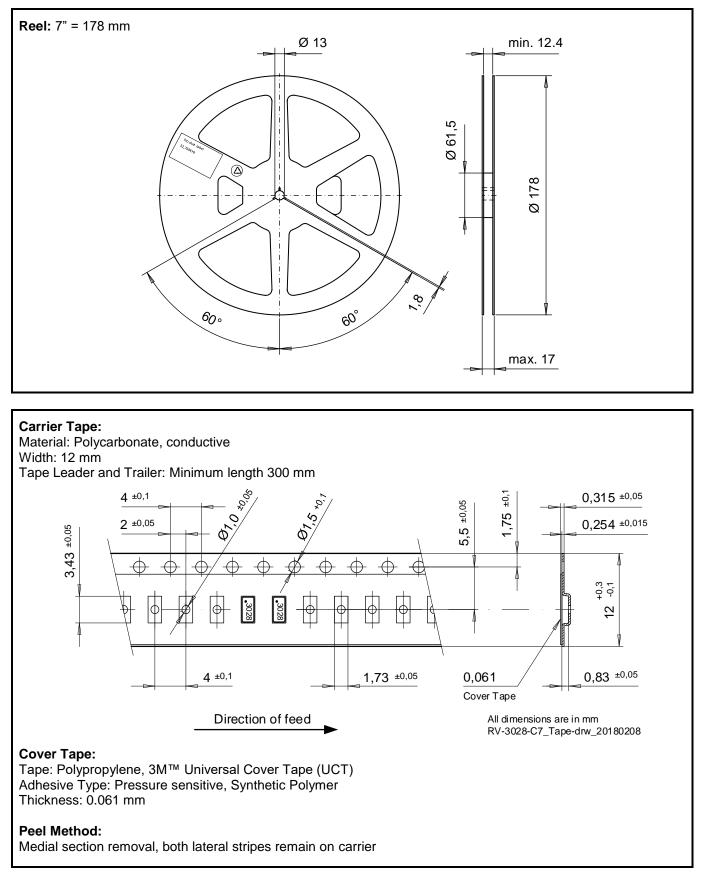

| 12 | 2. PA       | CKING & SHIPPING INFORMATION                                    | 15  |

|    |             | MPLIANCE INFORMATION                                            |     |

| 14 | I. DO       | CUMENT REVISION HISTORY                                         | 16  |

# RV-3028-C7

# Extreme Low Power Real-Time Clock (RTC) Module with I<sup>2</sup>C-Bus Interface

# 1. OVERVIEW

- RTC module with built-in 32.768 kHz "Tuning Fork" crystal oscillator

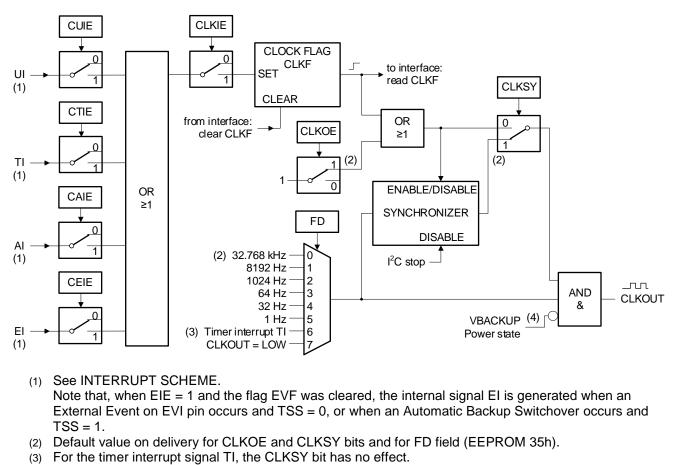

- Counters for seconds, minutes, hours, date, month, year and weekday

- 32-bit UNIX Time counter

- Automatic leap year correction: 2000 to 2099

- Aging compensation with user programmable EEPROM Offset value (Factory Calibrated value may be changed by the user)

- Periodic Countdown Timer Interrupt function; interrupt output also in VBACKUP Power state

- Periodic Time Update Interrupt function (seconds, minutes); interrupt output also in VBACKUP Power state

- Alarm Interrupts for weekday or date, hour and minute settings; interrupt output also in VBACKUP Power state

- External Event Input with Interrupt and Time Stamp function; interrupt output also in VBACKUP Power state

- Factory calibrated time accuracy: ±1 ppm @ 25°C (EEPROM Offset value may be changed by the user)

- 32.768 kHz Xtal oscillator frequency accuracy: ±5 ppm @ 25°C

- 43 bytes of user EEPROM

- Configuration registers stored in EEPROM and mirrored in RAM

- User programmable password for write protection of the time, control and configuration registers

- I<sup>2</sup>C-bus interface (up to 400 kHz)

- Programmable Clock Output

- Enable/disable by CLKOE bit

- Enable by an Interrupt function

- o 32.768 kHz, 8192 Hz, 1024 Hz, 64 Hz, 32 Hz, 1 Hz

- Periodic countdown timer interrupt as clock output frequency

- Synchronized enable/disable

- Automatic Backup switchover with Interrupt and Time Stamp function

- Internal Power On Reset (POR) with Interrupt function

- Trickle charger

- Wide Timekeeping voltage range: 1.1 to 5.5 V

- Wide interface operating voltage: 1.2 to 5.5 V

- Extreme low current consumption: 45 nA ( $V_{DD} = 3.0 \text{ V}, T_A = 25^{\circ}\text{C}$ )

- Operating temperature range: -40 to +85°C

- Ultra small and compact C7 package size (3.2 x 1.5 x 0.8 mm), RoHS-compliant and 100% lead-free

- Automotive qualification according to AEC-Q200 available

# **1.1. GENERAL DESCRIPTION**

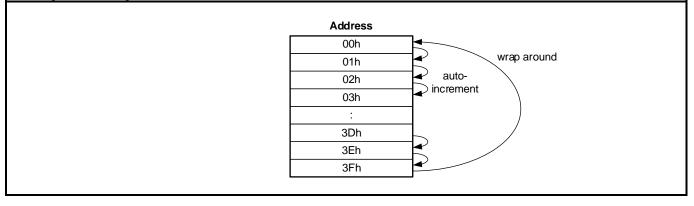

The RV-3028-C7 is a CMOS real-time clock/calendar module with an automatic backup switchover circuit and is optimized for extreme low power consumption. It provides full RTC function with programmable counters, alarm, selectable interrupt and clock output functions and also a 32-bit UNIX Time counter. The internal EEPROM memory hosts all configuration settings and allows for additional user memory. An EEOffset value allows compensating the frequency deviation of the 32.768 kHz clock. Addresses and data are transmitted via an I<sup>2</sup>C-bus interface for communication with a host controller. The Address Pointer is incremented automatically after each written or read data byte.

This ultra small RTC module has been specially designed for miniature and cost sensitive high volume applications.

# 1.2. APPLICATIONS

The RV-3028-C7 RTC module combines key functions with outstanding performance in an ultra small ceramic package:

- Extreme Low Power consumption

- Smallest RTC module (embedded XTAL) in an ultra-small 3.2 x 1.5 x 0.8 mm lead-free ceramic package

These unique features make this product perfectly suitable for many applications:

- Communication: IoT / Wearables / Wireless Sensors and Tags / Handsets

- Automotive: M2M / Navigation & Tracking Systems / Dashboard / Tachometers / Engine Controller Car Audio & Entertainment Systems

- Metering: E-Meter / Heating Counter / Smart Meters / PV Converter/ Utility metering

- Outdoor: ATM & POS systems / Surveillance & Safety systems / Ticketing Systems

- Medical: Glucose Meter / Health Monitoring Systems

- Safety: Security & Camera Systems / Door Lock & Access Control / Tamper Detection

- Consumer: Gambling Machines / TV & Set Top Boxes / White Goods

- Automation: PLC / Data Logger / Home & Factory Automation / Industrial and Consumer Electronics

# **1.3. ORDERING INFORMATION**

Example: RV-3028-C7 TA QC

| Code          | Operating temperature range |

|---------------|-----------------------------|

| TA (Standard) | -40 to +85°C                |

| Code          | Qualification             |

|---------------|---------------------------|

| QC (Standard) | Commercial Grade          |

| QA            | Automotive Grade AEC-Q200 |

RV-3028-C7

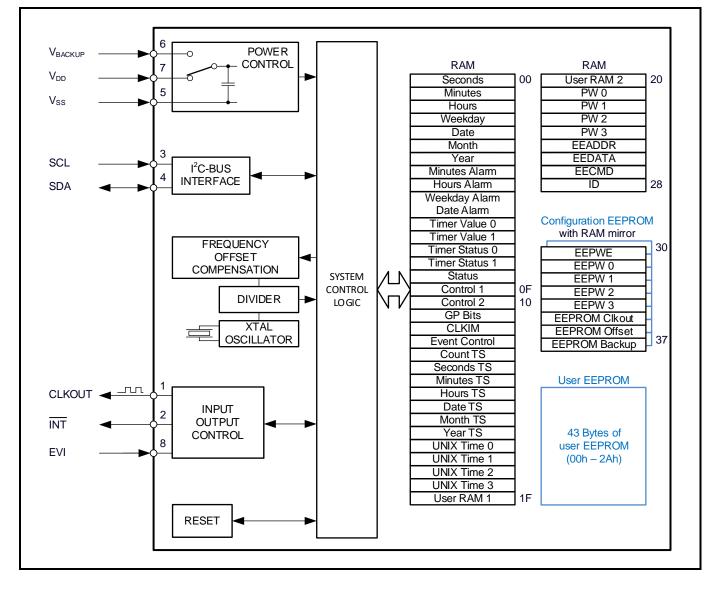

# 2. BLOCK DIAGRAM

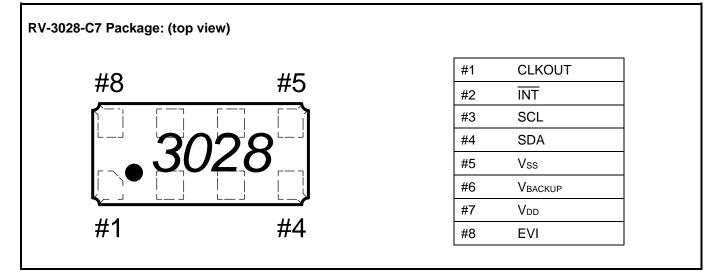

# 2.1. PINOUT

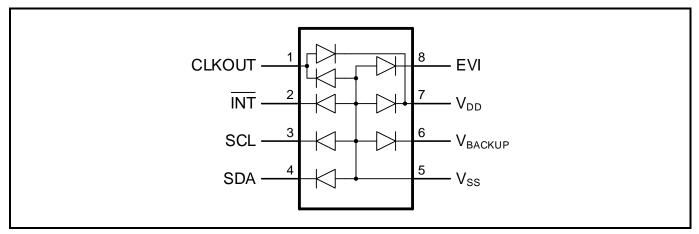

# 2.2. PIN DESCRIPTION

| Symbol          | Pin # | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CLKOUT          | 1     | <ul> <li>Clock Output; push-pull; Normal and Interrupt driven clock output can be activated concurrently: <ol> <li>Normal clock output can be controlled by the CLKOE bit (EEPROM 35h) when CLKF = 0. When CLKOE is set to 1 (default), the CLKOUT pin drives the square wave on the CLKOUT pin. When CLKOE bit is set to 0, the CLKOUT pin is LOW.</li> <li>Interrupt driven clock output can be controlled by interrupt events when CLKOE = 0. When CLKIE bit (10h) is set to 1 the occurrence of the interrupt selected in the Clock Interrupt Mask Register (12h) allows the square wave output on the CLKOUT pin. Writing 0 to CLKIE will disable new interrupts from driving square wave on CLKOUT. When CLKF flag is cleared, the CLKOUT pin is LOW.</li> </ol> </li> <li>Depending of the settings in the FD field (EEPROM 35h), the CLKOUT pin can drive the square wave of 32.768 kHz (default), 8192 Hz, 1024 Hz, 64 Hz, 32 Hz or 1 Hz, or the predefined periodic countdown timer interrupt. When FD field is 111 the CLKOUT pin is LOW.</li> <li>When CLKSY bit (EEPROM 35h) set to 1, the enabling and disabling of the clock output is synchronized. CLKSY has no effect on the timer interrupt signal.</li> <li>In VBACKUP Power state, the CLKOUT pin is LOW.</li> </ul> |  |  |  |  |  |

| ĪNT             | 2     | Interrupt Output; open-drain; active LOW; requires pull-up resistor when used; used to output<br>Periodic Countdown Timer, Periodic Time Update, Alarm, External Event, Automatic Backup<br>Switchover and Power On Reset Interrupt signals. Interrupt output also in VBACKUP Power state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| SCL             | 3     | I <sup>2</sup> C Serial Clock Input; requires pull-up resistor. In VBACKUP Power state, the SCL pin is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| SDA             | 4     | I <sup>2</sup> C Serial Data Input-Output; open-drain; requires pull-up resistor. In VBACKUP Power state, the SDA pin is disabled (high impedance).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| V <sub>SS</sub> | 5     | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| VBACKUP         | 6     | Backup Supply Voltage. When the backup switchover function is not needed, $V_{BACKUP}$ must be tied to $V_{SS}$ with a 10 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| V <sub>DD</sub> | 7     | Power Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| EVI             | 8     | External Event Input; used for interrupt generation, interrupt driven clock output and time stamp function. Remains active also in VBACKUP Power state. This pin should not be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

# 2.3. FUNCTIONAL DESCRIPTION

The RV-3028-C7 is an extreme-low power CMOS based Real-Time-Clock Module with embedded 32.768 kHz crystal oscillator. It includes an Automatic Backup switchover function with a Trickle charger where the interrupt output pin INT is also working in VBACKUP Power state. The clock output on CLKOUT pin can be enabled normally via command over I<sup>2</sup>C interface or can be interrupt driven and synchronized clock output enable/disable on CLKOUT pin can be freely selected. The configuration registers are stored permanently in EEPROM and mirrored in RAM in order that the RTC module is still configured correctly even after power down. For safety against inadvertent overwriting the time, control and configuration registers can be protected by a User Programmable Password. Additionally, there is an EEPROM Offset value customer use for aging correction.

The RV-3028-C7 provides standard Clock & Calendar function including seconds, minutes, hours (12 or 24 h), weekdays, date, months, years (with leap year correction) and interrupt functions for the Periodic Countdown Timer, Periodic Time Update, Alarm, External Event, Automatic Backup Switchover and Power On Reset. All is accessible via I<sup>2</sup>C-bus (2-wire Interface). The interrupt functions and the Time Stamp of the External Event function are also working in VBACKUP Power state. Beside the standard RTC functions a 32-bit UNIX Time counter and 43 Bytes of User Memory EEPROM and 2 Bytes of User RAM are provided. A further Byte can be used as User RAM when the Periodic Countdown Timer is not used (Timer Value register 0Ah) and a further Byte when the Alarm function is not used (Alarm register 07h).

The registers are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes can be performed in a single access, with the address automatically incremented after each byte by the Address Pointer. When address is automatically incremented, wrap around occurs from address 3Fh to address 00h (see figure below). All registers are designed as addressable 8-bit registers despite the fact that not all registers and bits are implemented.

Handling address registers:

# 2.4. DEVICE PROTECTION DIAGRAM

# 3. REGISTER ORGANIZATION

- RAM Registers at addresses 00h to 28h are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte.

- The Configuration Registers at addresses 30h to 37h are memorized in EEPROM and mirrored in RAM. For the RAM mirror, multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte.

- There are 43 bytes of non-volatile user memory EEPROM at addresses 00h to 2Ah for general use.

The following tables summarize the function of each register.

# **3.1. REGISTER CONVENTIONS**

The conventions in this table serve as a key for the register overview and individual register diagrams:

| Convention<br>(Conv.) | Description                                                                                      |  |  |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| R                     | Read only. Writing to this register has no effect.                                               |  |  |  |  |  |  |  |  |

| W                     | Write only. Returns 0 when read.                                                                 |  |  |  |  |  |  |  |  |

| R/WP                  | Read: Always readable. Write: Can be write-protected by password.                                |  |  |  |  |  |  |  |  |

| WP                    | Write only. Returns 0 when read. Can be write-protected by password.                             |  |  |  |  |  |  |  |  |

| *WP                   | EEPW registers: RAM mirror is Write only. Returns 0 when read. EEPROM can be READ when Unlocked. |  |  |  |  |  |  |  |  |

| Prot.                 | Protected. Writing to this register has no effect.                                               |  |  |  |  |  |  |  |  |

#### RV-3028-C7

# 3.2. REGISTER OVERVIEW

After reset, all registers are set according to Table in section REGISTER RESET VALUES SUMMARY.

# Register Definitions; RAM, Address 00h to 3Fh:

| Address                   | Function                 | Conv.    | Bit 7  | Bit 6    | Bit 5 | Bit 4 | Bit 3    | Bit 2 | Bit 1 | Bit |  |

|---------------------------|--------------------------|----------|--------|----------|-------|-------|----------|-------|-------|-----|--|

| 00h                       | Seconds                  | R/WP     | 0      | 40       | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 01h                       | Minutes                  | R/WP     | 0      | 40       | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 02h                       | Hours (24 hour)          | R/WP     | 0      | 0        | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 0211                      | Hours (12 hour)          | 1.7,4,41 | 0      | 0        | AMPM  | 10    | 8        | 4     | 2     | 1   |  |

| 03h                       | Weekday                  | R/WP     | 0      | 0        | 0     | 0     | 0        | 4     | 2     | 1   |  |

| 04h                       | Date                     | R/WP     | 0      | 0        | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 05h                       | Month                    | R/WP     | 0      | 0        | 0     | 10    | 8        | 4     | 2     | 1   |  |

| 06h                       | Year                     | R/WP     | 80     | 40       | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 07h                       | Minutes Alarm            | R/WP     | AE_M   | 40       | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 08h                       | Hours Alarm (24h)        | R/WP     | AE_H   | 0        | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 0011                      | Hours Alarm (12h)        |          |        | 0        | AMPM  | 10    | 8        | 4     | 2     | 1   |  |

| 09h                       | Weekday Alarm            | R/WP     | AE_WD  | <u>_</u> | 0     | 0     | 0        | 4     | 2     | 1   |  |

| 0911                      | Date Alarm               |          | AE_WD  | 0        | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 0Ah                       | Timer Value 0            | R/WP     | 128    | 64       | 32    | 16    | 8        | 4     | 2     | 1   |  |

| 0Bh                       | Timer Value 1            | R/WP     | 0      | 0        | 0     | 0     | 2048     | 1024  | 512   | 25  |  |

| 0Ch                       | Timer Status 0           | R        | 128    | 64       | 32    | 16    | 8        | 4     | 2     | 1   |  |

| 0Dh                       | Timer Status 1<br>shadow | R        | 0      | 0        | 0     | 0     | 2048     | 1024  | 512   | 25  |  |

| 0Eh                       | Status                   | R/WP     | EEbusy | CLKF     | BSF   | UF    | TF       | AF    | EVF   | PO  |  |

| 0Fh                       | Control 1                | R/WP     | TRPT   | -        | WADA  | USEL  | EERD     | TE    | Т     | D   |  |

| 10h                       | Control 2                | R/WP     | TSE    | CLKIE    | UIE   | TIE   | AIE      | EIE   | 12_24 | RES |  |

| 11h                       | GP Bits                  | R/WP     | -      | GP6      | GP5   | GP4   | GP3      | GP2   | GP1   | GF  |  |

| 12h                       | Clock Int. Mask          | R/WP     | -      | -        | -     | -     | CEIE     | CAIE  | CTIE  | CU  |  |

| 13h                       | Event Control            | R/WP     | 0      | EHL      | E     | Т     | 0        | TSR   | TSOW  | TS  |  |

| 14h                       | Count TS                 | R        | 128    | 64       | 32    | 16    | 8        | 4     | 2     | 1   |  |

| 15h                       | Seconds TS               | R        | 0      | 40       | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 16h                       | Minutes TS               | R        | 0      | 40       | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 471                       | Hours TS (24h)           | <b>_</b> |        |          | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 17h                       | Hours TS (12h)           | R        | 0      | 0        | AMPM  | 10    | 8        | 4     | 2     | 1   |  |

| 18h                       | Date TS                  | R        | 0      | 0        | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 19h                       | Month TS                 | R        | 0      | 0        | 0     | 10    | 8        | 4     | 2     | 1   |  |

| 1Ah                       | Year TS                  | R        | 80     | 40       | 20    | 10    | 8        | 4     | 2     | 1   |  |

| 1Bh                       | UNIX Time 0              | R/WP     |        |          |       | UNIX  | 0 [7:0]  |       |       |     |  |

| 1Ch                       | UNIX Time 1              | R/WP     |        |          |       |       | I [15:8] |       |       |     |  |

| 1Dh                       | UNIX Time 2              | R/WP     |        |          |       |       | [23:16]  |       |       |     |  |

| 1Eh                       | UNIX Time 3              | R/WP     |        |          |       |       | [31:24]  |       |       |     |  |

| 1Fh                       | User RAM 1               | R/WP     |        |          |       |       | 1 data   |       |       |     |  |

| 20h                       | User RAM 2               | R/WP     |        |          |       |       | 2 data   |       |       |     |  |

| 21h                       | Password 0               | W        |        |          |       |       | ) [7:0]  |       |       |     |  |

| 22h                       | Password 1               | W        |        |          |       |       | [15:8]   |       |       |     |  |

| 23h                       | Password 2               | W        |        |          |       | PW 2  |          |       |       |     |  |

| 24h                       | Password 3               | W        |        |          |       |       | [31:24]  |       |       |     |  |

| 25h                       | EE Address               | R/WP     |        |          |       |       | DDR      |       |       |     |  |

| 26h                       | EE Data                  | R/WP     |        |          |       |       | ATA      |       |       |     |  |

| 27h                       | EE Command               | WP       |        |          |       |       | CMD      |       |       |     |  |

| 28h                       | ID                       | R        |        | н        | ID    |       |          | V     | ID    |     |  |

|                           | RESERVED                 | Prot.    |        |          |       | RESE  | RVED     | v     |       |     |  |

| 29h and 2Ah               |                          |          |        |          |       |       |          |       |       |     |  |

| 29h and 2Ah<br>2Ch to 2Fh | RESERVED                 | Prot.    |        | RESERVED |       |       |          |       |       |     |  |

# Register Definitions; Configuration EEPROM with RAM mirror, Address 2Bh and 30h to 37h:

| Address | Function             | Conv. | Bit 7                          | Bit 6                              | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 |  |

|---------|----------------------|-------|--------------------------------|------------------------------------|-------|--------|-----------|-------|-------|-------|--|

| 2Bh     | EEPROM<br>Reserved   | R/WP  |                                | RESERVED (Must not be overwritten) |       |        |           |       |       |       |  |

| 30h     | EEPROM PW<br>Enable  | R/WP  |                                | EEPWE                              |       |        |           |       |       |       |  |

| 31h     | EEPROM<br>Password 0 | *WP   |                                | EEPW 0 [7:0]                       |       |        |           |       |       |       |  |

| 32h     | EEPROM<br>Password 1 | *WP   |                                | EEPW 1 [15:8]                      |       |        |           |       |       |       |  |

| 33h     | EEPROM<br>Password 2 | *WP   |                                | EEPW 2 [23:16]                     |       |        |           |       |       |       |  |

| 34h     | EEPROM<br>Password 3 | *WP   |                                |                                    |       | EEPW   | 3 [31:24] |       |       |       |  |

| 35h     | EEPROM<br>Clkout     | R/WP  | CLKOE                          | CLKSY                              | -     | -      | PORIE     |       | FD    |       |  |

| 36h     | EEPROM<br>Offset     | R/WP  |                                |                                    |       | EEOffs | set [8:1] |       |       |       |  |

| 37h     | EEPROM<br>Backup     | R/WP  | EEOffset BSIE TCE FEDE BSM TCF |                                    |       |        |           | R     |       |       |  |

# Register Definitions; User EEPROM, Address 00h to 2Ah:

| Address    | Function                  | Conv. | Bit 7                                | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------|---------------------------|-------|--------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| 00h to 2Ah | User EEPROM<br>(43 Bytes) | R/WP  | 43 Bytes of non-volatile User EEPROM |       |       |       |       |       |       |       |

#### Register Definitions; Reserved EEPROM, Address 2Ch to 2Fh and 38h to 3Fh:

| Address    | Function           | Conv. | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------|--------------------|-------|----------|-------|-------|-------|-------|-------|-------|-------|

| 2Ch to 2Fh | Reserved<br>EEPROM | Prot. | RESERVED |       |       |       |       |       |       |       |

| 38h to 3Fh | Reserved<br>EEPROM | Prot. | RESERVED |       |       |       |       |       |       |       |

# **3.3. CLOCK REGISTERS**

#### 00h - Seconds

This register holds the count of seconds, in two binary coded decimal (BCD) digits. Values will be from 00 to 59. Read: Always readable. Write: Can be write-protected by password.

| Address | Function | Conv. | Bit 7    | Bit 6                               | Bit 5                                                         | Bit 4                                  | Bit 3        | Bit 2        | Bit 1        | Bit 0      |

|---------|----------|-------|----------|-------------------------------------|---------------------------------------------------------------|----------------------------------------|--------------|--------------|--------------|------------|

| 00h     | Seconds  | R/WP  | 0        | 40                                  | 20                                                            | 10                                     | 8            | 4            | 2            | 1          |

| UUN     | Reset    |       | 0        | 0                                   | 0                                                             | 0                                      | 0            | 0            | 0            | 0          |

| Bit     | Symbol   |       | Value    |                                     |                                                               |                                        | Descriptio   | n            |              |            |

| 7       | 0        |       | 0        | Read only                           | y. Always 0                                                   | •                                      |              |              |              |            |

| 6:0     | Seconds  |       | 00 to 59 | When wri<br>update is<br>reset (sar | ting to the S<br>reset and t<br>ne effect as<br>ting 1 to the | Seconds re<br>he prescale<br>s RESET B | er frequenci | ventual pres | 92 Hz to 1 H | Hz will be |

#### 01h – Minutes

This register holds the count of minutes, in two binary coded decimal (BCD) digits. Values will be from 00 to 59. Read: Always readable. Write: Can be write-protected by password.

| Address | Function | Conv. | Bit 7    | Bit 6     | Bit 5       | Bit 4       | Bit 3       | Bit 2  | Bit 1 | Bit 0 |

|---------|----------|-------|----------|-----------|-------------|-------------|-------------|--------|-------|-------|

| 01h     | Minutes  | R/WP  | 0        | 40        | 20          | 10          | 8           | 4      | 2     | 1     |

| UIN     | Reset    |       | 0        | 0         | 0           | 0           | 0           | 0      | 0     | 0     |

| Bit     | Symbol   |       | Value    |           |             | [           | Descriptior | า      |       |       |

| 7       | 0        |       | 0        | Read only | . Always 0. |             | •           |        |       |       |

| 6:0     | Minutes  |       | 00 to 59 | Holds the | count of m  | inutes, cod | ed in BCD f | ormat. |       |       |

#### 02h – Hours

This register holds the count of hours, in two binary coded decimal (BCD) digits. If the 12\_24 bit is cleared (default) (see STATUS AND CONTROL REGISTERS, 10h – Control 2) the values will be from 0 to 23. If the 12\_24 bit is set, the hour values will range from 1 to 12 and the AMPM bit will be 0 for AM hours and 1 for PM hours.

The value in the Hours register changes automatically between 12 and 24 hour mode when 12\_24 bit is changed. The value in the Hours Alarm register (08h) however must be rewritten.

Read: Always readable. Write: Can be write-protected by password.

| Address          | Function                                   | Conv.     | Bit 7   | Bit 6     | Bit 5       | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

|------------------|--------------------------------------------|-----------|---------|-----------|-------------|-------------|------------|-------|-------|-------|

| 0.01             | Hours (24 hour<br>mode)<br>– default value | R/WP      | 0       | 0         | 20          | 10          | 8          | 4     | 2     | 1     |

| 02h              | Hours (12 hour mode)                       |           |         |           | AMPM        | 10          | 8          | 4     | 2     | 1     |

|                  | Reset                                      |           | 0       | 0         | 0           | 0           | 0          | 0     | 0     | 0     |

| •                | ode), 12_24 = 0 – defa                     | ult value |         |           |             |             |            |       |       |       |

| Bit              | Symbol                                     |           | Value   |           |             |             | Descriptio | n     |       |       |

| 7:6              | 0                                          |           |         | Read only | y. Always 0 |             |            |       |       |       |

| 5:0              | Hours (24 hour mo<br>– default value       | de)       | 0 to 23 | Holds the | count of ho | ours, codec | in BCD for | mat.  |       |       |

| lours (12 hour m | ode), 12_24 = 1                            |           |         |           |             |             |            |       |       |       |

| Bit              | Symbol                                     |           | Value   |           |             | [           | Descriptio | n     |       |       |

| 7:6              | 0                                          |           | 0       | Read only | y. Always 0 |             |            |       |       |       |

| F                |                                            |           | 0       | AM hours  | S.          |             |            |       |       |       |

| 5                | AMPM                                       |           | 1       | PM hours  | 3.          |             |            |       |       |       |

| 4:0              | Hours (12 hour mo                          | de)       | 1 to 12 | Holds the | count of ho | ours, coded | in BCD for | mat.  |       |       |

Hours values:

| 24 hour mode | 12 hour mode | 24 hour mode | 12 hour mode |

|--------------|--------------|--------------|--------------|

| 00           | 12 (AM 12)   | 12           | 32 (PM 12)   |

| 01           | 01 (AM 1)    | 13           | 21 (PM 1)    |

| 02           | 02 (AM 2)    | 14           | 22 (PM 2)    |

| :            | :            | :            | :            |

| 10           | 10 (AM 10)   | 22           | 30 (PM 10)   |

| 11           | 11 (AM 11)   | 23           | 31 (PM 11)   |

# 3.4. CALENDAR REGISTERS

#### 03h – Weekday

This register holds the current day of the week. Each value represents one weekday that is assigned by the user. Values will range from 0 to 6. The weekday counter is simply a 3-bit counter which counts up to 6 and then resets to 0.

Read: Always readable. Write: Can be write-protected by password.

| Address          | Function  | Conv. | Bit 7  | Bit 6     | Bit 5       | Bit 4       | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|------------------|-----------|-------|--------|-----------|-------------|-------------|-------------|-------|-------|-------|

| 0.2 h            | Weekday   | R/WP  | 0      | 0         | 0           | 0           | 0           | 4     | 2     | 1     |

| 03h              | Reset     | •     | 0      | 0         | 0           | 0           | 0           | 0     | 0     | 0     |

| Bit              | Symbol    |       | Value  |           |             |             | Description | า     |       |       |

| 7:3              | 0         |       | 0      | Read only | y. Always 0 |             |             |       |       |       |

| 2:0              | Weekday   |       | 0 to 6 | Holds the | weekday c   | ounter valu | e.          |       |       |       |

| Weekday          |           |       | Bit 7  | Bit 6     | Bit 5       | Bit 4       | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

| Weekday 1 - Defa | ult value |       |        |           |             |             |             | 0     | 0     | 0     |

| Weekday 2        |           |       |        |           |             |             |             | 0     | 0     | 1     |

| Weekday 3        |           |       |        |           |             |             |             | 0     | 1     | 0     |

| Weekday 4        |           |       | 0      | 0         | 0           | 0           | 0           | 0     | 1     | 1     |

| Weekday 5        |           |       |        |           |             |             |             | 1     | 0     | 0     |

| Weekday 6        |           |       |        |           |             |             |             | 1     | 0     | 1     |

| Weekday 7        |           |       |        |           |             |             |             | 1     | 1     | 0     |

#### 04h – Date

This register holds the current day of the month, in two binary coded decimal (BCD) digits. Values will range from 01 to 31. Leap years are correctly handled from 2000 to 2099.

| Address | Function | Conv. | Bit 7    | Bit 6     | Bit 5                     | Bit 4        | Bit 3       | Bit 2      | Bit 1 | Bit 0 |

|---------|----------|-------|----------|-----------|---------------------------|--------------|-------------|------------|-------|-------|

| 04h     | Date     | R/WP  | 0        | 0         | 20                        | 10           | 8           | 4          | 2     | 1     |

| 0411    | Reset    |       | 0        | 0         | 0                         | 0            | 0           | 0          | 0     | 1     |

| Bit     | Symbol   |       | Value    |           |                           |              | Description | า          |       |       |

| 7:6     | 0        |       | 0        | Read only | /. Always 0               |              |             |            |       |       |

| 5:0     | Date     |       | 01 to 31 |           | current dat<br>value = 01 | te of the mo | onth, coded | in BCD for | mat.  |       |

#### 05h – Month

This register holds the current month, in two binary coded decimal (BCD) digits. Values will range from 01 to 12. Read: Always readable. Write: Can be write-protected by password.

| Address           | Function | Conv. | Bit 7    | Bit 6     | Bit 5        | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|-------|----------|-----------|--------------|-------------|------------|-------|-------|-------|

| 054               | Month    | R/WP  | 0        | 0         | 0            | 10          | 8          | 4     | 2     | 1     |

| 05h               | Reset    |       | 0        | 0         | 0            | 0           | 0          | 0     | 0     | 1     |

| Bit               | Symbol   |       | Value    |           |              |             | Descriptio | n     |       |       |

| 7:5               | 0        |       | 0        | Read only | y. Always 0  |             |            |       |       |       |

| 4:0               | Month    |       | 01 to 12 | Holds the | e current mo | onth, coded | in BCD for | mat.  |       |       |

| Months            |          |       | Bit 7    | Bit 6     | Bit 5        | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

| January - Default | value    |       |          |           |              | 0           | 0          | 0     | 0     | 1     |

| February          |          |       |          |           |              | 0           | 0          | 0     | 1     | 0     |

| March             |          |       |          |           |              | 0           | 0          | 0     | 1     | 1     |

| April             |          |       |          |           |              | 0           | 0          | 1     | 0     | 0     |

| May               |          |       |          |           |              | 0           | 0          | 1     | 0     | 1     |

| June              |          |       |          | 0         | 0            | 0           | 0          | 1     | 1     | 0     |

| July              |          |       | 0        | 0         | 0            | 0           | 0          | 1     | 1     | 1     |

| August            |          |       |          |           |              | 0           | 1          | 0     | 0     | 0     |

| September         |          |       |          |           |              | 0           | 1          | 0     | 0     | 1     |

| October           |          |       |          |           |              | 1           | 0          | 0     | 0     | 0     |

| November          |          |       |          |           |              | 1           | 0          | 0     | 0     | 1     |

| December          |          |       |          |           |              | 1           | 0          | 0     | 1     | 0     |

# 06h – Year

This register holds the current year, in two binary coded decimal (BCD) digits. Values will range from 00 to 99. Leap years are correctly handled from 2000 to 2099.

| Address | Function | Conv. | Bit 7    | Bit 6     | Bit 5       | Bit 4        | Bit 3       | Bit 2        | Bit 1        | Bit 0 |

|---------|----------|-------|----------|-----------|-------------|--------------|-------------|--------------|--------------|-------|

| Och     | Year     | R/WP  | 80       | 40        | 20          | 10           | 8           | 4            | 2            | 1     |

| 06h     | Reset    | •     | 0        | 0         | 0           | 0            | 0           | 0            | 0            | 0     |

| Bit     | Symbol   |       | Value    |           |             | [            | Descriptior | ı            |              |       |

| 7:0     | Year     |       | 00 to 99 | Holds the | current yea | ar, coded in | BCD forma   | at. – Defaul | t value = 00 | )     |

#### 3.5. ALARM REGISTERS

#### 07h - Minutes Alarm

This register holds the Minutes Alarm Enable bit AE\_M and the alarm value for minutes, in two binary coded decimal (BCD) digits. Values will range from 00 to 59.

Read: Always readable. Write: Can be write-protected by password.

| Address | Function      | Conv. | Bit 7    | Bit 6      | Bit 5        | Bit 4        | Bit 3        | Bit 2      | Bit 1     | Bit 0 |

|---------|---------------|-------|----------|------------|--------------|--------------|--------------|------------|-----------|-------|

| 07h     | Minutes Alarm | R/WP  | AE_M     | 40         | 20           | 10           | 8            | 4          | 2         | 1     |

| 0711    | Reset         |       | 1        | 0          | 0            | 0            | 0            | 0          | 0         | 0     |

| Bit     | Symbol        |       | Value    |            |              | I            | Description  | n          |           |       |

|         |               |       | Mir      | utes Alarm |              |              | arm togethe  |            | H and AE_ | WD    |

| 7       | AE_M          |       | 0        | Minutes A  | larm is ena  | abled.       |              |            |           |       |

|         |               |       | 1        | Minutes A  | larm is disa | abled. – De  | fault value  |            |           |       |

| 6:0     | Minutes Alarm |       | 00 to 59 | Holds the  | alarm valu   | e for minute | es, coded ir | n BCD form | at.       |       |

#### 08h – Hours Alarm

This register holds the Hours Alarm Enable bit AE\_H and the alarm value for hours, in two binary coded decimal (BCD) digits. If the 12\_24 bit is cleared (default value) (see STATUS AND CONTROL REGISTERS, 10h – Control 2) the values will range from 0 to 23. If the 12\_24 bit is set, the hour values will be from 1 to 12 and the AMPM bit will be 0 for AM hours and 1 for PM hours.

If the 12\_24 hour mode bit is changed then the value in the Hours Alarm register must be re-initialized.

| Address           | Function                                         | Conv.       | Bit 7   | Bit 6                                                 | Bit 5                          | Bit 4        | Bit 3        | Bit 2       | Bit 1    | Bit 0 |  |  |  |

|-------------------|--------------------------------------------------|-------------|---------|-------------------------------------------------------|--------------------------------|--------------|--------------|-------------|----------|-------|--|--|--|

| 001               | Hours Alarm (24<br>hour mode)<br>– default value | R/WP        | AE_H    | 0                                                     | 20                             | 10           | 8            | 4           | 2        | 1     |  |  |  |

| 08h               | Hours Alarm (12<br>hour mode)                    |             |         |                                                       | AMPM                           | 10           | 8            | 4           | 2        | 1     |  |  |  |

|                   | Reset                                            |             | 1       | 0                                                     | 0                              | 0            | 0            | 0           | 0        | 0     |  |  |  |

| Hours Alarm (24 h | our mode), 12_24 = 0 -                           | - default \ | value   |                                                       |                                |              |              |             |          |       |  |  |  |

| Bit               | Symbol                                           |             | Value   |                                                       |                                |              | Description  | า           |          |       |  |  |  |

|                   |                                                  |             |         | Hours Ala                                             | rm Enable b                    | oit (see USI | OF THE A     | ALARM INT   | ERRUPT). |       |  |  |  |

| 7                 | AE_H                                             |             | 0       | Enabled                                               |                                |              |              |             |          |       |  |  |  |

|                   |                                                  |             |         | Disabled                                              | <ul> <li>Default va</li> </ul> | alue         |              |             |          |       |  |  |  |

| 6                 | 0                                                | )           |         | Read onl                                              | y. Always 0                    |              |              |             |          |       |  |  |  |

| 5:0               | Hours Alarm (24 ho<br>mode) – default valu       |             | 0 to 23 | Holds the alarm value for hours, coded in BCD format. |                                |              |              |             |          |       |  |  |  |

| Hours Alarm (12 h | our mode), 12_24 = 1                             |             |         |                                                       |                                |              |              |             |          |       |  |  |  |

| Bit               | Symbol                                           |             | Value   |                                                       |                                |              | Description  | n           |          |       |  |  |  |

|                   |                                                  |             |         | Hours Ala                                             | rm Enable b                    | oit (see USI | OF THE A     | ALARM INT   | ERRUPT). |       |  |  |  |

| 7                 | AE_H                                             |             | 0       | Enabled                                               |                                |              |              |             |          |       |  |  |  |

|                   |                                                  |             | 1       | Disabled                                              | <ul> <li>Default va</li> </ul> | alue         |              |             |          |       |  |  |  |

| 6                 | 0                                                |             | 0       | Read onl                                              | y. Always 0                    |              |              |             |          |       |  |  |  |

| 5                 | AMPM                                             |             | 0       | AM hours                                              | 3.                             |              |              |             |          |       |  |  |  |

| 5                 |                                                  |             | 1       | PM hours                                              | S.                             |              |              |             |          |       |  |  |  |

| 4:0               | Hours Alarm (12 ho mode)                         | ur          | 1 to 12 | Holds the                                             | e alarm valu                   | e for hours  | , coded in E | BCD format. | 1        |       |  |  |  |

#### 09h – Weekday/Date Alarm

This register holds the Weekday/Date Alarm Enable bit AE\_WD. If the WADA bit is 0 (Bit 5 in Register 0Fh), it holds the alarm value for the weekday (weekdays assigned by the user), in two binary coded decimal (BCD) digits. Values will range from 0 to 6. If the WADA bit is 1, it holds the alarm value for the date, in two binary coded decimal (BCD) digits. Values will range from 01 to 31. Leap years are correctly handled from 2000 to 2099. Read: Always readable. Write: Can be write-protected by password.

| Address | Function                         | Conv. | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|         | Weekday Alarm –<br>default value | R/WP  | AE WD | 0     | 0     | 0     | 0     | 4     | 2     | 1     |

| 09h     | Date Alarm                       |       | _     |       | 20    | 10    | 8     | 4     | 2     | 1     |

|         | Reset                            |       | 1     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Weekday Alarm, WADA = 0 – default value

| Bit | Symbol        | Value  | Description                                                                                               |

|-----|---------------|--------|-----------------------------------------------------------------------------------------------------------|

|     |               | Week   | day/Date Alarm Enable bit. Enables alarm together with AE_M and AE_H<br>(see USE OF THE ALARM INTERRUPT). |

| 7   | AE_WD         | 0      | Enabled                                                                                                   |

|     |               | 1      | Disabled – Default value                                                                                  |

| 6:3 | 0             | 0      | Read only. Always 0.                                                                                      |

| 2:0 | Weekday Alarm | 0 to 6 | Holds the weekday alarm value, coded in BCD format.                                                       |

| Date Alarm, WAI | DA = 1     |          |                                                                                                                                       |

|-----------------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Bit             | Symbol     | Value    | Description                                                                                                                           |

| _               |            | Week     | day/Date Alarm Enable bit. Enables alarm together with AE_M and AE_H<br>(see USE OF THE ALARM INTERRUPT).                             |

| 7               | AE_WD      | 0        | Enabled                                                                                                                               |

|                 |            | 1        | Disabled – Default value                                                                                                              |

| 6               | 0          | 0        | Read only. Always 0.                                                                                                                  |

| 5:0             | Date Alarm | 01 to 31 | Holds the alarm value for the date, coded in BCD format. The Reset value 00 after POR has to be replaced by a valid value (01 to 31). |

# 3.6. PERIODIC COUNTDOWN TIMER CONTROL REGISTERS

#### 0Ah – Timer Value 0

This register is used to set the lower 8 bits of the 12 bit Timer Value (preset value) for the Periodic Countdown Timer. This value will be automatically reloaded into the Countdown Timer when it reaches zero if the TRPT bit is 1. This allows for periodic timer interrupts (see calculation below).

Read: Always readable. Write: Can be write-protected by password.

| Address | Function      | Conv. | Bit 7         | Bit 6                                 | Bit 5                      | Bit 4                                                             | Bit 3       | Bit 2                    | Bit 1     | Bit 0    |

|---------|---------------|-------|---------------|---------------------------------------|----------------------------|-------------------------------------------------------------------|-------------|--------------------------|-----------|----------|

| 046     | Timer Value 0 | R/WP  | 128           | 64                                    | 32                         | 16                                                                | 8           | 4                        | 2         | 1        |

| 0Ah     | Reset         |       | 0             | 0                                     | 0                          | 0                                                                 | 0           | 0                        | 0         | 0        |

| Bit     | Symbol        |       | Value         |                                       |                            |                                                                   | Description | า                        |           |          |

| 7:0     | Timer Value 0 |       | 00h to<br>FFh | 8 bit) (see<br>only the p<br>When the | e USE OF 1<br>preset value | the Periodi<br>THE PERIO<br>is returned<br>countdown<br>RAM byte. | DIC COUN    | TDOWN TI<br>e actual val | MER). Whe | en read, |

#### 0Bh – Timer Value 1

This register is used to set the upper 4 bits of the 12 bit Timer Value (preset value) for the Periodic Countdown Timer. This value will be automatically reloaded into the Countdown Timer when it reaches zero if the TRPT bit is 1. This allows for periodic timer interrupts (see calculation below).

Read: Always readable. Write: Can be write-protected by password.

| Address | Function      | Conv. | Bit 7    | Bit 6                                                                    | Bit 5       | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

|---------|---------------|-------|----------|--------------------------------------------------------------------------|-------------|-------|------------|-------|-------|-------|

| 0Bh     | Timer Value 1 | R/WP  | 0        | 0                                                                        | 0           | 0     | 2048       | 1024  | 512   | 256   |

| UBII    | Reset         |       | 0        | 0                                                                        | 0           | 0     | 0          | 0     | 0     | 0     |

| Bit     | Symbol        |       | Value    |                                                                          |             |       | Descriptio | n     |       |       |

| 7:4     | 0             |       | 0        | Read only                                                                | y. Always 0 |       |            |       |       |       |

| 3:0     | Timer Value 1 |       | 0h to Fh | The Timer Value for the Periodic Countdown Timer in binary format (upper |             |       |            |       |       |       |

Countdown Period in seconds:

Countdown Period =  $\frac{\text{Timer Value}}{\text{Timer Clock Frequency}}$

#### 0Ch – Timer Status 0

This register holds the lower 8 bits of the current 12 bit value of the Periodic Countdown Timer. Read only. Writing to this register has no effect.

| Address | Function       | Conv. | Bit 7         | Bit 6       | Bit 5                      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     |  |  |

|---------|----------------|-------|---------------|-------------|----------------------------|-------|-------|-------|-------|-----------|--|--|

| 0Ch     | Timer Status 0 | R     | 128           | 64          | 32                         | 16    | 8     | 4     | 2     | 1         |  |  |

| UCN     | Reset          |       | 0             | 0           | 0                          | 0     | 0     | 0     | 0     | 0         |  |  |

| Bit     | Symbol         |       | Value         | Description |                            |       |       |       |       |           |  |  |

| 7:0     | Timer Status 0 |       | 00h to<br>FFh |             | ent value of<br>e USE OF T |       |       |       |       | at (lower |  |  |

#### 0Dh – Timer Status 1 shadow

This register holds the upper 4 bits of the current 12 bit value of the Periodic Countdown Timer. Read only. Writing to this register has no effect.

| Address | Function       | Conv. | Bit 7       | Bit 6       | Bit 5                      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     |  |

|---------|----------------|-------|-------------|-------------|----------------------------|-------|-------|-------|-------|-----------|--|

| 0Dh     | Timer Status 1 | R     | 0           | 0           | 0                          | 0     | 2048  | 1024  | 512   | 256       |  |

| UDII    | Reset          |       | 0           | 0           | 0                          | 0     | 0     | 0     | 0     | 0         |  |

| Bit     | Symbol         |       | Value       | Description |                            |       |       |       |       |           |  |

| 7:4     | 0              |       | 0           | Read only   | y. Always 0                |       |       |       |       |           |  |

| 3:0     | Timer Status 1 |       | 0h to<br>Fh |             | ent value of<br>e USE OF T |       |       |       |       | at (upper |  |

When TE bit (0Fh) is set to 1, the Timer Status 0 and Timer Status 1 shadow registers hold the current countdown value. When a 0 is written to the TE bit, the Timer Status 0 and Timer Status 1 registers store the last updated value. Reading the Timer Status 0 value updates the Timer Status 1 shadow register. Reading only the Timer Status 1 shadow register will return the not-updated Timer Status 1 shadow register value, memorized while reading Timer Status 0.

# 3.7. STATUS AND CONTROL REGISTERS

#### 0Eh – Status

This register is used to detect the occurrence of various interrupt events and reliability problems in internal data. Read: Always readable. Write: Can be write-protected by password.

| Address | Function | Conv. | Bit 7                                                                                                                                                                                                                                                                                                                        | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 5                                                      | Bit 4                                                 | Bit 3                                                                | Bit 2                      | Bit 1                          | Bit 0             |  |  |