### **DESCRIPTION**

The devices are full bridge drivers to control power devices like MOS-transistors or IGBTs in 3-phase systems with a maximum blocking voltage of +600 V. The six independent drivers are controlled at the low-side using CMOS and LSTTL compatible signals, down to 3.3V logic. The device includes an under-voltage detection unit with hysteresis characteristic and over-current detection. The over-current level is adjusted by choosing the resistor value and the threshold level at pin ITRIP. Both error conditions (under-voltage and over-current) lead to a definite shut down of all six switches. An error signal is provided at the FAULT open drain output pin. The blocking time after over-current can be adjusted with an RC-network at pin RCIN. Therefore, the resistor RRCIN is optional. The typical output current can be given with 200mA for pull-up and 400mA for pull down. Because of system safety reasons a 0.29us dead time has been realized. The function of inputs EN and ITRIP can optionally be extended with over-temperature detection, using an external NTC resistor, diodes and resistor network.

### **FEATURES**

- Drives up to six IGBT/MOSFET power devices

- All high side channels fully operate up to +600V

- Gate drive supplies up to 18 V per channel

- Under-voltage lockout for all channels

- Over-current protection

- Flexible over-temperature shutdown input

- Advanced input filter

- Built-in dead-time protection

- Shoot-through (cross-conduction) protection

- Independent Enable/disable input and fault reporting

- Shut down all switches during error conditions

- Adjustable fault clear timing

- Separate logic and power grounds

- 3.3 V/5V input logic compatible (positive logic)

- Designed for use with bootstrap power supplies

- Matched propagation delays for all channels

- Matched dead time

- -40°C to 125°C operating range

- SOP28 Package available

- Lead-free

### **APPLICATIONS**

- Appliance motor drives—air conditioners, washing machines, refrigerator, dish washer, Fans

- · Servo drives

- Industrial inverters. General purpose three phase inverters

## **FEATURES COMPARISON**

| Part    | Input Logic | Dead Time | t <sub>ON</sub> | t <sub>OFF</sub> | V <sub>CCUV+</sub> | V <sub>CCUV-</sub> |

|---------|-------------|-----------|-----------------|------------------|--------------------|--------------------|

| PT5616  | LIN/HIN     | 500ns     | 600ns           | 600ns            | 9.5V               | 9V                 |

| PT5616A | LIN/HIN     | 290ns     | 500ns           | 480ns            | 8.9V               | 8.2V               |

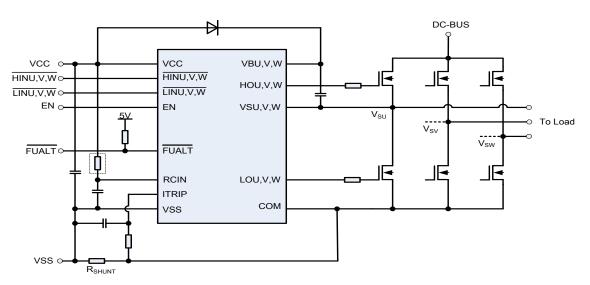

## **TYPICAL APPLICATION**

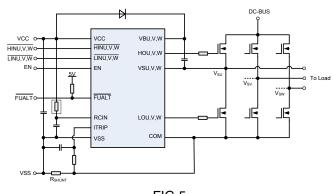

Typical connection of 3-phase HV motor driver

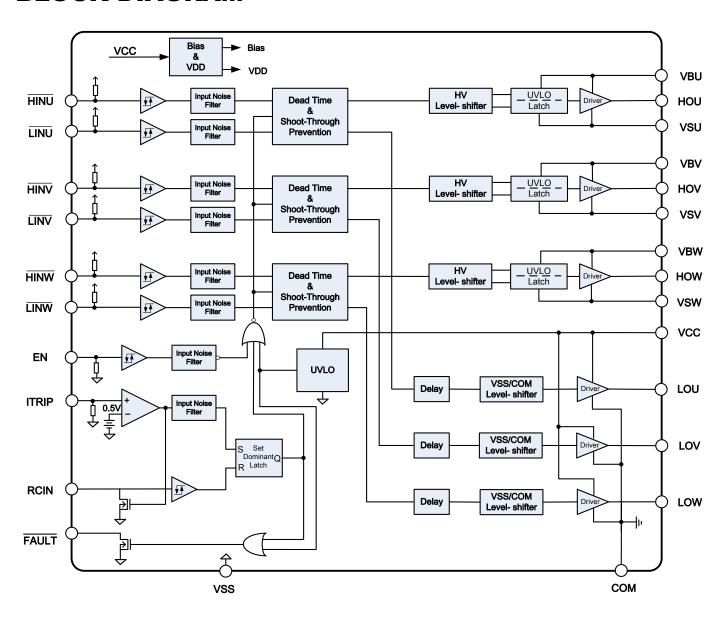

### **BLOCK DIAGRAM**

### **ORDER INFORMATION**

| Valid Part Number | Package Type  | Top Code  |

|-------------------|---------------|-----------|

| PT5616A-S         | SOP28, 300MIL | PT5616A-S |

### **PIN CONFIGURATION**

SOP28

# **PIN DESCRIPTION**

| Pin Name | Description                                                                                                                                                                                                                                                                            | Pin No. |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| VCC      | Logic and low-side gate drivers power supply voltage                                                                                                                                                                                                                                   | 1       |  |  |

| HINU     | Logic inputs for high-side gate driver outputs (phase U); input is out-phase with output                                                                                                                                                                                               |         |  |  |

| HINV     | Logic inputs for high-side gate driver outputs (phase V); input is out -phase with output                                                                                                                                                                                              | 3       |  |  |

| HINW     | Logic inputs for high-side gate driver outputs (phase W); input is out -phase with output                                                                                                                                                                                              | 4       |  |  |

| LINU     | Logic inputs for low-side gate driver outputs (phase U); input is out -phase with output                                                                                                                                                                                               | 5       |  |  |

| LINV     | Logic inputs for low-side gate driver outputs (phase V); input is out -phase with output                                                                                                                                                                                               | 6       |  |  |

| LINW     | Logic inputs for low-side gate driver outputs (phase W); input is out -phase with output                                                                                                                                                                                               | 7       |  |  |

| FAULT    | Indicates over-current, over-temperature (ITRIP), or low-side under-voltage lockout has occurred. This pin has negative logic and an open-drain output. The use of over-current and over-temperature protection requires the use of external components.                               | 8       |  |  |

| ITRIP    | Analog input for over-current shutdown. When active, ITRIP shuts down outputs and activates  FAULT and RCIN low. When ITRIP becomes inactive, FAULT stays active low for an externally set time t <sub>FLTCLR</sub> , then automatically becomes inactive (open-drain high impedance). | 9       |  |  |

| EN       | Logic input to shutdown functionality. Logic functions when EN is high (i.e., positive logic). No effect on FAULT and not latched. EN can also be extended as input of over-temperature protection when equipped with an external NTC resistor.                                        | 10      |  |  |

| RCIN     | An external RC network input used to define the FAULT CLEAR delay (t <sub>FLTCLR</sub> ) approximately equal to R*C. When RCIN > 8 V, the FAULT pin goes back into an open-drain high-impedance state.                                                                                 | 11      |  |  |

| VSS      | Logic ground                                                                                                                                                                                                                                                                           | 12      |  |  |

| СОМ      | Low-side gate drive return                                                                                                                                                                                                                                                             | 13      |  |  |

| LOW      | Low-side gate driver W-phase output                                                                                                                                                                                                                                                    | 14      |  |  |

| LOV      | Low-side gate driver V-phase output                                                                                                                                                                                                                                                    | 15      |  |  |

| LOU      | Low-side gate driver U-phase output                                                                                                                                                                                                                                                    | 16      |  |  |

| NC.      | Not Connected                                                                                                                                                                                                                                                                          | 17      |  |  |

| VSW      | High-side driver W-phase floating supply offset voltage                                                                                                                                                                                                                                | 18      |  |  |

| HOW      | High-side driver W-phase gate driver output                                                                                                                                                                                                                                            | 19      |  |  |

| VBW      | High-side driver W-phase floating supply                                                                                                                                                                                                                                               | 20      |  |  |

| NC.      | Not Connected                                                                                                                                                                                                                                                                          | 21      |  |  |

| VSV      | High-side driver V-phase floating supply offset voltage                                                                                                                                                                                                                                | 22      |  |  |

| HOV      | High-side driver V-phase gate driver output                                                                                                                                                                                                                                            | 23      |  |  |

| VBV      | High-side driver V-phase floating supply                                                                                                                                                                                                                                               | 24      |  |  |

| NC.      | Not Connected                                                                                                                                                                                                                                                                          | 25      |  |  |

| VSU      | High-side driver U-phase floating supply offset voltage                                                                                                                                                                                                                                | 26      |  |  |

| HOU      | High-side driver U-phase gate driver output                                                                                                                                                                                                                                            | 27      |  |  |

| VBU      | High-side driver U-phase floating supply                                                                                                                                                                                                                                               | 28      |  |  |

V1.0 5 August 2014

### **FUNCTION DESCRIPTION**

### LOW SIDE POWER SUPPLY (VCC, VSS, COM)

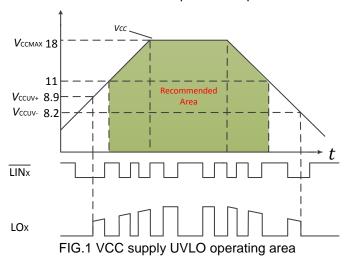

VCC is the low side supply and it provides power both to input logic and to low side output power stage. Input logic is referenced to VSS ground as well as the under-voltage detection circuit. Output power stage is referenced to COM ground. COM ground is floating respect to VSS ground with a recommended range of operation of +/-5V, which guarantees enough margin of gate to source voltage,  $V_{GS}$ , to driver power devices such as power MOSFET. The built-in under-voltage lockout circuit enables the device to operate at sufficient power on when a typical VCC supply voltage higher than  $V_{CCUV+}$ =8.9 is present, shown as FIG1. The IC shuts down all the gate drivers outputs, when the VCC supply voltage is below  $V_{CCUV-}$ =8.2 V, shown as FIG1. This prevents the external power devices from extremely low gate voltage levels during on-state and therefore from excessive power dissipation.

## HIGH SIDE POWER SUPPLY (VBU-VSU, VBV-VSV, VBW-VSW)

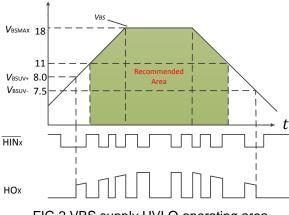

VB to VS is the high side supply voltage. The totally high side circuitry can float with respect to VSS following the external high side power device emitter/source voltage. Due to the internally low power consumption, the whole high side circuitry can be supplied by bootstrap topology connected to VCC, and it can be powered with small bootstrap capacitors. The device operating area as a function of the supply voltage is given in Figure 2.

FIG.2 VBS supply UVLO operating area

## LOW SIDE AND HIGH CONTROL INPUT LOGIC (HINU, V, W, LINU, V, W)

The Schmitt trigger threshold of each input is designed enough low such to guarantee LSTTL and CMOS compatibility down to 3.3 V controller outputs. Input Schmitt trigger and advanced noise filter provide beneficial noise rejection to short input pulses. An internal pull-down resistor of about  $50k\Omega$  (positive logic) pre-biases each input during VCC supply start-up state. It is anyway recommended for proper work of the driver not to provide input pulse-width lower than 800ns.

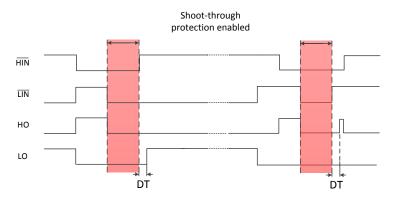

#### SHOOT-THROUGH PREVENTION

The IC is equipped with shoot-through prevention circuitry (also known as cross conduction prevention circuitry). Figure 3 shows how this prevention circuitry prevents both the high- and low-side switches from conducting at the same time. During the inputs controlling high side driver and low side driver are both "low", the both driver outputs are pulled down "low" to shutdown two power devices in the same bridge.

FIG.3 Shoot-through prevention

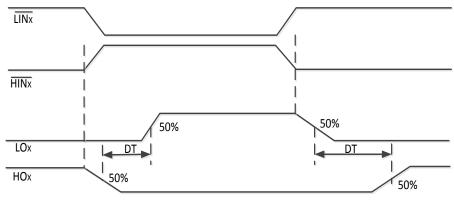

#### **DEAD TIME**

This PT5616A features integrated a fixed dead-time protection circuitry. The dead time feature inserts a time period (a minimum dead time) in which both the high- and low-side power switches are held off; this is done to ensure that the power switch being turned off has fully turned off before the second power switch is turned on. This minimum dead time is automatically inserted whenever the external dead time is shorter than DT; external dead times larger than DT are not modified by the gate driver. Figure 4 illustrates the dead time period and the relationship between the output gate signals.

FIG.4 Dead Time

## **ENABLE INPUT (EN)**

The signal applied to pin EN controls directly the output stages. All outputs are set to LOW, if EN is at "low" logic level. The switching levels of the Schmitt-Trigger are here  $V_{\text{EN, TH+}} = 2.0 \text{ V}$  and  $V_{\text{EN, TH-}} = 1.3 \text{ V}$ . The typical propagation delay time is  $t_{\text{EN}} = 400 \text{ ns}$ . There is an internal pull up resistor of about  $100\text{k}\Omega$ , which keeps the gate driver outputs on in case of EN pin floating and is extended to some special purpose.

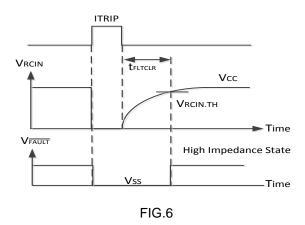

## FAULT INDICATOR (FAULT)

FAULT pin is an active low open-drain output indicating the states of the gate driver (see Figure 6). The pin is active (i.e. forces low voltage level) when one of the following conditions occur:

- Under-voltage condition of VCC supply: In this case the fault condition is released as soon as the supply voltage condition returns in the normal operation range (please refer to VCC pin description for more details).

- > Over-current detection (ITRIP): The fault condition is latched until current trip condition is finished and RCIN input is released (please refer to ITRIP pin).

## **OVER CURRENT PROTECTION (ITRIP)**

The PT5616A are equipped with an ITRIP input pin. This functionality can be used to detect over-current events in the power ground or DC-bus. Once the IC detects an over-current event through the ITRIP pin, the gate driver outputs are

shutdown, a fault is reported through the FAULT pin, and RCIN is pulled down to Vss.

The level of current at which the over-current protection is activated is determined by the shunt resistor, R<sub>SHUNT</sub>, placed between power devices source/emitter and VSS, which is shown in the FIG.5. The circuit designer will need to determine the maximum allowable level of motor current in the power ground or DC- bus through the followed equation:

$$I_{MOTOR} = \frac{V_{IT,TH+}}{R_{SHUNT}}$$

The ITRIP comparator threshold,  $V_{IT, TH+}$  (typical 0.45 V), is referenced to VSS ground. An internal blank time (typ.  $t_{BL}$  = 250 ns) prevents the IC to detect false over-current events.

RCIN input/output pin is used to determine the reset time of the fault condition. As soon as ITRIP threshold is exceeded the external capacitor connected to RCIN is fully discharged. The capacitor is then recharged by the internal RCIN current generator when the over-current condition is finished. As soon as RCIN voltage exceeds the rising threshold of typical  $V_{RCIN,TH} = 8 \text{ V}$ , the fault condition releases and the driver returns operational following the control input pins. The

relationship of FAULT, ITRIP and RCIN is given in the FIG.6.

FIG.5

## GATE DRIVER (HOU, V, W, LOU, V, W)

Low side and high side driver outputs are specifically designed for pulse operation and dedicated to drive the power devices such as IGBT and MOSFET. Low side outputs (i.e. LOU, V, W) are state triggered by the respective inputs, while high side outputs (i.e. HOU, V, W) are only changed at the edge of the respective inputs. In particular, after releasing from an under voltage condition of the VBS supply, a new turn-on signal (edge) is necessary to activate the respective high side output, while after releasing from a under voltage condition of the VCC supply, the low side outputs can directly switch to the state of their respective inputs and don't suffer from the trouble as high side driver.

#### SEPARATE LOGIC AND POWER GROUNDS

The PT5616A has separate logic and power ground pin (Vss and COM respectively) to eliminate some of the noise problems that can occur in power conversion applications. Current sensing shunt resistors are commonly used in many applications for power inverter protection (i.e., over-current protection), and in the case of motor drive applications, for motor current measurements. In these situations, it is often beneficial to separate the logic and power grounds. Figure 5 also shows an IC with separate  $V_{SS}$  and COM pins and how these two grounds are used in the system. The Vss is used as the reference point for the logic and over-current circuitry. Alternatively, the COM pin is the reference point for the low-side gate drive circuitry. The driver output voltage used to drive the low-side gate is  $V_{LO}$ -COM.

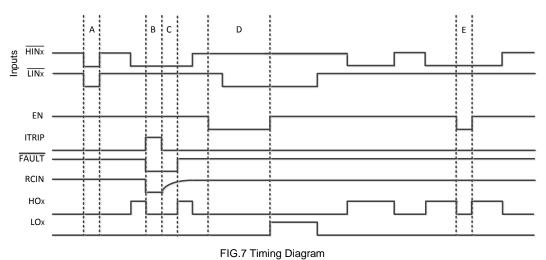

## TIMING DIAGRAM, FIG.7

V1.0 9 August 2014

### **ABSOLUTE MAXIMUM RATINGS**

Stresses exceeding the absolute maximum ratings may damage the device or make the function abnormal. All the voltage parameters are absolute voltages referenced to VSS unless otherwise stated in the table.

| Parameter                                         | Symbol               | Min.                      | Max.                      | Units |

|---------------------------------------------------|----------------------|---------------------------|---------------------------|-------|

| High-side floating supply voltage                 | $V_{B.U.V.W}$        | -0.3                      | 600                       |       |

| High-side offset voltage                          | V <sub>s-U.V.W</sub> | V <sub>B.U.V.W</sub> -20  | V <sub>B.U.V.W</sub> +0.3 |       |

| High-side gate driver output voltage              | $V_{HO.U.V.W}$       | V <sub>S.U.V.W</sub> -0.3 | V <sub>S.U.V.W</sub> +0.3 |       |

| Low-side gate driver output voltage               | $V_{LO.U.V.W}$       | COM-0.3                   | V <sub>CC</sub> +0.3      |       |

| Logic input voltage(HINX, LINX,, ITRIP, EN)       | VHINU,V,W            | -0.3                      | 20                        | V     |

| Low-side supply voltage                           | V <sub>cc</sub>      | -0.3                      | 20                        |       |

| Logic gate driver return                          | COM                  | V <sub>CC</sub> -20       | V <sub>CC</sub> +0.3      |       |

| FAULToutput voltage                               | $V_{FLT}$            | -0.3                      | VCC+0.3                   | V     |

| RCIN input voltage                                | $V_{RCIN}$           | -0.3                      | VCC+0.3                   | V     |

| High-side input pulse width                       | PW⊞                  | 600                       | -                         | ns    |

| Allowable Offset Voltage Slew Rate                | DV/DT                | -                         | 50                        | V/ns  |

| Package power dissipation @ T <sub>A</sub> ≤+25°C | PD                   | -                         | 1.6                       | W     |

| Thermal resistance, junction to ambient, SOP28L-W | Rth <sub>JA</sub>    |                           | 78                        | °C/W  |

| Junction temperature                              | TJ                   | -50                       | +150                      |       |

| Storage temperature                               | Ts                   | -40                       | +150                      | °C    |

| Lead temperature (soldering, 10 seconds)          | TL                   | -                         | 300                       |       |

## RECOMMENDED OPERATING CONDITIONS

| Parameter                                       | Symbol         | Min.               | Тур. | Max.               | Units |  |

|-------------------------------------------------|----------------|--------------------|------|--------------------|-------|--|

| Low-side supply voltage                         | $V_{CC}$       | 11                 | 15   | 18                 |       |  |

| High-side Floating Supply Offset Voltage(note1) | $V_{S.U.V.W}$  | V <sub>B</sub> -18 | -    | V <sub>B</sub> -11 |       |  |

| High-side Floating Supply Voltage               | $V_{B.U.V.W}$  | -10                | -    | 600                |       |  |

| High-side gate driver output voltage            | $V_{HO.U.V.W}$ | Vs                 | -    | $V_{B}$            |       |  |

| Low-side gate driver output voltage             | $V_{LO.U.V.W}$ | COM                | -    | $V_{CC}$           | V     |  |

| Logic gate driver return                        | COM            | -3                 |      | 3                  | ]     |  |

| Logic input voltage                             | VHINU,V,W      | 0                  | -    | 5                  |       |  |

| EN input voltage                                | $V_{EN}$       | 0                  | -    | $V_{CC}$           | V     |  |

| FAULT output voltage                            | $V_{FLT}$      | 0                  | -    | V <sub>CC</sub>    | V     |  |

| RCIN input voltage                              | VRCIN          | 0                  | -    | V <sub>cc</sub>    | V     |  |

| ITRIP input voltage                             | Vitrip         | 0                  | -    | V <sub>CC</sub>    | V     |  |

| IC operating junction temperature               | T <sub>J</sub> | -40                | -    | +125               | °C    |  |

Note1: For VBS=15V, normal Logic operation for VS of -10 V to 600 V. The parameter is only guaranteed by design.

## STATIC ELECTRICAL CHARACTERISTICS

(VCC-VSS) =(VB-VS)=15V. TAMB=25℃ unless otherwise specified .the VIN, VTH and IIN Parameters are reference to VSS and are applicable to all six channels. The Vo and Io parameters are referenced to respective VS and COM and are applicable to the respective output leads. The Vccuv parameters are referenced to VSS. The Vbsuv parameters are referenced to Vs.

| Parameter                                                                                          | Symbol                 | Test Conditions                                          | Min.    | Тур. | Max.   | Unit  |  |  |

|----------------------------------------------------------------------------------------------------|------------------------|----------------------------------------------------------|---------|------|--------|-------|--|--|

| Low Side Power Supply Characteristics                                                              | Syllibol               | rest conditions                                          | IVIIII. | ιyp. | IVIAX. | Offic |  |  |

| Low Side Fower Supply Characteristics                                                              | 1                      |                                                          |         |      |        |       |  |  |

| VCC quiescent current                                                                              | I <sub>QVCC</sub>      | VHINU,V,W =0 or 5V                                       | _       | 1    | 1.5    | mA    |  |  |

| voo quiescent current                                                                              | ·QVCC                  | VL <del>INU,V,W</del> =0 or 5V                           |         | '    | 1.5    | 1117  |  |  |

| VCC supply under-voltage positive going threshold                                                  | V <sub>CCUV+</sub>     | V2(0,1,11 =0 01 01                                       | 7.9     | 8.9  | 10     |       |  |  |

| VCC supply under-voltage negative going threshold                                                  | V <sub>CCUV</sub> -    |                                                          | 7.2     | 8.2  | 9.2    | V     |  |  |

| V <sub>CC</sub> supply under-voltage lockout hysteresis                                            | V <sub>CCHYS</sub>     |                                                          | -       | 0.7  | -      |       |  |  |

| High Side Floating Power Supply Characteristics                                                    | 1 001113               |                                                          |         | 0    |        |       |  |  |

| High side VBS supply under-voltage positive going threshold                                        | V <sub>BSUV+</sub>     |                                                          | 6.0     | 8.0  | 10.0   |       |  |  |

| High side VBS supply under-voltage negative going threshold                                        | V <sub>BSUV</sub> -    |                                                          | 5.5     | 7.5  | 9.5    | V     |  |  |

| High side VBS supply under-voltage lockout hysteresis                                              | V <sub>BSUVHYS</sub>   |                                                          | -       | 0.5  | -      |       |  |  |

| High side VBS quiescent current                                                                    | I <sub>QBS</sub>       | V <sub>BS</sub> =15V                                     | 45      | 65   | 85     |       |  |  |

| Offset supply leakage current                                                                      | I <sub>LK</sub>        | V <sub>B</sub> =V <sub>S</sub> =600V V <sub>CC</sub> =0V | -       | -    | 1      | μA    |  |  |

| Gate Driver Output Section                                                                         | ILK                    | VB- V3-000 V VCC-0 V                                     |         |      | '      |       |  |  |

| ·                                                                                                  |                        | $V_{HO}=V_{S}=0$ ,                                       |         |      |        |       |  |  |

| Output High Short-Circuit Pulse Current                                                            | I <sub>O+</sub>        | $V_{HO} = V_{B} = 15V$                                   | -       | 200  | -      |       |  |  |

|                                                                                                    |                        | $V_{LO}$ =COM=0,                                         |         |      |        | mA    |  |  |

| Output Low Short-Circuit Pulse Current                                                             | I <sub>O-</sub>        | $V_{LO}=V_{CC}=15V$                                      | -       | 400  | -      |       |  |  |

| High level output voltage drop, V <sub>CC</sub> -V <sub>LO</sub> ,V <sub>BS</sub> -V <sub>HO</sub> | V <sub>OH</sub>        | IO+= 20 mA                                               | -       | 0.8  | 1.5    | V     |  |  |

| Low level output voltage drop                                                                      | V <sub>OL</sub>        | IO-= 20 mA                                               | -       | 0.3  | 0.5    | V     |  |  |

| All 11 N c                                                                                         |                        |                                                          |         |      |        |       |  |  |

| Allowable Negative VS Pin Voltage for HINU,V,W Signal                                              | V <sub>SN</sub>        | Fixed V <sub>BS</sub> =15V                               | -       | -10  | -      | V     |  |  |

| · -                                                                                                | Propagation to HOU.V.W |                                                          |         |      |        |       |  |  |

| Logic Input Section                                                                                | l                      |                                                          |         |      |        |       |  |  |

| Logic"1" Input voltage HINU,V,W and LINU,V,W                                                       | V <sub>IH</sub>        |                                                          | 2.5     | -    | -      |       |  |  |

| Logic"0" Input voltage HINU,V,W and LINU,V,W                                                       | V <sub>IL</sub>        |                                                          | -       | -    | 0.8    | V     |  |  |

| Input positive going threshold                                                                     | V <sub>IN,TH+</sub>    |                                                          | -       | 2.0  | -      | ľ     |  |  |

| Input negative going threshold                                                                     | V <sub>IN,TH</sub> -   |                                                          | -       | 1.3  | -      |       |  |  |

| Logic "1" Input bias current                                                                       | I <sub>IN+</sub>       | V <sub>IN</sub> =5V                                      | _       | 0    | -      |       |  |  |

| Logic "0" Input bias current                                                                       | I <sub>IN-</sub>       | V <sub>IN</sub> =0                                       | _       | 100  | 150    | uA    |  |  |

| Shut down and protection Section                                                                   | -114-                  | T IIV C                                                  |         |      |        |       |  |  |

| RCIN positive going threshold                                                                      | V <sub>RCIN,TH</sub>   |                                                          | _       | 8    | _      | V     |  |  |

| RCIN hysteresis                                                                                    | V <sub>RCIN,HY</sub>   |                                                          | -       | 3    | -      | V     |  |  |

| RCIN internal charge current                                                                       | I <sub>RCIN</sub>      | V <sub>RCIN</sub> =3V                                    | -       | 2    | -      | uA    |  |  |

| RCIN low on resistance of pull down MOSFET                                                         | R <sub>ON,RCIN</sub>   | I <sub>SINK</sub> =2mA                                   | -       | 40   | 80     | Ω     |  |  |

| ITRIP positive going threshold                                                                     | V <sub>IT,TH+</sub>    | OHII                                                     | 0.3     | 0.45 | 0.6    | V     |  |  |

| ITRIP hysteresis                                                                                   | V <sub>IT,HYS</sub>    |                                                          | 40      | 70   | -      | mV    |  |  |

| "High" ITRIP input bias current                                                                    | I <sub>ITRIP+</sub>    | V <sub>IT</sub> =5V                                      | -       | 50   | 80     | uA    |  |  |

| "Low" ITRIP input bias current                                                                     | I <sub>ITRIP-</sub>    | V <sub>IT</sub> =0V                                      | -       | 0    | 1      | uA    |  |  |

| Enable positive going threshold                                                                    | V <sub>EN,TH+</sub>    |                                                          | -       | 2.0  | 2.5    | V     |  |  |

| Enable negative going threshold                                                                    | V <sub>EN,TH</sub> -   |                                                          | 0.8     | 1.3  | -      | V     |  |  |

| "High" enable input bias current                                                                   | I <sub>EN+</sub>       | V <sub>EN</sub> =5V                                      | -       | 100  | -      | uA    |  |  |

| "Low" enable input bias current                                                                    | I <sub>EN-</sub>       | V <sub>EN</sub> =0V                                      | -       | 0    | -      | uA    |  |  |

| FAULT low on resistance                                                                            | R <sub>ON,FLT</sub>    | I <sub>SINK</sub> =2mA                                   | _       | 40   | 80     | Ω     |  |  |

| I AOLI IOW OII TESISTATIOE                                                                         | · ·ON,FLI              | OHNO-ZIIII                                               |         |      |        |       |  |  |

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

$(\text{VCC-VSS}) = (\text{VB-VS}) = 15 \text{V }, \text{V}_{\text{SU,V,W}} = \text{VSS} = \text{COM}, \text{ and } \text{C}_{\text{HO}} = \text{C}_{\text{LO}} = 1 \text{nF unless otherwise specified, TAMB} = 25 \,^{\circ}\text{C} \,.$

| Parameter                                                             | Symbol                 | Test Conditions                                                                                                                  | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VCC operating Vcc supply current                                      | I <sub>VCCOP</sub>     | f пии, v, w = 20k,<br>f нии, v, w = 20k,                                                                                         | -    | 4    | 6    | mA   |

| Turn-On propagation delay                                             | t <sub>ON</sub>        | VHINU,V,W or VLINU,V,W =0V, V <sub>S.U.V.W</sub> =5V                                                                             | 250  | 500  | 750  |      |

| Turn-Off Propagation delay                                            | t <sub>OFF</sub>       | VHINU,V,W OR VINU,V,W =5V, V <sub>S.U.V.W</sub> =5V                                                                              | 240  | 480  | 720  |      |

| Turn-On Rise time                                                     | t <sub>R</sub>         | $V_{\text{HINU,V,W}}$ or $V_{\text{LINU,V,W}}$<br>=0V, $V_{\text{S.U.V.W}}$ =5V                                                  | -    | 120  | -    |      |

| Turn-Off Fall time                                                    | t <sub>F</sub>         | VHINU,V,W or VLINU,V,W =5V, V <sub>S.U.V.W</sub> =5V                                                                             | -    | 50   | -    |      |

| Input Filtering Time                                                  | t <sub>FIL,IN</sub>    |                                                                                                                                  | 150  | 250  | 350  | ns   |

| Dead Time                                                             | DT                     | HIN and LIN inputs<br>without external dead<br>time                                                                              | 300  | 500  | 700  | 110  |

| Dead-Time Matching(All Six Channels)                                  | MDT                    | HIN and LIN inputs<br>without external dead<br>time                                                                              | -    | ı    | 80   |      |

| Delay Matching(t <sub>ON</sub> , t <sub>OFF</sub> , All Six Channels) | MT                     | HIN and LIN inputs with external dead time >2us                                                                                  | -    | -    | 80   |      |

| Output Pulse-Width Matching                                           | PM                     | PW <sub>IN</sub> =5us,<br>PM=PW <sub>OUT</sub> -PW <sub>IN</sub>                                                                 | -    | -    | 80   |      |

| Enable low to output shutdown propagation delay                       | t <sub>EN</sub>        | $V_{\text{HINU,V,W}}$ or $V_{\text{LINU,V,W}}$<br>=0V, $V_{\text{EN}}$ = 0 V, $V_{\text{HOU,V,W}}$<br>or $V_{\text{LOU,V,W}}$ =0 | 200  | 400  | 600  | ns   |

| Enable input filter time                                              | t <sub>FILTER,EN</sub> |                                                                                                                                  | 100  | 200  |      | ns   |

| FAULT clear time                                                      | <b>t</b> FLTCLR        | RCIN: R = 2 M $\Omega$ ,<br>C = 1 nF                                                                                             | 1.2  | 1.6  | 2.0  | ms   |

| ITRIP to output shutdown propagation delay                            | t <sub>ITRIP</sub>     | $V_{\text{HINU,V,W}}$ or $V_{\text{LINU,V,W}}$<br>=5V, $V_{\text{HOU,V,W}}$ or $V_{\text{LOU,V,W}}$ =0, $V_{\text{IT}}$ =5 V     | 500  | 700  | 900  | ns   |

| ITRIP blanking time                                                   | t <sub>BL</sub>        | V <sub>IT</sub> = 5 V, V <sub>FAULT</sub> "Low"                                                                                  |      | 120  |      | ns   |

| ITRIP to FAULT propagation delay                                      | t <sub>FLT</sub>       | V <sub>IT</sub> = 5 V, V <sub>FLT</sub> "Low"                                                                                    | 250  | 450  | 650  | ns   |

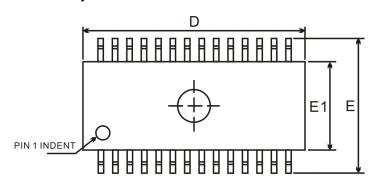

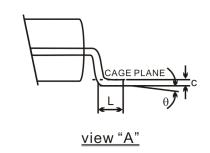

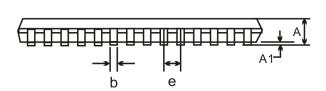

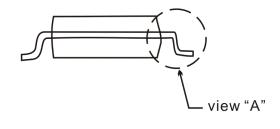

## **PACKAGE INFORMATION**

# 28-PIN, SOP 300MIL

| Symbol | Min.        | Max.      |      |  |  |

|--------|-------------|-----------|------|--|--|

| Α      | -           | -         | 2.65 |  |  |

| A1     | 0.10        | -         | 0.30 |  |  |

| b      | 0.31        | - 0.51    |      |  |  |

| С      | 0.20 - 0.33 |           |      |  |  |

| е      |             | 1.27 BSC. |      |  |  |

| D      | 17.90 BSC.  |           |      |  |  |

| E      | 10.30 BSC.  |           |      |  |  |

| E1     | 7.50 BSC.   |           |      |  |  |

| L      | 0.38 - 1.27 |           |      |  |  |

| θ      | 0° - 8°     |           |      |  |  |

#### Notes:

- All controlling dimensions are in millimeter.

Refer to JEDEC MS-013 AD.

#### **IMPORTANT NOTICE**

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian Dist., New Taipei City 23145, Taiwan

Tel: 886-2-66296288 Fax: 886-2-29174598

http://www.princeton.com.tw

V1.0 14 August 2014

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Display Drivers & Controllers category:

Click to view products by Princeton manufacturer:

Other Similar products are found below:

ICB2FL01G

LC74761M-9006-E

MP3360DG-LF-P

HV5812PJ-G-M904

TW8813-LB2-GR

TW8819AT-NA2-GR

TW8811-PC2-GR

MAX1839EEP+

TW9907-TA1-GR

S1D13503F00A200

MAX7370ETG+T

LX27901IDW

STVM100DC6F

DS3994Z+T&R

S1D13515F00A100

LX1686EIPW

AM26C32IDR

MAX7370ETG+

LX1688IPW

MAX1739EEP+

MAX17126BETM+

MAX14515AEWA+T

DS3992Z-18P

BTM7710GXUMA1

DS3881E+C

S1D13742F01A200

LX1688CPW

MAX17126AETM+

MAX8729EEI+

MAX7370ETG

TIOS1013DMWR

TLD5097EL

HV857LK7-G

TLD5097ELXUMA1

AAT2823IBK-1-T1

DLPA1000YFFT

ICB2FL01GXUMA2

DLP2000FQC

SC401U

IR2117PBF

PAD1000YFFR

S1D13746F01A600

S1D13748B00B100

FIN324CMLX

STVM100DS6F

HV850MG-G

AD8138ARZ-R7

AD8387JSVZ

ADDI9023BBCZ

ADM3202ARUZ-REEL7