### **75**Ω **47–2000 MHz Digital Step Attenuator**

### **Product Overview**

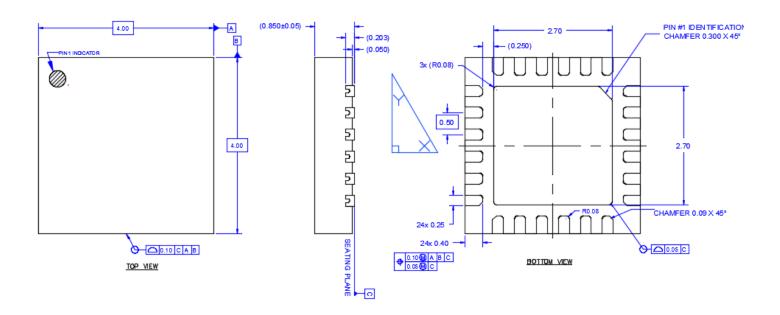

The QPC3624 is a  $75\Omega$  6-bit digital step attenuator (DSA) that features high linearity over the entire 31.5 dB gain control range in 0.5 dB steps and has a low insertion loss of 1.2 dB at 1 GHz. The QPC3624 features three modes of control: serial, latched parallel, and direct parallel programming. Patented circuit architecture provides overshoot-free transient switching performance. The QPC3624 is available in a 24-pad 4mm x 4mm x 0.90 mm QFN package.

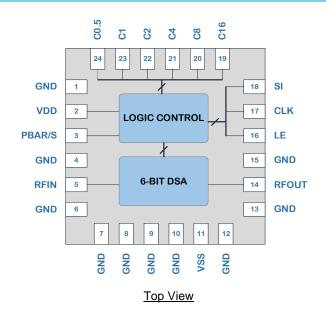

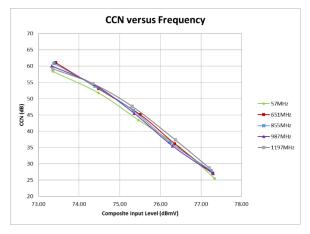

## **Functional Block Diagram**

24 Pad 4 x 4 mm QFN Package

### **Key Features**

- 6-Bit, 31.5 dB Range, 0.5 dB Step

- Patented Circuit Architecture

- Overshoot-free Transient Switching Performance

- Frequency Range 47 MHz to 2000 MHz

- High Linearity, IIP3 55dBm Typical

- Serial and Parallel Control Interface

- Fast Switching Speed, <250 nsec Typical

- RF Pads Have No DC Voltage, Can be DC Grounded Externally

- Option to Turn Off Negative Voltage Generator and Supply Vss Externally

- Power-up Default Setting Is Maximum Attenuation

## **Applications**

- Optical Nodes

- Point-to-Point

- MDU Amplifiers

- Pre-amplifier Attenuation

- Inter-stage Attenuation

- Return Attenuation

- AGC

## **Ordering Information**

| Part No.    | Description                              |

|-------------|------------------------------------------|

| QPC3624SQ   | Sample bag with 25 pieces                |

| QPC3624SR   | 7" Reel with 100 pieces                  |

| QPC3624TR13 | 13" Reel with 2500 pieces                |

| QPC3624PCK  | 47 – 2000 MHz PCBA with 5 pc. sample bag |

## **Absolute Maximum Ratings**

| Parameter                                                                                         | Rating          |

|---------------------------------------------------------------------------------------------------|-----------------|

| Supply Voltage (V <sub>DD</sub> )                                                                 | -0.5 to +6.0 V  |

| Supply Voltage (V <sub>SS</sub> )                                                                 | -6.0 to + 0.5 V |

| All Other DC and Logic Pads (Supply<br>Voltage Must Be Applied Prior to Any<br>Other Pin Voltage) | -0.5 to VDD     |

| Maximum Input Power at RFIN Pad at 85 °C Case Temperature                                         | +30 dBm         |

| Maximum Input Power at RFOUT Pad at 85 °C Case Temperature                                        | +27 dBm         |

| Storage Temperature Range                                                                         | −65 to +150 °C  |

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability.

## **Recommended Operating Conditions**

| Parameter                       | Min  | Тур  | Max  | Units |

|---------------------------------|------|------|------|-------|

| Supply Voltage, V <sub>DD</sub> | +2.7 | +5.0 | +5.5 | V     |

| Supply Voltage, V <sub>SS</sub> | -5.5 | -5.0 | -4.5 | V     |

| Temperature Range               | -40  |      | +85  | °C    |

| Junction Temperature            |      |      | +125 | °C    |

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

## **Electrical Specifications**

| Parameter                   | Condition (1)                                                                        | Min  | Тур         | Max  | Unit |

|-----------------------------|--------------------------------------------------------------------------------------|------|-------------|------|------|

| Supply Current (IDD)        | Steady state operation, current draw during attenuation state transitions is higher. |      | 190         |      | μΑ   |

| Supply Current (Iss)        | Steady state operation, current draw during attenuation state transitions is higher. |      | 105         |      | μA   |

| Frequency Range             |                                                                                      | 47   |             | 2000 | MHz  |

| Insertion Loss              | 1GHz                                                                                 |      | 1.2         |      |      |

| Maximum Attenuation         |                                                                                      |      | 31.5        |      | dB   |

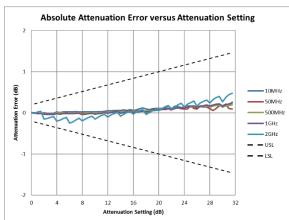

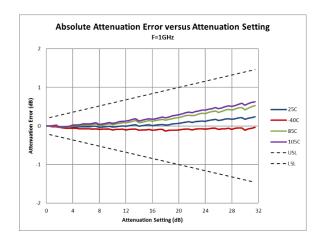

| Absolute Attenuation Error  |                                                                                      |      | ±(0.2 + 4%) |      | dB   |

| Input IP3                   | 47MHz, Two tones, 13dBm/tone                                                         |      | 55          |      | dBm  |

| Input P0.1dB <sup>(2)</sup> |                                                                                      |      | >30         |      | dBm  |

| CSO                         | 130 Channel, Flat Tilt, +42 dBmV/ch, 0dB Atten                                       |      | -80         |      | dBc  |

| СТВ                         | 130 Channel, Flat Tilt, +42 dBmV/ch, 0dB Atten                                       |      | <-90        |      | dBc  |

| Return Loss                 | 1GHz                                                                                 |      | 20          |      | dB   |

| Input and Output Impedance  |                                                                                      |      | 75          |      | Ω    |

| Switching Speed             | 50% control to 10% / 90% RF                                                          |      | 230         |      | nsec |

| Digital Logic Low           |                                                                                      |      |             | 0.63 | V    |

| Digital Logic High          |                                                                                      | 1.17 |             |      | V    |

| Thermal Resistance, θjc     | Junction to case                                                                     |      | 56          |      | °C/W |

#### Notes

- 1. Typical performance at these conditions: Temp = +25°C, 1000MHz,  $V_{DD} = +5V$ ,  $V_{SS} = -5V$ ,  $75\Omega$  system.

- 2. Figure of merit exceeds maximum input power of device.

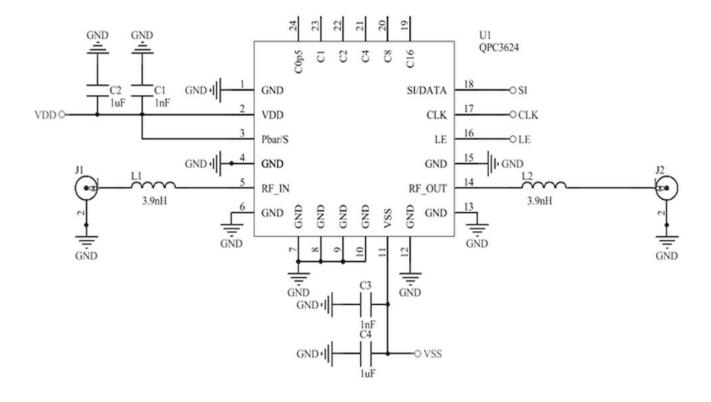

# Typical Application Schematic - Serial Mode 47-1200 MHz

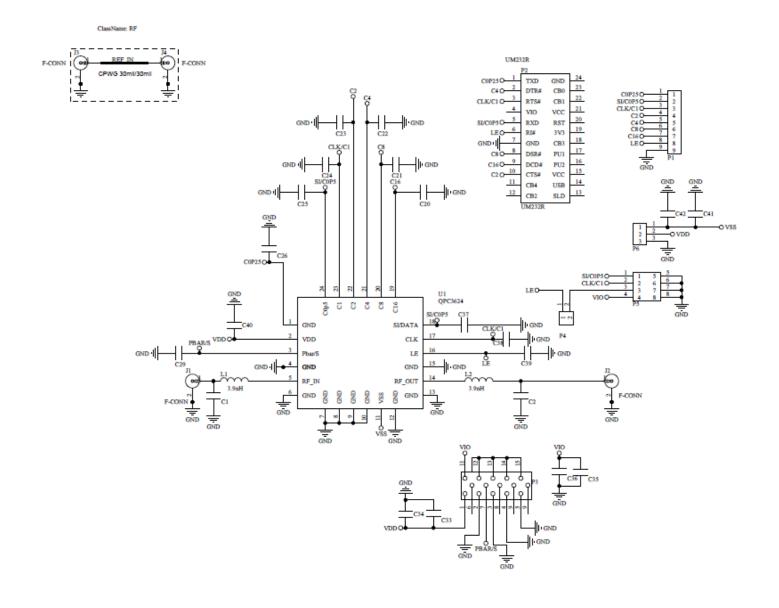

## **Evaluation Board Schematic 47-2000 MHz**

| Ref. Designator    | Description                                 | Manufacturer                    | Part Number        |

|--------------------|---------------------------------------------|---------------------------------|--------------------|

| PCB                | QPC3624-4000                                | Viasystems                      | QPC3624-4000(A)    |

| U1                 | Digital Step Attenuator, 47 MHz to 2000 MHz | Qorvo                           | QPC3624SB          |

| C34, C42           | CAP, 1 μF, 10%, 25 V, X7R, 1206             | Taiyo Yuden (USA), Inc.         | CE TMK316BJ105KL-T |

| J1-J4              | CONN, F FEM, EDGE MOUNT, 75 Ω, 0.065"       | Genesis Technology USA          | GT20-300204        |

| P1                 | CONN, HDR, ST, 9-PIN, 0.100"                | Samtec Inc.                     | TSW-109-07-G-S     |

| P3                 | CONN, HDR, ST, 3 x 5, 0.100", T/H           | Samtec Inc.                     | TSW-105-07-L-T     |

| P4                 | CONN, HDR, ST, 2-PIN, 0.100"                | Samtec Inc.                     | TSW-102-07-G-S     |

| P5                 | CONN, HDR, 2 x 4, RA, 0.100", T/H           | Samtec Inc.                     | TSW-104-08-G-D-RA  |

| P2                 | CONN, SKT, 24-PIN DIP, 0.600", T/H          | Aries Electronics Inc.          | 24-6518-10         |

| P6                 | CONN. HDR, SRT, PLRZD, 3-PIN, 0.100"        | ITW Pancon                      | MPSS100-3-C        |

| M1 (See Note 1)    | MOD, USB TO SERIAL UART, SSOP-28            | Future Technology Devices Int'l | UM232R             |

| S1, S2             | JMPR, 2-PIN                                 | 3M Interconnect Solutions       | 929950-00          |

| C40, C41           | CAP, 1 nF, 5%, 50 V, C0G, 0402              | Murata Electronics              | GRM1555C1H102JA01D |

| L1, L2             | IND, 3.9 nH, FILM, 0402, +/- 0.1 nH         | Murata Electronics              | LQP15MN3N9B02      |

| C1, C2, C5-C13, S6 | DNP                                         | N/A                             | N/A                |

#### Notes:

- 1. M1 should be mounted into P2 with respect to the Pin 1 alignment of M1 and P2.

- 2. Jumpers S1 and S2 should be installed on P3. Jumper S6 is DNP.

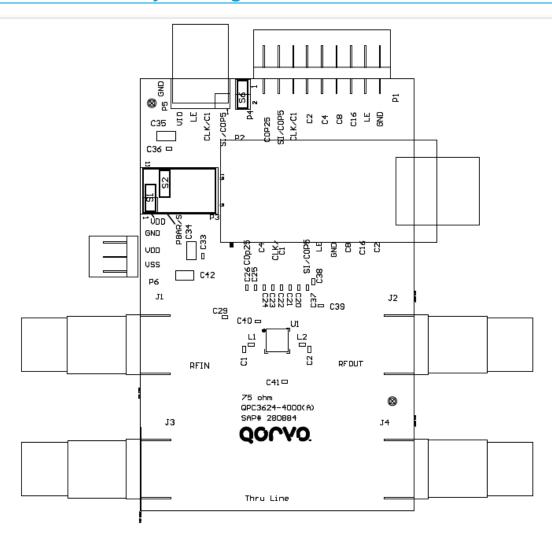

## **Evaluation Board Assembly Drawing**

## **On Board Jumpers**

| Jumpers    | Connector | Signal  | Position  | U1 Connection    | Comment                               |

|------------|-----------|---------|-----------|------------------|---------------------------------------|

| S1         |           | Logic   | 0         | VDD (From P6)    |                                       |

| <u> </u>   | P3        | Voltage | 1         | VIO (From P5)    |                                       |

| S2         | FS        | PBar/S  | 0         | GND              | Parallel Mode                         |

| 52         |           | Pbai/S  | 1         | U1_VDD           | Serial Mode                           |

| <b>S</b> 6 | D4        | 1.5     | OPEN      | LE (from UM232R) | Only install for external SPI control |

| S6         | P4 LE     |         | INSTALLED | LE (from P5.3)   | through P5                            |

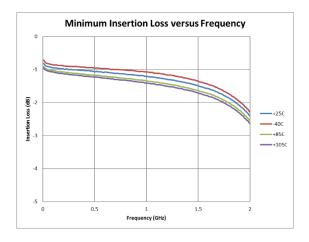

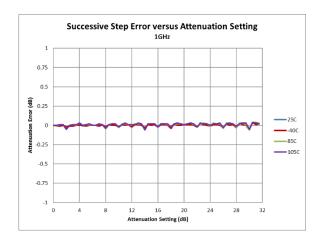

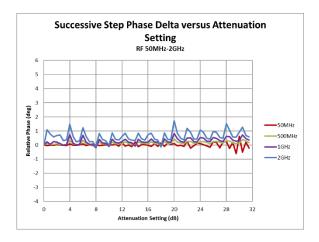

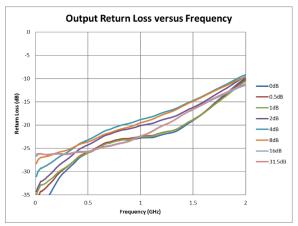

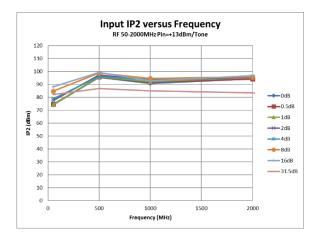

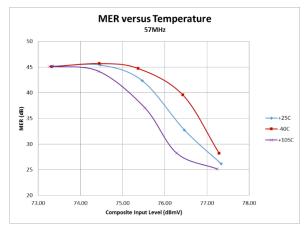

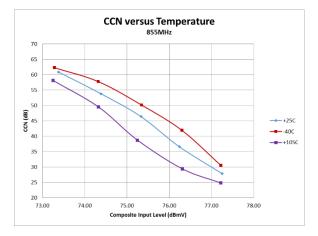

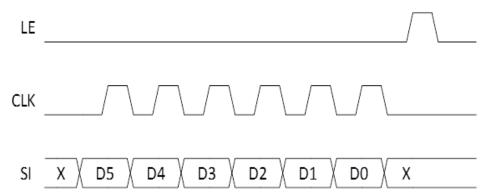

### **Performance Plots**

Test conditions unless otherwise noted:  $V_{DD}$  =+5 V,  $V_{SS}$  = -5 V,  $T_{SS}$  = -5 V,  $T_{CD}$  = +25 °C,  $T_{CD}$  = 75  $T_{CD}$

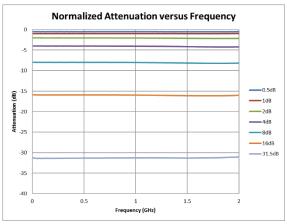

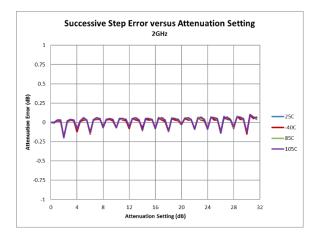

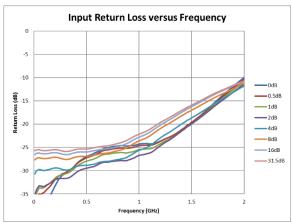

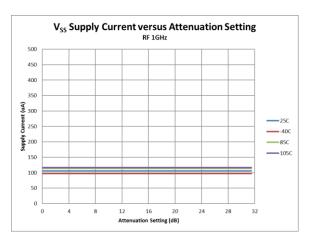

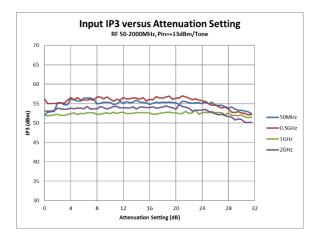

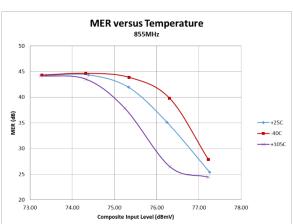

## **Performance Plots (cont'd.)**

Test conditions unless otherwise noted:  $V_{DD}$  =+5 V,  $V_{SS}$ = -5V Temp= +25 °C,  $Z_o$  = 75 $\Omega$

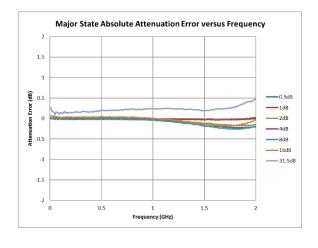

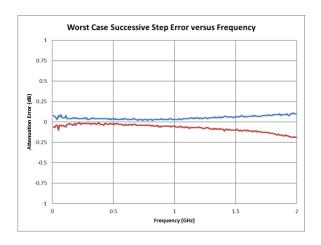

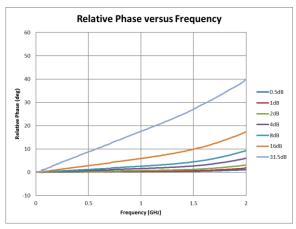

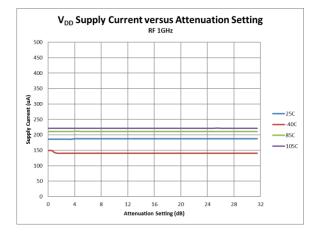

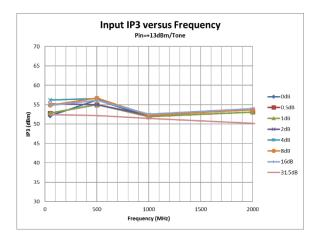

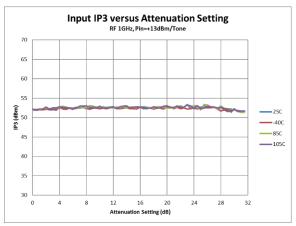

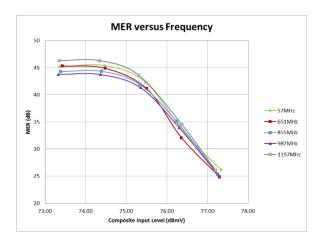

### Performance Plots (cont'd.)

Test conditions unless otherwise noted:  $V_{DD}$  =+5 V,  $V_{SS}$ = -5V Temp= +25 °C,  $Z_0$  = 75 $\Omega$

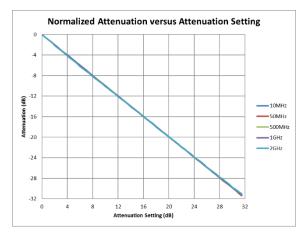

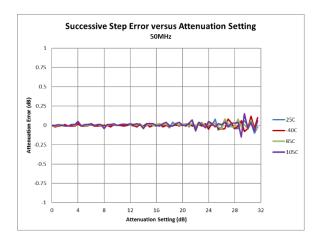

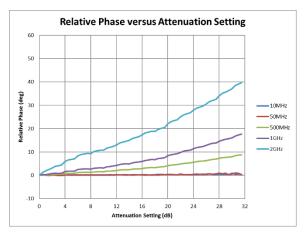

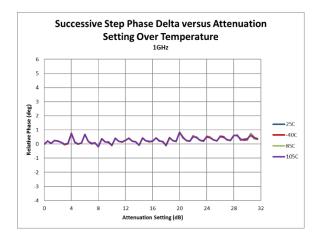

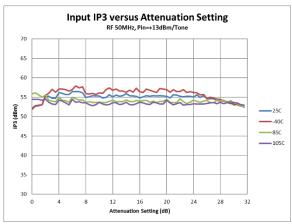

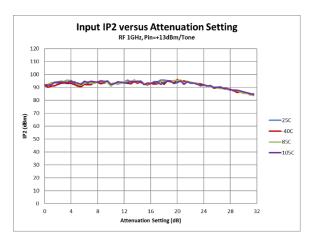

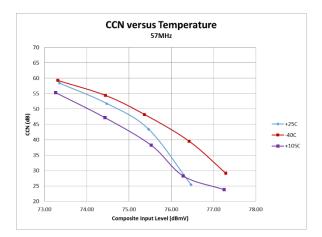

## **Performance Plots (cont'd.)**

Test conditions unless otherwise noted:  $V_{DD}$  =+5 V,  $V_{SS}$ = -5V Temp= +25 °C,  $Z_0$  = 75 $\Omega$

## **Performance Plots (cont'd.)**

Test conditions unless otherwise noted:  $V_{DD}$  =+5 V,  $V_{SS}$ = -5V Temp= +25 °C,  $Z_o$  = 75 $\Omega$

#### MER/CCN Test Conditions:

- 1. 190 QAM256 Channels, 57-1215MHz, ITU-T J.83, Annex B

- 2. CCN test procedure according to ANSI/SCTE 17. System BW 5.36MHz.

- 3. OdB Attenuation Setting

### **Evaluation Board Programming Using USB Interface**

#### **Serial Mode**

All programming jumpers on the evaluation board are set to the default values indicated in the table. Refer to the Control Bit Generator (CBG) Software Reference Manual for instructions on how to setup the software for use. Apply supply voltage to P6. Select 'QPC3624' for serial operation from the parts list of the CBG user interface. Set the attenuation value using the CBG user interface.

#### **Direct Parallel Mode**

Evaluation board programming jumper S2 is set to '0'. Refer to the Control Bit Generator (CBG) Software Reference Manual for instructions on how to setup the software for use. Apply the supply voltage to P6. Select 'QPC3624-P' from the parts list of the CBG user interface. Set the attenuation value using the CBG user interface.

### **Evaluation Board Programming Using External Bus**

#### **Serial Mode**

This configuration allows the user to control the attenuator through the P5 connector using an external harness. Remove the USB interface board if it is currently installed on the evaluation board. Connect a user-supplied harness to the P5 connector. Note that the top row of P5 contains the serial bus signals and the bottom row is ground. Programming jumper S2 is set to '1' to select serial mode. Jumper S6 is installed and allows the LE signal to be routed from the P5 connector to the attenuator. Apply the supply voltage to P6. Send the appropriate signals onto the serial bus lines in accordance with the Serial Addressable Mode Timing Diagram.

#### **Latched Parallel Mode**

This configuration allows the user to control the attenuator through the P1 connector using an external harness. Remove the USB interface if it is currently installed on the evaluation board. Connect a user-supplied harness to the P1 connector. The parallel bus signal names for P1 are indicated on the evaluation board. Programming jumper S2 is set to '0' to select parallel mode. Apply the supply voltage to P6. Send the appropriate signals onto the parallel bus lines in accordance with the Latched Parallel Mode Timing Diagram.

#### **Direct Parallel Mode**

This configuration allows the user to control the attenuator through the P1 connector using an external harness. When using this mode the LE signal is held at logic high so that the attenuation will change immediately when there is a change in logic state for any of the parallel bus signals. Remove the USB interface if it is currently installed on the evaluation board. Connect a user-supplied harness to the P1 connector. The parallel bus signal names for P1 are indicated on the evaluation board. Programming jumper S2 is set to '0' to select parallel mode. Apply the supply voltage to P6. Send the appropriate signals onto the parallel bus lines.

## **Default Power-up State**

This default attenuation state is maximum (31.5 dB) when supply voltage is applied to the attenuator in both serial and parallel modes. If a different attenuation state is desired during power-up, this can be accomplished by applying signals according to the Parallel Mode Truth Table. The attenuator will power-up to the state applied to the parallel bus during turn on. The LE signal must be held to logic '0' during power-up. Note that the FDTI controller can interfere with the default power-up state – removing the plug in module will allow normal expected power default operation.

## **Pad Configuration and Description**

Top View

| Pad No.                             | Label             | Description                                                                                                                                                                                                                 |  |  |  |  |  |

|-------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1, 4, 6, 7, 8, 9, 10,<br>12, 13, 15 | GND               | Ground Pad                                                                                                                                                                                                                  |  |  |  |  |  |

| 2                                   | VDD               | Positive Supply Voltage                                                                                                                                                                                                     |  |  |  |  |  |

| 3                                   | PBAR/S            | Mode Select Pad, Logic Low = Parallel, Logic High = Serial                                                                                                                                                                  |  |  |  |  |  |

| 5                                   | RF <sub>IN</sub>  | RF Input Pad. Incident RF power must enter this pad for rated thermal performance and reliability Do not apply DC power to this pad. Pad may be DC grounded externally and is grounded thru resistors internal to the part. |  |  |  |  |  |

| 11                                  | VSS               | External Negative Supply Voltage. Grounding pin enables on-chip negative voltage generator. Apply negative voltage to disable on-chip generator.                                                                            |  |  |  |  |  |

| 14                                  | RF <sub>OUT</sub> | RF Output Pad; Do not apply DC power to this pad. Pad may be DC grounded externally and is grounded thru resistors internal to the part.                                                                                    |  |  |  |  |  |

| 16                                  | LE                | Latch Enable. The leading edge of signal on LE causes the attenuator to change states for serial and latched parallel modes. For direct parallel mode, keep LE at a logic high level.                                       |  |  |  |  |  |

| 17                                  | CLK               | Serial Clock Input                                                                                                                                                                                                          |  |  |  |  |  |

| 18                                  | SI                | Serial Data Input                                                                                                                                                                                                           |  |  |  |  |  |

| 19                                  | C16               | 16 dB Parallel Control Bit                                                                                                                                                                                                  |  |  |  |  |  |

| 20                                  | C8                | 8 dB Parallel Control Bit                                                                                                                                                                                                   |  |  |  |  |  |

| 21                                  | C4                | 4 dB Parallel Control Bit                                                                                                                                                                                                   |  |  |  |  |  |

| 22                                  | C2                | 2 dB Parallel Control Bit                                                                                                                                                                                                   |  |  |  |  |  |

| 23                                  | C1                | 1 dB Parallel Control Bit                                                                                                                                                                                                   |  |  |  |  |  |

| 24                                  | C0.5              | 0.5 dB Parallel Control Bit                                                                                                                                                                                                 |  |  |  |  |  |

| Backside Paddle                     | RF/DC GND         | RF/DC ground. Use recommended via pattern to minimize inductance and thermal resistance. See PCB Mounting Pattern for suggested footprint.                                                                                  |  |  |  |  |  |

## **Serial Mode Attenuation Word Truth Table**

| D5 | D4 | D3 | D2 | D1 | D0<br>(LSB) | Attenuation State               |

|----|----|----|----|----|-------------|---------------------------------|

| L  | L  | L  | L  | L  | L           | 0 dB / Reference Insertion Loss |

| L  | L  | L  | L  | L  | Н           | 0.5 dB                          |

| L  | L  | L  | L  | Н  | L           | 1 dB                            |

| L  | L  | L  | Н  | L  | L           | 2 dB                            |

| L  | L  | Н  | L  | L  | L           | 4 dB                            |

| L  | Н  | L  | L  | L  | L           | 8 dB                            |

| Н  | L  | L  | L  | L  | L           | 16 dB                           |

| Н  | Н  | Н  | Н  | Н  | Н           | 31.5 dB                         |

### **Parallel Mode Attenuation Word Truth**

|     |            | Attenuat | ion Word |    |               |                                 |

|-----|------------|----------|----------|----|---------------|---------------------------------|

| C16 | <b>C</b> 8 | C4       | C2       | C1 | C0.5<br>(LSB) | Attenuation State               |

| L   | L          | L        | L        | L  | L             | 0 dB / Reference Insertion Loss |

| L   | L          | L        | L        | L  | Н             | 0.5 dB                          |

| L   | L          | L        | L        | Н  | L             | 1 dB                            |

| L   | L          | L        | Н        | L  | L             | 2 dB                            |

| L   | L          | Н        | L        | L  | L             | 4 dB                            |

| L   | Н          | L        | L        | L  | L             | 8 dB                            |

| Н   | L          | L        | L        | L  | L             | 16 dB                           |

| Н   | Н          | Н        | Н        | Н  | Н             | 31.5dB                          |

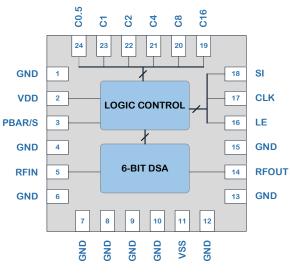

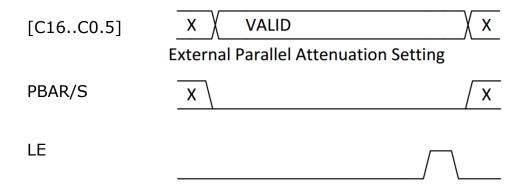

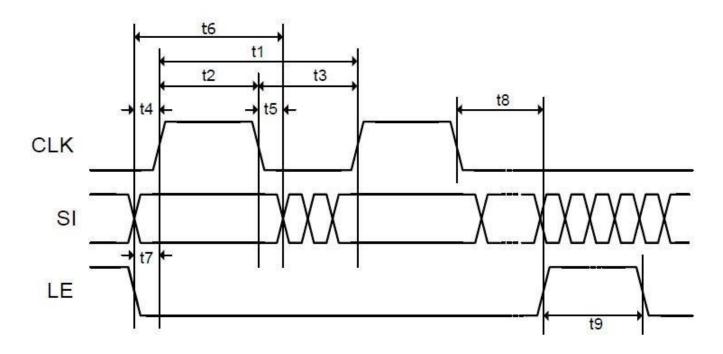

## **Serial Mode Timing Diagram**

## **Latched Parallel Mode Timing Diagram**

# **Serial BUS Timing Specifications**

| Limit | Unit                                | Comment                                                                                                                                                                                                                                       |

|-------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25    | MHz max                             | CLK Frequency                                                                                                                                                                                                                                 |

| 20    | ns min                              | CLK High                                                                                                                                                                                                                                      |

| 20    | ns min                              | CLK Low                                                                                                                                                                                                                                       |

| 5     | ns min                              | SI to CLK Setup Time                                                                                                                                                                                                                          |

| 5     | ns min                              | SI to CLK Hold Time                                                                                                                                                                                                                           |

| 30    | ns min                              | SI Valid                                                                                                                                                                                                                                      |

| 5     | ns min                              | LE to CLK Setup Time                                                                                                                                                                                                                          |

| 5     | ns min                              | CLK to LE Setup Time                                                                                                                                                                                                                          |

| 10    | ns min                              | LE Pulse Width                                                                                                                                                                                                                                |

|       | 25<br>20<br>20<br>5<br>5<br>30<br>5 | 25         MHz max           20         ns min           20         ns min           5         ns min           5         ns min           30         ns min           5         ns min           5         ns min           5         ns min |

## **Package Dimensions**

#### Notes:

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. Dimension and tolerance formats conform to ASME Y14.4M-1994.

- 3. The terminal #1 identifier and terminal numbering conform to JESD 95-1 SPP-012.

- 4. Contact plating: NiPdAu

### **Package Marking**

Pin 1 Indicator

Trace Code to be assigned by SubCon

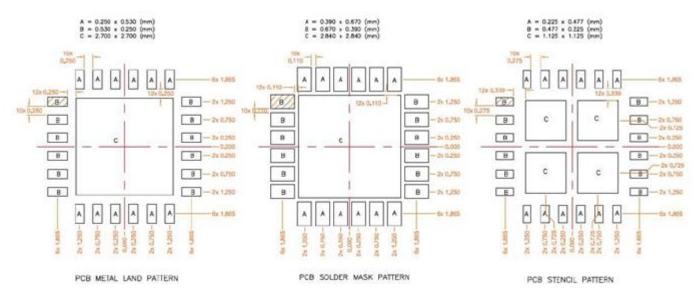

## **Recommended Mounting Pattern**

Thermal vias for center slug "C" should be incorporated into the PCB design. The number and size of thermal vias will depend on the application, the power dissipation, and the electrical requirements. Example of the number and size of vias can be found on the Qorvo evaluation board layout.

## **Handling Precautions**

| Parameter                        | Rating           | Standard               |

|----------------------------------|------------------|------------------------|

| ESD-Human Body Model (HBM)       | Class 1C (1000V) | ESDA/JEDEC JS-001-2012 |

| ESD-Charged Device Model (CDM)   | Class C3 (1000V) | JEDEC JESD22-C101F     |

| MSL – Moisture Sensitivity Level | Level 1          | IPC/JEDEC J-STD-020    |

Caution! ESD-Sensitive Device

### **Solderability**

Compatible with both lead-free (260°C max. reflow temp.) and tin/lead (245°C max. reflow temp.) soldering processes. Solder profiles available upon request.

Contact plating: NiPdAu

## **RoHS Compliance**

This part is compliant with 2011/65/EU RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) as amended by Directive.

This product also has the following attributes:

- Lead Free

- Halogen Free (Chlorine, Bromine)

- Antimony Free

- TBBP-A (C<sub>15</sub>H<sub>12</sub>Br<sub>4</sub>O<sub>2</sub>) Free

- PFOS Free

- SVHC Free

### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations:

Tel: 1-844-890-8163

Web: www.gorvo.com

Email: <u>customer.support@gorvo.com</u>

## **Important Notice**

The information contained herein is believed to be reliable; however, Qorvo makes no warranties regarding the information contained herein and assumes no responsibility or liability whatsoever for the use of the information contained herein. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for Qorvo products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information. THIS INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Without limiting the generality of the foregoing, Qorvo products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.

Copyright 2016 © Qorvo, Inc. | Qorvo is a registered trademark of Qorvo, Inc.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Attenuators category:

Click to view products by Qorvo manufacturer:

Other Similar products are found below:

ATN3580-01 HMC305SLP4ETR MAAD-009195-000100 TGL4201-00 TGL4201-02 TGL4201-03 TGL4201-06 TGL4201-10 ATN3590-15 20-50TPC D10AA5Z4 18AH-01 18AH-08 ATN3580-20 ATN3590-09 20-50RP MASW-008322-000000 MAATCC0009TR PCAF-10 EXB-24AT9AR5X ATN3580-10 HMC539ALP3ETR ATN3580-02 WA04P006XCTL SKY12408-321LF ATN3580-03 WA04P005XBTL HMC-VVD104-SX WA04P007XCTL SKY12236-11 MAATSS0018TR-3000 HMC656-SX WA04P001XBTL MAAV-007941-TR3000 WA04P004XBTL WA04P002XBTL HMC941A PAT0816-C-0DB-T5 PAT0816-C-8DB-T5 PAT1632-C-3DB-T1 PAT1632-C-6DB-T1 PAT1632-C-1DB-T1 PAT1632-C-1DB-T1 PAT1632-C-1DB-T1 PAT1632-C-1DB-T1 PAT1632-C-1DB-T1 PAT1632-C-1DB-T1 PAT1632-C-1DB-T1 PAT1632-C-1DB-T5 PAT0816-C-4DB-T5 DHM510-0100-006 CMD172 MAT10300 MAT10180 MAATCC0007-TB