### **Product Overview**

The Qorvo T2G6003028-FL is a 30W (P<sub>3dB</sub>) discrete GaN on SiC HEMT which operates from DC to 6 GHz. The device is constructed with Qorvo's proven QGaN25 process, which features advanced field plate techniques to optimize power and efficiency at high drain bias operating conditions. This optimization can potentially lower system costs in terms of fewer amplifier line-ups and lower thermal management costs.

Evaluation boards are available upon request.

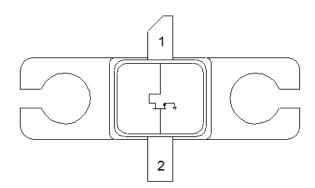

## **Functional Block Diagram**

## **Pin Configuration**

| Pin No. | Label                   |

|---------|-------------------------|

| 1       | V <sub>D</sub> / RF OUT |

| 2       | V <sub>G</sub> / RF IN  |

| Flange  | Source                  |

## **Key Features** <sup>1</sup>

• Frequency: DC to 6 GHz

• Output Power (P3dB): 42.7 W

• Linear Gain: >14 dB

· Operating Voltage: 28 V

· Low thermal resistance package

Pulse capable

Note 1: @ 3 Ghz

## **Applications**

- · Military radar

- · Civilian radar

- Professional and military radio communications

- · Test instrumentation

- · Wideband or narrowband amplifiers

- Jammers

## **Ordering info**

| Part No.          | Description                       |

|-------------------|-----------------------------------|

| T2G6003028-FL     | Packaged part<br>Flanged          |

| T2G6003028-FSEVB  | 5.4 – 5.9 GHz<br>Evaluation Board |

| T2G6003028-FSEVB2 | 1.3 – 1.9 GHz Evaluation Board    |

### **Absolute Maximum Ratings**

| Parameter                                          | Rating      | Units |

|----------------------------------------------------|-------------|-------|

| Breakdown Voltage, BV <sub>DG</sub>                | 100         | V     |

| Gate Voltage Range, V <sub>G</sub>                 | -7 to +2    | V     |

| Drain Current, I <sub>DMAX</sub>                   | 5.5         | Α     |

| Gate Current Range, I <sub>G</sub>                 | -10 to 28   | mA    |

| Power Dissipation, Pulsed, PDISS                   | 47.5        | W     |

| RF Input Power, CW,<br>T = 25°C (P <sub>IN</sub> ) | 40          | dBm   |

| Channel Temperature (T <sub>CH</sub> )             | 275         | °C    |

| Mounting Temperature (30 Seconds)                  | 320         | °C    |

| Storage Temperature                                | -40 to +150 | °C    |

Operation of this device outside the parameter ranges given above may cause permanent damage. These are stress ratings only, and functional operation of the device at these conditions is not implied.

## Recommended Operating Conditions 1,2

| Parameter                           | Min | Тур  | Max | Units |

|-------------------------------------|-----|------|-----|-------|

| Drain Voltage Range, V <sub>D</sub> | 12  |      | 40  | V     |

| Drain Bias Current, IDQ             |     | 200  |     | mA    |

| Gate Voltage, V <sub>G</sub>        | _   | -3.0 | _   | V     |

# **Electrical Specifications** 1, 2

| Parameter                                          | Min  | Тур  | Max | Units |

|----------------------------------------------------|------|------|-----|-------|

| Linear Gain, G <sub>LIN</sub>                      | 12   | 14   | _   | dB    |

| Output Power at 3dB compression point, P3dB        | 43.0 | 44.6 | _   | W     |

| Drain Efficiency at 3dB compression point, DEFF3dB | 45.0 | 54.0 | _   | %     |

| Gain at 3dB compression point, G3dB                | 9.0  | 11.0 | _   | dB    |

| Gate Leakage (VD = +10 V, VG = −3.7 V)             | -11  | _    | _   | mA    |

### Notes:

- 1. Performance at 5.6 GHz in the 5.4 to 5.9 GHz Evaluation Board

- 2.  $V_{DS} = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$ ; Pulse:  $100 \mu \text{s}$ , 20 %

## RF Characterization - Mismatch Ruggedness at 5.6 GHz <sup>1</sup>

| Symbol | Parameter                     | dB Compression | Typical |

|--------|-------------------------------|----------------|---------|

| VSWR   | Impedance Mismatch Ruggedness | 3              | 10:1    |

### Notes:

1. P<sub>1dB</sub> CW Input Power under matched condition.

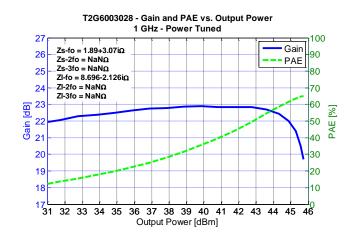

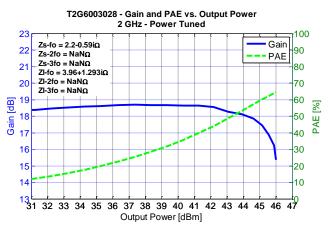

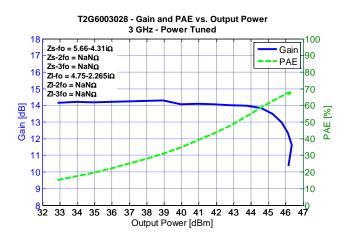

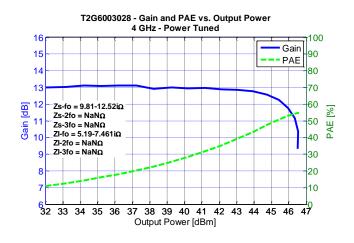

### **Power-Matched Load Pull Performance**

Test conditions unless otherwise noted:  $T = 25^{\circ}C$ .

| Parameter                                    | Typical | ypical Value |      |      |      |      | Units |

|----------------------------------------------|---------|--------------|------|------|------|------|-------|

| Frequency (F)                                | 1       | 2            | 3    | 4    | 5    | 6    | GHz   |

| Drain Voltage (V <sub>D</sub> )              | 28      | 28           | 28   | 28   | 28   | 28   | V     |

| Bias Current (IDQ)                           | 200     | 200          | 200  | 200  | 200  | 200  | mA    |

| Output P <sub>3dB</sub> (P <sub>3dB</sub> )  | 45.7    | 46           | 46.3 | 46.5 | 46.8 | 46.2 | dBm   |

| PAE @ P <sub>3dB</sub> (PAE <sub>3dB</sub> ) | 64.9    | 64.2         | 68.1 | 54.6 | 55.9 | 54.7 | %     |

| Gain @ P <sub>3dB</sub> (G <sub>3dB</sub> )  | 19.9    | 15.7         | 11.3 | 10.1 | 10.7 | 12.1 | dB    |

#### Notes:

- 1.  $V_D = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$ , Pulse Width = 100 uS, Duty Cycle = 20%

- 2. Characteristic Impedance ( $Z_0$ ) = 10  $\Omega$ . See pg. 14 for Load Pull Reference Planes.

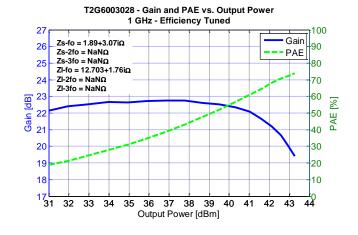

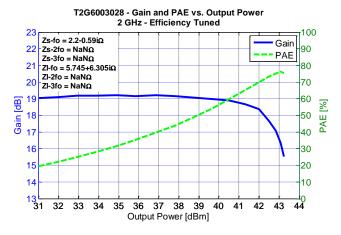

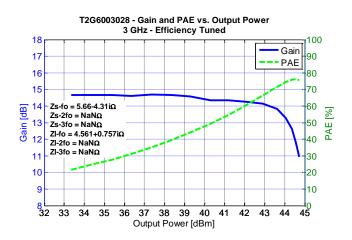

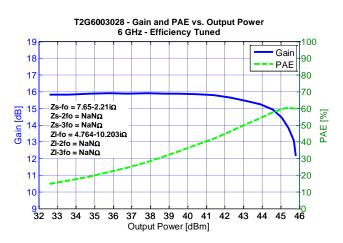

## **Efficiency-Matched Load Pull Performance**

Test conditions unless otherwise noted: T = 25°C.

| Parameter                                    | Typical | ypical Value |      |      |      |      | Units |

|----------------------------------------------|---------|--------------|------|------|------|------|-------|

| Frequency (F)                                | 1       | 2            | 3    | 4    | 5    | 6    | GHz   |

| Drain Voltage (V <sub>D</sub> )              | 28      | 28           | 28   | 28   | 28   | 28   | V     |

| Bias Current (IDQ)                           | 200     | 200          | 200  | 200  | 200  | 200  | mΑ    |

| Output P <sub>3dB</sub> (P <sub>3dB</sub> )  | 43.1    | 43.1         | 44.6 | 44.1 | 44.9 | 45.7 | dBm   |

| PAE @ P <sub>3dB</sub> (PAE <sub>3dB</sub> ) | 73      | 76           | 46.1 | 65.1 | 69.5 | 60   | %     |

| Gain @ P <sub>3dB</sub> (G <sub>3dB</sub> )  | 19.7    | 16.2         | 11.7 | 10.8 | 12.4 | 12.9 | dB    |

- 1.  $V_D = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$ , Pulse Width = 100 uS, Duty Cycle = 20%.

- 2. Characteristic Impedance ( $Z_0$ ) = 10  $\Omega$ . See pg. 14 for Load Pull Reference Planes.

## Thermal Information - CW <sup>1,2</sup>

| Parameter                                              | Test Conditions                     | Value  | Units |

|--------------------------------------------------------|-------------------------------------|--------|-------|

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | D 20 W Thosa 95°C                   | 2.51   | °C/W  |

| Maximum Channel Temperature, T <sub>CH</sub>           | P <sub>D</sub> = 30 W, Tbase = 85°C | 160.25 | °C    |

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | P <sub>D</sub> = 35 W, Tbase = 85°C | 2.58   | °C/W  |

| Maximum Channel Temperature, T <sub>CH</sub>           | FD = 33 W, TDase = 83 C             | 175.20 | °C    |

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | P <sub>D</sub> = 40 W, Tbase = 85°C | 2.67   | °C/W  |

| Maximum Channel Temperature, T <sub>CH</sub>           | FD = 40 W, Tbase = 85 C             | 191.68 | °C    |

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | P <sub>D</sub> = 45 W, Tbase = 85°C | 2.75   | °C/W  |

| Maximum Channel Temperature, T <sub>CH</sub>           | - FD - 45 W, IDase = 85 C           | 208.73 | °C    |

#### Notes:

- 1. Thermal resistance calculated to bottom of package.

- 2. Refer to the following document: GaN Device Channel Temperature, Thermal Resistance, and Reliability Estimates

## Thermal Information - Pulsed 1,2

| Parameter                                              | Test Conditions                                             | Value  | Units |

|--------------------------------------------------------|-------------------------------------------------------------|--------|-------|

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | $P_D = 40 \text{ W}, \text{ Tbase} = 85^{\circ}\text{C}$    | 1.56   | °C/W  |

| Peak Channel Temperature, T <sub>CH</sub>              | Pulse Width = 100 uS Duty Cycle = 5%                        | 147.37 | °C    |

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | P <sub>D</sub> = 40 W, Tbase = 85°C<br>Pulse Width = 100 uS | 1.62   | °C/W  |

| Peak Channel Temperature, T <sub>CH</sub>              | Duty Cycle = 10%                                            | 149.83 | °C    |

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | P <sub>D</sub> = 40 W, Tbase = 85°C                         | 1.77   | °C/W  |

| Peak Channel Temperature, T <sub>CH</sub>              | Pulse Width = 100 uS<br>Duty Cycle = 20%                    | 155.89 | °C    |

| Thermal Resistance, IR <sup>2</sup> (θ <sub>JC</sub> ) | $P_D = 40 \text{ W}, \text{ Tbase} = 85^{\circ}\text{C}$    | 2.07   | °C/W  |

| Peak Channel Temperature, T <sub>CH</sub>              | Pulse Width = 100 uS<br>Duty Cycle = 50%                    | 167.69 | °C    |

- 1. Thermal resistance calculated to bottom of package.

- 2. Refer to the following document: GaN Device Channel Temperature, Thermal Resistance, and Reliability Estimates

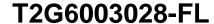

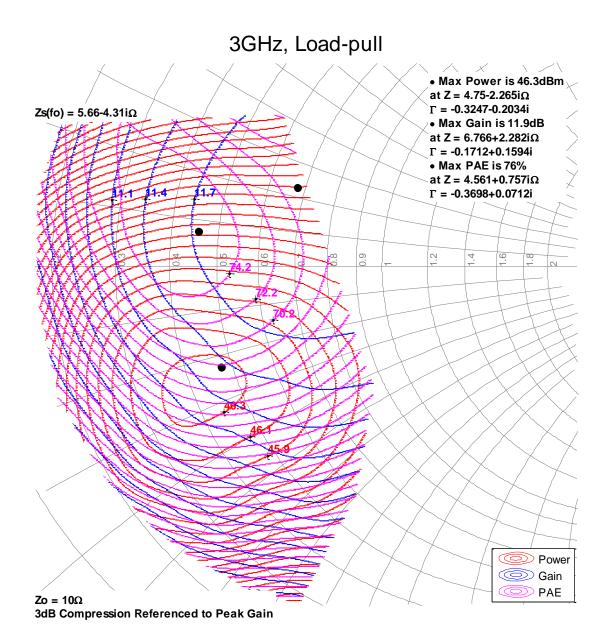

# Load Pull Contours 1, 2, 3

- 1. Test Conditions:  $V_{DS} = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$

- 2. Test Signal: Pulse Width = 100 µsec, Duty Cycle = 20%

- 3. See pg. 14 for load pull reference planes.

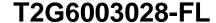

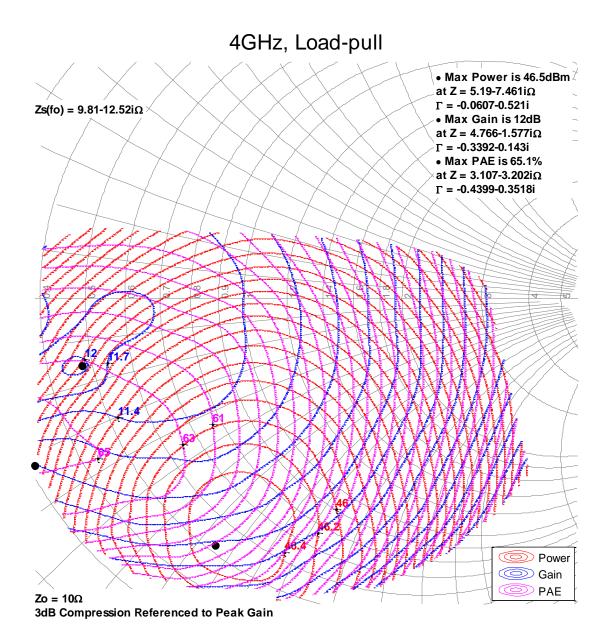

# **Load Pull Contours** 1, 2, 3

- 1. Test Conditions:  $V_{DS} = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$

- 2. Test Signal: Pulse Width = 100 µsec, Duty Cycle = 20%

- 3. See pg. 14 for load pull reference planes.

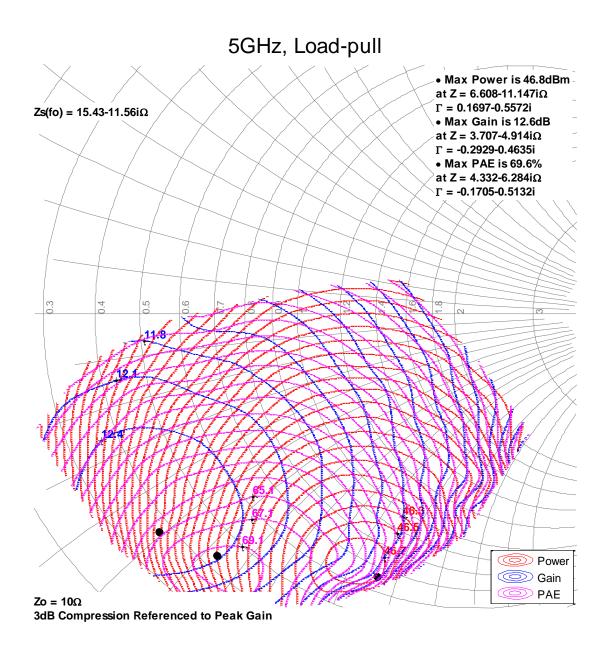

# Load Pull Contours 1, 2, 3

- Test Conditions: V<sub>DS</sub> = 28 V, I<sub>DQ</sub> = 200 mA

- 2. Test Signal: Pulse Width = 100 μsec, Duty Cycle = 20%

- 3. See pg. 14 for load pull reference planes.

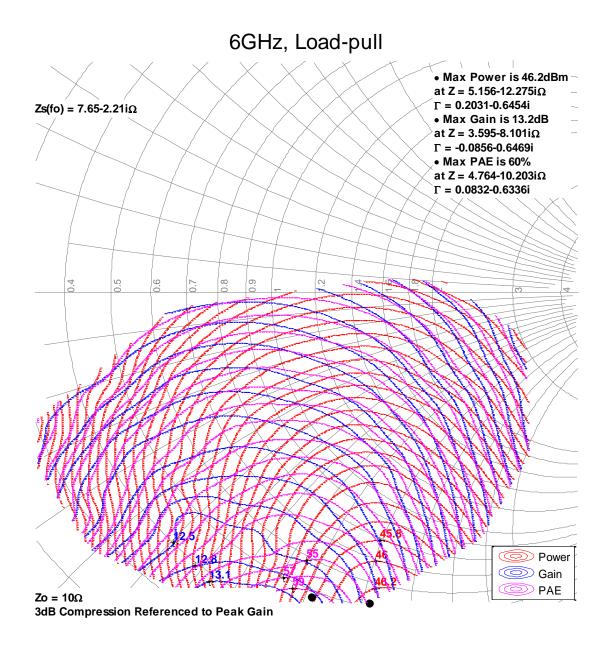

## Load Pull Contours 1, 2, 3

- 1. Test Conditions:  $V_{DS} = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$

- 2. Test Signal: Pulse Width = 100 µsec, Duty Cycle = 20%

- 3. See pg. 14 for load pull reference planes.

# Load Pull Contours 1, 2, 3

- 1. Test Conditions:  $V_{DS} = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$

- 2. Test Signal: Pulse Width = 100 µsec, Duty Cycle = 20%

- 3. See pg. 14 for load pull reference planes.

## **Load Pull Contours** 1, 2, 3

- 1. Test Conditions:  $V_{DS} = 28 \text{ V}$ ,  $I_{DQ} = 200 \text{ mA}$

- 2. Test Signal: Pulse Width = 100 µsec, Duty Cycle = 20%

- 3. See pg. 14 for load pull reference planes.

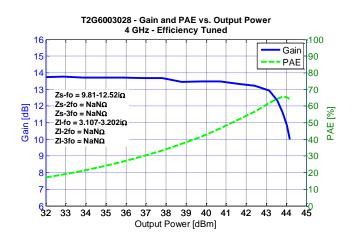

## Load Pull Drive-ups 1, 2

- 1. Vd = 28 V, Idq = 200 mA, Pulse Width = 100 uS, Duty Cycle = 20%

- 2. NaN means the parameter is either unavailable or undefined.

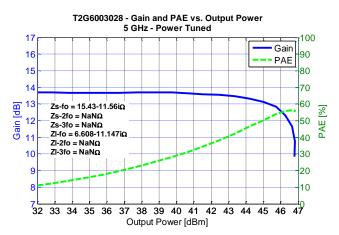

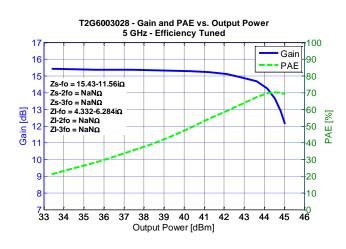

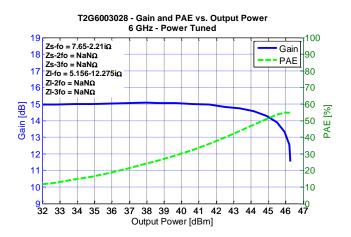

## Load Pull Drive-ups 1, 2

- 1. Vd = 28 V, Idq = 200 mA, Pulse Width = 100 uS, Duty Cycle = 20%

- 2. NaN means the parameter is either unavailable or undefined.

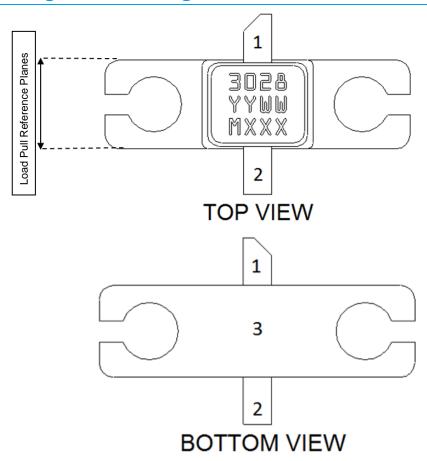

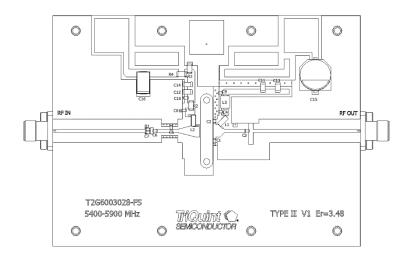

## Package Marking and Pin Configuration <sup>1</sup>

### Note:

The T2G6003028-FL will be marked with the "30282" designator and a lot code marked below the part designator. The "YY" represents the last two digits of the calendar year the part was manufactured, the "WW" is the work week of the assembly lot start, and the "ZZZ" is an auto-generated number.

| Pin | Symbol      | Description                                                                            |

|-----|-------------|----------------------------------------------------------------------------------------|

| 1   | VD / KF UUI | Drain voltage / RF Output matched to 50 ohms; see EVB Layout on page 17 as an example. |

| 2   | Vc/RFIN     | Gate voltage / RF Input matched to 50 ohms; see EVB Layout on page 17 as an example.   |

| 3   | Flange      | Source connected to ground; see EVB Layout on page 17 as an example.                   |

### Notes:

Thermal resistance measured to bottom of package

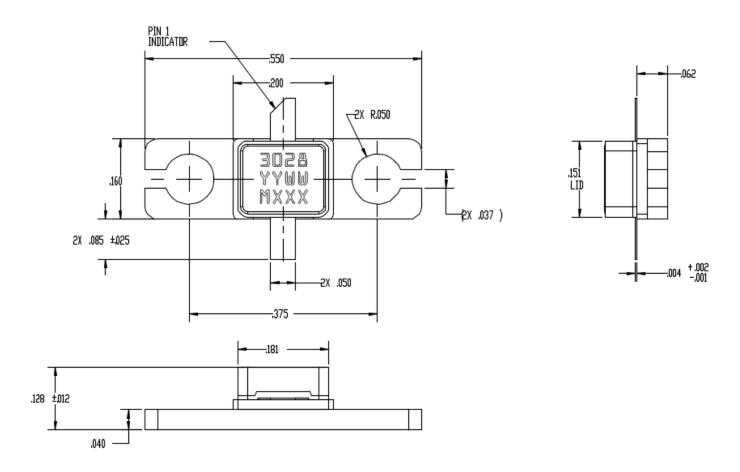

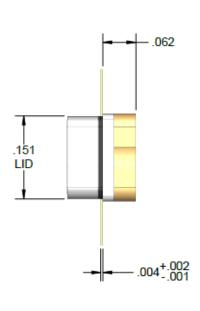

## **Package Dimensions**

- 1. Material:

- Package Base: Ceramic/Metal Package Lid: Ceramic

- 2. Part is epoxy sealed

- 3. All metalized features are gold plated

- 4. Part meets industry NI200 footprint

- 5. Body dimensions do not include lid shift or epoxy run out which can be up to 20 mils per side.

- 6. Dimensions are in inches. General tolerance is ±0.005".

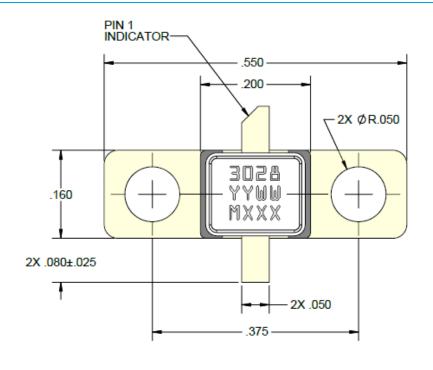

# **Package Dimensions**<sup>1-5</sup>

- 1. Material:

- Package Base: Ceramic/Metal

- Package Lid: Ceramic

- 2. Part is epoxy sealed

- 3. All metalized features are gold plated

- 4. Part meets industry NI200 footprint

- 5. Body dimensions do not include lid shift or epoxy run out which can be up to 20 mils per side.

- 6. Dimensions are in inches. General tolerance is  $\pm 0.005$ ".

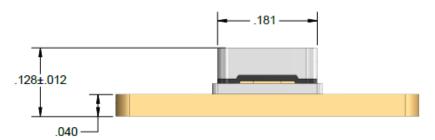

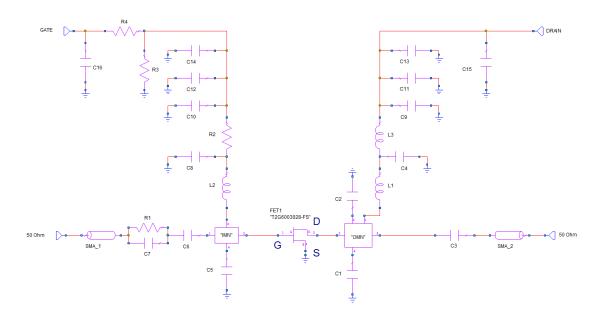

# **Application Circuit**

## **Bias Procedure**

| Bias-up Procedure                                                      | Bias-down Procedure                                      |

|------------------------------------------------------------------------|----------------------------------------------------------|

| 1. Set V <sub>G</sub> to -5 V.                                         | 1. Turn off RF signal.                                   |

| 2. Set I <sub>D</sub> current limit to 220 mA.                         | 2. Turn off V <sub>D</sub>                               |

| 3. Apply 28 V V <sub>D</sub> .                                         | 3. Wait 1 seconds to allow drain capacitor to discharge. |

| 4. Slowly adjust V <sub>G</sub> until I <sub>D</sub> is set to 200 mA. | 4. Turn off V <sub>G</sub>                               |

| 5. Set I <sub>D</sub> to 2.8 A.                                        |                                                          |

| 6. Apply RF signal                                                     |                                                          |

## 5.4 - 5.9 GHz Evaluation Board- Layout 1, 2, 3

#### Notes:

- 1. Top RF layer is 0.020" thick Rogers RO4350B,  $\varepsilon_r = 3.48$

- 2. The pad pattern shown has been developed and tested for optimized assembly at Qorvo Semiconductor.

- 3. The PCB land pattern has been developed to accommodate lead and package tolerances

# 5.4 - 5.9 GHz Application Circuit - Bill of Materials EVB1

| Ref Des            | Qty | Description | Mfg Name                | Mfg Part #                |

|--------------------|-----|-------------|-------------------------|---------------------------|

| C1                 | 1   | 0.3 pF      | ATC                     | ATC600S0R3                |

| C2                 | 1   | 0.2 pF      | ATC                     | ATC600S0R2                |

| L1, L2             | 2   | 8.8 NH      | COILCRAFT               | 1606-8                    |

| C3, C4, C6, C7, C8 | 5   | 3 pF        | ATC                     | ATC600S3R0                |

| C5                 | 1   | 0.4 pF      | ATC                     | ATC600S0R5                |

| R1                 | 1   | 97.6 Ohms   | Venkel                  | CR0604-16w-97R6FT         |

| R2                 | 1   | 4.7 Ohms    | Newark                  | 37C0064                   |

| R3                 | 1   | 330 Ohms    | Newark                  | TNPW1206330RBT9ET1-<br>E3 |

| R4                 | 1   | 50 Ohms     | ATC                     | CRCW120651R0FKEA          |

| C9, C10            | 2   | 220 pF      | AVX                     | AVX06035C22KAT2A          |

| C11, C12           | 2   | 2200 pF     | Vitramon                | VJ1206Y222KXA             |

| C13, C14           | 2   | 22000 pF    | Vitramon                | VJ1206Y223KXA             |

| C15                | 1   | 220 uF      | United Chemi-<br>Con    | EMVY500ADA221MJA0G        |

| C16                | 1   | 1.0 uF      | Allied                  | 541-1231                  |

| L3                 | 1   | 48 Ohm      | Ferrite, Laird<br>Tech. | 28F0121-0SR-10            |

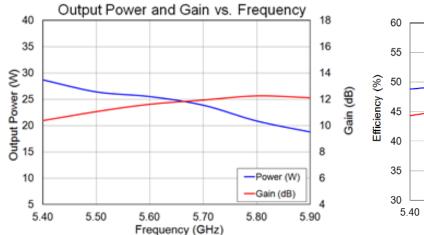

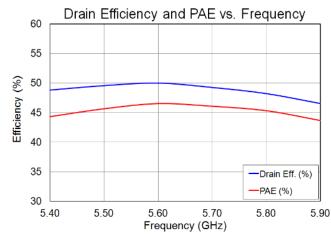

## **Evaluation Board Performance** <sup>1, 2, 3</sup>

- 1. Test Conditions: V<sub>DS</sub> = 28 V, I<sub>DQ</sub> = 200 mA

- 2. Test Signal: Pulse Width = 100  $\mu$ s, Duty Cycle = 20 %

- 3. Performance at 3dB compression.

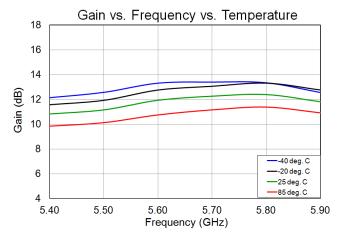

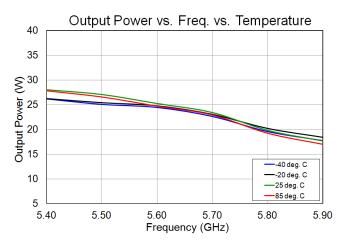

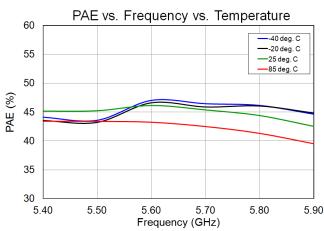

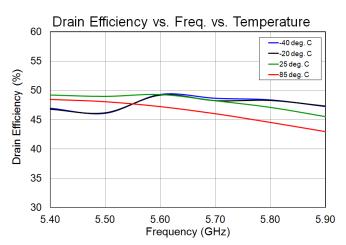

# Performance over Temperatures of 5.4 – 5.9 GHz EVB <sup>1, 2</sup>

- 1. Test Conditions: V<sub>D</sub> = 28 V, I<sub>DQ</sub> = 200 mA, 100 us Pulse Width, 20% Duty Cycle.

- 2. Performance at 3dB compression.

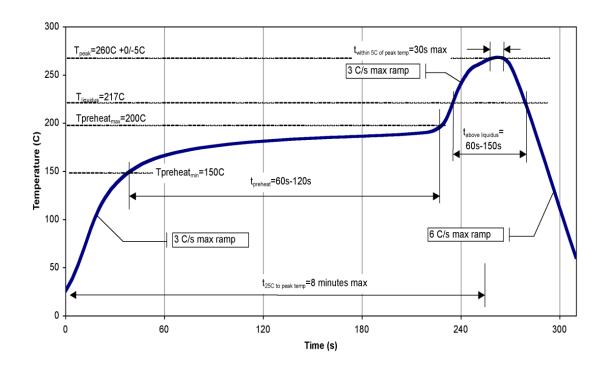

# **Recommended Solder Temperature Profile**

### **Handling Precautions**

| Parameter                        | Rating           | Standard          |

|----------------------------------|------------------|-------------------|

| ESD-Human Body Model (HBM)       | Class 1A (250V)  | JEDEC JESD22-A114 |

| ESD - Charged Device Model (CDM) | Class C3 (1000V) | JEDEC JS-002      |

| MSL-Moisture Sensitivity Level   | MSL3             | JESD J-STD-020    |

Caution! ESD-Sensitive Device

## **Solderability**

Compatible with both lead-free (260°C max. reflow temp.) and tin/lead (245°C max. reflow temp.) soldering processes. Solder profiles available upon request.

The use of no-clean solder to avoid washing after soldering is recommended.

Contact plating: NiAu. Minimum Au thickness is 60 µinches.

## **RoHS Compliance**

This part is compliant with 2011/65/EU RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) as amended by Directive 2015/863/EU.

This product also has the following attributes:

- Halogen Free (Chlorine, Bromine)

- · Antimony Free

- TBBP-A (C<sub>15</sub>H<sub>12</sub>Br<sub>4</sub>O<sub>2</sub>) Free

- PFOS Free

- SVHC Free

### Contact Information

For the latest specifications, additional product information, worldwide sales and distribution locations:

Web: <u>www.qorvo.com</u>

Tel: 1-844-890-8163

Email: customer.support@qorvo.com

## **Important Notice**

The information contained herein is believed to be reliable; however, Qorvo makes no warranties regarding the information contained herein and assumes no responsibility or liability whatsoever for the use of the information contained herein. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for Qorvo products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information. THIS INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Without limiting the generality of the foregoing, Qorvo products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.

Copyright 2021 © Qorvo, Inc. | Qorvo is a registered trademark of Qorvo, Inc.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RF JFET Transistors category:

Click to view products by Qorvo manufacturer:

Other Similar products are found below:

CE3514M4 CE3514M4-C2 CE3520K3-C1 CE3521M4 CE3521M4-C2 CE3512K2-C1 CE3520K3 CG2H80030D-GP4 TGF2023-2-02

NPT1004D MAGX-011086 NPT25015D JANTXV2N4858 MMBFJ211 NPT2021 NPTB00025B 2SK3557-6-TB-E J211\_D74Z

NPTB00004A QPD0020 QPD1006 QPD1016 QPD1025L QPD1029L QPD1881L T2G6001528-Q3 SKY65050-372LF TGF2965-SM

QPD1009 QPD1010 J304 CGH27015F CGH55015F1 CMPA801B030F GTVA262711FA-V2-R0 GTVA262701FA-V2-R0 CGH40006S

CGH40010F CGH40025F CGH40045F CGH40120F CGH55015F2 CGH60008D CGH60030D CGHV14500F CGHV1F006S

CGHV1J006D CGHV27030S CGHV27060MP CGHV40030F