| <b>USP</b>              |                                  |        |

|-------------------------|----------------------------------|--------|

| QMI                     | 3658A DATASHEET<br>JUNE 20, 2022 |        |

|                         | Security Level: 3                |        |

| Document No.: 13-52-25  | Title: QMI8658A Datasheet        | Rev: A |

| Originator: Chunlei Dai | ·                                | L      |

| 02                      |                                  |        |

# QMI8658A Low Noise, Wide Bandwidth 6D Inertial Measurement Unit with Motion Co-Processor

### Features

- Low Noise 150µg/√Hz accelerometer noise

- Host (slave) interface supports MIPI™ I3C, I<sup>2</sup>C, and 3-wire or 4-wire SPI

- Accelerometer and gyroscope sensors feature signal processing paths with digitally programmable data rates and filtering

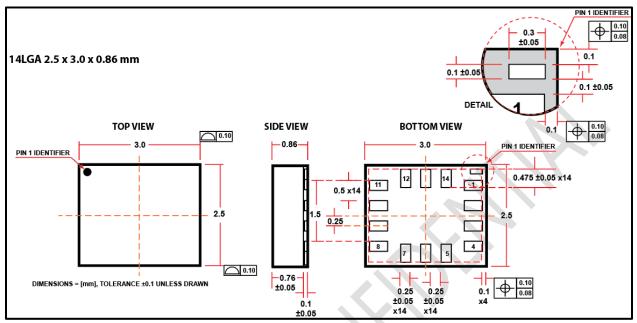

- 3-axis gyroscope and 3-axis accelerometer in a small 2.5 x 3.0 x 0.86 mm 14-pin LGA package

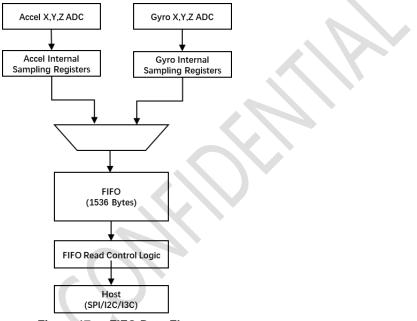

- Large 1536-byte FIFO can be used to buffer sensor data to lower system power dissipation

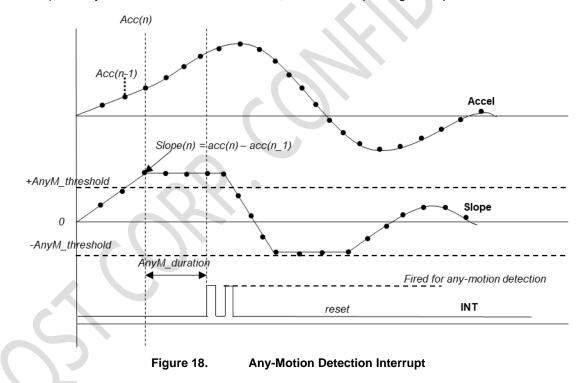

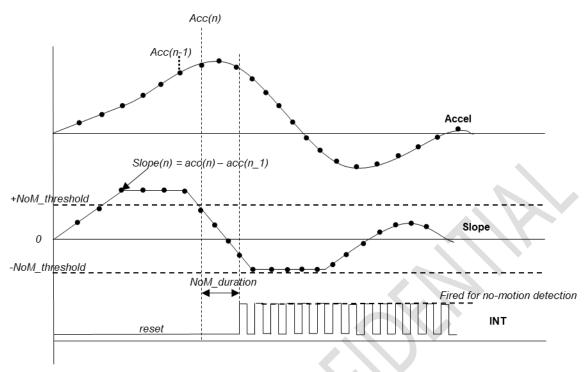

- Integrated Pedometer, Tap, Any-Motion, No-Motion, Significant-Motion detection

- Large sensor dynamic ranges from ±16°/s to ±2048°/s for gyroscope and ±2 g to ±16 g for accelerometer

- Low power modes for effective power management

- Digitally programmable sampling rate and filters

- Embedded temperature sensor

- Wide extended operating temperature range (-40°C to 85°C)

### Description

The QMI8658A is a complete 6D MEMS inertial measurement unit (IMU). With tight board-level gyroscope sensitivity of  $\pm$ 3%, gyroscope noise density of 13 mdps/ $\sqrt{Hz}$ , and low latency, the QMI8658A is ideal for consumer and industrial applications.

The QMI8658A incorporates a 3-axis gyroscope and a 3-axis accelerometer. It provides a host-processor interface supporting I3C,  $I^2C$  and 3-wire or 4-wire SPI.

With its built-in digital functionality, low power, and small size, the QMI8658A is the ideal part for applications requiring motion-based functionality.

# Applications

- Smartphones

- Game controllers, remote controls and pointing devices

- Robotic vacuums

- E-bikes and scooters

- Bluetooth headsets

- Automotive security systems

- Toys

- Portrait-landscape display control

| QMI8658A                                                            |

|---------------------------------------------------------------------|

| 6D                                                                  |

| <ul> <li>6D Inertial Measurement Unit with Motion Co-Pro</li> </ul> |

| Measur                                                              |

| ement l                                                             |

| Unit                                                                |

| with                                                                |

| Motion                                                              |

| Co-Pro                                                              |

| ocessor                                                             |

# **Table of Contents**

| 1 Ge  | neral Information                                       | 5    |

|-------|---------------------------------------------------------|------|

| 1.1   | Ordering Information                                    | 5    |

| 1.2   | Marking Information                                     | 5    |

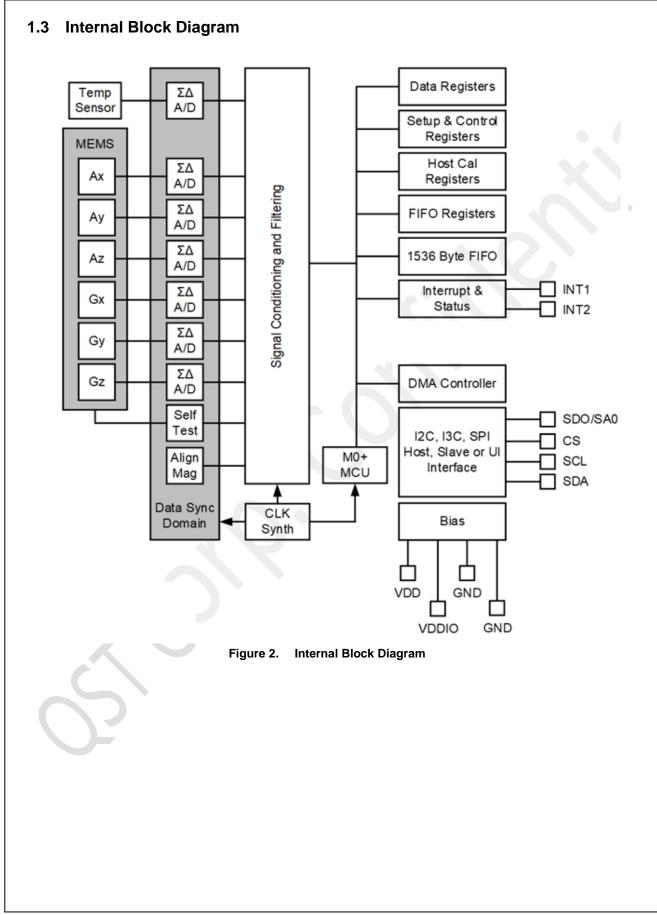

| 1.3   | Internal Block Diagram                                  | 6    |

| 1.4   | Interface Operating                                     | 7    |

| 1.5   | Application Diagrams                                    | 8    |

| 1.6   | Package & Pin Information                               |      |

| 1.7   | Recommended External Components                         |      |

| 2 QN  | AI8658A Chip Orientation Coordinate System              | . 13 |

|       | stem, Electrical and Electro-Mechanical Characteristics | . 14 |

| 3.1   | Absolute Maximum Ratings                                |      |

| 3.2   | Recommended Operating Conditions                        |      |

| 3.3   | Power On Sequence of VDDIO and VDD                      |      |

| 3.3   |                                                         |      |

| 3.3   |                                                         |      |

| 3.3   |                                                         |      |

| 3.4   | Electro-Mechanical Specifications                       |      |

| 3.5   | Accelerometer Programmable Characteristics              |      |

| 3.6   | Gyroscope Programmable Characteristics                  |      |

| 3.7   | Electrical Characteristics                              |      |

| 3.8   | Current Consumption                                     |      |

| 3.9   | Temperature Sensor                                      |      |

| 4 Re  | gister Map Overview                                     |      |

| 4.1   | UI Register Map Overview                                | 25   |

| 5 UI  | Sensor Configuration Settings and Output Data           | . 28 |

| 5.1   | Typical Sensor Mode Configuration and Output Data       |      |

| 5.2   | Chip Information Register                               |      |

| 5.3   | Configuration Registers                                 |      |

| 5.4   | FIFO Registers                                          |      |

| 5.5   | Status and Time Stamp Registers                         | 35   |

| 5.6   | Sensor Data Output Registers                            | 37   |

| 5.7   | Calibration-On-Demand (COD) Status Register             | 38   |

| 5.8   | Activity Detection Output Registers                     | 39   |

| 5.9   | Reset Register                                          | 40   |

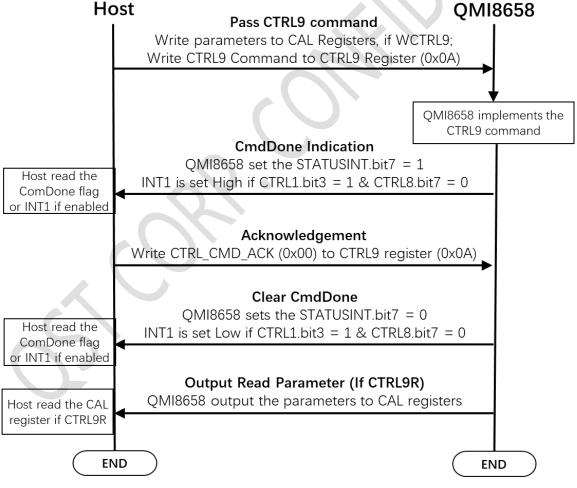

| 5.10  | CTRL 9 Functionality (Executing Pre-defined Commands)   | 41   |

| 5.1   | 0.1 CTRL9 Protocol Description                          | 41   |

| 5.1   | 0.2 CTRL9 Command List                                  | 42   |

| 5.1   | 0.3 CAL Registers                                       | 42   |

| 5.1   | .0.4 WCtrl9 (Write – CTRL9 Protocol)                    | 43   |

| 5.1   | .0.5 Ctrl9R (CTRL9 Protocol - Read)                     |      |

| 5.1   | .0.6 CTRL9 Commands in Details                          | 43   |

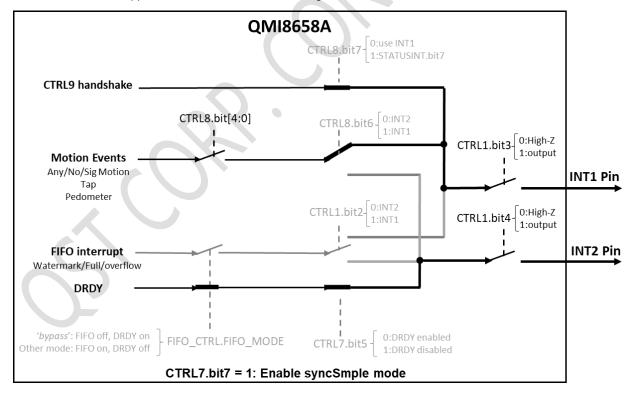

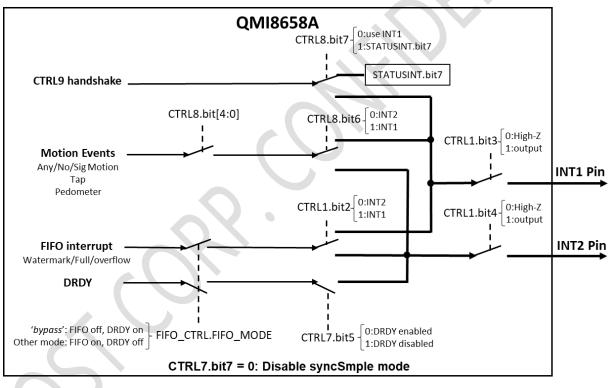

| 6 Int | errupts                                                 | . 46 |

| 6.1   | SyncSample mode                                         |      |

| 6.2   | Non-SyncSample mode                                     |      |

| 6.3   | DRDY(Data Ready)                                        |      |

|       | · · · · · · · · · · · · · · · · · · ·                   | -    |

| QMI8658A                                                |

|---------------------------------------------------------|

| -<br>6D                                                 |

| ) Inertial                                              |

| Measuremen                                              |

| t Unit                                                  |

| with                                                    |

| Motion                                                  |

| - 6D Inertial Measurement Unit with Motion Co-Processor |

| -              | erating Modes 49               |

|----------------|--------------------------------|

| 7.1            | Operating Modes Descriptions49 |

| 7.2            | General Mode Transitioning49   |

| 7.3            | Transition Time                |

| 7.4            | Chip Reset Process             |

| 8 FIF          | 0 Description                  |

| 8.1            | FIFO Structure                 |

| 8.2            | FIFO Size                      |

| 8.3            | Configure FIFO Mode            |

| 8.4            | FIFO Sample Count              |

| 8.5            | FIFO Watermark Interrupt53     |

| 8.6            | FIFO Full                      |

| 8.7            | FIFO Read Mode53               |

| 8.8            | Read FIFO Data53               |

| 8.9            | FIFO Data Pattern              |

| 8.10           | Reset FIFO54                   |

| 9 Mo           | tion Detection                 |

| 9.1            | Motion Detection Principle     |

| 9.1.           |                                |

| 9.1.           | ,                              |

| 9.1.           |                                |

| 9.2            | Motion Detection Flow          |

| 9.3            | Parameters of Motion Detection |

| 9.4            | Config Motion Detection        |

| 9.5            | Enabling Motion Detection      |

| 9.6            | Motion Interrupt               |

| 10 Ton         |                                |

| 10 Tap<br>10.1 | Tap Detection Principle        |

| 10.1           | Tap Detection Principle        |

| 10.2           | Configure Tap                  |

| 10.5           | Enable Tap Detection           |

| 10.4           | Tap Interrupt                  |

| 10.5           | Tap Detection Output           |

|                |                                |

|                | lometer                        |

| 11.1           | Pedometer Parameters           |

| 11.2           | Configure Pedometer            |

| 11.3           | Enable Pedometer65             |

| 11.4           | Pedometer Interrupt            |

| 11.5           | Read Step Count                |

| 11.6           | Reset Step Count               |

| 12 Wa          | ke on Motion (WoM)             |

| 12.1           | Wake on Motion Principle67     |

| 12.2           | Wake on Motion Parameters67    |

| 12.3           | Accelerometer Configuration67  |

| 12.4           | Wake on Motion Event67         |

| 12.5           | Configuration Procedure68      |

| 12.6           | Exit Wake on Motion Mode68     |

www. qstcorp.com 3

<sup>3</sup>

| 13 Loc                                                                                                   | cking Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 13.1                                                                                                     | Locking Mechanism Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69                                                                                                                                     |

| 13.2                                                                                                     | Locking Mechanism Data Reading Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 69                                                                                                                                     |

| 13.                                                                                                      | 2.1 Disable/Enable AHB Clock Gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70                                                                                                                                     |

| 13.                                                                                                      | 2.2 Enable Locking Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70                                                                                                                                     |

| 13.                                                                                                      | 2.3 Reading Sensor Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                                                                                                     |

| 13.3                                                                                                     | Data_Lock_Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 70                                                                                                                                     |

| 13.4                                                                                                     | Exit Locking Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71                                                                                                                                     |

| 13.5                                                                                                     | On-The-Fly ODR Change in Locking Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                                                                                     |

| 14 Cal                                                                                                   | libration-On-Demand (COD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

| 14.1                                                                                                     | COD Principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72                                                                                                                                     |

| 14.2                                                                                                     | Run COD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 14.3                                                                                                     | COD Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72                                                                                                                                     |

| 14.4                                                                                                     | Save and Restore the New Gain Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 72                                                                                                                                     |

| 15 Sel                                                                                                   | lf-Test (Check-Alive)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                        |

| 15.1                                                                                                     | Accelerometer Self-Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 15.2                                                                                                     | Gyroscope Self-Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

| 16 Ho                                                                                                    | st Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                        |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |

| 161                                                                                                      | Address Auto Increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                                                                                                     |

| 16.1<br>16.2                                                                                             | Address Auto Increment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

| 16.2                                                                                                     | Serial Peripheral Interface (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                                                                                                                     |

| <b>16.2</b><br>16.                                                                                       | Serial Peripheral Interface (SPI)           2.1         SPI Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>75</b><br>75                                                                                                                        |

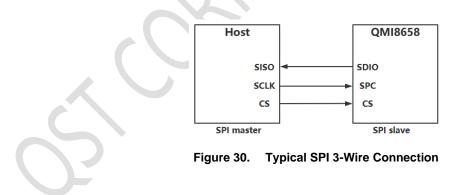

| <b>16.2</b><br>16.<br>16.                                                                                | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>75</b><br>75<br>76                                                                                                                  |

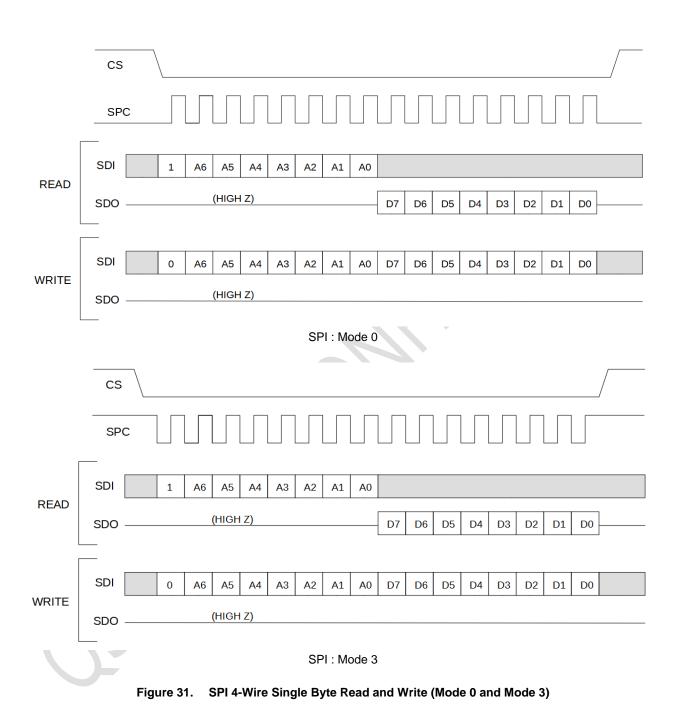

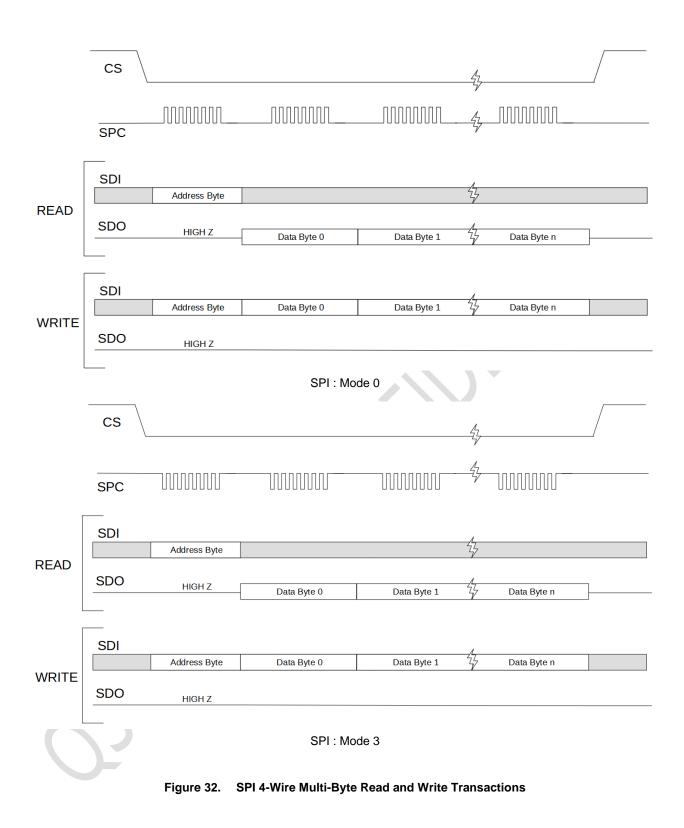

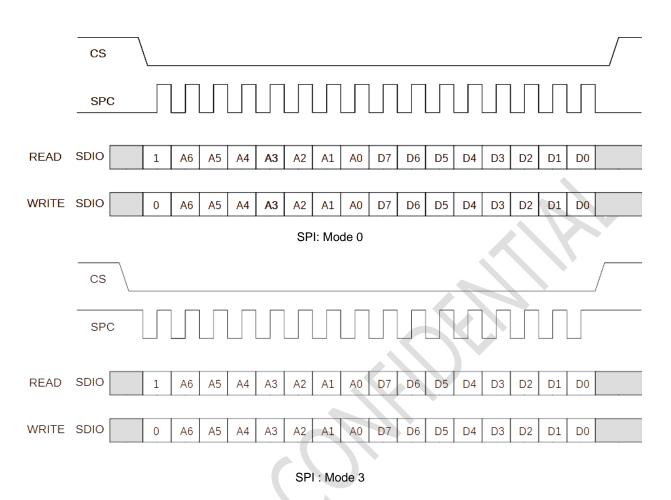

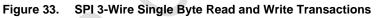

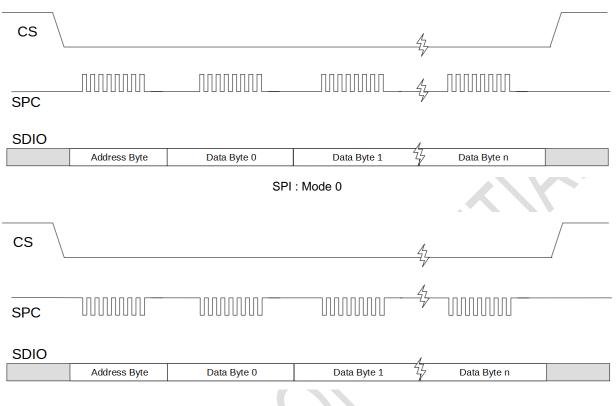

| <b>16.2</b><br>16.<br>16.<br>16.                                                                         | Serial Peripheral Interface (SPI)2.1SPI Features2.2SPI Interface Connection2.3SPI Transaction Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>75</b><br>75<br>76<br>77                                                                                                            |

| <b>16.2</b><br>16.<br>16.<br>16.                                                                         | Serial Peripheral Interface (SPI)2.1SPI Features2.2SPI Interface Connection2.3SPI Transaction Protocol2.4SPI Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>75</b><br>75<br>76<br>77<br>81                                                                                                      |

| <b>16.2</b><br>16.<br>16.<br>16.<br>16.<br><b>16.3</b>                                                   | Serial Peripheral Interface (SPI)2.1SPI Features2.2SPI Interface Connection2.3SPI Transaction Protocol2.4SPI Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>75</b><br>75<br>76<br>77<br>81<br>83                                                                                                |

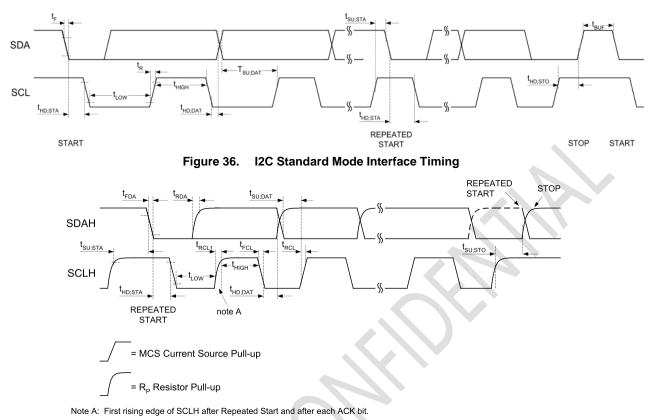

| <b>16.2</b><br>16.<br>16.<br>16.<br>16.<br><b>16.3</b><br>16.                                            | Serial Peripheral Interface (SPI)2.1SPI Features2.2SPI Interface Connection2.3SPI Transaction Protocol2.4SPI Timing CharacteristicsI <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>75</b><br>75<br>76<br>77<br>81<br>83<br>83                                                                                          |

| <b>16.2</b><br>16.<br>16.<br>16.<br>16.<br><b>16.3</b><br>16.                                            | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         I <sup>2</sup> C Interface         3.1       I <sup>2</sup> C Slave Address Selection                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

| <b>16.2</b><br>16.<br>16.<br>16.<br>16.<br><b>16.3</b><br>16.<br>16.<br><b>16.4</b>                      | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         I <sup>2</sup> C Interface         3.1       I <sup>2</sup> C Slave Address Selection         3.2       I <sup>2</sup> C Interface Characteristics         I <sup>3</sup> C Interface                                                                                                                                                                                                | 75<br>76<br>77<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>84                                                                         |

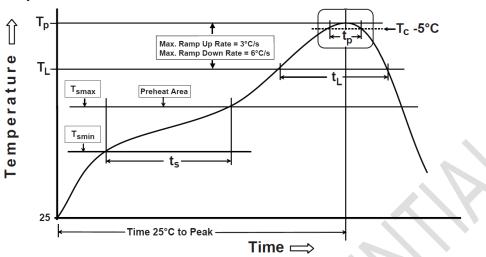

| 16.2<br>16.<br>16.<br>16.<br>16.<br>16.<br>16.<br>16.<br>16.4<br>17 Pac                                  | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         I <sup>2</sup> C Interface         3.1       I <sup>2</sup> C Slave Address Selection         3.2       I <sup>2</sup> C Interface Characteristics         I <sup>3</sup> C Interface         ckage and Handling                                                                                                                                                                     | 75<br>76<br>76<br>77<br>81<br>83<br>83<br>83<br>83<br>83<br>84<br>84                                                                   |

| 16.2<br>16.<br>16.<br>16.<br>16.<br>16.3<br>16.<br>16.<br>16.4<br>17 Pac<br>17.1                         | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         I <sup>2</sup> C Interface       Iterface         3.1       I <sup>2</sup> C Slave Address Selection         3.2       I <sup>2</sup> C Interface Characteristics         I <sup>3</sup> C Interface       Iterface         ckage and Handling       Package Drawing                                                                                                                 | 75<br>76<br>76<br>77<br>81<br>83<br>83<br>83<br>83<br>83<br>84<br>85<br>85                                                             |

| 16.2<br>16.<br>16.<br>16.<br>16.3<br>16.<br>16.<br>16.4<br>17 Pao<br>17.1<br>17.2                        | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         1 <sup>2</sup> C Interface         3.1       I <sup>2</sup> C Slave Address Selection         3.2       I <sup>2</sup> C Interface Characteristics         I <sup>3</sup> C Interface         ckage and Handling         Package Drawing         Reflow Specification                                                                                                                | 75<br>76<br>76<br>77<br>81<br>83<br>83<br>83<br>83<br>83<br>84<br>85<br>85<br>85<br>86                                                 |

| 16.2<br>16.<br>16.<br>16.<br>16.3<br>16.<br>16.4<br>17 Pao<br>17.1<br>17.2<br>17.3                       | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         1 <sup>2</sup> C Interface         3.1       I <sup>2</sup> C Slave Address Selection         3.2       I <sup>2</sup> C Interface Characteristics         I <sup>3</sup> C Interface         ckage and Handling         Package Drawing         Reflow Specification         Storage Specifications                                                                                 | 75<br>76<br>76<br>77<br>81<br>83<br>83<br>83<br>83<br>83<br>84<br>85<br>85<br>85<br>86<br>86<br>86<br>86                               |

| 16.2<br>16.<br>16.<br>16.<br>16.<br>16.<br>16.<br>16.<br>16.4<br>17 Pac<br>17.1<br>17.2<br>17.3<br>18 Do | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         1 <sup>2</sup> C Interface       Interface         3.1       I <sup>2</sup> C Slave Address Selection         3.2       I <sup>2</sup> C Interface Characteristics         I <sup>3</sup> C Interface       Interface         ckage and Handling       Package Drawing         Reflow Specification       Storage Specifications         cument Information       Cument Information | 75<br>76<br>76<br>77<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>84<br>85<br>85<br>85<br>85<br>85<br>85<br>85<br>86<br>86<br>87 |

| 16.2<br>16.<br>16.<br>16.<br>16.3<br>16.<br>16.4<br>17 Pao<br>17.1<br>17.2<br>17.3                       | Serial Peripheral Interface (SPI)         2.1       SPI Features         2.2       SPI Interface Connection         2.3       SPI Transaction Protocol         2.4       SPI Timing Characteristics         1 <sup>2</sup> C Interface         3.1       I <sup>2</sup> C Slave Address Selection         3.2       I <sup>2</sup> C Interface Characteristics         I <sup>3</sup> C Interface         ckage and Handling         Package Drawing         Reflow Specification         Storage Specifications                                                                                 | 75<br>76<br>76<br>77<br>81<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>84<br>85<br>85<br>85<br>85<br>85<br>85<br>85<br>86<br>86<br>87 |

# **1** General Information

# 1.1 Ordering Information

### Table 1. Ordering Information

| Part Number | Package | Packing Method |  |

|-------------|---------|----------------|--|

| QMI8658A    | LGA14   | Tape & Reel    |  |

## 1.2 Marking Information

| ROW | EXAMPLE | CODE/EXPLANATION                                                    |

|-----|---------|---------------------------------------------------------------------|

| 1   | 8658    | DDDD – Device code                                                  |

| 2   | 2113    | YWLL-Y (Year code), W (1-digit, biweekly code), LL (Lot indication) |

| 3   | • RB    | CR – C (Assembly location), R (Product revision)                    |

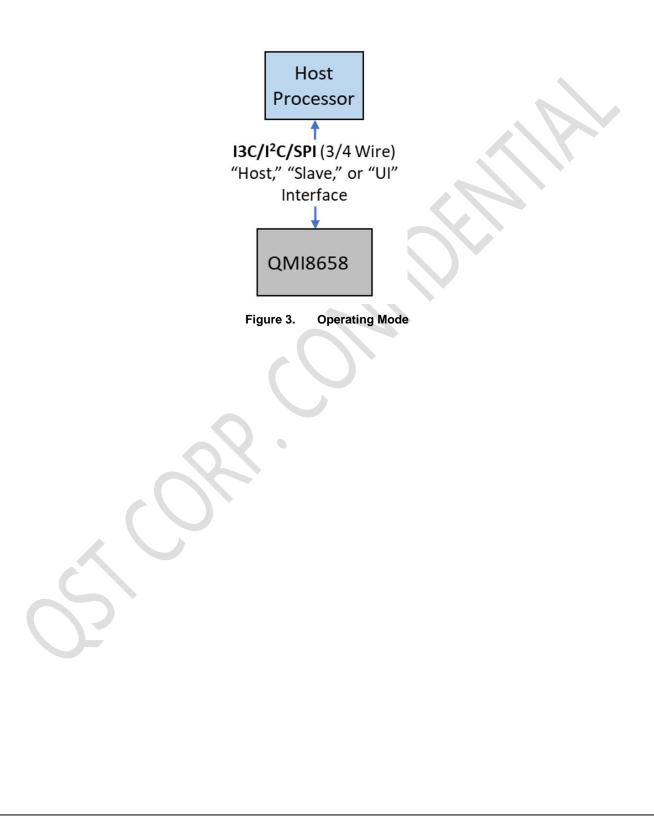

# **1.4 Interface Operating**

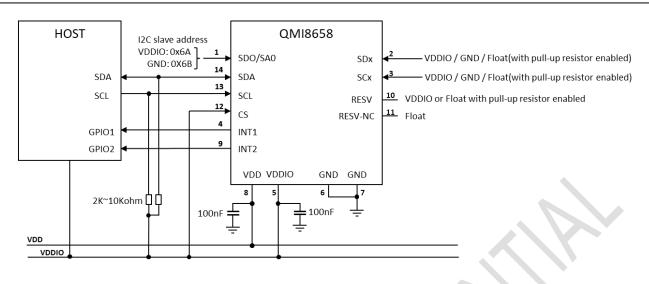

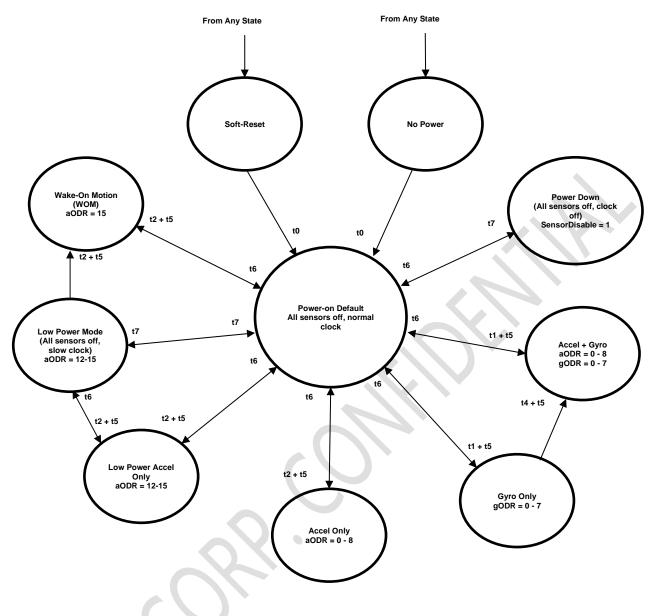

The QMI8658A can operate in below mode, as shown in the Figure 3.

The QMI8658A is a slave device to a host processor that communicates to it using one of the following interfaces: I<sup>2</sup>C, I<sup>3</sup>C, and SPI (3-wire or 4-wire modes). This slave relationship to the host is the same for all operating modes.

Figure 6. I3C/I2C-UI mode

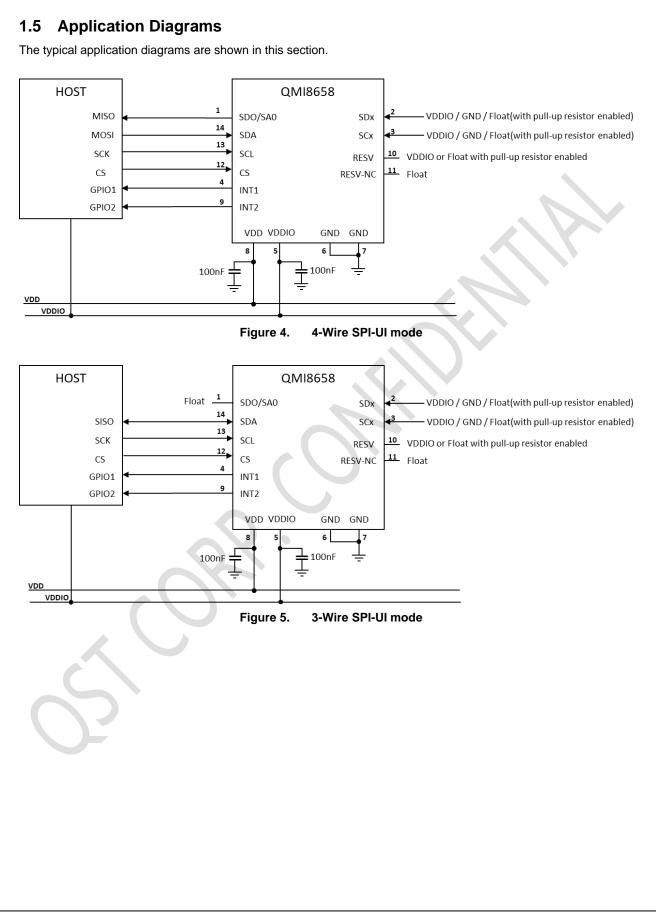

There is internal 200Kohm pull-up resistor on the SCL, SDA, CS, SDx, SCx, RESV (Pin10). By default, all those pullup resistors are enabled. All the resistors can be disabled by CTRL9 command, refer to *1.6 Package & Pin Information* and *5.10.6 CTRL\_CMD\_SET\_RPU* for details.

There is internal 200Kohm pull-up resistor on SDO/SA0 pin, and is enabled during Power-On Reset or Soft-Reset, is automatically disabled after detecting the I2C slave address during the Reset Process. Therefore, in I2C/I3C mode leave the SDO/SA0 float or connect it to High level (recommended, to provide a stable level), will set the I2C slave address/I3C static address to 0x6A. And connect it to Low level, will set the I2C slave address to 0x6B.

In 3-wire SPI mode, leave the SDO/SA0 pin float.

SCx and SDx can be connected to VDDIO or Logic High, GND or Logic Low, or be left float if internal pull-up resistors are enabled.

RESV (Pin 10) should NOT be connected to GND or Logic Low. It can be connected to VDDIO or Logic High, or leave it externally float and enable the internal pull-up resistor(by default the pull-up resistor is enabled). Connecting it to VDDIO is preferred, which can provide a stable High level.

RESV-NC (Pin 11) is by default an output pin, should be float (no connection). In case of the necessity to connect it to High or Low level, the RESV(Pin 10) should be firmly connected to VDDIO, providing a stable High level, to disable the output of Pin 11.

Table 2 describes the names for the pins in different functions. The later descriptions will directly use the function name in different scenarios instead of the pin name.

| Pin Number | Туре | Pin Name | Function Name in<br>4-wire SPI | Function Name in<br>3-wire SPI | Function Name in<br>Host I2C / I3C |

|------------|------|----------|--------------------------------|--------------------------------|------------------------------------|

| 1          | 0    | SDO/SA0  | SDO                            |                                | SA0                                |

| 12         | I    | CS       | CS                             | CS                             |                                    |

| 13         | 10   | SCL      | SPC                            | SPC                            | SCL                                |

| 14         | Ю    | SDA      | SDI                            | SDIO                           | SDA                                |

Table 2. Pin Name Mapped to Function Name

QMI8658A — 6D Inertial Measurement Unit with Motion Co-Processor

### **1.6** Package & Pin Information The pinout of the QMI8658A is shown in Figure 7 and Figure 8. The pin names and functionality are detailed in Table 3. The pin functionality is dictated by the QMI8658A's operating mode, as described in 1.5 Application Diagrams.

Pin 1 Identifier SDA SDA Pin 1 Identifier SCL SCL S S Ū, ( )12 12 13 14 14 13 SDO/SA0 SDO-AUX SDO-AUX 11 1 SDO/SA0 11 1 SDx CS-AUX CS-AUX 10 SDx 10 2 Top Through View **Bottom View** (Pads <u>not</u> Visible) (Pads Visible) SCx 3 9 INT2 INT2 9 3 SCx 8 VDD VDD INT1 4 8 4 INT1 7 5 6 6 5 7 VDDIO GND GND GND GND VDDIO Pins Face Down (Top View) Figure 8. Pins Face Up (Bottom View) Figure 7.

| Pin<br>Number | Туре | Pin Name                  | Function                                                                                                      |  |  |

|---------------|------|---------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| 1             | 0    | SDO/SA0 <sup>(1)(3)</sup> | SPI-UI Data Out (SDO) in SPI-UI 4-Wire Mode                                                                   |  |  |

|               |      |                           | SA0, I <sup>2</sup> C Slave address and I <sup>3</sup> C Static address select:                               |  |  |

|               |      |                           | If SA0 = 0, $I^2C / I^3C$ address = 0x6B                                                                      |  |  |

|               |      |                           | If SA0 = 1, $I^2C / I^3C$ address = 0x6A                                                                      |  |  |

| 2             | IO   | SDx <sup>(1)(2)</sup>     | Reserved. Connect to VDDIO, GND or No Connection                                                              |  |  |

| 3             | ю    | SCx <sup>(1)(2)</sup>     | Reserved. Connect to VDDIO, GND or No Connection                                                              |  |  |

| 4             | 0    | INT1                      | Programmable Interrupt 1                                                                                      |  |  |

| 5             | I    | VDDIO                     | Power Supply for IO Pins                                                                                      |  |  |

| 6             | I    | GND                       | Ground (0 V supply)                                                                                           |  |  |

| 7             | I    | GND                       | Ground (0 V supply)                                                                                           |  |  |

| 8             | I    | VDD                       | ower supply                                                                                                   |  |  |

| 9             | 0    | INT2                      | rogrammable Interrupt 2 (INT2) / Data Ready (DRDY)                                                            |  |  |

|               |      | RESV <sup>(1)(2)</sup>    | Reserved. Connect to VDDIO or Logic High, or No Connection and enable (by default) internal pull up resistor. |  |  |

|               |      |                           | Refer to 1.5 Application Diagrams.                                                                            |  |  |

| 11            | I    | RESV-NC                   | Reserved. Connect to VDDIO or Logic High, GND or Logic Low.                                                   |  |  |

|               |      |                           | Refer to 1.5 Application Diagrams.                                                                            |  |  |

| 12            | I    | CS <sup>(1)(2)</sup>      | I <sup>2</sup> C/I <sup>3</sup> C /SPI-UI selection Pin.                                                      |  |  |

|               |      |                           | (If 1: I <sup>2</sup> C-UI Mode: I <sup>2</sup> C/I <sup>3</sup> C communication enabled, SPI idle mode)      |  |  |

|               |      |                           | (If 0: SPI-UI mode: I <sup>2</sup> C/I <sup>3</sup> C disabled)                                               |  |  |

| 13            | 10   | SCL <sup>(1)(2)</sup>     | I <sup>2</sup> C/I <sup>3</sup> C-UI Data (SDA) in I <sup>2</sup> C/ I <sup>3</sup> C mode                    |  |  |

|               |      |                           | SPI-UI Serial Clock (SPC) <sup>(3)</sup> in SPI mode                                                          |  |  |

| 14            | 10   | SDA <sup>(1)(2)</sup>     | I <sup>2</sup> C/I <sup>3</sup> C-UI Data (SDA)                                                               |  |  |

|               |      |                           | SPI-UI Data In (SDI) <sup>(3)</sup> in 4 wire Mode                                                            |  |  |

|               |      |                           | SPI-UI Data IO (SDIO) (3) in 3 Wire Mode                                                                      |  |  |

### Notes:

- 1. This pin has an internal 200K $\Omega$  pull up resistor.

- 2. The internal pull-up resistor can be disabled by CTRL9 command (CTRL\_CMD\_SET\_RPU). Refer to **5.10.6** *CTRL\_CMD\_SET\_RPU* for details.

- 3. Refer to Section 16 for detailed configuration information.

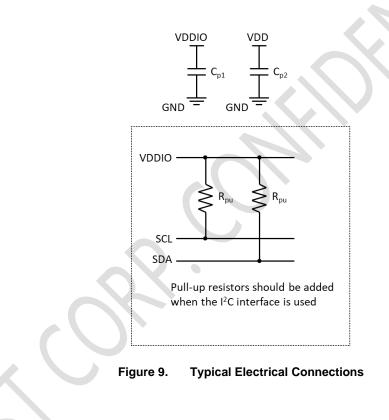

### 1.7 Recommended External Components

| Component                      | Description | Parameter   | Typical     |

|--------------------------------|-------------|-------------|-------------|

| Cp1                            | Capacitor   | Capacitance | 100 nF      |

| C <sub>p2</sub>                | Capacitor   | Capacitance | 100 nF      |

| R <sub>pu</sub> <sup>(4)</sup> | Resistor    | Resistance  | 2KΩ ~ 10 kΩ |

### Table 4. Recommended External Components

### Note:

4. R<sub>pu</sub> resistors are only needed when the Host Serial Interface is configured for I<sup>2</sup>C (see I2C Interface section). They are not needed when the Host Serial Interface is configured for SPI or I3C. If pull-up resistors are used on SCL and SDA, then SPI, I3C and I<sup>2</sup>C Modes are all possible. If a pull-down resistor is used on SA0, an alternate slave address is used for I<sup>2</sup>C. SPI and I3C modes will be unaltered with the use of pull-up resistors for I<sup>2</sup>C. Additionally, a suitable pull up resistance (R<sub>pu</sub>) value should be selected, accounting for the tradeoff between current consumption and rise time.

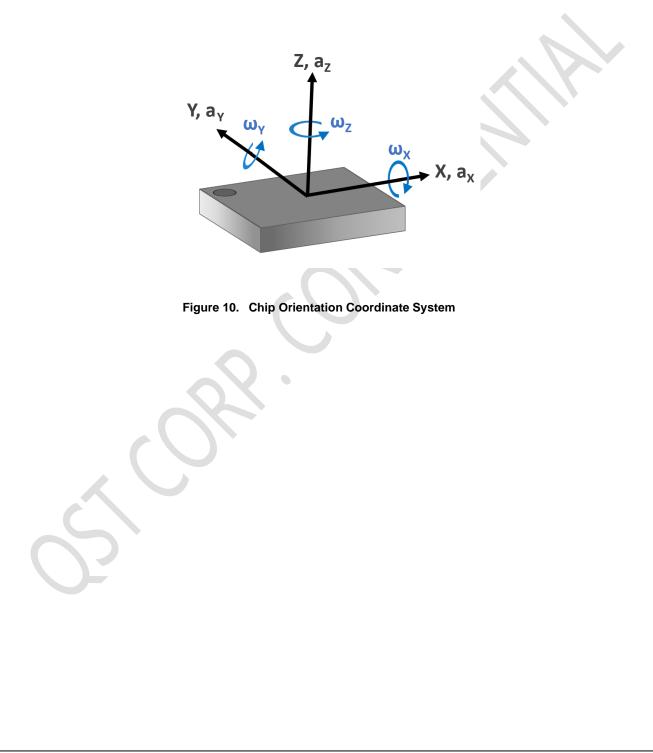

# 2 QMI8658A Chip Orientation Coordinate System

The QMI8658A uses a right-handed coordinate system as the basis for the sensor frame of reference. Acceleration  $(a_x, a_y, a_z)$  are given with respect to the X-Y-Z coordinate system shown above. Increasing accelerations along the positive X-Y-Z axes are considered positive. Angular Rate  $(\omega_x, \omega_y, \omega_z)$  in the counterclockwise direction around the respective axis are considered positive.

Figure 10 shows the various frames of reference and conventions for using the QMI8658A.

# 3 System, Electrical and Electro-Mechanical Characteristics

# 3.1 Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions. Stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

### Table 5. Absolute Maximum Ratings

| Symbol                        | Parameter                |                                        |        | Max. | Unit |

|-------------------------------|--------------------------|----------------------------------------|--------|------|------|

| Tstg                          | Storage Temperature      | Storage Temperature                    |        |      | °C   |

| T <sub>Pmax</sub>             | Lead Soldering Tempera   | Lead Soldering Temperature, 10 Seconds |        |      | °C   |

| VDD                           | Supply Voltage           |                                        |        | 3.6  | V    |

| VDDIO                         | I/O Pins Supply Voltage  |                                        |        | 3.6  | V    |

| S <sub>g</sub> <sup>(5)</sup> | Acceleration g for 0.2 m |                                        | 10,000 | g    |      |

| ESD <sup>(6)</sup>            | Electrostatic Discharge  | Human Body Model per JES001-2014       | ±2000  |      | v    |

|                               | Protection Level         | Charged Device Model per JESD22-C101   | ±ť     | 500  | V    |

Notes:

5. This is a mechanical shock (g) sensitive device. Proper handling is required to prevent damage to the part.

6. This is an ESD-sensitive device. Proper handling is required to prevent damage to the part.

# 3.2 Recommended Operating Conditions

The Recommended Operating Conditions table defines the conditions for device operation. Recommended operating conditions are specified to ensure optimal performance. It is not forbidden to design beyond to Absolute Maximum Ratings.

### Table 6. Recommended Operating Conditions

| Symbol   | Parameter                         | Min        | Тур | Мах         | Unit |

|----------|-----------------------------------|------------|-----|-------------|------|

| VDD      | Supply Voltage                    | 1.71       | 1.8 | 3.6         | V    |

| VDDIO    | I/O Pins Supply Voltage           | 1.71       | 1.8 | 3.6         | V    |

| VIL      | Digital Low Level Input Voltage   |            |     | 0.3 *VDDIO  | V    |

| VIH      | Digital High Level Input Voltage  | 0.7 *VDDIO |     | VDDIO + 0.3 | V    |

| Vol      | Digital Low Level Output Voltage  |            |     | 0.1 *VDDIO  | V    |

| Vон      | Digital High Level Output Voltage | 0.9 *VDDIO |     |             | V    |

| VPOR_RLS | POR Threshold Voltage             |            | 1.1 |             | V    |

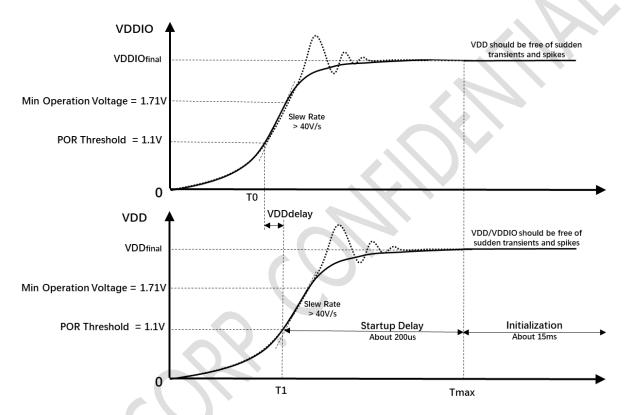

# 3.3 Power On Sequence of VDDIO and VDD

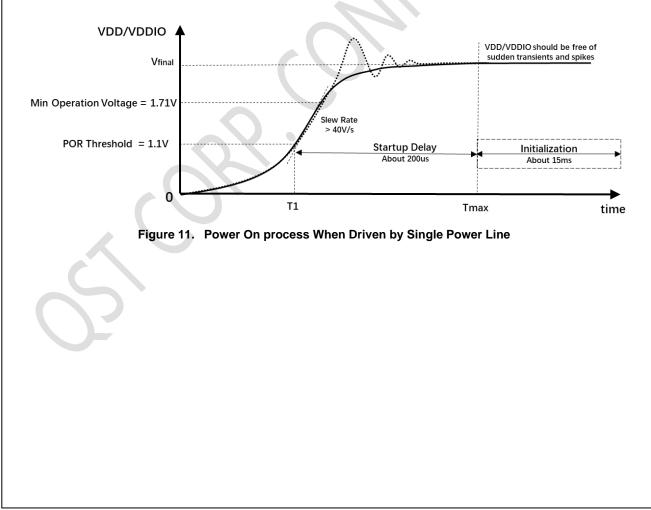

### 3.3.1 Power-On Reset(POR)

Once the VDD & VDDIO are powered from 0V to a certain level, the internal power voltage detector will trigger the Power-On Reset (POR) automatically, and then exit/release the POR mode as the VDD voltage rises over the POR Threshold (about 1.1V). Refer to *Table 6.*

After POR release, there will be about 200us Startup Delay, followed by the QMI8658A Initialization.

The instability of VDDIO & VDD power lines, especially the power increase/drop with high slew rate, would interfere the QMI8658A Initialization and operation. Therefore, there should be no sudden transients and spikes on power lines after Startup Delay, to make sure the Initialization and later on operations are properly implemented.

Normally it takes within about 15ms (refer to System Turn On Time in Table 7 and Table 8) for QMI8658A to finish the Initialization and during which, there should be no write/configuration to QMI8658A, to prevent possible interference and failure.

Note that the Software Reset is triggered by the reset command that host write to QMI8658A, which means POR is not involved, while the following sequence are similar (Startup Delay and Initialization) to POR. Refer to 7.4 for more details.

### 3.3.2 VDDIO and VDD Are Driven by Single Power

As shown in *Figure 11*, when QMI8658A is driven by single/same power line, the power line should ramp up from POR Threshold (about 1.1V) to Min Operation Voltage(1.71V) with slew rate higher than 40V/s, otherwise the Initialization might fail, and QMI8658A might not work properly.

### 3.3.3 VDDIO and VDD Are Driven by Separate Power Lines

As shown in *Figure 12*, when QMI8658A is driven by separate power lines, the VDDIO should be always powered ahead of (no later than) VDD, which means:

VDDdelay >= 0, VDDIO should be driven no later than VDD

Note that the VDDdelay starts from the point when VDDIO rises over the POR Threshold and ended at the VDD rises over the POR Threshold. It should always be non-negative.

The power lines should ramp up from POR Threshold (about 1.1V) to Min Operation Voltage(1.71V) with slew rate higher than 40V/s, otherwise the Initialization might fail, and QMI8658A might not work properly.

Figure 12. Power On process When Driven by Separate Power Lines

# 3.4 Electro-Mechanical Specifications

VDD = VDDIO = 1.8 V, T = 25°C unless otherwise noted.

### Table 7. Accelerometer Electro-Mechanical Specifications

| Subsystem     | Parameter                                                                                                               | Турі          | cal         | Unit   | Comments                                                                                            |

|---------------|-------------------------------------------------------------------------------------------------------------------------|---------------|-------------|--------|-----------------------------------------------------------------------------------------------------|

|               | Noise Density                                                                                                           | 150           | )           | µg/√Hz | High-Resolution Mode                                                                                |

|               |                                                                                                                         | Scale Setting | Sensitivity |        |                                                                                                     |

|               |                                                                                                                         | ±2 g          | 16,384      |        |                                                                                                     |

|               | Sensitivity Scale Factor                                                                                                | ±4 g          | 8,192       | LSB/g  | 16-Bit Output                                                                                       |

|               | Cross-Axis Sensitivity<br>Temperature Coefficient of<br>Offset (TCO)<br>Temperature Coefficient of<br>Sensitivity (TCS) | ±8 g          | 4,096       |        |                                                                                                     |

|               |                                                                                                                         | ±16 g         | 2,048       |        |                                                                                                     |

|               | Cross-Axis Sensitivity                                                                                                  | ±1            |             | %      |                                                                                                     |

| Accelerometer | -                                                                                                                       | ±1            |             | mg/°C  | Over-Temperature Range of<br>-40°C to 85°C, at Board<br>Level                                       |

|               | Offset (TCO)<br>Temperature Coefficient of<br>Sensitivity (TCS)<br>Initial Offset Tolerance                             | ±0.0          | )4          | %/°C   | Over-Temperature Range of<br>-40°C to 85°C, at Board<br>Level                                       |

|               |                                                                                                                         | ±10           | 0           | mg     | Board Level                                                                                         |

|               | Initial Sensitivity Tolerance                                                                                           | ±6            |             | %      | Board Level                                                                                         |

|               | Non-Linearity                                                                                                           | ±0.7          | ′5          | %      | Best Fit Line                                                                                       |

|               | System Turn On Time <sup>(1)</sup>                                                                                      | 15            |             | ms     | From Software Reset, No<br>Power, or Power Down to<br>Power-on Default state = t0<br>in Figure 16   |

|               | Initial Sensitivity Tolerance<br>Non-Linearity                                                                          | 3 ms + 3      | 3/ODR       | ms     | Accel Turn on from Power-<br>On Default state or from Low<br>Power state = t2 + t5 in<br>Figure 16. |

### Note:

7. System Turn-On Time defines the initialization duration of QMI8658A, it starts from about 200us later than the release of POR(Power On Reset) or the Software Reset. Refer to 3.3 and 7.4 for details.

| Subsystem | Parameter                                       | Тур                    | ical        | Unit     | Comments                                                                                          |  |  |  |

|-----------|-------------------------------------------------|------------------------|-------------|----------|---------------------------------------------------------------------------------------------------|--|--|--|

|           |                                                 | Scale<br>Setting       | Sensitivity |          |                                                                                                   |  |  |  |

|           |                                                 | ±16 dps                | 2048        |          |                                                                                                   |  |  |  |

|           |                                                 | ±32 dps                | 1024        |          |                                                                                                   |  |  |  |

|           |                                                 | ±64 dps                | 512         | LSB/dps  |                                                                                                   |  |  |  |

|           | Sensitivity                                     | ±128 dps               | 256         | LSB/dps  | 16-Bit Output                                                                                     |  |  |  |

|           |                                                 | ±256 dps               | 128         |          |                                                                                                   |  |  |  |

|           |                                                 | ±512 dps               | 64          |          |                                                                                                   |  |  |  |

|           |                                                 | ±1024 dps              | 32          |          |                                                                                                   |  |  |  |

|           |                                                 | ±2048 dps              | 16          |          | $\langle \cdot \rangle$                                                                           |  |  |  |

|           | Natural Frequency                               | 22.                    | 42          | kHz      | Precision +/- 2%(typical)                                                                         |  |  |  |

|           | Noise Density                                   | 1                      | 3           | mdps/√Hz | High-Resolution Mode                                                                              |  |  |  |

|           | Non-Linearity                                   | ±0                     | .2          | %        |                                                                                                   |  |  |  |

| Gyroscope | Noise Density                                   | ±                      | 2           | %        |                                                                                                   |  |  |  |

| -,        |                                                 | ±0                     | dps/g       |          |                                                                                                   |  |  |  |

|           | System Turn On Time <sup>(1)</sup>              | 1                      | 5           | ms       | From Software Reset, No<br>Power, or Power Down to<br>Power-on Default state<br>= t0 in Figure 16 |  |  |  |

|           | Gyro Turn On Time                               | 150 ms -               | + 3/ODR     | ms       | Gyro Turn on from Power-<br>On Default = t1 + t5 in<br>Figure 16                                  |  |  |  |

|           | Temperature Coefficient of<br>Offset (TCO)      | X/Y:<br>Z: ±0          |             | dps/°C   | Over-Temperature Range of<br>-40°C to 85°C, at Board<br>Level                                     |  |  |  |

|           | Temperature Coefficient of<br>Sensitivity (TCS) | X/Y: <u>-</u><br>Z: ±0 |             | %/°C     | Over-Temperature Range of<br>-40°C to 85°C, at Board<br>Level                                     |  |  |  |

|           | Initial Offset Tolerance                        | ±1                     | 0           | dps      | Board Level                                                                                       |  |  |  |

|           | Initial Sensitivity Tolerance                   | ±                      | 3           | %        | Board Level                                                                                       |  |  |  |

### Table 8. Gyroscope Electro-Mechanical Specifications

### Note:

8. System Turn-On Time defines the initialization duration of QMI8658A, it starts from about 200us later than the release of POR(Power On Reset) or the Software Reset. Refer to 3.3 and 7.4 for details.

### 3.5 Accelerometer Programmable Characteristics

VDD = VDDIO = 1.8 V, T = 25°C unless otherwise noted. Typical numbers are provided below unless otherwise noted.

If only accelerometer is enabled, the ODR frequency is derived from the internal oscillator. If both accelerometer and gyroscope (6DOF mode) are enabled, the ODR frequency is derived from the natural frequency of gyroscope. Table 9 shows the two ODR frequencies, which can be referenced for later descriptions in the datasheet. Refer to section 5.3 for detailed ODR configuration.

RMS noise can be calculated based on the noise density and the bandwidth.

| Mode                        |        |        |        | High- | Resolu | ition |       |       |        | Low-Power |     |     |     | Unit   |

|-----------------------------|--------|--------|--------|-------|--------|-------|-------|-------|--------|-----------|-----|-----|-----|--------|

| ODR<br>(Accel<br>only)      |        |        |        | 1000  | 500    | 250   | 125   | 62.5  | 31.25  | 128       | 21  | 11  | 3   | Hz     |

| ODR<br>(Accel +<br>Gyro)    | 7174.4 | 3587.2 | 1793.6 | 896.8 | 448.4  | 224.2 | 112.1 | 56.05 | 28.025 |           |     |     |     | Hz     |

| Typical<br>Noise<br>Density | 150    | 150    | 150    | 150   | 150    | 150   | 150   | 150   | 150    | 125       | 180 | 285 | 700 | µg/√Hz |

### Table 9. Accelerometer Noise Density

| Mode                                                                    |      |      |      | High- | Resolu | tion |      |      |       | L    | ow-P | ower | •   | Unit |

|-------------------------------------------------------------------------|------|------|------|-------|--------|------|------|------|-------|------|------|------|-----|------|

| ODR                                                                     | 8000 | 4000 | 2000 | 1000  | 500    | 250  | 125  | 62.5 | 31.25 | 128  | 21   | 11   | 3   |      |

| Bandwidth<br>(Default, 27.5% of<br>ODR)                                 | NA   | NA   | NA   | 275   | 137.5  | 68.8 | 34.4 | 17.2 | 8.6   | 35.2 | 5.8  | 3.0  | 0.8 |      |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 00<br>(2.66% of ODR)  | NA   | NA   | NA   | 26.6  | 13.3   | 6.7  | 3.3  | 1.7  | 0.8   | 3.4  | 0.6  | 0.3  | 0.1 |      |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 01<br>(3.63% of ODR)  | NA   | NA   | NA   | 36.3  | 18.2   | 9.1  | 4.5  | 2.3  | 1.1   | 4.6  | 0.8  | 0.4  | 0.1 | Hz   |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 10<br>(5.39% of ODR)  | NA   | NA   | NA   | 53.9  | 27     | 13.5 | 6.7  | 3.4  | 1.7   | 6.9  | 1.1  | 0.6  | 0.2 |      |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 11<br>(13.37% of ODR) | NA   | NA   | NA   | 133.7 | 66.9   | 33.4 | 16.7 | 8.4  | 4.2   | 17.1 | 2.8  | 1.5  | 0.4 |      |

### Table 10. Accelerometer Filter Characteristics (Accelerometer only)<sup>(9)</sup>

Note:

9. When only accelerometer is enabled, the ODR is derived from the internal oscillator, rather than the nature frequency of Gyroscope

| Table 11.                                                                         | Accele | rometer | r Filter Cl | haracte | eristics | (6DOF | ) <sup>(10)</sup> |       |        |     |       |     |    |      |

|-----------------------------------------------------------------------------------|--------|---------|-------------|---------|----------|-------|-------------------|-------|--------|-----|-------|-----|----|------|

| Mode                                                                              |        |         |             | High-   | Resolu   | tion  |                   |       |        | L   | .ow-F | owe | r  | Unit |

| ODR                                                                               | 7174.4 | 3587.2  | 1793.6      | 896.8   | 448.4    | 224.2 | 112.1             | 56.05 | 28.025 | 128 | 21    | 11  | 3  |      |

| Bandwidth<br>(Default,<br>27.5% of<br>ODR)                                        | 1973.0 | 986.5   | 493.2       | 246.6   | 123.3    | 61.7  | 30.8              | 15.4  | 7.7    | NA  | NA    | NA  | NA |      |

| Bandwidth<br>with Low-<br>Pass Filter<br>Enabled<br>Mode 00<br>(2.66% of<br>ODR)  | 190.8  | 95.4    | 47.7        | 23.9    | 11.9     | 6.0   | 3.0               | 1.5   | 0.7    | NA  | NA    | NA  | NA | •    |

| Bandwidth<br>with Low-<br>Pass Filter<br>Enabled<br>Mode 01<br>(3.63% of<br>ODR)  | 260.4  | 130.2   | 65.1        | 32.6    | 16.3     | 8.1   | 4.1               | 2.0   | 1.0    | NA  | NA    | NA  | NA | Hz   |

| Bandwidth<br>with Low-<br>Pass Filter<br>Enabled<br>Mode 10<br>(5.39% of<br>ODR)  | 386.7  | 193.4   | 96.7        | 48.3    | 24.2     | 12.1  | 6.0               | 3.0   | 1.5    | NA  | NA    | NA  | NA |      |

| Bandwidth<br>with Low-<br>Pass Filter<br>Enabled<br>Mode 11<br>(13.37% of<br>ODR) | 959.2  | 479.6   | 239.8       | 119.9   | 60.0     | 30.0  | 15.0              | 7.5   | 3.7    | NA  | NA    | NA  | NA |      |

### ... ...

Note:

10. When both accelerometer and gyroscope are both enabled, all frequencies are synchronized to the nature frequency of gyroscope.

© 2022 QST Corporation

### 3.6 Gyroscope Programmable Characteristics

VDD = VDDIO = 1.8 V, T = 25°C, and represent typical numbers unless otherwise noted. All frequencies are synchronized to the gyroscope nature frequency.

Table 12 shows the noise density of gyroscope output over different ODR configurations.

The typical bandwidths of gyroscope over different ODR settings are listed in Table 13.

RMS noise can be calculated based on the noise density and the bandwidth.

### Table 12. Gyroscope Noise Density

| Mode                    |                     | High-Resolution                                          |                     |    |    |    |    |    |    |                   |  |  |

|-------------------------|---------------------|----------------------------------------------------------|---------------------|----|----|----|----|----|----|-------------------|--|--|

| ODR (Gyro and/or Accel) | 7174.4              | 174.4 3587.2 1793.6 896.8 448.4 224.2 112.1 56.05 28.025 |                     |    |    |    |    |    |    |                   |  |  |

| Typical Noise Density   | RSV <sup>(11)</sup> | RSV <sup>(11)</sup>                                      | RSV <sup>(11)</sup> | 13 | 13 | 13 | 13 | 13 | 13 | mdps/ $\sqrt{Hz}$ |  |  |

Note:

11. The gyroscope noise increases significantly when the ODR is set above 1KHz. It is not recommended to set the ODR beyond 1KHz for the applications that are impacted by gyroscope noise. For more information please contact QST FAE team.

### Table 13. Gyroscope Filter Characteristics

| Mode                                                                    |        |        |        | High  | -Resolu | tion  | -     |       |        | Unit |

|-------------------------------------------------------------------------|--------|--------|--------|-------|---------|-------|-------|-------|--------|------|

| ODR                                                                     | 7174.4 | 3587.2 | 1793.6 | 896.8 | 448.4   | 224.2 | 112.1 | 56.05 | 28.025 |      |

| Bandwidth<br>(Default, 27.5% of<br>ODR)                                 | 1973.0 | 986.5  | 493.2  | 246.6 | 123.3   | 61.7  | 30.8  | 15.4  | 7.7    |      |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 00<br>(2.66% of ODR)  | 190.8  | 95.4   | 47.7   | 23.9  | 11.9    | 6.0   | 3.0   | 1.5   | 0.7    |      |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 01<br>(3.63% of ODR)  | 260.4  | 130.2  | 65.1   | 32.6  | 16.3    | 8.1   | 4.1   | 2.0   | 1.0    | Hz   |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 10<br>(5.39% of ODR)  | 386.7  | 193.4  | 96.7   | 48.3  | 24.2    | 12.1  | 6.0   | 3.0   | 1.5    |      |

| Bandwidth with<br>Low-Pass Filter<br>Enabled Mode 11<br>(13.37% of ODR) | 959.2  | 479.6  | 239.8  | 119.9 | 60.0    | 30.0  | 15.0  | 7.5   | 3.7    |      |

# 3.7 Electrical Characteristics

$VDD = VDDIO = 1.8 V, T = 25^{\circ}C$  unless otherwise noted.

### Table 14. Electrical Subsystem Characteristics

| Symbol           | Paramet                                                        | ter                      | Min. | Тур. | Max. | Unit |

|------------------|----------------------------------------------------------------|--------------------------|------|------|------|------|

| f <sub>SPC</sub> | Host SPI Interface Speed                                       |                          |      |      | 15   | MHz  |

| fsc∟             | Host I <sup>2</sup> C Interface Speed (sta Mode are supported) | ndard mode and Fast      |      |      | 400  | kHz  |

| fscL3            | Host I <sup>3</sup> C Interface Speed                          | Standard Data Rate (SDR) |      |      | 12.5 | MHz  |

# QMI8658A — 6D Inertial Measurement Unit with Motion Co-Processor

# 3.8 Current Consumption

VDD = VDDIO = 1.8 V, T = 25°C unless otherwise noted. IDD Current refers to the current flowing into the VDD pin. Typical numbers are provided below.

### Table 15. Current Consumption for Accelerometer Only Sensor Mode (Gyroscope Disabled)

|                                                    | Mode                         |     | ł   | ligh-F | Resolut | l     | Low-Power |    |    |    |    |    |

|----------------------------------------------------|------------------------------|-----|-----|--------|---------|-------|-----------|----|----|----|----|----|

|                                                    | 1000                         | 500 | 250 | 125    | 62.5    | 31.25 | 128       | 21 | 11 | 3  | Hz |    |

| Typical                                            | Filters Disabled<br>(aLPF=0) | 182 | 155 | 142    | 134     | 133   | 132       | 55 | 42 | 35 | 30 |    |

| Overall IDD<br>Current Filters Enabled<br>(aLPF=1) |                              | 182 | 155 | 142    | 134     | 133   | 132       | 55 | 42 | 35 | 30 | μΑ |

### Table 16. Current Consumption for Gyroscope Only Sensor Mode (Accelerometer Disabled)

|                    | Mode                         |        |        |        | High- | Resolut | tion  |       |       |        | Unit |

|--------------------|------------------------------|--------|--------|--------|-------|---------|-------|-------|-------|--------|------|

|                    | ODR                          | 7174.4 | 3587.2 | 1793.6 | 896.8 | 448.4   | 224.2 | 112.1 | 56.05 | 28.025 | Hz   |

| Typical<br>Overall | Filters Disabled<br>(gLPF=0) | 908    | 861    | 748    | 689   | 659     | 656   | 654   | 653   | 651    |      |

| IDD<br>Current     | Filters Enabled<br>(gLPF=1)  | 916    | 863    | 748    | 689   | 659     | 656   | 654   | 653   | 651    | μA   |

### Table 17. Current Consumption for 6DOF Sensor Mode (Accelerometer and Gyroscope Enabled)

| Ν                      | lode                                    |        |        |       | High-F | Resolut | ion   |       |        |     | Unit |

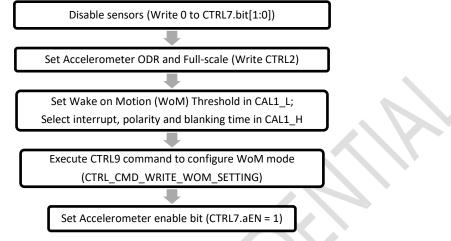

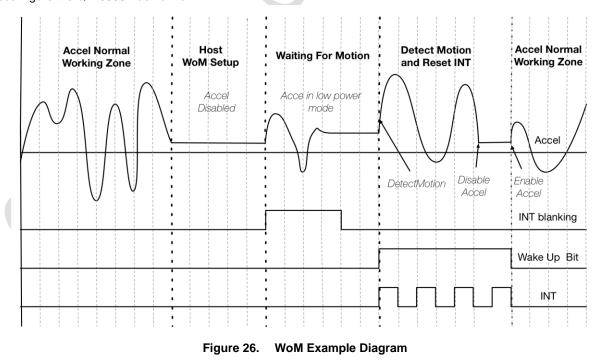

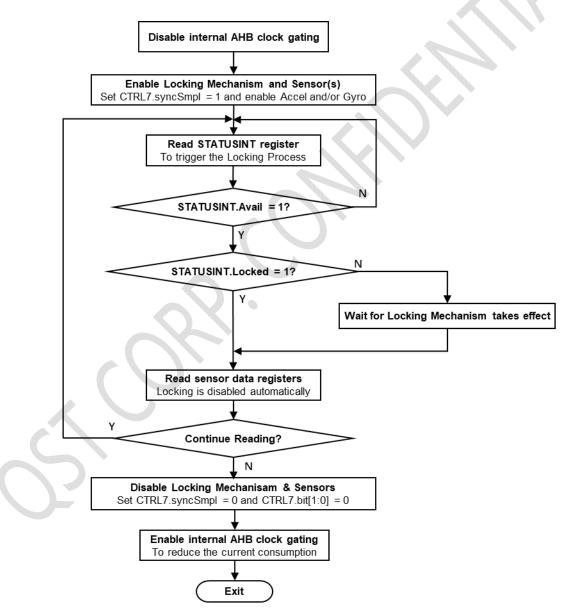

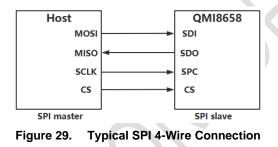

|------------------------|-----------------------------------------|--------|--------|-------|--------|---------|-------|-------|--------|-----|------|