# 3.3V Phase-Lock Loop Clock Driver

## **General Description**

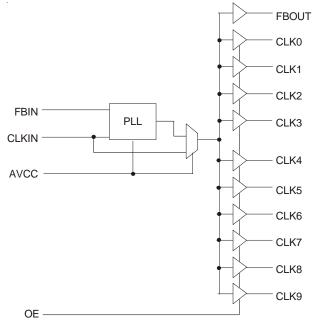

**The ICS2510C** is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the CLKIN signal with the CLKOUT signal. It is specifically designed for use with synchronous SDRAMs. The **ICS2510C** operates at 3.3V VCC and drives up to ten clock loads.

One bank of ten outputs provide low-skew, low-jitter copies of CLKIN. Output signal duty cycles are adjusted to 50 percent, independent of the duty cycle at CLKIN. Outputs can be enabled or disabled via control (OE) inputs. When the OE inputs are high, the outputs align in phase and frequency with CLKIN; when the OE inputs are low, the outputs are disabled to the logic low state.

The **ICS2510C** does not require external RC filter components. The loop filter for the PLL is included on-chip, minimizing component count, board space, and cost. The test mode shuts off the PLL and connects the input directly to the output buffer. This test mode, the **ICS2510C** can be use as low skew fanout clock buffer device. The **ICS2510C** comes in 24 pin 173mil Thin Shrink Small-Outline package (TSSOP) package.

## **Features**

- Meets or exceeds PC133 registered DIMM specification1.1

- Spread Spectrum Clock Compatible

- Distributes one clock input to one bank of ten outputs

- Operating frequency 25MHz to 175MHz

- External feedback input (FBIN) terminal is used to synchrionize the outputs to the clock input

- No external RC network required

- Operates at 3.3V Vcc

- Plastic 24-pin 173mil TSSOP package

## **Block Diagram**

0010G-09/22/09

© 2019 Renesas Electronics Corporation

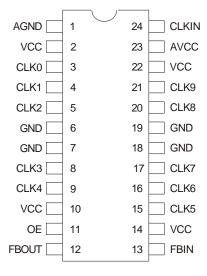

## **Pin Configuration**

24 Pin TSSOP 4.40 mm. Body, 0.65 mm. pitch

## **Pin Descriptions**

| PIN NUMBER   | PIN NAME | TYPE | DESCRIPTION                                                                                                                      |  |  |  |

|--------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1            | AGND     | PWR  | Analog Ground                                                                                                                    |  |  |  |

| 2, 10, 14    | VCC      | PWR  | Power Supply (3.3V)                                                                                                              |  |  |  |

| 3            | CLK0     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 4            | CLK1     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 5            | CLK2     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 6, 7, 18, 19 | GND      | PWR  | Ground                                                                                                                           |  |  |  |

| 8            | CLK3     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 9            | CLK4     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 11           | $OE^1$   | IN   | Output enable (has internal pull_up). When high, normal operation.<br>When low, clock outputs are disabled to a logic low state. |  |  |  |

| 12           | FBOUT    | OUT  | Feedback output                                                                                                                  |  |  |  |

| 13           | FBIN     | IN   | Feedback input                                                                                                                   |  |  |  |

| 15           | CLK5     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 16           | CLK6     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 17           | CLK7     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 20           | CLK8     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 21           | CLK9     | OUT  | Buffered clock output.                                                                                                           |  |  |  |

| 22           | VCC      | PWR  | Power Supply (3.3V) digital supply.                                                                                              |  |  |  |

| 23           | AVCC     | IN   | Analog power supply (3.3V). When input is ground PLL is off and bypassed.                                                        |  |  |  |

| 24           | CLKIN    | IN   | Clock input                                                                                                                      |  |  |  |

Note:

1. Weak pull-ups on these inputs

## Functionality

| INPUTS |             |           | PLL    |        |          |  |  |

|--------|-------------|-----------|--------|--------|----------|--|--|

| OE     | AVCC        | CLK (9:0) | FBOUT  | Source | Shutdown |  |  |

| 0      | 3.33        | 0         | Driven | PLL    | Ν        |  |  |

| 1      | 3.33        | Driven    | Driven | PLL    | N        |  |  |

|        | Buffer Mode |           |        |        |          |  |  |

| 0      | 0           | 0         | Driven | CLKIN  | Y        |  |  |

| 1      | 0           | Driven    | Driven | CLKIN  | Y        |  |  |

Test mode:

When AVCC is 0, shuts off the PLL and connects the input directly to the output buffers

## **Absolute Maximum Ratings**

| Supply Voltage (AVCC)         | $AVCC < (V_{cc} + 0.7V)$             |

|-------------------------------|--------------------------------------|

| Supply Voltage (VCC)          | 4.3 V                                |

| Logic Inputs                  | GND –0.5 V to V <sub>cc</sub> +0.5 V |

| Ambient Operating Temperature | 0°C to +70°C                         |

| Storage Temperature           | –65°C to +150°C                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| $T_A = 0 - 70^{\circ}C; V_{DD} = V_{DDL} = 3.3 V + -10\%; C_L = 20 - 30 pF; R_L = 470 Ohms (unless otherwise stated)$ |                              |                                                  |      |      |       |       |  |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------|------|------|-------|-------|--|

| PARAMETER                                                                                                             | SYMBOL                       | CONDITIONS                                       | MIN  | TYP  | MAX   | UNITS |  |

| Output Impedance                                                                                                      | R <sub>DSP</sub>             | $V_{\rm O} = V_{\rm DD}^{*}(0.5)$                |      | 36   |       | Ω     |  |

| Output Impedance                                                                                                      | R <sub>DSN</sub>             | $V_{\rm O} = V_{\rm DD}^{*}(0.5)$                |      | 32   |       | Ω     |  |

| Output High Voltage                                                                                                   |                              | I <sub>OH</sub> = -8 mA                          | 2.4  | 2.9  |       | V     |  |

| Output Low Voltage                                                                                                    | V <sub>OL</sub>              | $I_{OL} = 8 \text{ mA}$                          |      | 0.25 | 0.4   | V     |  |

| Output High Current                                                                                                   | 1                            | V <sub>OH</sub> = 2.4 V                          |      | -26  | -13.6 |       |  |

|                                                                                                                       | I <sub>OH</sub>              | V <sub>OH</sub> = 2.0 V                          |      | -37  | -22   | mA    |  |

| Output Low Current                                                                                                    | 1                            | $V_{OL} = 0.8 V$                                 | 19   | 25   |       | m۸    |  |

|                                                                                                                       | I <sub>OL</sub>              | V <sub>OL</sub> = 0.55 V                         | 13   | 17   |       | mA    |  |

| Rise Time <sup>1</sup>                                                                                                | Tr                           | V <sub>OL</sub> = 0.8 V, V <sub>OH</sub> = 2.0 V | 0.5  | 1.4  | 2.1   | ns    |  |

| Fall Time <sup>1</sup>                                                                                                | T <sub>f</sub>               | V <sub>OH</sub> = 2.0 V, V <sub>OL</sub> = 0.8 V | 0.5  | 1.5  | 2.7   | ns    |  |

| Duty Cycle <sup>1</sup>                                                                                               | Dt                           | V <sub>T</sub> = 1.5 V;C <sub>L</sub> =30 pF     | 45   | 50   | 55    | %     |  |

| Cuala ta Cuala iittar <sup>1</sup>                                                                                    | Тсус-сус                     | at 66-100 MHz ; loaded outputs                   |      | 52   | 100   | ne    |  |

| Cycle to Cycle jitter <sup>1</sup>                                                                                    | TCyC-CyC                     | at 133 MHz ; loaded outputs                      |      | 39   | 75    | ps    |  |

| Absolute Jitter <sup>1</sup>                                                                                          | Tjabs                        | 10000 cycles; C <sub>L</sub> = 30 pF             |      | 57   |       | ps    |  |

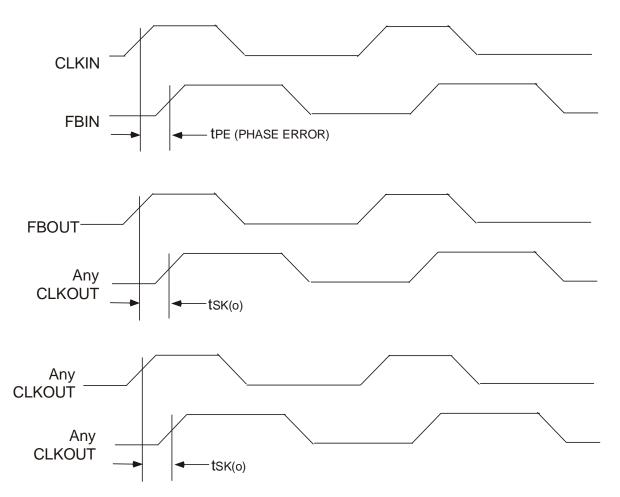

| Skew <sup>1</sup>                                                                                                     | T <sub>sk</sub>              | $V_T = 1.5 V$ (Window) Output to Output          |      | 80   | 150   | ps    |  |

| Phase error <sup>1</sup>                                                                                              | T <sub>pe</sub>              | V <sub>T</sub> = Vdd/2; CLKIN-FBIN               | -150 | 40   | 150   | ps    |  |

| Phase error Jitter <sup>1</sup>                                                                                       | T <sub>pe</sub> <sup>3</sup> | V <sub>T</sub> = Vdd/2; CLKIN-FBIN; Delay Jitter | -50  | 35   | 50    | ps    |  |

| Delay Input-Output <sup>1</sup>                                                                                       | D <sub>R1</sub>              | $V_{T} = 1.5 V; PLL_EN = 0$                      |      | 3.3  | 3.7   | ns    |  |

|                                                                                                                       |                              |                                                  |      |      |       |       |  |

## **Electrical Characteristics - OUTPUT**

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = V_{DDL} = 3.3 \text{ V} + -10\%$ ;  $C_L = 20 - 30 \text{ pF}$ ;  $R_L = 470 \text{ Ohms}$  (unless otherwise stated)

<sup>1</sup> Guaranteed by design, not 100% tested in production.

## **Electrical Characteristics - Input & Supply**

$T_A = 0 - 70^{\circ}$ C; Supply Voltage  $V_{DD} = 3.3 V + -10\%$  (unless otherwise stated)

| PARAMETER          | SYMBOL           | CONDITIONS                                   | MIN                   | TYP | MAX            | UNITS |

|--------------------|------------------|----------------------------------------------|-----------------------|-----|----------------|-------|

| Input High Voltage | V <sub>IH</sub>  |                                              | 2                     |     | $V_{DD} + 0.3$ | V     |

| Input Low Voltage  | V <sub>IL</sub>  |                                              | V <sub>SS</sub> - 0.3 |     | 0.8            | V     |

| Input High Current | IIH              | $V_{IN} = V_{DD}$                            |                       | 0.1 | 100            | uA    |

| Input Low Current  | I                | $V_{IN} = 0 V;$                              |                       | 19  | 50             | uA    |

| Operating current  | I <sub>DD1</sub> | C <sub>L</sub> = 0 pF; F <sub>IN</sub> @ 66M |                       | 140 | 170            | mA    |

| Input Capacitance  |                  | Logic Inputs                                 |                       | 4   |                | pF    |

| Output Capacitance | $C_0^1$          | Logic Outputs                                |                       | 8   |                | pF    |

<sup>1</sup>Guaranteed by design, not 100% tested in production.

# Timing requirements over recommended ranges of supply voltage and operating free-air temperature

| Symbol | Parameter          | Test Conditions | Min. | Max. | Unit |

|--------|--------------------|-----------------|------|------|------|

| Fclk   | Input clock        |                 | 25   | 175  | MHz  |

| FUK    | frequency          |                 | 25   | 175  |      |

|        | Input clock        |                 |      |      |      |

|        | frequency duty     |                 | 40   | 60   | %    |

|        | cycle              |                 |      |      |      |

|        | Stabilization time | After power up  |      | 1    | ms   |

Note: Time required for the PLL circuit to obtain phase lock of its feedback signal to its In order for phase lock to be obtained, a fixed-frequency, fixed-phase reference signal Until phase lock is obtained, the specifications for parameters given in the switching

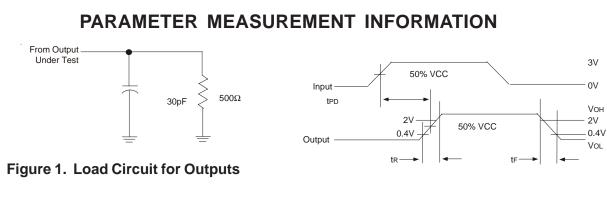

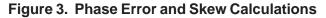

Figure 2. Voltage Waveforms

**Propagation Delay Times**

#### Notes:

- 1. C<sub>L</sub> includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq 133$  MHz,  $Z_0 = 50\Omega$ ,  $T_r \leq 1.2$  ns,  $T_f \leq 1.2$  ns.

- 3. The outputs are measured one at a time with one transition per measurement.

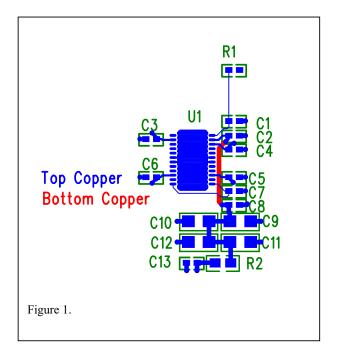

#### **General Layout Precautions:**

An ICS2509C is used as an example. It is similar to the ICS2510C. The same rules and methods apply.

- Use copper flooded ground on the top signal layer under the clock buffer The area under U1 in figure 1 on the right is an example. Every ground pin goes to a ground via. The vias are not visible in figure 1.

- Use power vias for power and ground. Vias 20 mil or larger in diameter have lower high frequency impedance. Vias for signals may be minimum drill size.

- 3) Make all power and ground traces are as wide as the via pad for lower inductance.

- 4) VAA for pin 23 has a low pass RC filter to decouple the digital and analog supplies. C9-12 may be replaced with a single low ESR (0.8 ohm or less) device with the same total capacitance. R2 may be replaced with a ferrite bead. The bead should have a DC resistance of at least 0.5 ohms. 1 ohm is better. It should have an impedance of at least 300 ohms at 100MHz. 600 ohms at 100MHz is better.

- 5) Notice that ground vias are never shared.

- 6) All VCC pins have a decoupling capacitor. Power is always routed from the plane connection via to the capacitor pad to the VCC pin on the clock buffer.

- 7) Component R1 is located at the clock source.

- 8) Component C1, if used, has the effect of adding delay.

- 9) Component C7, if used, has the effect of subtracting delay. Delaying the FBIn clock will cause the output clocks to be earlier. A more effective method is to use the propagation time of a trace between FBOut and FBIn.

#### Component Values:

C1,C7= As necessary for delay adjust C[6:2]=.01uF C8,C13=0.1uF C[12:9]=4.7Uf R1=10 ohm. Locate at driver R2=10 ohm.

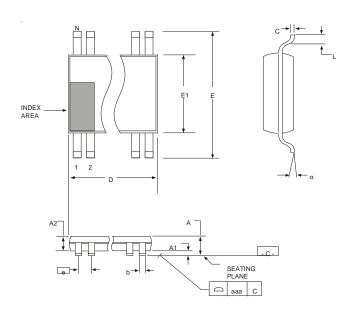

|        | In Millimeters |           | In Inches         |          |  |

|--------|----------------|-----------|-------------------|----------|--|

| SYMBOL | COMMON D       | IMENSIONS | COMMON DIMENSIONS |          |  |

|        | MIN            | MAX       | MIN               | MAX      |  |

| А      |                | 1.20      |                   | .047     |  |

| A1     | 0.05           | 0.15      | .002              | .006     |  |

| A2     | 0.80           | 1.05      | .032              | .041     |  |

| b      | 0.19           | 0.30      | .007              | .012     |  |

| С      | 0.09           | 0.20      | .0035             | .008     |  |

| D      | SEE VARIATIONS |           | SEE VARIATIONS    |          |  |

| Е      | 6.40           | BASIC     | 0.252 BASIC       |          |  |

| E1     | 4.30           | 4.50      | .169              | .177     |  |

| е      | 0.65           | BASIC     | 0.0256 BASIC      |          |  |

| L      | 0.45           | 0.75      | .018              | .030     |  |

| Ν      | SEE VARIATIONS |           | SEE VAF           | RIATIONS |  |

| α      | 0°             | 8°        | 0°                | 8°       |  |

| aaa    |                | 0.10      |                   | .004     |  |

VARIATIONS

| Ν  | D mm. |      | D (inch) |      |

|----|-------|------|----------|------|

|    | MIN   | MAX  | MIN      | MAX  |

| 24 | 7.70  | 7.90 | .303     | .311 |

Reference Doc.: JEDEC Publication 95, MO-153 10-0035

#### 4.40 mm. Body, 0.65 mm. pitch TSSOP (173 mil) (0.0256 lnch)

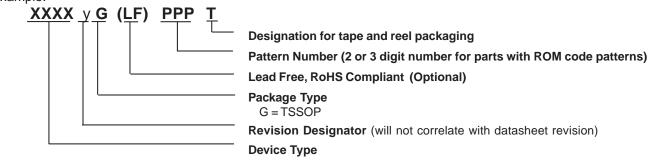

## **Ordering Information**

### 2510CGLFT

#### Example:

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Synthesizer/Jitter Cleaner category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

MPC9230EIR2 PL902166USY 954204CGLF 9LPRS485DGLF PL902167USY MAXREFDES161# 8V19N490ABDGI LMK04821NKDT CDCE937QPWRQ1 PI6CX201ALE 9LPRS355BGLF CDCEL913IPWRQ1 ABMJB-903-101UMG-T5 ABMJB-903-150UMG-T5 ABMJB-903-151UMG-T5 AD9542BCPZ AD9578BCPZ 9FG104EFILF 9FG104EFLF 308RILF 840001BGI-25LF 843004AGLF 843801AGI-24LF 844004BGI-01LF 844S42BKILF 8A34044C-000NLG 954226AGLF 9FG108EFLF 9LPR363EGLF 9LPRS355BKLF 9LPRS365BGLF MK2703BSILF GS4915-INE3 9DB306BLLF ABMJB-902-155USY-T5 ABMJB-902-156USY-T5 ABMJB-902-Q76USY-T5 ABMJB-902-Q82USY-T5 ABMJB-902-104USY-T5 ABMJB-902-153USY-T5 ABMJB-902-154USY-T5 ABMJB-902-Q42USY-T5 ABMJB-902-Q57USY-T5 ABMJB-902-Q74USY-T5 ABMJB-902-Q78USY-T5 LTC6951IUHF-1#PBF 650GI-44LF 8430252CGI-45LF 8432DYI-101LF 84329BYLF