## **Description**

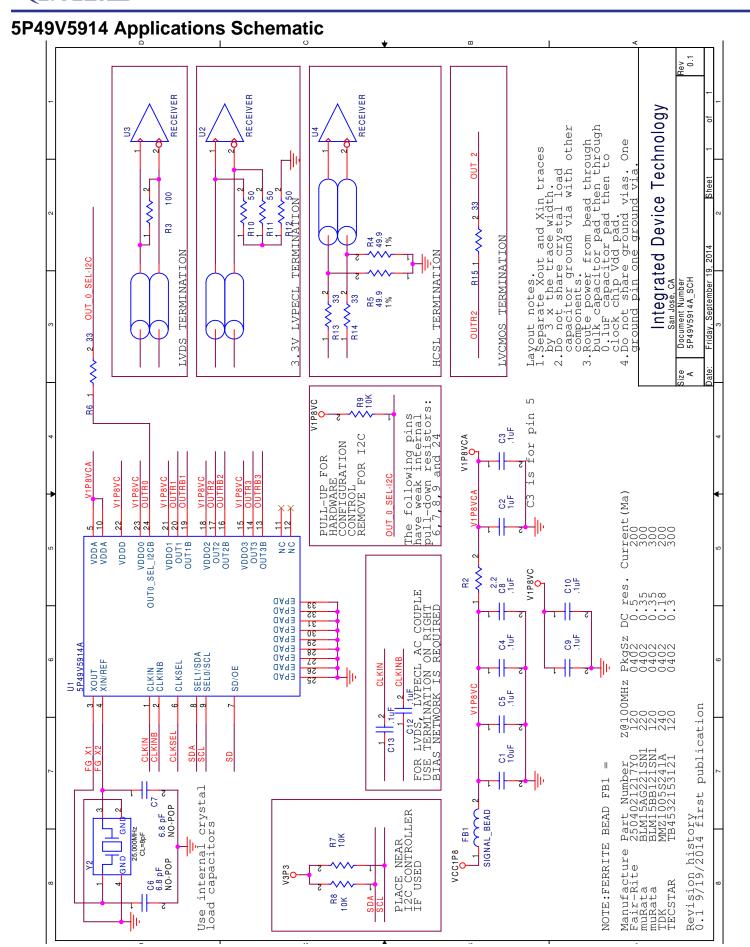

The 5P49V5914 is a programmable clock generator intended for high performance consumer, networking, industrial, computing, and data-communications applications. Configurations may be stored in on-chip One-Time Programmable (OTP) memory or changed using I<sup>2</sup>C interface. This is IDTs fifth generation of programmable clock technology (VersaClock® 5).

The frequencies are generated from a single reference clock. The reference clock can come from one of the two redundant clock inputs. A glitchless manual switchover function allows one of the redundant clocks to be selected during normal operation.

Two select pins allow up to 4 different configurations to be programmed and accessible using processor GPIOs or bootstrapping. The different selections may be used for different operating modes (full function, partial function, partial power-down), regional standards (US, Japan, Europe) or system production margin testing.

The device may be configured to use one of two I<sup>2</sup>C addresses to allow multiple devices to be used in a system.

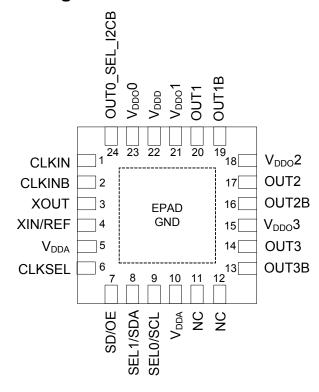

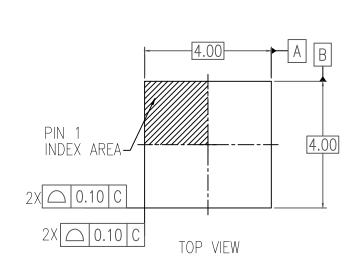

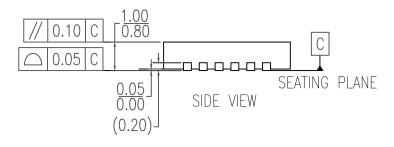

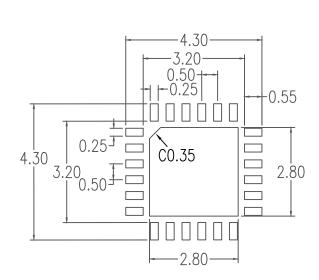

### **Pin Assignment**

24-pin VFQFPN

#### **Features**

- Generates up to three independent output frequencies

- High performance, low phase noise PLL, <0.7ps RMS</li> typical phase jitter on outputs:

- PCle Gen1, 2, 3 compliant clock capability

- USB 3.0 compliant clock capability

- 1GbE and 10GbE

- Three fractional output dividers (FODs)

- Independent Spread Spectrum capability on each output pair

- Four banks of internal non-volatile in-system programmable or factory programmable OTP memory

- I<sup>2</sup>C serial programming interface

- One reference LVCMOS output clock

- Three universal output pairs:

- Each configurable as one differential output pair or two LVCMOS outputs

- I/O Standards:

- Single-ended I/Os: 1.8V to 3.3V LVCMOS

- Differential I/Os: LVPECL, LVDS and HCSL

- Input frequency ranges:

- LVCMOS Reference Clock Input (XIN/REF) 1MHz to 200MHz

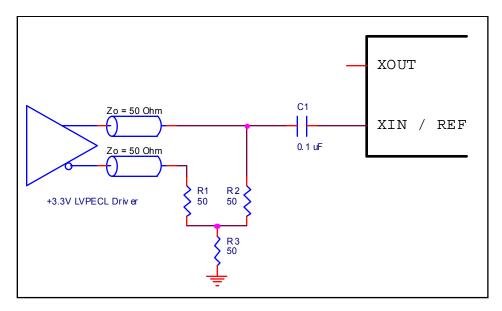

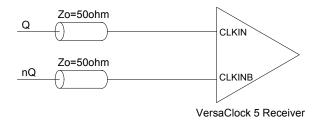

- LVDS, LVPECL, HCSL Differential Clock Input (CLKIN, CLKINB) - 1MHz to 350MHz

- Crystal frequency range: 8MHz to 40MHz

- Output frequency ranges:

- LVCMOS Clock Outputs 1MHz to 200MHz

- LVDS, LVPECL, HCSL Differential Clock Outputs -1MHz to 350MHz

- Individually selectable output voltage (1.8V, 2.5V, 3.3V) for each output pair

- Redundant clock inputs with manual switchover

- Programmable loop bandwidth

- Programmable slew rate control

- Programmable crystal load capacitance

- Individual output enable/disable

- Power-down mode

- 1.8V, 2.5V or 3.3V core V<sub>DDD</sub>, V<sub>DDA</sub>

- Available in 24-pin VFQFPN 4mm x 4mm package

- -40° to +85°C industrial temperature operation

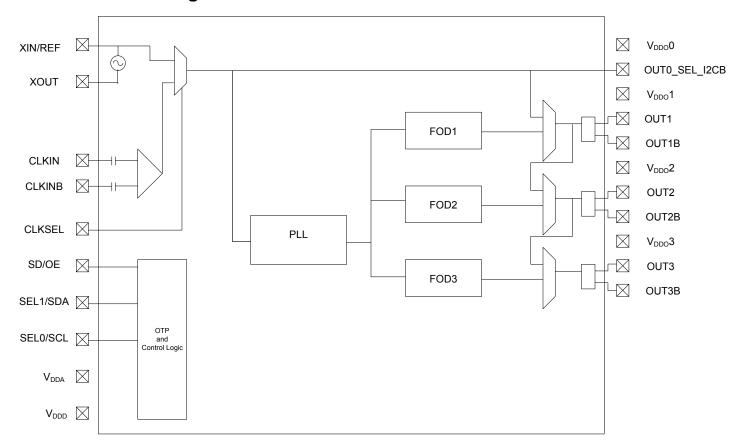

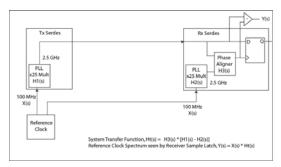

## **Functional Block Diagram**

## **Applications**

- Ethernet switch/router

- PCI Express 1.0/2.0/3.0

- Broadcast video/audio timing

- Multi-function printer

- Processor and FPGA clocking

- Any-frequency clock conversion

- MSAN/DSLAM/PON

- Fiber Channel, SAN

- Telecom line cards

- 1 GbE and 10 GbE

# **Table 1: Pin Descriptions**

| Number | Name               |        | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|--------------------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

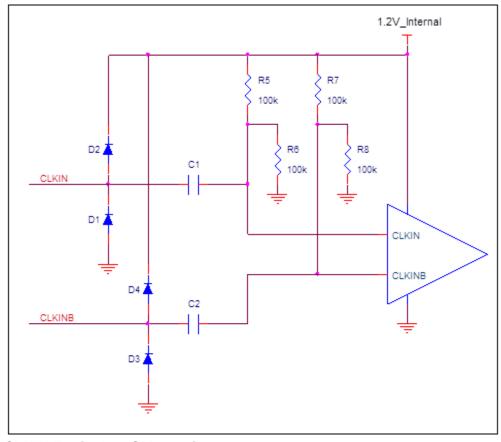

| 1      | CLKIN              | Input  | Internal<br>Pull-down | Differential clock input. Weak 100kohms internal pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2      | CLKINB             | Input  | Internal<br>Pull-down | Complementary differential clock input. Weak 100kohms internal pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3      | XOUT               | Input  |                       | Crystal Oscillator interface output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

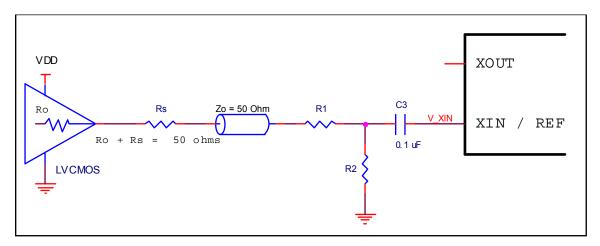

| 4      | XIN/REF            | Input  |                       | Crystal Oscillator interface input, or single-ended LVCMOS clock input. Ensure that the input voltage is 1.2V max.Refer to the section "Overdriving the XIN/REF Interface".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5      | $V_{DDA}$          | Power  |                       | Analog functions power supply pin.Connect to 1.8V to 3.3V. $V_{DDA}$ and $V_{DDD}$ should have the same voltage applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6      | CLKSEL             | Input  | Internal<br>Pull-down | Input clock select. Selects the active input reference source in manual switchover mode.  0 = XIN/REF, XOUT (default)  1 = CLKIN, CLKINB  CLKSEL Polarity can be changed by I2C programming as shown in Table 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7      | SD/OE              | Input  | Internal<br>Pull-down | Enables/disables the outputs (OE) or powers down the chip (SD). The SH bit controls the configuration of the SD/OE pin. The SH bit needs to be high for SD/OE pin to be configured as SD. The SP bit (0x02) controls the polarity of the signal to be either active HIGH or LOW only when pin is configured as OE (Default is active LOW.) Weak internal pull down resistor. When configured as SD, device is shut down, differential outputs are driven high/low, and the single-ended LVCMOS outputs are driven low. When configured as OE, and outputs are disabled, the outputs can be selected to be tri-stated or driven high/low, depending on the programming bits as shown in the SD/OE Pin Function Truth table. |

| 8      | SEL1/SDA           | Input  | Internal<br>Pull-down | Configuration select pin, or I <sup>2</sup> C SDA input as selected by OUT0_SEL_I2CB. Weak internal pull down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9      | SEL0/SCL           | Input  | Internal<br>Pull-down | Configuration select pin, or I <sup>2</sup> C SCL input as selected by OUT0_SEL_I2CB. Weak internal pull down resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10     | $V_{DDA}$          | Power  |                       | Analog functions power supply pin.Connect to 1.8V to 3.3V. $V_{DDA}$ and $V_{DDD}$ should have the same voltage applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11     | NC                 | _      | _                     | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12     | NC                 | _      | _                     | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13     | OUT3B              | Output |                       | Complementary Output Clock 3. Please refer to the Output Drivers section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14     | OUT3               | Output |                       | Output Clock 3. Please refer to the Output Drivers section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15     | V <sub>DDO</sub> 3 | Power  |                       | Output power supply. Connect to 1.8 to 3.3V. Sets output voltage levels for OUT3/OUT3B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16     | OUT2B              | Output |                       | Complementary Output Clock 2. Please refer to the Output Drivers section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17     | OUT2               | Output |                       | Output Clock 2. Please refer to the Output Drivers section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18     | V <sub>DDO</sub> 2 | Power  |                       | Output power supply. Connect to 1.8 to 3.3V. Sets output voltage levels for OUT2/OUT2B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19     | OUT1B              | Output |                       | Complementary Output Clock 1. Please refer to the Output Drivers section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20     | OUT1               | Output |                       | Output Clock 1. Please refer to the Output Drivers section for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 21     | V <sub>DDO</sub> 1 | Power  |                       | Output power supply. Connect to 1.8 to 3.3V. Sets output voltage levels for OUT1/OUT1B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 22     | $V_{DDD}$          | Power  |                       | Digital functions power supply pin. Connect to 1.8 to 3.3V. $\rm V_{DDA}$ and $\rm V_{DDD}$ should have the same voltage applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Number | Name               |                  | Туре                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|--------------------|------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23     | V <sub>DDO</sub> 0 | Power            |                       | Power supply pin for OUT0_SEL_I2CB. Connect to 1.8 to 3.3V. Sets output voltage levels for OUT0.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24     | OUT0_SEL_I2CB      | Input/<br>Output | Internal<br>Pull-down | Latched input/LVCMOS Output. At power up, the voltage at the pin OUT0_SEL_I2CB is latched by the part and used to select the state of pins 8 and 9. If a weak pull up (10kohms) is placed on OUT0_SEL_I2CB, pins 8 and 9 will be configured as hardware select pins, SEL1 and SEL0. If a weak pull down (10Kohms) is placed on OUT0_SEL_I2CB or it is left floating, pins 8 and 9 will act as the SDA and SCL pins of an I <sup>2</sup> C interface. After power up, the pin acts as a LVCMOS reference output. |

| ePAD   | GND                | GND              |                       | Connect to ground pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

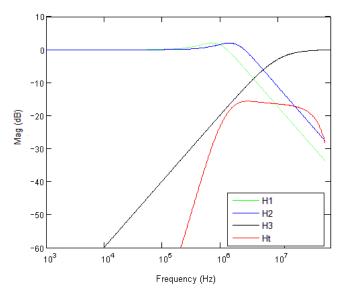

### **PLL Features and Descriptions**

#### **Spread Spectrum**

To help reduce electromagnetic interference (EMI), the 5P49V5914 supports spread spectrum modulation. The output clock frequencies can be modulated to spread energy across a broader range of frequencies, lowering system EMI. The 5P49V5914 implements spread spectrum using the Fractional-N output divide, to achieve controllable modulation rate and spreading magnitude. The Spread spectrum can be applied to any output clock, any clock frequency, and any spread amount from  $\pm 0.25\%$  to  $\pm 2.5\%$  center spread and -0.5% to -5% down spread.

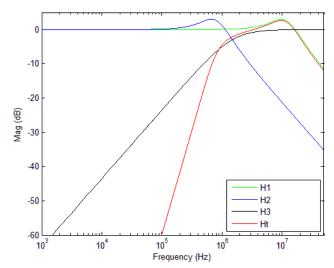

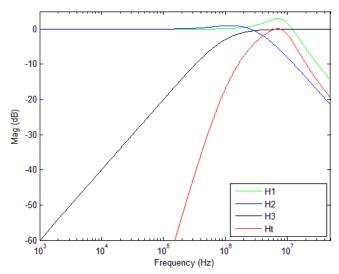

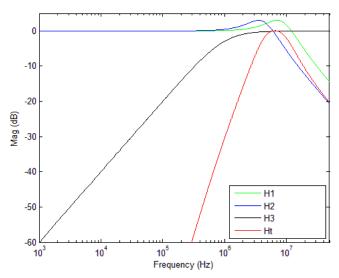

#### Table 2: Loop Filter

PLL loop bandwidth range depends on the input reference frequency (Fref) and can be set between the loop bandwidth range as shown in the table below.

| Input Reference<br>Frequency–Fref<br>(MHz) | Loop<br>Bandwidth<br>Min (kHz) | Loop<br>Bandwidth<br>Max (kHz) |

|--------------------------------------------|--------------------------------|--------------------------------|

| 5                                          | 40                             | 126                            |

| 350                                        | 300                            | 1000                           |

#### **Table 3: Configuration Table**

This table shows the SEL1, SEL0 settings to select the configuration stored in OTP. Four configurations can be stored in OTP. These can be factory programmed or user programmed.

| OUT0_SEL_I2CB<br>@ POR | SEL1 | SEL0 | I <sup>2</sup> C<br>Access | REG0:7 | Config          |

|------------------------|------|------|----------------------------|--------|-----------------|

| 1                      | 0    | 0    | No                         | 0      | 0               |

| 1                      | 0    | 1    | No                         | 0      | 1               |

| 1                      | 1    | 0    | No                         | 0      | 2               |

| 1                      | 1    | 1    | No                         | 0      | 3               |

| 0                      | Х    | Х    | Yes                        | 1      | I2C<br>defaults |

| 0                      | Х    | Х    | Yes                        | 0      | 0               |

At power up time, the SEL0 and SEL1 pins must be tied to either the VDDD/VDDA power supply so that they ramp with that supply or are tied low (this is the same as floating the pins). This will cause the register configuration to be loaded that is selected according to Table 3 above. Providing that OUT0\_SEL\_I2CB was 1 at POR and OTP register 0:7=0, after the first 10mS of operation the levels of the SELx pins can be changed, either to low or to the same level as VDDD/VDDA. The SELx pins must be driven with a digital signal of < 300ns Rise/Fall time and only a single pin can be changed at a time. After a pin level change, the device must not be interrupted for at least 1ms so that the new values have time to load and take effect.

If OUT0\_SEL\_I2CB was 0 at POR, alternate configurations can only be loaded via the I2C interface.

#### **Table 4: Input Clock Select**

Input clock select. Selects the active input reference source in manual switchover mode.

0 = XIN/REF, XOUT (default)

1 = CLKIN, CLKINB

CLKSEL Polarity can be changed by I<sup>2</sup>C programming as shown in Table 4.

| PRIMSRC | CLKSEL | Source        |

|---------|--------|---------------|

| 0       | 0      | XIN/REF       |

| 0       | 1      | CLKIN, CLKINB |

| 1       | 0      | CLKIN, CLKINB |

| 1       | 1      | XIN/REF       |

PRIMSRC is bit 1 of Register 0x13.

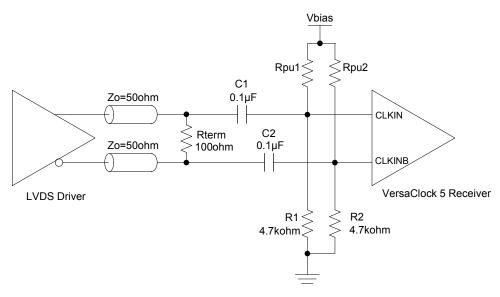

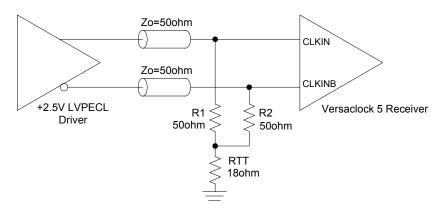

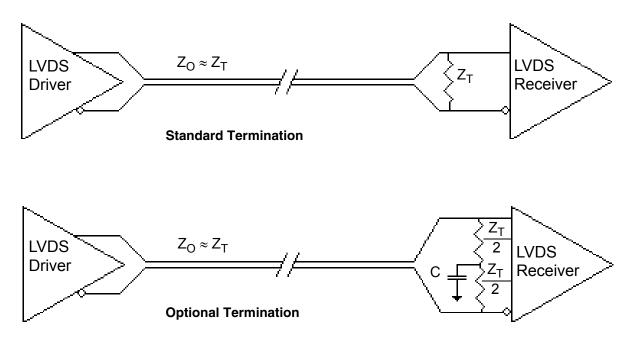

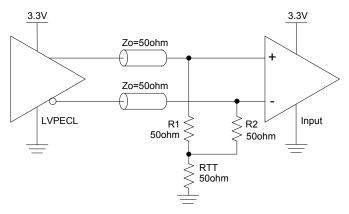

# Reference Clock Input Pins and Selection

The 5P49V5914 supports up to two clock inputs. One input supports a crystal between XIN and XOUT. XIN can also be driven from a single ended reference clock. XIN can accept small amplitude signals like from TCXO or one channel of a differential clock.

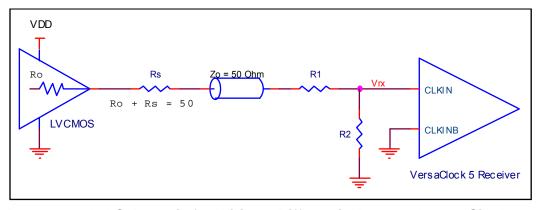

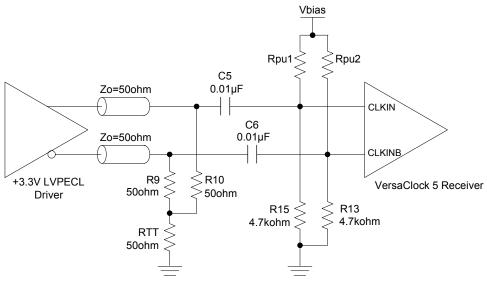

The second clock input (CLKIN, CLKINB) is a fully differential input that only accepts a reference clock. The differential input accepts differential clocks from all the differential logic types and can also be driven from a single ended clock on one of the input pins.

The CLKSEL pin selects the input clock between either XTAL/REF or (CLKIN, CLKINB).

Either clock input can be set as the primary clock. The primary clock designation is to establish which is the main reference clock to the PLL. The non-primary clock is designated as the secondary clock in case the primary clock goes absent and a backup is needed. See the previous page for more details about primary versus secondary clock operation.

The two external reference clocks can be manually selected using the CLKSEL pin. The SM bits must be set to "0x" for manual switchover which is detailed in Manual Switchover Mode section.

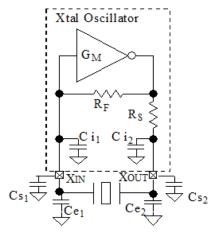

#### **Crystal Input (XIN/REF)**

The crystal used should be a fundamental mode quartz crystal; overtone crystals should not be used.

A crystal manufacturer will calibrate its crystals to the nominal frequency with a certain load capacitance value. When the oscillator load capacitance matches the crystal load capacitance, the oscillation frequency will be accurate. When the oscillator load capacitance is lower than the crystal load capacitance, the oscillation frequency will be higher than nominal and vice versa so for an accurate oscillation frequency you need to make sure to match the oscillator load capacitance with the crystal load capacitance.

To set the oscillator load capacitance there are two tuning capacitors in the IC, one at XIN and one at XOUT. They can be adjusted independently but commonly the same value is used for both capacitors. The value of each capacitor is composed of a fixed capacitance amount plus a variable capacitance amount set with the XTAL[5:0] register. Adjustment of the crystal tuning capacitors allows for maximum flexibility to accommodate crystals from various manufacturers. The range of tuning capacitor values available are in accordance with the following table.

#### XTAL[5:0] Tuning Capacitor Characteristics

| Parameter | Bits | Step (pF) | Min (pF) | Max (pF) |

|-----------|------|-----------|----------|----------|

| XTAL      | 6    | 0.5       | 9        | 25       |

The capacitance at each crystal pin inside the chip starts at 9pF with setting 000000b and can be increased up to 25pF with setting 111111b. The step per bit is 0.5pF.

You can write the following equation for this capacitance:

$$Ci = 9pF + 0.5pF \times XTAL[5:0]$$

The PCB where the IC and the crystal will be assembled adds some stray capacitance to each crystal pin and more capacitance can be added to each crystal pin with additional external capacitors.

You can write the following equations for the total capacitance at each crystal pin:

$$C_{XIN} = Ci_1 + Cs_1 + Ce_1$$

$C_{XOUT} = Ci_2 + Cs_2 + Ce_2$

Ci<sub>1</sub> and Ci<sub>2</sub> are the internal, tunable capacitors. Cs<sub>1</sub> and Cs<sub>2</sub> are stray capacitances at each crystal pin and typical values are between 1pF and 3pF.

${\rm Ce_1}$  and  ${\rm Ce_2}$  are additional external capacitors that can be added to increase the crystal load capacitance beyond the tuning range of the internal capacitors. However, increasing the load capacitance reduces the oscillator gain so please consult the factory when adding  ${\rm Ce_1}$  and/or  ${\rm Ce_2}$  to avoid crystal startup issues.  ${\rm Ce_1}$  and  ${\rm Ce_2}$  can also be used to adjust for unpredictable stray capacitance in the PCB.

The final load capacitance of the crystal:

$$CL = C_{XIN} \times C_{XOUT} / (C_{XIN} + C_{XOUT})$$

For most cases it is recommended to set the value for capacitors the same at each crystal pin:

$$C_{XIN} = C_{XOUT} = Cx \rightarrow CL = Cx / 2$$

The complete formula when the capacitance at both crystal pins is the same:

$$CL = (9pF + 0.5pF \times XTAL[5:0] + Cs + Ce) / 2$$

**Example 1**: The crystal load capacitance is specified as 8pF and the stray capacitance at each crystal pin is Cs=1.5pF. Assuming equal capacitance value at XIN and XOUT, the equation is as follows:

```

8pF = (9pF + 0.5pF \times XTAL[5:0] + 1.5pF) / 2 \rightarrow 0.5pF \times XTAL[5:0] = 5.5pF \rightarrow XTAL[5:0] = 11 (decimal)

```

**Example 2**: The crystal load capacitance is specified as 12pF and the stray capacitance Cs is unknown. Footprints for external capacitors Ce are added and a worst case Cs of 5pF is used. For now we use Cs + Ce = 5pF and the right value for Ce can be determined later to make 5pF together with Cs.

12pF =

$$(9pF + 0.5pF \times XTAL[5:0] + 5pF) / 2 \rightarrow XTAL[5:0] = 20 (decimal)$$

#### **Manual Switchover Mode**

When SM[1:0] is "0x", the redundant inputs are in manual switchover mode. In this mode, CLKSEL pin is used to switch between the primary and secondary clock sources. The primary and secondary clock source setting is determined by the PRIMSRC bit. During the switchover, no glitches will occur at the output of the device, although there may be frequency and phase drift, depending on the exact phase and frequency relationship between the primary and secondary clocks.

#### **OTP Interface**

The 5P49V5914 can also store its configuration in an internal OTP. The contents of the device's internal programming registers can be saved to the OTP by setting burn\_start (W114[3]) to high and can be loaded back to the internal programming registers by setting usr\_rd\_start(W114[0]) to high.

To initiate a save or restore using I<sup>2</sup>C, only two bytes are transferred. The Device Address is issued with the read/write bit set to "0", followed by the appropriate command code. The save or restore instruction executes after the STOP condition is issued by the Master, during which time the 5P49V5914 will not generate Acknowledge bits. The 5P49V5914 will acknowledge the instructions after it has completed execution of them. During that time, the I<sup>2</sup>C bus should be interpreted as busy by all other users of the bus.

On power-up of the 5P49V5914, an automatic restore is performed to load the OTP contents into the internal programming registers. The 5P49V5914 will be ready to accept a programming instruction once it acknowledges its 7-bit I<sup>2</sup>C address.

Availability of Primary and Secondary I<sup>2</sup>C addresses to allow programming for multiple devices in a system. The I<sup>2</sup>C slave address can be changed from the default 0xD4 to 0xD0 by programming the I2C\_ADDR bit D0. *VersaClock 5 Programming Guide* provides detailed I<sup>2</sup>C programming guidelines and register map.

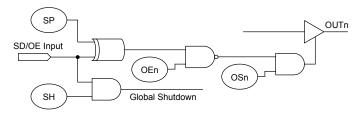

#### **SD/OE Pin Function**

The polarity of the SD/OE signal pin can be programmed to be either active HIGH or LOW with the SP bit (W16[1]). When SP is "0" (default), the pin becomes active LOW and when SP is "1", the pin becomes active HIGH. The SD/OE pin can be configured as either to shutdown the PLL or to enable/disable the outputs. The SH bit controls the configuration of the SD/OE pin The SH bit needs to be high for SD/OE pin to be configured as SD.

When configured as SD, device is shut down, differential outputs are driven High/low, and the single-ended LVCMOS outputs are driven low. When configured as OE, and outputs are disabled, the outputs are driven high/low.

Table 5: SD/OE Pin Function Truth Table

| SH bit | SP bit | OSn bit | OEn bit | SD/OE | OUTn                     |

|--------|--------|---------|---------|-------|--------------------------|

| 0      | 0      | 0       | Х       | х     | Tri-state <sup>2</sup>   |

| 0      | 0      | 1       | 0       | Х     | Output active            |

| 0      | 0      | 1       | 1       | 0     | Output active            |

| 0      | 0      | 1       | 1       | 1     | Output driven High Low   |

| 0      | 1      | 0       | Х       | х     | Tri-state <sup>2</sup>   |

| 0      | 1      | 1       | 0       | Х     | Output active            |

| 0      | 1      | 1       | 1       | 0     | Output driven High Low   |

| 0      | 1      | 1       | 1       | 1     | Output active            |

| 1      | 0      | 0       | Х       | 0     | Tri-state <sup>2</sup>   |

| 1      | 0      | 1       | 0       | 0     | Output active            |

| 1      | 0      | 1       | 1       | 0     | Output active            |

| 1      | 1      | 0       | Х       | 0     | Tri-state <sup>2</sup>   |

| 1      | 1      | 1       | 0       | 0     | Output active            |

| 1      | 1      | 1       | 1       | 0     | Output driven High Low   |

| 1      | Х      | х       | Х       | 1     | Output driven High Low 1 |

Note 1 : Global Shutdown

Note 2: Tri-state regardless of OEn bits

#### **Output Alignment**

Each output divider block has a synchronizing POR pulse to provide startup alignment between outputs. This allows alignment of outputs for low skew performance. The phase alignment works both for integer output divider values and for fractional output divider values.

Besides the POR at power up, the same synchronization reset is also triggered when switching between configurations with the SEL0/1 pins. This ensures that the outputs remain aligned in every configuration. This reset causes the outputs to suspend for a few hundred microseconds so the switchover is not glitch-less. The reset can be disabled for applications where glitch-less switch over is required and alignment is not critical.

When using  $I^2C$  to reprogram an output divider during operation, alignment can be lost. Alignment can be restored by manually triggering the reset through  $I^2C$ .

When alignment is required for outputs with different frequencies, the outputs are actually aligned on the falling edges of each output by default. Rising edge alignment can also be achieved by utilizing the programmable skew feature to delay the faster clock by 180 degrees. The programmable skew feature also allows for fine tuning of the alignment.

For details of register programming, please see <u>VersaClock 5</u> <u>Family Register Descriptions and Programming Guide</u> for details.

#### **Output Divides**

Each of the four output divides are comprised of a 12-bit integer counter, and a 24-bit fractional counter. The output divide can operate in integer divide only mode for improved performance, or utilize the fractional counters to generate any frequency with a synthesis accuracy better than 50ppb.

The Output Divide also has the capability to apply a spread modulation to the output frequency. Independent of output frequency, a triangle wave modulation between 30 and 63kHz may be generated.

#### **Output Skew**

For outputs that share a common output divide value, there will be the ability to skew outputs by quadrature values to minimize interaction on the PCB. The skew on each output can be adjusted from 0 to 360 degrees. Skew is adjusted in units equal to 1/32 of the VCO period. So, for 100 MHz output and a 2800 MHz VCO, you can select how many 11.161pS units you want added to your skew (resulting in units of 0.402 degrees). For example, 0, 0.402, 0.804, 1.206, 1.408, and so on. The granularity of the skew adjustment is always dependent on the VCO period and the output period.

#### **Output Drivers**

The LVCMOS clock outputs are provided with register-controlled output drivers. By selecting the output drive type in the appropriate register, any of these outputs can support LVCMOS logic levels

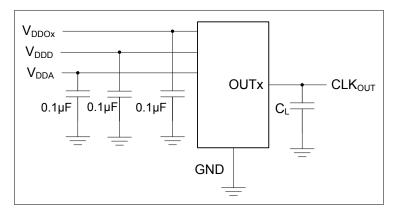

The operating voltage ranges of each output is determined by its independent output power pin ( $V_{DDO}$ ) and thus each can have different output voltage levels. Output voltage levels of 2.5V or 3.3V are supported for differential HCSL, LVPECL operation, and 1. 8V, 2.5V, or 3.3V are supported for LVCMOS and differential LVDS operation.

Each output may be enabled or disabled by register bits. When disabled an output will be in a logic 0 state as determined by the programming bit table shown on page 6.

#### **LVCMOS Operation**

When a given output is configured to provide LVCMOS levels, then both the OUTx and OUTxB outputs will toggle at the selected output frequency. All the previously described configuration and control apply equally to both outputs. Frequency, phase alignment, voltage levels and enable / disable status apply to both the OUTx and OUTxB pins. The OUTx and OUTxB outputs can be selected to be phase-aligned with each other or inverted relative to one another by register programming bits. Selection of phase-alignment may have negative effects on the phase noise performance of any part of the device due to increased simultaneous switching noise within the device.

### **Device Hardware Configuration**

The 5P49V5914 supports an internal One-Time Programmable (OTP) memory that can be pre-programmed at the factory with up to 4 complete device configuration.

These configurations can be over-written using the serial interface once reset is complete. Any configuration written via the programming interface needs to be re-written after any power cycle or reset. Please contact IDT if a specific factory-programmed configuration is desired.

#### **Device Start-up & Reset Behavior**

The 5P49V5914 has an internal power-up reset (POR) circuit. The POR circuit will remain active for a maximum of 10ms after device power-up.

Upon internal POR circuit expiring, the device will exit reset and begin self-configuration.

The device will load internal registers according to Table 3.

Once the full configuration has been loaded, the device will respond to accesses on the serial port and will attempt to lock the PLL to the selected source and begin operation.

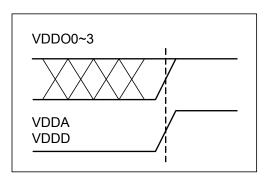

### **Power Up Ramp Sequence**

VDDA and VDDD must ramp up together. VDDO0~3 must ramp up before, or concurrently with, VDDA and VDDD. All power supply pins must be connected to a power rail even if the output is unused. All power supplies must ramp in a linear fashion and ramp monotonically.

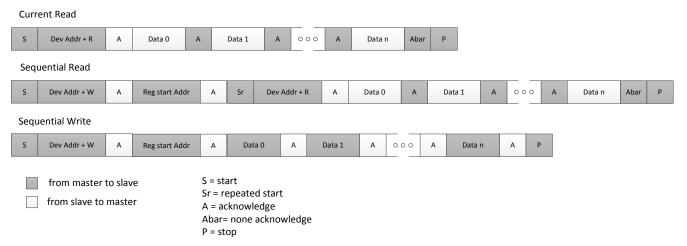

# I<sup>2</sup>C Mode Operation

The device acts as a slave device on the  $I^2C$  bus using one of the two  $I^2C$  addresses (0xD0 or 0xD4) to allow multiple devices to be used in the system. The interface accepts byte-oriented block write and block read operations. Two address bytes specify the register address of the byte position of the first register to write or read. Data bytes (registers) are accessed in sequential order from the lowest to the highest byte (most significant bit first). Read and write block transfers can be stopped after any complete byte transfer. During a write operation, data will not be moved into the registers until the STOP bit is received, at which point, all data received in the block write will be written simultaneously.

For full electrical I<sup>2</sup>C compliance, it is recommended to use external pull-up resistors for SDATA and SCLK. The internal pull-down resistors have a size of  $100k\Omega$  typical.

I<sup>2</sup>C Slave Read and Write Cycle Sequencing

# Table 6: I<sup>2</sup>C Bus DC Characteristics

| Symbol           | Parameter             | Conditions                         | Min                   | Тур | Max                  | Unit |

|------------------|-----------------------|------------------------------------|-----------------------|-----|----------------------|------|

| $V_{IH}$         | Input HIGH Level      | For SEL1/SDA pin and SEL0/SCL pin. | 0.7xV <sub>DDD</sub>  |     | 5.5 <sup>2</sup>     | V    |

| V <sub>IL</sub>  | Input LOW Level       | For SEL1/SDA pin and SEL0/SCL pin. | GND-0.3               |     | 0.3xV <sub>DDD</sub> | V    |

| V <sub>HYS</sub> | Hysteresis of Inputs  |                                    | 0.05xV <sub>DDD</sub> |     |                      | V    |

| I <sub>IN</sub>  | Input Leakage Current |                                    | -1                    |     | 30                   | μΑ   |

| V <sub>OL</sub>  | Output LOW Voltage    | I <sub>OL</sub> = 3 mA             |                       |     | 0.4                  | V    |

# Table 7: I<sup>2</sup>C Bus AC Characteristics

| Symbol                | Parameter                                | Min                     | Тур | Max | Unit |

|-----------------------|------------------------------------------|-------------------------|-----|-----|------|

| F <sub>SCLK</sub>     | Serial Clock Frequency (SCL)             | 10                      |     | 400 | kHz  |

| t <sub>BUF</sub>      | Bus free time between STOP and START     | 1.3                     |     |     | μs   |

| t <sub>SU:START</sub> | Setup Time, START                        | 0.6                     |     |     | μs   |

| t <sub>HD:START</sub> | Hold Time, START                         | 0.6                     |     |     | μs   |

| t <sub>SU:DATA</sub>  | Setup Time, data input (SDA)             | 0.1                     |     |     | μs   |

| t <sub>HD:DATA</sub>  | Hold Time, data input (SDA) <sup>1</sup> | 0                       |     |     | μs   |

| t <sub>OVD</sub>      | Output data valid from clock             |                         |     | 0.9 | μs   |

| C <sub>B</sub>        | Capacitive Load for Each Bus Line        |                         |     | 400 | pF   |

| t <sub>R</sub>        | Rise Time, data and clock (SDA, SCL)     | 20 + 0.1xC <sub>B</sub> |     | 300 | ns   |

| t <sub>F</sub>        | Fall Time, data and clock (SDA, SCL)     | 20 + 0.1xC <sub>B</sub> |     | 300 | ns   |

| t <sub>HIGH</sub>     | HIGH Time, clock (SCL)                   | 0.6                     |     |     | μs   |

| t <sub>LOW</sub>      | LOW Time, clock (SCL)                    | 1.3                     |     |     | μs   |

| t <sub>SU:STOP</sub>  | Setup Time, STOP                         | 0.6                     |     |     | μs   |

Note 1: A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the  $V_{IH}(MIN)$  of the SCL signal) to bridge the undefined region of the falling edge of SCL.

Note 2: I2C inputs are 5V tolerant.

### **Table 8: Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 5P49V5914. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                                                 | Rating                                                                                         |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Supply Voltage, V <sub>DDA,</sub> V <sub>DDD,</sub> V <sub>DDO</sub> | 3.465V                                                                                         |

| Inputs XIN/REF CLKIN, CLKINB Other inputs                            | 0V to 1.2V voltage swing<br>0V to 1.2V voltage swing single-ended<br>-0.5V to V <sub>DDD</sub> |

| Outputs, V <sub>DDO</sub> (LVCMOS)                                   | -0.5V to V <sub>DDO</sub> + 0.5V                                                               |

| Outputs, I <sub>O</sub> (SDA)                                        | 10mA                                                                                           |

| Package Thermal Impedance, $\theta_{JA}$                             | 42°C/W (0 mps)                                                                                 |

| Package Thermal Impedance, $\theta_{JC}$                             | 41.8°C/W (0 mps)                                                                               |

| Storage Temperature, T <sub>STG</sub>                                | -65°C to 150°C                                                                                 |

| ESD Human Body Model                                                 | 2000V                                                                                          |

| Junction Temperature                                                 | 125°C                                                                                          |

# **Table 9: Recommended Operation Conditions**

| Symbol                | Parameter                                                                                                  | Min   | Тур | Max   | Unit     |

|-----------------------|------------------------------------------------------------------------------------------------------------|-------|-----|-------|----------|

| V <sub>DDOX</sub>     | Power supply voltage for supporting 1.8V outputs                                                           | 1.71  | 1.8 | 1.89  | V        |

| $V_{DDOX}$            | Power supply voltage for supporting 2.5V outputs                                                           | 2.375 | 2.5 | 2.625 | V        |

| V <sub>DDOX</sub>     | Power supply voltage for supporting 3.3V outputs                                                           | 3.135 | 3.3 | 3.465 | V        |

| $V_{DDD}$             | Power supply voltage for core logic functions                                                              | 1.71  |     | 3.465 | <b>\</b> |

| $V_{DDA}$             | Analog power supply voltage. Use filtered analog power supply.                                             | 1.71  |     | 3.465 | V        |

| T <sub>A</sub>        | Operating temperature, ambient                                                                             | -40   |     | +85   | °C       |

| C <sub>LOAD_OUT</sub> | Maximum load capacitance (3.3V LVCMOS only)                                                                |       |     | 15    | pF       |

| F <sub>IN</sub>       | External reference crystal                                                                                 | 1     |     | 40    | MHz      |

|                       | External reference clock CLKIN, CLKINB                                                                     | 5     |     | 350   |          |

| t <sub>PU</sub>       | Power up time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps must be monotonic) | 0.05  |     | 5     | ms       |

Note:  $V_{DDO}1$ ,  $V_{DDO}2$ , and  $V_{DDO}3$ , must be powered on either before or simultaneously with  $V_{DDD}$ ,  $V_{DDA}$  and  $V_{DDO}0$ .

# Table 10:Input Capacitance, LVCMOS Output Impedance, and Internal Pull-down Resistance $(\mathsf{T_A}$ = +25 $^{\circ}\mathrm{C})$

| Symbol                | Parameter                                                            | Min | Тур | Max | Unit |

|-----------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| C <sub>IN</sub>       | Input Capacitance (CLKIN, CLKINB, CLKSEL, SD/OE, SEL1/SDA, SEL0/SCL) |     | 3   | 7   | pF   |

| Pull-down<br>Resistor | CLKSEL, SD/OE, SEL1/SDA, SEL0/SCL, CLKIN, CLKINB, OUT0_SEL_I2CB      | 100 |     | 300 | kΩ   |

| R <sub>OUT</sub>      | LVCMOS Output Driver Impedance (V <sub>DDO</sub> = 1.8V, 2.5V, 3.3V) |     | 17  |     | Ω    |

| XIN/REF               | Programmable input capacitance at XIN/REF                            | 0   |     | 8   | pF   |

| XOUT                  | Programmable input capacitance at XOUT                               | 0   |     | 8   | pF   |

# **Table 11:Crystal Characteristics**

| Parameter                          | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------------------------|-----------------|---------|---------|---------|-------|

| Mode of Oscillation                |                 | F       | ĺ       |         |       |

| Frequency                          |                 | 8       | 25      | 40      | MHz   |

| Equivalent Series Resistance (ESR) |                 |         | 10      | 100     | Ω     |

| Shunt Capacitance                  |                 |         |         | 7       | pF    |

| Load Capacitance (CL) @ <=25 MHz   |                 | 6       | 8       | 12      | pF    |

| Load Capacitance (CL) >25M to 40M  |                 | 6       |         | 8       | pF    |

| Maximum Crystal Drive Level        |                 |         |         | 100     | μW    |

Note: Typical crystal used is <u>FOX 603-25-150</u>. For different reference crystal options please go to <u>www.foxonline.com</u>.

### **Table 12:DC Electrical Characteristics**

| Symbol               | Parameter                    | Test Conditions                            | Min | Тур | Max | Unit |

|----------------------|------------------------------|--------------------------------------------|-----|-----|-----|------|

| Iddcore <sup>3</sup> | Core Supply Current          | 100 MHz on all outputs, 25 MHz             |     |     |     |      |

| iducole              | Core Supply Current          | REFCLK                                     |     | 30  | 34  | mA   |

|                      |                              | LVPECL, 350 MHz, 3.3V VDDOx                |     | 42  | 47  | mA   |

|                      |                              | LVPECL, 350 MHz, 2.5V VDDOx                |     | 37  | 42  | mA   |

|                      |                              | LVDS, 350 MHz, 3.3V VDDOx                  |     | 18  | 21  | mA   |

|                      |                              | LVDS, 350 MHz, 2.5V VDDOx                  |     | 17  | 20  | mA   |

|                      |                              | LVDS, 350 MHz, 1.8V VDDOx                  |     | 16  | 19  | mA   |

|                      |                              | HCSL, 250 MHz, 3.3V VDDOx, 2 pF load       |     | 29  | 33  | mA   |

| lddox                | Output Buffer Supply Current | HCSL, 250 MHz, 2.5V VDDOx, 2 pF load       |     | 28  | 33  | mA   |

|                      |                              | LVCMOS, 50 MHz, 3.3V, VDDOx 1,2            |     | 16  | 18  | mA   |

|                      |                              | LVCMOS, 50 MHz, 2.5V, VDDOx 1,2            |     | 14  | 16  | mA   |

|                      |                              | LVCMOS, 50 MHz, 1.8V, VDDOx 1,2            |     | 12  | 13  | mA   |

|                      |                              | LVCMOS, 200 MHz, 3.3V VDDOx <sup>1</sup>   |     | 36  | 42  | mA   |

|                      |                              | LVCMOS, 200 MHz, 2.5V VDDOx <sup>1,2</sup> |     | 27  | 32  | mA   |

|                      |                              | LVCMOS, 200 MHz, 1.8V VDDOx <sup>1,2</sup> |     | 16  | 19  | mA   |

| lddpd                | Power Down Current           | SD asserted, I2C Programming               |     | 10  | 14  | mA   |

<sup>1.</sup> Single CMOS driver active.

<sup>2.</sup> Measured into a 5" 50 Ohm trace with 2 pF load.

<sup>3.</sup> Iddcore = IddA+ IddD, no loads.

# Table 13:Electrical Characteristics – Differential Clock Input Parameters $^{1,2}$ (Supply Voltage $V_{DDA}, V_{DDD}, V_{DDO}0$ = 3.3V ±5%, 2.5V ±5%, 1.8V ±5%, TA = -40°C to +85°C)

| Symbol             | Parameter                        | Test Conditions                        | Min       | Тур | Max  | Unit |

|--------------------|----------------------------------|----------------------------------------|-----------|-----|------|------|

| V <sub>IH</sub>    | Input HIGH Voltage-CLKIN, CLKINB | Single-ended input                     | 0.55      |     | 1.7  | V    |

| V <sub>IL</sub>    | Input LOW Voltage-CLKIN, CLKINB  | Single-ended input                     | GND - 0.3 |     | 0.4  | V    |

| V <sub>SWING</sub> | Input Amplitude - CLKIN, CLKINB  | Peak to Peak value, single-ended       | 200       |     | 1200 | mV   |

| dv/dt              | Input Slew Rate - CLKIN, CLKINB  | Measured differentially                | 0.4       |     | 8    | V/ns |

| I <sub>IL</sub>    | Input Leakage Low Current        | V <sub>IN</sub> = GND                  | -5        |     | 5    | μΑ   |

| I <sub>IH</sub>    | Input Leakage High Current       | V <sub>IN</sub> = 1.7V                 |           |     | 20   | μA   |

| d <sub>TIN</sub>   | Input Duty Cycle                 | Measurement from differential waveform | 45        |     | 55   | %    |

<sup>1.</sup> Guaranteed by design and characterization, not 100% tested in production.

# Table 14:DC Electrical Characteristics for 3.3V LVCMOS ( $V_{DDO} = 3.3V \pm 5\%$ , TA = -40°C to +85°C) <sup>1</sup>

| Symbol | Parameter                       | Test Conditions                     | Min       | Тур | Max         | Unit |

|--------|---------------------------------|-------------------------------------|-----------|-----|-------------|------|

| VOH    | Output HIGH Voltage             | IOH = -15mA                         | 2.4       |     | VDDO        | V    |

| VOL    | Output LOW Voltage              | IOL = 15mA                          |           |     | 0.4         | V    |

| IOZDD  | Output Leakage Current (OUT1~3) | Tri-state outputs, VDDO = 3.465V    |           |     | 5           | μΑ   |

| IOZDD  | Output Leakage Current (OUT0)   | Tri-state outputs, VDDO = 2.625V    |           |     | 30          | μA   |

| VIH    | Input HIGH Voltage              | Single-ended inputs - CLKSEL, SD/OE | 0.7xVDDD  |     | VDDD + 0.3  | V    |

| VIL    | Input LOW Voltage               | Single-ended inputs - CLKSEL, SD/OE | GND - 0.3 |     | 0.3xVDDD    | V    |

| VIH    | Input HIGH Voltage              | Single-ended input OUT0_SEL_I2CB    | 2         |     | VDDO0 + 0.3 | V    |

| VIL    | Input LOW Voltage               | Single-ended input OUT0_SEL_I2CB    | GND - 0.3 |     | 0.4         | V    |

| VIH    | Input HIGH Voltage              | Single-ended input - XIN/REF        | 0.8       |     | 1.2         | V    |

| VIL    | Input LOW Voltage               | Single-ended input - XIN/REF        | GND - 0.3 |     | 0.4         | V    |

| TR/TF  | Input Rise/Fall Time            | CLKSEL, SD/OE, SEL1/SDA, SEL0/SCL   |           |     | 300         | ns   |

<sup>1.</sup> See "Recommended Operating Conditions" table.

<sup>2.</sup> Slew rate measured through ±75mV window centered around differential zero.

# Table 15:DC Electrical Characteristics for 2.5V LVCMOS ( $V_{DDO}$ = 2.5V±5%, TA = -40°C to +85°C)

| Symbol | Parameter                       | Test Conditions                     | Min       | Тур | Max         | Unit |

|--------|---------------------------------|-------------------------------------|-----------|-----|-------------|------|

| VOH    | Output HIGH Voltage             | IOH = -12mA                         | 0.7xVDDO  |     |             | V    |

| VOL    | Output LOW Voltage              | IOL = 12mA                          |           |     | 0.4         | V    |

| IOZDD  | Output Leakage Current (OUT1~3) | Tri-state outputs, VDDO = 2.625V    |           |     | 5           | μA   |

| IOZDD  | Output Leakage Current (OUT0)   | Tri-state outputs, VDDO = 2.625V    |           |     | 30          | μA   |

| VIH    | Input HIGH Voltage              | Single-ended inputs - CLKSEL, SD/OE | 0.7xVDDD  |     | VDDD + 0.3  | V    |

| VIL    | Input LOW Voltage               | Single-ended inputs - CLKSEL, SD/OE | GND - 0.3 |     | 0.3xVDDD    | V    |

| VIH    | Input HIGH Voltage              | Single-ended input OUT0_SEL_I2CB    | 1.7       |     | VDDO0 + 0.3 | V    |

| VIL    | Input LOW Voltage               | Single-ended input OUT0_SEL_I2CB    | GND - 0.3 |     | 0.4         | V    |

| VIH    | Input HIGH Voltage              | Single-ended input - XIN/REF        | 0.8       |     | 1.2         | V    |

| VIL    | Input LOW Voltage               | Single-ended input - XIN/REF        | GND - 0.3 |     | 0.4         | V    |

| TR/TF  | Input Rise/Fall Time            | CLKSEL, SD/OE, SEL1/SDA, SEL0/SCL   |           |     | 300         | ns   |

# Table 16:DC Electrical Characteristics for 1.8V LVCMOS ( $V_{DDO}$ = 1.8V±5%, TA = -40°C to +85°C)

| Symbol | Parameter                       | Test Conditions                     | Min          | Тур | Max         | Unit |

|--------|---------------------------------|-------------------------------------|--------------|-----|-------------|------|

| VOH    | Output HIGH Voltage             | IOH = -8mA                          | 0.7 xVDDO    |     | VDDO        | V    |

| VOL    | Output LOW Voltage              | IOL = 8mA                           |              |     | 0.25 x VDDO | V    |

| IOZDD  | Output Leakage Current (OUT1~3) | Tri-state outputs, VDDO = 3.465V    |              |     | 5           | μA   |

| IOZDD  | Output Leakage Current (OUT0)   | Tri-state outputs, VDDO = 2.625V    |              |     | 30          | μA   |

| VIH    | Input HIGH Voltage              | Single-ended inputs - CLKSEL, SD/OE | 0.7 * VDDD   |     | VDDD + 0.3  | V    |

| VIL    | Input LOW Voltage               | Single-ended inputs - CLKSEL, SD/OE | GND - 0.3    |     | 0.3 * VDDD  | V    |

| VIH    | Input HIGH Voltage              | Single-ended input OUT0_SEL_I2CB    | 0.65 * VDDO0 | )   | VDDO0 + 0.3 | V    |

| VIL    | Input LOW Voltage               | Single-ended input OUT0_SEL_I2CB    | GND - 0.3    |     | 0.4         | V    |

| VIH    | Input HIGH Voltage              | Single-ended input - XIN/REF        | 0.8          |     | 1.2         | V    |

| VIL    | Input LOW Voltage               | Single-ended input - XIN/REF        | GND - 0.3    |     | 0.4         | V    |

| TR/TF  | Input Rise/Fall Time            | CLKSEL, SD/OE, SEL1/SDA, SEL0/SCL   |              |     | 300         | ns   |

# **Table 17:DC Electrical Characteristics for LVDS**( $V_{DDO}$ = 3.3V±5% or 2.5V±5%, TA = -40°C to +85°C)

| Symbol                      | Parameter                                                                                        | Min   | Тур  | Max   | Unit |

|-----------------------------|--------------------------------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>OT</sub> (+)         | Differential Output Voltage for the TRUE binary state                                            | 247   |      | 454   | mV   |

| V <sub>OT</sub> (-)         | Differential Output Voltage for the FALSE binary state                                           | -247  |      | -454  | mV   |

| $\triangle$ V <sub>OT</sub> | Change in V <sub>OT</sub> between Complimentary Output States                                    |       |      | 50    | mV   |

| V <sub>OS</sub>             | Output Common Mode Voltage (Offset Voltage)                                                      | 1.125 | 1.25 | 1.375 | V    |

| △Vos                        | Change in V <sub>OS</sub> between Complimentary Output States                                    |       |      | 50    | mV   |

| Ios                         | Outputs Short Circuit Current, V <sub>OUT</sub> + or V <sub>OUT</sub> - = 0V or V <sub>DDO</sub> |       | 9    | 24    | mA   |

| I <sub>OSD</sub>            | Differential Outputs Short Circuit Current, V <sub>OUT</sub> + = V <sub>OUT</sub> -              |       | 6    | 12    | mA   |

# Table 18:DC Electrical Characteristics for LVDS ( $V_{DDO}$ = 1.8 $V\pm5\%$ , TA = -40°C to +85°C)

| Symbol              | Parameter                                                                                        | Min  | Тур   | Max  | Unit |

|---------------------|--------------------------------------------------------------------------------------------------|------|-------|------|------|

| V <sub>OT</sub> (+) | Differential Output Voltage for the TRUE binary state                                            | 247  |       | 454  | mV   |

| V <sub>OT</sub> (-) | Differential Output Voltage for the FALSE binary state                                           | -247 |       | -454 | mV   |

| $\triangle V_{OT}$  | Change in V <sub>OT</sub> between Complimentary Output States                                    |      |       | 50   | mV   |

| Vos                 | Output Common Mode Voltage (Offset Voltage)                                                      | 0.8  | 0.875 | 0.95 | V    |

| △Vos                | Change in V <sub>OS</sub> between Complimentary Output States                                    |      |       | 50   | mV   |

| I <sub>OS</sub>     | Outputs Short Circuit Current, V <sub>OUT</sub> + or V <sub>OUT</sub> - = 0V or V <sub>DDO</sub> |      | 9     | 24   | mA   |

| I <sub>OSD</sub>    | Differential Outputs Short Circuit Current, V <sub>OUT</sub> + = V <sub>OUT</sub> -              |      | 6     | 12   | mA   |

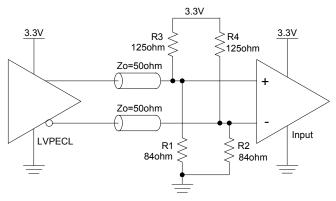

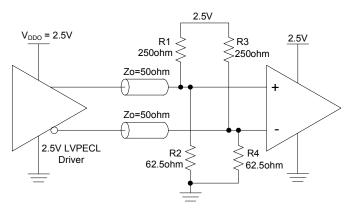

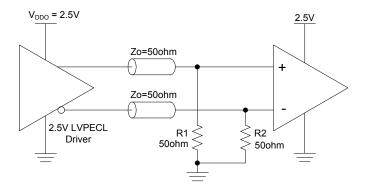

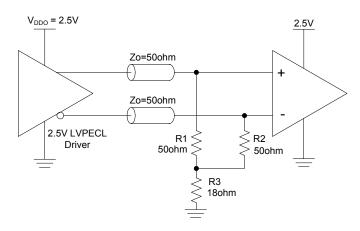

# **Table 19:DC Electrical Characteristics for LVPECL** ( $V_{DDO}$ = $3.3V\pm5\%$ or $2.5V\pm5\%$ , TA = -40°C to +85°C)

| Symbol          | Parameter                                                                          | Min                     | Тур | Max                     | Unit |

|-----------------|------------------------------------------------------------------------------------|-------------------------|-----|-------------------------|------|

| V <sub>OH</sub> | Output Voltage HIGH, terminated through $50\Omega$ tied to $\mathrm{V}_{DD}$ - 2 V | V <sub>DDO</sub> - 1.19 |     | V <sub>DDO</sub> - 0.69 | V    |

| $V_{OL}$        | Output Voltage LOW, terminated through $50\Omega$ tied to $\mathrm{V}_{DD}$ - 2 V  | V <sub>DDO</sub> - 1.94 |     | V <sub>DDO</sub> - 1.4  | V    |

| $V_{SWING}$     | Peak-to-Peak Output Voltage Swing                                                  | 0.55                    |     | 0.993                   | V    |

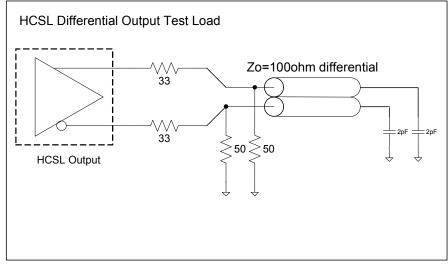

# Table 20:Electrical Characteristics – DIF 0.7V HCSL Differential Outputs ( $V_{DDO} = 3.3V \pm 5\%$ , $2.5V \pm 5\%$ , TA = -40°C to +85°C)

| Symbol  | Parameter                  | Conditions                                                                      | Min  | Тур | Max  | Units | Notes |

|---------|----------------------------|---------------------------------------------------------------------------------|------|-----|------|-------|-------|

| dV/dt   | Slew Rate                  | Scope averaging on                                                              | 1    |     | 4    | V/ns  | 1,2,3 |

| ∆dV/dt  | Slew Rate                  | Scope averaging on                                                              |      |     | 20   | %     | 1,2,3 |

| VHIGH   | Voltage High               | Statistical measurement on single-ended signal using oscilloscope math function | 660  |     | 850  | mV    | 1,6,7 |

| VLOW    | Voltage Low                | (Scope averaging ON)                                                            | -150 |     | 150  | mV    | 1,6   |

| VMAX    | Maximum Voltage            | Measurement on single-ended signal using                                        |      |     | 1150 | mV    | 1     |

| VMIN    | Minimum Voltage            | absolute value (Scope averaging off)                                            | -300 |     |      | mV    | 1     |

| VSWING  | Voltage Swing              | Scope averaging off                                                             | 300  |     |      | mV    | 1,2,6 |

| VCROSS  | Crossing Voltage Value     | Scope averaging off                                                             | 250  |     | 550  | mV    | 1,4,6 |

| ?VCROSS | Crossing Voltage variation | Scope averaging off                                                             |      |     | 140  | mV    | 1,5   |

Note 1: Guaranteed by design and characterization. Not 100% tested in production

Note 4: VCROSS is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

Note 5: the total variation of all VCROSS measurements in any particular system. Note that this is a subset of VCROSS min/max (VCROSS absolute) allowed. The intent is to limit VCROSS induced modulation by setting ?VCROSS to be smaller than VCROSS absolute.

Note 6: Measured from single-ended waveform.

Note 7. Measured with scope averaging off, using statistics function. Variation is difference between min. and max.

Note 2: Measured from differential waveform.

Note 3: Slew rate is measured through the VSWING voltage range centered around differential 0V. This results in a +/-150mV window around differntial 0V.

# **Table 21:1AC Timing Electrical Characteristics**

$(V_{DDO}$  = 3.3V+5% or 2.5V+5% or 1.8V ±5%, TA = -40°C to +85°C)

(Spread Spectrum Generation = OFF)

| Symbol           | Parameter                 | Test Conditions                                                                        | Min.           | Тур. | Max. | Units |

|------------------|---------------------------|----------------------------------------------------------------------------------------|----------------|------|------|-------|

|                  |                           | Input frequency limit (XIN)                                                            | 8              |      | 40   | MHz   |

| fIN <sup>1</sup> | Input Frequency           | Input frequency limit (REF)                                                            | 1              |      | 200  | MHz   |

|                  |                           | Input frequency limit (CLKIN, CLKINB)                                                  | 1              |      | 350  | MHz   |

|                  |                           | Single ended clock output limit (LVCMOS)                                               | 1              |      | 200  |       |

| fOUT             | Output Frequency          | Differential clock output limit (LVPECL/<br>LVDS/HCSL)                                 | 1              |      | 350  | MHz   |

| fVCO             | VCO Frequency             | VCO operating frequency range                                                          | 2500           |      | 2900 | MHz   |

| fPFD             | PFD Frequency             | PFD operating frequency range                                                          | 1 <sup>1</sup> |      | 150  | MHz   |

| fBW              | Loop Bandwidth            | Input frequency = 25MHz                                                                | 0.06           |      | 0.9  | MHz   |

| t2               | Input Duty Cycle          | Duty Cycle                                                                             | 45             |      | 55   | %     |

|                  |                           | Measured at VDD/2, all outputs except Reference output OUT0, VDDOX= 2.5V or 3.3V       | 45             | 50   | 55   | %     |

|                  |                           | Measured at VDD/2, all outputs except<br>Reference output OUT0, VDDOX=1.8V             | 40             | 50   | 60   | %     |

| t3 <sup>5</sup>  | Output Duty Cycle         | Measured at VDD/2, Reference output OUT0 (5MHz - 120MHz) with 50% duty cycle input     | 40             | 50   | 60   | %     |

|                  |                           | Measured at VDD/2, Reference output OUT0 (150.1MHz - 200MHz) with 50% duty cycle input | 30             | 50   | 70   | %     |

|                  | Slew Rate, SLEW[1:0] = 00 | , .                                                                                    | 1.0            | 2.2  |      |       |

|                  | Slew Rate, SLEW[1:0] = 01 | Single-ended 3.3V LVCMOS output clock                                                  | 1.2            | 2.3  |      |       |

|                  | Slew Rate, SLEW[1:0] = 10 | rise and fall time, 20% to 80% of VDDO (Output Load = 5 pF) VDDOX=3.3V                 | 1.3            | 2.4  |      |       |

|                  | Slew Rate, SLEW[1:0] = 11 | (Gutput 2000                                                                           | 1.7            | 2.7  |      |       |

|                  | Slew Rate, SLEW[1:0] = 00 | 0: 1 1051/11/01/02                                                                     | 0.6            | 1.3  |      |       |

| t4 <sup>2</sup>  | Slew Rate, SLEW[1:0] = 01 | Single-ended 2.5V LVCMOS output clock rise and fall time, 20% to 80% of VDDO           | 0.7            | 1.4  |      | V/ns  |

| ι4               | Slew Rate, SLEW[1:0] = 10 | (Output Load = 5 pF) VDDOX=2.5V                                                        | 0.6            | 1.4  |      | V/IIS |

|                  | Slew Rate, SLEW[1:0] = 11 | (Gutput 2000 Gp. ) 1226/t 2:01                                                         | 1.0            | 1.7  |      |       |

|                  | Slew Rate, SLEW[1:0] = 00 |                                                                                        | 0.3            | 0.7  |      |       |

|                  | Slew Rate, SLEW[1:0] = 01 | Single-ended 1.8V LVCMOS output clock                                                  | 0.4            | 0.8  |      |       |

|                  | Slew Rate, SLEW[1:0] = 10 | rise and fall time, 20% to 80% of VDDO (Output Load = 5 pF) VDDOX=1.8V                 | 0.4            | 0.9  |      | 1     |

|                  | Slew Rate, SLEW[1:0] = 11 | (30:50: 200 3 51 ) 1250/ 1.01                                                          | 0.7            | 1.2  |      | 1     |

|                  | Rise Times                | LVDS, 20% to 80%                                                                       |                | 300  |      |       |

| t5               | Fall Times                | LVDS, 80% to 20%                                                                       |                | 300  |      | †     |

| ເວ               | Rise Times                | LVPECL, 20% to 80%                                                                     |                | 400  |      | ps    |

|                  | Fall Times                | LVPECL, 80% to 20%                                                                     |                | 400  |      |       |

|                 |              | Cycle-to-Cycle jitter (Peak-to-Peak),        |      |     |    |

|-----------------|--------------|----------------------------------------------|------|-----|----|

|                 |              | multiple output frequencies switching,       |      |     |    |

|                 |              | differential outputs (1.8V to 3.3V nominal   |      |     |    |

|                 |              | output voltage)                              | 40   |     |    |

|                 |              | OUT0=25MHz                                   | 46   |     | ps |

|                 |              | OUT1=100MHz                                  |      |     |    |

|                 |              | OUT2=125MHz                                  |      |     |    |

|                 |              | OUT3=156.25MHz                               |      |     |    |

|                 |              | Cycle-to-Cycle jitter (Peak-to-Peak),        |      |     |    |

|                 |              | multiple output frequencies switching,       |      |     |    |

|                 |              | LVCMOS outputs (1.8 to 3.3V nominal          |      |     |    |

|                 |              | output voltage)                              |      |     |    |

|                 |              | OUT0=25MHz                                   | 74   |     | ps |

|                 |              | OUT1=100MHz                                  |      |     |    |

|                 |              | OUT2=125MHz                                  |      |     |    |

|                 |              | OUT3=156.25MHz                               |      |     |    |

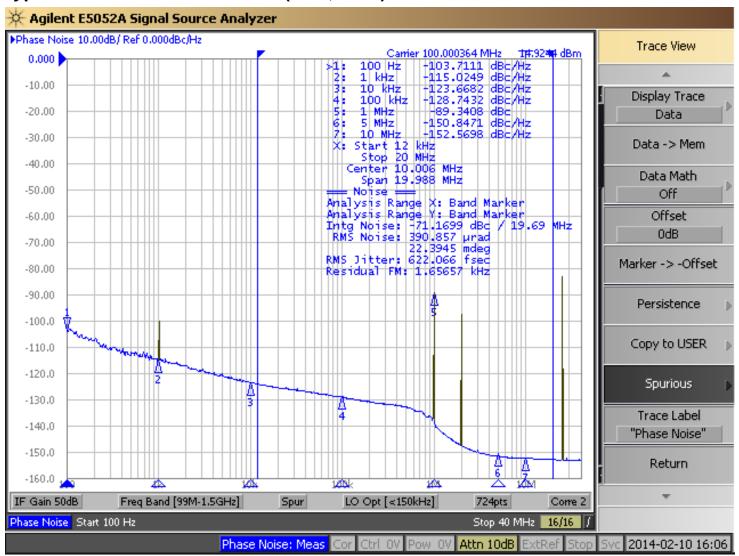

| t6              | Clock Jitter | RMS Phase Jitter (12kHz to 5MHz              |      |     |    |

|                 |              | integration range) reference clock (OUT0),   |      |     |    |

|                 |              | 25 MHz LVCMOS outputs (1.8 to 3.3V           |      |     |    |

|                 |              | nominal output voltage).                     |      |     |    |

|                 |              | OUT0=25MHz                                   | 0.5  |     | ps |

|                 |              | OUT1=100MHz                                  |      |     |    |

|                 |              | OUT2=125MHz                                  |      |     |    |

|                 |              | OUT3=156.25MHz                               |      |     |    |

|                 |              | RMS Phase Jitter (12kHz to 20MHz             |      |     |    |

|                 |              | integration range) differential output, VDDO |      |     |    |

|                 |              | = 3.465V, 25MHz crystal, 156.25MHz           |      |     |    |

|                 |              | output frequency                             |      |     |    |