# 2.5V TO 3.3V HIGH PERFORMANCE CLOCK BUFFER

#### **FEATURES:**

- High performance 1:10 clock driver for general purpose applications

- Operates up to 200MHz at VDD = 3.3V

- Pin-to-pin skew < 100ps

- VDD range: 2.3V to 3.6V

- · Output enable glitch suppression

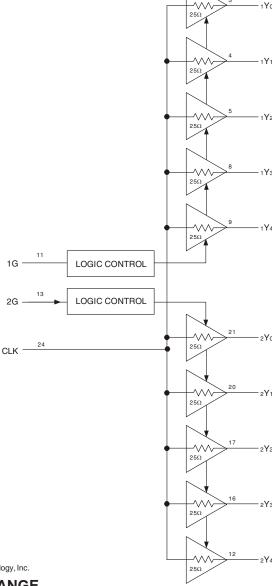

- · Distributes one clock input to two banks of five outputs

- 25Ω on-chip series dampening resistors

- Available in TSSOP package

NOTE: EOL for non-green parts to occur on 5/13/10 per PDN U-09-01

#### **DESCRIPTION:**

The IDT5V2310 is a high performance, low skew clock buffer that operates up to 200MHz. Two banks of five outputs each provide low skew copies of CLK. Through the use of control pins 1G and 2G, the outputs of banks 1Y(0:4) and 2Y(0:4) can be placed in a low state regardless of CLK input. The device operates in 2.5V and 3.3V environments. The built-in output enable glitch suppression ensures a synchronized output enable sequence to distribute full period clock signals.

The IDT5V2310 is characterized for operation from -40°C to +85°C.

#### **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

**DECEMBER 2012**

#### **PINCONFIGURATION**

#### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Description                                      | Max              | Unit |

|--------|--------------------------------------------------|------------------|------|

| VDD    | Power Supply Voltage                             | -0.5 to +4.6     | V    |

| Vı     | Input Voltage <sup>(2)</sup>                     | -0.5 to VDD +0.5 | V    |

| Vo     | Output Voltage <sup>(2)</sup>                    | -0.5 to VDD +0.5 | V    |

| lıĸ    | Input Clamp Current VI < 0 or VI > VDD           | ±50              | mA   |

| Іок    | Output Clamp Current<br>Vo < 0 or Vo > VDD       | ±50              | mA   |

| lo     | Continuous Total Output Current<br>Vo < 0 to VDD | ±50              | mA   |

| Tstg   | Storage Temperature                              | -65 to +150      | °C   |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Not to exceed 4.6V.

# **CAPACITANCE**(TA = +25°C, f = 1MHz, VIN = 0V)

| Parameter | Description       | Min. | Тур. | Max. | Unit |

|-----------|-------------------|------|------|------|------|

| CIN       | Input Capacitance | _    | 2.5  | _    | pF   |

|           | VI = 0V or VDD    |      |      |      |      |

# **FUNCTION TABLE**(1)

|    | Inputs | Out | outs             |         |

|----|--------|-----|------------------|---------|

| 1G | 2G     | CLK | 1 <b>Y</b> (0:4) | 2Y(0:4) |

| L  | L      | Χ   | L                | L       |

| Н  | L      | Н   | Н                | L       |

| L  | Н      | Н   | L                | Н       |

| Н  | Н      | Н   | Н                | Н       |

#### NOTE:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- X = Don't Care

#### **PIN DESCRIPTION**

| TERMINAL        |     |                                                                                                                                                                                                                                                                           |

|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | I/O | Description                                                                                                                                                                                                                                                               |

| 1G              | -   | Output Enable Control for $1Y(0:4)$ Outputs. This output enable is active HIGH. If this pin is Logic HIGH, the $1Y(0:4)$ clock outputs will follow the input clock (CLK). If this pin is logic LOW, the $1Y(0:4)$ outputs will drive low independent of the state of CLK. |

| 2G              | -   | Output Enable Control for $2Y(0:4)$ Outputs. This output enable is active HIGH. If this pin is Logic HIGH, the $2Y(0:4)$ clock outputs will follow the input clock (CLK). If this pin is logic LOW, the $2Y(0:4)$ outputs will drive low independent of the state of CLK. |

| 1Y(0:4)         | 0   | Buffered Output Clocks                                                                                                                                                                                                                                                    |

| 2Y(0:4)         | 0   | Buffered Output Clocks                                                                                                                                                                                                                                                    |

| CLK             | I   | Input Reference Frequency                                                                                                                                                                                                                                                 |

| GND             | ·   | Ground                                                                                                                                                                                                                                                                    |

| V <sub>DD</sub> | PWR | DC Power Supply, 2.3V to 3.6V                                                                                                                                                                                                                                             |

# **RECOMMENDED OPERATING RANGE**

| Symbol | Description                   |                    | Min. | Тур. | Max. | Unit |

|--------|-------------------------------|--------------------|------|------|------|------|

| Vdd    | Internal Power Supply Voltage | ;                  | 2.3  | 2.5  |      | V    |

|        |                               |                    |      | 3.3  | 3.6  |      |

| VIL    | Input Voltage LOW             | VDD = 3V to 3.6V   |      |      | 0.8  | V    |

|        |                               | VDD = 2.3V to 2.7V |      |      | 0.7  |      |

| VIH    | Input Voltage HIGH            | VDD = 3V to 3.6V   | 2    |      |      | V    |

|        |                               | VDD = 2.3V to 2.7V | 1.7  |      |      |      |

| Vı     | Input Voltage                 |                    | 0    |      | Vdd  | V    |

| Іон    | Output Current HIGH           | VDD = 3V to 3.6V   |      |      | -12  | mA   |

|        |                               | VDD = 2.3V to 2.7V |      |      | -6   |      |

| lol    | Output Current LOW            | VDD = 3V to 3.6V   |      |      | 12   | mA   |

|        |                               | VDD = 2.3V to 2.7V |      |      | 6    |      |

| TA     | Ambient Operating Temperatur  | е                  | -40  |      | +85  | °C   |

#### DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

| Symbol | Parameter                            | Test Conditions                                          | Min. | Тур. | Max   | Unit |

|--------|--------------------------------------|----------------------------------------------------------|------|------|-------|------|

| Vik    | Input Voltage                        | $V_{DD} = 3V$ , $I_{IN} = -18mA$                         |      |      | - 1.2 | V    |

| lin    | Input Current                        | $V_I = 0V \text{ or } V_{DD}$                            |      |      | ±5    | μΑ   |

| Idd    | Static Device Current <sup>(1)</sup> | $CLK = 0V$ or $V_{DD}$ , $I_{O} = 0mA$ , $V_{DD} = 3.3V$ |      |      | 25    | μΑ   |

#### NOTE:

# DC ELECTRICAL CHARACTERISTICS-VDD = 3.3V ± 0.3V

| Symbol | Parameter                 | Test Cor                       | nditions     | Min.      | Typ. <sup>(1)</sup> | Max  | Unit |

|--------|---------------------------|--------------------------------|--------------|-----------|---------------------|------|------|

|        |                           | V <sub>DD</sub> = Min. to Max. | Іон = -100μА | VDD - 0.2 |                     |      |      |

| Vон    | HIGH level Output Voltage | VDD = 3V                       | Iон = -12mA  | 2.1       |                     |      | V    |

|        |                           |                                | Iон = -6mA   | 2.4       |                     |      |      |

|        |                           | V <sub>DD</sub> = Min. to Max. | IoL = 100μA  |           |                     | 0.2  |      |

| Vol    | LOW level Output Voltage  | VDD = 3V                       | IoL = 12mA   |           |                     | 0.8  | V    |

|        |                           |                                | IoL = 6mA    |           |                     | 0.55 |      |

|        |                           | VDD = 3V                       | Vo = 1V      | -28       |                     |      |      |

| Іон    | HIGH level Output Current | VDD = 3.3V                     | Vo = 1.65V   |           | -36                 |      | mA   |

|        |                           | VDD = 3.6V                     | Vo = 3.135V  |           |                     | -14  |      |

|        |                           | VDD = 3V                       | Vo = 1.95V   | 28        |                     |      |      |

| lol    | LOW level Output Current  | VDD = 3.3V                     | Vo = 1.65V   |           | 36                  |      | mA   |

|        |                           | V <sub>DD</sub> = 3.6V         | Vo = 0.4V    |           |                     | 14   |      |

#### NOTE:

<sup>1.</sup> For IDD over frequency, see TEST CIRCUIT AND WAVEFORMS.

<sup>1.</sup> All typical values are at respective nominal  $\ensuremath{\text{V}_{\text{DD}}}$ .

# DC ELECTRICAL CHARACTERISTICS - VDD = 2.5V ± 0.2V

| Symbol | Parameter                 | Test Cor                       | nditions     | Min.                  | Typ. <sup>(1)</sup> | Max  | Unit |

|--------|---------------------------|--------------------------------|--------------|-----------------------|---------------------|------|------|

| Vон    | HIGH level Output Voltage | V <sub>DD</sub> = Min. to Max. | Іон = -100μΑ | V <sub>DD</sub> - 0.2 |                     |      | V    |

|        |                           | VDD = 2.3V                     | Iон = -6mA   | 1.8                   |                     |      |      |

| Vol    | LOW level Output Voltage  | V <sub>DD</sub> = Min. to Max. | IoL = 100μA  |                       |                     | 0.2  | V    |

|        |                           | VDD = 2.3V                     | IoL = 6mA    |                       |                     | 0.55 |      |

|        |                           | VDD = 2.3V                     | Vo = 1V      | -17                   |                     |      |      |

| Іон    | HIGH level Output Current | VDD = 2.5V                     | Vo = 1.25V   |                       | -25                 |      | mA   |

|        |                           | VDD = 2.7V                     | Vo = 2.375V  |                       |                     | -10  |      |

|        |                           | VDD = 2.3V                     | Vo = 1.2V    | 17                    |                     |      |      |

| lol    | LOW level Output Current  | VDD = 2.5V                     | Vo = 1.25V   |                       | 25                  |      | mA   |

|        |                           | V <sub>DD</sub> = 2.7V         | Vo = 0.3V    |                       |                     | 10   |      |

#### NOTE:

# TIMING REQUIREMENTS OVER RECOMMENDED RANGE

| Symbol | Parameter       | Test Conditions                | Min. | Тур. | Max | Unit |

|--------|-----------------|--------------------------------|------|------|-----|------|

| fclk   | Clock Frequency | $V_{DD} = 3V \text{ to } 3.6V$ | 0    |      | 200 | MHz  |

|        |                 | V <sub>DD</sub> = 2.3V to 2.7V | 0    |      | 170 |      |

<sup>1.</sup> All typical values are at respective nominal  $\ensuremath{\text{V}_{\text{DD}}}$ .

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE-

$V_{DD} = 3.3V \pm 0.3V^{(1)}$

| Symbol                | Parameter             | Test Conditions                   | Min. | Typ. <sup>(1)</sup> | Max | Unit |

|-----------------------|-----------------------|-----------------------------------|------|---------------------|-----|------|

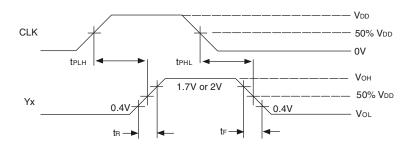

| t <sub>PLH</sub>      | CLK to Yx             | f = 0MHz to 200MHz                | 1.3  |                     | 2.8 | ns   |

| tphL                  |                       |                                   |      |                     |     |      |

| tsk(o) <sup>(2)</sup> | Output Skew, Yx to Yx |                                   |      |                     | 100 | ps   |

| tsk(p)                | Pulse Skew            |                                   |      |                     | 250 | ps   |

| tsk(pp)               | Part-to-Part Skew     |                                   |      |                     | 500 | ps   |

| tr                    | RiseTime              | $Vo = 0.4V \text{ to } 2V^{(3)}$  | 0.7  |                     | 2   | V/ns |

| tr                    | FallTime              | $V_0 = 2V \text{ to } 0.4V^{(3)}$ | 0.7  |                     | 2   | V/ns |

| tsu                   | G before CLK↓         | V(THRESHOLD) = VDD/2              | 0.1  |                     |     | ns   |

| tн                    | G after CLK↓          |                                   | 0.4  |                     |     |      |

#### NOTES:

- 1. All typical values are at respective nominal VDD.

- 2. This specification is only valid for equal loading of all outputs.

- 3. Measured at 100MHz.

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE-

$V_{DD} = 2.5V \pm 0.2V^{(1)}$

| Symbol                | Parameter             | Test Conditions                    | Min. | Typ. <sup>(1)</sup> | Max | Unit |

|-----------------------|-----------------------|------------------------------------|------|---------------------|-----|------|

| <b>t</b> PLH          | CLK to Yx             | f = 0MHz to 170MHz                 | 1.5  |                     | 3.5 | ns   |

| <b>t</b> PHL          |                       |                                    |      |                     |     |      |

| tsk(o) <sup>(2)</sup> | Output Skew, Yx to Yx |                                    |      |                     | 100 | ps   |

| tsk(p)                | Pulse Skew            |                                    |      |                     | 400 | ps   |

| tsk(pp)               | Part-to-Part Skew     |                                    |      |                     | 600 | ps   |

| tr                    | Rise Time             | $Vo = 0.4V \text{ to } 1.7V^{(3)}$ | 0.5  |                     | 1.4 | V/ns |

| t⊧                    | FallTime              | $Vo = 1.7V \text{ to } 0.4V^{(3)}$ | 0.5  |                     | 1.4 | V/ns |

| tsu                   | G before CLK↓         | V(THRESHOLD) = VDD/2               | 0.1  |                     |     | ns   |

| tн                    | G after CLK↓          |                                    | 0.4  |                     |     |      |

#### NOTES:

- 1. All typical values are at respective nominal VDD.

- 2. This specification is only valid for equal loading of all outputs.

- 3. Measured at 100MHz.

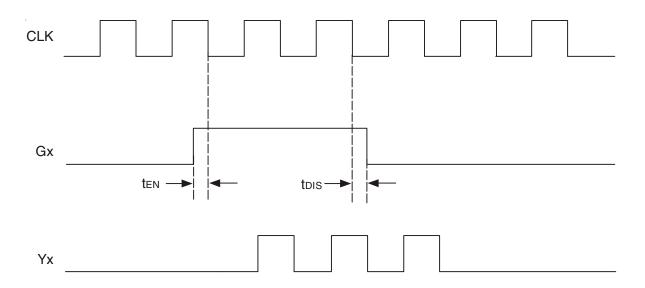

# **OUTPUTENABLE GLITCH SUPPRESSION CIRCUIT**

The purpose of the glitch suppression circuitry is to ensure the output enable sequence is synchronized with the clock input such that the output buffer will be enabled on the next full period of the input clock (negative edge triggered by the input clock). The G input must be stable one ten-time prior to the falling edge of the CLK for predictable operation.

G (ten, tdis) Relative to CLK↓

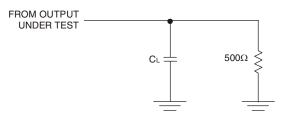

#### **TEST CIRCUITS AND WAVEFORMS**

#### NOTES:

- 1.  $C_L$  includes probe and jig capacitance.

- 2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$ 200MHz; Zo =  $50\Omega$ ; tR < 1.2ns; tF < 1.2ns.

#### Test Load Circuit

Voltage Waveforms Propagation Delay Times

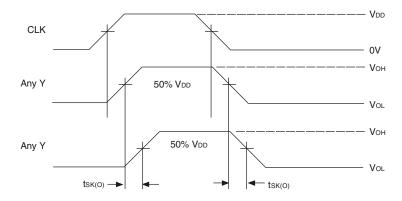

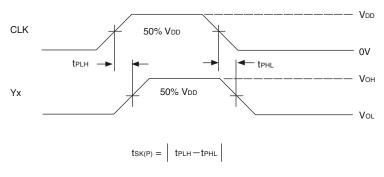

Output Skew

Pulse Skew

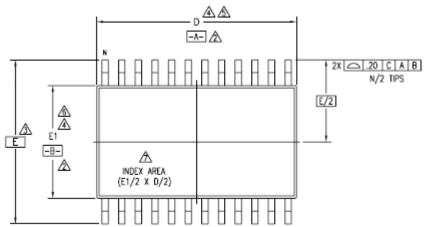

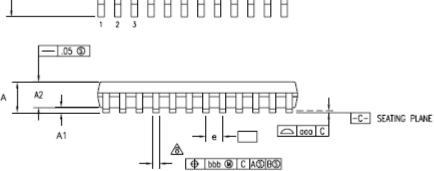

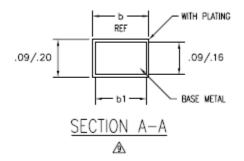

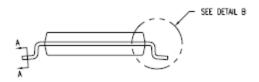

# PACKAGE DRAWING AND DIMENSIONS (24-PINTSSOP)

| JEDE | N        |      |         |

|------|----------|------|---------|

|      | AD       |      | N D T E |

| MIN  | NOM      | MAX  | E       |

| -    | -        | 1.20 |         |

| .05  | -        | .15  |         |

| .80  | 1.00     | 1.05 |         |

| 7.70 | 7.80     | 7.90 | 4,5     |

| (    | 6.40 BSC | ;    | 3       |

| 4.30 | 4.40     | 4.50 | 4,6     |

|      | .65 BSC  |      |         |

| .19  | -        | .30  |         |

| .19  | .22      | .25  |         |

| -    |          |      |         |

| -    | 10       |      |         |

|      |          |      |         |

#### NOTES:

- 1 ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994

- A DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

b

- △ DIMENSION E TO BE DETERMINED AT SEATING PLANE —C—

- A DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE -H-

- DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED .15 mm PER SIDE.

- DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED .25 mm PER SIDE

- DETAIL OF PIN 1 IDENTIFIER IS OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED

- LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION IS .08 mm in excess of the lead width dimension at maximum material condition. Dambar cannot be located on the lower radius or the foot

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .10 AND .25 mm FROM THE LEAD TIP

- 10 ALL DIMENSIONS ARE IN MILLIMETERS

- 11 THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-153, VARIATION AA, AB-1, AB, AC, AD & AE

# 10'-20' R.09 MIN R.09 MIN 10'-20' 10'-20' 10'-8' DETAIL B

#### **MARKING DIAGRAM**

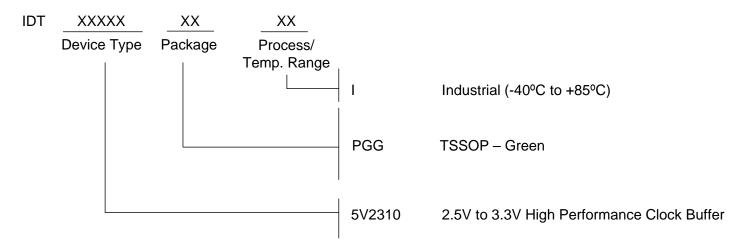

# **ORDERING INFORMATION**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Buffer category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

MPC962309EJ-1H NB4N121KMNG IDT49FCT805ASO MK2308S-1HILF PL133-27GI-R NB3L02FCT2G NB3L03FCT2G

ZL40203LDG1 ZL40200LDG1 ZL40205LDG1 9FG1200DF-1LF 9FG1001BGLF ZL40202LDG1 PI49FCT20802QE SL2305SC-1T

PI6C4931502-04LIE NB7L1008MNG NB7L14MN1G PI49FCT20807QE PI6C4931502-04LIEX ZL80002QAB1 PI6C4931504-04LIEX

PI6C10806BLEX ZL40226LDG1 ZL40219LDG1 8T73S208B-01NLGI SY75578LMG PI49FCT32805QEX PL133-27GC-R

CDCV304PWG4 MC10LVEP11DG MC10EP11DTG MC100LVEP11DG MC100E111FNG MC100EP11DTG NB6N11SMNG

NB7L14MMNG NB3N2304NZDTR2G NB6L11MMNG NB6L14MMNR2G NB6L611MNG PL123-02NGI-R NB3N111KMNR4G

ADCLK944BCPZ-R7 ZL40217LDG1 NB7LQ572MNG HMC940LC4BTR ADCLK946BCPZ-REEL7 ADCLK946BCPZ

ADCLK846BCPZ-REEL7