# Octal T1/E1/J1 Long Haul / Short Haul Transceiver IDT82P2288

Version 8 JANUARY 10, 2011

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: 1-800-345-7015 or 408-284-8200• TWX: 910-338-2070 • FAX: 408-284-2775

Printed in U.S.A.

© 2011 Integrated Device Technology, Inc.

#### DISCLAIMER

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# **Table of Contents**

| TΑ  | BLE   | OF CO        | ONTENT   | TS                                               | 3   |

|-----|-------|--------------|----------|--------------------------------------------------|-----|

| LIS | O T   | F TAB        | LES      |                                                  | 7   |

| LIS | ST OI | F FIGU       | JRES     |                                                  | . 9 |

| FΕ  | ATU   | RES          |          |                                                  | 11  |

|     |       |              |          |                                                  |     |

|     |       |              |          |                                                  |     |

|     |       |              |          |                                                  |     |

|     |       |              |          | V                                                |     |

|     |       |              |          | SCRIPTION                                        |     |

| J   |       |              |          | DE SELECTION                                     |     |

|     |       |              |          | EDANCE MATCHING                                  |     |

|     | J.Z   |              |          | nitor                                            |     |

|     | 3.3   |              |          | ALIZER                                           |     |

|     |       |              | -        |                                                  |     |

|     |       |              |          | ATA RECOVERY                                     |     |

|     | 3.6   | <b>RECEI</b> | VE JITTE | R ATTENUATOR                                     | 27  |

|     | 3.7   | DECO         | DER      |                                                  | 29  |

|     |       | 3.7.1        |          | de Rule                                          |     |

|     |       |              |          | T1/J1 Mode                                       |     |

|     |       |              |          | E1 Mode                                          |     |

|     |       | 3.7.2        |          | Error Detection                                  |     |

|     |       |              | 3.7.2.1  | T1 / J1 ModeE1 Mode                              |     |

|     |       | 272          |          | ection                                           |     |

|     | 3.8   |              |          | SSOR                                             |     |

|     | 0.0   |              |          | ode                                              |     |

|     |       | 0.0          | 3.8.1.1  | Synchronization Searching                        |     |

|     |       |              | 3.8.1.2  | Error Event And Out Of Synchronization Detection |     |

|     |       |              | 3.8.1.3  | Overhead Extraction (T1 Mode SLC-96 Format Only) | 36  |

|     |       |              | 3.8.1.4  | Interrupt Summary                                | 39  |

|     |       | 3.8.2        |          | 9                                                |     |

|     |       |              | 3.8.2.1  | Synchronization Searching                        |     |

|     |       |              | 3.8.2.2  | Error Event And Out Of Synchronization Detection |     |

|     |       |              | 3.8.2.3  | Overhead Extraction                              |     |

|     |       |              | 3.8.2.4  | V5.2 Link                                        | 48  |

|     | 3 0   | DEREC        |          | Interrupt Summary  E MONITOR                     |     |

|     | J.J   |              |          | ode                                              |     |

|     |       |              |          |                                                  |     |

|     | 3.10  |              |          | TOR                                              |     |

|     |       |              |          | ode                                              |     |

|     |       | 3.10.2       | E1 Mode  | ·                                                | 60  |

|     | 3.11  |              |          | R                                                |     |

|     |       |              |          | hannel Configuration                             |     |

|     |       | 3.11.2       | _        | ode                                              | 61  |

|     |       |              | 3 11 2 1 | HDLC Mode                                        | h1  |

| 3.12 | BIT-ORI                                    | IENTED MESSAGE RECEIVER (T1/J1 ONLY)                        | 64 |  |  |  |  |

|------|--------------------------------------------|-------------------------------------------------------------|----|--|--|--|--|

| 3.13 | INBAND LOOPBACK CODE DETECTOR (T1/J1 ONLY) |                                                             |    |  |  |  |  |

|      |                                            | C STORE BUFFER                                              |    |  |  |  |  |

|      |                                            | /E CAS/RBS BUFFER                                           |    |  |  |  |  |

|      | 3.15.1                                     | T1/J1 Mode                                                  | 65 |  |  |  |  |

|      | 3.15.2 E                                   | E1 Mode                                                     | 66 |  |  |  |  |

| 3.16 |                                            | /E PAYLOAD CONTROL                                          |    |  |  |  |  |

|      |                                            | /E SYSTEM INTERFACE                                         |    |  |  |  |  |

|      |                                            | T1/J1 Mode                                                  |    |  |  |  |  |

|      |                                            | 3.17.1.1 Receive Clock Master Mode                          |    |  |  |  |  |

|      |                                            | 3.17.1.2 Receive Clock Slave Mode                           |    |  |  |  |  |

|      |                                            | 3.17.1.3 Receive Multiplexed Mode                           |    |  |  |  |  |

|      |                                            | 3.17.1.4 Offset                                             |    |  |  |  |  |

|      | 3                                          | 3.17.1.5 Output On RSDn/MRSDA(MRSDB) & RSIGn/MRSIGA(MRSIGB) | 76 |  |  |  |  |

|      | 3.17.2 E                                   | E1 Mode                                                     | 77 |  |  |  |  |

|      |                                            | 3.17.2.1 Receive Clock Master Mode                          |    |  |  |  |  |

|      |                                            | 3.17.2.2 Receive Clock Slave Mode                           |    |  |  |  |  |

|      |                                            | 3.17.2.3 Receive Multiplexed Mode                           |    |  |  |  |  |

|      |                                            | 3.17.2.4 Offset                                             |    |  |  |  |  |

|      |                                            | 3.17.2.5 Output On RSDn/MRSDA(MRSDB) & RSIGn/MRSIGA(MRSIGB) | 78 |  |  |  |  |

| 3.18 | TRANSI                                     | MIT SYSTEM INTERFACE                                        | 80 |  |  |  |  |

| •    |                                            | T1/J1 Mode                                                  |    |  |  |  |  |

|      |                                            | 3.18.1.1 Transmit Clock Master Mode                         |    |  |  |  |  |

|      |                                            | 3.18.1.2 Transmit Clock Slave Mode                          |    |  |  |  |  |

|      |                                            | 3.18.1.3 Transmit Multiplexed Mode                          |    |  |  |  |  |

|      |                                            | 3.18.1.4 Offset                                             |    |  |  |  |  |

|      |                                            | E1 Mode                                                     |    |  |  |  |  |

|      |                                            | 3.18.2.1 Transmit Clock Master Mode                         |    |  |  |  |  |

|      |                                            | 3.18.2.2 Transmit Clock Slave Mode                          |    |  |  |  |  |

|      |                                            | 3.18.2.3 Transmit Multiplexed Mode                          |    |  |  |  |  |

|      | 3                                          | 3.18.2.4 Offset                                             | 88 |  |  |  |  |

| 3.19 | TRANSI                                     | MIT PAYLOAD CONTROL                                         | 88 |  |  |  |  |

| 3.20 | FRAME                                      | GENERATOR                                                   | 90 |  |  |  |  |

|      | 3.20.1                                     | Generation                                                  | 90 |  |  |  |  |

|      | 3                                          | 3.20.1.1 T1 / J1 Mode                                       | 90 |  |  |  |  |

|      |                                            | 3.20.1.2 E1 Mode                                            |    |  |  |  |  |

|      | 3.20.2 H                                   | HDLC Transmitter                                            | 95 |  |  |  |  |

|      |                                            | 3.20.2.1 HDLC Channel Configuration                         |    |  |  |  |  |

|      |                                            | 3.20.2.2 HDLC Mode                                          |    |  |  |  |  |

|      |                                            | 3.20.2.3 Interrupt Summary                                  |    |  |  |  |  |

|      |                                            | 3.20.2.4 Reset                                              |    |  |  |  |  |

|      |                                            | Automatic Performance Report Message (T1/J1 Only)           |    |  |  |  |  |

|      |                                            | Bit-Oriented Message Transmitter (T1/J1 Only)               |    |  |  |  |  |

|      |                                            | Inband Loopback Code Generator (T1/J1 Only)                 |    |  |  |  |  |

|      |                                            | All 'Zero's & All 'One's                                    |    |  |  |  |  |

|      |                                            | Change Of Frame Alignment                                   |    |  |  |  |  |

|      |                                            | MIT BUFFER                                                  |    |  |  |  |  |

| 3.22 |                                            | ER                                                          |    |  |  |  |  |

|      |                                            | Line Code Rule                                              |    |  |  |  |  |

|      |                                            | 3.22.1.1 T1/J1 Mode                                         |    |  |  |  |  |

|      |                                            | 3.22.1.2 E1 Mode                                            |    |  |  |  |  |

|      |                                            | BPV Error Insertion                                         |    |  |  |  |  |

|      |                                            | All 'One's Insertion                                        |    |  |  |  |  |

| 3.23 | TRANSI                                     | MIT JITTER ATTENUATOR                                       | 99 |  |  |  |  |

|   | 3.24 | WAVE       | FORM SH  | IAPER / LINE BUILD OUT              | 100 |

|---|------|------------|----------|-------------------------------------|-----|

|   |      | 3.24.1     | Preset W | Vaveform Template                   | 100 |

|   |      |            | 3.24.1.1 | T1/J1 Mode                          | 100 |

|   |      |            | 3.24.1.2 | E1 Mode                             | 101 |

|   |      |            |          | ld Out (LBO) (T1 Only)              |     |

|   |      |            |          | ogrammable Arbitrary Waveform       |     |

|   |      |            |          |                                     |     |

|   |      |            |          | IMPEDANCE MATCHING                  |     |

|   | 3.27 |            |          | DIAGNOSTIC FACILITIES               |     |

|   |      | 3.27.1     |          | enerator / Detector                 |     |

|   |      |            |          | Pattern Generator                   |     |

|   |      |            |          | Pattern Detector                    |     |

|   |      | 3.27.2     | •        | k                                   |     |

|   |      |            |          | System Loopback                     |     |

|   |      |            |          | Payload Loopback                    |     |

|   |      |            |          | Local Digital Loopback 1            |     |

|   |      |            |          | Remote Loopback                     |     |

|   |      |            |          | Local Digital Loopback 2            |     |

|   |      | 2 27 2     |          | Analog Loopback                     |     |

|   | 2 20 |            |          | on-Intrusive Monitoring             |     |

| 4 |      |            |          | MMARY                               |     |

| 4 |      |            |          |                                     |     |

|   |      |            |          | QUENCE                              |     |

|   |      |            |          | NOME DATH DOMED DOMAI               |     |

|   | 4.3  |            |          | NSMIT PATH POWER DOWN               |     |

|   | 4.4  | 4.4.1      |          | SOR INTERFACE                       |     |

|   |      |            |          | e                                   |     |

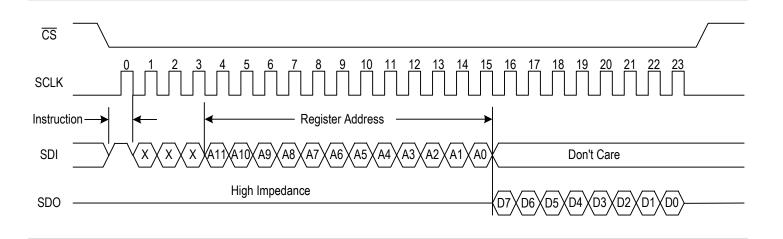

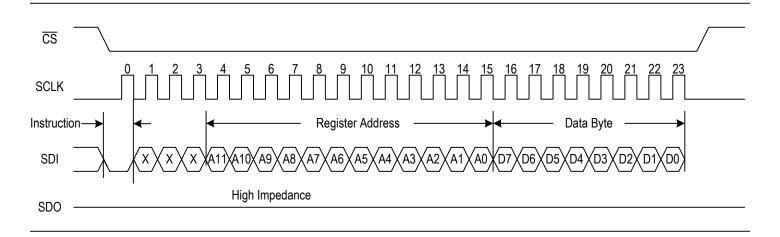

|   | 4.5  |            |          | STER ACCESS SCHEME                  |     |

|   | 4.5  | 4.5.1      |          | Register Read Access                |     |

|   |      | 4.5.2      |          | Register Write Access               |     |

| 5 | DDC  | -          |          | NFORMATION                          |     |

| J |      |            |          |                                     |     |

|   | J. I |            |          | ode                                 |     |

|   |      | J. I. I    | 5.1.1.1  |                                     |     |

|   |      |            |          | Indirect Register                   |     |

|   |      | 512        |          | mulieut Negister                    |     |

|   |      | V. 1.Z     |          |                                     |     |

|   |      |            |          | Indirect Register                   |     |

|   | 5.2  | REGIS      |          | CRIPTION                            |     |

|   | V    |            |          | ode                                 |     |

|   |      | <b>V</b> . | 5.2.1.1  | Direct Register                     |     |

|   |      |            | 5.2.1.2  | Indirect Register                   |     |

|   |      | 5.2.2      | E1 Mode  |                                     |     |

|   |      |            | 5.2.2.1  | Direct Register                     |     |

|   |      |            | 5.2.2.2  | Indirect Register                   |     |

| 6 | IEEI | E STD      |          | JTAG TEST ACCESS PORT               |     |

| - |      |            |          | TIONS AND INSTRUCTION REGISTER (IR) |     |

|   |      |            |          | GISTER                              |     |

|   |      | 6.2.1      |          | dentification Register (IDR)        |     |

|   |      | 6.2.2      |          | Register (BYP)                      |     |

|   |      | 6.2.3      | • •      | ry Scan Register (BSR)              |     |

|   | 6.3  | -          |          | PORT CONTROLLER                     | 343 |

| 7  | PHY  | SICAL AND ELECTRICAL SPECIFICATIONS               | 346   |

|----|------|---------------------------------------------------|-------|

|    | 7.1  | ABSOLUTE MAXIMUM RATINGS                          | . 346 |

|    | 7.2  | RECOMMENDED OPERATING CONDITIONS                  | . 346 |

|    |      | D.C. CHARACTERISTICS                              |       |

|    | 7.4  | DIGITAL I/O TIMING CHARACTERISTICS                | . 348 |

|    | 7.5  | CLOCK FREQUENCY REQUIREMENT                       | . 348 |

|    | 7.6  | T1/J1 LINE RECEIVER ELECTRICAL CHARACTERISTICS    | . 349 |

|    |      | E1 LINE RECEIVER ELECTRICAL CHARACTERISTICS       |       |

|    | 7.8  | T1/J1 LINE TRANSMITTER ELECTRICAL CHARACTERISTICS | . 350 |

|    | 7.9  | E1 LINE TRANSMITTER ELECTRICAL CHARACTERISTICS    | . 351 |

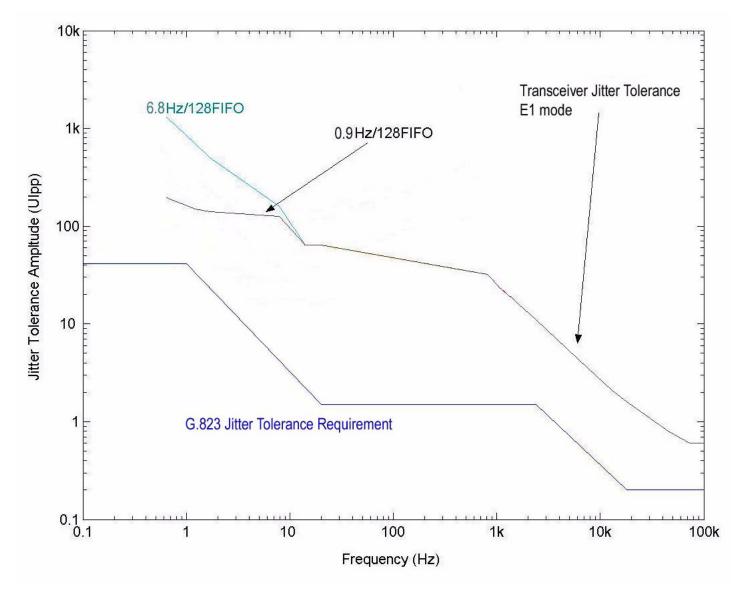

|    | 7.10 | JITTER TOLERANCE                                  |       |

|    |      | 7.10.1 T1/J1 Mode                                 |       |

|    |      | 7.10.2 E1 Mode                                    | . 353 |

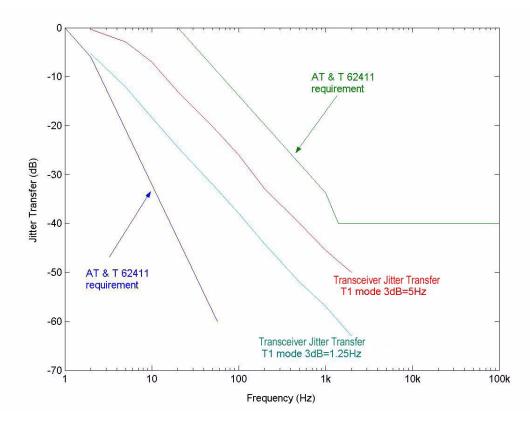

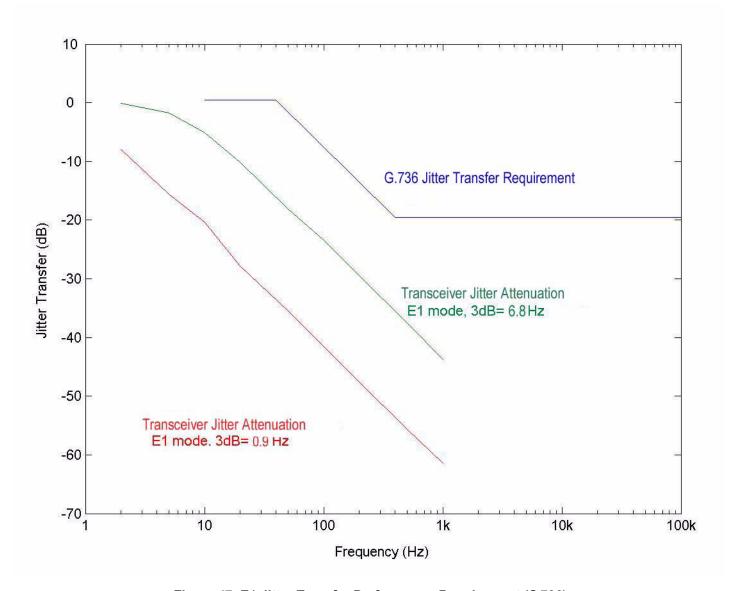

|    | 7.11 | JITTER TRANSFER                                   |       |

|    |      | 7.11.1 T1/J1 Mode                                 |       |

|    |      | 7.11.2 E1 Mode                                    | . 356 |

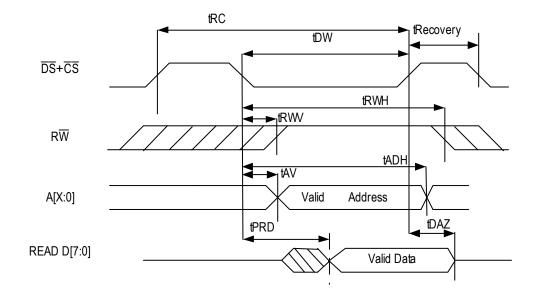

|    | 7.12 | MICROPROCESSOR TIMING SPECIFICATION               |       |

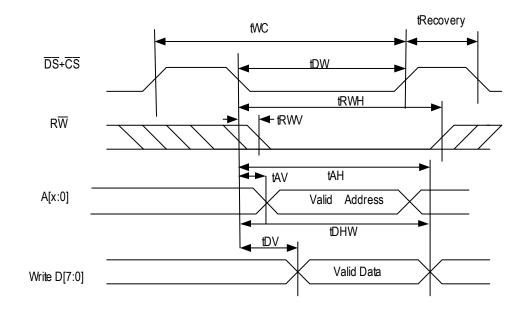

|    |      | 7.12.1 Motorola Non-Multiplexed Mode              | . 357 |

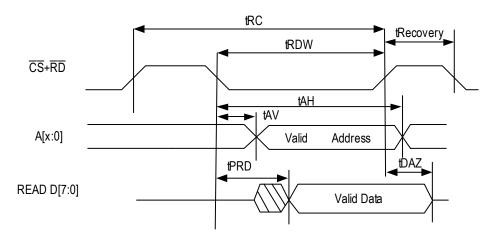

|    |      | 7.12.1.1 Read Cycle Specification                 |       |

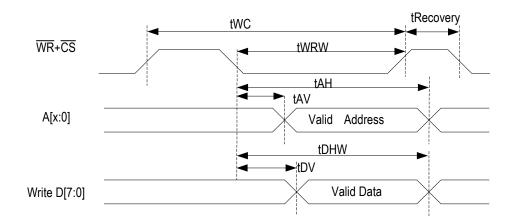

|    |      | 7.12.1.2 Write Cycle Specification                |       |

|    |      | 7.12.2 Intel Non-Multiplexed Mode                 |       |

|    |      | 7.12.2.1 Read Cycle Specification                 |       |

|    |      | 7.12.2.2 Write Cycle Specification                |       |

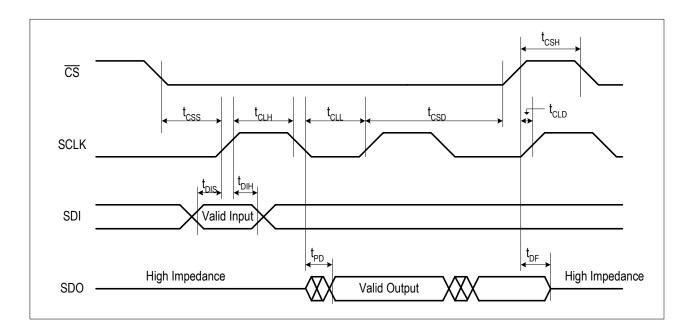

|    |      | 7.12.3 SPI Mode                                   |       |

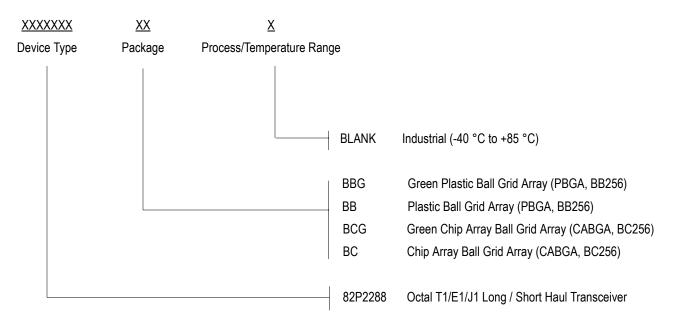

| OF | RDER | RING INFORMATION                                  | . 362 |

| DO | OCUN | MENT HISTORY                                      | 362   |

|    |      |                                                   |       |

# **List of Tables**

| Table 1:  | Operating Mode Selection                            | 23 |

|-----------|-----------------------------------------------------|----|

| Table 2:  | Related Bit / Register In Chapter 3.1               | 23 |

|           |                                                     |    |

| Table 4:  | Related Bit / Register In Chapter 3.2               | 26 |

| Table 5:  | Related Bit / Register In Chapter 3.3 & Chapter 3.4 | 27 |

| Table 6:  | Criteria Of Speed Adjustment Start                  | 28 |

| Table 7:  | Related Bit / Register In Chapter 3.6               | 28 |

| Table 8:  | Excessive Zero Error Definition                     | 30 |

| Table 9:  | LOS Condition In T1/J1 Mode                         | 32 |

| Table 10: | LOS Condition In E1 Mode                            | 32 |

| Table 11: | Related Bit / Register In Chapter 3.7               | 33 |

| Table 12: | The Structure of SF                                 | 34 |

| Table 13: | The Structure of ESF                                | 35 |

| Table 14: | The Structure of T1 DM                              | 36 |

| Table 15: | The Structure of SLC-96                             | 37 |

| Table 16: | Interrupt Source In T1/J1 Frame Processor           | 40 |

| Table 17: | Related Bit / Register In Chapter 3.8.1             | 40 |

| Table 18: | The Structure Of TS0 In CRC Multi-Frame             | 45 |

| Table 19: | FAS/NFAS Bit/Pattern Error Criteria                 | 47 |

| Table 20: | Interrupt Source In E1 Frame Processor              | 49 |

|           | Related Bit / Register In Chapter 3.8.2             |    |

| Table 22: | Monitored Events In T1/J1 Mode                      | 54 |

| Table 23: | Related Bit / Register In Chapter 3.9.1             | 55 |

|           | Monitored Events In E1 Mode                         |    |

| Table 25: | Related Bit / Register In Chapter 3.9.2             | 57 |

|           | RED Alarm, Yellow Alarm & Blue Alarm Criteria       |    |

| Table 27: | Related Bit / Register In Chapter 3.10.1            | 59 |

| Table 28: | Related Bit / Register In Chapter 3.10.2            | 60 |

|           | Related Bit / Register In Chapter 3.11.1            |    |

|           | Interrupt Summarize In HDLC Mode                    |    |

|           | Related Bit / Register In Chapter 3.11.2            |    |

|           | Related Bit / Register In Chapter 3.12              |    |

|           | Related Bit / Register In Chapter 3.13              |    |

|           | Related Bit / Register In Chapter 3.14              |    |

|           | Related Bit / Register In Chapter 3.15              |    |

|           | A-Law Digital Milliwatt Pattern                     |    |

|           | μ-Law Digital Milliwatt Pattern                     |    |

|           | Related Bit / Register In Chapter 3.16              |    |

|           | Operating Modes Selection In T1/J1 Receive Path     |    |

|           | Operating Modes Selection In E1 Receive Path        |    |

| Table 41: | Related Bit / Register In Chapter 3.17              | 79 |

|           | Operating Modes Selection In T1/J1 Transmit Path    |    |

|           | Operating Modes Selection In E1 Transmit Path       |    |

|           | Related Bit / Register In Chapter 3.18              |    |

|           | Related Bit / Register In Chapter 3.19              |    |

|           | Related Bit / Register In Chapter 3.20.1.1          |    |

|           | E1 Frame Generation                                 | 92 |

| Table 10. | Control Over E Dita                                 | വാ |

# OCTAL T1/E1/J1 LONG HAUL / SHORT HAUL TRANSCEIVER

# IDT82P2288

|           | Interrupt Summary In E1 Mode                                            |     |

|-----------|-------------------------------------------------------------------------|-----|

|           | Related Bit / Register In Chapter 3.20.1.2                              |     |

|           | Related Bit / Register In Chapter 3.20.2.1                              |     |

|           | Related Bit / Register In Chapter 3.20.2.2 ~ Chapter 3.20.2.4           |     |

|           | APRM Message Format                                                     |     |

| Table 54: | APRM Interpretation                                                     | 97  |

|           | Related Bit / Register In Chapter 3.20.3                                |     |

|           | Related Bit / Register In Chapter 3.20.4 & Chapter 3.20.5               |     |

|           | Related Bit / Register In Chapter 3.20.6, Chapter 3.20.7 & Chapter 3.21 |     |

|           | Related Bit / Register In Chapter 3.22                                  |     |

|           | Related Bit / Register In Chapter 3.23                                  |     |

|           | PULS[3:0] Setting In T1/J1 Mode                                         |     |

|           | LBO PULS[3:0] Setting In T1 Mode                                        |     |

|           | Transmit Waveform Value For E1 75 W                                     |     |

|           | Transmit Waveform Value For E1 120 W                                    |     |

|           | Transmit Waveform Value For T1 0~133 ft                                 |     |

|           | Transmit Waveform Value For T1 133~266 ft                               |     |

|           | Transmit Waveform Value For T1 266~399 ft                               |     |

|           | Transmit Waveform Value For T1 399~533 ft                               |     |

|           | Transmit Waveform Value For T1 533~655 ft                               |     |

|           | Transmit Waveform Value For J1 0~655ft                                  |     |

|           | Transmit Waveform Value For DS1 0 dB LBO                                |     |

|           | Transmit Waveform Value For DS1 -7.5 dB LBO                             |     |

|           | Transmit Waveform Value For DS1 -15.0 dB LBO                            |     |

|           | Transmit Waveform Value For DS1 -22.5 dB LBO                            |     |

|           | Related Bit / Register In Chapter 3.24                                  |     |

|           | Impedance Matching Value For The Transmitter                            |     |

|           | Related Bit / Register In Chapter 3.25 & Chapter 3.26                   |     |

|           | Related Bit / Register In Chapter 3.27.1                                |     |

|           | Related Bit / Register In Chapter 3.27.2 & Chapter 3.27.3               |     |

|           | Related Bit / Register In Chapter 3.28                                  |     |

|           | Parallel Microprocessor Interface                                       |     |

|           | Related Bit / Register In Chapter 4                                     |     |

|           | IR Code                                                                 |     |

|           | IDR                                                                     |     |

|           | Boundary Scan (BS) Sequence                                             |     |

| Table 85: | TAP Controller State Description                                        | 343 |

# **List of Figures**

| Figure 1. | 256-Pin CABGA and PBGA (Top View)                                                       | 13  |

|-----------|-----------------------------------------------------------------------------------------|-----|

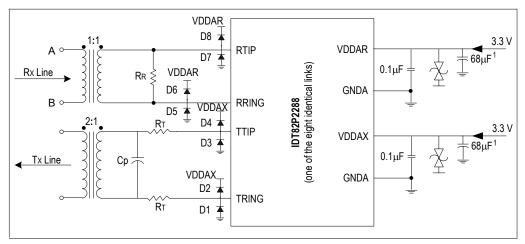

|           | Receive / Transmit Line Circuit                                                         |     |

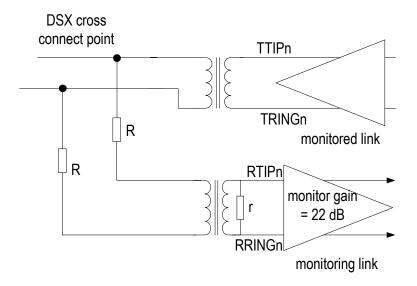

| Figure 3. | Receive Path Monitoring (Twisted Pair)                                                  | 25  |

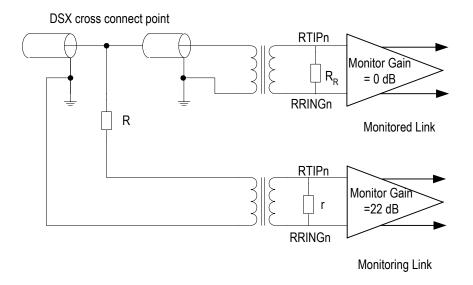

|           | Transmit Path Monitoring (Twisted Pair)                                                 |     |

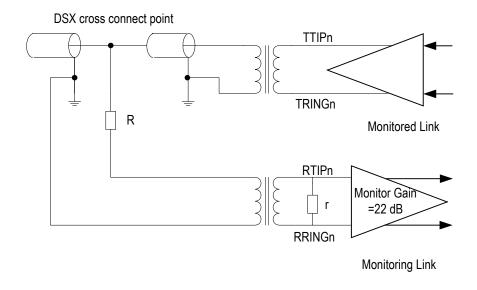

|           | Receive Path Monitoring (COAX)                                                          |     |

| Figure 6. | Transmit Path Monitoring (COAX)                                                         | 26  |

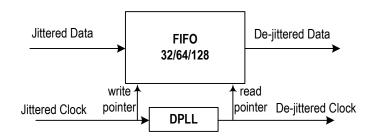

| Figure 7. | Jitter Attenuator                                                                       | 27  |

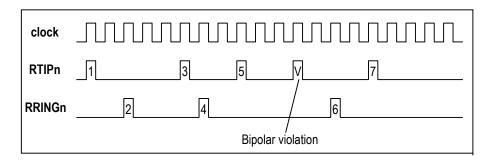

| Figure 8. | AMI Bipolar Violation Error                                                             | 30  |

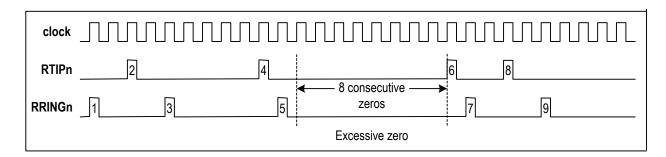

|           | B8ZS Excessive Zero Error                                                               |     |

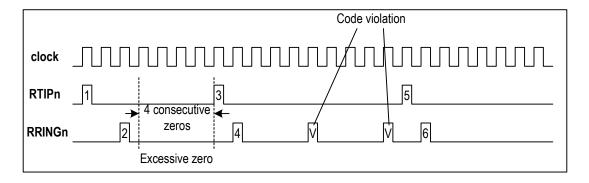

| Figure 10 | HDB3 Code Violation & Excessive Zero Error                                              | 30  |

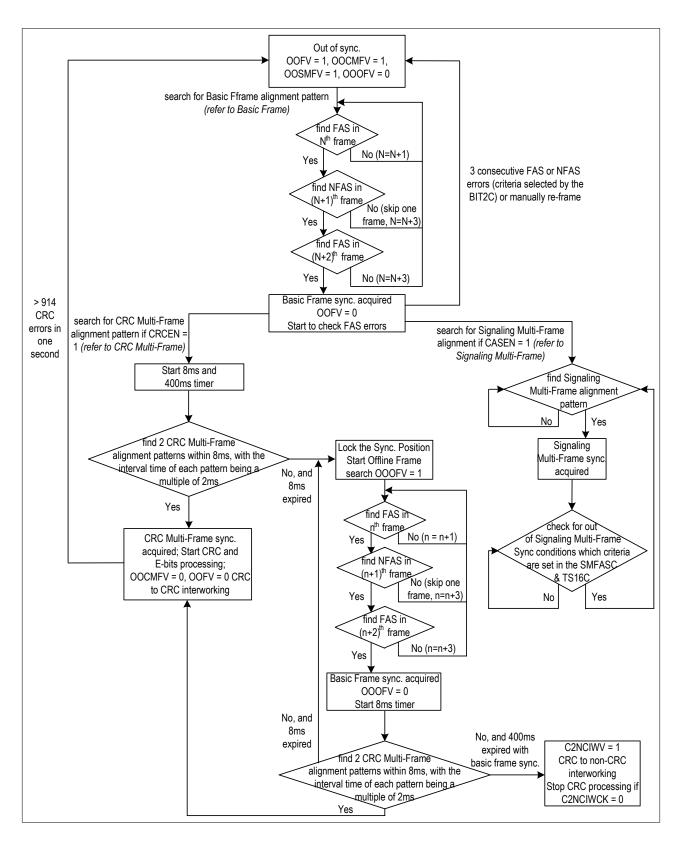

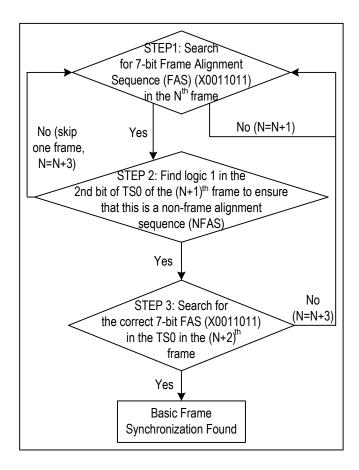

| Figure 11 | E1 Frame Searching Process                                                              | 43  |

| Figure 12 | Basic Frame Searching Process                                                           | 44  |

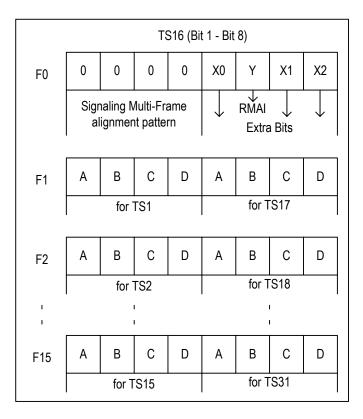

| Figure 13 | TS16 Structure Of CAS Signaling Multi-Frame                                             | 46  |

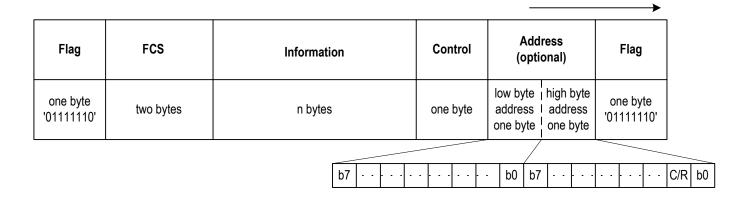

|           | Standard HDLC Packet                                                                    |     |

| Figure 15 | Overhead Indication In The FIFO                                                         | 62  |

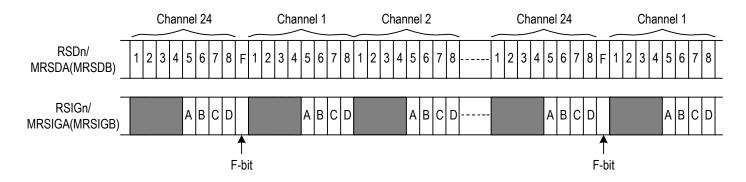

|           | Signaling Output In T1/J1 Mode                                                          |     |

|           | Signaling Output In E1 Mode                                                             |     |

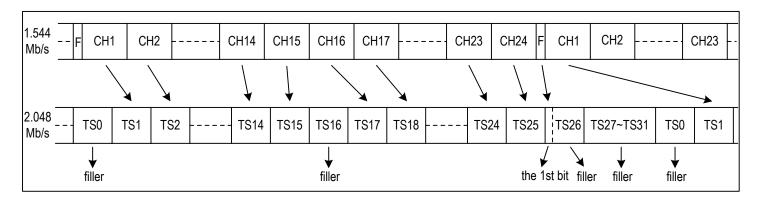

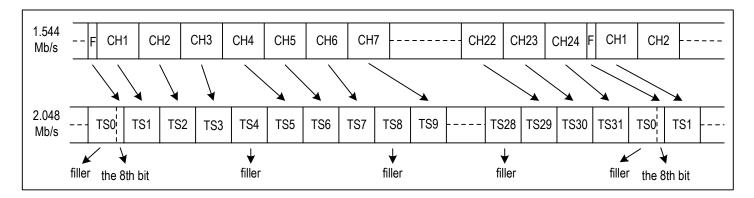

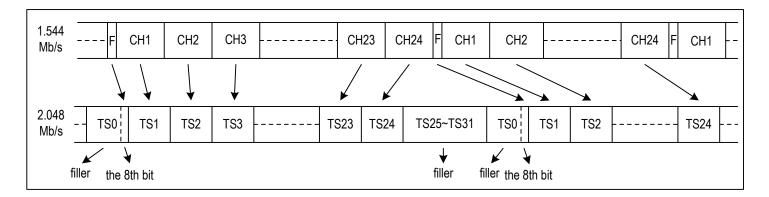

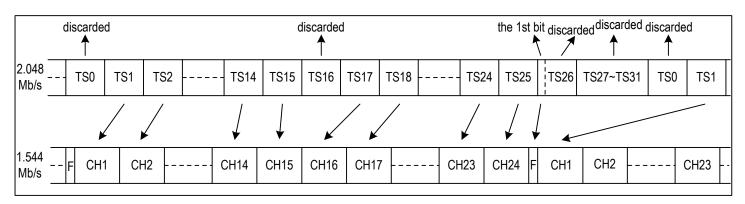

|           | T1/J1 To E1 Format Mapping - G.802 Mode                                                 |     |

| •         | T1/J1 To E1 Format Mapping - One Filler Every Fourth Channel Mode                       |     |

|           | T1/J1 To E1 Format Mapping - Continuous Channels Mode                                   |     |

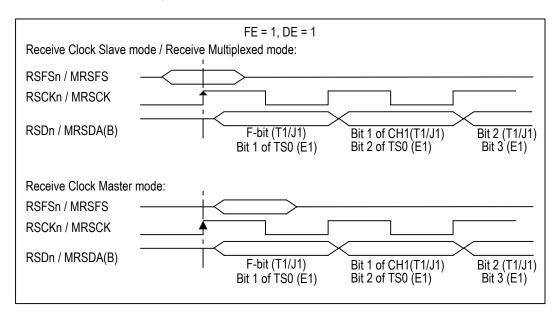

|           | No Offset When FE = 1 & DE = 1 In Receive Path                                          |     |

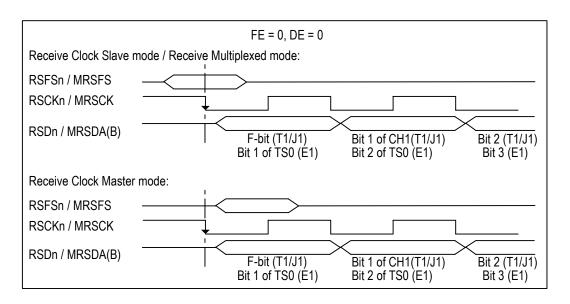

|           | No Offset When FE = 0 & DE = 0 In Receive Path                                          |     |

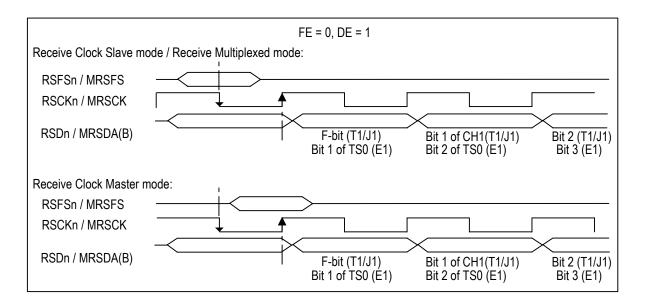

| -         | No Offset When FE = 0 & DE = 1 In Receive Path                                          |     |

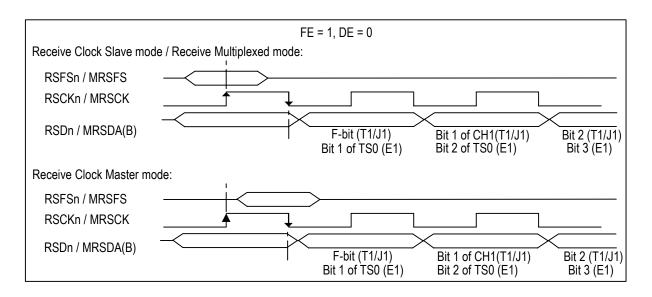

|           | No Offset When FE = 1 & DE = 0 In Receive Path                                          |     |

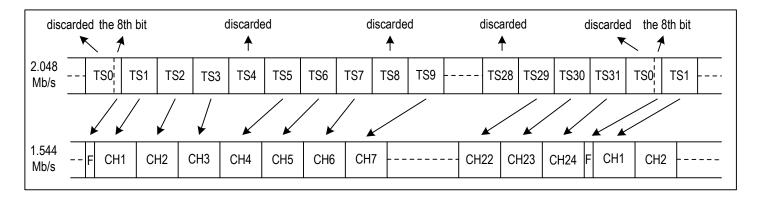

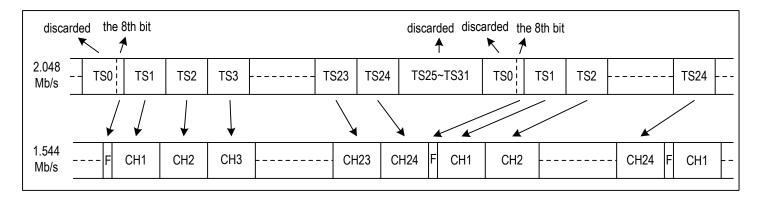

|           | E1 To T1/J1 Format Mapping - G.802 Mode                                                 |     |

|           | E1 To T1/J1 Format Mapping - One Filler Every Fourth Channel Mode                       |     |

|           | E1 To T1/J1 Format Mapping - Continuous Channels Mode                                   |     |

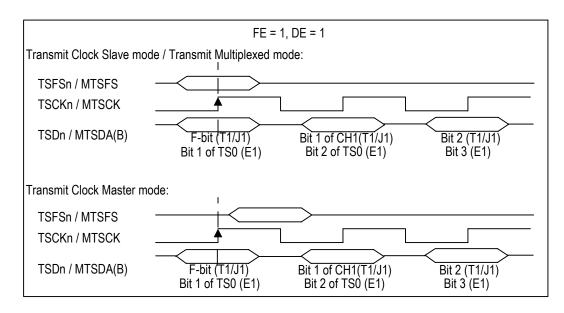

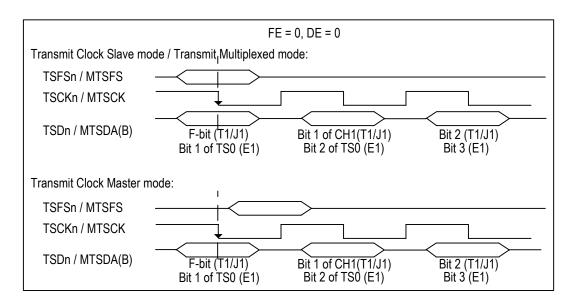

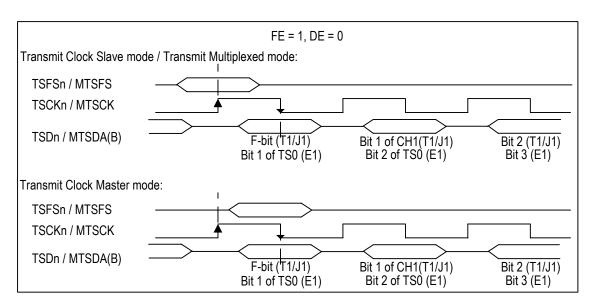

| •         | No Offset When FE = 1 & DE = 1 In Transmit Path                                         |     |

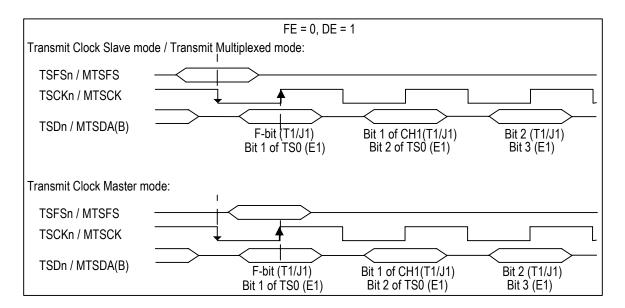

| •         | No Offset When FE = 0 & DE = 0 In Transmit Path                                         |     |

| •         | No Offset When FE = 0 & DE = 1 In Transmit Path                                         |     |

| •         | No Offset When FE = 1 & DE = 0 In Transmit Path                                         |     |

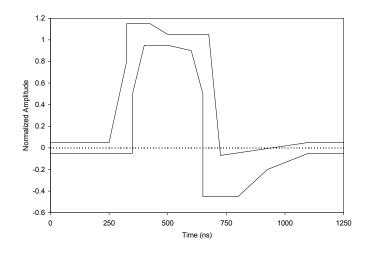

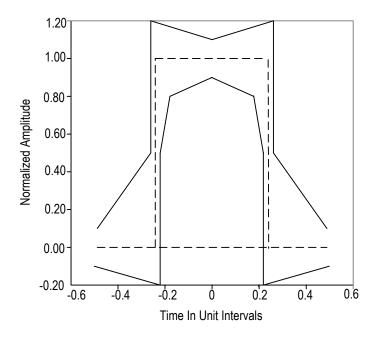

|           | DSX-1 Waveform Template                                                                 |     |

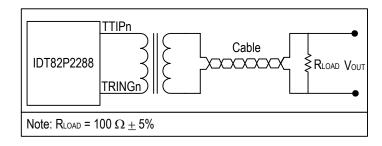

| •         | T1/J1 Pulse Template Measurement Circuit                                                |     |

| •         | E1 Waveform Template                                                                    |     |

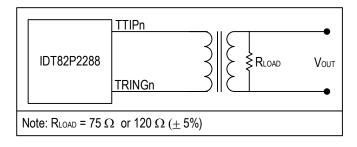

|           | E1 Pulse Template Measurement Circuit                                                   |     |

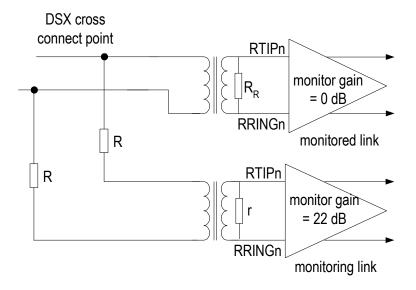

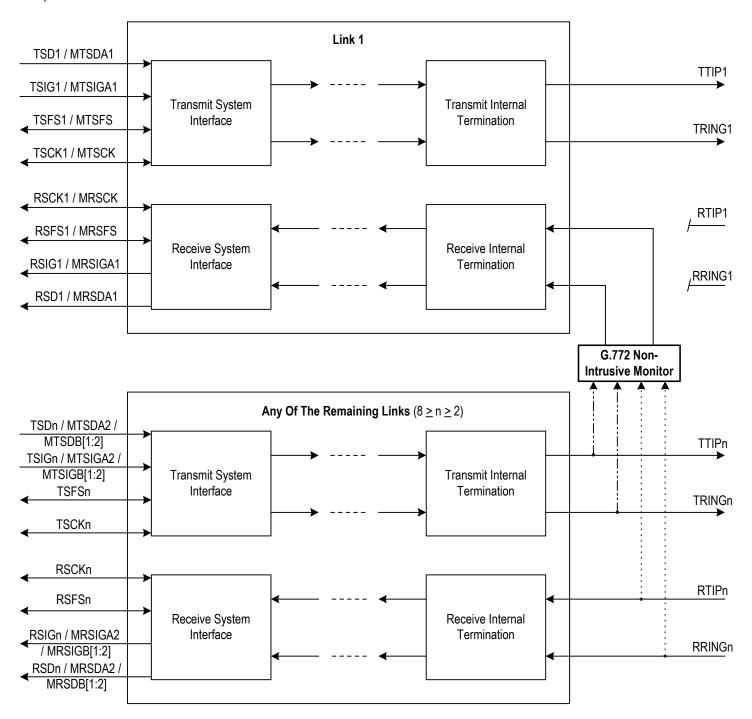

| •         | G.772 Non-Intrusive Monitor                                                             |     |

| •         | Hardware Reset When Powered-Up                                                          |     |

| -         | Hardware Reset In Normal Operation                                                      |     |

| •         | Read Operation In SPI Mode                                                              |     |

| •         | Write Operation In SPI Mode                                                             |     |

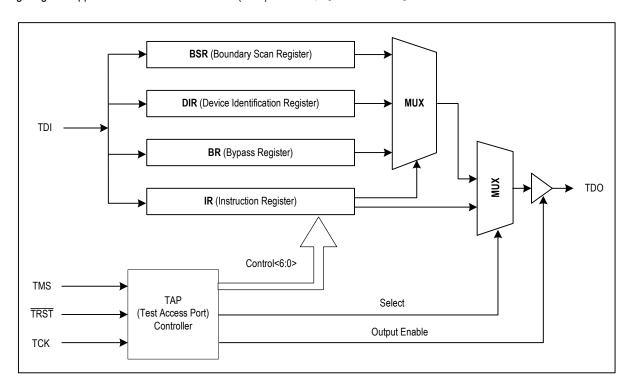

| •         | JTAG Architecture                                                                       |     |

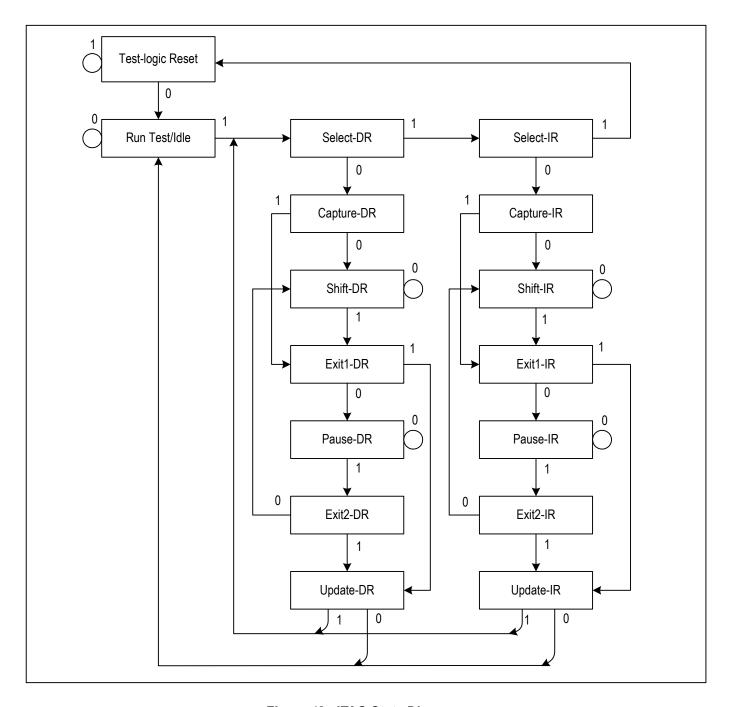

| •         | JTAG State Diagram                                                                      |     |

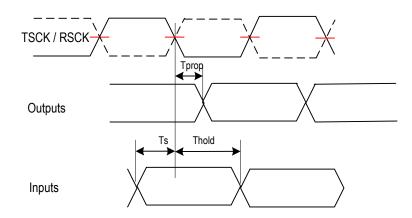

| •         | I/O Timing in Mode                                                                      |     |

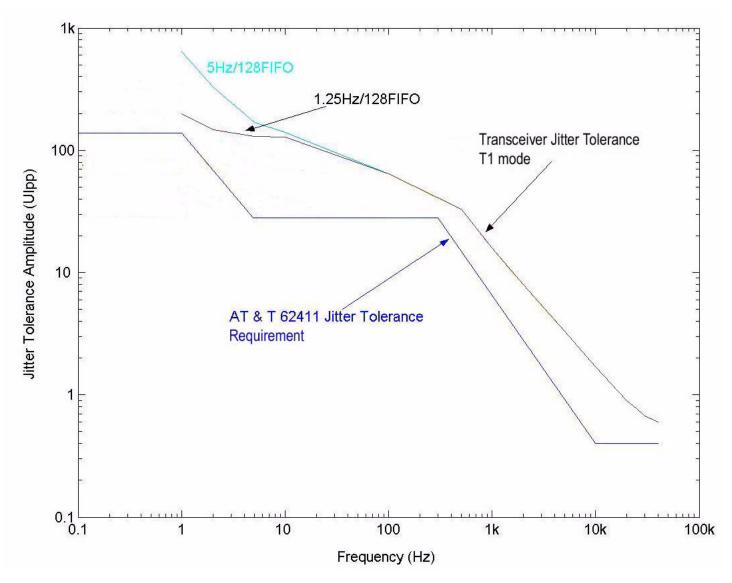

| •         | T1/J1 Jitter Tolerance Performance Requirement                                          |     |

|           | E1 Jitter Tolerance Performance Requirement                                             |     |

|           | T1/J1 Jitter Transfer Performance Requirement (AT&T62411 / GR-253-CORE / TR-TSY-000009) |     |

| -         | E1 Jitter Transfer Performance Requirement (G.736)                                      |     |

| FIGURE 4X | MODOLOIS MODEMINIDIESED MODE RESOLVOIE                                                  | 35/ |

# OCTAL T1/E1/J1 LONG HAUL / SHORT HAUL TRANSCEIVER

| Figure 49. | Motorola Non-Multiplexed Mode Write Cycle | 358 |

|------------|-------------------------------------------|-----|

| •          |                                           | 359 |

|            |                                           | 360 |

|            |                                           | 361 |

List of Figures 10 JANUARY 10, 2011

# Octal T1/E1/J1 Long Haul / Short Haul Transceiver

IDT82P2288

#### **FEATURES**

#### LINE INTERFACE

- Each link can be configured as T1, E1 or J1

- Supports T1/E1/J1 long haul/short haul line interface

- HPS for 1+1 protection without external relays

- Receive sensitivity exceeds -36 dB @ 772 Hz and -43 dB @ 1024 Hz

- Selectable internal line termination impedance: 100  $\Omega$  (for T1), 75  $\Omega$  / 120  $\Omega$  (for E1) and 110  $\Omega$  (for J1)

- Supports AMI/B8ZS (for T1/J1) and AMI/HDB3 (for E1) line encoding/decoding

- Provides T1/E1/J1 short haul pulse templates, long haul LBO (per ANSI T1.403 and FCC68: 0 dB, -7.5 dB, -15 dB, -22 dB) and userprogrammable arbitrary pulse template

- · Supports G.772 non-intrusive monitoring

- Supports T1.102 line monitor

- · Transmit line short-circuit detection and protection

- Separate Transmit and Receive Jitter Attenuators (2 per link)

- Indicates the interval between the write pointer and the read pointer of the FIFO in JA

- Loss of signal indication with programmable thresholds according to ITUT-T G.775, ETS 300 233 (E1) and ANSI T1.403 (T1/J1)

- Supports Analog Loopback, Digital Loopback and Remote Loopback

- Each receiver and transmitter can be individually powered down

#### **FRAMER**

- · Each link can be configured as T1, E1 or J1

- Frame alignment/generation for T1 (per ITU-T G.704, TA-TSY-000278, TR-TSY-000008), E1 (per ITU-T G.704), J1 (per JT G.704) and un-framed mode

- Supports T1/J1 Super Frame and Extended Super Frame, T1 Digital Multiplexer and Switch Line Carrier 96, E1 CRC Multi-frame and Signaling Multi-frame

- Signaling extraction/insertion for CAS and RBS signaling

- Provides programmable system interface supporting Mitel<sup>TM</sup> STbus, AT&T<sup>TM</sup> CHI and MVIP bus, 8.192 Mb/s multiplexed bus and 1.544 Mb/s or 2.048 Mb/s non-multiplexed bus

- Three HDLC controllers per link with separate 128-byte transmit and receive FIFOs per controller

- Programmable bit insertion and bit inversion on per channel/ timeslot basis

- · Provides Bit Oriented Message (BOM) generation and detection

- Provides Automatic Performance Report Message (APRM) generation

- Detects and generates alarms (AIS, RAI)

- Provides performance monitor to count Bipolar Violation error, Excess Zero error, CRC error, framing bit error, far end CRC error, out of frame and change of framing alignment position

- Supports System Loopback, Payload Loopback, Digital Loopback and Inband Loopback

- · Detects and generates selectable PRBS and QRSS

#### **CONTROL INTERFACE**

- Supports Serial Peripheral Interface (SPI) microprocessor and parallel Intel/Motorola non-multiplexed microprocessor interface

- · Global hardware and software reset

- Two general purpose I/O pins

- Per link power down

#### **GENERAL**

- Flexible reference clock (N x 1.544 MHz or N x 2.048 MHz) (0<N<5)</li>

- · JTAG boundary scan

- 3.3 V I/O with 5 V tolerant inputs

- · Low power consumption (Typical 900 mW)

- 3.3 V and 1.8 V power supply

- 256-pin CABGA package

## **APPLICATIONS**

- C.O, PABX, ISDN PRI

- Wireless Base Stations

- T1/E1/J1 ATM Gateways, Multiplexer

- T1/E1/J1 Access Networks

- · LAN/WAN Router

- · Digital Cross Connect

- SONET/SDH Add/Drop Equipment

The IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

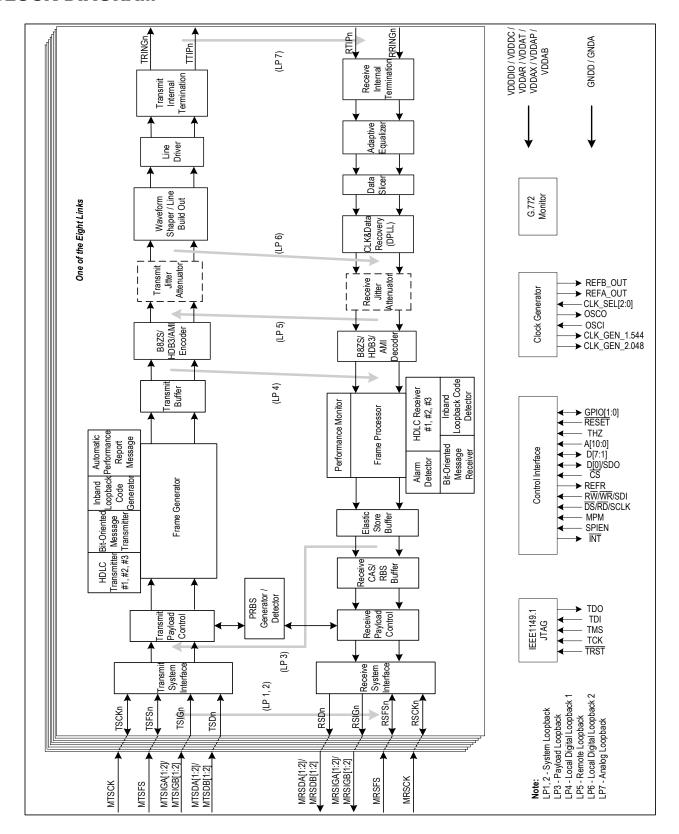

#### **BLOCK DIAGRAM**

**Block Diagram** 12 **JANUARY 10, 2011**

**CENESAS**

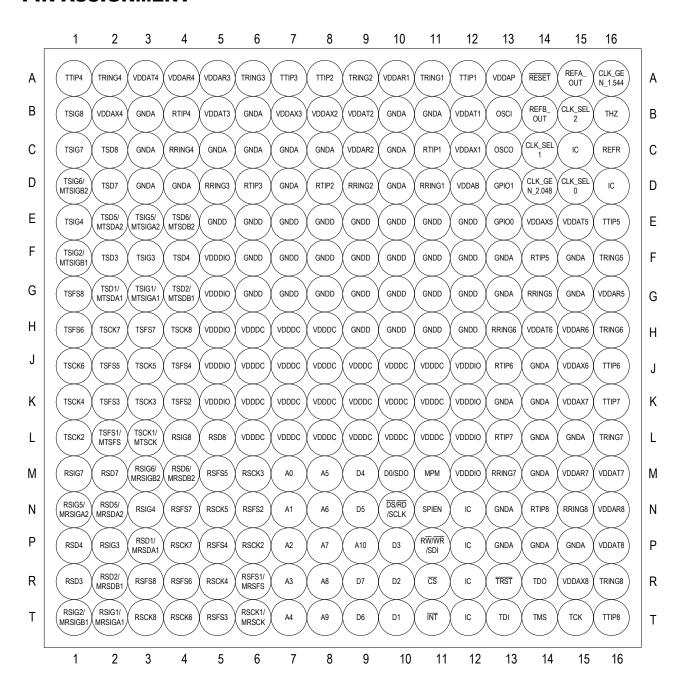

#### PIN ASSIGNMENT

Figure 1. 256-Pin CABGA and PBGA (Top View)

13 **JANUARY 10, 2011 Pin Assignment**

#### 2 **PIN DESCRIPTION**

| Name                                                                                                                     | Туре             | Pin No.                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line and System Interface                                                                                                |                  |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RTIP[1] RTIP[2] RTIP[3] RTIP[4] RTIP[5] RTIP[6] RTIP[6] RTIP[7] RTIP[8]                                                  | Input            | C11<br>D8<br>D6<br>B4<br>F14<br>J13<br>L13<br>N14 | RTIP[1:8] / RRING[1:8]: Receive Bipolar Tip/Ring for Link 1 ~ 8 These pins are the differential line receiver inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RRING[1] RRING[2] RRING[3] RRING[4] RRING[5] RRING[6] RRING[7] RRING[8]                                                  |                  | D11<br>D9<br>D5<br>C4<br>G14<br>H13<br>M13<br>N15 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TTIP[1] TTIP[2] TTIP[3] TTIP[4] TTIP[5] TTIP[6] TTIP[7] TTIP[8]                                                          | Output           | A12<br>A8<br>A7<br>A1<br>E16<br>J16<br>K16<br>T16 | TTIP[1:8] / TRING[1:8]: Transmit Bipolar Tip/Ring for Link 1 ~ 8  These pins are the differential line driver outputs and can be set to high impedance state globally or individually. A logic high on the THZ pin sets all these pins to high impedance state. When the T_HZ bit (b4, T1/J1-023H, / b4, E1-023H,) * is set to '1', the TTIPn/TRINGn pins in the corresponding link are set to high impedance state. Besides, TTIPn/TRINGn will also be set to high impedance state by other ways (refer to Chapter 3.25 Line Driver for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TRING[1] TRING[2] TRING[3] TRING[4] TRING[5] TRING[6] TRING[7] TRING[8]                                                  |                  | A11<br>A9<br>A6<br>A2<br>F16<br>H16<br>L16<br>R16 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

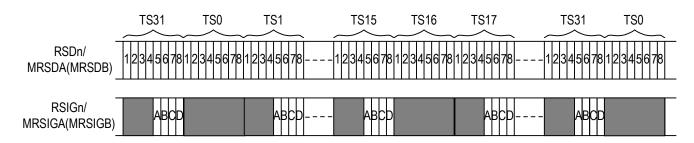

| RSD[1] / MRSDA[1]<br>RSD[2] / MRSDB[1]<br>RSD[3]<br>RSD[4]<br>RSD[5] / MRSDA[2]<br>RSD[6] / MRSDB[2]<br>RSD[7]<br>RSD[8] | High-Z<br>Output | P3<br>R2<br>R1<br>P1<br>N2<br>M4<br>M2<br>L5      | RSD[1:8]: Receive Side System Data for Link 1 ~ 8  The processed data stream is output on these pins.  In Receive Clock Master mode, the RSDn pins are updated on the active edge of the corresponding RSCKn.  In Receive Clock Slave mode, determined by the RSLVCK bit (b4, T1/J1-010H / b4, E1-010H), the RSDn pins are updated on the active edge of the corresponding RSCKn or all eight RSDn pins are updated on the active edge of RSCK[1].  MRSDA[1:2] / MRSDB[1:2]: Multiplexed Receive Side System Data A / B for Link 1 ~ 8  In Receive Multiplexed mode, the MRSDA[1:2] pins or the MRSDB[1:2] pins are used to output the processed data stream. Using a byte-interleaved multiplexing scheme, the MRSDA[1]/MRSDB[1] pins output the data from Link 1 to Link 4, while the MRSDA[2]/MRSDB[2] pins output the data from Link 5 to Link 8. The data on the MRSDA[1:2]/MRSDB[1:2] pins are updated on the active edge of the MRSCK. The data on MRSDA[1:2] is the same as the data on MRSDB[1:2]. MRSDB[1:2] are for back-up purpose. |

#### Note:

Pin Description 14 **JANUARY 10, 2011**

<sup>\*</sup> The contents in the brackets indicate the position of the preceding bit and the address of the register. After the address, if the punctuation ',...' is followed, this bit is in a per-link control register and the listed address belongs to Link 1. Users can find the omitted addresses in Chapter 5. If there is no punctuation following the address, this bit is in a global control register.

| Name                                                                                                                                 | Туре           | Pin No.                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSIG[1] / MRSIGA[1]<br>RSIG[2] / MRSIGB[1]<br>RSIG[3]<br>RSIG[4]<br>RSIG[5] / MRSIGA[2]<br>RSIG[6] / MRSIGB[2]<br>RSIG[7]<br>RSIG[8] | Output         | T2<br>T1<br>P2<br>N3<br>N1<br>M3<br>M1<br>L4 | RSIG[1:8]: Receive Side System Signaling for Link 1 ~ 8  The extracted signaling bits are output on these pins. They are located in the lower nibble (b5 ~ b8) and are channel/timeslot-aligned with the data output on the corresponding RSDn pin.  In Receive Clock Master mode, the RSIGn pins are updated on the active edge of the corresponding RSCKn.  In Receive Clock Slave mode, determined by the RSLVCK bit (b4, T1/J1-010H / b4, E1-010H), the RSIGn pins are updated on the active edge of the corresponding RSCKn or all eight RSIGn are updated on the active edge of RSCK[1].  MRSIGA[1:2] / MRSIGB[1:2]: Multiplexed Receive Side System Signaling A / B for Link 1 ~ 8  In Receive Multiplexed mode, the MRSIGA[1:2] pins or the MRSIGB[1:2] pins are used to output the extracted signaling bits. The signaling bits are located in the lower nibble (b5 ~ b8) and are channel/timeslot-aligned with the data output on the corresponding MRSDA[1:2]/MRSDB[1:2] pins. Using the byte-interleaved multiplexing scheme, the MRSIGA[1]/MRSIGB[1] pins output the signaling bits from Link 1 to Link 4, while the MRSDA[2]/MRSDB[2] pins output the signaling bits from Link 5 to Link 8. The signaling bits on the MRSIGA[1:2]/MRSIGB[1:2] pins are updated on the active edge of the MRSCK. The signaling bits on MRSIGA[1:2] is the same as the signaling bits on MRSIGB[1:2]. MRSIGB[1:2] are for back-up purpose. |

| RSFS[1] / MRSFS<br>RSFS[2]<br>RSFS[3]<br>RSFS[4]<br>RSFS[5]<br>RSFS[6]<br>RSFS[7]<br>RSFS[7]                                         | Output / Input | R6<br>N6<br>T5<br>P5<br>M5<br>R4<br>N4<br>R3 | RSFS[1:8]: Receive Side System Frame Pulse for Link 1 ~ 8  In T1/J1 Receive Clock Master mode, RSFSn outputs the pulse to indicate each F-bit, every second F-bit in SF frame, the first F-bit of every SF/ESF/T1 DM/SLC-96 multi-frame or the first F-bit of every second SF multi-frame. In T1/J1 Receive Clock Slave mode, RSFSn inputs the pulse at a rate of integer multiple of 125 μs to indicate the start of a frame.  In E1 Receive Clock Master mode, RSFSn outputs the pulse to indicate the Basic frame, CRC Multi-frame, Signaling Multi-frame, or both the CRC Multi-frame and Signaling Multi-frame, or the TS1 and TS16 overhead.  In E1 Receive Clock Slave mode, RSFSn inputs the pulse at a rate of integer multiple of 125 μs to indicate the start of a frame.  RSFSn is updated/sampled on the active edge of the corresponding RSCKn. The active polarity of RSFSn is determined by the FSINV bit (b4, T1/J1-048H, / b4, E1-048H,).  MRSFS: Multiplexed Receive Side System Frame Pulse for Link 1 ~ 8  In Receive Multiplexed mode, MRSFS inputs the pulse at a rate of integer multiple of 125 μs to indicate the start of a frame on the multiplexed data bus. MRSFS is sampled on the active edge of MRSCK. The active polarity of MRSFS is determined by the FSINV bit (b4, T1/J1-048H, / b4, E1-048H,).  RSFS[1:8]/MRSCK are Schmitt-triggered inputs/outputs with pull-up resistors.                    |

| RSCK[1] / MRSCK<br>RSCK[2]<br>RSCK[3]<br>RSCK[4]<br>RSCK[5]<br>RSCK[6]<br>RSCK[6]<br>RSCK[7]<br>RSCK[8]                              | Output / Input | T6<br>P6<br>M6<br>R5<br>N5<br>T4<br>P4<br>T3 | RSCK[1:8]: Receive Side System Clock for Link 1 ~ 8  In Receive Clock Master mode, the RSCKn pins output a (gapped) 1.544 MHz (for T1/J1 mode) / 2.048 MHz (for E1 mode) clock used to update the signal on the corresponding RSDn, RSIGn and RSFSn pins.  In Receive Clock Slave mode, the RSCKn pins input a 1.544 MHz (for T1/J1 mode only), 2.048 MHz or 4.096 MHz clock used to update the signals on the corresponding RSDn and RSIGn pins and sample the signals on the corresponding RSFSn pins. Selected by the RSLVCK bit (b4, T1/J1-010H / b4, E1-010H), the RSCK[1] pin can be used for all eight links.  MRSCK: Multiplexed Receive Side System Clock for Link 1 ~ 8  In Receive Multiplexed mode, MRSCK inputs a 8.192 MHz or 16.384 MHz clock used to update the signals on the corresponding MRSDA/MRSDB and MRSIGA/MRSIGB pins and sample the signal on the corresponding MRSPS pin.  RSCK[1:8]/MRSCK are Schmitt-triggered inputs/outputs with pull-up resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Pin Description 15 JANUARY 10, 2011

| Name                                                                                                            | Туре           | Pin No.                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSD[1] / MTSDA[1] TSD[2] / MTSDB[1] TSD[3] TSD[4] TSD[5] / MTSDA[2] TSD[6] / MTSDB[2] TSD[7] TSD[8]             | Input          | G2<br>G4<br>F2<br>F4<br>E2<br>E4<br>D2<br>C2 | TSD[1:8]: Transmit Side System Data for Link 1 ~ 8  The data stream from the system side is input on these pins.  In Transmit Clock Master mode, the TSDn pins are sampled on the active edge of the corresponding TSCKn.  In Transmit Clock Slave mode, selected by the TSLVCK bit (b1, T1/J1-010H / b1, E1-010H), the TSDn pins are sampled on the active edge of the corresponding TSCKn or all eight TSDn pins are sampled on the active edge of TSCK[1].  MTSDA[1:2] / MTSDB[1:2]: Multiplexed Transmit Side System Data A / B for Link 1 ~ 8  In Transmit Multiplexed mode, selected by the MTSDA bit (b2, T1/J1-010H / b2, E1-010H), the MTSDA[1:2] pins or the MTSDB[1:2] pins are used to input the data stream. Using a byte-interleaved multiplexing scheme, the MTSDA[1]/MTSDB[1] pins input the data for Link 1 to Link 4, while the MTSDA[2]/MTSDB[2] pins input the data for Link 5 to Link 8. The data on the MTSDA[1:2]/MTSDB[1:2] pins are sampled on the active edge of MTSCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TSIG[1] / MTSIGA[1] TSIG[2] / MTSIGB[1] TSIG[3] TSIG[4] TSIG[5] / MTSIGA[2] TSIG[6] / MTSIGB[2] TSIG[7] TSIG[8] | Input          | G3<br>F1<br>F3<br>E1<br>E3<br>D1<br>C1<br>B1 | TSIG[1:8]/MTSDA[1:2]/MTSDB[1:2] are Schmitt-triggered inputs.  TSIG[1:8]: Transmit Side System Signaling for Link 1 ~ 8  The signaling bits are input on these pins. They are located in the lower nibble (b5 ~ b8) and are channel/timeslot-aligned with the data input on the corresponding TSDn pin.  In Transmit Clock Master mode, TSIGn is sampled on the active edge of the corresponding TSCKn.  In Transmit Clock Slave mode, selected by the TSLVCK bit (b1, T1/J1-010H / b1, E1-010H), TSIGn is sampled on the active edge of the corresponding TSCKn or all eight TSIGn are updated on the active edge of TSCK[1].  MTSIGA[1:2] / MTSIGB[1:2]: Multiplexed Transmit Side System Signaling A / B for Link 1 ~ 8  In Transmit Multiplexed mode, selected by the MTSDA bit (b2, T1/J1-010H / b2, E1-010H), the MTSIGA[1:2] pins or the MTSIGB[1:2] pins are used to input the signaling bits. The signaling bits are located in the lower nibble (b5 ~ b8) and are channel/timeslot-aligned with the data input on the corresponding MTSDA[1:2]/MTSDB[1:2] pins. Using the byte-interleaved multiplexing scheme, the MTSIGA[1]/MTSIGB[1] pins input the signaling bits for Link 1 to Link 4, while the MTSIGA[2]/MTSIGB[2] pins input the signaling bits for Link 5 to Link 8. The signaling bits on the MTSIGA[1:2]/MTSIGB[1:2] pins are sampled on the active edge of MTSCK.  TSIG[1:8]/MTSIGA[1:2]/MTSIGB[1:2] are Schmitt-triggered inputs.                                                                                                                                                |

| TSFS[1] / MTSFS                                                                                                 | Output / Input | L2<br>K4<br>K2<br>J4<br>J2<br>H1<br>H3<br>G1 | TSFS[1:8]: Transmit Side System Frame Pulse for Link 1 ~ 8 In T1/J1 Transmit Clock Master mode, TSFSn outputs the pulse to indicate each F-bit or the first F-bit of every SF/ESF/T1 DM/SLC-96 multi-frame. In T1/J1 Transmit Clock Slave mode, TSFSn inputs the pulse to indicate each F-bit or the first F-bit of every SF/ESF/T1 DM/SLC-96 multi-frame. In E1 Transmit Clock Master mode, TSFSn outputs the pulse to indicate the Basic frame, CRC Multi-frame and/or Signaling Multi-frame. In E1 Transmit Clock Slave mode, TSFSn inputs the pulse to indicate the Basic frame, CRC Multi-frame and/or Signaling Multi-frame. In E1 Transmit Clock Slave mode, TSFSn inputs the pulse to indicate the Basic frame, CRC Multi-frame and/or Signaling Multi-frame.  TSFSn is updated/sampled on the active edge of the corresponding TSCKn. The active polarity of TSFSn is selected by the FSINV bit (b1, T1/J1-042H,/ b1, E1-042H,).  MTSFS: Multiplexed Transmit Side System Frame Pulse for Link 1 ~ 8 In T1/J1 Transmit Multiplexed mode, MTSFS inputs the pulse to indicate each F-bit or the first F-bit of every SF/ESF/T1 DM/SLC-96 multi-frame of one link on the multiplexed data bus. In E1 Transmit Multiplexed mode, MTSFS inputs the pulse to indicate each Basic frame, CRC Multi-frame and/or Signaling Multi-frame of one link on the multiplexed data bus.  MTSFS is sampled on the active edge of MTSCK. The active polarity of MTSFS is selected by the FSINV bit (b1, T1/J1-042H,/b1, E1-042H,).  TSFS[1:8]/MTSFS are Schmitt-triggered inputs/outputs with pull-up resistors. |

Pin Description 16 JANUARY 10, 2011

| Name                                                                    | Туре           | Pin No.                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------|----------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSCK[1] / MTSCK TSCK[2] TSCK[3] TSCK[4] TSCK[5] TSCK[6] TSCK[7] TSCK[8] | Output / Input | L3<br>L1<br>K3<br>K1<br>J3<br>J1<br>H2<br>H4 | TSCK[1:8]: Transmit Side System Clock for Link 1 ~ 8 In Transmit Clock Master mode, TSCKn outputs a (gapped) 1.544 MHz (for T1/J1 mode) / 2.048 MHz (for E1 mode) clock used to sample the signal on the corresponding TSDn and TSIGn pins and update the signal on the corresponding TSFSn pin. In Transmit Clock Slave mode, TSCKn inputs a 1.544 MHz (for T1/J1 mode only), 2.048 MHz or 4.096 MHz clock used to sample the signal on the corresponding TSDn, TSIGn and TSFSn pins. Selected by the TSLVCK bit (b1, T1/J1-010H / b1, E1-010H), the TSCK[1] can be used for all eight links.  MTSCK: Multiplexed Transmit Side System Clock for Link 1 ~ 8 In Transmit Multiplexed mode, MTSCK inputs a 8.192 MHz or 16.384 MHz clock used to sample the signal on the corresponding MTSDA/MTSDB, MTSIGA/MTSIGB and MTSFS pins.  TSCK[1:8]/MTSCK are Schmitt-triggered inputs/outputs with pull-up resistors. |

|                                                                         |                |                                              | Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OSCI                                                                    | Input          | B13                                          | OSCI: Crystal Oscillator Input This pin is connected to an external clock source. In T1 mode E1 Rate of Transmit System interface, this clock must keep the source same with system transmit clock (TSCKn/MTSCK). The clock frequency of OSCI is defined by CLK_SEL[2:0]. The clock accuracy should be ±32 ppm and duty cycle should be from 40% to 60%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OSCO                                                                    | Output         | C13                                          | OSCO: Crystal Oscillator Output This pin outputs the inverted, buffered clock input from OSCI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLK_SEL[0]<br>CLK_SEL[1]<br>CLK_SEL[2]                                  | Input          | D15<br>C14<br>B15                            | CLK_SEL[2:0]: Clock Selection  These three pins select the input clock signal:  When the CLK_SEL[2] pin is low, the input clock signal is N X 1.544 MHz;  When the CLK_SEL[2] pin is high, the input clock signal is N X 2.048 MHz.  When the CLK_SEL[1:0] pins are '00', the N is 1;  When the CLK_SEL[1:0] pins are '01', the N is 2;  When the CLK_SEL[1:0] pins are '10', the N is 3;  When the CLK_SEL[1:0] pins are '11', the N is 4.  CLK_SEL[2:0] are Schmitt-trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLK_GEN_1.544                                                           | Output         | A16                                          | CLK_GEN_1.544: Clock Generator 1.544 MHz Output This pin outputs the 1.544 MHz clock signal generated by the Clock Generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLK_GEN_2.048                                                           | Output         | D14                                          | CLK_GEN_2.048: Clock Generator 2.048 MHz Output This pin outputs the 2.048 MHz clock signal generated by the Clock Generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| REFA_OUT                                                                | Output         | A15                                          | REFA_OUT: Reference Clock Output A The frequency is 2.048 MHz (E1) or 1.544 MHz (T1/J1) When no LOS is detected, this pin outputs a recovered clock from the Clock and Data Recovery function block of one of the eight links. The link is selected by the RO1[2:0] bits (b2~0, T1/J1-007H / b2~0, E1-007H). When LOS is detected, this pin outputs MCLK or high level, as selected by the REFH_LOS bit (b0, T1/J1-03EH, / b0, E1-03EH,) * Note: MCLK is a clock derived from OSCI using an internal PLL, and the frequency is 2.048 MHz (E1) or 1.544 MHz (T1/J1).                                                                                                                                                                                                                                                                                                                                             |

| REFB_OUT                                                                | Output         | B14                                          | REFB_OUT: Reference Clock Output B The frequency is 2.048 MHz (E1) or 1.544 MHz (T1/J1) When no LOS is detected, this pin outputs a recovered clock from the Clock and Data Recovery function block of one of the eight links. The link is selected by the RO2[2:0] bits (b5~3, T1/J1-007H / b5~3, E1-007H). When LOS is detected, this pin outputs MCLK or high level, as selected by the REFH_LOS bit (b0, T1/J1-03EH, / b0, E1-03EH,). *                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### Note:

Pin Description 17 JANUARY 10, 2011

<sup>\*</sup> This feature is available in ZB revision only.

| Name                                                                                  | Туре              | Pin No.                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|---------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                       | Control Interface |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

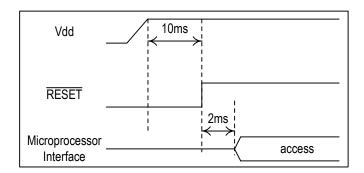

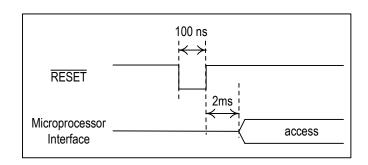

| RESET                                                                                 | Input             | A14                                                      | RESET: Reset (Active Low) A low pulse for more than 100 ns on this pin resets the device. All the registers are accessible 2 ms after the resets.  The RESET pin is a Schmitt-trigger input with a weak pull-up resistor. The OSCI clock must exist when the devireset.                                                                                                                                                                                                                           |  |  |  |