# Dual Synchronous Ethernet Line Card PLL

# Short Form Datasheet IDT82V3396

### **FEATURES**

#### HIGHLIGHTS

- Dual PLL chip:

- Provides node clock for ITU-T G.8261/G.8262 Synchronous Ethernet (SyncE)

- Exceeds GR-253-CORE (OC-12) and ITU-T G.813 (STM-4) jitter generation requirements

- · Provides node clocks for Cellular and WLL base-station (GSM and 3G networks)

- · Provides clocks for 1 Gigabit and 10 Gigabit Ethernet applications

#### MAIN FEATURES

- Employs PLL architecture to feature excellent jitter performance and minimize the number of external components

- Integrates 2 DPLLs; one can be used on the transmit path and the other on the receive path

- Supports programmable DPLL bandwidth: 18 Hz, 35 Hz, 70 Hz and 560 Hz

- Provides OUT1~OUT6 output clock frequencies up to 644.53125

- Includes 25MHz, 125 MHz and 156.25 MHz for CMOS outputs

- Includes 25.78125MHz, 128.90625 MHz and 161.1328125 MHz for CMOS outputs

- Includes 25MHz, 125 MHz, 156.25 MHz, 312.5 MHz and 625 MHz for differential outputs

- Includes 25.78125 MHz, 128.90625 MHz, 161.1328125 MHz, 322.265625 MHz and 644.53125 MHz for differential outputs

- Provides IN1~IN6 input clock frequencies cover from 2 kHz to

- Supports Forced or Automatic operating mode switch controlled by an internal state machine. It supports Free- Run, Locked and Holdover modes

- Supports manual and automatic selected input clock switch

- Supports automatic hitless selected input clock switch on clock fail-

- Supports three types of input clock sources: recovered clock from STM-N or OC-n, PDH network synchronization timing and external synchronization reference timing

- Provides a 2 kHz, 4 kHz, or 8 kHz frame sync input signal, and a 2 kHz or 8 kHz frame sync output signals

- Provides a 1PPS sync input signal and a 1PPS sync output signal

- Provides output clocks for BITS, GPS, 3G, GSM, etc.

- Supports PECL/LVDS and CMOS input/output technologies

- Supports master clock calibration

- Supports Telcordia GR-1244-CORE, Telcordia GR-253-CORE, ITU-T G.812, ITU-T G.8262. ITU-T G.813 and ITU-T G.783 Recommendations

#### OTHER FEATURES

- 12C and Serial microprocessor interface modes

- IEEE 1149.1 JTAG Boundary Scan

- Single 3.3 V operation with 5 V tolerant CMOS I/Os

- 72-pin QFN package, green package options available

#### APPLICATIONS

- 1 Gigabit Ethernet and 10 Gigabit Ethernet

- BITS / SSU

- SMC / SEC (SONET / SDH)

- DWDM cross-connect and transmission equipment

- Synchronous Ethernet equipment

- Central Office Timing Source and Distribution

- Core and access IP switches / routers

- Gigabit and Terabit IP switches / routers

- IP and ATM core switches and access equipment

- Cellular and WLL base-station node clocks

- Broadband and multi-service access equipment

The Short Form Datasheet presented herein represents a product currently in design or being considered for design. The noted characteristics are design targets. Integrated Device Technologies, Incorporated (IDT) reserves the right to change any circuitry or specifications without notice.

IDT and the IDT logo are trademarks of Integrated Device Technology, Inc.

**February 4, 2013**

### **DESCRIPTION**

The IDT82V3396 Dual Synchronous Ethernet Line Card PLL is used to synchronize line cards in Synchronous Ethernet and SONET/SDH equipment, and in wireless base stations. The two independent timing paths allow the device to simultaneously synchronize transmit interfaces with the selected system backplane clock, and provide a recovered clock from a selected receive interface to the system backplane.

The IDT82V3396 accepts up to 6 input references operating at common Ethernet, SONET/SDH and PDH frequencies as well as other frequencies. The references are continually monitored for loss of signal and for frequency offset per user programmed thresholds. The active reference for each of the two Digital PLLs (DPLLs) is determined by forced selection or by automatic selection based on user programmed priorities and locking allowances and based on the reference monitors.

The two IDT82V3396 timing paths are defined by independent DPLLs with embedded clock synthesizers. Both DPLLs support three primary operating modes: Free-Run, Locked and Holdover. In Free-Run mode the DPLLs generate clocks based on the master clock alone. In Locked mode the DPLLs filter reference clock jitter with one of the following selectable bandwidths: 18 Hz, 35 Hz, 70 Hz or 560 Hz. In Locked mode the long-term DPLL frequency accuracy is the same as the long

term frequency accuracy of the selected input reference. In Holdover mode the DPLL uses frequency data acquired while in Locked mode to generate accurate frequencies for short periods.

The IDT82V3396 requires a 12.8 MHz master clock for its reference monitors and other digital circuitry. The frequency accuracy of the master clock determines the frequency accuracy of the DPLLs in Free-Run mode. The frequency stability of the master clock determines the frequency stability of the DPLLs in Free-Run mode and in Holdover mode.

The clocks synthesized by the IDT82V3392 DPLLs can be passed through one of the two independent jitter attenuating APLLs (for jitter sensitive applications). Any of the DPLL or APLL clocks can be routed through a mux to any of the six clock outputs via independent output dividers.

The IDT82V3392 accepts sync pulse inputs that are associated with input references; the sync pulses can have frequencies of 1 Hz, 2 kHz or 8 kHz. The device aligns its output sync pulses with the selected input sync pulse.

All IDT82V3392 read/write registers are accessed through a SPI/I2C microprocessor interface.

Description 2 February 4, 2013

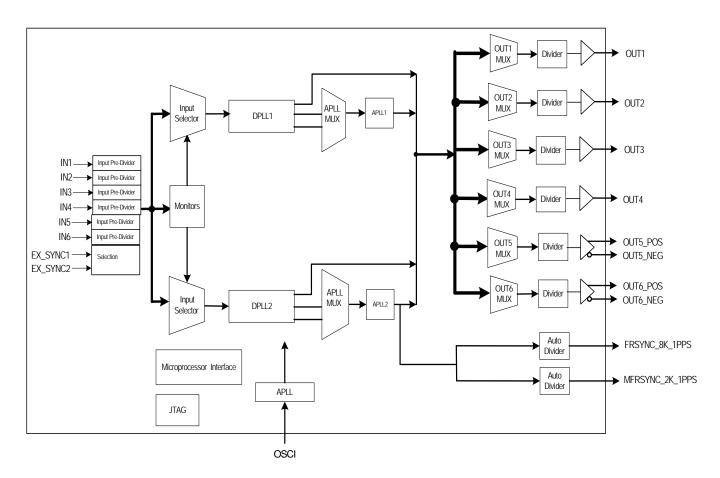

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

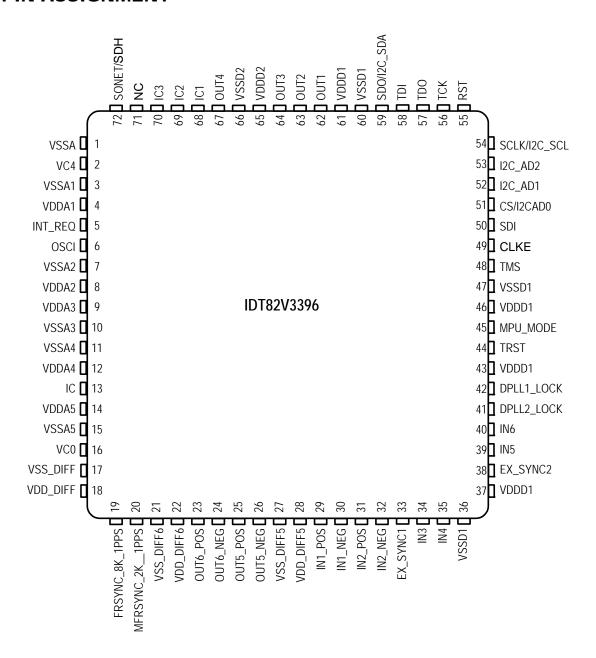

## 1 PIN ASSIGNMENT

Figure 2. Pin Assignment (Top View)

Pin Assignment 4 February 4, 2013

# 2 PIN DESCRIPTION

Table 1: Pin Description

| Name                                | Pin No.  | I/O            | Туре      | Description <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                               |  |

|-------------------------------------|----------|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                     |          |                | -         | Global Control Signal                                                                                                                                                                                                                                                                                                                                                     |  |

| OSCI                                | 6        | I              | CMOS      | OSCI: Crystal Oscillator Master Clock A nominal 12.8000 MHz clock provided by a crystal oscillator is input on this pin. It is the master clock for the device.                                                                                                                                                                                                           |  |

| SONET/SDH                           | 72       | l<br>pull-down | CMOS      | SONET/SDH: SONET / SDH Frequency Selection During reset, this pin determines the default value of the IN_SONET_SDH bit (b2, 09H): High: The default value of the IN_SONET_SDH bit is '1' (SONET); Low: The default value of the IN_SONET_SDH bit is '0' (SDH). After reset, the value on this pin takes no effect.                                                        |  |

| RST                                 | 55       | l<br>pull-up   | CMOS      | RST: Reset A low pulse of at least 50 µs on this pin resets the device. After this pin is high, the device will still be held in reset state for 500 ms (typical).                                                                                                                                                                                                        |  |

|                                     |          | •              | Frame     | Synchronization Input Signal                                                                                                                                                                                                                                                                                                                                              |  |

| EX_SYNC1                            | 33       | I<br>pull-down | CMOS      | EX_SYNC1: External Sync Input 1 A 2 kHz, 4 kHz, 8 kHz, or 1PPS signal is input on this pin.                                                                                                                                                                                                                                                                               |  |

| EX_SYNC2                            | 38       | I<br>pull-down | CMOS      | EX_SYNC2: External Sync Input 1 A 2 kHz, 4 kHz, or 1PPS signal is input on this pin.                                                                                                                                                                                                                                                                                      |  |

|                                     |          |                |           | Input Clock                                                                                                                                                                                                                                                                                                                                                               |  |

| IN1_POS<br>IN1_NEG                  | 29<br>30 | ı              | PECL/LVDS | IN1_POS / IN1_NEG: Positive / Negative Input Clock 1 A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, or 156.25 MHz is differentially input on this pair of pins. Whether the clock signal is PECL or LVDS is automatically detected. |  |

|                                     |          |                |           | Single-ended input for differential input is also supported.  IN2_POS / IN2_NEG: Positive / Negative Input Clock 2  A 2kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz,                                                                                                                                                      |  |

| IN2_POS<br>IN2_NEG                  | 31<br>32 | ı              | PECL/LVDS | 10 MHz, 19.44 MHz, 25MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz, or 156.25 MHz clock is differentially input on this pair of pins. Whether the clock signal is PECL or LVDS is automatically detected.  Single-ended input for differential input is also supported.                                                                                     |  |

| IN3                                 | 34       | I<br>pull-down | CMOS      | IN3: Input Clock 3 A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz or 156.25 MHz clock is input on this pin.                                                                                                                          |  |

| IN4                                 | 35       | l<br>pull-down | CMOS      | IN4: Input Clock 4  A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz or 156.25 MHz clock is input on this pin.                                                                                                                         |  |

| IN5                                 | 39       | l<br>pull-down | CMOS      | IN5: Input Clock 5 A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz or 156.25 MHz clock is input on this pin.                                                                                                                          |  |

| IN6                                 | 40       | I<br>pull-down | CMOS      | IN6: Input Clock 6 A 2 kHz, 4 kHz, N x 8 kHz <sup>3</sup> , 1.544 MHz (SONET) / 2.048 MHz (SDH), 6.25 MHz, 6.48 MHz, 10 MHz, 19.44 MHz, 25 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 155.52 MHz or 156.25 MHz clock is input on this pin.                                                                                                                          |  |

| Output Frame Synchronization Signal |          |                |           |                                                                                                                                                                                                                                                                                                                                                                           |  |

| FRSYN-<br>C_8K_1PPS                 | 19       | 0              | CMOS      | FRSYNC_8K_1PPS: 8 kHz Frame Sync Output An 8 kHz signal or a 1PPS sync signal is output on this pin.                                                                                                                                                                                                                                                                      |  |

Pin Description 5 February 4, 2013

Table 1: Pin Description (Continued)

| Name                 | Pin No.  | I/O            | Туре      | Description <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|----------------------|----------|----------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MFRSYN-<br>C_2K_1PPS | 20       | 0              | CMOS      | MFRSYNC_2K_1PPS: 2 kHz Multiframe Sync Output A 2 kHz signal or a 1PPS sync signal is output on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Output Clock         |          |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| OUT1                 | 62       |                |           | OUT1 ~ OUT4: Output Clock 1 ~ 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| OUT2                 | 63       | 0              | CMOS      | A 1PPS, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 25MHz, 25.78125 MHz, 125 MHz, 128.90625 MHz, 155.52 MHz or 156.25 MHz                                                                                                                                                                                                                                    |  |  |

| OUT3                 | 64       |                |           | or 161.1328125 MHz clock is output on these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| OUT4                 | 67       |                |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| OUT5_POS OUT5_NEG    | 25<br>26 | 0              | PECL/LVDS | OUT5_POS / OUT5_NEG: Positive / Negative Output Clock 5 A 1PPS, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, 25 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 125 MHz, 128.90625 MHz, 155.52 MHz, 156.25 MHz, 161.1328125 MHz, 311.04 MHz, 312.5 MHz, 322.265625 MHz, 622.08 MHz, 625 MHz or 644.53125 MHz                                                                                             |  |  |

|                      |          |                |           | clock is differentially output on these pair of pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| OUT6_POS<br>OUT6_NEG | 23<br>24 | 0              | PECL/LVDS | OUT6_POS / OUT6_NEG: Positive / Negative Output Clock 6 A 1PPS, 400 Hz, 2 kHz, 8 kHz, 64 kHz, N x E1 <sup>4</sup> , N x T1 <sup>5</sup> , N x 13.0 MHz <sup>6</sup> , N x 3.84 MHz <sup>7</sup> , 5 MHz, 10 MHz, 20 MHz, 25 MHz, E3, T3, 6.48 MHz, 19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz, 125 MHz, 128.90625 MHz, 155.52 MHz, 156.25 MHz, 161.1328125 MHz, 311.04 MHz, 312.5 MHz, 322.265625 MHz, 622.08 MHz, 625 MHz or 644.53125MHz clock is differentially output on these pair of pins.                                        |  |  |

| VC4                  | 2        | 0              | Analog    | VC4: T4 APLL VC Output<br>External RC filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| VC0                  | 16       | 0              | Analog    | VC0: T0 APLL VC Output<br>External RC filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                      |          | -              |           | Lock Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| DPLL2_LOCK           | 41       | 0              | CMOS      | DPLL2_LOCK This pin goes high when DPLL2 is locked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DPLL1_LOCK           | 42       | 0              | CMOS      | DPLL1_LOCK This pin goes high when DPLL1 is locked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                      |          |                | Mi        | icroprocessor Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| CS / I2C_AD0         | 51       | I/O<br>pull-up | CMOS      | CS: Chip Selection In Serial mode, this pin is an input.A transition from high to low must occur on this pin for each read or write operation and this pin should remain low until the operation is over.                                                                                                                                                                                                                                                                                                                                          |  |  |

|                      |          |                |           | I2C_AD0: Device Address Bit 0 In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| INT_REQ              | 5        | 0              | CMOS      | INT_REQ: Interrupt Request This pin is used as an interrupt request. The output characteristics are determined by the HZ_EN bit (b1, 0CH) and the INT_POL bit (b0, 0CH).                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| MPU_MODE             | 45       | l<br>pull-down | CMOS      | MPU_MODE: Microprocessor Interface Mode Selection The device supports 2 microprocessor interface modes: I2C and Serial.  During reset, these pins determine the default value of the MPU_SEL_CNFG[0] bit(b0, 7FH) as follows: 0: I2C mode 1: Serial mode After reset, these pins are general purpose inputs. The microprocessor interface mode is selected by the MPU_SEL_CNFG[0] bits (b0, 7FH).  After reset de-assertion, wait 10 µs for the mode to be active. The value of this pin is always reflected by the MPU_PIN_STS[0] bits (b0, 02H). |  |  |

Pin Description 6 February 4, 2013

Table 1: Pin Description (Continued)

| Name           | Pin No.       | I/O              | Туре | Description <sup>1, 2</sup>                                                                                                                                                                                                                                                                                                                  |

|----------------|---------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKE           | 49            | I/O<br>pull-down | CMOS | CLKE: SCLK Active Edge Selection In Serial mode, this pin is an input, it selects the active edge of SCLK to update the SDO: High - The falling edge; Low - The rising edge.                                                                                                                                                                 |

| SDI            | 50            | I/O<br>pull-down | CMOS | SDI: Serial Data Input In Serial mode, this pin is used as the serial data input. Address and data on this pin are serially clocked into the device on the rising edge of SCLK.                                                                                                                                                              |

| SDO / I2C_SDA  | 59            | I/O<br>pull-down | CMOS | SDO: Serial Data Output In Serial mode, this pin is used as the serial data output. Data on this pin is serially clocked out of the device on the active edge of SCLK.  I2C_SDA: Serial Data Input/Output In I2C mode, this pin is used as the input/output for the serial data.                                                             |

| I2C_AD1        | 52            | l<br>pull-up     | CMOS | I2C_AD1: Device Address Bit 1 In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface. In Serial mode, this pin should be connected to ground.                                                                                                                                                                     |

| I2C_AD2        | 53            | l<br>pull-up     | CMOS | I2C_AD2: Device Address Bit 2 In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface. In Serial mode, this pin should be connected to ground.                                                                                                                                                                     |

| SCLK / I2C_SCL | 54            | l<br>pull-down   | CMOS | SCLK: Shift Clock In Serial mode, a shift clock is input on this pin. Data on SDI is sampled by the device on the rising edge of SCLK. Data on SDO is updated on the active edge of SCLK. The active edge is determined by the CLKE.  I2C_SCL: Serial Clock Line                                                                             |

|                |               |                  |      | In I2C mode, the serial clock is input on this pin.                                                                                                                                                                                                                                                                                          |

|                |               |                  |      | JTAG (per IEEE 1149.1)                                                                                                                                                                                                                                                                                                                       |

| TRST           | 44            | l<br>pull-down   | CMOS | TRST: JTAG Test Reset (Active Low) A low signal on this pin resets the JTAG test port. This pin should be connected to ground when JTAG is not used.                                                                                                                                                                                         |

| TMS            | 48            | l<br>pull-up     | CMOS | TMS: JTAG Test Mode Select The signal on this pin controls the JTAG test performance and is sampled on the rising edge of TCK.                                                                                                                                                                                                               |

| TCK            | 56            | I<br>pull-down   | CMOS | TCK: JTAG Test Clock The clock for the JTAG test is input on this pin. TDI and TMS are sampled on the rising edge of TCK and TDO is updated on the falling edge of TCK.  If TCK is idle at a low level, all stored-state devices contained in the test logic will indefinitely retain their state.                                           |

| TDI            | 58            | l<br>pull-up     | CMOS | TDI: JTAG Test Data Input The test data are input on this pin. They are clocked into the device on the rising edge of TCK.                                                                                                                                                                                                                   |

| TDO            | 57            | 0                | CMOS | TDO: JTAG Test Data Output The test data are output on this pin. They are clocked out of the device on the falling edge of TCK. TDO pin outputs a high impedance signal except during the process of data scanning. This pin can indicate the interrupt of T0 selected input clock fail, as determined by the LOS_FLAG_ON_TDO bit (b6, 0BH). |

|                |               |                  |      | Power & Ground                                                                                                                                                                                                                                                                                                                               |

| VDDD1          | 37,43, 46, 61 | Power            | -    | VDDD1: Digital Core Power.                                                                                                                                                                                                                                                                                                                   |

| VDDD2          | 65            | Power            | -    | VDDD2: CMOS CLK Output Power                                                                                                                                                                                                                                                                                                                 |

Pin Description 7 February 4, 2013

Table 1: Pin Description (Continued)

| Name        | Pin No.    | I/O    | Туре | Description <sup>1, 2</sup>                                        |  |  |

|-------------|------------|--------|------|--------------------------------------------------------------------|--|--|

| VDD_DIFF    | 18         | Power  | -    | VDD_DIFF: Differential I/O Power Supply                            |  |  |

| VDD_DIFF6   | 22         | Power  | -    | VDD_DIFF6: Differential I/O Power Supply                           |  |  |

| VDD_DIFF5   | 28         | Power  | -    | VDD_DIFF5: Differential I/O Power Supply                           |  |  |

| VSSD1       | 36, 47, 60 | Ground | -    | VSSD1: Digital Core Ground                                         |  |  |

| VSSD2       | 66         | Ground | -    | VSSD2: CMOS CLK Output Ground                                      |  |  |

| VSS_DIFF    | 17         | Ground | -    | VSS_DIFF: Differential I/O Ground                                  |  |  |

| VSS_DIFF6   | 21         | Ground | -    | VSS_DIFF6: Differential I/O Ground                                 |  |  |

| VSS_DIFF5   | 27         | Ground | -    | VSS_DIFF5: Differential I/O Ground                                 |  |  |

| VSSA        | 1          | Ground | -    | VSSA: Common Ground                                                |  |  |

| VSSA1       | 3          |        |      | VSSAn: T4 & T0 APLL Ground                                         |  |  |

| VSSA2       | 7          |        |      |                                                                    |  |  |

| VSSA3       | 10         | Ground | -    |                                                                    |  |  |

| VSSA4       | 11         |        |      |                                                                    |  |  |

| VSSA5       | 15         |        |      |                                                                    |  |  |

| VDDA1       | 4          |        |      | VDDAn: T4 & T0 APLL Power                                          |  |  |

| VDDA2       | 8          |        |      |                                                                    |  |  |

| VDDA3       | 9          | Power  | -    |                                                                    |  |  |

| VDDA4       | 12         |        |      |                                                                    |  |  |

| VDDA5       | 14         |        |      |                                                                    |  |  |

| L           | Others     |        |      |                                                                    |  |  |

| IC          | 13         |        |      | IC: Internal Connected                                             |  |  |

| IC1         | 68         |        | _    | Internal Use. These pins should be left open for normal operation. |  |  |

| IC2         | 69         |        |      |                                                                    |  |  |

| IC3         | 70         |        |      |                                                                    |  |  |

| NC<br>Note: | 71         | -      | -    | NC: Not Connected                                                  |  |  |

Pin Description 8 February 4, 2013

<sup>1.</sup> All the unused input pins should be connected to ground; the output of all the unused output pins are don't-care.

<sup>2.</sup> The contents in the brackets indicate the position of the register bit/bits.

**<sup>3.</sup>** N x 8 kHz: 1 ≤ N ≤ 19440.

<sup>4.</sup> N x E1: N = 1, 2, 3, 4, 6, 8, 12, 16

<sup>5.</sup> N x T1: N = 1, 2, 3, 4, 6, 8, 12, 16, 24

**<sup>6</sup>**. N x 13.0 MHz: N = 1, 2

<sup>7.</sup> N x 3.84 MHz: N = 1, 2, 4, 8

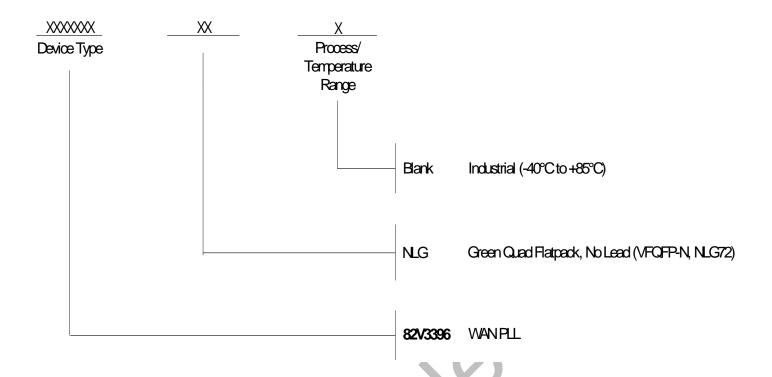

# **ORDERING INFORMATION**

# We've Got Your Timing Solution

6024 Silver Creek Valley Road San Jose, California 95138 Sales

800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775

Fax: 408-284-2775 www.IDT.com/go/contactIDT **Technical Support**

tsd@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's product are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

Copyright 2013. All rights reserved.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Phase Locked Loops - PLL category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

CPLL58-2400-2500 MB15E07SLPFV1-G-BND-6E1 PI6C2409-1HWEX BA4116FV-E2 HMC764LP6CETR HMC820LP6CETR

CY22050KFI LMX2430TMX/NOPB NB3N5573DTG ADF4153ABCPZ PI6C2405A-1LE CD74HC4046AM CPLL66-2450-2450

NJM567D 74HC4046ADB.112 74HC4046APW.112 CY23S05SXI-1 STW81200T ADF4208BRUZ ADF4218LBRUZ ADF4355-3BCPZ

ADF4355BCPZ ADF4169WCCPZ ADF4360-6BCPZ ADF4360-5BCPZRL7 ADF4360-5BCPZ ADF4360-4BCPZRL7 ADF4360-4BCPZ

ADF4360-3BCPZ ADF4360-2BCPZRL7 ADF4252BCPZ ADF4159CCPZ ADF4169CCPZ ADF4360-0BCPZ ADF4360-1BCPZ ADF43601BCPZRL7 ADF4360-2BCPZ ADF4360-3BCPZRL7 ADF4360-7BCPZRL7 ADF4360-8BCPZ ADF4360-8BCPZRL7 ADF4360-9BCPZ

ADF4360-9BCPZRL7 ADF4159CCPZ-RL7 ADF4159WCCPZ ADF4360-0BCPZRL7 AD9901KPZ AD9901KQ ADF4001BCPZ

ADF4002BCPZ-RL7