## **General Description**

The 894D115I-04 is a clock and data recovery circuit. The device is designed to extract the clock signal from a NRZ-coded STM-4 (OC-12/STS-12) or STM-1 (OC-3/STS-3) input data signal. The output signals of the device are the recovered clock and retimed data signals. Input and output are differential signals for best signal integrity and to support high clock and data rates. All control inputs and outputs are single-ended signals. An internal PLL is used for clock generation and recovery. An external clock input is provided to establish an initial operating frequency of the clock recovery PLL and to provide a clock reference in the absence of serial input data. The device supports a signal detect input and a lock detect output. A bypass circuit is provided to facilitate factory tests.

## Features

- Clock recovery for STM-4 (OC-12/STS-12) and STM-1 (OC-3/STS-3)

- Input: NRZ data (622.08 or 155.52 Mbit/s)

- Output: clock signal (622.08MHz or 155.52MHz) and retimed data signal at 622.08 or 155.52 Mbit/s

- Internal PLL for clock generation and clock recovery

- Differential inputs can accept LVPECL levels

- Differential LVDS data and clock outputs

- Lock reference input and PLL lock output

- 19.44MHz reference clock input

- Full 3.3V supply mode

- -40°C to 85°C operating temperature

- Available in lead-free (RoHS 6) package

- See 894D115I for a clock/data recovery circuit with a TSSOP EPAD package and LVPECL outputs

- See 894D115I-01 for a clock/data recovery circuit with LVPECL outputs

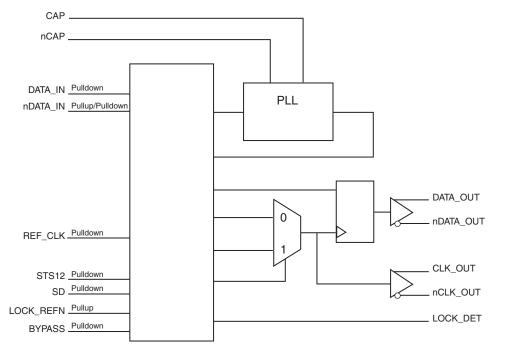

## Block Diagram

## **Pin Assignment**

### 894D115I-04

20-Lead TSSOP 6.5mm x 4.4mm x 0.925mm package body G Package Top View

### **Functional Description**

The 894D115I-04 is designed to extract the clock from a NRZ-coded STM-4 (OC-12/STS-12) or STM-1 (OC-3/STS-3) input data signals. The output signals are the recovered clock and retimed data signals. The device contains an integrated PLL for clock generation and to lock the output clock to the input data stream. The PLL attempts to lock to the reference clock input (REF\_CLK) in absence of the serial data stream or if it is forced to by the control inputs LOCK\_REFN or SD. The output clock frequency is controlled by the STS12 input. The output frequency is 622.08MHz in STM-4/OC-12/STS-12 mode and 155.52MHz in STM-1/OC-3/STS-3 mode.

The 894D115I-04 will maintain an output (CLK\_OUT/ nCLK\_OUT) frequency deviation of less than ±500ppm with respect to the REF\_CLK reference frequency in a loss of signal state (LOS). During the LOS state, the data outputs (DATA\_OUT/ nDATA\_OUT) are held at logic low state. An LOS state of the 894D115I-04 is given when BYPASS is set to the logic low state and either one of the SD or LOCK\_REFN inputs are at a logic low state.

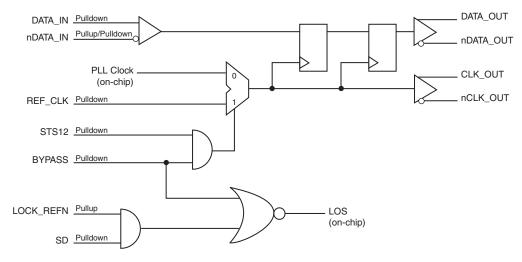

This will enable the use of the SD (signal detect) and the LOCK\_REFN (lock-to-reference) inputs to accept loss of signal status information from electro-optical receivers. Please refer to *Figure 1, "Signal Detect/PLL Bypass Operation Control Diagram",* for details.

The lock detect output (LOCK\_DET) can be used to monitor the operating state of the clock/data recovery circuit. LOCK\_DET is set to logic low level when the internal oscillator of the PLL and the reference clock (REF\_CLK) deviate from each other by more than 500ppm, or when the CDR is forced to lock the REF\_CLK input by the LOCK\_REFN or SD control input. LOCK\_DET is set to high when the PLL is locked to the input data stream and indicates valid clock and data output signals.

The BYPASS pin should be set to logic low state in all applications. BYPASS set to logic high state is used during factory test. In BYPASS mode (BYPASS and STS12 are at logic high state), the internal PLL is bypassed and the inverted REF\_CLK input signal is output at CLK\_OUT/nCLK\_OUT.

Figure 1. Signal Detect/PLL BYPASS Operation Control Diagram

|       | Inj    | Out       | puts |             |             |  |

|-------|--------|-----------|------|-------------|-------------|--|

| STS12 | BYPASS | LOCK_REFN | SD   | DATA_OUT    | CLK_OUT     |  |

| 1     | 0      | 1         | 1    | DATA_IN     | PLL Clock   |  |

| 1     | 0      | 1         | 0    | LOW         | PLL Clock   |  |

| 1     | 0      | 0         | 1    | LOW         | PLL Clock   |  |

| 1     | 0      | 0         | 0    | LOW         | PLL Clock   |  |

| 1     | 1      | X         | Х    | DATA_IN     | REF_CLK     |  |

| 0     | 0      | 1         | 1    | DATA_IN     | PLL Clock   |  |

| 0     | 0      | 1         | 0    | LOW         | PLL Clock   |  |

| 0     | 0      | 0         | 1    | LOW         | PLL Clock   |  |

| 0     | 0      | 0         | 0    | LOW         | PLL Clock   |  |

| 0     | 1      | Х         | Х    | Not Allowed | Not Allowed |  |

### Table 1. Signal Detect/PLL BYPASS Operation Control Table

# **Table 2. Pin Descriptions**

| Number    | Name                   | Т      | уре                 | Description                                                                                                                                                 |

|-----------|------------------------|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 20     | V <sub>DDA</sub>       | Power  |                     | Analog supply pins.                                                                                                                                         |

| 2         | DATA_IN                | Input  | Pulldown            | Non-inverting differential signal input.                                                                                                                    |

| 3         | nDATA_IN               | Input  | Pullup/<br>Pulldown | Inverting differential signal input. V <sub>DD</sub> /2 default when left floating.                                                                         |

| 4, 19     | GND_PLL                | Power  |                     | Power supply ground.                                                                                                                                        |

| 5         | LOCK_DT                | Output |                     | Lock detect output. See Table 4A. Single-ended LVPECL interface levels.                                                                                     |

| 6         | STS12                  | Input  | Pulldown            | STM-4 (OC-12, STS-12) or STM-1 (OC-3, STS-3) selection mode. See Table 4B. LVCMOS/LVTTL interface levels.                                                   |

| 7         | REF_CLK                | Input  | Pulldown            | Reference clock input of 19.44MHz. LVCMOS/LVTTL interface levels.                                                                                           |

| 8         | LOCK_REFN              | Input  | Pullup              | Lock to REF_CLK input. See Table 4C. LVCMOS/LVTTL interface levels.                                                                                         |

| 9         | GND                    | Power  |                     | Power supply ground.                                                                                                                                        |

| 10        | V <sub>DD</sub>        | Power  |                     | Core supply pin.                                                                                                                                            |

| 11,<br>12 | nCLK_OUT,<br>CLK_OUT   | Output |                     | Differential clock output pair. LVDS interface levels.                                                                                                      |

| 13,<br>14 | nDATA_OUT,<br>DATA_OUT | Output |                     | Differential clock output pair. LVDS interface levels.                                                                                                      |

| 15        | SD                     | Input  | Pulldown            | Signal detect input. Typically, SD is driven by the signal detect output of the electro-optical module. See Table 4D. Single-ended LVPECL interface levels. |

| 16        | BYPASS                 | Input  | Pulldown            | PLL bypass mode. See Table 4E. LVCMOS/LVTTL interface levels.                                                                                               |

| 17, 18    | nCAP, CAP              | Input  |                     | External loop filter (1.0µF ±10%).                                                                                                                          |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 3, Pin Characteristics, for typical values.

## **Table 3. Pin Characteristics**

| Symbol                | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance       |                 |         | 4       |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |                 |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                 |         | 51      |         | kΩ    |

## **Function Tables**

#### Table 4A. LOCK\_DET Operation Table

| Operation                                                                                                                                                                                                                                                             | LOCK_DET |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| The PLL is not locked to the serial input data stream if any of these three conditions occur:<br>A. Internal oscillator and REF_CLK input frequency are not within 500ppm of each other.<br>B. SD input is at logic LOW state.<br>C. LOCK_REFN is at logic LOW state. | LOW      |

| When the PLL is locked to the serial input data stream, the CLK_OUT and DATA_OUT signals are valid.                                                                                                                                                                   | HIGH     |

### Table 4B. STS12 Mode Configuration Table

| Input |                                                                                                                                                                                 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STS12 | Operation                                                                                                                                                                       |

| 0     | STM-1 (OC-3, STS-3) operation. The clock/data recovery circuit attempts to recover the clock from a 155.52 Mbit/s input data stream. The output clock frequency is 155.52MHz.   |

| 1     | STM-4 (OC-12, STS-12) operation. The clock/data recovery circuit attempts to recover the clock from a 622.08 Mbit/s input data stream. The output clock frequency is 622.08MHz. |

#### Table 4C. LOCK\_REFN Mode Configuration Table

| Input     |                                                                                                                                                                                                                            |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOCK_REFN | Operation                                                                                                                                                                                                                  |

| 0         | Lock to reference clock. CLK_OUT/nCLK_OUT output frequency is within ±500ppm of the reference clock (REF_CLK). DATA_OUT is set to logic LOW state and nDATA_OUT is set to logic HIGH state. (DATA_OUT = L, nDATA_OUT = H). |

| 1         | Normal operation.                                                                                                                                                                                                          |

### Table 4D. SD Mode Configuration Table

| Input |                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD    | Operation                                                                                                                                                                                                                                                   |

| 0     | Indicates a loss-of-signal (LOS) condition to the device. CLK_OUT/nCLK_OUT output frequency is within ±500ppm of the reference clock (REF_CLK). DATA_OUT is set to logic LOW state and nDATA_OUT is set to logic HIGH state. (DATA_OUT = L, nDATA_OUT = H). |

| 1     | Normal operation.                                                                                                                                                                                                                                           |

### Table 4E. BYPASS Mode Configuration Table

| Input  |                                                                                                   |

|--------|---------------------------------------------------------------------------------------------------|

| BYPASS | Operation                                                                                         |

| 0      | Normal operation.                                                                                 |

| 1      | PLL bypassed (for factory test). The inverted REF_CLK input signal is output at CLK_OUT/nCLK_OUT. |

## **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics or AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                     | Rating                          |

|------------------------------------------|---------------------------------|

| Supply Voltage, V <sub>DD</sub>          | 4.6V                            |

| Inputs, V <sub>I</sub>                   | -0.5V to V <sub>DD</sub> + 0.5V |

| Outputs, I <sub>O</sub> (LVDS)           |                                 |

| Continuos Current                        | 10mA                            |

| Surge Current                            | 15mA                            |

| Outputs, I <sub>O</sub> (LVPECL)         |                                 |

| Continuous Current                       | 50mA                            |

| Surge Current                            | 100mA                           |

| Package Thermal Impedance, $\theta_{JA}$ | 81.3°C/W (0 mps)                |

| Storage Temperature, T <sub>STG</sub>    | -65°C to 150°C                  |

## **DC Electrical Characteristics**

#### Table 5A. Power Supply DC Characteristics, $V_{DD} = 3.3V \pm 5\%$ , T = -40°C to 85°C

| Symbol           | Parameter             | Test Conditions | Minimum                | Typical | Maximum         | Units |

|------------------|-----------------------|-----------------|------------------------|---------|-----------------|-------|

| V <sub>DD</sub>  | Core Supply Voltage   |                 | 3.135                  | 3.3     | 3.465           | V     |

| V <sub>DDA</sub> | Analog Supply Voltage |                 | V <sub>DD</sub> – 0.10 | 3.3     | V <sub>DD</sub> | V     |

| I <sub>DD</sub>  | Power Supply Current  |                 |                        |         | 112             | mA    |

| I <sub>DDA</sub> | Analog Supply Current |                 |                        |         | 10              | mA    |

### Table 5B. LVCMOS/LVTTL DC Characteristics, V\_{DD} = 3.3V $\pm$ 5%, T = -40°C to 85°C

| Symbol          | Parameter          | Test Conditions | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------|-----------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage |                 | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage  |                 | -0.3    |         | 0.8                   | V     |

# RENESAS

| Symbol                  | Parameter          |                           | Test Conditions                                | Minimum | Typical | Maximum | Units |

|-------------------------|--------------------|---------------------------|------------------------------------------------|---------|---------|---------|-------|

| ц <sub>н</sub>          | Input High Current | REF_CLK,<br>STS12, BYPASS | $V_{DD} = V_{IN} = 3.465V$                     |         |         | 150     | μA    |

|                         |                    | LOCK_REFN                 | $V_{DD} = V_{IN} = 3.465V$                     |         |         | 10      | μA    |

| I <sub>IL</sub> Input I | Input Low Current  | REF_CLK,<br>STS12, BYPASS | $V_{DD} = 3.465 V, V_{IN} = 0 V$               | -10     |         |         | μA    |

|                         | •                  | LOCK_REFN                 | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -150    |         |         | μA    |

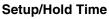

### Table 5C. Differential DC Characteristics, $V_{DD}$ = 3.3V ± 5%, T = -40°C to 85°C

| Symbol                 | Parameter             |                  | Test Conditions                                | Minimum                | Typical | Maximum               | Units |

|------------------------|-----------------------|------------------|------------------------------------------------|------------------------|---------|-----------------------|-------|

| I <sub>IH</sub>        | Input High Current    | DATA_IN/nDATA_IN | $V_{DD} = V_{IN} = 3.465V$                     |                        |         | 150                   | μA    |

|                        |                       | DATA_IN          | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -10                    |         |                       | μA    |

| ۱                      | Input Low Current     | nDATA_IN         | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -150                   |         |                       | μA    |

| V <sub>IH</sub>        | Input High Voltage    |                  |                                                | V <sub>DD</sub> – 1.75 |         | V <sub>DD</sub> – 0.4 | V     |

| V <sub>IL</sub>        | Input Low Voltage     |                  |                                                | V <sub>DD</sub> – 2.0  |         | V <sub>DD</sub> – 0.7 | V     |

| $\Delta V_{\text{IN}}$ | Differential Input Vo | oltage           |                                                | 250                    |         |                       | mV    |

## Table 5D. LVPECL DC Characteristics, $V_{DD} = 3.3V \pm 5\%$ , T = -40°C to 85°C

| Symbol          | Parameter                      |         | Test Conditions                                | Minimum                | Typical | Maximum               | Units |

|-----------------|--------------------------------|---------|------------------------------------------------|------------------------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage             | SD      |                                                | V <sub>DD</sub> -1.125 |         |                       | V     |

| V <sub>IL</sub> | Input Low Voltage              | SD      |                                                |                        |         | V <sub>DD</sub> – 1.5 | V     |

| I <sub>IH</sub> | Input High Current             | SD      | $V_{DD} = V_{IN} = 3.465V$                     |                        |         | 150                   | μA    |

| IIL             | Input Low Current              | SD      | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -10                    |         |                       | μA    |

| V <sub>OH</sub> | Output High Voltage;<br>NOTE 1 | LOCK_DT |                                                | V <sub>DD</sub> – 1.4  |         | V <sub>DD</sub> – 0.9 | V     |

| V <sub>OL</sub> | Output Low Voltage<br>NOTE 1   | LOCK_DT |                                                | V <sub>DD</sub> – 2.0  |         | V <sub>DD</sub> – 1.7 | V     |

NOTE 1: Outputs terminated with 50  $\Omega$  to V\_DD – 2V.

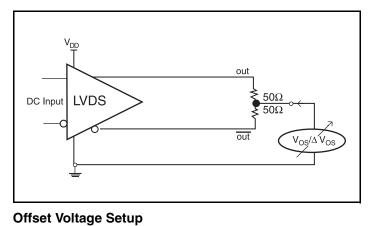

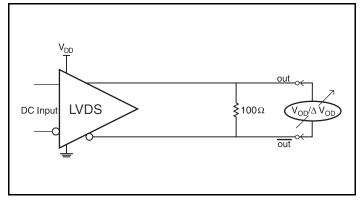

# Table 5E. LVDS DC Characteristics, $V_{DD} = 3.3V \pm 5\%$ , T = -40°C to 85°C

| Symbol          | Parameter                        | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|----------------------------------|-----------------|---------|---------|---------|-------|

| V <sub>OD</sub> | Differential Output Voltage      |                 | 247     | 380     | 454     | mV    |

| $\Delta V_{OD}$ | V <sub>OD</sub> Magnitude Change |                 |         | 5       | 50      | mV    |

| V <sub>OS</sub> | Offset Voltage                   |                 | 1.125   | 1.25    | 1.375   | V     |

| $\Delta V_{OS}$ | V <sub>OS</sub> Magnitude Change |                 |         | 5       | 50      | mV    |

# **AC Electrical Characteristics**

| Parameter                       | Symbol                     |                         | Test Conditions                                                     | Minimum | Typical | Maximum | Units |

|---------------------------------|----------------------------|-------------------------|---------------------------------------------------------------------|---------|---------|---------|-------|

| f <sub>VCO</sub>                | VCO Center Frequency       |                         |                                                                     |         | 622.08  |         | MHz   |

| f <sub>TOL</sub>                | CRU's Refer<br>Frequency T |                         |                                                                     | -250    |         | 250     | ppm   |

| fT <sub>REF_CLK</sub>           | OC-12/STS-12 Capture Range |                         | With respect to the fixed<br>reference frequency                    |         | ±500    |         | ppm   |

| t <sub>LOCK</sub>               | Acquisition<br>Lock Time   | OC-12/STS-12            | Valid REF_CLK and device already<br>powered-up                      |         |         | 16      | μs    |

| J <sub>GEN_CLK</sub>            | Jitter<br>Generation       | CLK_OUT/<br>nCLK_OUT    | 14ps rms (max.) jitter on<br>DATA_IN/nDATA_IN                       |         | 0.005   | 0.01    | UI    |

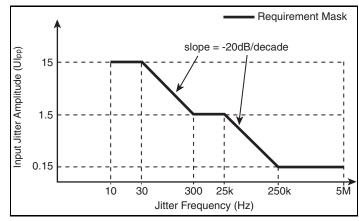

| J <sub>TOL</sub>                | Jitter<br>Tolerance        | OC-12/STS-12;<br>NOTE 1 | Sinusoidal input jitter of DATA_IN/<br>nDATA_IN from 250kHz to 5MHz | 0.45    |         |         | UI    |

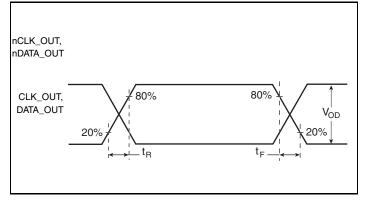

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/               | Fall Time; NOTE 1       | 20% to 80%                                                          |         |         | 500     | ps    |

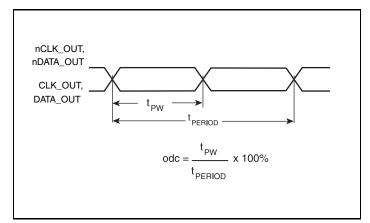

| odc                             | Output Duty                | Cycle; NOTE 1           | 20% minimum transition density                                      | 45      |         | 55      | %     |

|                                 |                            |                         | STS-3                                                               | 2000    | 3220    |         | ps    |

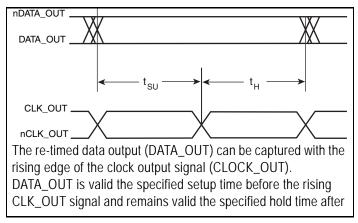

| t <sub>S</sub>                  | Setup Time;                | NUTET                   | STS-12                                                              | 450     | 800     |         | ps    |

| +                               |                            |                         | STS-3                                                               | 3000    | 3220    |         | ps    |

| t <sub>H</sub>                  | Hold Time; N               |                         | STS-12                                                              | 650     | 800     |         | ps    |

NOTE 1: See diagram in Parameter Measurement Information section.

# **Parameter Measurement Information**

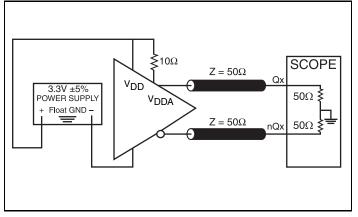

LVDS 3.3V Output Load AC Test Circuit

Output Duty Cycle/Pulse Width/Period

**Jitter Tolerance Specification**

**Differential Input Level**

# RENESAS

# Parameter Measurement Information, continued

#### **Output Rise/Fall Time**

**Differential Output Voltage Setup**

# **Application Information**

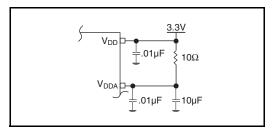

## **Power Supply Filtering Technique**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The 894D115I-04 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL. V<sub>DD</sub> and V<sub>DDA</sub> should be individually connected to the power supply plane through vias, and 0.01µF bypass capacitors should be used for each pin. *Figure 2* illustrates this for a generic V<sub>DD</sub> pin and also shows that V<sub>DDA</sub> requires that an additional 10 $\Omega$  resistor along with a 10µF bypass capacitor be connected to the V<sub>DDA</sub> pin.

Figure 2. Power Supply Filtering

### **Recommendations for Unused Input and Output Pins**

#### Inputs:

#### **LVCMOS Control Pins**

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

### **Outputs:**

### LVDS Outputs

All unused LVDS output pairs can be either left floating or terminated with  $100\Omega$  across. If they are left floating, there should be no trace attached.

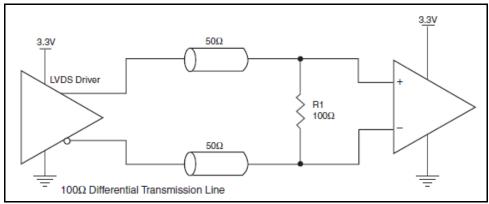

### 3.3V LVDS Driver Termination

A general LVDS interface is shown in *Figure 3.* In a  $100\Omega$  differential transmission line environment, LVDS drivers require a

Figure 3. Typical LVDS Driver Termination

matched load termination of  $100\Omega$  across near the receiver input.

## **Power Considerations**

This section provides information on power dissipation and junction temperature for the 894D115I-04. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the 894D115I-04 is the sum of the core power plus the power dissipated in the load(s). The following is the power dissipation for  $V_{DD} = 3.465V$ , which gives worst case results.

NOTE: Please refer to Section 3 for details on calculating power dissipated in the load.

#### Core and LVDS Output Power Dissipation

Power (core, LVDS)<sub>MAX</sub> = V<sub>DD\_MAX</sub> \* (I<sub>DD\_MAX</sub> + I<sub>DDA\_MAX</sub>) = 3.4655V \* (92mA + 10mA) = 353.43mW

#### Single-ended LVPECL Output Power Dissipation

• Power (LVPECL outputs)<sub>MAX</sub> = **19.8mW (for logic high)**

Total Power\_MAX (3.465V, with all outputs switching) = 353.43mW + 19.8mW = 373.23mW

#### 2. Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the device. The maximum recommended junction temperature for HiPerClockS devices is 125°C.

Lower temperature refers to ambient temperature, maximum temperature refers to case temperature.

#### Table 7. Thermal Resistance $\theta_{JA}$ for 20 Lead TSSOP, Forced Convection

| θ <sub>JA</sub> by Velocity                 |          |          |          |  |

|---------------------------------------------|----------|----------|----------|--|

| Meters per Second                           | 0        | 1        | 2.5      |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 81.3°C/W | 76.9°C/W | 74.8°C/W |  |

## **Reliability Information**

Table 8.  $\theta_{\text{JA}}$  vs. Air Flow Table for a 20 Lead TSSOP

| θ <sub>JA</sub> by Velocity                 |          |          |          |  |  |

|---------------------------------------------|----------|----------|----------|--|--|

| Meters per Second                           | 0        | 1        | 2.5      |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 81.3°C/W | 76.9°C/W | 74.8°C/W |  |  |

### **Transistor Count**

The transistor count for 894D115I-04 is: 10,557

Compatible with VSC8115

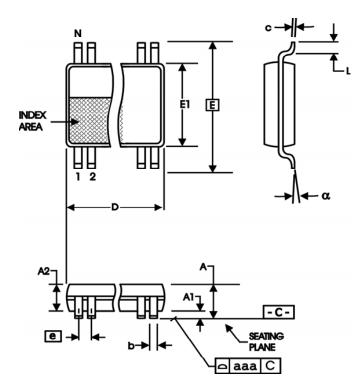

# Package Outline and Package Dimensions

Package Outline - G Suffix for 20 Lead TSSOP

#### Table 9. Package Dimensions

|        | All Dimensions in Millimeters |            |  |  |  |  |  |

|--------|-------------------------------|------------|--|--|--|--|--|

| Symbol | Minimum                       | Maximum    |  |  |  |  |  |

| N      |                               | 20         |  |  |  |  |  |

| Α      |                               | 1.20       |  |  |  |  |  |

| A1     | 0.05                          | 0.15       |  |  |  |  |  |

| A2     | 0.80                          | 1.05       |  |  |  |  |  |

| b      | 0.19                          | 0.30       |  |  |  |  |  |

| С      | 0.09                          | 0.20       |  |  |  |  |  |

| D      | 6.40                          | 6.60       |  |  |  |  |  |

| E      | 6.40                          | Basic      |  |  |  |  |  |

| E1     | 4.30                          | 4.50       |  |  |  |  |  |

| е      | 0.65                          | Basic      |  |  |  |  |  |

| L      | 0.45                          | 0.75       |  |  |  |  |  |

| α      | 0°                            | <b>8</b> ° |  |  |  |  |  |

| aaa    |                               | 0.10       |  |  |  |  |  |

Reference Document: JEDEC Publication 95, MO-153

# **Ordering Information**

### Table 10. Ordering Information

| Part/Order Number | Marking      | Package                   | Shipping Packaging | Temperature   |

|-------------------|--------------|---------------------------|--------------------|---------------|

| 894D115AGI-04LF   | ICSD115AI04L | "Lead-Free" 20 Lead TSSOP | Tube               | -40°C to 85°C |

| 894D115AGI-04LFT  | ICSD115AI04L | "Lead-Free" 20 Lead TSSOP | Tape & Reel        | -40°C to 85°C |

# **Revision History Sheet**

| Rev | Table | Page    | Description of Change                                                                                                                                                                                                                                             | Date     |

|-----|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| В   | Т6    | 7       | AC Characteristics Table - corrected typo for Hold Time, STS-3 spec. from 300ps to 3000ps max.                                                                                                                                                                    | 6/24/08  |

| с   | T5C   | 6<br>8  | Differential DC Characteristics Table - deleted V <sub>PP</sub> and V <sub>CMR</sub> specs and added V <sub>IH</sub> , V <sub>IL</sub> , $\Delta$ V <sub>IN</sub> specs.<br>Parameter Measurement Information Section - updated Differential Input Level diagram. | 10/15/08 |

| с   | T10   | 1<br>13 | Removed ICS from part numbers where needed.<br>General Description - Deleted ICS chip.<br>Ordering Information - Deleted quantity from tape and reel. Deleted LF note below<br>table.<br>Updated header and footer.                                               | 1/27/16  |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Generators & Support Products category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

CV183-2TPAG 950810CGLF 9DBV0741AKILF 9VRS4420DKLF CY25404ZXI226 CY25422SXI-004 MPC9893AE NB3H5150-01MNTXG PL602-20-K52TC ICS557GI-03LF PI6LC48P0101LIE 82P33814ANLG 840021AGLF ZL30244LFG7 PI6LC48C21LE ZL30245LFG7 PI6LC48P0405LIE PI6LC48P03LE MAX24505EXG+ ZL30163GDG2 5L1503L-000NVGI8 ZL30673LFG7 MAX24188ETK2 ZL30152GGG2 5L1503-000NVGI8 PI6C557-01BZHIEX PI6LC48C21LIE CY2542QC002 5P35023-106NLGI 5X1503L-000NLGI8 ZL30121GGG2V2 ZL30282LDG1 ZL30102QDG1 ZL30159GGG2 DS1070K ZL30145GGG2 ZL30312GKG2 MAX24405EXG2 ZL30237GGG2 SY100EL34LZG 9FGV1002BQ506LTGI AD9518-4ABCPZ MX852BB0030 PI6LC4840ZHE AD9516-0BCPZ-REEL7 AD9574BCPZ-REEL7 PL602-21TC-R ZL30105QDG1 ZL30100QDG1 ZL30142GGG2