# Description

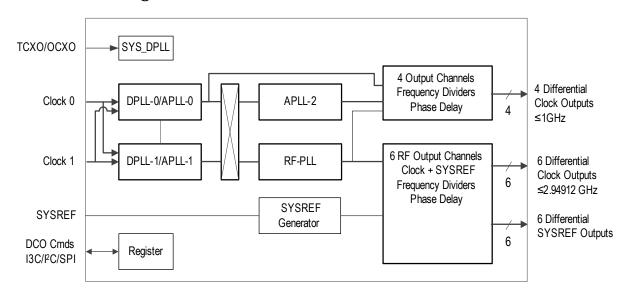

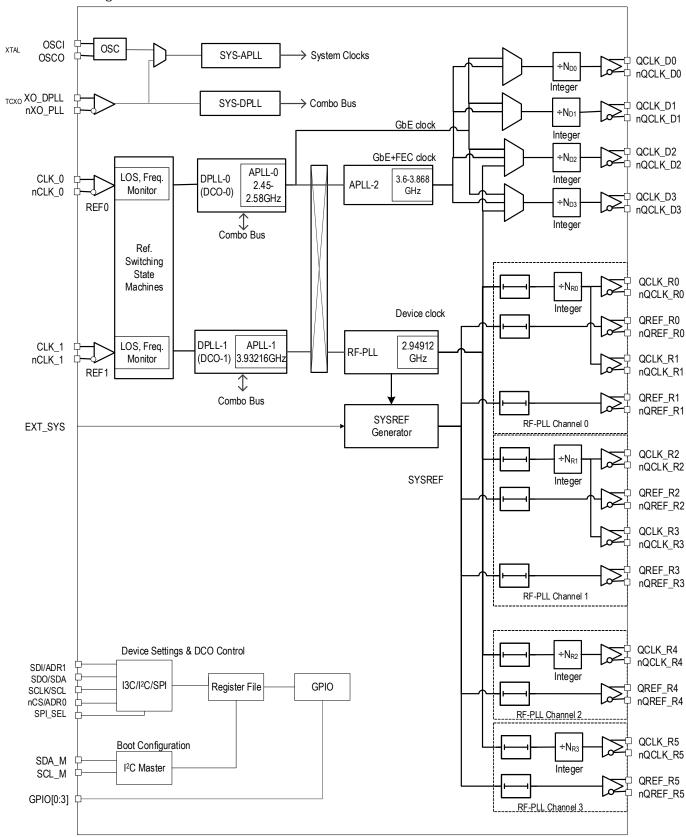

The 8V19N850 is a fully integrated Radio Unit Clock Synchronizer and Converter Clock Generator designed as a high-performance clock solution for phase/frequency synchronization and signal conditioning of wireless base station radio equipment. The device supports JESD204B/C subclass 0 and 1 device clocks and SYSREF synchronization for converters.

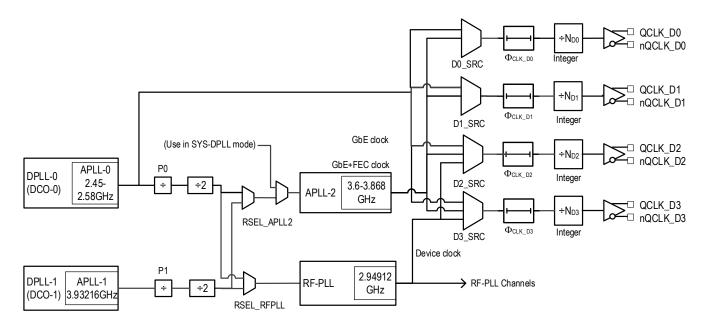

The 8V19N850 supports two independent frequency domains: one that can be used for the digital clock (Ethernet and FEC rates) domain with four outputs, and the device clock (RF-PLL) domain with 12 outputs. The Ethernet domain generates frequencies from two independent APLLs for flexibility; the outputs of the RF clock domain generate very low phase noise clocks for ADC/DAC circuits.

From the integrated RF-PLL, the device supports the clock generation of high-frequency device clocks for driving ADC/DAC devices low-frequency synchronization signals (SYSREF).

A dual DPLL front-end architecture supports any frequency translation. Each DPLL provides a programmable bandwidth and a DCO function for real-time frequency/phase adjustments. The DPLLs can lock on 1PPS input signals and establish lock within 100s or less. Frequency information can be applied from DPLL-0 to DPLL-1 and vice versa to enable the combining of the frequency characteristics of two references (combo-mode).

The 8V19N850 is configured through a pin-mapped I3C $^{\text{SM}}$  (including legacy I $^2$ C) and 3/4-wire SPI interface. I $^2$ C with master capabilities reads a default configuration from an external ROM device. GPIO ports can be configured for reporting and controlling purposes.

# **Applications**

Wireless infrastructure 5G radio

# Simplified Block Diagram

# Features

- High-performance radio clock synchronizer clock

- Device clock domain (RF-PLL) with support for JESD204B/C

- Digital clock domain (Ethernet, FEC) with support for eEEC and T-BC/T-TSC Class C

- 2 differential clock reference inputs

- 1PPS (1Hz) to 1GHz input frequency

- Dual DPLL front-end with independent clock paths

- External control of the DCO for IEEE1588

- Digital holdover with a 1.1 × 10<sup>-7</sup> ppb accuracy

- Programmable DPLL loop bandwidth 1mHz 6kHz

- Configurable phase delay (range: 1UI)

- Hitless input switching with < 1ns output phase error</li>

- Reference monitors for input LOS, activity and frequency

- 1 external synchronization input for JESD204B/C (LVCMOS)

- 16 differential outputs

- Dedicated phase management capabilities

- Optimized for low phase noise:

- Device clocks: -149.9dBc/Hz (1MHz offset; 245.76MHz clock)

- Supply voltage (core): 3.3V; (outputs): 3.3V, 2.5V, and 1.8V

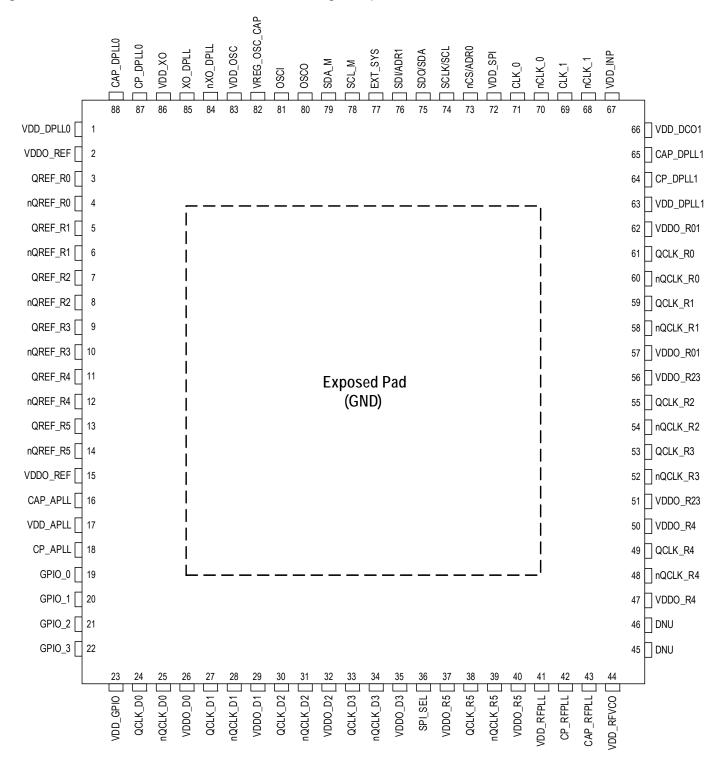

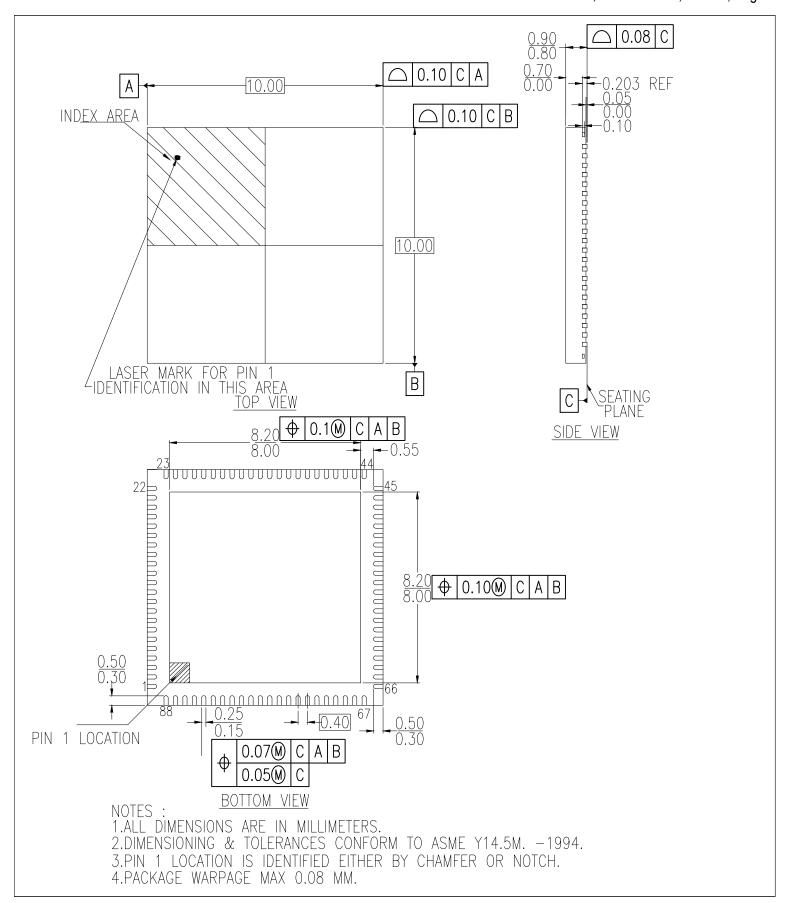

- Package: 10 × 10 mm 88-VFQFPN

- Board temperature range: -40°C to +105°C

# Applicable Standards

- ITU-T G.8262 EEC1/2, G.8262.1 eEEC

- ITU-T G.8273.2 T-BC/T-TSC Class C

- JESD204B and C

# **Block Diagram**

Figure 1. Block Diagram

# Features (Full List)

- High-performance radio clock synchronizer clock

- Device clock domain (RF-PLL) with support for JESD204B/C

- Digital clock domain (Ethernet, FEC) with support for eEEC and T-BC/T-TSC Class C

- Dual DPLL front-end with independent clock paths

- Compliant to ITU-T G.8262 (EEC1/2), G.8262.1 (eEEC), and G.8273.2 (T-BC/T-TSC)

- External control of the DCO for IEEE1588 (with a resolution of 1.1 × 10<sup>-7</sup> ppb)

- Reference monitors for input LOS, activity and frequency

- Fast lock to input signals, incl. 1PPS lock

- Digital holdover with a 1.1 × 10<sup>-7</sup> ppb accuracy

- Programmable DPLL loop bandwidth 1mHz 6kHz

- Configurable phase delay (range: 1UI)

- Hitless input switching with < 1ns output phase error</li>

- 2 differential clock reference inputs

- LVDS and LVPECL compatible, non-inverted input also supports LVCMOS

- 1PPS (1Hz) to 1GHz input frequency

- 1 external synchronization input for JESD204B/C (LVCMOS)

- 16 differential outputs

- 12 device clock domain outputs (from RF-PLL), 6 clock and 6 SYSREF outputs

- 4 digital clock domain outputs

- Low-power LVPECL/LVDS outputs support configurable signal amplitude, DC and AC coupling and LVPECL, LVDS line terminations techniques

- Device clock outputs programmable in output amplitude

- Frequency range: 0.4608MHz–2.94912GHz (RF-PLL) and up to 1GHz (Digital clocks)

- 1PPS (Digital clocks) for T-BC/T-TSC

- Dedicated phase management capabilities

- Static phase delay for every device clock and SYSREF output

- Static and dynamically adjustable phase delay in each DPLL

- Supports less than ±0.5ns input to output phase offset

- Optimized for low phase noise

- Device clocks (RF-PLL): -149.9dBc/Hz (1MHz offset; 245.76MHz clock)

- Serial interface ports

- 3/4-wire SPI or 2-wire I3C (including legacy I<sup>2</sup>C), pin-mapped, for phase/frequency control and other configurations

- Single I<sup>2</sup>C master boot for obtaining a start-up configuration

- Serial control I/O voltage: 1.8V (outputs: selectable 1.8/3.3V voltage)

- Supply voltage (core): 3.3V; (outputs): 3.3V, 2.5V, and 1.8V

- Package: 10 × 10 mm 88-VFQFPN

- Board temperature range: -40°C to +105°C

# Contents

| Description                                       |    |

|---------------------------------------------------|----|

| Applications                                      |    |

| Simplified Block Diagram                          | 1  |

| eatures                                           | 1  |

| Applicable Standards                              |    |

| Block Diagram                                     | 2  |

| eatures (Full List)                               | 3  |

| Contents                                          | 4  |

| Pinout                                            | 7  |

| Pin Descriptions                                  | 8  |

| Principles of Operation                           | 12 |

| Signal Flow                                       | 12 |

| One and Two Frequency Domains                     | 12 |

| Three Frequency Domains                           |    |

| System APLL (SYS-APLL)                            |    |

| System DPLL (SYS-DPLL)                            |    |

| Digital PLLs (DPLL-0, DPLL-1)                     | 17 |

| DPLL-0 Frequency Plan                             |    |

| DPLL-1 Frequency Plan                             |    |

| DPLL-0/DPLL-1 Operation States                    |    |

| DPLL Loop Bandwidth                               |    |

| Holdover State                                    |    |

| Pull-in/Hold-in                                   |    |

| Free-Run Frequency Accuracy                       |    |

| Phase Slope Limiting (PSL)                        |    |

| IEEE 1588 Modes of operation                      |    |

| Phase Adjustment through DPLL                     |    |

| Input Clock Qualification and Reference Selection |    |

| Pin Selection Mode                                |    |

| Manual Selection Mode                             |    |

| Automatic Input Clock Selection Mode              |    |

| Reference Switching                               |    |

| 1PPS Fast Lock                                    |    |

| Input to Output Phase Alignment                   |    |

| Input Disqualification by GPIO pins               |    |

| APLL-2                                            |    |

| Frequency Plan                                    |    |

| Crystal Oscillator Interface (XO_DPLL/nXO_DPLL)   |    |

| Crystal Interface (OSCI/OSCO)                     |    |

| Digital Frequency Domains                         |    |

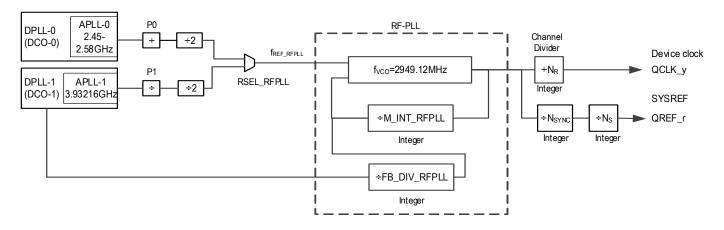

| Converter Clock Domain and RF-PLL                 |    |

| RF-PLL Channel                                    |    |

| RF-PLL Channel Frequency Divider                  |    |

| Configuration for JESD204B Operation              |    |

| Differential Outputs                              |    |

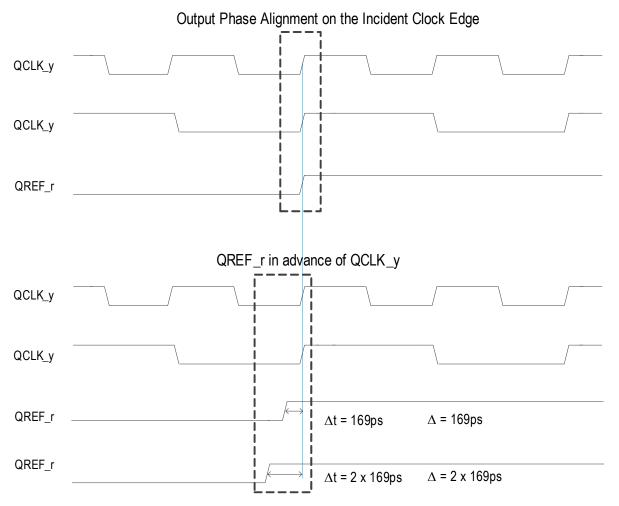

| Output Phase-Delay                                |    |

| General Purpose Input/Outputs (GPIOs)             |    |

| Power-up and Internal Reset                       | 4ŏ |

| Power Supply Sequence                                                       | 48  |

|-----------------------------------------------------------------------------|-----|

| Automatic Startup and Self-Configuration                                    |     |

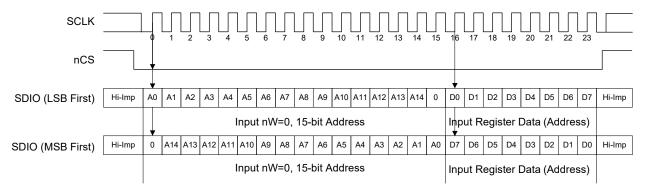

| Serial Port Description                                                     |     |

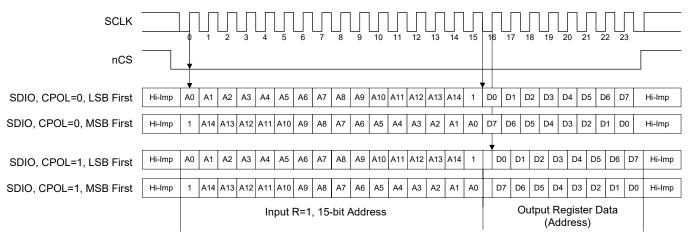

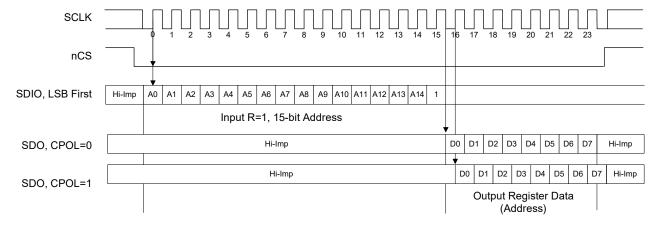

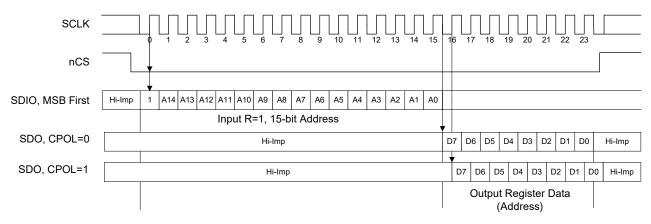

| SPI Interface (SPI_SEL = 1)                                                 |     |

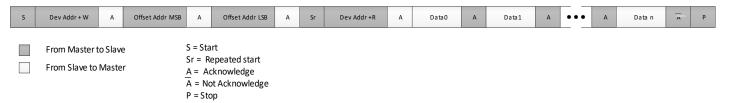

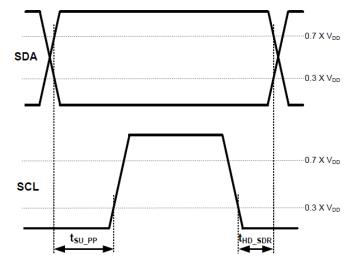

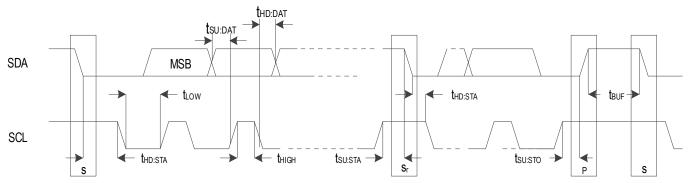

| 13C Interface (SPI_SEL = 0)                                                 |     |

| I2C Master Interface                                                        |     |

| Configuration and Status Registers                                          | 60  |

| General Device Configuration                                                | 60  |

| General Power Down Registers                                                | 62  |

| Read EEPROM Status                                                          | 63  |

| I/O Voltage Select Configuration                                            |     |

| System APLL (SYS-APLL) Configuration                                        | 64  |

| System DPLL (SYS-DPLL) Configuration                                        | 65  |

| System DPLL (SYS-DPLL) Lock Threshold, Lock Timer, Bandwidth                | 66  |

| System DPLL (SYS-DPLL) Phase Error Compensation (PEC) and Frequency Divider | 68  |

| Reference Monitor for Input CLK_0                                           | 69  |

| Reference Monitor for Input CLK_1                                           | 73  |

| Global Status                                                               | 77  |

| DPLL-0 (APLL-0) Frequency Configuration                                     | 82  |

| DPLL-0 (APLL-0) DSM Control and APLL-0 Charge Pump Configuration            |     |

| DPLL-0 Feedback Divider M0                                                  |     |

| DPLL-0 Frequency Control                                                    |     |

| DPLL-0 Lock Timer                                                           | 88  |

| DPLL-0 Hitless Switch                                                       |     |

| DPLL-0 Mode Control                                                         |     |

| DPLL-0 Phase Offset, Write Phase and Frequency                              |     |

| DPLL-0 Reference State                                                      |     |

| DPLL-0 Lock Threshold, Lock Timer, Bandwidth                                |     |

| DPLL-0 Phase Slope Limiting                                                 |     |

| DPLL-0 Holdover, Phase Error Compensation (PEC)                             |     |

| DPLL-0 Fractional Feedback Divider M1                                       |     |

| DPLL-1 (APLL-1) Frequency Configuration                                     |     |

| DPLL-1 (APLL-1) DSM Control and APLL-1 Charge Pump Configuration            |     |

| DPLL-1 Lock Timer                                                           |     |

| DPLL-1 Hitless Switch                                                       |     |

| DPLL-1 Mode Control                                                         |     |

| DPLL-1 Phase Offset, Write Phase and Frequency                              |     |

| DPLL-1 Reference State                                                      |     |

| DPLL-1 Lock Threshold, Lock Timer, Bandwidth                                |     |

| DPLL-1 Phase Slope Limiting                                                 |     |

| DPLL-1 Holdover, Phase Error Compensation (PEC)                             |     |

| DPLL-1 Fractional Feedback Divider M1                                       |     |

| APLL-2 Configuration Registers                                              |     |

| RF-PLL Configuration Registers                                              |     |

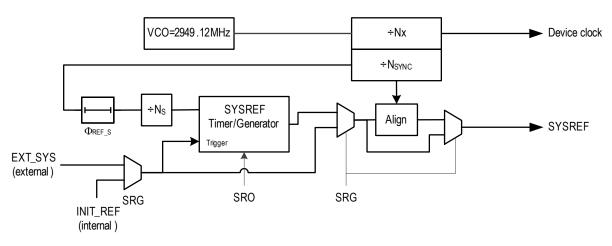

| SYSREF Registers                                                            |     |

| Channel D0-D3 and R0-R3 Registers                                           |     |

| Output Registers                                                            |     |

| GPIO Registers                                                              |     |

| Device Status                                                               | 141 |

| DPLL-0/DPLL-1/APLL-2/RF-PLL Status                         | 42  |

|------------------------------------------------------------|-----|

| Initialization and Internal SYSREF Trigger                 | 43  |

| Channel Enable and PLL Reference Registers Descriptions    | 45  |

| Electrical Characteristics                                 | 47  |

| Absolute Maximum Ratings                                   | 47  |

| Pin Characteristics                                        | 48  |

| External Oscillator Characteristics                        | 48  |

| DC Characteristics                                         | 49  |

| AC Characteristics                                         | 53  |

| Application Information                                    |     |

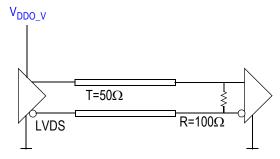

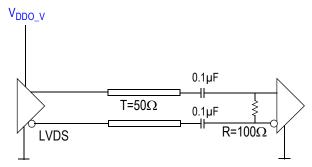

| Termination for QCLK_y, QREF_r LVDS Outputs (STYLE = 0)    | 66  |

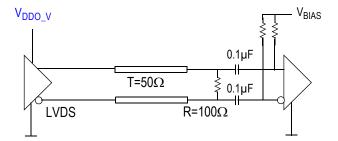

| AC Termination for QCLK_y, QREF_r LVDS Outputs (STYLE = 0) |     |

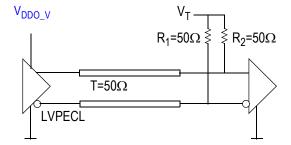

| Termination for QCLK_y, QREF_r LVPECL Outputs (STYLE = 1)  | 67  |

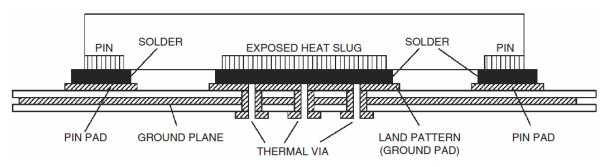

| Thermal Characteristics                                    | 68  |

| Case Temperature Considerations                            | 68  |

| Package Exposed Pad Thermal Release Path                   | 69  |

| Package Outline Drawings                                   | 69  |

| Marking Diagram                                            | 69  |

| Ordering Information                                       | 70  |

| Glossary                                                   | 71  |

| Errata                                                     | 72  |

| Revision History                                           | 172 |

# Pinout

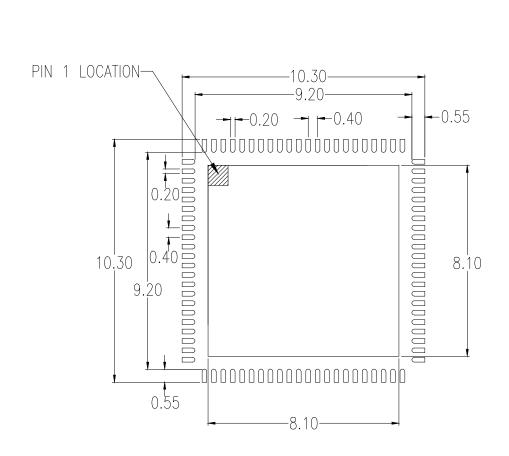

Figure 2. Pinout 10 x 10 mm<sup>2</sup> 88-VFQFPN Package (Top View)

# Pin Descriptions

Table 1. Pin Descriptions<sup>a</sup>

| Pin       | Name                 | Type <sup>b</sup> |       | Description                                                                                                                                                                                                                                                       |  |  |

|-----------|----------------------|-------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|           | Signal Inputs        |                   |       |                                                                                                                                                                                                                                                                   |  |  |

| 71        | CLK_0                |                   | PD    | Device clock 0 inverting and non-inverting differential clock input. Inverting input is                                                                                                                                                                           |  |  |

| 70        | nCLK_0               | Input             | PD/PU | biased to V <sub>DD_V</sub> /2 by default when left floating. Compatible with LVPECL, LVDS, and LVCMOS signals.                                                                                                                                                   |  |  |

| 69        | CLK_1                | la a cut          | PD    | Device clock 1 inverting and non-inverting differential clock input. Inverting input is                                                                                                                                                                           |  |  |

| 68        | nCLK_1               | Input             | PD/PU | biased to V <sub>DD_V</sub> /2 by default when left floating. Compatible with LVPECL, LVDS, and LVCMOS signals.                                                                                                                                                   |  |  |

| 85        | XO_DPLL              |                   | PD    | Single-ended or differential crystal oscillator input for the system DPLL (SYS-DPLL)                                                                                                                                                                              |  |  |

| 84        | nXO_DPLL             | Input             | PD/PU | and for the SYS-APLL (selectable). May also be a reference to APLL-0 and APLL-1. For a frequency specification, see Table 132. Inverting input is biased to V <sub>DD_V</sub> /2 by default when left floating. Compatible with LVPECL, LVDS, and LVCMOS signals. |  |  |

| 81        | OSCI                 | Input             |       | XTAL interface of the system APLL (SYS-APLL) and reference to APLL-0 and                                                                                                                                                                                          |  |  |

| 80        | osco                 | Output            |       | APLL-1. It is also a reference for APLL-2 when APLL-2 is used as part of the system DPLL (SYS-DPLL). For a frequency and interface specification, see Table 132. OSCI should be AC-coupled, if an oscillator (XO) is used on OSCI, leave OSCO unconnected.        |  |  |

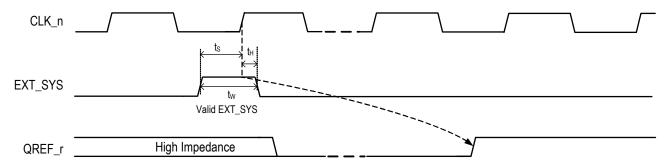

| 77        | EXT_SYS              | Input             | PD    | External SYSREF pulse trigger input. 1.8V LVCMOS interface levels (3.3V tolerant)                                                                                                                                                                                 |  |  |

| 36        | SPI_SEL              | Input             | PU    | SPI/I3C Select. 1.8V/2.5V/3.3V LVCMOS interface levels. For levels, see Table 134.                                                                                                                                                                                |  |  |

|           |                      |                   |       | Signal Outputs                                                                                                                                                                                                                                                    |  |  |

| 61,<br>60 | QCLK_R0,<br>nQCLK_R0 | Output            |       | Differential clock output R0 (Device clock from RF-PLL, Channel 0). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                      |  |  |

| 59,<br>58 | QCLK_R1,<br>nQCLK_R1 | Output            |       | Differential clock output R1 (Device clock from RF-PLL, Channel 0). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                      |  |  |

| 55,<br>54 | QCLK_R2,<br>nQCLK_R2 | Output            |       | Differential clock output R2 (Device clock from RF-PLL, Channel 1). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                      |  |  |

| 53,<br>52 | QCLK_R3,<br>nQCLK_R3 | Output            |       | Differential clock output R3 (Device clock from RF-PLL, Channel 1). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                      |  |  |

| 49,<br>48 | QCLK_R4,<br>nQCLK_R4 | Output            |       | Differential clock output R4 (Device clock from RF-PLL, Channel 2). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                      |  |  |

| 38,<br>39 | QCLK_R5,<br>nQCLK_R5 | Output            |       | Differential clock output R5 (Device clock from RF-PLL, Channel 3). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                      |  |  |

| 3,<br>4   | QREF_R0,<br>nQREF_R0 | Output            |       | Differential SYSREF output R0 (RF-PLL, Channel 0). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                                       |  |  |

Table 1. Pin Descriptions<sup>a</sup>

| Pin       | Name                 | Тур          | oe <sup>b</sup> | Description                                                                                                                                                                                                                                           |  |

|-----------|----------------------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5,<br>6   | QREF_R1,<br>nQREF_R1 | Output       |                 | Differential SYSREF output R1 (RF-PLL, Channel 0). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                           |  |

| 7,<br>8   | QREF_R2,<br>nQREF_R2 | Output       |                 | Differential SYSREF output R2 (RF-PLL, Channel 1). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                           |  |

| 9,<br>10  | QREF_R3,<br>nQREF_R3 | Output       |                 | Differential SYSREF output R3 (RF-PLL, Channel 1). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                           |  |

| 11,<br>12 | QREF_R4,<br>nQREF_R4 | Output       |                 | Differential SYSREF output R4 (RF-PLL, Channel 2). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                           |  |

| 13,<br>14 | QREF_R5,<br>nQREF_R5 | Output       |                 | Differential SYSREF output R5 (RF-PLL, Channel 3). Configurable LVPECL/LVDS style, offset voltage and amplitude. 3.3V, 2.5V, or 1.8V output voltage supply.                                                                                           |  |

| 24,<br>25 | QCLK_D0,<br>nQCLK_D0 | Output       |                 | Differential clock output D0 (Digital clock). Configurable LVPECL/LVDS/LVCMOS style and amplitude. 3.3V, 2.5V, or 1.8V output voltage.                                                                                                                |  |

| 27,<br>28 | QCLK_D1,<br>nQCLK_D1 | Output       |                 | Differential clock output D1 (Digital clock). Configurable LVPECL/LVDS/LVCMOS style and amplitude. 3.3V, 2.5V, or 1.8V output voltage.                                                                                                                |  |

| 30,<br>31 | QCLK_D2,<br>nQCLK_D2 | Output       |                 | Differential clock output D2 (Digital clock). Configurable LVPECL/LVDS/LVCMOS style and amplitude. 3.3V, 2.5V, or 1.8V output voltage.                                                                                                                |  |

| 33,<br>34 | QCLK_D3,<br>nQCLK_D3 | Output       |                 | Differential clock output D3 (Digital clock). Configurable LVPECL/LVDS/LVCMOS style and amplitude. 3.3V, 2.5V, or 1.8V output voltage.                                                                                                                |  |

|           |                      |              |                 | Serial Interface 0                                                                                                                                                                                                                                    |  |

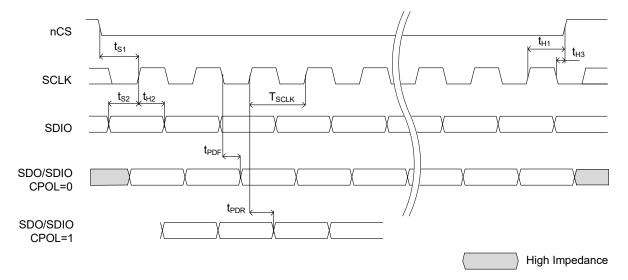

| 76        | SDI/SDIO/ADR1        | Input/Output | _               | SPI: Data Input in 4-wire mode (SDI) or Data Input/Output in 3-wire mode (SDIO). 1.8V interface levels with hysteresis and 3.3V tolerance. When output, selectable 1.8V/3.3V levels.  I3C: Static address bit input and part of the 48-bit unique ID. |  |

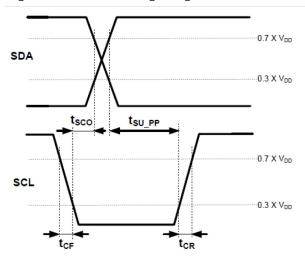

| 75        | SDO/SDA              | Input/Output | _               | SPI: Data Output in 4-wire mode (SDO). Selectable 1.8V/3.3V output levels I3C: Data I/O (SDA). 1.8V interface levels with hysteresis and 3.3V tolerance                                                                                               |  |

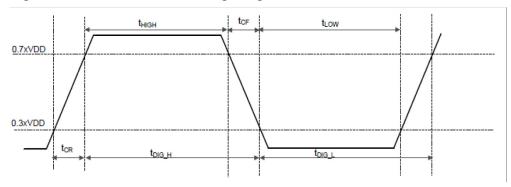

| 74        | SCLK/SCL             | Input        | _               | SPI: Clock Input. 1.8V interface levels with hysteresis and 3.3V tolerance. I3C: Clock Input / SPI Clock Input.                                                                                                                                       |  |

| 73        | nCS/ADR0             | Input        | _               | SPI: Chip Select Input. 1.8V interface levels with hysteresis and 3.3V tolerance. I3C: Static address bit input and part of 48-bit unique ID.                                                                                                         |  |

|           | Serial Interface 1   |              |                 |                                                                                                                                                                                                                                                       |  |

| 79        | SDA_M                | Input/Output | _               | Serial Control Port I <sup>2</sup> C (Master) Data Input/Output. 1.8V interface levels with hysteresis and 3.3V tolerance. Open collector when output. External resistor (pull high) is required if pin is not used.                                  |  |

| 78        | SCL_M                | Output       | _               | Serial Control Port I <sup>2</sup> C (Master) Clock Output. Open-collector / 1.8V interface levels with hysteresis and 3.3V tolerance. External resistor (pull high) is required if pin is not used.                                                  |  |

Table 1. Pin Descriptions<sup>a</sup>

| Pin    | Name                    | Ту           | pe <sup>b</sup> | Description                                                                                            |  |  |

|--------|-------------------------|--------------|-----------------|--------------------------------------------------------------------------------------------------------|--|--|

|        | GPIO                    |              |                 |                                                                                                        |  |  |

| 19     | GPIO_0                  | Input/Output | PU              | General purpose I/O port. Selectable 1.8V/3.3V LVCMOS interface levels. 3.3V tolerant                  |  |  |

| 20     | GPIO_1                  | Input/Output | PD              | when configured as input and set to 1.8V logic levels.                                                 |  |  |

| 21     | GPIO_2                  | Input/Output | PD              |                                                                                                        |  |  |

| 22     | GPIO_3                  | Input/Output | PD              |                                                                                                        |  |  |

|        | PLL Circuit Connections |              |                 |                                                                                                        |  |  |

| 18     | CP_APLL                 |              |                 | APLL-2 loop filter.                                                                                    |  |  |

| 42     | CP_RFPLL                |              |                 | RF-PLL loop filter.                                                                                    |  |  |

| 87     | CP_DPLL0                |              |                 | APLL-0 loop filter.                                                                                    |  |  |

| 64     | CP_DPLL1                |              |                 | APLL-1 loop filter.                                                                                    |  |  |

| 16     | CAP_APLL                |              |                 | Bypass capacitor (1µF to GND) for the internal regulator for the APLL-2 block.                         |  |  |

| 43     | CAP_RFPLL               |              |                 | Bypass capacitor (1µF to GND) for internal regulator for the RF-PLL block.                             |  |  |

| 88     | CAP_DPLL0               |              |                 | Bypass capacitor (1µF to GND) for internal regulator for the DPLL-0 block.                             |  |  |

| 65     | CAP_DPLL1               |              |                 | Bypass capacitor (1µF to GND) for internal regulator for the DPLL-1 block.                             |  |  |

| 82     | VREG_OSC_CAP            |              |                 | Bypass capacitor (1µF to GND) for internal regulator for the OSC block.                                |  |  |

|        |                         | •            |                 | Power and Ground                                                                                       |  |  |

| 2, 15  | VDDO_REF                | Power        |                 | Positive supply voltage (3.3V) for the QREF_R0-QREF_R5 outputs. Supplied with 3.3V, 2.5V, or 1.8V      |  |  |

| 35     | VDDO_D3                 | Power        |                 | Positive supply voltage (3.3V) for the QCLK_D3 outputs. Supplied with 3.3V, 2.5V, or 1.8V.             |  |  |

| 32     | VDDO_D2                 | Power        |                 | Positive supply voltage (3.3V) for the QCLK_D2 outputs. Supplied with 3.3V, 2.5V, or 1.8V.             |  |  |

| 29     | VDDO_D1                 | Power        |                 | Positive supply voltage (3.3V) for the QCLK_D1 outputs. Supplied with 3.3V, 2.5V, or 1.8V.             |  |  |

| 26     | VDDO_D0                 | Power        |                 | Positive supply voltage (3.3V) for the QCLK_D0 outputs. Supplied with 3.3V, 2.5V, or 1.8V.             |  |  |

| 57, 62 | VDDO_R01                | Power        |                 | Positive supply voltage (3.3V) for the QCLK_R0 and QCLK_R1 outputs. Supplied with 3.3V, 2.5V, or 1.8V. |  |  |

| 51, 56 | VDDO_R23                | Power        |                 | Positive supply voltage (3.3V) for the QCLK_R2 and QCLK_R3 outputs. Supplied with 3.3V, 2.5V, or 1.8V. |  |  |

| 47, 50 | VDDO_R4                 | Power        |                 | Positive supply voltage (3.3V) for the QCLK_R4 output. Supplied with 3.3V, 2.5V, or 1.8V.              |  |  |

| 37, 40 | VDDO_R5                 | Power        |                 | Positive supply voltage (3.3V) for the QCLK_R5 output. Supplied with 3.3V, 2.5V, or 1.8V.              |  |  |

| 1      | VDD_DPLL0               | Power        |                 | Positive supply voltage (3.3V) for the DPLL-0 block                                                    |  |  |

| 17     | VDD_APLL                | Power        |                 | Positive supply voltage (3.3V) for the APLL blocks                                                     |  |  |

| 23     | VDD_GPIO                | Power        |                 | Positive supply voltage (3.3V) for the GPIO block                                                      |  |  |

Table 1. Pin Descriptions<sup>a</sup>

| Pin            | Name      | Тур   | oe <sup>b</sup> | Description                                                                     |  |

|----------------|-----------|-------|-----------------|---------------------------------------------------------------------------------|--|

| 41             | VDD_RFPLL | Power |                 | Positive supply voltage (3.3V) for the RF-PLL block                             |  |

| 44             | VDD_RFVCO | Power |                 | Positive supply voltage (3.3V) for the VCO in the RF-PLL block                  |  |

| 63             | VDD_DPLL1 | Power |                 | Positive supply voltage (3.3V) for the DPLL-1 block                             |  |

| 66             | VDD_DCO1  | Power |                 | Positive supply voltage (3.3V) for the VCO in the DPLL-1 block                  |  |

| 67             | VDD_INP   | Power |                 | Positive supply voltage (3.3V) for the CLK_0, CLK_1 inputs                      |  |

| 72             | VDD_SPI   | Power |                 | Positive supply voltage (3.3V) for the SPI interface and for digital blocks     |  |

| 83             | VDD_OSC   | Power |                 | Positive supply voltage (3.3V) for the internal crystal oscillator (OSCI, OSCO) |  |

| 86             | VDD_XO    | Power |                 | Positive supply voltage (3.3V) for the XO_DPLL interface                        |  |

| Exposed<br>Pad | GND       | Power |                 | Ground supply voltage (GND) and ground return path. Connect to board GND (0V).  |  |

a. For essential information on power supply filtering, see Application Information.

b. PU (pull-up) and PD (pull-down) indicate internal input resistors (for values, see Figure 131).

# Principles of Operation

# Signal Flow

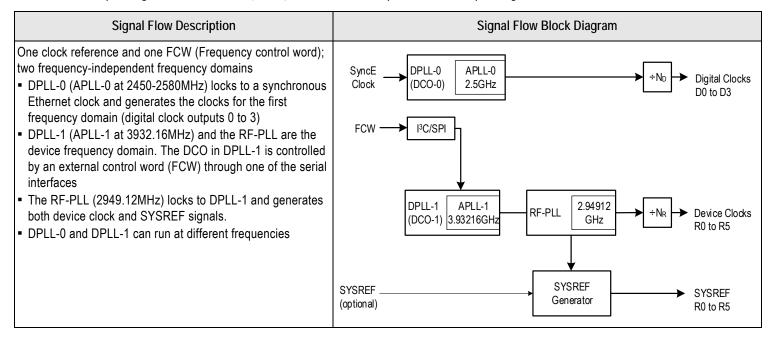

One and Two Frequency Domains

Applications generating the signals for one or two frequency domains do not require the use of the APLL-2. APLL-2 is available to be used as the high-frequency VCO in the SYS-DPLL (see System DPLL (SYS-DPLL)).

Table 2. Frequency Control Word (FCW) and Two Independent Frequency Domains

Table 3. Synchronous Ethernet Frequency, IEEE1588 Phase Control Mode

| Signal Flow                                                                                                                                                                                                                                                                                                                                    | Description                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Synchronous Ethernet frequency and IEEE1588 Phase Control Mode  DPLL-0 (APLL-0 at 2450-2580MHz) locks to a synchronous Ethernet input clock and generates the clocks for the digital                                                                                                                                                           | SyncE DPLL-0 APLL-0 Digital Clocks D0 to D3 |

| <ul> <li>frequency domain (digital clock outputs 0 to 3)</li> <li>DPLL-1 (APLL-1 at 3932.16MHz) is frequency locked to DPLL-0 through the internal combo bus</li> <li>DPLL-1 is phase-controlled by an external control word (PCW) through a serial interface (S/I)</li> <li>The RF-PLL (2949.12MHz) locks to the DPLL-1 output and</li> </ul> | FCW   3C/SPI   9                            |

| generates both device clock and SYSREF signals  • DPLL-0 (synchronous Ethernet) controls the DPLL-1 frequency while the external PCW applied to DPLL-1 allows for phase adjustments (IEEE1588 application)                                                                                                                                     | (DCO-1) 3.93216 GHz                         |

|                                                                                                                                                                                                                                                                                                                                                | SYSREF SYSREF Generator SYSREF R0 to R5     |

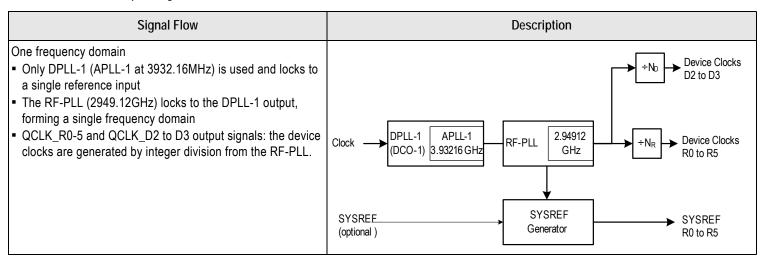

Table 4. One Frequency Domain

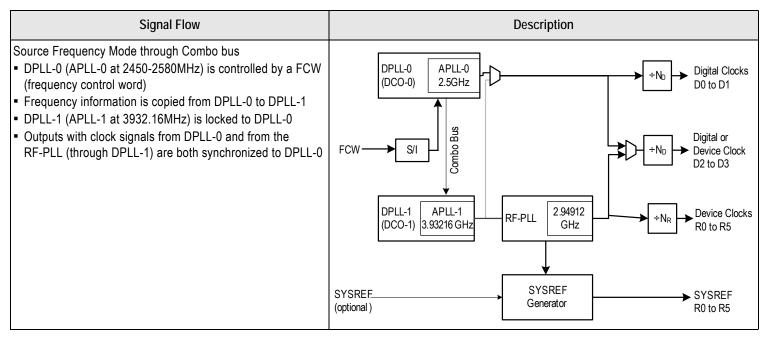

Table 5. Source Frequency Mode through Combo Bus

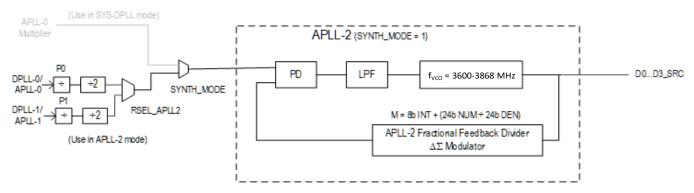

## Three Frequency Domains

Applications generating signals for three frequency domains require the use of at least one DPLL, APLL-0, APLL-1, the RF-PLL, and APLL-2. APLL-2 is used to generate frequencies not available from DPLL-0/APLL-0 (Ethernet) or from DPLL-1/APLL-1/RF-PLL (RF clocks). APLL-2 can lock to APLL-0 or APLL-1 and generate frequencies unrelated to other frequency domains. In these use cases, APLL-2 is unavailable to be used as the high-frequency PLL in the SYS-DPLL (see System DPLL (SYS-DPLL)).

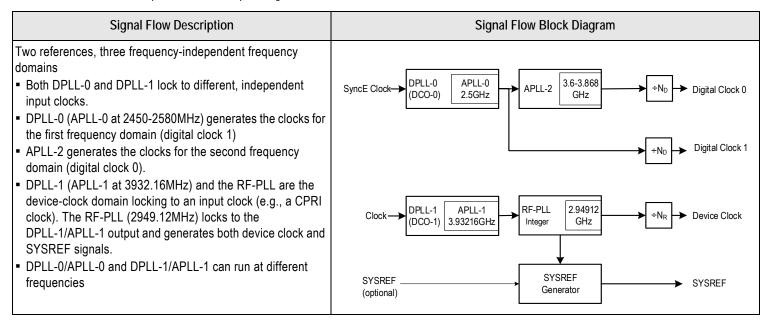

Table 6. Three Independent Frequency Domains

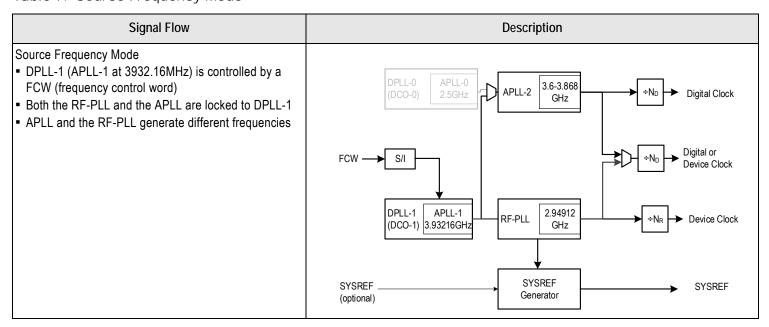

Table 7. Source Frequency Mode

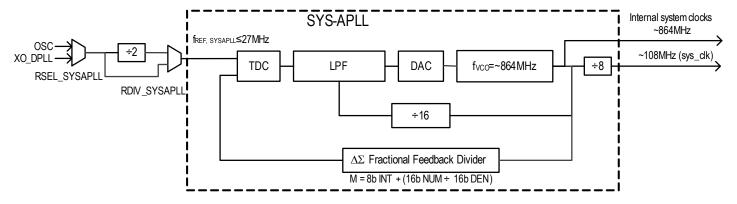

# System APLL (SYS-APLL)

The SYS-APLL generates internal system clocks of  $\sim$ 864MHz and  $\sim$ 108MHz, which are used by multiple internal digital function blocks. The SYS-APLL locks to the selected reference clock (XTAL oscillator OSCI/OSCO or XO\_DPLL). The fractional feedback divider of the SYS-APLL must be configured to enable PLL to clock at f<sub>VCO</sub> = $\sim$ 864MHz. Select the pre-divider of  $\div$ 2 to limit the SYS-APLL reference frequency f<sub>REF,SYS-APLL</sub> to 27MHz or less.

SYS-APLL can be powered down through bit 5 in register 0x011 to save current consumption. If the device is operated with both DPLL-0 and DPLL-1 in DCO mode and without using CLK\_0 and CLK\_1 as clock signal source for the DPLLs, SYS-APLL can be powered down.

Figure 3. System APLL (SYS-APLL) Diagram

Table 8. SYS-APLL Frequency Divider<sup>a</sup>

| Block                  | Frequency                                      | Description                        | Register       |

|------------------------|------------------------------------------------|------------------------------------|----------------|

| Selectable pre-divider | f <sub>REF,SYS-APLL</sub> < 27MHz              | Reference Pre-Divider for SYS-APLL | RDIV_SYSAPLL   |

| SYS-APLL Fractional    | $f_{VCO}$ (864MHz) = [M_INT + (M_NUM ÷ DEN)] ÷ | 8-bit Integer portion (M_INT)      | M_INT_SA[7:0]  |

| feedback divider (M)   | fREF,SYS-APLL                                  | 16-bit Numerator (M_NUM)           | M_NUM_SA[15:0] |

|                        |                                                | 16-bit Denominator (M_DEN)         | M_DEN_SA[15:0] |

a. See "System APLL (SYS-APLL) Configuration"

# System DPLL (SYS-DPLL)

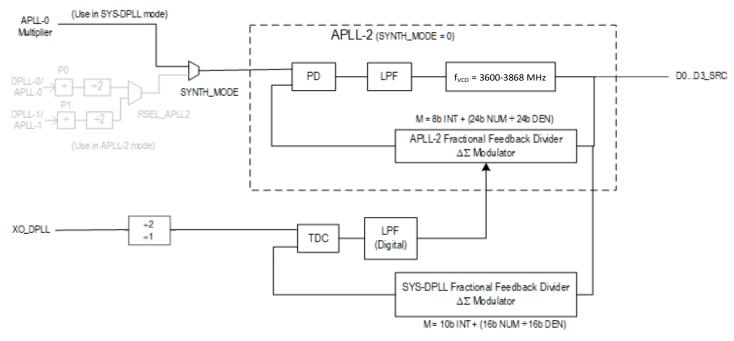

The use of the SYS-DPLL is optional. When used, the purpose of the SYS-DPLL is to generate an internal frequency that is used for combo mode. The SYS-DPLL locks to an external oscillator on XO\_DPLL (XO, TCXO, or OCXO) as a frequency reference for the device. By using the SYS-DPLL as a combo master with DPLL-0 or DPLL-1 as slave DPLLs, DPLL-0 and DPLL-1 will have the same frequency stability of the external oscillator locked to the SYS-DPLL. SYS-DPLL can only be used as a master for the combo bus.

When using SYS-DPLL, it is recommended to also have SYS-APLL locked the XO\_DPLL so that the reference monitors have the same frequency stability of the external oscillator.

The SYS-DPLL implementation uses the APLL-2 as a high-speed oscillator. Therefore, APLL-2 is not available to be used as stand-alone synthesizer when the SYS-DPLL is used. When using the SYS-DPLL together with APLL-2, DPLL-0 must be also powered on.

Figure 4. System DPLL (SYS-DPLL) Diagram

Table 9. SYS-DPLL Frequency Divider<sup>a</sup> in SYS-DPLL Mode (SYNTH\_MODE = 0)

| Block                     | Frequency <sup>b</sup>                                                      | Description                    | Register          |

|---------------------------|-----------------------------------------------------------------------------|--------------------------------|-------------------|

| SYS-DPLL Fractional       | $f_{VCO-2} = \frac{1}{2} \times f_{TCXO} \times [M_INT_SD + (M_NUM_SD \div$ | 10-bit Integer portion (M_INT) | M_INT_SD[9:0]     |

| feedback divider<br>(FFB) | M_DEN_SD)]                                                                  | 16-bit Numerator (N_NUM)       | M_NUM_SD[15:0]    |

| ,                         |                                                                             | 16-bit Denominator (M_DEN)     | M_DEN_SD[15:0]    |

| APLL-2 Fractional         | $f_{VCO_2} = 2 \times f_{XO} \times [M_INT + (M_NUM \div M_DEN)]$           | 8-bit Integer portion          | M_INT_APLL2[7:0]  |

| feedback divider          |                                                                             | 24-bit Numerator               | M_NUM_APLL2[23:0] |

|                           |                                                                             | 24-bit Denominator             | M_DEN_APLL2[23:0] |

a. See System DPLL (SYS-DPLL) Configuration and APLL-2.

b. f<sub>xo</sub> is the OSCI/OSCO/XO\_DPLL frequency.

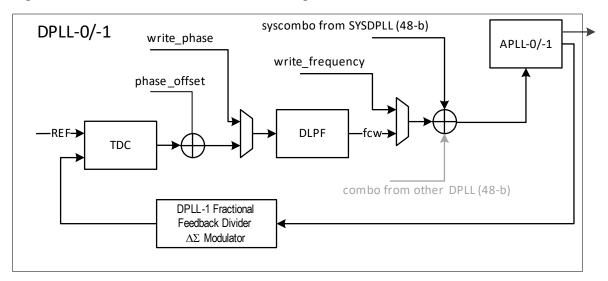

# Digital PLLs (DPLL-0, DPLL-1)

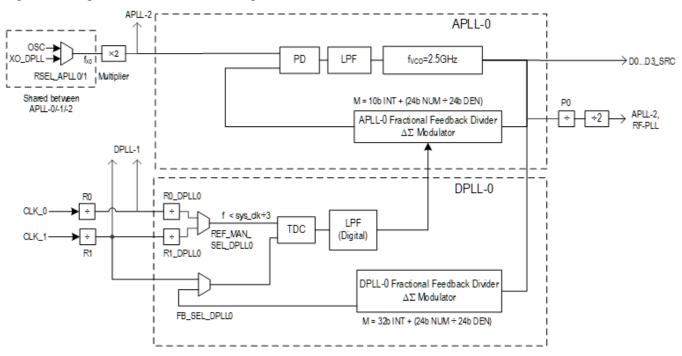

# DPLL-0 Frequency Plan

Figure 5. Digital PLL 0 (DPLL-0) Diagram

Table 10. DPLL-0 Frequency Divider<sup>a</sup>

| Block                                 | Frequency <sup>b</sup>                                                                                                                 | Description                              | Register           |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------|

| APLL-0 Fractional                     | $f_{VCO} = 2 \times f_{XO} \times [M_INT + (M_NUM \div M_DEN)]$                                                                        | 10-bit Integer portion                   | M_INT_APLL0[9:0]   |

| feedback divider                      |                                                                                                                                        | 24-bit Numerator                         | M_NUM_APLL0[23:0]  |

|                                       |                                                                                                                                        | 24-bit Denominator                       | M_DEN_APLL0[23:0]  |

| Post divider P0                       | $f_{REF\_APLL2} = f_{VCO} \div (2 \times P0)$<br>$f_{REF\_RFPLL} = f_{VCO} \div (2 \times P0)$                                         | APLL-0 output frequency divider          | P0[6:0]            |

| DPLL-0 Fractional<br>feedback divider | + (M0_NUM ÷ M0_DEN)]                                                                                                                   | Input high frequency pre-divider (CLK_0) | R0[2:0]            |

| (M)<br>for use with input<br>CLK_0    |                                                                                                                                        | Input pre-divider (CLK_0)                | R0_DPLL0[9:0]      |

|                                       |                                                                                                                                        | 32-bit Integer portion                   | M0_INT_DPLL0[31:0] |

|                                       |                                                                                                                                        | 24-bit Numerator                         | M0_NUM_DPLL0[23:0] |

|                                       |                                                                                                                                        | 24-bit Denominator                       | M0_DEN_DPLL0[23:0] |

| DPLL-0 Fractional<br>feedback divider | $ \begin{aligned} & M = f_{VCO} \div (f_{CLK\_1} \div (R1 \times R1\_DPLL0)) = [M1\_INT \\ & + (M1\_NUM \div M1\_DEN)] \end{aligned} $ | Input high frequency pre-divider (CLK_1) | R1[2:0]            |

| (M)<br>for use with input<br>CLK_1    | with input                                                                                                                             | Input pre-divider (CLK_1)                | R1_DPLL0[9:0]      |

|                                       |                                                                                                                                        | 32-bit Integer portion                   | M1_INT_DPLL0[31:0] |

|                                       |                                                                                                                                        | 24-bit Numerator                         | M1_NUM_DPLL0[23:0] |

|                                       |                                                                                                                                        | 24-bit Denominator                       | M1_DEN_DPLL0[23:0] |

a. See DPLL-0 (APLL-0) Frequency Configuration and DPLL-0 Fractional Feedback Divider M1.

b.  $f_{xo}$  is the OSCI/OSCO/XO\_DPLL frequency

In most uses cases, DPLL-0/APLL-0 drive the QCLK\_Dn outputs directly for the generation of output frequencies such as 125MHz and 156.25MHz by integer division of the VCO frequency of 2450-2580MHz. The fractional feedback divider of APLL-0 must be configured to enable the PLL to clock at any frequency in the range f<sub>VCO</sub> = 2450-2580MHz. In use cases where DPLL-0/APLL-0 drives the RF-PLL at its nominal VCO frequency of 2949.12MHz, DPLL-0/APLL-0 must be configured to a VCO frequency of 2457.6MHz. The frequency ratio of RF-PLL to APLL-0 must be integer in these use cases. AC Characteristics defines the operational frequency range for the VCOs in all APLLs and the RF-PLL.

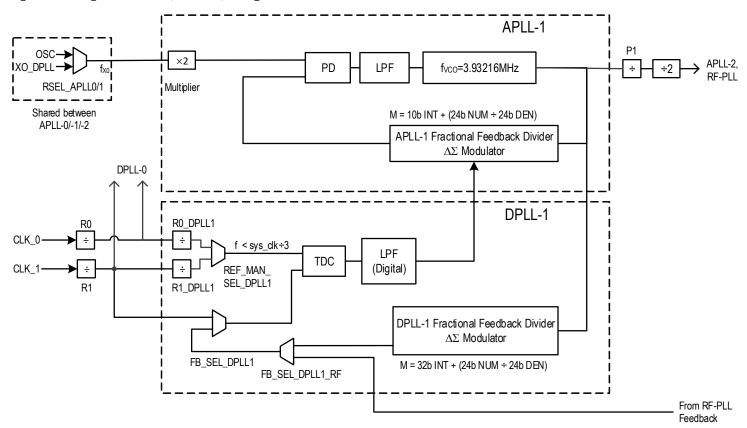

## DPLL-1 Frequency Plan

Figure 6. Digital PLL 1 (DPLL-1) Diagram

Table 11. DPLL-1 Frequency Divider<sup>a</sup>

| Block                              | Frequency <sup>b</sup>                                                                                                               | Description                              | Register           |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------|

| APLL-1 Fractional                  | $f_{VCO} = 2 \times f_{XO} \times [M_{INT} + (M_{NUM} \div M_{DEN})]$                                                                | 10-bit Integer portion                   | M_INT_APLL1[9:0]   |

| feedback divider                   |                                                                                                                                      | 24-bit Numerator                         | M_NUM_APLL1[23:0]  |

|                                    |                                                                                                                                      | 24-bit Denominator                       | M_DEN_APLL1[23:0]  |

| Post divider                       | $f_{REF\_APLL2} = f_{VCO} \div (2 \times P1)$<br>$f_{REF\_RFPLL} = f_{VCO} \div (2 \times P1)$                                       | APLL-1 output frequency divider          | P1[6:0]            |

| DPLL-1 Fractional feedback divider | $\begin{aligned} & M = f_{VCO} \div (f_{CLK\_0} \div (R0 \times R0\_DPLL1)) = [M0\_INT \\ & + (M0\_NUM \div M0\_DEN)] \end{aligned}$ | Input high frequency pre-divider (CLK_0) | R0[2:0]            |

| (M)<br>for use with input<br>CLK_0 |                                                                                                                                      | Input pre-divider (CLK_0)                | R0_DPLL1[9:0]      |

|                                    |                                                                                                                                      | 32-bit Integer portion                   | M0_INT_DPLL1[31:0} |

|                                    |                                                                                                                                      | 24-bit Numerator                         | M0_NUM_DPLL1[23:0] |

|                                    |                                                                                                                                      | 24-bit Denominator                       | M0_DEN_DPLL1[23:0] |

Table 11. DPLL-1 Frequency Divider<sup>a</sup>

| Block                                                                                                             | Frequency <sup>b</sup>                   | Description               | Register           |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------|--------------------|

| DPLL-1 Fractional $M = f_{VCO} \div (f_{CLK\_1} \div (R1 \times R1\_DPLL1)) = [M1\_INT + (M1\_NUM \div M0\_DEN)]$ | Input high frequency pre-divider (CLK_1) | R1[2:0]                   |                    |

| \ /                                                                                                               | (M) for use with input CLK_1             | Input pre-divider (CLK_1) | R1_DPLL1[9:0]      |

|                                                                                                                   |                                          | 32 bit Integer portion    | M1_INT_DPLL1[31:0] |

|                                                                                                                   |                                          | 24 bit Numerator          | M1_NUM_DPLL1[23:0] |

|                                                                                                                   |                                          | 24 bit Denominator        | M1_DEN_DPLL1[23:0] |

- a. See "DPLL-1 (APLL-1) Frequency Configuration" and See "DPLL-1 Fractional Feedback Divider M1"

- b.  $f_{xo}$  is the OSCI/OSCO/XO\_DPLL frequency.

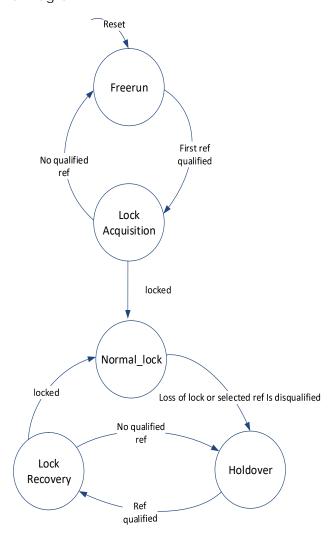

#### DPLL-0/DPLL-1 Operation States

DPLL-0 and DPLL-1 support the same modes of operation. APLL-0 and APLL-1 are part of the loop for DPLL-0 and DPLL-1, respectively. The VCO frequency for the APLL-0 is 2450-2580MHz and VCO frequency for the APLL-1 is 3932.16MHz. Both DPLLs have five states of operation as follows:

- Locked/Normal state The output clock is synchronized to an input reference. In this mode, the DPLL is tracking the selected reference

with normal locking bandwidth and damping factor. The phase and frequency offset of the DPLL output track those of the DPLL selected

input clock.

- Holdover state The DPLL has lost its reference with no other qualified references available and uses the stored data acquired in Locked mode to control its output clock. After the DPLL enters holdover, the accuracy of its output depends on the master clock oscillator (OSCI/OSCO or XO\_DPLL).

- Free-run state The DPLL has never locked to any input reference and the accuracy of its output is dependent on the master clock oscillator (OSCI/OSCO or XO\_DPLL).

- Lock acquisition At least one qualified reference is present prior to reaching the locked state. The DPLL will be tracking the selected reference at acquisition bandwidth and damping factor.

- Lock recovery The DPLL is tracking the selected reference at acquisition bandwidth and damping factor.

Register bits DPLL\_STATE\_DPLL0[2:0] and DPLL\_STATE\_DPLL1[2:0] can be used to force the DPLL-0 and DPLL-1, respectively, to any of the five DPLL states described above. The default value set the DPLLs in free run. When these bits are set to program the DPLL in lock acquisition, or lock recovery, or Locked/Normal state, and if the selected reference is disqualified, then the DPLL will automatically go into holdover if the FAIL\_HOLD\_DPLL0/FAIL\_HOLD\_DPLL1 bit is asserted. Otherwise, the DPLL will stay at the programmed state (mode).

If the bits DPLL\_STATE\_DPLL0[2:0] and DPLL\_STATE\_DPLL1[2:0] are set to 0b101, then the DPLLs are programmed to use an internal automatic state machine. The DPLL state machine diagram is shown in Figure 7.

Figure 7. DPLL State Machine Diagram

As showed in Figure 7, the DPLL state changes are as follows:

- 1. After reset, the DPLL enters Free-Run State.

- 2. After an input clock is qualified and it is selected, it enters the Lock Acquisition State.

- 3. If the DPLL selected input clock is disqualified AND no qualified input clock is available, it goes back to Free-run State.

- 4. If the DPLL locks to the selected input clock, it enters Normal\_lock State.

- 5. The DPLL selected input clock is disqualified AND No qualified input clock is available, it enters Holdover State.

- 6. If a qualified input clock is now available, it enters lock recovery State.

- 7. If the DPLL selected input clock is disqualified AND no qualified input clock is available, it goes back to Holdover State.

- 8. If the DPLL locks to the selected input clock, it enters Normal\_lock State.

In state changes 6 above, the DPLL switches to another qualified clock because of one of the following:

- The selected input clock was disqualified and another qualified input clock is available

- The device is set to revertive mode and a qualified input clock with a higher priority is available.

While in the Normal\_lock state, if the input clock exceeds the programmed Lock Threshold, then the DPLL will enter the Holdover state.

## DPLL Loop Bandwidth

The bandwidth (BW) of the DPLL is precise and static and independent on the clock frequency. The bandwidth of the DPLL does not change with the frequency plan. The bandwidth is programmable from 1mHz to approximately 6kHz.

There are two register fields associated with the bandwidth settings: NORMAL\_BW\_SHIFT\_DPLL0[4:0]/ NORMAL\_BW\_SHIFT\_DPLL1[4:0] and NORMAL\_BW\_MULT\_DPLL0[2:0]/NORMAL\_BW\_MULT\_DPLL1[2:0]. To calculate the BW, the following equation is used:

```

BW = (K_{TDC} \times K_{PEC} \times K_P) / 2\pi

```

#### Where:

```

\begin{split} &K_{TDC} = 1 \ / \ T_{DC\_STEP} \\ &T_{DC\_STEP} = T_{SYSAPLL\_VCO} \ / \ 62 = 18.67 ps \\ &K_{PEC} = 2 \times 10^7 \\ &K_P = (NORMAL\_BW\_SHIFT\_DPLL0[4:0] \ / 4) \times 2^{(NORMAL\_BW\_MULT\_DPLL0[2:0]-53)} \end{split}

```

#### Holdover State

In holdover state, the DPLL has lost its reference and uses the stored data acquired in Locked mode to control its output clock. The initial frequency offset is 1.1 × 10<sup>-7</sup> ppb. After the DPLL enters holdover, the accuracy of its output depends on the master clock oscillator (connected to OSCI/OSCO or XO\_DPLL/nXO\_DPLL pins). If the SYS-DPLL is enabled, then it is assumed that the SYS-DPLL is locked to the master clock oscillator that is connected to XO\_DPLL/nXO\_DPLL pins, and therefore the holdover is based on this master clock oscillator. If SYS-DPLL is not enabled, then holdover is based on the master clock oscillator that is connected to the OSCI/OSCO pins.

The 8V19N850 supports the following holdover states:

- Instantaneous Holdover

- History Instantaneous Holdover

- History Averaged Holdover

- Manual Holdover

The holdover states can be set by programming bits HOLDOVER\_MODE\_DPLL0[1:0] and HOLDOVER\_MODE\_DPLL1[1:0] for DPLL-0 and DPLL-1, respectively.

### Instantaneous Holdover

If DPLL-0/-1 is set to operate in Instantaneous Holdover, then the DPLL freezes at the operating frequency when it enters holdover state. The initial frequency offset is better than is  $1.1 \times 10^{-7}$  pbb assuming that there is no in-band jitter/wander at the input just before entering holdover state.

#### History Instantaneous Holdover

The 8V19N850 implements a history of the instantaneous holdover values. Previously stored instantaneous holdover value can be retrieved. The rate at which the holdover registers are stored is programmable. It can be programmed in steps of 1 second between 1 and 64 s by programming register bits, HOLDOVER\_HISTORY\_DPLL0[5:0] and HOLDOVER\_MODE\_DPLL1[1:0] for DPLL-0 and DPLL-1 respectively. The default value is 1s.

### History Averaged Holdover

When a DPLL is set to history averaged holdover state, the holdover value is post filtered. The filter bandwidth is programmable from approximately 0.12mHz to 0.5Hz. When a DPLL enters the history averaged holdover state, the holdover register value is restored into the integrator inside that DPLL. The rate at which the holdover registers are stored is programmable between 1 and 64 s in steps of 1 s by programming register bits HOLDOVER\_HISTORY\_DPLL0[5:0] and HOLDOVER\_HISTORY\_DPLL1[5:0] for DPLL-0 and DPLL-1, respectively. The default value is 1s.

The holdover filter bandwidth value is programmed by setting HOLDOVER\_BW\_SHIFT\_DPLL0[4:0] / HOLDOVER\_BW\_SHIFT\_DPLL1[4:0] (for DPLL-0) and HOLDOVER\_MULT\_DPLL1[2:0] / HOLDOVER\_MULT\_DPLL1[2:0] (for DPLL-1) as follows:

Holdover filter bandwidth =  $\cos \times f / (2\pi)$  where

- coe = 2<sup>-(33-HOLDOVER\_BW\_SHIFT\_DPLLn)'</sup> × HOLDOVER\_MULT\_DPLLn / 4 (n = 0 for DPLL-0, n = 1 for DPLL-1)

- f is the update rate of both DPLLs (600kHz).

If coe is zero then the filter is bypassed.

#### Manual Holdover

In manual holdover, the frequency offset is set by the DPLL manual holdover value register bits HOLDOVER\_VALUE\_DPLL0[41:0] and HOLDOVER\_VALUE\_DPLL1[41:0] for DPLL-0 and DPLL-1, respectively.

#### Forced into Holdover

The DPLL can also be forced into the holdover state. If it is forced into holdover state, then the DPLL will stay in holdover even if there are valid references available for the DPLL to lock to. Register bits DPLL\_STATE\_DPLL0[2:0] and DPLL\_STATE\_DPLL1[2:0] can be used to set the DPLL-0 and DPLL-1, respectively, to holdover.

#### Pull-in/Hold-in

Both DPLLs support independently a pull-in range of  $\pm 4.6 \times 10^{-6}$ ,  $\pm 12 \times 10^{-6}$ ,  $\pm 20 \times 10^{-6}$ ,  $\pm 32 \times 10^{-6}$ ,  $\pm 52 \times 10^{-6}$ ,  $\pm 83 \times 10^{-6}$ ,  $\pm 131 \times 10^{-6}$ , and  $\pm 147 \times 10^{-6}$ .

# Free-Run Frequency Accuracy

The free-run accuracy is dependent on the oscillator, both DPLLs support free run accuracy based on the local oscillator.

## Phase Slope Limiting (PSL)

Each DPLL supports independent phase slope limiting that is programmable through registers. Each DPLL allows the phase slope limiting to be set such as 1ns/s, 5ns/s, 10 ns/s, 885ns/s, 7.5μs/s, or 61μs/s to meet different applications. It can also be bypassed.

## IEEE 1588 Modes of operation

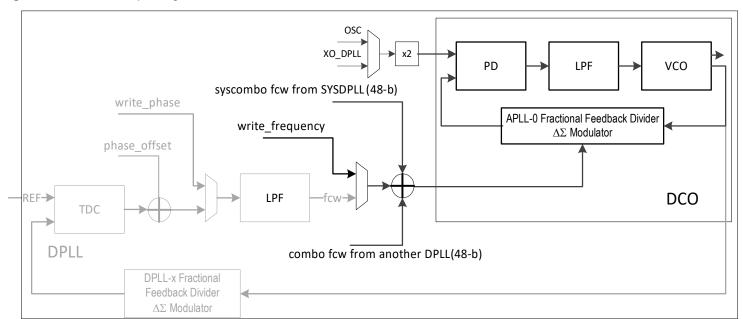

## Write Frequency Mode

The DCO circuits from DPLL-0 and DPLL-1 can be controlled by a digital word that can represent phase offset and frequency offset. Bits WRITE\_FREQUENCY\_EN\_DPLL0 and WRITE\_FREQUENCY\_EN\_DPLL1can be used to program DPLL-0 and DPLL-1 respectively in the write frequency mode.

Figure 8 shows the DCO being controlled by writing a frequency control word into the DCO. The Frequency Control Word (FCW) is used to adjust the frequency output of the DCO, the phase detector and loop filter are bypassed. In this case, the filtering is done by an external processor that will be controlling the DCO. The frequency offset written into the register is passed on directly to the output clocks. The FCW (WRITE\_FREQUENCY\_DPLL1[41:0]) is a 42-bit 2's-complement value, the total range is ±244ppm of the nominal DCO frequency, and the DCO programming resolution is 1.1 × 10<sup>-7</sup>ppb.

Figure 8. Write Frequency Mode

In write frequency mode, APLL VCO is tuned by the FCW as follows:

$$f_{vco} = f_{xo} \times N \times (1+FCW)$$

Where:

f<sub>vco</sub> is the APLL VCO frequency.

f<sub>x0</sub> is the OSCI/OSCO/XO\_DPLL frequency which is fixed.

N is the nominal APLL feedback divider ratio.

FCW is the tuning word which is 42-bit 2's complement and LSB is 2<sup>-53</sup>.

FCW is calculated as follows:

FCW = FFO

$$\times$$

10<sup>-6</sup>  $\times$  2<sup>53</sup>

and

FFO is the target fractional frequency in ppm.

As an example, change the output frequency by 10ppb ( $10 \times 10^{-3}$ ppm) on DPLL-1:

Control word (in decimal):  $10 \times 10^{-3} \times 10^{-6} \times 2^{53} = 90,071,992.547409020$

Convert 90,071,992 into Hex (0x55E63B8) to write into register (WRITE\_FREQUENCY\_DPLL0[41:0]/WRITE\_FREQUENCY\_DPLL1[41:0]).

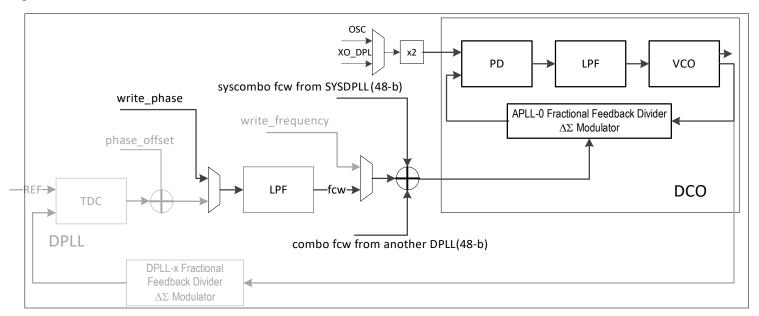

#### Write Phase Mode

Each DCO of DPLL-0 and DPLL-1 can be controlled by a digital word that can represent phase offset, and use the hardware loop filter to filter it per Figure 9.

Bits WRITE\_PHASE\_EN\_DPLL0 and WRITE\_PHASE\_EN\_DPLL1 can be used to program DPLL-0 and DPLL-1 respectively in the write phase mode.

Figure 9. Write Phase Mode

Figure 9 shows the DCO being controlled by writing a phase offset word into the DCO, then an external processor directly controls the DCO phase through the Microport interface with hardware controlled bandwidth (e.g., 0.1Hz per G.8273.2) and phase slope limiting.

The phase control word (PCW) can be written into WRITE\_PHASE\_DPLL0[31:0]/WRITE\_PHASE\_DPLL1[31:0] bits for DPLL-0/1.

The PCW is a 32-bit 2's-complement value. The resolution of the PCW is 1 TDC step. The TDC step is  $T_{SYSAPLL\_VCO}$  / 62 and the range is  $\pm$ (2147483647×(TDC step)). For example, if the system DPLL VCO frequency is 864MHz, then the TDC step is 18.6678614097969ps, and the range is  $\pm$ 40.0889271020012ms.

The PCW applied to LPF (Low Pass Filter) is equivalent to applying a phase error measured by the on-chip TDC (Phase Detector) applied to LPF when the DPLL is operating in closed loop. The update rate needs to be at least 60 times of the loop filter bandwidth; as an example, for 0.1Hz, the update rate should be greater than 6Hz.

To assist in the above, there is an optional timer associated with the PCW and the FCW. This allows a phase/frequency control word to be applied for a limited period of time after which it will automatically go into holdover, and therefore it will avoid the DCO to continue to apply the phase/frequency adjustment indefinitely until it reaches its tuning range limits. The timer value is a 16-bit integer (see WRITE\_TIMER\_DPLL0[15:0]/WRITE\_TIMER\_DPLL1[15:0]), it can be set in multiples of 125µs.

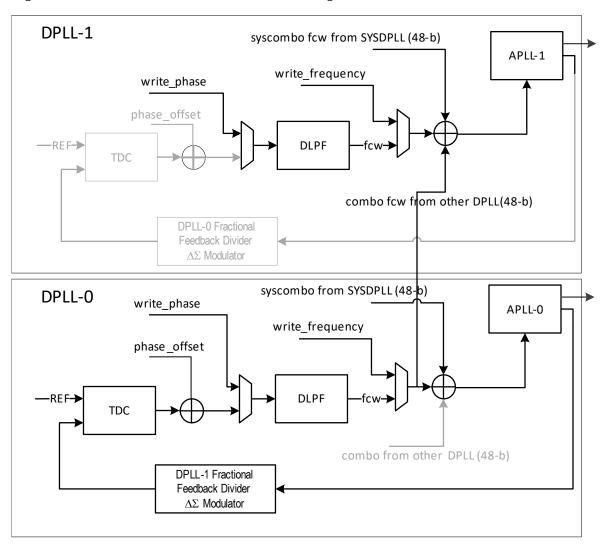

#### Combo Mode

The 8V19N850 supports DPLL combo mode. Both DPLL-0 or DPLL-1 can be programmed to either the combo master (the generator of the frequency control word (FCW), or the combo slave (the receiver of the FCW).

For example, if COMBO\_MODE\_EN\_DPLL0 is set to zero, and COMBO\_MODE\_EN\_DPLL1 is set to 1, then DPLL-0 is the combo master and DPLL-1 is the combo slave. In this example, DPLL-0 can be locked to an input reference clock, such as a Synchronous Ethernet clock, which is a regular PLL channel and can generate output clocks of different frequencies that track the Synchronous Ethernet input reference clock. And the DPLL-1 can be used as a DCO and it will be controlled externally, as an example by an IEEE 1588 clock recovery servo algorithm running in an external processor.

In this example, the IEEE 1588 timestamps can be used to calculate the phase offset between the IEEE 1588 master's 1PPS pulse and then align the two pulses by moving the slave's 1PPS pulse in phase. The phase offset between the IEEE 1588 master's 1PPS pulse and the IEEE 1588 slave's 1PPS pulse can be written into the Phase Control Word into DPLL-1 channel over the serial port to correct the phase, as described in the Write-Phase Mode section.

Figure 10 shows a functional block diagram of the combo mode.

Figure 10. Combo Mode Functional Block Diagram

The phase and frequency offsets between the combo master and slave are available for software to read at all times. The frequency information can be temporarily placed on hold (i.e., to ride out a phase transient).

## Phase Adjustment through DPLL

The 8V19N850 supports phase adjustments to be done through the DPLL-0 and DPLL-1. Figure 11 shows a functional block DPLL-0/-1.

Figure 11. DPLL-0/-1 Functional Block Diagram

When DPLL-0/-1 is locked to a clock, the phase of the output clock can be adjusted using a Phase Offset Word (phase\_offset in Figure 11).

The phase offset word (POW) is a 36-bit 2's-complement value. It can be written into PHASE\_OFFSET\_DPLL0[35:0]/PHASE\_OFFSET\_DPLL1[35:0] bits for DPLL-0/1. The resolution of the POW is 1 TDC step. The TDC step is  $T_{SYSAPLL\_VCO}$  / 62 and the range is  $\pm$ (2147483647  $\times$  ( $T_{DC\_STEP}$ )). For example, if the system DPLL VCO frequency is 864MHz, then the TDC step is 18.6678614097969ps, and the range is  $\pm$ 40.0889271020012ms.

#### Input Clock Qualification and Reference Selection

The input clock qualification is based on the reference monitoring (for more information, see Input Clock Quality Monitoring). The device has three reference selection modes set by the REF\_SEL\_MODE\_DPLL0/1 bits as follows:

- Pin selection mode through selection pins (assigned GPIO pins)

- Manual selection mode through register bits set through SPI/I3C interface.

- Automatic input clock selection mode

There is an independent reference selection process for each DPLL. The mode for each DPLL can be set as shown in Table 12

Table 12. REF\_SEL\_MODE\_DPLL0/1 Bits to Select the DPLL Mode

| REF_SEL_MODE_DPLL0[1:0],<br>REF_SEL_MODE_DPLL1[1:0] | Description                                                               |

|-----------------------------------------------------|---------------------------------------------------------------------------|

| 00                                                  | Pin Selection Mode through assigned GPIO pins                             |

| 01                                                  | Manual selection Mode through register bits set through SPI/I3C interface |

| 10                                                  | Automatic selection mode                                                  |

| 11                                                  | Reserved                                                                  |

#### Pin Selection Mode

In this mode, if REF\_SEL\_MODE\_DPLL0/1[1:0] are set to 00, then both DPLLs lock to the input reference selected by GPIOs

Table 13. Reference Input Selection by Pins for DPLL-0

| Selection by GPIO<br>CLKnSEL0 | Description |

|-------------------------------|-------------|

| 0.                            | CLK_0       |

| 1.                            | CLK_1       |

Table 14. Reference Input Selection by Pins for DPLL-1

| Selection by GPIO<br>CLKnSEL1 | Description |

|-------------------------------|-------------|

| 0                             | CLK_0       |

| 1                             | CLK_1       |

The input clock monitoring will continue to monitor the input clock, and if the selected input reference fails and the bit fail\_hold is set, then the DPLL will enter holdover automatically. The DPLL will automatically recover from holdover (or free-run) when the reference becomes valid or if another valid reference is selected by GPIO (CLKnSEL1/0) pins. If the selected reference is invalid and no other valid reference gets selected by the GPIO (CLKnSEL1/0) pins, then the DPLL will continue in holdover state.

If fail\_hold bit is not set, then the DPLL continues to lock to the reference clock selected by GPIO (CLKnSEL1/0) pins, even if that particular reference is no longer valid. The DPLL will continue to track the clock selected by GPIO (CLKnSEL1/0) pins and will do a reference switching once the GPIO (CLKnSEL1/0) pins select another clock input. If the selected reference is invalid and no other valid reference gets selected by the GPIO (CLKnSEL1/0) pins, then the DPLL will continue to track to the invalid reference.

In this mode, when doing a reference switching between two inputs, they must be at the same frequency. If they have different frequencies, then the input dividers can be used to divide down the frequency to a common frequency to the internal input of the DPLL.

#### Manual Selection Mode

In this mode, each DPLL locks to the input reference selected by ref man sel dpll0/1 bit in the appropriated register per Table 15.

Table 15. Manual Reference Input Selection by Register Bits

| ref_man_sel_dpll0/1 | Description |

|---------------------|-------------|

| 0                   | CLK_0       |

| 1                   | CLK_1       |

In this mode, each DPLL has its own set of registers and therefore each DPLL can select a different input based on the ref\_man\_sel\_dpll0/1 selection bits for each DPLL. The automatic state machine is disabled and the input clock monitoring does not affect the input clock selection.

In this mode, the input clock selection is done by setting the proper bits in the control registers related to each DPLL, the input clock monitoring will continue to monitor the input clock (see Input Clock Quality Monitoring), and if the selected input reference fails, then the DPLL will enter holdover automatically. The DPLL will automatically recover from holdover (or free-run) when the reference becomes valid or if another valid reference is selected by the ref man sel dpll0/1 register bit.

In this mode, if the selected reference is invalid and no other valid reference gets selected by the ref\_man\_sel\_dpll0/1 register bit, then the DPLL will enter holdover state.

## Automatic Input Clock Selection Mode

If automatic input clock selection is used, then an internal automatic state machine will automatically do reference switching and the input clock selection is determined by the input clock being qualified. An input is considered qualified based on being valid by the clock monitor (see Input Clock Quality Monitoring), the priority of each input clock, and the input clock configuration.

If bits DIS\_CLK0\_BY\_PIN and DIS\_CLK1\_BY\_PIN are set to 1, then a GPIO (see Input Disqualification by GPIO pins) can be used to disable CLK\_0 and CLK\_1 to be used by DPLL-O and DPLL-1.

If bits DIS\_CLK0\_BY\_PIN and DIS\_CLK1\_BY\_PIN are set to 0, then bits DIS\_CLK0 and DIS\_CLK1 can be used to disable CLK\_0 and CLK\_1 to be used by DPLL-O and DPLL-1. If the input is enabled (DIS\_CLK0 or DIS\_CLK1 is set to 0) and the reference monitors declare that input valid, then that input is qualified to be used by the DPLLs. If the input is disabled (DIS\_CLK0 or DIS\_CLK1 is set to 1), and even though the reference monitors declare that input valid, then that input is disqualified to be used by the DPLLs.

Within all the qualified inputs, the one with the highest priority is selected by the DPLL. The input clock priority is set by setting bits REF\_PRIORITY\_DPLL0 and REF\_PRIORITY\_DPLL1 for DPLL-0 and DPLL-1 respectively.

#### Reference Switching

### Automatic reference Switching

In Automatic Locked Mode, the input clock selection must be determined by the input clock being qualified. An input is considered qualified based on being valid by the clock monitor (see Input Clock Quality Monitoring), the priority of each input clock, and the input clock configuration.

The input clock must be declared valid depending on the results of input clock quality monitoring (refer to Input Clock Quality Monitoring). Within all the valid input clocks (the ones that do not have fail alarm(s)), the one with the highest priority must be selected.

The priority must be set by setting bits REF\_PRIORITY\_DPLL0 and REF\_PRIORITY\_DPLL1 for DPLL-0 and DPLL-1 respectively. The input clock must also be configured to be valid or invalid by register configuration. If hitless reference switching is enabled, then the output phase change is below 1ns when the device performs a reference switching between two reference inputs that are integer multiple ratios of each other, and are divided down to the least common frequency through the pre-dividers.

#### Hitless Reference Switching

Hitless reference switching is supported for all frequency clocks.

The Hitless Switching (HS) circuit eliminates phase transients on the output clock that may occur during reference switching or the recovery from Holdover state to Locked state. On recovery from holdover state or when switching to another reference input, the HS circuit measures the phase delay between the current phase (feedback signal) and the phase of the newly selected reference input. This delay value is used by the PLL to minimize the phase transient it experiences when it switches to another reference input or recovers from holdover state.

An HS event must be triggered if either of the following conditions occurs:

- DPLLs selected input clock switches to a different reference

- DPLLs exits from holdover state

For the two conditions above, the phase transients on the DPLLs output are minimized < 1ns with Hitless Switching (HS) enabled.

If HS is disabled, then there may be a phase shift on the DPLLs output, as the DPLLs output tracks back to 0 degree phase offset with respect to the DPLLs selected input clock.

When HS is enabled, there could be cases where it is needed to clear the phase (as an example, the DPLL goes into holdover for a long period of time, and therefore it is better to not do a hitless reference switching when it recovers from a long-term holdover state). In this case a bit, HS\_CLR, can be set to clear the delay value (TIE). In general, HS\_CLK should not be exercised when holdover state is entered for short time periods. The speed of the phase alignment correction is limited by the PSL setting.

## Revertive and Non-Revertive Reference Switching

The 8V19N850 supports revertive and non-revertive reference switching. Revertive switching can be disabled by register bit.

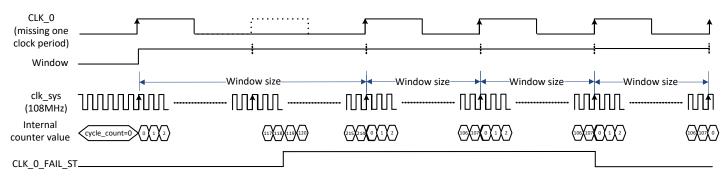

#### Input Clock Quality Monitoring

The quality of all the input reference clocks is always monitored individually (excluding the OSCI/OSCO or XO\_DPLL input), 8V19N850 has 3 reference monitors as follows:

- Short-term monitor (this monitor can be used for LOS (loss of signal) detector)

- Medium-term monitor (this monitor can be used for activity)

- Long-term monitor (this monitor can be used for detecting frequency offset)

Each input clock can be individually configured for monitoring, and each monitor type can be masked. The active reference is also monitored to ensure that it is still a valid reference. If an input clock fails, then an alarm will be generated, an input clock with an alarm condition cannot be used for an input reference if the alarm is not masked. The reference monitor is based on reference clock of the system APLL (OSCI/OSCO or XO\_DPLL). A TCXO/OCXO must be used for better accuracy.

#### Short-Term Monitor

Each input clock reference is monitored using the short-term monitor. The short-term monitor can be used to detect loss of signal. It supports input clock frequencies equal to or above 1MHz.

The short-term monitor takes the input clock from after the input high frequency pre-divider (maximum frequency is 36MHz) and before the input pre-divider. The period of this frequency is used to create a window to compare whether or not the input clock is within a certain frequency. The window size is programmable.

- Window size = T<sub>RFF</sub> (if DIV\_RATIO\_ST is set to 0 or to 1)

- Window size = (DIV\_RATIO\_ST+2) × T<sub>RFF</sub>

- T<sub>RFF</sub> = period of the input reference clock, after high frequency pre-divider

Where DIV\_RATIO\_ST is programmable by using bits DIV\_RATIO\_ST\_REF\_MON0[5:0] and DIV\_RATIO\_ST\_REF\_MON1[5:0] for CLK\_0 and CLK\_1, respectively.

A counter that is part of the short-term monitor is used to count the number of system clocks (SYS\_CLK that is approximately 108MHz) within the window.

The nominal counter value is calculated as follows:

- NOMINAL\_NUM\_ST = f<sub>SYS\_CLK</sub> / f<sub>REF</sub> (if DIV\_RATIO\_ST is set to 0 or to 1)