## 10G Ethernet PLL and IEEE 1588 Synthesizer for Industrial Automa-

# Short Form Datasheet IDT8V89317

## FEATURES

## HIGHLIGHTS

- Digital PLL locks to GPS or Ethernet physical layer clocks

- Provides clocks for 1 Gigabit and 10 Gigabit Ethernet, QSGMII and XAUI

- Internal Digitally Controlled Oscillator supports IEEE 1588 clocks generation

- Jitter generation <0.3ps RMS (10 kHz to 20 MHz), meets jitter requirements of leading PHYs supporting 10GBASE-R, QSGMII and XAUI

## MAIN FEATURES

- Digital PLL synchronizes with GPS or Ethernet connected synchronization sources

- DPLL bandwidth is selectable to be 15 mHz or 1.2 Hz

- DPLL holdover accuracy is 1.1X10-5 ppm and instantaneous holdover accuracy is 4.4X10-8 ppm

- Input references are monitored for frequency offset and activity

- DPLL holdover, free run and hitless reference switching can be forced by the host processor or can be automatically controlled by an internal state machine

- Internal DCO has resolution of 0.01105 ppb and can be controlled by an external processor via I2C interface for IEEE 1588 clock generation

- Two Analog PLLs for jitter attenuation and frequency translation

- IN1, IN2 and IN3 accept single ended reference clocks whose frequencies can be 1PPS (1 Hz), 25 MHz, 125 MHz or 156.25 MHz

- OUT1 and OUT2 output differential clocks with frequencies of 125 MHz or 156.25 MHz

- OUT3 outputs a differential clock with frequency of 322.265625 MHz or 644.53125 MHz

- OUT4 outputs a free-running LVCMOS clock with frequency of 25 MHz

## **OTHER FEATURES**

- I2C microprocessor interface mode

- IEEE 1149.1 JTAG Boundary Scan

- 1mm ball pitch CABGA green package

## **APPLICATIONS**

- Industrial Automation

- Power Systems

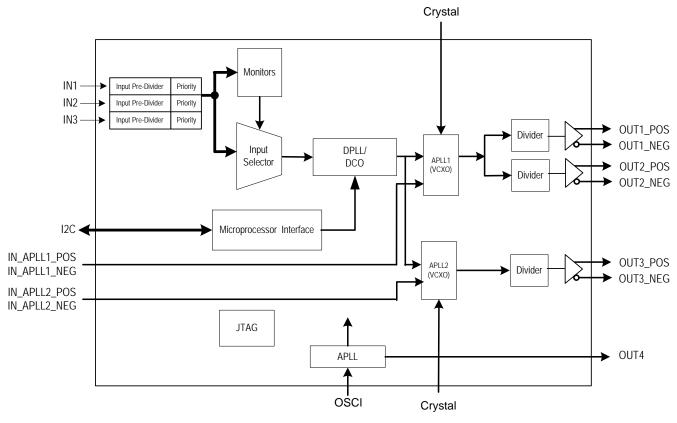

Figure 1. Functional Block Diagram

IDT and the IDT logo are trademarks of Integrated Device Technology, Inc IEEE 1588 $^{\rm TM}$  is a trademark of its respective owner

## DESCRIPTION

The IDT8V89317 10G Ethernet PLL for Industrial Automation and Power Systems is used to synchronize equipment with synchronization sources using the Ethernet physical layer, or with a 1 PPS (1 Hz) GPS clock; it can also be used by external IEEE 1588 clock recovery servos to synthesize IEEE 1588 clocks. The IDT8V89317 ultra-low jitter output clocks can be used to directly synchronize 10GBASE-R Ethernet PHYs and XAUI or QSGMII devices.

The IDT8V89317 synchronization functions are provided by a Digital PLL (DPLL) with an embedded clock synthesizer. The DPLL accepts three single ended reference inputs that can operate at 1PPS (1 Hz), 25 MHz, 125 MHz or 156.25 MHz. The references are continually monitored for loss of signal and for frequency offset per user programmed thresholds. The active reference for the DPLL is determined by forced selection or by automatic selection based on user programmed priorities and locking allowances and based on the reference monitors.

The DPLL supports four primary operating modes: Free-Run, Locked, Holdover and Digitally Controlled Oscillator (DCO) Control. In Free-Run mode the DPLL generates a clock based on the master clock alone. In Locked mode the DPLL filters reference clock jitter with the selected bandwidth. In Locked mode the long-term DPLL frequency accuracy is the same as the long term frequency accuracy of the selected input reference. In Holdover mode the DPLL uses frequency data acquired while in Locked mode to generate accurate frequencies when input references are not available. In DCO Control Mode the DPLL control loop is opened and the DCO can be used by an algorithm (e.g. IEEE 1588 clock servo) running on an external processor to synthesize clock signals.

The IDT8V89317 requires a 12.8 MHz master clock for its reference monitors and other digital circuitry. The frequency accuracy of the master clock determines the frequency accuracy of the DPLL in Free-Run mode. The frequency stability of the master clock determines the frequency stability of the DPLL in Free-Run mode and in Holdover mode. The master clock must be sufficiently stable to support the selected DPLL filtering bandwidth; in particular, the 15 mHz bandwidth requires a very stable temperature compensated crystal oscillator (TCXO) or ovenized crystal oscillator (OCXO). Refer to the IDT application note "Recommended Crystal Oscillators for IDT's Network Synchronization WAN-PLL<sup>™</sup> for quidance.

The DPLL can be configured with a filtering bandwidth of 15 mHz or 1.2 Hz. The 15 mHz bandwidth can be used to lock the DPLL directly to a 1 pulse per second (PPS) reference. 1.2 Hz bandwidth can be used to lock to Ethernet connected synchronization sources operating at 25 MHz, 125 MHz or 156.25 MHz.

The clock synthesized by the IDT8V89317 DPLL is passed through two independent voltage controlled crystal oscillator (VCXO) based jitter attenuating analog PLLs (APLLs). The APLLs drive independent dividers that have differential outputs. The APLLs use external crystal resonators with resonant frequencies equal to the APLL base frequency divided by 25. The output clocks generated by the APLLs exhibit jitter below 0.30ps RMS over the integration range 10 kHz to 20 MHz.

The IDT8V89317 generates a 25 MHz single ended output that is based on the free running 12.8 MHz master clock. The frequency accuracy and the frequency stability of this 25 MHz clock are determined by the master clock.

© 2019 Renesas Electronics Corporation

## 1 PIN ASSIGNMENT

|   | 1               | 2        | 3         | 4     | 5                | 6                | 7     | 8       | 9       | 10        | 11        | 12    | 13      | 14      |   |

|---|-----------------|----------|-----------|-------|------------------|------------------|-------|---------|---------|-----------|-----------|-------|---------|---------|---|

| А | IC1             | VDDA     | XTAL1_IN  | CAP1  | IN_APLL1_N<br>EG | IC1              | IC1   | TDI     | IC1     | IC2       | OSCI      | TMS   | IC1     | TRST    | Α |

| В | IC1             | VSSA     | XTAL1_OUT | VSSA  | IN_APLL1_P<br>OS | IC1              | IC1   | TDO     | VSSA    | тск       | VSSA      | VSSA  | VSSDO   | VDDDO   | В |

| с | IC1             | VDDA     | NC        | CAP2  | IC1              | IC1              | VDDDO | VSSDO   | VDDA    | VSSA      | VDDA      | VDDA  | INT_REQ | IC1     | С |

| D | VSSA            | VSSA     | САРЗ      | VSSA  | VDDA             | IC1              | VSSD  | VDDD    | IC1     | VDDA      | VSSA      | VDDA  | IC1     | IC1     | D |

| E | IC1             | IC1      | VSSA      | VSSA  | VSSA             | IC3              | VSSD  | VDDD    | IC1     | VSSA      | VDDA      | VSSA  | IC1     | IC1     | E |

| F | VDDD            | VSSD     | VSSA      | VSSA  | VDDA             | VSSA             | VSSD  | VDDD    | VSSD    | VDDD      | IC1       | VDDDO | OUT4    | VSSDO   | F |

| G | VSSD            | VDDD     | VSSA      | VSSA  | VSSA             | VSSD             | VDDD  | IC1     | VDDD    | VSSD      | IC1       | IC1   | IC1     | IC1     | G |

| н | VDDAO           | VSSAO    | VDDAO     | VSSAO | VSSAO            | VSSAO            | VSSD  | VDDD    | VSSD    | VDDD      | IC1       | IC1   | RST     | IN1     | Н |

| L | OUT1_NEG        | OUT1_POS | VDDAO     | VSSAO | VDDAO            | VSSAO            | VDDAO | VSSA    | VSSA    | VDDA      | DPLL_LOCK | IC1   | IN2     | IN3     | J |

| к | VSSAO           | VSSAO    | VSSAO     | VDDAO | VSSAO            | VDDAO            | VSSAO | VSSD    | VDDD    | VSSD      | IC1       | IC1   | I2C_SCL | I2C_SDA | К |

| L | OUT2_NEG        | OUT2_POS | VDDAO     | VSSAO | VSSAO            | VSSAO            | VSSAO | I2C_AD1 | I2C_AD2 | CAP4      | VSSA      | CAP5  | VSSA    | САР6    | L |

| м | VDDAO           | VSSAO    | VSSAO     | VSSAO | VDDAO            | VSSAO            | VDDAO | VSSA    | VSSA    | VSSA      | VSSA      | NC    | ю       | IC      | М |

| N | VSSAO           | OUT3_POS | VSSAO     | IC1   | VSSAO            | IN_APLL2_P<br>OS | IC2   | IC2     | VSSA    | XTAL2_OUT | VSSA      | IC1   | VSSA    | VSSA    | N |

| Р | VDDAO           | OUT3_NEG | VSSAO     | IC1   | VDDAO            | IN_APLL2_N<br>EG | IC2   | IC2     | VDDA    | XTAL2_IN  | VDDA      | IC1   | IC1     | VDDA    | P |

|   | 1               | 2        | 3         | 4     | 5                | 6                | 7     | 8       | 9       | 10        | 11        | 12    | 13      | 14      |   |

|   | Key:            |          |           |       |                  |                  |       |         |         |           |           |       |         |         |   |

|   | Diff<br>Outputs | Outputs  | Inputs    | Power | Ground           |                  |       |         |         |           |           |       |         |         |   |

Figure 2. Pin Assignment (Top View)

## 2 PIN DESCRIPTION

Table 1: Pin Description

| Name                                                            | Name Pin No. |                         | Туре    | Description <sup>1</sup>                                                                                                                                                      |  |  |  |  |

|-----------------------------------------------------------------|--------------|-------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                 |              |                         | Glob    | al Control Signal                                                                                                                                                             |  |  |  |  |

| OSCI                                                            | A11          | I                       | CMOS    | OSCI: Crystal Oscillator Master Clock<br>A nominal 12.8000 MHz clock provided by a crystal oscillator is input on this pin. It is the<br>master clock for the device.         |  |  |  |  |

| RST H13                                                         |              | l<br>pull-up            | CMOS    | RST: Reset<br>A low pulse of at least 50 $\mu$ s on this pin resets the device. After this pin is high, the<br>device will still be held in reset state for 500 ms (typical). |  |  |  |  |

|                                                                 |              |                         |         | Input Clock                                                                                                                                                                   |  |  |  |  |

| IN1                                                             | H14          | l<br>pull-down          | CMOS    | IN1: Input Clock 1<br>Either a 1 PPS, 25 MHz, 125 MHz or 156.25 MHz is input on this pin.                                                                                     |  |  |  |  |

| IN2                                                             | J13          | l<br>pull-down          | CMOS    | IN2: Input Clock 2<br>Either a 1 PPS, 25 MHz, 125 MHz or 156.25 MHz is input on this pin.                                                                                     |  |  |  |  |

| IN3                                                             | J14          | l<br>pull-down          | CMOS    | IN3: Input Clock 3<br>Either a 1 PPS, 25 MHz, 125 MHz or 156.25 MHz is input on this pin.                                                                                     |  |  |  |  |

| IN_APLL1_POS                                                    | B5           | I pull-down             | LVPECL/ | IN_APLL1_POS / IN_APLL1_NEG: Input Clock to APLL1<br>Direct input clock to APLL1.                                                                                             |  |  |  |  |

| IN_APLL1_NEG                                                    | A5           | l pull-up/<br>pull-down | LVDS    |                                                                                                                                                                               |  |  |  |  |

| IN_APLL2_POS                                                    | N6           | I pull-down             | LVPECL/ | IN_APLL2_POS / IN_APLL2_NEG: Input Clock APLL2<br>Direct input clock to APLL2.                                                                                                |  |  |  |  |

| IN_APLL2_NEG                                                    | P6           | l pull-up/<br>pull-down | LVDS    |                                                                                                                                                                               |  |  |  |  |

|                                                                 |              |                         | (       | Dutput Clock                                                                                                                                                                  |  |  |  |  |

| OUT1_POS<br>OUT1_NEG                                            | J2<br>J1     | 0                       | LVPECL  | OUT1_POS / OUT1_NEG: Positive / Negative Output Clock 1<br>A clock is differentially output on this pair of pins. It outputs either 125 MHz or 156.25<br>MHz                  |  |  |  |  |

| OUT2_POS<br>OUT2_NEG                                            | L2<br>L1     | 0                       | LVPECL  | OUT2_POS / OUT2_NEG: Positive / Negative Output Clock 2<br>A clock is differentially output on this pair of pins. It outputs either 125 MHz or 156.2<br>MHz                   |  |  |  |  |

| OUT3_POS<br>OUT3_NEG                                            | N2<br>P2     | 0                       | LVPECL  | OUT3_POS / OUT3_NEG: Positive / Negative Output Clock 3<br>A clock is differentially output on this pair of pins. It outputs 322.265625 MHz or<br>644.53125 MHz               |  |  |  |  |

| OUT4                                                            | F13          | 0                       | CMOS    | OUT4: CMOS Output Clock 4<br>A free run 25 MHz clock is output on this pin.                                                                                                   |  |  |  |  |

|                                                                 | 1            |                         | N       | liscellaneous                                                                                                                                                                 |  |  |  |  |

| CAP1, CAP2, CAP3,<br>CAP4, CAP5, CAP6 A4, C4, D3, L10, L12, L14 |              | Output                  | Analog  | CAP1 ~ CAP6: Analog Power Filter Capacitor connection 1 to 6<br>Connect a 10 uF capacitor in parallel with a low ESR 100 nF capacitor between these<br>pins and VSS1          |  |  |  |  |

| XTAL1_IN                                                        | A3           | Input                   | Analog  | Crystal 1 oscillator input.<br>Crystal oscillator input for APLL.                                                                                                             |  |  |  |  |

| XTAL1_OUT                                                       | B3           | Output                  | Analog  | Crystal 1oscillator output.<br>Crystal oscillator output for APLL.                                                                                                            |  |  |  |  |

| XTAL2_IN                                                        | P10          | Input                   | Analog  | Crystal 2 oscillator input.<br>Crystal oscillator input for APLL.                                                                                                             |  |  |  |  |

| XTAL2_OUT                                                       | N10          | Output                  | Analog  | Crystal 2 oscillator output.<br>Crystal oscillator output for APLL.                                                                                                           |  |  |  |  |

|                                                                 |              |                         | Lock    | Indication Signals                                                                                                                                                            |  |  |  |  |

© 2019 Renesas Electronics Corporation

### Table 1: Pin Description (Continued)

| Name      | Pin No.                                                              | I/O            | Туре       | Description <sup>1</sup>                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-----------|----------------------------------------------------------------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DPLL_LOCK | DPLL_LOCK J11                                                        |                | CMOS       | DPLL lock indicator.<br>This pin goes high when DPLL is locked.                                                                                                                                                                                                                                                                                           |  |  |  |

|           |                                                                      |                | Microp     | rocessor Interface                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| INT_REQ   | C13                                                                  | 0              | CMOS       | INT_REQ: Interrupt Request<br>This pin is used as an interrupt request. The output characteristics are determined by<br>the HZ_EN bit (b1, 0CH) and the INT_POL bit (b0, 0CH).                                                                                                                                                                            |  |  |  |

| I2C_SCL   | K13                                                                  | I              | Open Drain | I2C_SCL: Serial Clock Line<br>In I2C mode, the serial clock is input on this pin.                                                                                                                                                                                                                                                                         |  |  |  |

| I2C_SDA   | K14                                                                  | I/O            | Open Drain | I2C_SDA: Serial Data Input/Output<br>In I2C mode, this pin is used as the input/output for the serial data.                                                                                                                                                                                                                                               |  |  |  |

| I2C_AD1   | L8                                                                   | l<br>pull-up   | CMOS       | I2C_AD1: Device Address Bit 1<br>In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface.                                                                                                                                                                                                                                       |  |  |  |

| I2C_AD2   | I2C_AD2 L9                                                           |                | CMOS       | I2C_AD2: Device Address Bit 2<br>In I2C mode, I2C_AD[2:0] pins are the address bus of the microprocessor interface.                                                                                                                                                                                                                                       |  |  |  |

|           |                                                                      |                | JTAG       | (per IEEE 1149.1)                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TRST      | A14                                                                  | l<br>pull-down | CMOS       | TRST: JTAG Test Reset (Active Low)<br>A low signal on this pin resets the JTAG test port.<br>This pin should be connected to ground when JTAG is not used.                                                                                                                                                                                                |  |  |  |

| TMS       | A12                                                                  | l<br>pull-up   | CMOS       | TMS: JTAG Test Mode Select<br>The signal on this pin controls the JTAG test performance and is sampled on the rising<br>edge of TCK.                                                                                                                                                                                                                      |  |  |  |

| TCK       | B10                                                                  | l<br>pull-down | CMOS       | TCK: JTAG Test Clock<br>The clock for the JTAG test is input on this pin. TDI and TMS are sampled on the rising<br>edge of TCK and TDO is updated on the falling edge of TCK.<br>If TCK is idle at a low level, all stored-state devices contained in the test logic will indef-<br>initely retain their state.                                           |  |  |  |

| TDI       | A8                                                                   | l<br>pull-up   | CMOS       | TDI: JTAG Test Data Input<br>The test data is input on this pin. It is clocked into the device on the rising edge of TCK.                                                                                                                                                                                                                                 |  |  |  |

| TDO       | B8                                                                   | 0              | CMOS       | TDO: JTAG Test Data Output<br>The test data is output on this pin. It is clocked out of the device on the falling edge of<br>TCK.<br>TDO pin outputs a high impedance signal except during the process of data scanning.<br>This pin can indicate the interrupt of DPLL selected input clock fail, as determined by<br>the LOS_FLAG_ON_TDO bit (b6, 0BH). |  |  |  |

|           | •                                                                    |                | Po         | wer & Ground                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VDDD      | D8, E8, F1, F8, F10, G2,<br>G7, G9, H8, H10, K9                      | Power          | -          | Digital Core Power - +3.3V DC nominal                                                                                                                                                                                                                                                                                                                     |  |  |  |

| VDDDO     | B14, C7, F12                                                         | Power          |            | Digital Output Power - +3.3V DC nominal                                                                                                                                                                                                                                                                                                                   |  |  |  |

| VDDA      | A2, C2, C9, C11, C12, D5,<br>D10, D12, E11, F5, J10,<br>P9, P11, P14 | Power          |            | Analog Core Power - +3.3V DC nominal                                                                                                                                                                                                                                                                                                                      |  |  |  |

| VDDAO     | H1, H3, J3, J5, J7, K4, K6,<br>L3, M1, M5, M7, P1, P5                | Power          |            | Analog Output Power - +3.3V DC nominal                                                                                                                                                                                                                                                                                                                    |  |  |  |

| VSSD      | D7, E7, F2, F7, F9, G1,<br>G6, G10, H7, H9, K8, K10                  | Ground         | -          | Ground                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| VSSDO     | B13, C8, F14                                                         | Ground         | -          | Ground                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

#### Table 1: Pin Description (Continued)

| Name  | Pin No.                                                                                                                                                                                              | I/O    | Туре | Description <sup>1</sup>                                                                       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------------------------------------------------------------------------------------------------|

| VSSA  | B2, B4, B9, B11, B12,<br>C10, D1, D2, D4, D11, E3,<br>E4, E5, E10, E12, F3, F4,<br>F6, J9, G3, G4, G5, J8,<br>L11, L13, M8, M9, M10,<br>M11, N9, N11, N13, N14                                       | Ground | -    | Analog Ground                                                                                  |

| VSSAO | H2, H4, H5, H6, J4, J6,<br>K1, K2, K3, K5,K7, L4, L5,<br>L6, L7, M2, M3, M4, M6,<br>N1, N3, N5, P3                                                                                                   | Ground | -    | Analog Output Ground                                                                           |

|       |                                                                                                                                                                                                      |        |      | Others                                                                                         |

| IC1   | A1, A6, A7, A9, A13, B1,<br>B6, B7, C1, C5, C6, C14,<br>D6, D9, D13, D14, E1, E2,<br>E9, E13, E14, F11, G8,<br>G11, G12, G13, G14, H11,<br>H12, J12, K11, K12, M13,<br>M14, N4, N12, P4, P12,<br>P13 | -      | -    | IC1: Internal Connection<br>Internal Use. These pins should be left open for normal operation. |

| IC2   | A10, N7, N8, P7, P8                                                                                                                                                                                  | -      | -    | IC2: Internal Connection<br>Internal Use. These pins should be left open for normal operation. |

| IC3   | E6                                                                                                                                                                                                   | -      | -    | IC3: Internal Connection<br>Internal Use. This pin should be left open for normal operation.   |

| NC    | C3, M12                                                                                                                                                                                              | -      | -    | NC: Not Connected<br>These pins should be left open for normal operation.                      |

1. All the unused input pins should be connected to ground; the output of all the unused output pins are don't-care.

#### 2.1 RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

#### INPUTS 2.1.1

### Control Pins

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A 1  $k\Omega$ resistor can be used.

#### Single-Ended Clock Inputs

For protection, unused single-ended clock inputs should be tied to ground.

#### **Differential Clock Inputs**

For applications not requiring the use of a differential input, both \*\_POS and \*\_NEG can be left floating. Though not required, but for additional protection, a 1 k $\Omega$  resistor can be tied from \_POS to ground.

#### XTAL Inputs

For applications not requiring the use of a crystal oscillator input, both \_IN and \_OUT can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from \_IN to ground.

#### 2.1.2 OUTPUTS

#### Status Pins

For applications not requiring the use of a status pin, we recommend bringing out to a test point for debugging purposes.

### Single-Ended Clock Outputs

All unused single-ended clock outputs can be left floating, or can be broughtouttoatestpointfordebuggingpurposes.

#### **Differential Clock Outputs**

All unused differential outputs can be left floating. We recommend that there is no trace attached. Both sides of the differential output pair should either be left floating or terminated.

6

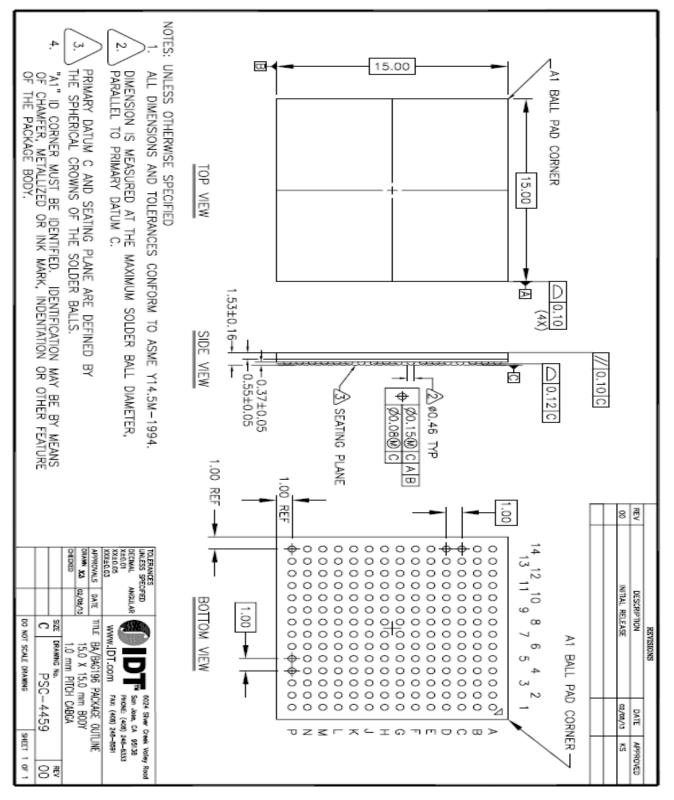

## PACKAGE DIMENSIONS

7

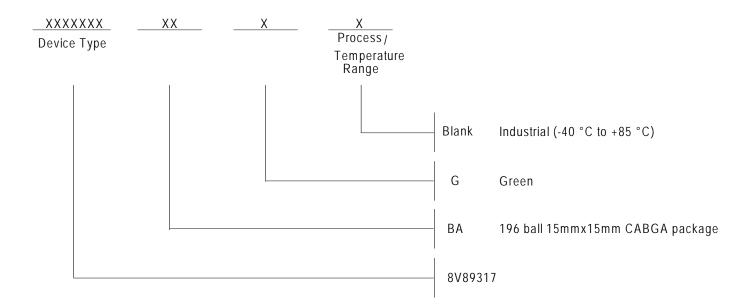

## **ORDERING INFORMATION**

## **REVISION HISTORY**

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Synthesizer/Jitter Cleaner category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

MPC9230EIR2 PL902166USY 954204CGLF 9LPRS485DGLF PL902167USY 8V19N490ABDGI LMK04821NKDT CDCE937QPWRQ1 PI6CX201ALE 9LPRS355BGLF CDCEL913IPWRQ1 ABMJB-903-101UMG-T5 ABMJB-903-150UMG-T5 ABMJB-903-151UMG-T5 AD9542BCPZ AD9578BCPZ 9FG104EFILF 9FG104EFLF 308RILF 840001BGI-25LF 843004AGLF 843801AGI-24LF 844004BGI-01LF 844S42BKILF 8A34044C-000NLG 954226AGLF 9FG108EFLF 9LPR363EGLF 9LPRS355BKLF 9LPRS365BGLF GS4915-INE3 9DB306BLLF ABMJB-902-155USY-T5 ABMJB-902-156USY-T5 ABMJB-902-Q76USY-T5 ABMJB-902-Q82USY-T5 ABMJB-902-104USY-T5 ABMJB-902-153USY-T5 ABMJB-902-154USY-T5 ABMJB-902-Q42USY-T5 ABMJB-902-Q57USY-T5 ABMJB-902-Q74USY-T5 ABMJB-902-Q78USY-T5 LTC6951IUHF-1#PBF 650GI-44LF 8430252CGI-45LF 8432DYI-101LF 84329BYLF 8432DY-101LF 8432BY-51LF