# 6-Output 1.8V PCIe Zero-Delay/Fanout Clock Buffer with Zo = 33Ohms

**DATASHEET**

## **Description**

The 9DBV0631 is a member of Renesas' 1.8V Very-Low-Power (VLP) PCIe family. The device has 6 output enables for clock management and 3 selectable SMBus addresses.

## **Recommended Application**

1.8V PCIe Gen1–5 Zero Delay/Fanout Buffer (ZDB/FOB)

## **Output Features**

• Six 1-200 MHz Low-Power (LP) HCSL DIF pairs

## **Key Specifications**

- DIF additive cycle-to-cycle jitter < 5ps

- DIF output-to-output skew < 60ps

- PCIe Gen5 CC additive phase jitter < 40fs RMS</li>

- 12kHz–20MHz additive phase jitter = 156fs RMS at 156.25MHz (typical)

#### Features/Benefits

- LP-HCSL outputs; save 12 resistors compared to standard PCIe devices

- 55mW typical power consumption in PLL mode; minimal power consumption

- Outputs can optionally be supplied from any voltage between 1.05 and 1.8V; maximum power savings

- OE# pins; support DIF power management

- HCSL-compatible differential input; can be driven by common clock sources

- · Spread Spectrum tolerant; allows reduction of EMI

- Programmable Slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- Pin/software selectable PLL bandwidth and PLL Bypass; minimize phase jitter for each application

- Outputs blocked until PLL is locked; clean system start-up

- Configuration can be accomplished with strapping pins;

SMBus interface not required for device control

- 3.3V tolerant SMBus interface works with legacy controllers

- Space saving 5 × 5mm 40-VFQFPN; minimal board space

- 3 selectable SMBus addresses; multiple devices can easily share an SMBus segment

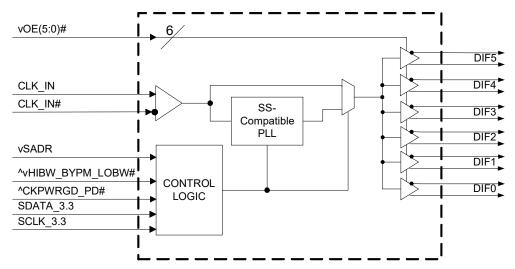

## **Block Diagram**

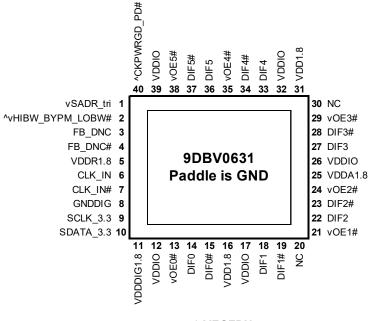

## **Pin Configuration**

#### 40-VFQFPN

^ prefix indicates internal Pull-Up Resistor v prefix indicates Internal Pull-Down Resistor 5mm x 5mm 0.4mm pin pitch

#### **SMBus Address Selection Table**

|                                       | SADR | Address | + Read/Write bit |

|---------------------------------------|------|---------|------------------|

| State of SADR on first application of | 0    | 1101011 | X                |

| CKPWRGD_PD#                           | M    | 1101100 | Х                |

|                                       | 1    | 1101101 | x                |

#### **Power Management Table**

| CKPWRGD PD# | CLK IN  | SMBus   | OEx# Pin  | D        | lFx       | PLL             |

|-------------|---------|---------|-----------|----------|-----------|-----------------|

| CKFWKGD_FD# | OLK_IN  | OEx bit | OLX# FIII | True O/P | Comp. O/P | FLL             |

| 0           | Х       | Х       | Х         | Low      | Low       | Off             |

| 1           | Running | 0       | Х         | Low      | Low       | On <sup>1</sup> |

| 1           | Running | 1       | 0         | Running  | Running   | On <sup>1</sup> |

| 1           | Running | 1       | 1         | Low      | Low       | On <sup>1</sup> |

<sup>1.</sup> If Bypass mode is selected, the PLL will be off, and outputs will follow this table.

#### **Power Connections**

| Pin Number |                    |     | Description   |

|------------|--------------------|-----|---------------|

| VDD        | VDDIO              | GND | Description   |

|            |                    |     | Input         |

| 5          |                    | 41  | receiver      |

|            |                    |     | analog        |

| 11         |                    | 8   | Digital Power |

| 16 21      | 12,17,26,32,       | 41  | DIF outputs,  |

| 16, 31     | 12,17,26,32,<br>39 | 41  | Logic         |

| 25         |                    | 41  | PLL Analog    |

## **Frequency Select Table**

| FSEL<br>Byte3 [1:0] | CLK_IN<br>(MHz) | DIFx<br>(MHz) |

|---------------------|-----------------|---------------|

| 00                  | 100.00          | CLK IN        |

| 01                  | 50.00           | CLK_IN        |

| 10                  | 125.00          | CLK_IN        |

| 11                  | Reserved        | Reserved      |

## **PLL Operating Mode**

|                 |           | Byte1 [7:6] | Byte1 [4:3] |

|-----------------|-----------|-------------|-------------|

| HiBW_BypM_LoBW# | MODE      | Readback    | Control     |

| 0               | PLL Lo BW | 00          | 00          |

| M               | Bypass    | 01          | 01          |

| 1               | PLL Hi BW | 11          | 11          |

# **Pin Descriptions**

| PIN# | PIN NAME                               | PIN TYPE      | DESCRIPTION                                                                                                                                                         |

|------|----------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                        |               |                                                                                                                                                                     |

| 1    | vSADR_tri                              | LATCHED<br>IN | Tri-level latch to select SMBus Address. See SMBus Address Selection Table.                                                                                         |

| 2    | ^vHIBW BYPM LOBW#                      |               | Trilevel input to select High BW, Bypass or Low BW mode.                                                                                                            |

|      | ************************************** | IN            | See PLL Operating Mode Table for Details.                                                                                                                           |

| 3    | FB_DNC                                 | DNC           | True clock of differential feedback. The feedback output and feedback input are connected                                                                           |

|      | -                                      |               | internally on this pin. Do not connect anything to this pin.                                                                                                        |

| 4    | FB_DNC#                                | DNC           | Complement clock of differential feedback. The feedback output and feedback input are                                                                               |

|      |                                        |               | connected internally on this pin. Do not connect anything to this pin.  1.8V power for differential input clock (receiver). This VDD should be treated as an Analog |

| 5    | VDDR1.8                                | PWR           | power rail and filtered appropriately.                                                                                                                              |

| 6    | CLK IN                                 | IN            | True Input for differential reference clock.                                                                                                                        |

| 7    | CLK IN#                                | IN            | Complementary Input for differential reference clock.                                                                                                               |

| 8    | GNDDIG                                 | GND           | Ground pin for digital circuitry                                                                                                                                    |

| 9    | SCLK 3.3                               | IN            | Clock pin of SMBus circuitry, 3.3V tolerant.                                                                                                                        |

|      | SDATA 3.3                              | I/O           | Data pin for SMBus circuitry, 3.3V tolerant.                                                                                                                        |

|      | VDDDIG1.8                              | PWR           | 1.8V digital power (dirty power)                                                                                                                                    |

|      | VDDIO                                  | PWR           | Power supply for differential outputs                                                                                                                               |

|      |                                        |               | Active low input for enabling DIF pair 0. This pin has an internal pull-down.                                                                                       |

| 13   | vOE0#                                  | IN            | 1 =disable outputs, 0 = enable outputs                                                                                                                              |

| 14   | DIF0                                   | OUT           | Differential true clock output                                                                                                                                      |

|      | DIF0#                                  | OUT           | Differential Complementary clock output                                                                                                                             |

|      | VDD1.8                                 | PWR           | Power supply, nominal 1.8V                                                                                                                                          |

| 17   | VDDIO                                  | PWR           | Power supply for differential outputs                                                                                                                               |

|      | DIF1                                   | OUT           | Differential true clock output                                                                                                                                      |

|      | DIF1#                                  | OUT           | Differential Complementary clock output                                                                                                                             |

|      | NC NC                                  | N/A           | No Connection.                                                                                                                                                      |

|      |                                        |               | Active low input for enabling DIF pair 1. This pin has an internal pull-down.                                                                                       |

| 21   | vOE1#                                  | IN            | 1 =disable outputs, 0 = enable outputs                                                                                                                              |

| 22   | DIF2                                   | OUT           | Differential true clock output                                                                                                                                      |

| _    | DIF2#                                  | OUT           | Differential Complementary clock output                                                                                                                             |

|      |                                        |               | Active low input for enabling DIF pair 2. This pin has an internal pull-down.                                                                                       |

| 24   | vOE2#                                  | IN            | 1 =disable outputs, 0 = enable outputs                                                                                                                              |

| 25   | VDDA1.8                                | PWR           | 1.8V power for the PLL core.                                                                                                                                        |

| 26   | VDDIO                                  | PWR           | Power supply for differential outputs                                                                                                                               |

|      | DIF3                                   | OUT           | Differential true clock output                                                                                                                                      |

|      | DIF3#                                  | OUT           | Differential Complementary clock output                                                                                                                             |

|      |                                        |               | Active low input for enabling DIF pair 3. This pin has an internal pull-down.                                                                                       |

| 29   | vOE3#                                  | IN            | 1 =disable outputs, 0 = enable outputs                                                                                                                              |

| 30   | NC                                     | N/A           | No Connection.                                                                                                                                                      |

| 31   | VDD1.8                                 | PWR           | Power supply, nominal 1.8V                                                                                                                                          |

| 32   | VDDIO                                  | PWR           | Power supply for differential outputs                                                                                                                               |

| 33   | DIF4                                   | OUT           | Differential true clock output                                                                                                                                      |

| 34   | DIF4#                                  | OUT           | Differential Complementary clock output                                                                                                                             |

|      |                                        |               | Active low input for enabling DIF pair 4. This pin has an internal pull-down.                                                                                       |

| 35   | vOE4#                                  | IN            | 1 =disable outputs, 0 = enable outputs                                                                                                                              |

| 36   | DIF5                                   | OUT           | Differential true clock output                                                                                                                                      |

| 37   | DIF5#                                  | OUT           | Differential Complementary clock output                                                                                                                             |

| 20   | VOE5#                                  | INI           | Active low input for enabling DIF pair 5. This pin has an internal pull-down.                                                                                       |

| 38   | vOE5#                                  | IN            | 1 =disable outputs, 0 = enable outputs                                                                                                                              |

| 39   | VDDIO                                  | PWR           | Power supply for differential outputs                                                                                                                               |

|      |                                        |               | Input notifies device to sample latched inputs and start up on first high assertion. Low enters                                                                     |

| 40   | ^CKPWRGD_PD#                           | IN            | Power Down Mode, subsequent high assertions exit Power Down Mode. This pin has internal                                                                             |

|      |                                        |               | pull-up resistor.                                                                                                                                                   |

| 41   | ePAD                                   | GND           | Connect paddle to ground.                                                                                                                                           |

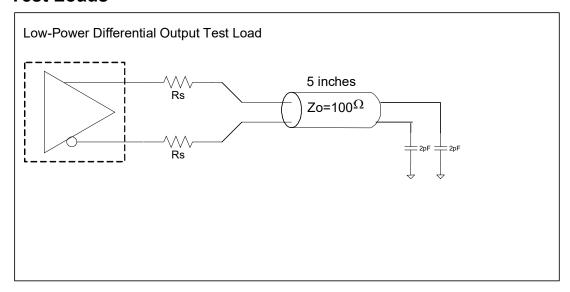

## **Test Loads**

## **Alternate Terminations**

The 9DBV family can easily drive LVPECL, LVDS, and CML logic. See "AN-891 Driving LVPECL, LVDS, and CML Logic with "Universal" Low-Power HCSL Outputs" for details.

## **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 9DBV0631. These ratings, which are standard values for Renesas commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| PARAMETER                 | SYMBOL             | CONDITIONS                | MIN  | TYP | MAX                  | UNITS | NOTES |

|---------------------------|--------------------|---------------------------|------|-----|----------------------|-------|-------|

| Supply Voltage            | VDDx               |                           | -0.5 |     | 2.5                  | V     | 1,2   |

| Input Voltage             | $V_{IN}$           |                           | -0.5 |     | V <sub>DD</sub> +0.5 | V     | 1,3   |

| Input High Voltage, SMBus | V <sub>IHSMB</sub> | SMBus clock and data pins |      |     | 3.6                  | V     | 1     |

| Storage Temperature       | Ts                 |                           | -65  |     | 150                  | °C    | 1     |

| Junction Temperature      | Tj                 |                           |      |     | 125                  | °C    | 1     |

| Input ESD protection      | ESD prot           | Human Body Model          | 2000 |     |                      | V     | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

## **Electrical Characteristics-Clock Input Parameters**

TA = T<sub>AMB</sub>; Supply Voltage per VDD, VDDIO of normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER                             | SYMBOL             | CONDITIONS                                                    | MIN                   | TYP | MAX  | UNITS | NOTES |

|---------------------------------------|--------------------|---------------------------------------------------------------|-----------------------|-----|------|-------|-------|

| Input High Voltage - DIF_IN           | V <sub>IHDIF</sub> | Differential inputs (single-ended measurement)                | 300                   | 750 | 1150 | mV    | 1     |

| Input Low Voltage - DIF_IN            | V <sub>ILDIF</sub> | Differential inputs (single-ended measurement)                | V <sub>SS</sub> - 300 | 0   | 300  | mV    | 1     |

| Input Common Mode<br>Voltage - DIF_IN | V <sub>COM</sub>   | Common Mode Input Voltage                                     | 200                   |     | 725  | mV    | 1     |

| Input Amplitude - DIF_IN              | $V_{SWING}$        | Peak to Peak value (V <sub>IHDIF</sub> - V <sub>ILDIF</sub> ) | 300                   |     | 1450 | mV    | 1     |

| Input Slew Rate - DIF_IN              | dv/dt              | Measured differentially                                       | 0.35                  |     | 8    | V/ns  | 1,2   |

| Input Leakage Current                 | I <sub>IN</sub>    | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                            | -5                    |     | 5    | uA    |       |

| Input Duty Cycle                      | $d_{tin}$          | Measurement from differential waveform                        | 45                    |     | 55   | %     | 1     |

| Input Jitter - Cycle to Cycle         | $J_{DIFIn}$        | Differential Measurement                                      | 0                     |     | 150  | ps    | 1     |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

<sup>&</sup>lt;sup>3</sup> Not to exceed 2.5V.

<sup>&</sup>lt;sup>2</sup> Slew rate measured through +/-75mV window centered around differential zero.

# **Electrical Characteristics-Input/Supply/Common Parameters-Normal Operating Conditions**

TA = T<sub>AMB</sub>, Voltage per VDD, VDDIO of normal operation conditions. See Test Loads for Loading Conditions.

| AIVID, TOILE. 90 POL TOO                  | ,                      |                                                                                                                                     | ng containe          |                                                  |                      |        |       |

|-------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------|----------------------|--------|-------|

| PARAMETER                                 | SYMBOL                 | CONDITIONS                                                                                                                          | MIN                  | TYP                                              | MAX                  |        | NOTES |

| Supply Voltage                            | VDDx                   | Supply voltage for core and analog                                                                                                  | 1.7                  | 1.8                                              | 1.9                  | V      |       |

| Output Supply Voltage                     | VDDIO                  | Supply voltage for Low Power HCSL Outputs                                                                                           | 0.95                 | 1.05-1.8                                         | 1.9                  | V      |       |

| Ambient Operating                         | T <sub>AMB</sub>       | Commercial range                                                                                                                    | 0                    | 25                                               | 70                   | °C     | 1     |

| Temperature                               |                        | Industrial range                                                                                                                    | -40                  | 25                                               | 85                   | °C     | 1     |

| Input High Voltage                        | V <sub>IH</sub>        | Single-ended inputs, except SMBus                                                                                                   | 0.75 V <sub>DD</sub> |                                                  | $V_{DD} + 0.3$       | V      |       |

| Input Mid Voltage                         | $V_{IM}$               | Single-ended tri-level inputs ('_tri' suffix)                                                                                       | $0.4 V_{DD}$         |                                                  | 0.6 V <sub>DD</sub>  | V      |       |

| Input Low Voltage                         | $V_{IL}$               | Single-ended inputs, except SMBus                                                                                                   | -0.3                 |                                                  | 0.25 V <sub>DD</sub> | V      |       |

|                                           | I <sub>IN</sub>        | Single-ended inputs, $V_{IN}$ = GND, $V_{IN}$ = VDD                                                                                 | -5                   |                                                  | 5                    | uA     |       |

| Input Current                             | I <sub>INP</sub>       | Single-ended inputs $V_{IN}$ = 0 V; Inputs with internal pull-up resistors $V_{IN}$ = VDD; Inputs with internal pull-down resistors | -200                 |                                                  | 200                  | uA     |       |

|                                           | $F_{ibyp}$             | Bypass mode                                                                                                                         | 1                    |                                                  | 200                  | MHz    | 2     |

| Innut Fraguency                           | F <sub>ipll</sub>      | 100MHz PLL mode                                                                                                                     | 50                   | 100.00                                           | 140                  | MHz    | 2     |

| Input Frequency                           | F <sub>ipll</sub>      | 125MHz PLL mode                                                                                                                     | 62.5                 | 125.00                                           | 175                  | MHz    | 2     |

|                                           | F <sub>ipll</sub>      | 50MHz PLL mode                                                                                                                      | 25                   | 50.00                                            | 65                   | MHz    | 2     |

| Pin Inductance                            | L <sub>pin</sub>       |                                                                                                                                     |                      |                                                  | 7                    | nH     | 1     |

|                                           | C <sub>IN</sub>        | Logic Inputs, except DIF_IN                                                                                                         | 1.5                  |                                                  | 5                    | pF     | 1     |

| Capacitance                               | C <sub>INDIF_IN</sub>  | DIF_IN differential clock inputs                                                                                                    | 1.5                  |                                                  | 2.7                  | pF     | 1,6   |

|                                           | C <sub>OUT</sub>       | Output pin capacitance                                                                                                              |                      |                                                  | 6                    | pF     | 1     |

| Clk Stabilization                         | T <sub>STAB</sub>      | From V <sub>DD</sub> Power-Up and after input clock stabilization or de-assertion of PD# to 1st clock                               |                      |                                                  | 1                    | ms     | 1,2   |

| Input SS Modulation<br>Frequency PCle     | f <sub>MODINPCle</sub> | Allowable Frequency for PCle Applications (Triangular Modulation)                                                                   | 30                   |                                                  | 33                   | kHz    |       |

| Input SS Modulation<br>Frequency non-PCle | f <sub>MODIN</sub>     | Allowable Frequency for non-PCle Applications (Triangular Modulation)                                                               | 0                    |                                                  | 66                   | kHz    |       |

| OE# Latency                               | t <sub>LATOE</sub> #   | DIF start after OE# assertion DIF stop after OE# deassertion                                                                        | 1                    |                                                  | 3                    | clocks | 1,3   |

| Tdrive_PD#                                | t <sub>DRVPD</sub>     | DIF output enable after PD# de-assertion                                                                                            |                      |                                                  | 300                  | us     | 1,3   |

| Tfall                                     | t <sub>F</sub>         | Fall time of single-ended control inputs                                                                                            |                      |                                                  | 5                    | ns     | 2     |

| Trise                                     | t <sub>R</sub>         | Rise time of single-ended control inputs                                                                                            |                      |                                                  | 5                    | ns     | 2     |

| SMBus Input Low Voltage                   | V <sub>ILSMB</sub>     | $V_{\rm DDSMB}$ = 3.3V, see note 4 for $V_{\rm DDSMB}$ < 3.3V                                                                       |                      |                                                  | 0.8                  | V      | 4     |

| SMBus Input High Voltage                  | V <sub>IHSMB</sub>     | $V_{\rm DDSMB}$ = 3.3V, see note 5 for $V_{\rm DDSMB}$ < 3.3V                                                                       | 2.1                  |                                                  | 3.6                  | V      | 5     |

| SMBus Output Low Voltage                  |                        | @ I <sub>PULLUP</sub>                                                                                                               |                      |                                                  | 0.4                  | V      |       |

| SMBus Sink Current                        | I <sub>PULLUP</sub>    | @ V <sub>OL</sub>                                                                                                                   | 4                    |                                                  |                      | mA     |       |

| Nominal Bus Voltage                       | V <sub>DDSMB</sub>     | Bus Voltage                                                                                                                         | 1.7                  |                                                  | 3.6                  | V      |       |

| SCLK/SDATA Rise Time                      | t <sub>RSMB</sub>      | (Max VIL - 0.15) to (Min VIH + 0.15)                                                                                                |                      |                                                  | 1000                 | ns     | 1     |

|                                           | LYOND                  | , , ,                                                                                                                               |                      | <del>                                     </del> | 300                  | ns     | 1     |

| SCLK/SDATA Fall Time                      | t <sub>FSMB</sub>      | (Min VIH + 0.15) to (Max VIL - 0.15)                                                                                                |                      |                                                  | 500                  |        |       |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>Control input must be monotonic from 20% to 80% of input swing.

<sup>&</sup>lt;sup>3</sup> Time from deassertion until outputs are >200 mV.

$<sup>^{4}</sup>$  For  $V_{DDSMB}$  < 3.3V,  $V_{ILSMB}$  <=  $0.35V_{DDSMB}$ .

$<sup>^{5}</sup>$  For  $V_{DDSMB}$  < 3.3V,  $V_{IHSMB}$  >= 0.65 $V_{DDSMB}$ .

<sup>&</sup>lt;sup>6</sup> DIF\_IN input.

<sup>&</sup>lt;sup>7</sup> The differential input clock must be running for the SMBus to be active.

## **Electrical Characteristics-Low-Power HCSL Outputs**

TA = T<sub>AMB</sub>; Supply Voltage per VDD, VDDIO of normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER              | SYMBOL            | CONDITIONS                                                                              | MIN  | TYP  | MAX  | UNITS | NOTES |

|------------------------|-------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|-------|

| Slew rate              | dV/dt             | Scope averaging on, fast setting                                                        | 1.7  | 2.9  | 4    | V/ns  | 1,2,3 |

| Siew rate              | dV/dt             | Scope averaging on, slow setting                                                        | 1.1  | 2.1  | 3.4  | V/ns  | 1,2,3 |

| Slew rate matching     | □dV/dt            | Slew rate matching, Scope averaging on                                                  |      | 7    | 20   | %     | 1,2,4 |

| Voltage High           | V <sub>HIGH</sub> | Statistical measurement on single-ended signal using oscilloscope math function. (Scope | 660  | 774  | 850  | mV    | 7     |

| Voltage Low            | $V_{LOW}$         | averaging on)                                                                           | -150 | 18   | 150  | IIIV  | 7     |

| Max Voltage            | Vmax              | Measurement on single ended signal using                                                |      | 821  | 1150 | mV    | 7     |

| Min Voltage            | Vmin              | absolute value. (Scope averaging off)                                                   | -300 | -15  |      | IIIV  | 7     |

| Vswing                 | Vswing            | Scope averaging off                                                                     | 300  | 1536 |      | mV    | 1,2   |

| Crossing Voltage (abs) | Vcross_abs        | Scope averaging off                                                                     | 250  | 414  | 550  | mV    | 1,5   |

| Crossing Voltage (var) | Δ-Vcross          | Scope averaging off                                                                     |      | 13   | 140  | mV    | 1,6   |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

# **Electrical Characteristics-Current Consumption**

TA = T<sub>AMB</sub>; Supply Voltage per VDD, VDDIO of normal operation conditions, See Test Loads for Loading Conditions

| AND, 113 O I             |                    | ,                                 |     | 0      |     |       |       |

|--------------------------|--------------------|-----------------------------------|-----|--------|-----|-------|-------|

| PARAMETER                | SYMBOL             | CONDITIONS                        | MIN | TYP    | MAX | UNITS | NOTES |

| Operating Supply Current | I <sub>DDA</sub>   | VDDA+VDDR, PLL Mode, @100MHz      |     | 11     | 15  | mA    | 1     |

|                          | I <sub>DD</sub>    | VDD, All outputs active @100MHz   |     | 6      | 10  | mA    | 1     |

|                          | I <sub>DDO</sub>   | VDDIO, All outputs active @100MHz |     | 24     | 30  | mA    | 1     |

| Powerdown Current        | I <sub>DDAPD</sub> | VDDA+VDDR, CKPWRGD_PD#=0          |     | 0.4    | 0.6 | mA    | 1, 2  |

|                          | I <sub>DDPD</sub>  | VDD, CKPWRGD_PD#=0                |     | 0.5    | 0.8 | mA    | 1, 2  |

|                          | I <sub>DDOPD</sub> | VDDIO, CKPWRGD_PD#=0              |     | 0.0003 | 0.1 | mA    | 1, 2  |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform

<sup>&</sup>lt;sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

<sup>&</sup>lt;sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>&</sup>lt;sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>&</sup>lt;sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

<sup>&</sup>lt;sup>7</sup> At default SMBus settings.

<sup>&</sup>lt;sup>2</sup> Input clock stopped.

## Electrical Characteristics-Output Duty Cycle, Jitter, Skew and PLL Characteristics

TA = T<sub>AMB</sub>; Supply Voltage per VDD, VDDIO of normal operation conditions, See Test Loads for Loading Conditions

| AIVID, 117 3 1         | ,                     | 2.0 0                                        |      | J -  |      |       |       |

|------------------------|-----------------------|----------------------------------------------|------|------|------|-------|-------|

| PARAMETER              | SYMBOL                | CONDITIONS                                   | MIN  | TYP  | MAX  | UNITS | NOTES |

| PLL Bandwidth          | BW                    | -3dB point in High BW Mode                   | 1.8  | 2.7  | 3.8  | MHz   | 1,5   |

| PLL Bandwidth          | DVV                   | -3dB point in Low BW Mode                    | 0.8  | 1.4  | 2    | MHz   | 1,5   |

| PLL Jitter Peaking     | t <sub>JPEAK</sub>    | Peak Pass band Gain                          |      | 1.1  | 2    | dB    | 1     |

| Duty Cycle             | t <sub>DC</sub>       | Measured differentially, PLL Mode            | 45   | 50.1 | 55   | %     | 1     |

| Duty Cycle Distortion  | t <sub>DCD</sub>      | Measured differentially, Bypass Mode @100MHz | -1   | 0.0  | 1    | %     | 1,3   |

| Skow Input to Output   | t <sub>pdBYP</sub>    | Bypass Mode, V <sub>T</sub> = 50%            | 3000 | 3636 | 4500 | ps    | 1     |

| Skew, Input to Output  | t <sub>pdPLL</sub>    | PLL Mode V <sub>T</sub> = 50%                | 0    | 81   | 200  | ps    | 1,4   |

| Skew, Output to Output | t <sub>sk3</sub>      | V <sub>T</sub> = 50%                         |      | 26   | 50   | ps    | 1,4   |

| Jitter, Cycle to cycle | t.                    | PLL mode                                     |      | 13   | 50   | ps    | 1,2   |

| Sitter, Cycle to Cycle | t <sub>jcyc-cyc</sub> | Additive Jitter in Bypass Mode               |      | 0.1  | 5    | ps    | 1,2   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

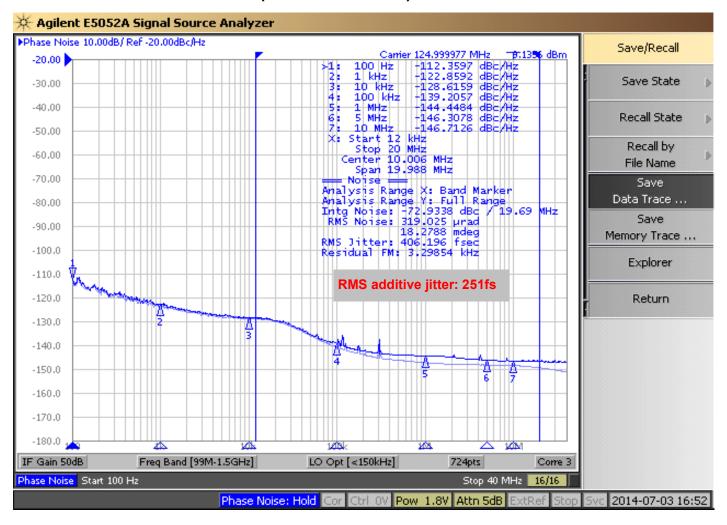

### Electrical Characteristics-Phase Jitter Parameters - 12kHz to 20MHz

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions. See Test Loads for loading conditions.

| Parameter                                                    | Symbol         | Conditions                                 | Minimum | Typical | Maximum | Specification<br>Limit | Units       | Notes   |

|--------------------------------------------------------------|----------------|--------------------------------------------|---------|---------|---------|------------------------|-------------|---------|

| 12k-20M <i>Additive</i> Phase Jitter,<br>Fan-out Buffer Mode | tjph12k-20MFOB | Fan-out Buffer Mode,<br>SSC OFF, 156.25MHz |         | 156     |         | n/a                    | fs<br>(rms) | 1, 2, 3 |

#### Notes:

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform

<sup>&</sup>lt;sup>3</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

<sup>&</sup>lt;sup>4</sup> All outputs at default slew rate

<sup>&</sup>lt;sup>5</sup> The MIN/TYP/MAX values of each BW setting track each other, i.e., Low BW MAX will never occur with Hi BW MIN.

<sup>1.</sup> Applies to all differential outputs, guaranteed by design and characterization. See Test Loads for measurement setup details.

<sup>2. 12</sup>kHz to 20MHz brick wall filter.

<sup>3.</sup> For RMS values additive jitter is calculated by solving for b where  $[b = sqrt(c^2 - a^2)]$ , a is rms input jitter and c is rms total jitter.

# Electrical Characteristics-Additive PCle Phase Jitter for Fanout Buffer Mode<sup>[7]</sup>

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions. See Test Loads for loading conditions.

| Parameter                                          | Symbol                    | Conditions                    | Minimum | Typical | Maximum | Limit | Units       | Notes      |

|----------------------------------------------------|---------------------------|-------------------------------|---------|---------|---------|-------|-------------|------------|

|                                                    | tjphPCleG1-CC             | PCIe Gen 1 (2.5 GT/s)         |         | 1.7     | 3.0     | 86    | ps<br>(p-p) | 1, 2       |

|                                                    | t                         | PCle Gen 2 Hi Band (5.0 GT/s) |         | 0.033   | 0.049   | 3     | ps<br>(RMS) | 1, 2       |

| Additive PCIe Phase Jitter,<br>Fan-out Buffer Mode | <sup>t</sup> jphPCleG2-CC | PCle Gen 2 Lo Band (5.0 GT/s) |         | 0.122   | 0.199   | 3.1   | ps<br>(RMS) | 1, 2       |

| (Common Clocked Architecture)                      | tjphPCleG3-CC             | PCIe Gen 3 (8.0 GT/s)         |         | 0.059   | 0.098   | 1     | ps<br>(RMS) | 1, 2       |

|                                                    | tjphPCleG4-CC             | PCIe Gen 4 (16.0 GT/s)        |         | 0.059   | 0.098   | 0.5   | ps<br>(RMS) | 1, 2, 3, 4 |

|                                                    | tjphPCleG5-CC             | PCle Gen 5 (32.0 GT/s)        |         | 0.023   | 0.038   | 0.15  | ps<br>(RMS) | 1, 2, 3, 5 |

|                                                    | tjphPCleG1-SRIS           | PCIe Gen 1 (2.5 GT/s)         |         | 0.175   | 0.038   | n/a   | ps<br>(RMS) | 1, 2, 6    |

| Additive PCIe Phase Jitter,                        | tjphPCleG2-SRIS           | PCIe Gen 2 (5.0 GT/s)         |         | 0.156   | 0.275   | n/a   | ps<br>(RMS) | 1, 2, 6    |

| Fan-out Buffer Mode (SRIS Architecture)            | tphPCleG3-SRIS            | PCIe Gen 3 (8.0 GT/s)         |         | 0.041   | 0.247   | n/a   | ps<br>(RMS) | 1, 2, 6    |

| (SINS AIGIIEGUIE)                                  | tphPCleG4-SRIS            | PCIe Gen 4 (16.0 GT/s)        |         | 0.043   | 0.064   | n/a   | ps<br>(RMS) | 1, 2, 6    |

|                                                    | phPCleG5-SRIS             | PCIe Gen 5 (32.0 GT/s)        |         | 0.036   | 0.066   | n/a   | ps<br>(RMS) | 1, 2, 6    |

#### Notes:

- 1. The Refclk jitter is measured after applying the filter functions found in PCI Express Base Specification 5.0, Revision 1.0. See the Test Loads section of the data sheet for the exact measurement setup. The total Ref Clk jitter limits for each data rate are listed for convenience. The worst case results for each data rate are summarized in this table. If oscilloscope data is used, equipment noise is removed from all results.

- 2. Jitter measurements shall be made with a capture of at least 100,000 clock cycles captured by a real-time oscilloscope (RTO) with a sample rate of 20 GS/s or greater. Broadband oscilloscope noise must be minimized in the measurement. The measured PP jitter is used (no extrapolation) for RTO measurements. Alternately Jitter measurements may be used with a Phase Noise Analyzer (PNA) extending (flat) and integrating and folding the frequency content up to an offset from the carrier frequency of at least 200 M Hz (at 300 M Hz absolute frequency) below the Nyquist frequency. For PNA measurements for the 2.5 GT/s data rate, the RMS jitter is converted to peak to peak jitter using a multiplication factor of 8.83. In the case where real-time oscilloscope and PNA measurements have both been done and produce different results the RTO result must be used.

- 3. SSC spurs from the fundamental and harmonics are removed up to a cutoff frequency of 2 MHz taking care to minimize removal of any non-SSC content.

- 4. Note that 0.7 ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 5. Note that 0.25 ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 6. The PCI Express Base Specification 5.0, Revision 1.0 provides the filters necessary to calculate SRIS jitter values, however, it does not provide specification limits, hence the n/a in the Limit column. SRIS values are informative only. In general, a clock operating in an SRIS system must be twice as good as a clock operating in a Common Clock system. For RMS values, twice as good is equivalent to dividing the CC value by  $\sqrt{2}$ . And additional consideration is the value for which to divide by  $\sqrt{2}$ . The conservative approach is to divide the ref clock jitter limit, and the case can be made for dividing the channel simulation values by  $\sqrt{2}$ , if the ref clock is close to the Tx clock input. An example for Gen4 is as follows. A "rule-of-thumb" SRIS limit would be either 0.5ps RMS/ $\sqrt{2}$  = 0.35ps RMS if the clock chip is far from the clock input, or 0.7ps RMS/ $\sqrt{2}$  = 0.5ps RMS if the clock chip is near the clock input.

- 7. Additive jitter for RMS values is calculated by solving for b where  $b = \sqrt{(c^2 a^2)}$ , and a is rms input jitter and c is rms output jitter.

## Additive Phase Jitter: 125M (12kHz to 20MHz)

#### **General SMBus Serial Interface Information**

#### **How to Write**

- · Controller (host) sends a start bit

- Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- Controller (host) sends the byte count = X

- Renesas clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- Renesas clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

| Index Blo    | ck Write C | Opera  | ation                    |

|--------------|------------|--------|--------------------------|

| Controller ( | Host)      |        | Renesas (Slave/Receiver) |

| T            | starT bit  |        |                          |

| Slave Addre  | ess        |        |                          |

| WR           | WRite      |        |                          |

|              |            |        | ACK                      |

| Beginning E  | Byte = N   |        |                          |

|              |            |        | ACK                      |

| Data Byte 0  | Count = X  |        |                          |

|              |            |        | ACK                      |

| Beginning E  | Byte N     | ×      |                          |

|              |            | X Byte | ACK                      |

| 0            |            |        |                          |

| 0            |            |        | 0                        |

| 0            |            |        | 0                        |

|              |            |        | 0                        |

| Byte N + X   | - 1        |        |                          |

|              |            |        | ACK                      |

| Р            | stoP bit   |        |                          |

Note: Read/Write address is latched on SADR pin.

#### How to Read

- Controller (host) will send a start bit

- Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- · Controller (host) will send a separate start bit

- Controller (host) sends the read address

- Renesas clock will acknowledge

- Renesas clock will send the data byte count = X

- Renesas clock sends Byte N+X-1

- Renesas clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- · Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

| Index B   | lock Read Operat | tion   |                   |

|-----------|------------------|--------|-------------------|

| Controlle | r (Host)         |        | Renesas           |

| Т         | starT bit        |        |                   |

| Slave Ad  | dress            |        |                   |

| WR        | WRite            |        |                   |

|           |                  |        | ACK               |

| Beginning | g Byte = N       |        |                   |

|           |                  |        | ACK               |

| RT        | Repeat starT     |        |                   |

| Slave Ad  | dress            |        |                   |

| RD        | ReaD             |        |                   |

|           |                  |        | ACK               |

|           |                  |        |                   |

|           |                  |        | Data Byte Count=X |

| ACK       |                  |        |                   |

|           |                  |        | Beginning Byte N  |

| ACK       |                  |        |                   |

|           |                  |        | 0                 |

| 0         |                  |        | 0                 |

| 0         | 0                |        | 0                 |

| 0         |                  | X Byte |                   |

|           | T                | ×      | Byte N + X - 1    |

| N         | Not acknowledge  |        |                   |

| Р         | stoP bit         |        |                   |

SMBus Table: Output Enable Register <sup>1</sup>

| Byte 0 | Name     | Control Function |    | 0       | 1       | Default |

|--------|----------|------------------|----|---------|---------|---------|

| Bit 7  | DIF OE5  | Output Enable    | RW | Low/Low | Enabled | 1       |

| Bit 6  | DIF OE4  | Output Enable    | RW | Low/Low | Enabled | 1       |

| Bit 5  | Reserved |                  |    |         |         |         |

| Bit 4  | DIF OE3  | Output Enable    | RW | Low/Low | Enabled | 1       |

| Bit 3  | DIF OE2  | Output Enable    | RW | Low/Low | Enabled | 1       |

| Bit 2  | DIF OE1  | Output Enable    | RW | Low/Low | Enabled | 1       |

| Bit 1  | Reserved |                  |    |         |         |         |

| Bit 0  | DIF OE0  | Output Enable    | RW | Low/Low | Enabled | 1       |

<sup>1.</sup> A low on these bits will override the OE# pin and force the differential output Low/Low

SMBus Table: PLL Operating Mode and Output Amplitude Control Register

| Byte 1 | Name             | Control Function          | Туре            | 0                 | 1                 | Default |

|--------|------------------|---------------------------|-----------------|-------------------|-------------------|---------|

| Bit 7  | PLLMODERB1       | PLL Mode Readback Bit 1   | R               | See PLL Operat    | Latch             |         |

| Bit 6  | PLLMODERB0       | PLL Mode Readback Bit 0   | R               | See Fill Operat   | ing wode rable    | Latch   |

| Bit 5  | PLLMODE SWCNTRL  | Enable SW control of PLL  | RW              | Values in B1[7:6] | Values in B1[4:3] | 0       |

| DIL 3  | FEEMODE_SWCITTLE | Mode:                     | 1700            | set PLL Mode      | set PLL Mode      | U       |

| Bit 4  | PLLMODE1         | PLL Mode Control Bit 1    | RW <sup>1</sup> | See PLL Operat    | ing Mode Table    | 0       |

| Bit 3  | PLLMODE0         | PLL Mode Control Bit 0    | RW <sup>1</sup> | See FLL Opera     | ing wode rable    | 0       |

| Bit 2  |                  | Reserved                  |                 |                   |                   | 1       |

| Bit 1  | AMPLITUDE 1      | Controls Output Amplitude | RW              | 00 = 0.6V         | 01 = 0.7V         | 1       |

| Bit 0  | AMPLITUDE 0      | Controls Output Amplitude | RW              | 10= 0.8V          | 11 = 0.9V         | 0       |

<sup>1.</sup> B1[5] must be set to a 1 for these bits to have any effect on the part.

#### SMBus Table: DIF Slew Rate Control Register

| empas rabior pir sion rate solitor region. |                  |                          |          |              |                     |   |  |  |  |

|--------------------------------------------|------------------|--------------------------|----------|--------------|---------------------|---|--|--|--|

| Byte 2                                     | Name             | Control Function         | Type 0 1 |              | Default             |   |  |  |  |

| Bit 7                                      | SLEWRATESEL DIF5 | Adjust Slew Rate of DIF5 | RW       | Slow setting | etting Fast setting |   |  |  |  |

| Bit 6                                      | SLEWRATESEL DIF4 | Adjust Slew Rate of DIF4 | RW       | Slow setting | Fast setting        | 1 |  |  |  |

| Bit 5                                      |                  | Reserved                 |          |              |                     |   |  |  |  |

| Bit 4                                      | SLEWRATESEL DIF3 | Adjust Slew Rate of DIF3 | RW       | Slow setting | Fast setting        | 1 |  |  |  |

| Bit 3                                      | SLEWRATESEL DIF2 | Adjust Slew Rate of DIF2 | RW       | Slow setting | Fast setting        | 1 |  |  |  |

| Bit 2                                      | SLEWRATESEL DIF1 | Adjust Slew Rate of DIF1 | RW       | Slow setting | Fast setting        | 1 |  |  |  |

| Bit 1                                      | Reserved         |                          |          |              |                     | 1 |  |  |  |

| Bit 0                                      | SLEWRATESEL DIF0 | Adjust Slew Rate of DIF0 | RW       | Slow setting | Fast setting        | 1 |  |  |  |

### SMBus Table: Frequency Select Control Register

| Byte 3 | Name           | Control Function                                    | Туре            | 0                            | 1                           | Default |

|--------|----------------|-----------------------------------------------------|-----------------|------------------------------|-----------------------------|---------|

| Bit 7  | Reserved       |                                                     |                 |                              |                             |         |

| Bit 6  | Reserved       |                                                     |                 |                              |                             | 1       |

| Bit 5  | FREQ_SEL_EN    | I RVV I                                             |                 | SW frequency change disabled | SW frequency change enabled | 0       |

| Bit 4  | FSEL1          | Freq. Select Bit 1                                  | RW <sup>1</sup> | See Frequency                | 0                           |         |

| Bit 3  | FSEL0          | Freq. Select Bit 0                                  | RW <sup>1</sup> | See Frequenc                 | y Select Table              | 0       |

| Bit 2  |                | Reserved                                            |                 |                              |                             | 1       |

| Bit 1  | Reserved       |                                                     |                 |                              |                             | 1       |

| Bit 0  | SLEWRATESEL FB | Adjust Slew Rate of FB RW Slow setting Fast setting |                 | 1                            |                             |         |

<sup>1.</sup> B3[5] must be set to a 1 for these bits to have any effect on the part.

#### Byte 4 is Reserved and reads back 'hFF

#### SMBus Table: Revision and Vendor ID Register

| Byte 5 | Name | Control Function | Type | 0          | 1            | Default |  |

|--------|------|------------------|------|------------|--------------|---------|--|

| Bit 7  | RID3 |                  | R    |            |              | 0       |  |

| Bit 6  | RID2 | Revision ID      | R    | Λ rov -    | 0            |         |  |

| Bit 5  | RID1 |                  | R    | A lev -    | A rev = 0000 |         |  |

| Bit 4  | RID0 |                  | R    |            | 0            |         |  |

| Bit 3  | VID3 |                  | R    |            |              | 0       |  |

| Bit 2  | VID2 | VENDOR ID        | R    | 0001       | 0001 = IDT   |         |  |

| Bit 1  | VID1 | VENDOR ID        | R    | 0001 – 101 |              | 0       |  |

| Bit 0  | VID0 |                  | R    |            | 1            |         |  |

SMBus Table: Device Type/Device ID

| Byte 6 | Name         | Control Function | Type | 0                         | 1            | Default |

|--------|--------------|------------------|------|---------------------------|--------------|---------|

| Bit 7  | Device Type1 | Device Type      | R    | <b>R</b> 00 = FG, 01 = DB |              | 0       |

| Bit 6  | Device Type0 | Device Type      | R    | 10 = DM, 11=              | 1            |         |

| Bit 5  | Device ID5   |                  | R    |                           |              | 0       |

| Bit 4  | Device ID4   |                  | R    |                           | 0            |         |

| Bit 3  | Device ID3   | Device ID        | R    | 000110 bina               | ny or 06 boy | 0       |

| Bit 2  | Device ID2   | Device ID        | R    | 000 FTO DITIA             | ry or oo nex | 1       |

| Bit 1  | Device ID1   |                  | R    |                           |              |         |

| Bit 0  | Device ID0   | 7                | R    |                           |              | 0       |

SMBus Table: Byte Count Register

| Byte 7 | Name     | Control Function       | Type | 0                      | 1                    | Default |  |

|--------|----------|------------------------|------|------------------------|----------------------|---------|--|

| Bit 7  | Reserved |                        |      |                        |                      |         |  |

| Bit 6  |          | Reserved               |      |                        |                      | 0       |  |

| Bit 5  |          | Reserved               |      |                        |                      | 0       |  |

| Bit 4  | BC4      |                        | RW   |                        |                      | 0       |  |

| Bit 3  | BC3      |                        |      | Writing to this regist |                      |         |  |

| Bit 2  | BC2      | Byte Count Programming | RW   | many bytes will be r   | ead back, default is | 0       |  |

| Bit 1  | BC1      |                        | RW   | = 8 b                  | ytes.                | 0       |  |

| Bit 0  | BC0      |                        | RW   |                        |                      | 0       |  |

## **Marking Diagrams**

#### Notes:

- 1. "LOT" is the lot sequence number.

- 2. "COO" denotes country of origin.

- 3. "YYWW" is the last two digits of the year and week that the part was assembled.

- 4. Line 2: truncated part number

- 5. "L" denotes RoHS compliant package.

- 6. "I" denotes industrial temperature range device.

#### **Thermal Characteristics**

| PARAMETER          | SYMBOL         | CONDITIONS                      | PKG   | TYP<br>VALUE | UNITS | NOTES |

|--------------------|----------------|---------------------------------|-------|--------------|-------|-------|

|                    | $\theta_{JC}$  | Junction to Case                |       | 42           | °C/W  | 1     |

|                    | $\theta_{Jb}$  | Junction to Base                | 2.4   |              | °C/W  | 1     |

| Thermal Resistance | $\theta_{JA0}$ | Junction to Air, still air      | NDG40 | 39           | °C/W  | 1     |

| mermai Resistance  | $\theta_{JA1}$ | Junction to Air, 1 m/s air flow | NDG40 | 33           | °C/W  | 1     |

|                    | $\theta_{JA3}$ | Junction to Air, 3 m/s air flow | 28    |              | °C/W  | 1     |

|                    | $\theta_{JA5}$ | Junction to Air, 5 m/s air flow |       | 27           | °C/W  | 1     |

<sup>&</sup>lt;sup>1</sup>ePad soldered to board

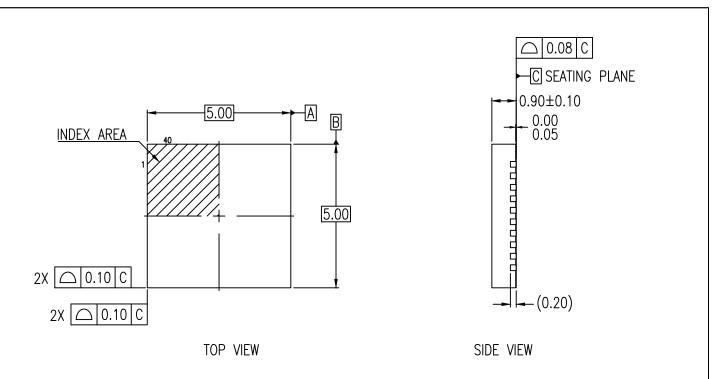

## **Package Outline Drawings**

The package outline drawings are located at the end of this document and are accessible from the Renesas website. The package information is the most current data available and is subject to change without revision of this document.

40-VFQFPN (NDG40P2)

## **Ordering Information**

| Part / Order Number | <b>Shipping Packaging</b> | Package       | Temperature   |

|---------------------|---------------------------|---------------|---------------|

| 9DBV0631BKLF        | Trays                     | 40-pin VFQFPN | 0 to +70° C   |

| 9DBV0631BKLFT       | Tape and Reel             | 40-pin VFQFPN | 0 to +70° C   |

| 9DBV0631BKILF       | Trays                     | 40-pin VFQFPN | -40 to +85° C |

| 9DBV0631BKILFT      | Tape and Reel             | 40-pin VFQFPN | -40 to +85° C |

<sup>&</sup>quot;LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

<sup>&</sup>quot;B" is the device revision designator (will not correlate with the datasheet revision).

# **Revision History**

| Revision Date      | Description                                                                     |  |  |

|--------------------|---------------------------------------------------------------------------------|--|--|

|                    | 1. Pinout changed from 48 to 40 pins. Paddle is now GND.                        |  |  |

|                    | 2. Thermal data added                                                           |  |  |

|                    | 3. General Description/Front Page Text updated to match other 9DBVxx31 devices. |  |  |

| September 5, 2012  | 4. SMBus updated.                                                               |  |  |

|                    | 5. Power Ground Connections updated.                                            |  |  |

|                    | 6. Electrical tables updated.                                                   |  |  |

|                    | 7. Move to preliminary.                                                         |  |  |

| September 17, 2012 | Changed ordering information from 9DBV0631A to 9DBV0631B                        |  |  |

|                    | 1. Changed VIH min. from 0.65*VDD to 0.75*VDD                                   |  |  |

| February 25, 2013  | 2. Changed VIL max. from 0.35*VDD to 0.25*VDD                                   |  |  |

|                    | 3. Added missing mid-level input voltage spec (VIM) of 0.4*VDD to 0.6*VDD.      |  |  |

| July 7, 2014       | Updated top-side device marking and associated notes.                           |  |  |

|                    | Updated front page text for consistency.                                        |  |  |

|                    | 2. Updated block diagram for consistency.                                       |  |  |

| September 10, 2014 | Updated electrical tables with characterization data.                           |  |  |

| Ocptomber 10, 2014 | 4. Updated SMBus nomenclature - bits did NOT change.                            |  |  |

|                    | 5. Converted to new doc template.                                               |  |  |

|                    | 6. Changed IDD spec from 8mA to 10mA MAX                                        |  |  |

| November 7, 2014   | Widened input frequency ranges for PLL modes.                                   |  |  |

|                    | Updated max frequency of 100MHz PLL mode to 140MHz                              |  |  |

| April 28, 2016     | 2. Updated max frequency of 125MHz PLL mode to 175MHz                           |  |  |

|                    | 3. Updated max frequency of 50MHz PLL mode to 65MHz                             |  |  |

| July 27, 2016      | Corrected ordering information typo by adding "T" for Tape and Reel devices.    |  |  |

|                    | Updated document title.                                                         |  |  |

|                    | 2. Updated Recommended Applications.                                            |  |  |

| August 2, 2021     | 3. Updated Key Specifications.                                                  |  |  |

|                    | 4. Updated Package Outline Drawings section.                                    |  |  |

|                    | 5. Updated Phase Jitter tables.                                                 |  |  |

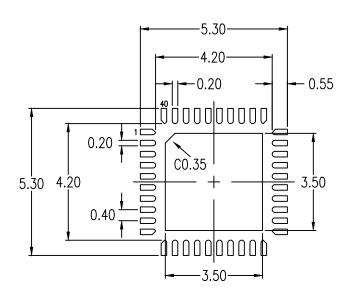

# 40-VFQFPN, Package Outline Drawing

5.00 x 5.00 x 0.90 mm Body, 3.50 x 3.50 mm Epad, 0.40mm Pitch NDG40P2, PSC-4292-02, Rev 01, Page 1

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5-2009

- 2. ALL DIMENSIONS ARE IN MILLIMETERS

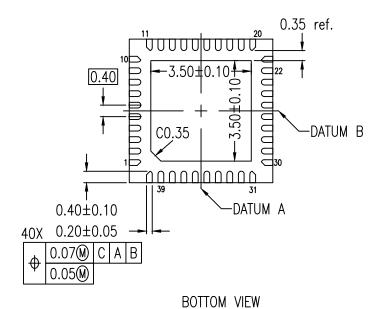

## 40-VFQFPN, Package Outline Drawing

5.00 x 5.00 x 0.90 mm Body, 3.50 x 3.50 mm Epad, 0.40mm Pitch NDG40P2, PSC-4292-02, Rev 01, Page 2

RECOMMENDED LAND PATTERN DIMENSION

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MM. ANGLES IN DEGREES

- 2. TOP DOWN VIEW. AS VIEWED ON PCB

- 3. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

- 4. NSMD PATTERN ASSUMED

| Package Revision History |         |                                      |  |

|--------------------------|---------|--------------------------------------|--|

| Date Created             | Rev No. | Description                          |  |

| Feb 25, 2021             | 01      | Update Template to Marketing Version |  |

| May 17, 2016             | 00      | Initial release                      |  |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Buffer category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

MPC962309EJ-1H NB4N121KMNG IDT49FCT805ASO MK2308S-1HILF PL133-27GI-R NB3L02FCT2G NB3L03FCT2G

ZL40203LDG1 ZL40200LDG1 ZL40205LDG1 9FG1200DF-1LF 9FG1001BGLF ZL40202LDG1 PI49FCT20802QE SL2305SC-1T

PI6C4931502-04LIE NB7L1008MNG NB7L14MN1G PI49FCT20807QE PI6C4931502-04LIEX ZL80002QAB1 PI6C4931504-04LIEX

PI6C10806BLEX ZL40226LDG1 ZL40219LDG1 8T73S208B-01NLGI SY75578LMG PI49FCT32805QEX PL133-27GC-R

MC10LVEP11DG MC10EP11DTG MC100LVEP11DG MC100E111FNG MC100EP11DTG NB6N11SMNG NB7L14MMNG

NB6L11MMNG NB6L14MMNR2G NB6L611MNG PL123-02NGI-R NB3N111KMNR4G ADCLK944BCPZ-R7 ZL40217LDG1

NB7LQ572MNG HMC940LC4BTR ADCLK946BCPZ-REEL7 ADCLK946BCPZ ADCLK846BCPZ-REEL7 ADCLK854BCPZ-REEL7

ADCLK905BCPZ-R2