# System Clock for Embedded AMD<sup>TM</sup> based Systems

•

#### **Recommended Application:**

AMD M690T/780E systems

#### **Output Features:**

- Integrated series resistors on all differential outputs.

- 1 Greyhound compatible low-power CPU pair

- 6 low-power differential SRC pairs

- 2 low-power differential chipset SouthBridge SRC pairs

- 1 Selectable low-power differential 100MHz non-spread SATA/ SRC output

- 1 Selectable low-power differential SRC / 27MHz Single Ended output

- 1 Selectable HT3 100MHz low-power differential hypertransport clock / HT66MHz Single Ended output

- 2 48MHz USB clock

- 3 14.318MHz Reference clock

- 3 low-power differential ATIG pairs

- 5- Dedicated CLKREQ# pins

#### Kev Specifications:

- CPU outputs cycle-to-cycle jitter < 150ps

- SRC outputs cycle-to-cycle jitter < 125ps

- SB\_SRC outputs cycle-to-cycle jitter < 125ps

- +/- 100ppm frequency accuracy on CPU, SRC, ATIG

- Oppm frequency accuracy on 48MHz

#### Features/Benefits:

- **Power Saving Features:** SB\_SRC\_SLOW# input to throttle Chipset clocks (SB\_SRC) to 80% of normal. Optional Separate supply rail for SRC low Voltage I/O - ~33% power saving when 1.5V is used for this rail

- Spread Spectrum for EMI reduction

- Outputs may be disabled via SMBus .

- External crystal load capacitors for maximum frequency accuracy

1616-08/20/09

\*Other names and brands may be claimed as the property of others.

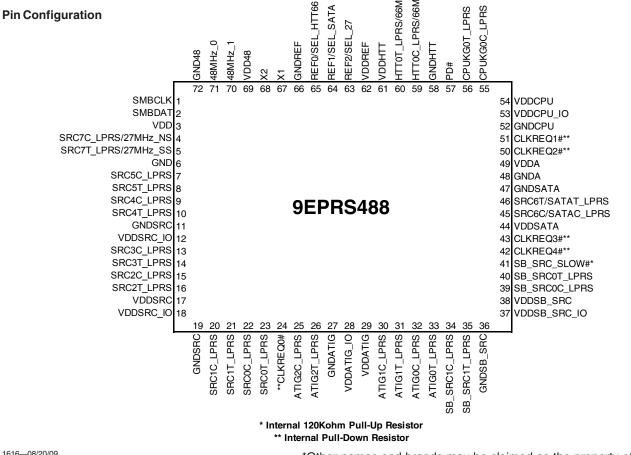

### **Pin Description**

| r        | Description                |            |                                                                                                                                                                                                 |

|----------|----------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN #    |                            | PIN TYPE   | DESCRIPTION                                                                                                                                                                                     |

| 1        | SMBCLK                     | IN         | Clock pin of SMBus circuitry, 5V tolerant.                                                                                                                                                      |

| 2        | SMBDAT                     | I/O        | Data pin for SMBus circuitry, 5V tolerant.                                                                                                                                                      |

| 3        | VDD                        | PWR        | Power supply for SRC7/27MHz                                                                                                                                                                     |

| 4        | SRC7C_LPRS/27MHz_NS        | OUT        | True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm<br>series resistor needed)/27MHz 3.3V Single-ended non-spread output for discrete graphics   |

| 5        | SRC7T_LPRS/27MHz_SS        | OUT        | Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)/27MHz 3.3V Single-ended spreading output for discrete graphics |

| 6        | GND                        | GND        | Ground pin for SRC7/27MHz                                                                                                                                                                       |

|          |                            | GIVE       | Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33                                                                                            |

| 7        | SRC5C_LPRS                 | OUT        | ohm series resistor needed)                                                                                                                                                                     |

| 8        | SRC5T_LPRS                 | OUT        | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                      |

| 9        | SRC4C_LPRS                 | OUT        | Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)                                                                |

| 10       | SRC4T_LPRS                 | OUT        | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                      |

| 11       | GNDSRC                     | GND        | Ground pin for the SRC outputs                                                                                                                                                                  |

| 12       | VDDSRC_IO                  | PWR        | Power supply for differential SRC outputs, nominal 1.05V to 3.3V                                                                                                                                |

| 12       |                            |            | Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33                                                                                            |

| 13       | SRC3C_LPRS                 | OUT        | ohm series resistor needed)                                                                                                                                                                     |

| 14       |                            |            | True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm                                                                                              |

| 14       | SRC3T_LPRS                 | OUT        | series resistor needed)                                                                                                                                                                         |

| 15       | SRC2C_LPRS                 | OUT        | Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                |

| 16       | SRC2T_LPRS                 | OUT        | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm                                                                                              |

|          |                            | 514/5      | series resistor needed)                                                                                                                                                                         |

| 17       | VDDSRC                     | PWR        | Supply for SRC core, 3.3V nominal                                                                                                                                                               |

| 18       | VDDSRC_IO                  | PWR        | Power supply for differential SRC outputs, nominal 1.05V to 3.3V                                                                                                                                |

| 19       | GNDSRC                     | GND        | Ground pin for the SRC outputs                                                                                                                                                                  |

| 20       | SRC1C_LPRS                 | OUT        | Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)                                                                |

|          |                            |            | True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm                                                                                              |

| 21       | SRC1T_LPRS                 | OUT        | series resistor needed)                                                                                                                                                                         |

| 22       | SRC0C_LPRS                 | OUT        | Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33                                                                                            |

|          |                            |            | ohm series resistor needed)<br>True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm                                                               |

| 23       | SRC0T_LPRS                 | OUT        | series resistor needed)                                                                                                                                                                         |

| 24       | **CLKREQ0#                 | IN         | Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:                                                                               |

| ĺ        |                            |            | 0 = enabled, 1 = Low-Low                                                                                                                                                                        |

| 25       | ATIG2C_LPRS                | OUT        | Complementary clock of low-power differential push-pull PCI-Express pair with integrated series                                                                                                 |

| ┣───     |                            |            | resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                 |

| 26       | ATIG2T_LPRS                | OUT        | True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no                                                                                            |

|          | _                          |            | 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                               |

|          | GNDATIG                    |            | Ground pin for the ATIG outputs                                                                                                                                                                 |

| 28       | VDDATIG_IO                 | PWR        | Power supply for differential ATIG outputs, nominal 1.05V to 3.3V                                                                                                                               |

| 29       | VDDATIG                    | PWR        | Power supply for ATIG core, nominal 3.3V                                                                                                                                                        |

| 30       | ATIG1C_LPRS                | OUT        | Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                 |

| 31       | ATIG1T_LPRS                | OUT        | True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no                                                                                            |

| 32       | ATIG0C_LPRS                | OUT        | 50ohm shunt resistor to GND and no 33 ohm series resistor needed)<br>Complementary clock of low-power differential push-pull PCI-Express pair with integrated series                            |

|          |                            |            | resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)<br>True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no         |

| 33       | ATIG0T_LPRS                | OUT        | 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                               |

| 34       | SB_SRC1C_LPRS              | OUT        | Complement clock of low power differential Chipset-to-Chipset SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed                                              |

| <u> </u> |                            | 0.117      | True clock of low power differential Chipset-to-Chipset SRC clock pair. (no 500hm shunt resistor to GND                                                                                         |

| 05       |                            |            |                                                                                                                                                                                                 |

| 35<br>36 | SB_SRC1T_LPRS<br>GNDSB_SRC | OUT<br>GND | and no 33 ohm series resistor needed<br>Ground pin for the SB_SRC outputs                                                                                                                       |

### **Pin Description (Continued)**

|        | Description (Con | ,        |                                                                                                                                                                                                                                      |

|--------|------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN #  |                  | PIN TYPE | DESCRIPTION                                                                                                                                                                                                                          |

| 37     | VDDSB_SRC_IO     | PWR      | Power supply for differential SB_SRC outputs, nominal 1.05V to 3.3V                                                                                                                                                                  |

| 38     | VDDSB_SRC        | PWR      | Supply for SB SRC PLL core, 3.3V nominal                                                                                                                                                                                             |

| 39     | SB_SRC0C_LPRS    | OUT      | Complement clock of low power differential Chipset-to-Chipset SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed                                                                                   |

| 40     | SB_SRC0T_LPRS    | OUT      | True clock of low power differential Chipset-to-Chipset SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed                                                                                         |

| 41     | SB_SRC_SLOW#*    | IN       | When low, this real-time, level-sensitive input slows down the SB_SRC outputs to a user determined lower frequency to save power. The default lower frequency is 80 MHz.<br>0 = Slow Down, 1 = normal operation.                     |

| 42     | CLKREQ4#**       | IN       | Clock Request pin for SRC4/5 outputs. If output is selected for control, then that output is controlled as follows:<br>0 = enabled, 1 = Low-Low                                                                                      |

| 43     | CLKREQ3#**       | IN       | Clock Request pin for SRC3 outputs. If output is selected for control, then that output is controlled as follows:<br>0 = enabled, 1 = Low-Low                                                                                        |

| 44     | VDDSATA          | PWR      | Power supply for SATA core logic, nominal 3.3V                                                                                                                                                                                       |

| 45     | SRC6C/SATAC_LPRS | OUT      | Complement clock of low power differential SRC/SATA clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                |

| 46     | SRC6T/SATAT_LPRS | OUT      | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                           |

| 47     | GNDSATA          | GND      | Ground pin for the SRC outputs                                                                                                                                                                                                       |

| 48     | GNDA             | GND      | Ground for the Analog Core                                                                                                                                                                                                           |

| 49     | VDDA             | PWR      | 3.3V Power for the Analog Core                                                                                                                                                                                                       |

| 50     | CLKREQ2#**       | IN       | Clock Request pin for SRC2 outputs. If output is selected for control, then that output is controlled as follows:<br>0 = enabled, 1 = Low-Low                                                                                        |

| 51     | CLKREQ1#**       | IN       | Clock Request pin for SRC1 outputs. If output is selected for control, then that output is controlled as follows:<br>0 = enabled, 1 = Low-Low                                                                                        |

| 52     | GNDCPU           | GND      | Ground pin for the CPU outputs                                                                                                                                                                                                       |

| 53     | VDDCPU_IO        | PWR      | Power supply for differential CPU outputs, nominal 1.05V to 3.3V                                                                                                                                                                     |

| 54     | VDDCPU           | PWR      | Supply for CPU core, 3.3V nominal                                                                                                                                                                                                    |

| 55     | CPUKG0C_LPRS     | OUT      | Complementary signal of low-power differential push-pull AMD K8 "Greyhound" clock with integrated<br>series resistor. (no 33 ohm series resistor needed)                                                                             |

| 56     | CPUKG0T_LPRS     | OUT      | True signal of low-power differential push-pull AMD K8 "Greyhound" clock with integrated series resistor (no 33 ohm series resistor needed)                                                                                          |

| 57     | PD#              | IN       | Enter /Exit Power Down.<br>0 = Power Down, 1 = normal operation.                                                                                                                                                                     |

| 58     | GNDHTT           | PWR      | Ground pin for the HTT outputs                                                                                                                                                                                                       |

| 59     | HTT0C_LPRS/66M   | OUT      | Complementary signal of low-power differential push-pull hypertransport clock with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) / 1.8V single ended 66MHz hyper transport clock |

| 60     | HTT0T_LPRS/66M   | OUT      | True signal of low-power differential push-pull hypertransport clock with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) /1.8V single ended 66MHz hyper transport clock           |

| 61     | VDDHTT           | PWR      | Supply for HTT clocks, nominal 3.3V.                                                                                                                                                                                                 |

| 62     | VDDREF           | PWR      | Ref, XTAL power supply, nominal 3.3V                                                                                                                                                                                                 |

| 63     | REF2/SEL_27      | OUT      | 14.318 MHz reference clock, 3.3V/3.3V Latched input to select 27MHz SS and non SS on SRC7<br>0 = 100MHz differential spreading SRC clock, 1 = 27MHz non-spreading singled clock on pin 4 and<br>27MHz spread clock on pin 5.         |

| 64     | REF1/SEL_SATA    | I/O      | 14.318 MHz 3.3V reference clock./ 3.3V tolerant latched input to select function of SRC6/SATA output 0 = 100MHz differential spreading SRC clock, 1 = 100MHz non-spreading differential SATA clock                                   |

| 65     | REF0/SEL_HTT66   | I/O      | 14.318 MHz 3.3V reference clock./ 3.3V tolerant latched input to select Hyper Transport Clock<br>Frequency.<br>0 = 100MHz differential HTT clock, 1 = 66MHz 3.3V single ended HTT clock                                              |

| 66     | GNDREF           | GND      | Ground pin for the REF outputs.                                                                                                                                                                                                      |

| 67     | X1               | IN       | Crystal input, nominally 14.318MHz                                                                                                                                                                                                   |

| 68     | Х2               | OUT      | Crystal output, nominally 14.318MHz                                                                                                                                                                                                  |

| 69     | VDD48            | PWR      | Power pin for the 48MHz outputs and core. 3.3V                                                                                                                                                                                       |

|        | 48MHz_1          | OUT      | 48MHz clock output.                                                                                                                                                                                                                  |

| -      | 48MHz_0          | OUT      | 48MHz clock output.                                                                                                                                                                                                                  |

| 72     | GND48            | GND      | Ground pin for the 48MHz outputs                                                                                                                                                                                                     |

| 1616—0 | 8/20/09          |          |                                                                                                                                                                                                                                      |

© 2019 Renesas Electronics Corporation

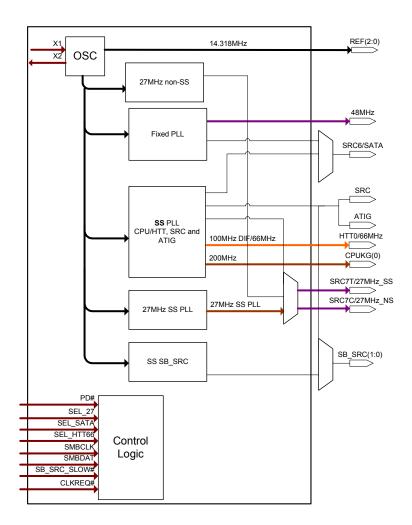

#### **General Description**

The **ICS9EPRS488** is a main clock synthesizer chip that provides all clocks required for AMD M690T or 780E embedded systems. An SMBus interface allows full control of the device.

#### **Block Diagram**

#### **Power Groups**

|     | Pin Number | ·     | Description                        |

|-----|------------|-------|------------------------------------|

| VDD | VDDIO      | GND   | Description                        |

| 69  |            | 72    | USB_48 outputs                     |

| 3   |            | 6     | SRC/27MHz Outputs                  |

| 17  |            | 11,19 | SRC Logic Core                     |

|     | 12,18      |       | SRC differential outputs (IO's)    |

| 38  | 36         |       | SB_SRC Core Logic                  |

|     | 37         |       | SB_SRC differential outputs (IO's) |

| 44  |            | 47    | SRC/SATA differential output       |

| 29  |            | 27    | ATIG Core Logic                    |

|     | 28         |       | ATIG differential outputs (IO's)   |

| 49  |            | 48    | 3.3V Analog                        |

| 54  |            | 52    | CPUKG Core Logic                   |

|     | 53         |       | CPUKG differential outputs (IO's)  |

| 61  |            | 58    | HTTCLK output                      |

| 62  |            | 66    | REF outputs                        |

<sup>© 2019</sup> Renesas Electronics Corporation

| Byte 0 |            | Byt        | te 3       |            | •            | HTT              | Differential  |          |             |                  |

|--------|------------|------------|------------|------------|--------------|------------------|---------------|----------|-------------|------------------|

| Bit0   | Bit3       | Bit2       | Bit1       | Bit0       | CPU<br>(MHz) | Single-<br>ended | HTT           | SRC/ATIG | Spread<br>% | CPU<br>OverClock |

| SS_EN  | CPU<br>FS3 | CPU<br>FS2 | CPU<br>FS1 | CPU<br>FS0 | (1117)       | SEL_HTT66 = 1    | SEL_HTT66 = 0 |          | 70          | %                |

| 0      | 0          | 0          | 0          | 0          | 173.63       | 57.88            | 86.81         | 86.81    |             | -13%             |

| 0      | 0          | 0          | 0          | 1          | 177.17       | 59.06            | 88.58         | 88.58    |             | -11%             |

| 0      | 0          | 0          | 1          | 0          | 180.78       | 60.26            | 90.39         | 90.39    |             | -10%             |

| 0      | 0          | 0          | 1          | 1          | 184.47       | 61.49            | 92.24         | 92.24    |             | -8%              |

| 0      | 0          | 1          | 0          | 0          | 188.24       | 62.75            | 94.12         | 94.12    |             | -6%              |

| 0      | 0          | 1          | 0          | 1          | 192.08       | 64.03            | 96.04         | 96.04    |             | -4%              |

| 0      | 0          | 1          | 1          | 0          | 196.00       | 65.33            | 98.00         | 98.00    |             | -2%              |

| 0      | 0          | 1          | 1          | 1          | 200.00       | 66.67            | 100.00        | 100.00   | Off         | 0%               |

| 0      | 1          | 0          | 0          | 0          | 204.00       | 68.00            | 102.00        | 102.00   |             | 2%               |

| 0      | 1          | 0          | 0          | 1          | 208.08       | 69.36            | 104.04        | 104.04   |             | 4%               |

| 0      | 1          | 0          | 1          | 0          | 212.24       | 70.75            | 106.12        | 106.12   |             | 6%               |

| 0      | 1          | 0          | 1          | 1          | 216.49       | 72.16            | 108.24        | 108.24   |             | 8%               |

| 0      | 1          | 1          | 0          | 0          | 220.82       | 73.61            | 110.41        | 110.41   |             | 10%              |

| 0      | 1          | 1          | 0          | 1          | 225.23       | 75.08            | 112.62        | 112.62   |             | 13%              |

| 0      | 1          | 1          | 1          | 0          | 229.74       | 76.58            | 114.87        | 114.87   |             | 15%              |

| 0      | 1          | 1          | 1          | 1          | 234.33       | 78.11            | 117.17        | 117.17   |             | 17%              |

| 1      | 0          | 0          | 0          | 0          | 173.63       | 57.88            | 86.81         | 86.81    |             | -13%             |

| 1      | 0          | 0          | 0          | 1          | 175.00       | 59.06            | 88.58         | 88.58    |             | -11%             |

| 1      | 0          | 0          | 1          | 0          | 180.78       | 60.26            | 90.39         | 90.39    |             | -10%             |

| 1      | 0          | 0          | 1          | 1          | 184.47       | 61.49            | 92.24         | 92.24    |             | -8%              |

| 1      | 0          | 1          | 0          | 0          | 188.24       | 62.75            | 94.12         | 94.12    |             | -6%              |

| 1      | 0          | 1          | 0          | 1          | 192.08       | 64.03            | 96.04         | 96.04    |             | -4%              |

| 1      | 0          | 1          | 1          | 0          | 196.00       | 65.33            | 98.00         | 98.00    |             | -2%              |

| 1      | 0          | 1          | 1          | 1          | 200.00       | 66.67            | 100.00        | 100.00   | -0.5%       | 0%               |

| 1      | 1          | 0          | 0          | 0          | 204.00       | 68.00            | 102.00        | 102.00   | -0.5 /0     | 2%               |

| 1      | 1          | 0          | 0          | 1          | 208.08       | 69.36            | 104.04        | 104.04   |             | 4%               |

| 1      | 1          | 0          | 1          | 0          | 212.24       | 70.75            | 106.12        | 106.12   |             | 6%               |

| 1      | 1          | 0          | 1          | 1          | 216.49       | 72.16            | 108.24        | 108.24   |             | 8%               |

| 1      | 1          | 1          | 0          | 0          | 220.82       | 73.61            | 110.41        | 110.41   |             | 10%              |

| 1      | 1          | 1          | 0          | 1          | 225.23       | 75.08            | 112.62        | 112.62   |             | 13%              |

| 1      | 1          | 1          | 1          | 0          | 229.74       | 76.58            | 114.87        | 114.87   |             | 15%              |

| 1      | 1          | 1          | 1          | 1          | 234.33       | 78.11            | 117.17        | 117.17   |             | 17%              |

Table1: CPU/HTT, SRC and ATIG Frequency Selection Table

| Table 2 | : SB_S    |           |           | y Sele    | ction Table | •      |             |

|---------|-----------|-----------|-----------|-----------|-------------|--------|-------------|

| Byte 0  |           | By        | te 4      |           |             |        |             |

| Bit0    | Bit3      | Bit2      | Bit1      | Bit0      | SRC         | Spread | SB_SRC      |

| SS_EN   | SB<br>FS3 | SB<br>FS2 | SB<br>FS1 | SB<br>FS0 | (MHz)       | %      | OverClock % |

| 0       | 0         | 0         | 0         | 0         | 80.00       |        | -20%        |

| 0       | 0         | 0         | 0         | 1         | 81.25       | ] [    | -19%        |

| 0       | 0         | 0         | 1         | 0         | 82.63       | I      | -17%        |

| 0       | 0         | 0         | 1         | 1         | 84.00       | Ĩ      | -16%        |

| 0       | 0         | 1         | 0         | 0         | 85.25       | Ī      | -15%        |

| 0       | 0         | 1         | 0         | 1         | 86.63       | Ī      | -13%        |

| 0       | 0         | 1         | 1         | 0         | 88.00       | 1 1    | -12%        |

| 0       | 0         | 1         | 1         | 1         | 89.25       | Off    | -11%        |

| 0       | 1         | 0         | 0         | 0         | 90.63       |        | -9%         |

| 0       | 1         | 0         | 0         | 1         | 92.00       |        | -8%         |

| 0       | 1         | 0         | 1         | 0         | 93.25       | 1 1    | -7%         |

| 0       | 1         | 0         | 1         | 1         | 94.63       | 1      | -5%         |

| 0       | 1         | 1         | 0         | 0         | 96.00       | 1      | -4%         |

| 0       | 1         | 1         | 0         | 1         | 97.25       | Ī      | -3%         |

| 0       | 1         | 1         | 1         | 0         | 98.63       | Ī      | -1%         |

| 0       | 1         | 1         | 1         | 1         | 100.00      | Ī      | 0%          |

| 1       | 0         | 0         | 0         | 0         | 80.00       |        | 20%         |

| 1       | 0         | 0         | 0         | 1         | 175.00      | Ι      | -19%        |

| 1       | 0         | 0         | 1         | 0         | 82.63       | Ι      | -17%        |

| 1       | 0         | 0         | 1         | 1         | 84.00       |        | -16%        |

| 1       | 0         | 1         | 0         | 0         | 85.25       |        | -15%        |

| 1       | 0         | 1         | 0         | 1         | 86.63       |        | -13%        |

| 1       | 0         | 1         | 1         | 0         | 88.00       |        | -12%        |

| 1       | 0         | 1         | 1         | 1         | 89.25       | -0.50% | -11%        |

| 1       | 1         | 0         | 0         | 0         | 90.63       | 0.0070 | -9%         |

| 1       | 1         | 0         | 0         | 1         | 92.00       | ] [    | -8%         |

| 1       | 1         | 0         | 1         | 0         | 93.25       | ļļ     | -7%         |

| 1       | 1         | 0         | 1         | 1         | 94.63       | ļļ     | -5%         |

| 1       | 1         | 1         | 0         | 0         | 96.00       | ļ      | -4%         |

| 1       | 1         | 1         | 0         | 1         | 97.25       |        | -3%         |

| 1       | 1         | 1         | 1         | 0         | 98.63       |        | -1%         |

| 1       | 1         | 1         | 1         | 1         | 100.00      |        | 0%          |

### Table 2: SB\_SRC Frequency Selection Table

| SS Enable | SS3    | SS2    | SS1    | SS0    | 27MHz_Spread | Spr     | ead       |  |  |

|-----------|--------|--------|--------|--------|--------------|---------|-----------|--|--|

| B2b1      | Byte 4 | Byte 4 | Byte 4 | Byte 4 | (MHz)        | % (whon | enabled)  |  |  |

| 0201      | bit 7  | bit 6  | bit 5  | bit 4  | (10112)      |         | ellableu) |  |  |

| 0         | 0      | 0      | 0      | 0      | 27.00        |         |           |  |  |

| 0         | 0      | 0      | 0      | 1      | 27.00        |         |           |  |  |

| 0         | 0      | 0      | 1      | 0      | 27.00        |         |           |  |  |

| 0         | 0      | 0      | 1      | 1      | 27.00        |         |           |  |  |

| 0         | 0      | 1      | 0      | 0      | 27.00        |         |           |  |  |

| 0         | 0      | 1      | 0      | 1      | 27.00        |         |           |  |  |

| 0         | 0      | 1      | 1      | 0      | 27.00        |         |           |  |  |

| 0         | 0      | 1      | 1      | 1      | 27.00        | No S    | oroad     |  |  |

| 0         | 1      | 0      | 0      | 0      | 27.00        | 10.3    | pieau     |  |  |

| 0         | 1      | 0      | 0      | 1      | 27.00        |         |           |  |  |

| 0         | 1      | 0      | 1      | 0      | 27.00        |         |           |  |  |

| 0         | 1      | 0      | 1      | 1      | 27.00        |         |           |  |  |

| 0         | 1      | 1      | 0      | 0      | 27.00        | ]       |           |  |  |

| 0         | 1      | 1      | 0      | 1      | 27.00        |         |           |  |  |

| 0         | 1      | 1      | 1      | 0      | 27.00        |         |           |  |  |

| 0         | 1      | 1      | 1      | 1      | 27.00        |         |           |  |  |

| 1         | 0      | 0      | 0      | 0      | 27.00        | -0.50   | Down      |  |  |

| 1         | 0      | 0      | 0      | 1      | 27.00        | -1.00   | Down      |  |  |

| 1         | 0      | 0      | 1      | 0      | 175.00       | -1.50   | Down      |  |  |

| 1         | 0      | 0      | 1      | 1      | 27.00        | -2.00   | Down      |  |  |

| 1         | 0      | 1      | 0      | 0      | 27.00        | -0.75   | Down      |  |  |

| 1         | 0      | 1      | 0      | 1      | 27.00        | -1.25   | Down      |  |  |

| 1         | 0      | 1      | 1      | 0      | 27.00        | -1.75   | Down      |  |  |

| 1         | 0      | 1      | 1      | 1      | 27.00        | -2.25   | Down      |  |  |

| 1         | 1      | 0      | 0      | 0      | 27.00        | +/-0.25 | Center    |  |  |

| 1         | 1      | 0      | 0      | 1      | 27.00        | +/-0.5  | Center    |  |  |

| 1         | 1      | 0      | 1      | 0      | 27.00        | +/-0.75 | Center    |  |  |

| 1         | 1      | 0      | 1      | 1      | 27.00        | +/-1.0  | Center    |  |  |

| 1         | 1      | 1      | 0      | 0      | 27.00        | +/-0.25 | Center    |  |  |

| 1         | 1      | 1      | 0      | 1      | 27.00        | +/-0.5  | Center    |  |  |

| 1         | 1      | 1      | 1      | 0      | 27.00        | +/-0.75 | Center    |  |  |

| 1         | 1      | 1      | 1      | 1      | 27.00        | +/-1.0  | Center    |  |  |

Table 3: 27Mhz\_Spread and Frequency Selection Table

#### Table 4: CPU Divider Ratios

|         |     |         |     | Divi    | der | (3:2)   |     |         |     |

|---------|-----|---------|-----|---------|-----|---------|-----|---------|-----|

| -       | Bit | 00      |     | 01      |     | 10      |     | 11      | MSB |

| (1:0)   | 00  | 0000    | 2   | 0100    | 4   | 1000    | 8   | 1100    | 16  |

| ir (1   | 01  | 0001    | 3   | 0101    | 6   | 1001    | 12  | 1101    | 24  |

| ide     | 10  | 0010    | 5   | 0110    | 10  | 1010    | 20  | 1110    | 40  |

| Divider | 11  | 0011    | 15  | 0111    | 30  | 1011    | 60  | 1111    | 120 |

|         | LSB | Address | Div | Address |     | Address | Div | Address | Div |

### Table 5: SRC, SB\_SRC, ATIG Divider Ratios

|          |     |         |     | Divi    | der | (3:2)   |     |         |     |

|----------|-----|---------|-----|---------|-----|---------|-----|---------|-----|

|          | Bit | 00      |     | 01      |     | 10      |     | 11      | MSB |

| (1:0)    | 00  | 0000    | 2   | 0100    | 4   | 1000    | 8   | 1100    | 16  |

| ir (1    | 01  | 0001    | 3   | 0101    | 6   | 1001    | 12  | 1101    | 24  |

| Divider  | 10  | 0010    | 5   | 0110    | 10  | 1010    | 20  | 1110    | 40  |

| <u>è</u> | 11  | 0011    | 15  | 0111    | 14  | 1011    | 28  | 1111    | 56  |

|          | LSB | Address | Div | Address |     | Address | Div | Address | Div |

#### **Differential Output Power Management Table**

| PD# | CLKREQ# | SMBus       | True<br>output | Complement<br>Output | True<br>output   | Complement<br>Output |  |

|-----|---------|-------------|----------------|----------------------|------------------|----------------------|--|

| 12. | 011116  | Register OE | Fre            | ee-Run               | CLKREQ# Selected |                      |  |

| 1   | 0       | Enable      | Running        | Running              | Running          | Running              |  |

| 0   | Х       | Х           | Low/20K        | Low                  | Low/20K          | Low                  |  |

| 1   | 1       | Enable      | Running        | Running              | Low/20K          | Low                  |  |

| Х   | Х       | Disable     | Low/20K        | Low                  | Low/20K          | Low                  |  |

Note: 20K means 20Kohm Pull Down

#### Singled-ended Power Management Table

| PD# | SMBus<br>Register OE | 48MHz   | 27MHz   | HTT66MHz | REF(2:0) |  |

|-----|----------------------|---------|---------|----------|----------|--|

| 1   | Enable               | Running | Running | Running  | Running  |  |

| 0   | Enable               | Low     | Low     | Low      | Hi-Z     |  |

### **Absolute Max**

| PARAMETER                | SYMBOL   | CONDITIONS | MIN  | TYP | MAX        | UNITS | Notes |

|--------------------------|----------|------------|------|-----|------------|-------|-------|

| 3.3V Supply Voltage      | VDDxxx   | -          |      | 3.3 | GND + 3.9V | V     | 1     |

| Storage Temperature      | Ts       | -          | -65  |     | 150        | °C    | 1     |

| Ambient Operating Temp   | Tambient | -          | 0    |     | 70         | °C    | 1     |

| Case Temperature         | Tcase    | -          |      |     | 115        | °C    | 1     |

| Input ESD protection HBM | ESD prot | _          | 2000 |     |            | V     | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

#### Electrical Characteristics - Input/Supply/Common Output Parameters

| PARAMETER                                     | SYMBOL                    | CONDITIONS*                                                 | MIN                   | J<br>TYP | MAX                            | UNITS | Notes |

|-----------------------------------------------|---------------------------|-------------------------------------------------------------|-----------------------|----------|--------------------------------|-------|-------|

| 3.3V Core Supply Voltage                      | VDDxxx                    |                                                             | 3.135                 | 3.3      | 3.465                          | V     | 1     |

| Input High Voltage                            | VDDXXX<br>V <sub>IH</sub> | -<br>VDD = 3.3 V +/-5%                                      | 2                     | 0.0      | 3.465<br>V <sub>DD</sub> + 0.3 | V     | 1     |

|                                               |                           | VDD = 3.3 V +/-5%                                           |                       |          |                                | V     | 1     |

| Input Low Voltage                             | V <sub>IL</sub>           |                                                             | V <sub>SS</sub> - 0.3 |          | 0.8                            | -     |       |

| Input High Current                            | I <sub>IH</sub>           | $V_{\rm IN} = V_{\rm DD}$                                   | -5                    |          | 5                              | uA    | 1     |

| Input Low Current                             | I <sub>IL1</sub>          | V <sub>IN</sub> = 0 V; Inputs with no pull-<br>up resistors | -5                    |          |                                | uA    | 1     |

|                                               | I <sub>IL2</sub>          | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors        | -200                  |          |                                | uA    | 1     |

| Low Threshold Input-<br>High Voltage          | $V_{IH_FS}$               | VDD = 3.3 V +/-5%                                           | 0.7                   |          | V <sub>DD</sub> + 0.3          | V     | 1     |

| Low Threshold Input-<br>Low Voltage           | V <sub>IL_FS</sub>        | VDD = 3.3 V +/-5%                                           | V <sub>SS</sub> - 0.3 |          | 0.35                           | V     | 1     |

| Operating Current                             | I <sub>DD3.3OP</sub>      | 3.3V VDD current, all outputs driven                        |                       |          | 175                            | mA    | 1     |

| Powerdown Current                             | I <sub>DD3.3PD</sub>      | all diff pairs low/low                                      |                       |          | 2                              | mA    | 1     |

| Input Frequency                               | Fi                        | VDD = 3.3 V +/-5%                                           |                       | 14.31818 |                                | MHz   | 2     |

| Pin Inductance                                | L <sub>pin</sub>          |                                                             |                       |          | 7                              | nH    | 1     |

|                                               | C <sub>IN</sub>           | Logic Inputs                                                |                       |          | 5                              | pF    | 1     |

| Input Capacitance                             | C <sub>OUT</sub>          | Output pin capacitance                                      |                       |          | 6                              | pF    | 1     |

|                                               | C <sub>INX</sub>          | X1 & X2 pins                                                |                       |          | 5                              | pF    | 1     |

| Clk Stabilization                             | T <sub>STAB</sub>         | From VDD Power-Up or de-<br>assertion of PD to 1st clock    |                       |          | 3                              | ms    | 1     |

| Modulation Frequency                          |                           | Triangular Modulation                                       | 30                    |          | 33                             | kHz   | 1     |

| Tdrive_PD                                     |                           | CPU output enable after<br>PD de-assertion                  |                       |          | 300                            | us    | 1     |

| Tfall_PD                                      |                           | PD fall time of                                             |                       |          | 5                              | ns    | 1     |

| Trise_PD                                      |                           | PD rise time of                                             |                       |          | 5                              | ns    | 1     |

| SMBus Voltage                                 | V <sub>DDSMB</sub>        |                                                             | 2.7                   |          | 5.5                            | V     | 1     |

| Low-level Output Voltage                      | V <sub>OLSMB</sub>        | @ I <sub>PULLUP</sub>                                       |                       |          | 0.4                            | V     | 1     |

| Current sinking at<br>V <sub>OL</sub> = 0.4 V | IPULLUPSMB                |                                                             | 4                     | 6        |                                | mA    | 1     |

| SMBCLK/SMBDAT<br>Clock/Data Rise Time         | T <sub>RSMB</sub>         | (Max VIL - 0.15) to<br>(Min VIH + 0.15)                     |                       |          | 1000                           | ns    | 1     |

| SMBCLK/SMBDAT<br>Clock/Data Fall Time         | T <sub>FSMB</sub>         | (Min VIH + 0.15) to<br>(Max VIL - 0.15)                     |                       |          | 300                            | ns    | 1     |

\*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V + -5%

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Input frequency should be measured at the REF pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

#### AC Electrical Characteristics - Low-Power DIF Outputs: CPUKG and HTT

|                                         |                       | •                                 |       |     |      |       |       |

|-----------------------------------------|-----------------------|-----------------------------------|-------|-----|------|-------|-------|

| PARAMETER                               | SYMBOL                | CONDITIONS                        | MIN   | TYP | MAX  | UNITS | NOTES |

| Crossing Point Variation                | $\Delta V_{CROSS}$    | Single-ended Measurement          |       |     | 140  | mV    | 1,2,5 |

| Frequency - CPU                         | f <sub>CPU</sub>      | Spread Specturm On                | 198.8 |     | 200  | MHz   | 1,3   |

| Frequency - HTT                         | f <sub>нтт</sub>      | Spread Specturm On                | 99.4  |     | 100  | MHz   | 1,3   |

| Long Term Accuracy                      | ppm                   | Spread Specturm Off               | -300  |     | +300 | ppm   | 1,11  |

| Rising Edge Slew Rate                   | S <sub>RISE</sub>     | Differential Measurement          | 0.5   |     | 10   | V/ns  | 1,4   |

| Falling Edge Slew Rate                  | S <sub>FALL</sub>     | Differential Measurement          | 0.5   |     | 10   | V/ns  | 1,4   |

| Slew Rate Variation                     | t <sub>SLVAR</sub>    | Single-ended Measurement          |       |     | 20   | %     | 1     |

| CPU, DIF HTT Jitter - Cycle to<br>Cycle | CPUJ <sub>C2C</sub>   | Differential Measurement          |       |     | 150  | ps    | 1,6   |

| Accumulated Jitter                      | t <sub>JACC</sub>     | See Notes                         |       |     | 1    | ns    | 1,7   |

| Peak to Peak Differential Voltage       | V <sub>D(PK-PK)</sub> | Differential Measurement          | 400   |     | 2400 | mV    | 1,8   |

| Differential Voltage                    | VD                    | Differential Measurement          | 200   |     | 1200 | mV    | 1,9   |

| Duty Cycle                              | D <sub>CYC</sub>      | Differential Measurement          | 45    |     | 55   | %     | 1     |

| Amplitude Variation                     | $\Delta V_D$          | Change in $V_D DC$ cycle to cycle | -75   |     | 75   | mV    | 1,10  |

| CPU[1:0] Skew                           | CPU <sub>SKEW10</sub> | Differential Measurement          |       |     | 100  | ps    | 1     |

#### Notes on Electrical Characteristics:

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Single-ended measurement at crossing point. Value is maximum – minimum over all time. DC value of common mode is not <sup>3</sup>Minimum Frequency is a result of 0.5% down spread spectrum

<sup>4</sup>Differential measurement through the range of ±100 mV, differential signal must remain monotonic and within slew rate spec when crossing through this region.

<sup>5</sup> Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets CLK#.

$^{\rm 6}\,{\rm Max}$  difference of  $t_{\rm CYCLE}$  between any two adjacent cycles.

<sup>7</sup> Accumulated tjc.over a 10 µs time period, measured with JIT2 TIE at 50ps interval.

<sup>8</sup> VD(PK-PK) is the overall magnitude of the differential signal.

<sup>9</sup> VD(min) is the amplitude of the ring-back differential measurement, guaranteed by design, that ring-back will not cross 0V VD. VD(max) is the largest amplitude allowed.

<sup>10</sup> The difference in magnitude of two adjacent VD\_DC measurements. VD\_DC is the stable post overshoot and ring-back part of

<sup>11</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

#### AC Electrical Characteristics - Low-Power DIF Outputs: SRC, SB\_SRC and ATIG

| PARAMETER                             | SYMBOL              | CONDITIONS               | MIN  | TYP | MAX  | UNITS | NOTES |

|---------------------------------------|---------------------|--------------------------|------|-----|------|-------|-------|

| Rising Edge Slew Rate                 | t <sub>SLR</sub>    | Differential Measurement | 0.6  |     | 4    | V/ns  | 1,2   |

| Falling Edge Slew Rate                | t <sub>FLR</sub>    | Differential Measurement | 0.6  |     | 4    | V/ns  | 1,2   |

| Slew Rate Variation                   | t <sub>SLVAR</sub>  | Single-ended Measurement |      |     | 20   | %     | 1     |

| Maximum Output Voltage                | V <sub>HIGH</sub>   | Includes overshoot       |      |     | 1150 | mV    | 1     |

| Minimum Output Voltage                | V <sub>LOW</sub>    | Includes undershoot      | -300 |     |      | mV    | 1     |

| Differential Voltage Swing            | V <sub>SWING</sub>  | Differential Measurement | 300  |     |      | mV    | 1     |

| Crossing Point Voltage                | V <sub>XABS</sub>   | Single-ended Measurement | 300  |     | 550  | mV    | 1,3,4 |

| Crossing Point Variation              | VXABSVAR            | Single-ended Measurement |      |     | 140  | mV    | 1,3,5 |

| Duty Cycle                            | D <sub>CYC</sub>    | Differential Measurement | 45   |     | 55   | %     | 1     |

| SRC, ATIG, Jitter - Cycle to<br>Cycle | SRCJ <sub>C2C</sub> | Differential Measurement |      |     | 125  | ps    | 1     |

| SRC[5:0] Skew                         | SRC <sub>SKEW</sub> | Differential Measurement |      |     | 250  | ps    | 1     |

| SB_SRC[1:0] Skew                      | SRC <sub>SKEW</sub> | Differential Measurement |      |     | 100  | ps    | 1     |

| ATIG[2:0] Skew                        | SRC <sub>SKEW</sub> | Differential Measurement |      |     | 100  | ps    | 1     |

#### Notes on Electrical Characteristics:

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Slew rate measured through Vswing centered around differential zero

<sup>3</sup> Vxabs is defined as the voltage where CLK = CLK#

<sup>4</sup> Only applies to the differential rising edge (CLK rising and CLK# falling)

<sup>5</sup> Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of

<sup>6</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

#### Electrical Characteristics - Single-ended HTT 66MHz Clock

| <u> </u>                                          |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                          |                                                          |                                                          |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|

| SYMBOL                                            | CONDITIONS                                                                                                                               | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MAX                                                      | UNITS                                                    | Notes                                                    |

| ppm                                               | see Tperiod min-max values                                                                                                               | -100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                                                      | ppm                                                      | 1,2                                                      |

| т                                                 | 66.67MHz output nominal                                                                                                                  | 14.9955                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15.0045                                                  | ns                                                       | 2                                                        |

| It High Voltage V <sub>OH</sub> I <sub>OH</sub> = | 66.67MHz output spread                                                                                                                   | 14.9955                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15.0799                                                  | ns                                                       | 2                                                        |

| V <sub>OH</sub>                                   | I <sub>ОН</sub> = -1 mА                                                                                                                  | 1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.3                                                      | V                                                        | 1                                                        |

| V <sub>OL</sub>                                   | I <sub>OL</sub> = 1 mA                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.2                                                      | V                                                        | 1                                                        |

| t <sub>r1</sub>                                   | $V_{OL} = 0.36 \text{ V}, \text{ V}_{OH} = 1.44 \text{ V}$                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.5                                                      | ns                                                       | 1                                                        |

| t <sub>f1</sub>                                   | $V_{OH} = 1.44 \text{ V}, V_{OL} = 0.36 \text{ V}$                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.5                                                      | ns                                                       | 1                                                        |

| d <sub>t1</sub>                                   | $V_{T} = 0.9 V$                                                                                                                          | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55                                                       | %                                                        | 1                                                        |

| t <sub>jcyc-cyc</sub>                             | $V_{T} = 0.9 V$                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 300                                                      | ps                                                       | 1                                                        |

| t <sub>LTJ</sub>                                  | $V_{T} = 0.9 V$                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                        | ns                                                       | 1                                                        |

|                                                   | SYMBOL   ppm   T <sub>period</sub> V <sub>OH</sub> V <sub>OL</sub> t <sub>r1</sub> t <sub>f1</sub> d <sub>t1</sub> t <sub>jcyc-cyc</sub> | $\begin{tabular}{ c c c c c } \hline SYMBOL & CONDITIONS \\ \hline ppm & see Tperiod min-max values \\ \hline T_{period} & \hline 66.67MHz output nominal \\ \hline 66.67MHz output spread \\ \hline V_{OH} & I_{OH} = -1 mA \\ \hline V_{OL} & I_{OL} = 1 mA \\ \hline V_{OL} & I_{OL} = 1 mA \\ \hline t_{r1} & V_{OL} = 0.36 V, V_{OH} = 1.44 V \\ \hline t_{f1} & V_{OH} = 1.44 V, V_{OL} = 0.36 V \\ \hline d_{t1} & V_{T} = 0.9 V \\ \hline t_{jcyc-cyc} & V_{T} = 0.9 V \\ \hline \end{array}$ | $\begin{tabular}{ c c c c c c } \hline SYMBOL & CONDITIONS & MIN \\ \hline ppm & see Tperiod min-max values & -100 \\ \hline T_{period} & 66.67MHz output nominal & 14.9955 \\ \hline V_{OH} & I_{OH} = -1 mA & 1.6 \\ \hline V_{OL} & I_{OL} = 1 mA & 1.6 \\ \hline V_{OL} & I_{OL} = 0.36 V, V_{OH} = 1.44 V \\ \hline t_{f1} & V_{OH} = 1.44 V, V_{OL} = 0.36 V & \\ \hline d_{t1} & V_{T} = 0.9 V & 45 \\ \hline t_{jcyc-cyc} & V_{T} = 0.9 V & \\ \hline \end{array}$ | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ |

\*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs =  $22\Omega$  (unless otherwise specified)

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that REF is at 14.31818MHz

| PARAMETER              | SYMBOL                | CONDITIONS*                                      | MIN     | TYP | MAX     | UNITS | NOTES |

|------------------------|-----------------------|--------------------------------------------------|---------|-----|---------|-------|-------|

| Long Accuracy          | ppm                   | see Tperiod min-max values                       | -100    | 0   | 100     | ppm   | 1,2   |

| Clock period           | T <sub>period</sub>   | 48.00MHz output nominal                          | 20.8229 |     | 20.8344 | ns    | 2     |

| Clock Low Time         | T <sub>low</sub>      | Measure from < 0.6V                              | 9.3750  |     | 11.4580 | ns    | 2     |

| Clock High Time        | T <sub>high</sub>     | Measure from > 2.0V                              | 9.3750  |     | 11.4580 | ns    | 2     |

| Output High Voltage    | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                          | 2.4     |     |         | V     | 1     |

| Output Low Voltage     | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA                           |         |     | 0.55    | V     | 1     |

| Output Lligh Current   |                       | V <sub>OH</sub> @MIN = 1.0 V                     | -33     |     |         | mA    | 1     |

| Output High Current    | I <sub>ОН</sub>       | V <sub>OH</sub> @MAX = 3.135 V                   |         |     | -33     | mA    | 1     |

| Output Low Ourront     | I                     | V <sub>OL</sub> @ MIN = 1.95 V                   | 30      |     |         | mA    | 1     |

| Output Low Current     | I <sub>OL</sub>       | V <sub>OL</sub> @ MAX = 0.4 V                    |         |     | 38      | mA    | 1     |

| Rise Time              | t <sub>r_USB</sub>    | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ | 0.5     |     | 1.5     | ns    | 1     |

| Fall Time              | t <sub>f_USB</sub>    | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ | 0.5     |     | 1.5     | ns    | 1     |

| Duty Cycle             | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V                           | 45      |     | 55      | %     | 1     |

| Group Skew             | t <sub>skew</sub>     | V <sub>T</sub> = 1.5 V                           |         |     | 250     | ps    | 1     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V                           |         |     | 130     | ps    | 1,2   |

#### **Electrical Characteristics - USB - 48MHz**

\*TA = 0 - 70°C; Supply Voltage VDD = 3.3 V +/-5%, CL = 5 pF with Rs =  $22\Omega$  (unless otherwise specified)

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>ICS recommended and/or chipset vendor layout guidelines must be followed to meet this specification

#### **Electrical Characteristics - 27MHz**

| PARAMETER                   | SYMBOL                | CONDITIONS                 | MIN     | TYP | MAX                                             | UNITS    | Notes |