### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## 16

# H8S/2140B Group

Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2100 Series

H8S/2161B HD64F2161BV

H8S/2160B HD64F2160BV

H8S/2141B HD64F2141BV

H8S/2140B HD64F2140BV

H8S/2145B HD64F2145BV

HD64F2145B

H8S/2148B HD64F2148BV

HD64F2148B

Renesas Electronics

www.renesas.com

Rev.3.00 2006.03

- Technology Corp. product best suited to the customer's application; they do not convey any under any intellectual property rights, or any other rights, belonging to Renesas Technology a third party.

- Renesas Technology Corp. assumes no responsibility for any damage, or infringement of an party's rights, originating in the use of any product data, diagrams, charts, programs, algorith circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, progra algorithms represents information on products at the time of publication of these materials, a subject to change by Renesas Technology Corp. without notice due to product improvemen other reasons. It is therefore recommended that customers contact Renesas Technology C an authorized Renesas Technology Corp. product distributor for the latest product information of the product information.

an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various

including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.co

- When using any or all of the information contained in these materials, including product data diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a system before making a final decision on the applicability of the information and products. Frechnology Corp. assumes no responsibility for any damage, liability or other loss resulting information contained herein.

Renesas Technology Corp. semiconductors are not designed or manufactured for use in a contained herein.

- Information contained nerein.5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a consistent system that is used under circumstances in which human life is potentially at stake. Please Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor considering the use of a product contained herein for any specific purposes, such as appara

- considering the use of a product contained herein for any specific purposes, such as appara systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater us 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduct whole or in part these materials.

- whole or in part these materials.7. If these products or technologies are subject to the Japanese export control restrictions, the be exported under a license from the Japanese government and cannot be imported into a control restriction.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/o country of destination is prohibited.8. Please contact Renesas Technology Corp. for further details on these materials or the prod

Rev. 3.00 Mar 21, 2006 page ii of liv

contained therein.

other than the approved destination.

2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. In

Generally, the input pins of CMOS products are high-impedance input pins. It are in their open states, intermediate levels are induced by noise in the vicinity through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throug chip and a low level is input on the reset pin. During the period where the stat undefined, the register settings and the output state of each pin are also undefined your system so that it does not malfunction because of processing while it is is undefined state. For those products which have a reset function, reset the LSI

4. Prohibition of Access to Undefined or Reserved Addresses

after the power supply has been turned on.

Note: Access to undefined or reserved addresses is prohibited

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test may have been be allocated to these addresses. Do not access these registers; operation is not guaranteed if they are accessed.

Rev. 3.00 Mar 21, 2006

The list of revisions is a summary of points that have been revised or added to earlie. This does not include all of the revised contents. For details, see the actual locations

- manual.5. Contents

- 6. Overview

- 7. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. E includes notes in relation to the descriptions given, and usage notes are given, as requir final part of each section.

- 8. List of Registers

- 9. Electrical Characteristics

- 10. Appendix

- 11. Index

Rev. 3.00 Mar 21, 2006 page iv of liv

RENESAS

This I CI is a suite and suith a data town of an acceptable (DTC) as a large massive DOM D

This LSI is equipped with a data transfer controller (DTC) as a bus master, ROM, RA PWM timer (PWM), a 14-bit PWM timer (PWMX), a 16-bit free-running timer (FRT timer (TMR), timer connection, a watchdog timer (WDT), a serial communication int a keyboard buffer controller, a host interface X-bus interface (XBS), a host interface I

optional interface.

A high-functionality bus controller is also provided, enabling fast and easy connection and other kinds of memory.

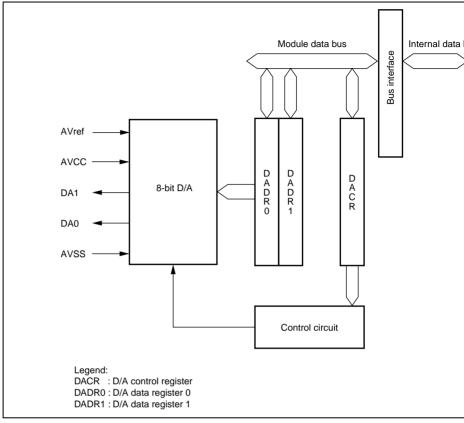

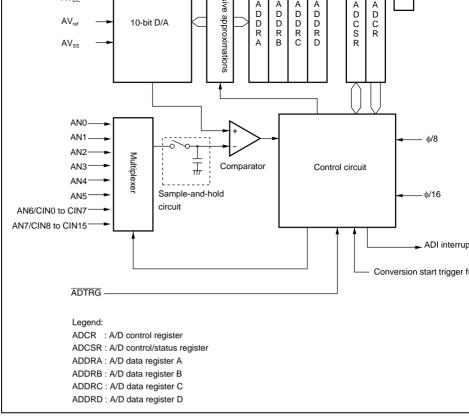

(LPC), an 8-bit D/A converter, a 10-bit A/D converter, and I/O ports as on-chip peripl modules required for system configuration. An I<sup>2</sup>C bus interface (IIC) can also be incl

and other kinds of memory.

A flash memory (F-ZTAT<sup>™\*</sup>) version is available for this LSI's ROM. This provides

it can be reprogrammed in no time to cope with all situations from the early stages of

production to full-scale mass production. This is particularly applicable to application specifications that will most probably change.

Note: \* F-ZTAT is a trademark of Renesas Technology Corp.

Target Users: This manual was written for users who will be using the H8S/2140B of design of application systems. Target users are expected to understand fundamentals of electrical circuits, logical circuits, and microcompute

Objective: This manual was written to explain the hardware functions and electric characteristics of the H8S/2140B Group to the target users.

Refer to the H8S/2600 Series, H8S/2000 Series Programming Manual detailed description of the instruction set.

his manual:

Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized on the CPU, system control functions, peripheral functions and electrical characters

Rev. 3.00 Mar 21, 2006

|                  | XXX_N (XXX is the register name and N is the     |

|------------------|--------------------------------------------------|

|                  | number)                                          |

| Bit order:       | The MSB is on the left and the LSB is on the rig |

| Number notation: | Binary is B'xxxx, hexadecimal is H'xxxx, decim   |

| Signal notation: | An overbar is added to a low-active signal: xxxx |

ADE-7

ADE-7

ADE-7

Related Manuals: The latest versions of all related manuals are available from our w Please ensure you have the latest versions of all documents you re http://www.renesas.com/

H8S/2140B Group manuals:

| Document Title                                                                        | Docu   |

|---------------------------------------------------------------------------------------|--------|

| H8S/2140B Group Hardware Manual                                                       | This n |

| H8S/2600 Series, H8S/2000 Series Programming Manual                                   | REJ09  |

| User's manuals for development tools:                                                 |        |

| Document Title                                                                        | Docu   |

| H8S, H8/300 Series C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | REJ10  |

|                                                                                       |        |

Rev. 3.00 Mar 21, 2006 page vi of liv

H8S, H8/300 Series Simulator/Debugger User's Manual

High-performance Embedded Workshop User's Manual

High-performance Debugging Interface Tutorial

H8S, H8/300 Series High-performance Embedded Workshop,

|   | Note: * The    | e LPC functio  | n is not su | pported h | v H8S/      |

|---|----------------|----------------|-------------|-----------|-------------|

|   |                | 3 (5-V version |             | pported t | /y 1100/    |

| 2 | On-chip r      |                |             |           |             |

| 2 | •              | •              |             |           |             |

|   | Table ame      | nded           |             |           |             |

|   | ROM            | Model          | ROM         | RAM       | Remark      |

|   | F-ZTAT Version | HD64F2161BV*   | 128 kbytes  | 4 kbytes  |             |

|   |                | HD64F2160BV*   | 64 kbytes   | 4 kbytes  | _           |

|   |                | HD64F2141BV*   | 128 kbytes  | 4 kbytes  |             |

|   |                | HD64F2140BV*   | 64 kbytes   | 4 kbytes  | <del></del> |

|   |                | HD64F2145BV*   | 256 kbytes  | 8 kbytes  | Under d     |

|   |                | HD64F2145B     | 256 kbytes  | 8 kbytes  |             |

|   |                | HD64F2148BV*   | 128 kbytes  | 4 kbytes  | _           |

|   |                | HD64F2148B     | 128 kbytes  | 4 kbytes  |             |

Note amended

Note \* added

Host Interface LPC interface\*

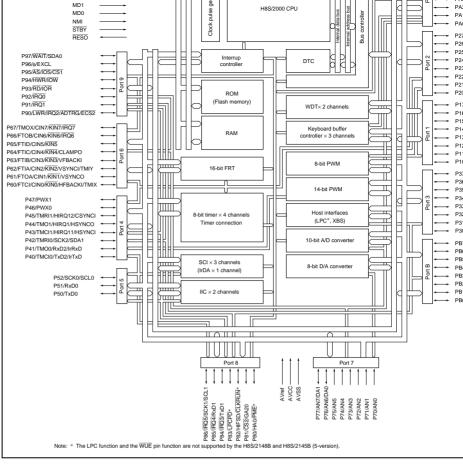

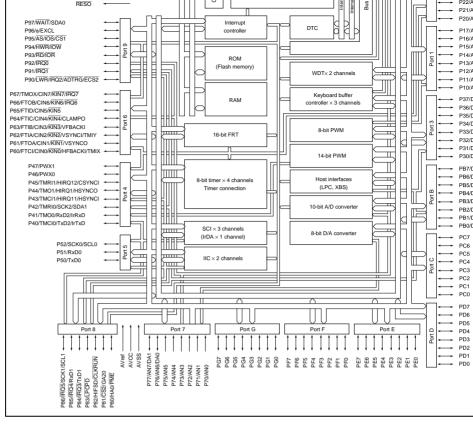

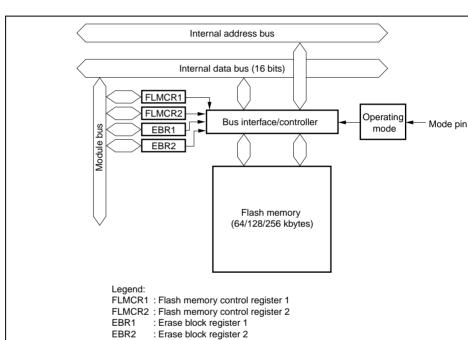

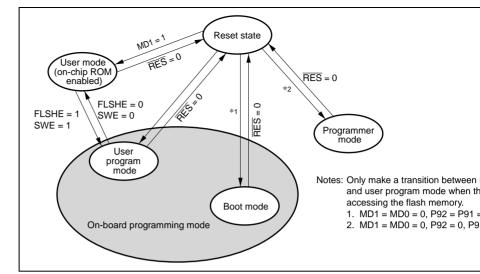

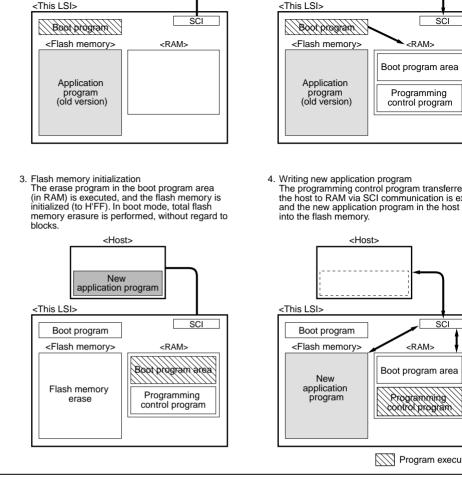

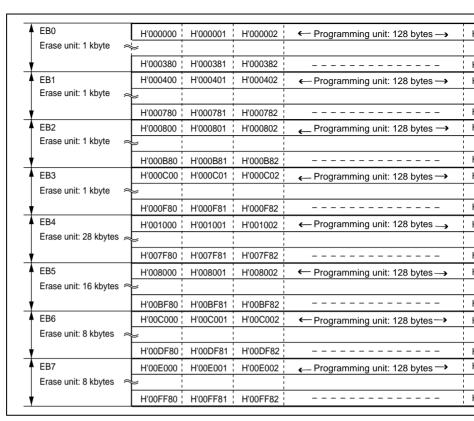

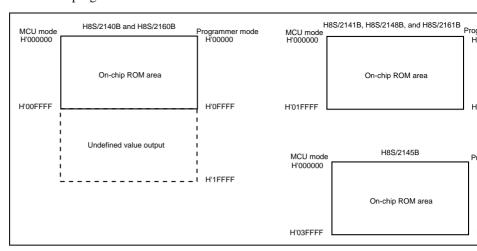

1.2 Block Diagram

Figure 1.1 Internal

Block Diagram of H8S/2140B,

H8S/2141B, H8S/2145B, and H8S/2148B

Figure 1.2 Internal Block Diagram of H8S/2160B and H8S/2161B

(Before) ROM (Flash memory, Masked ROM) → (A (Flash memory)

3

4

RENESAS

Figure 1.2 amended

Rev. 3.00 Mar 21, 2006

Note: \* The LPC function and the WUE pin function

supported by the H8S/2148B and H8S/2145B (5-V

| 1.3.2 FILL FULLCHIONS III                                                                                            | 1.1                                                                                        | Note · amended |          |                                                                                                                     |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Each Operating Mode Table 1.1 Pin Functions of H8S/2140B, H8S/2141B, H8S/2145B, and H8S/2148B in Each Operating Mode | able 1.1 Pin<br>unctions of<br>8S/2140B,<br>8S/2141B,<br>8S/2145B, and<br>8S/2148B in Each |                |          | Note: * The LPC function and the WUE pin function supported by the H8S/2148B and H8S/2145B (5-V v                   |  |  |  |  |

| 2.4.4 Condition-Code                                                                                                 | 36                                                                                         | Table ar       | mended   | I                                                                                                                   |  |  |  |  |

| Register (CCR)                                                                                                       |                                                                                            | Interrup       | t Mask I | Bit                                                                                                                 |  |  |  |  |

|                                                                                                                      |                                                                                            | Masks ii       | nterrupt | s when set to 1. NMI is accepted                                                                                    |  |  |  |  |

| 2.6.1 Table of                                                                                                       | 46                                                                                         | Table ar       | mended   | I                                                                                                                   |  |  |  |  |

| Instructions Classified                                                                                              |                                                                                            | Instruction    | Size*    | Function                                                                                                            |  |  |  |  |

| by Function                                                                                                          |                                                                                            | BIAND          | В        | $C \wedge [\sim (< bit-No.> of < EAd>)] \rightarrow C$                                                              |  |  |  |  |

| Table 2.7 Bit                                                                                                        |                                                                                            |                |          | Logically ANDs the carry flag with the inverse of a speci<br>general register or memory operand and stores the resu |  |  |  |  |

BIOR

В

Description amended

| @aa:16, @aa:24, or<br>@aa:32 | absolute addre |

|------------------------------|----------------|

|                              |                |

Rev. 3.00 Mar 21, 2006 page viii of liv

53

Manipulation

Instructions (1)

2.7.5 Absolute

Address-@aa:8,

RENESAS

The bit number is specified by 3-bit immediate data.

Logically ORs the carry flag with the inverse of a specific general register or memory operand and stores the resu flag.

The bit number is specified by 3-bit immediate data.

$C \vee \llbracket \sim (< bit-No. > of < EAd >) \rrbracket \rightarrow C$

... absolute address, the upper 24 bits are all assum

|    |       | ор       | abs   | S   |       |       |      |  |

|----|-------|----------|-------|-----|-------|-------|------|--|

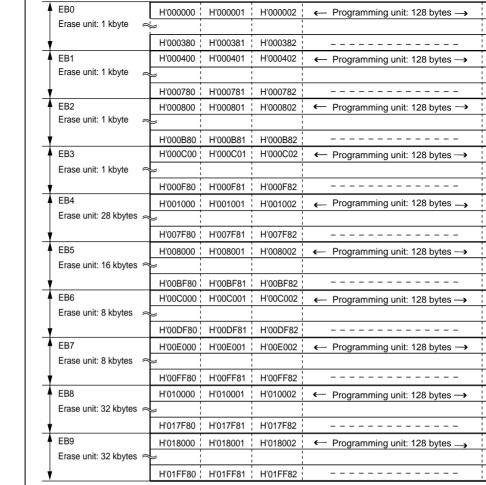

| 78 | Figui | re 3.7 a | ind f | Fig | ure 3 | 3.8 a | dded |  |

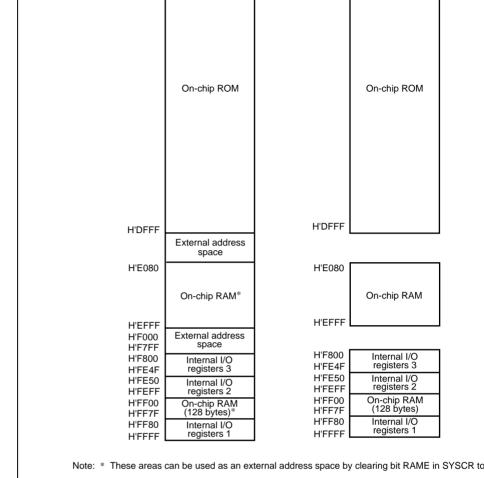

| Each Operating Mode                         |    |                                                          |  |  |  |  |

|---------------------------------------------|----|----------------------------------------------------------|--|--|--|--|

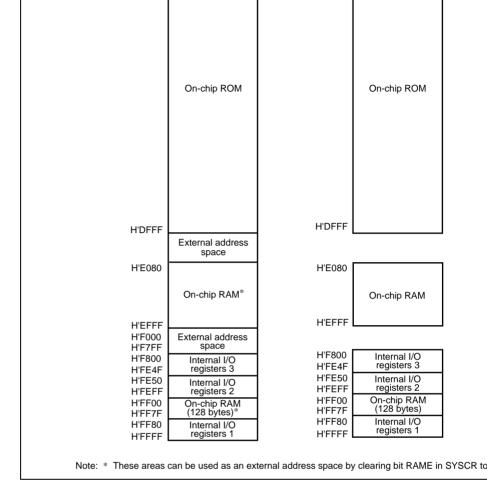

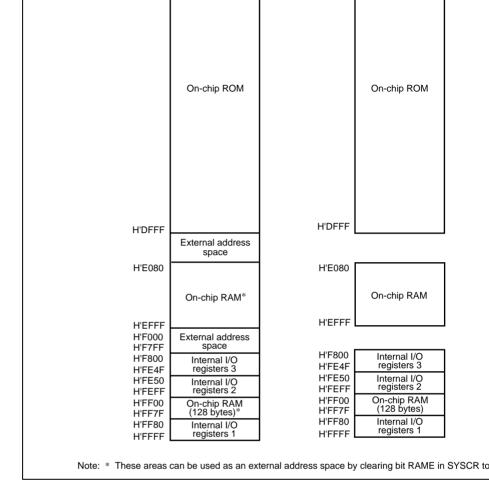

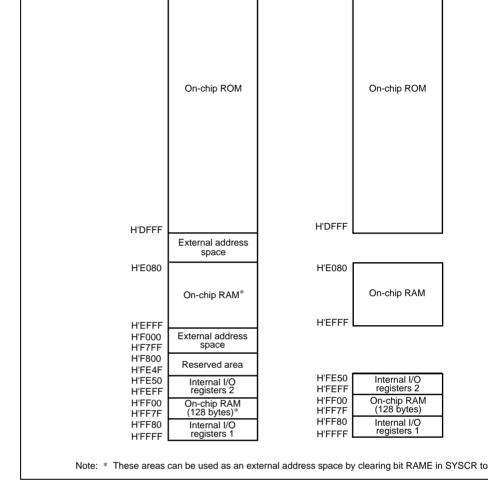

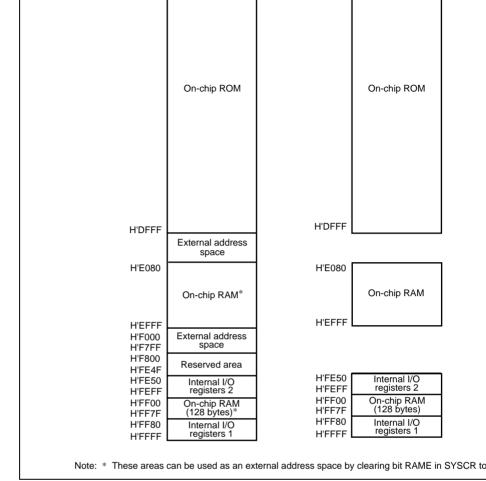

| Figure 3.7 Address<br>Map for H8S/2145B (1) |    |                                                          |  |  |  |  |

| Figure 3.8 Address<br>Map for H8S/2145B (2) |    |                                                          |  |  |  |  |

| Figure 3.9 Address                          | 79 | Figure 3.9 amended                                       |  |  |  |  |

| Map for H8S/2148B(1)                        |    | H'01FFFF                                                 |  |  |  |  |

|                                             |    | H'020000                                                 |  |  |  |  |

|                                             |    | H'FFE080                                                 |  |  |  |  |

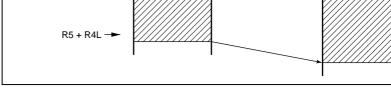

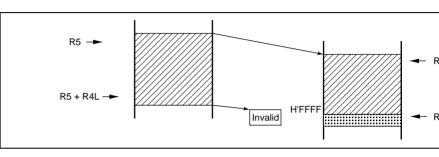

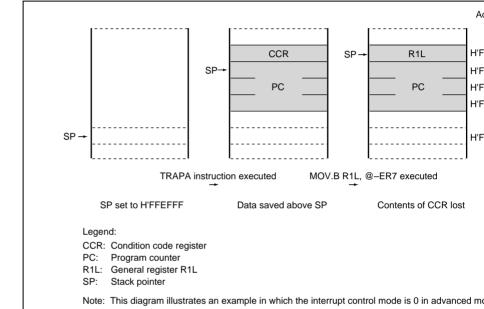

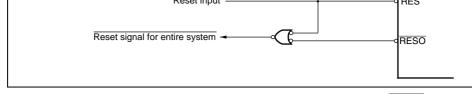

| 4.7 Usage Note                              | 87 | Figure 4.3 amended                                       |  |  |  |  |

| Figure 4.3 Operation when SP Value Is Old   |    | H'FFEFFF                                                 |  |  |  |  |

| 5.2 Input/Output Pins                       | 91 | Note * amended                                           |  |  |  |  |

| Table 5.1 Pin Configuration                 |    | Note: * Not supported by the H8S/2148B and H8S version). |  |  |  |  |

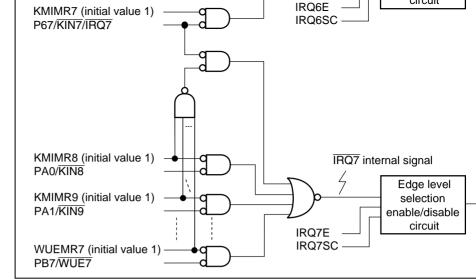

| 5.3.7 Keyboard Matrix                       | 98 | • WUEMRB*                                                |  |  |  |  |

| Interrupt Mask                              |    | Note * amended                                           |  |  |  |  |

| Registers (KMIMRA,                          |    | Note: * Not supported by the HOC/24 40D and HOC          |  |  |  |  |

3.4 Address Map in

KMIMR) and Wake-Up

Event Mask Register

(WUEMRB)

77,

Note: \* Not supported by the H8S/2148B and H8S/

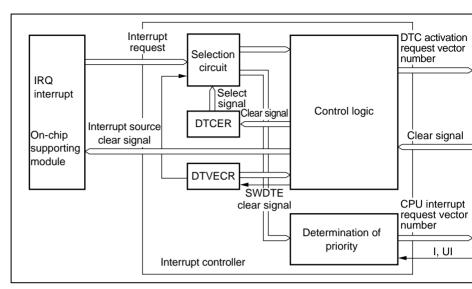

| 7.2.8 DTC Vector<br>Register (DTVECR)                                               | 151 | Description amended software activation interrupt.                 |

|-------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|

|                                                                                     |     | DTVECR is initialized to H'00 at a reset and in hard standby mode. |

| 7.4 Location of                                                                     | 154 | Note 2 amended                                                     |

| Register Information and DTC Vector Table                                           |     | Note: 2. Not supported by the H8S/2148B and H8S/version).          |

| Table 7.1 Interrupt<br>Sources, DTC Vector<br>Addresses, and<br>Corresponding DTCEs |     |                                                                    |

| 8.1 Overview                                                                        | 167 | Description amended                                                |

|                                                                                     |     | in addition to DDR, to control the on/off                          |

| Table 8.1 Port                                                                      | 171 | Note * amended                                                     |

| Functions of H8S/2140B,                                                             |     | Note: * Not supported by the H8S/2148B and H8S/version)            |

version).

Note amended

Description amended

... the DTCE bit of DTC's DTCER, and the DISEL bit

• P37/D15/HDB7/SERIRQ\*, ..., P30/D8/HDB0/LAD

Note: \* Not supported by the H8S/2148B and H8S/2

Rev. 3.00 Mar 21, 2006 page x of liv

181

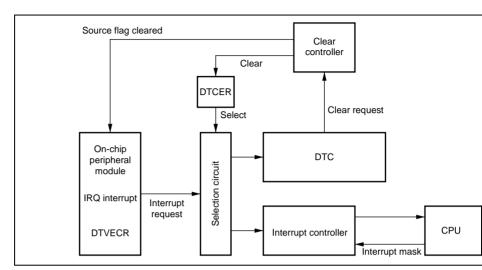

5.6.5 DTC Activation

by Interrupt

H8S/2141B, H8S/2145B, and H8S/2148B

8.4.4 Pin Functions

114

RENESAS

|                                                                      |               | Note 3 amended                                                |

|----------------------------------------------------------------------|---------------|---------------------------------------------------------------|

|                                                                      |               | Note: 3. Not supported by the H8S/2148B and H8 version).      |

| 8.12.4 Pin Functions                                                 | 213 to<br>215 | • PB7/D7/WUE7*2, PB6/D6/WUE6*2, PB5/D5/WU<br>PB4/D4/WUE4*2 to |

|                                                                      |               | • PB0/D0/WUE0/HIRQ3/LSMI*4                                    |

|                                                                      |               | Notes amended                                                 |

|                                                                      |               | Note: Not supported by the H8S/2148B and H8S/version).        |

| 11.3.6 Timer Interrupt                                               | 265           | Table amended                                                 |

| Enable Register (TIER)                                               |               | Initial Value                                                 |

|                                                                      |               | (Before) $0 \rightarrow$ (After) 1                            |

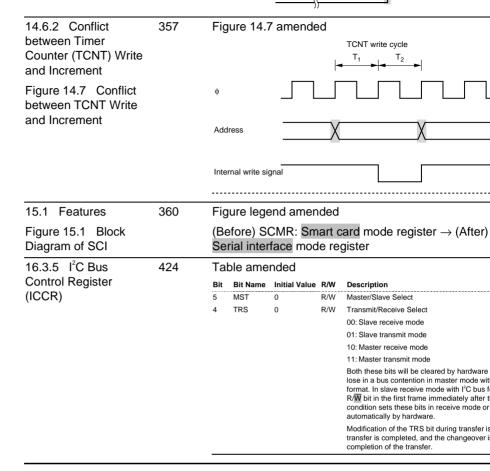

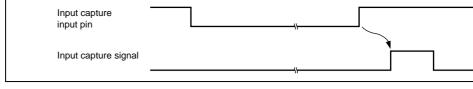

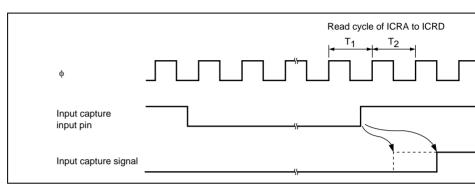

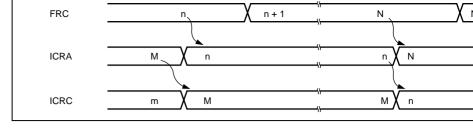

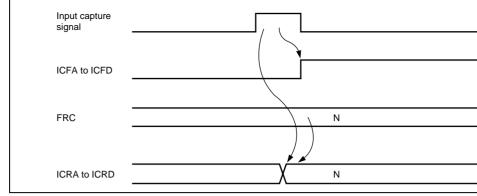

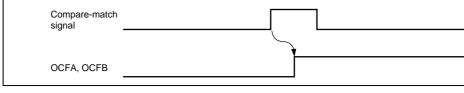

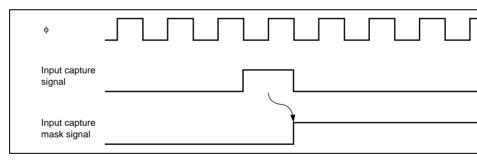

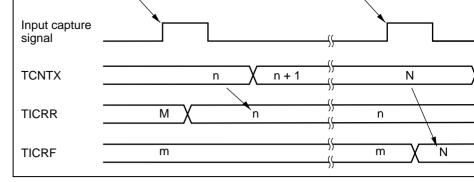

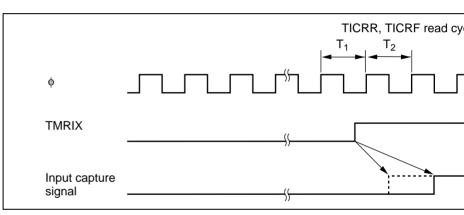

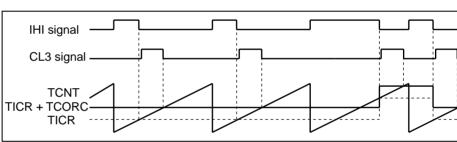

| 12.7 Input Capture                                                   | 307           | Figure 12.11 amended                                          |

| Operation                                                            |               | · 7                                                           |

| Figure 12.11 Timing of Input Capture Operation                       |               | TMRIX                                                         |

| Ореганоп                                                             |               | Input capture signal                                          |

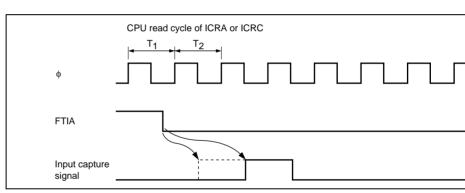

| Figure 12.12 Timing of Input Capture Signal (Input capture signal is | 307           | Figure 12.12 amended  TICRR, TICRI T1 T2                      |

| input during TICRR<br>and TICRF read)                                |               |                                                               |

|                                                                      |               | TMRIX                                                         |

|                                                                      |               | Input capture signal                                          |

|                                                                      |               | Rev. 3.00 Mar 21, 20                                          |

|                                                                      |               | RENESAS                                                       |

199

• P80/HA0/<u>PME</u>\*3

Rev. 3.00 Mar 21, 2006 page xii of liv

Rev. 3.00 Mar 21, 2006

Rev. 3.00 Mar 21, 2006 page xiv of liv

487, 488

Description added

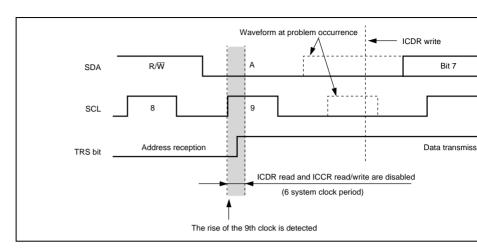

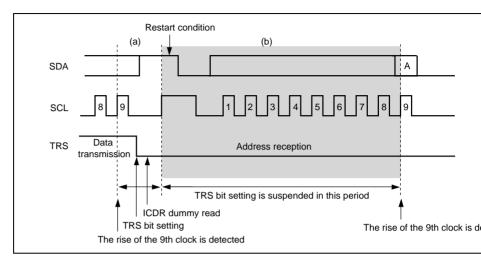

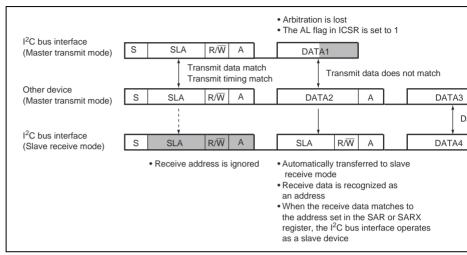

14. Notes on Arbitration Lost in Master Mode

| 19.4.4 Hos                               | st Interface | 569                      | Table 19.      | 5 ame   | ended             |          |             |                              |

|------------------------------------------|--------------|--------------------------|----------------|---------|-------------------|----------|-------------|------------------------------|

| Shutdown F (LPCPD)                       | unction      |                          | Abbreviation   | Port    | Scope o<br>Shutdo |          | No          |                              |

| Table 40.5                               | C            |                          | CLKRUN         | P82     | 0                 | Input    | Hi-         | Z                            |

| Table 19.5<br>Host Interface<br>Shutdown | •            |                          | <u> </u>       | P83     | ×                 | Input    | Ne          | eded to clear shutdo         |

| Section 22                               | RAM          | 601                      | Masked R       | NOS     | version de        | eleted   |             |                              |

|                                          |              | Product Classification R |                |         | RAM Capac         | itance   | RAM Address |                              |

|                                          |              |                          | Flash memory v | version | H8S/2161B         | 4 kbytes |             | H'E080-H'EFFF,               |

|                                          |              |                          |                |         | H8S/2160B         | 4 kbytes |             | H'E080-H'EFFF,               |

|                                          |              |                          |                |         | H8S/2141B         | 4 kbytes |             | H'E080-H'EFFF,               |

|                                          |              |                          |                |         | H8S/2140B         | 4 kbytes |             | H'E080-H'EFFF,               |

|                                          |              |                          |                |         | H8S/2145B         | 8 kbytes |             | H'D080-H'EFFF,               |

|                                          |              |                          |                |         | H8S/2148B         | 4 kbytes |             | H'E080-H'EFFF,               |

| Castian 22                               | DOM          | 602                      | Dogorintic     |         | andad             |          |             |                              |

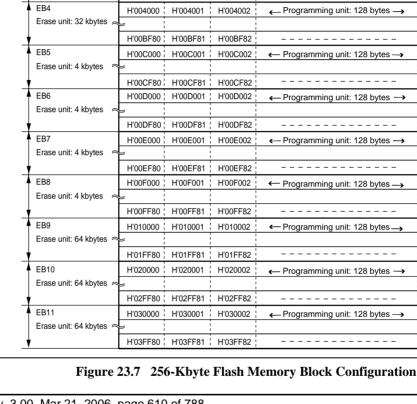

| Section 23                               | ROM          | 603                      | Description    | n am    | ienaea            |          |             |                              |

|                                          |              |                          | ` /            | ROM).   |                   |          |             | 1 (flash mem<br>has an on-ch |

Rev. 3.00 Mar 21, 2006

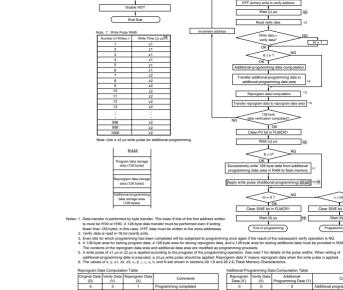

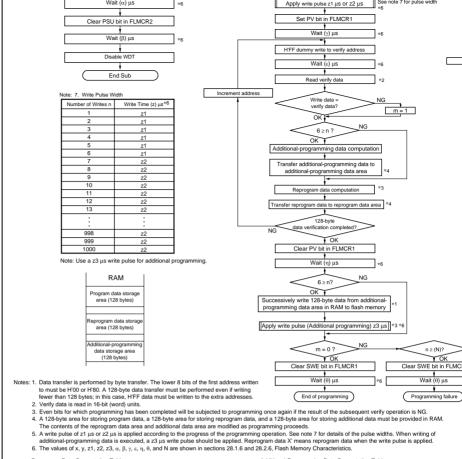

| gram Da         | ita Computat                | ion Table             |                                   |  | Additional-Pro         | gramming De        | ata Computation Table               |                    |  |

|-----------------|-----------------------------|-----------------------|-----------------------------------|--|------------------------|--------------------|-------------------------------------|--------------------|--|

| nal Data<br>(D) | Verify Data<br>(V)          | Reprogram Data<br>(X) | Comments                          |  | Reprogram<br>Data (X') | Verify Data<br>(V) | Additional-<br>Programming Data (Y) | Co                 |  |

| 0               | 0                           | - 1                   | Programming completed             |  | 0                      | 0                  | 0                                   | Additional program |  |

| 0               | - 1                         | 0                     | Programming incomplete; reprogram |  | 0                      | - 1                | 1                                   | Additional program |  |

| 1               | 0                           | - 1                   |                                   |  | - 1                    | 0                  | 1                                   |                    |  |

| 1               | 1                           | - 1                   | Still in erased state; no action  |  | - 1                    | 1                  | 1                                   | Additional program |  |

|                 |                             |                       |                                   |  |                        |                    |                                     |                    |  |

| tio             | ion of "Masked ROM" deleted |                       |                                   |  |                        |                    |                                     |                    |  |

### Secti

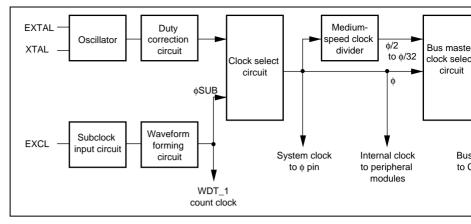

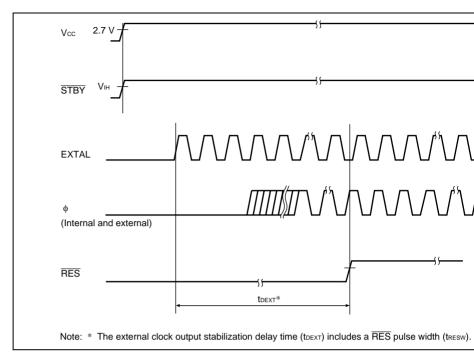

| Section 24 Clock Pulse Generator Figure 24.1 Block Diagram of Clock Pulse Generator | 633 | Figure 24.1 amended (Before) $\phi$ 2 to $\phi$ 32                      |

|-------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------|

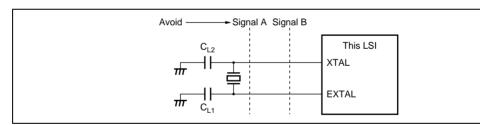

| 24.5 Subclock Input<br>Circuit                                                      | 639 | Description of "When Subclock Is Not Needed" and 'Subclock Usage" added |

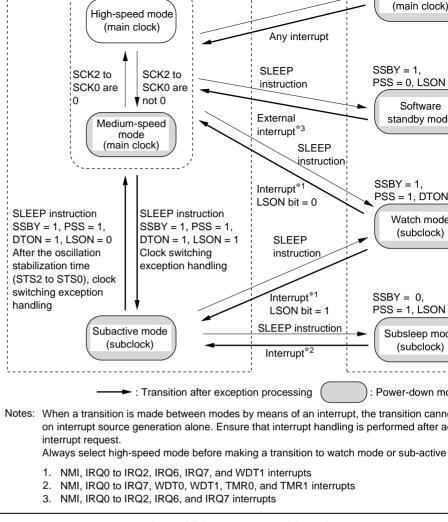

| 25.1.1 Standby<br>Control Register<br>(SBYCR)                                       | 643 | Table amended SCK2 to SCK0 must be cleared to B'000.                    |

Rev. 3.00 Mar 21, 2006 page xvi of liv

| 26.3 Register States      | 688 | Note 2 amended                                           |

|---------------------------|-----|----------------------------------------------------------|

| in Each Operating<br>Mode |     | Note: 2. Not supported by the H8S/2148B and H8 version). |

| 26.4 Register Select      | 690 | Table amended                                            |

| Conditions                |     | H8S/2160B, H8S/2161B Register Select Condition           |

|                           |     | (Before) $\longrightarrow$ (After) No condition          |

| 27.1.1 Absolute           | 701 | Table 27.1 amended                                       |

| Maximum Ratings           |     | item                                                     |

| Table 27.1 Absolute       |     | (Ports C to G are added in the H8S/2160B and H8          |

| Maximum Ratings           |     | input voltage (P97, P86, P52, P42)                       |

| 27.1.2 DC                 | 703 | Table 27.2 amended                                       |

| Characteristics           |     | Item                                                     |

| Table 27.2 DC             |     | P97, P86, P52, P42                                       |

| Characteristics (1)       |     | (Ports C to G are added in the H8S/2160B and H8          |

Note 5 amended

Note: 5. Not supported by the H8S/2148B and H8S

679

Oldel)

26.2 Register Bits

Rev. 3.00 Mar 21, 2006 p

|                                                            |     |                          | a retention char<br>ne specification                 |                                   |                                                                           |       |                                              | •   |

|------------------------------------------------------------|-----|--------------------------|------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------|-------|----------------------------------------------|-----|

| 27.2.2 DC<br>Characteristics                               | 736 | Table 2                  | 7.17 (5) amend                                       | ed                                |                                                                           |       |                                              |     |

| T-bl- 27 47 DC                                             |     |                          | Item                                                 | Symbol                            | Min                                                                       | Тур   | Max                                          | Uni |

| Table 27.17 DC<br>Characteristics (5)                      |     | Schmitt<br>trigger input |                                                      | V <sub>T</sub>                    | $V_{\rm cc} \times 0.2$<br>$V_{\rm cc} B \times 0.2$                      | _     | _                                            | V   |

|                                                            |     | voltage                  | KIN15 to KIN8***,<br>IRQ2 to IRQ0*3,<br>IRQ5 to IRQ3 | $V_{\scriptscriptstyle T}^{\; *}$ | _                                                                         | _     | $V_{cc} \times 0.7$<br>$V_{cc} B \times 0.7$ |     |

|                                                            |     |                          | Ingo to Ingo                                         | $V_T^+ - V_T^-$                   | $\begin{array}{c} V_{cc} \times 0.05 \\ V_{cc} B \times 0.05 \end{array}$ | _     | _                                            | L   |

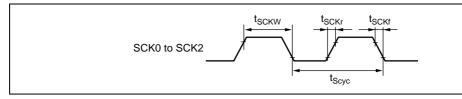

| 27.2.3 AC                                                  | 752 | Table 2                  | 7.23 (1) amend                                       | ed                                |                                                                           |       |                                              |     |

| Characteristics                                            |     | (Before)                 | $t_{cscvc} \rightarrow (After)$                      | tsove                             |                                                                           |       |                                              |     |

| Table 27.23 Timing of<br>On-Chip Peripheral<br>Modules (1) |     | ,                        | Cacyo                                                | 55,6                              |                                                                           |       |                                              |     |

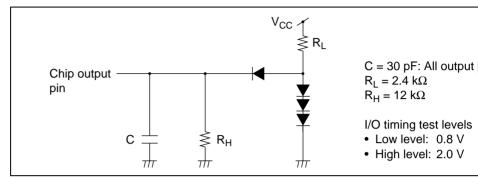

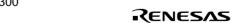

| 27.2.7 Usage Notes                                         | 761 | Figure 2                 | 27.5 amended                                         |                                   |                                                                           |       |                                              |     |

| Figure 27.5                                                |     | < Produ                  | ct with internal                                     | step-d                            | own fund                                                                  | ction | ۱ >                                          |     |

| Connection of VCL                                          |     | HD64F2                   | 2145B                                                |                                   |                                                                           |       |                                              |     |

| Capacitor                                                  |     | HD64F2                   | 2148B                                                |                                   |                                                                           |       |                                              |     |

minimum value).

are guaranteed after rewriting (Guarantee range is 1

9. Reference value for 25°C (as a guideline, rewriting normally function up to this value).

Rev. 3.00 Mar 21, 2006 page xviii of liv

|                                                      |         |     | ф            |                      | $\bigcup^* \bigcup \bigcup^* \bigcup^* \bigcup^* \bigcup^* \bigcup^* \bigcup^* \bigcup^* \bigcup^* \bigcup^$ | \\\\\-\ <u>\</u> | -(1111)]           |

|------------------------------------------------------|---------|-----|--------------|----------------------|--------------------------------------------------------------------------------------------------------------|------------------|--------------------|

| Appendix B                                           | Product | 779 | Table ar     | nended               |                                                                                                              |                  |                    |

| Codes                                                |         |     | Product Type |                      | Product Code                                                                                                 | Mark Code        | Package<br>(Packag |

|                                                      |         |     | H8S/2145B    | Flash memory version | HD64F2145BV                                                                                                  | F2145BVFA10      | 100-pin (          |

|                                                      |         |     |              | (3-V version)        |                                                                                                              | F2145BVTE10      | 100-pin 7          |

|                                                      |         |     |              | Flash memory version | HD64F2145B                                                                                                   | F2145BFA20       | 100-pin (          |

|                                                      |         |     |              | (5-V version)        |                                                                                                              | F2145BTE20       | 100-pin 7          |

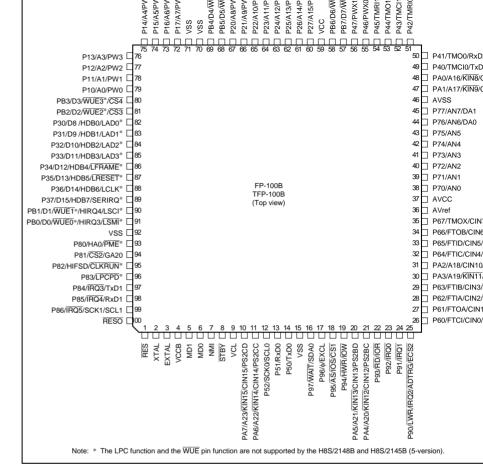

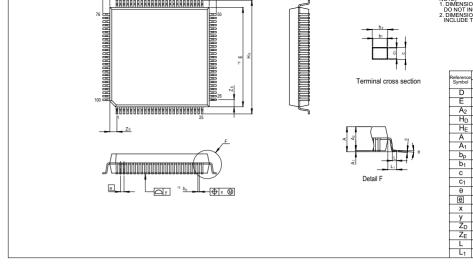

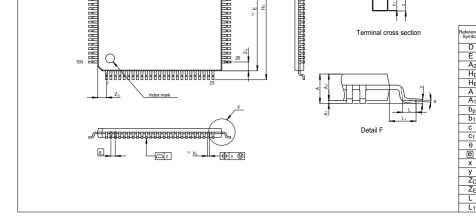

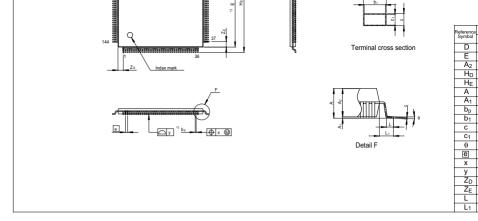

| Appendix C<br>Dimensions<br>Figure C.1<br>Dimensions | Package | 780 | Figure re    | eplaced              |                                                                                                              |                  |                    |

| Figure C.2<br>Dimensions<br>(TFP-100B)               | Package | 781 | Figure re    | eplaced              |                                                                                                              |                  |                    |

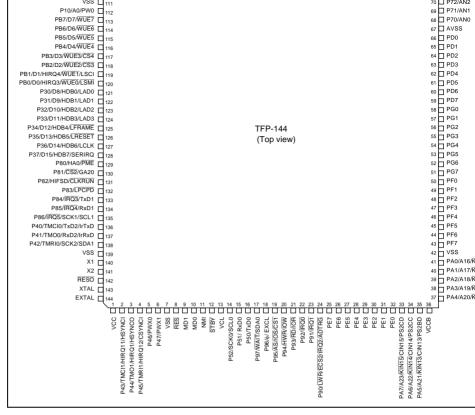

| Figure C.3<br>Dimensions                             | •       | 782 | Figure re    | eplaced              |                                                                                                              |                  |                    |

RES

Rev. 3.00 Mar 21, 2006 |

Rev. 3.00 Mar 21, 2006 page xx of liv

RENESAS

| Secti | on 2    | CPU                                                              |

|-------|---------|------------------------------------------------------------------|

| 2.1   | Featur  | es                                                               |

|       | 2.1.1   | Differences between H8S/2600 CPU and H8S/2000 CPU                |

|       | 2.1.2   | Differences from H8/300 CPU                                      |

|       | 2.1.3   | Differences from H8/300H CPU                                     |

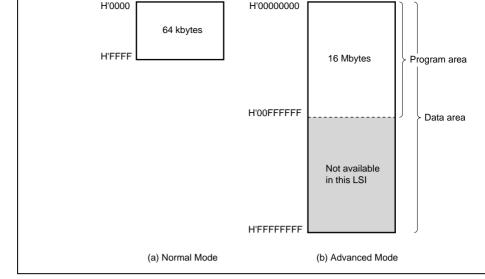

| 2.2   | CPU (   | Operating Modes                                                  |

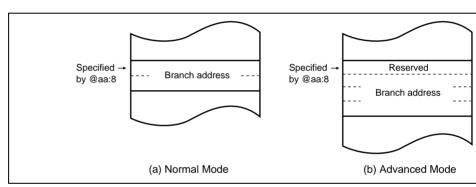

|       | 2.2.1   | Normal Mode                                                      |

|       | 2.2.2   | Advanced Mode                                                    |

| 2.3   | Addre   | ss Space                                                         |

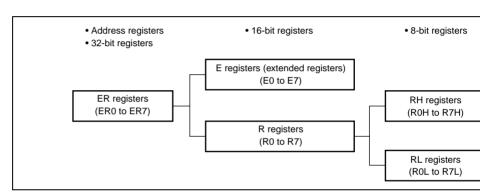

| 2.4   | Regist  | er Configuration                                                 |

|       | 2.4.1   | General Registers                                                |

|       | 2.4.2   | Program Counter (PC)                                             |

|       | 2.4.3   | Extended Control Register (EXR)                                  |

|       | 2.4.4   | Condition-Code Register (CCR)                                    |

|       | 2.4.5   | Initial Register Values                                          |

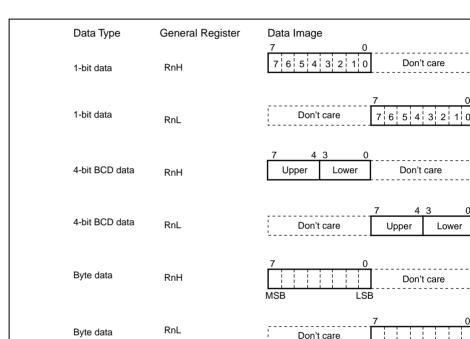

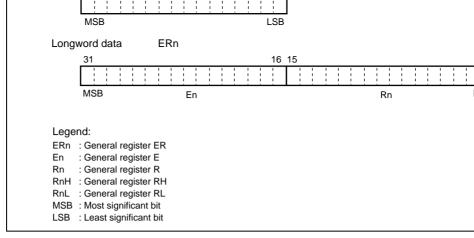

| 2.5   | Data F  | Formats                                                          |

|       | 2.5.1   | General Register Data Formats                                    |

|       | 2.5.2   | Memory Data Formats                                              |

| 2.6   | Instruc | ction Set                                                        |

|       | 2.6.1   | Table of Instructions Classified by Function                     |

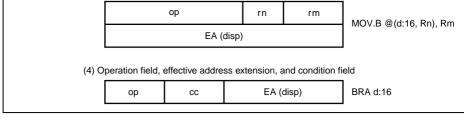

|       | 2.6.2   | Basic Instruction Formats                                        |

| 2.7   | Addre   | ssing Modes and Effective Address Calculation                    |

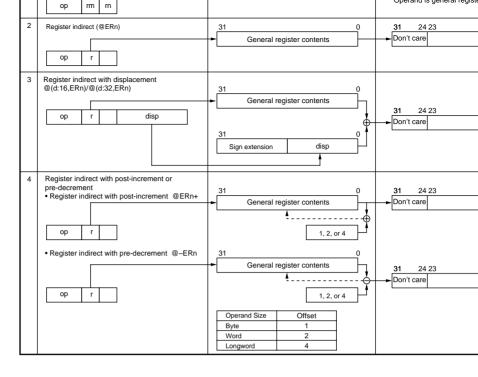

|       | 2.7.1   | Register Direct—Rn                                               |

|       | 2.7.2   | Register Indirect—@ERn                                           |

|       | 2.7.3   | Register Indirect with Displacement—@(d:16, ERn) or @(d:32, ERn) |

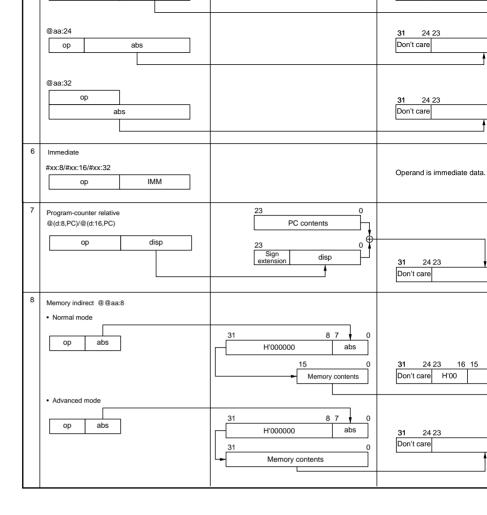

|       | 2.7.4   | Register Indirect with Post-Increment or Pre-Decrement—@ERn+ or  |

|       | 2.7.5   | Absolute Address—@aa:8, @aa:16, @aa:24, or @aa:32                |

|       |         |                                                                  |

1.3.3

2.7.6

2.7.7

1.5.2 Fill Fullctions in Each Operating Wode ..... Pin Functions .....

Rev. 3.00 Mar 21, 2006 |

Immediate—#xx:8, #xx:16, or #xx:32.....

Program-Counter Relative—@(d:8, PC) or @(d:16, PC).....

| 3.1   | MCU Operating Mode Selection                                         |

|-------|----------------------------------------------------------------------|

| 3.2   | Register Descriptions                                                |

|       | 3.2.1 Mode Control Register (MDCR)                                   |

|       | 3.2.2 System Control Register (SYSCR)                                |

|       | 3.2.3 Serial Timer Control Register (STCR)                           |

| 3.3   | Operating Mode Descriptions                                          |

|       | 3.3.1 Mode 1                                                         |

|       | 3.3.2 Mode 2                                                         |

|       | 3.3.3 Mode 3                                                         |

|       | 3.3.4 Pin Functions in Each Operating Mode                           |

| 3.4   | Address Map in Each Operating Mode                                   |

|       |                                                                      |

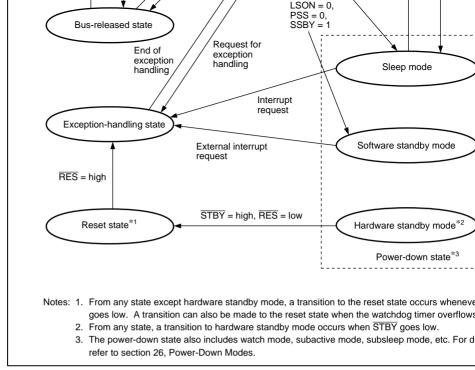

| Secti | on 4 Exception Handling                                              |

| 4.1   | Exception Handling Types and Priority                                |

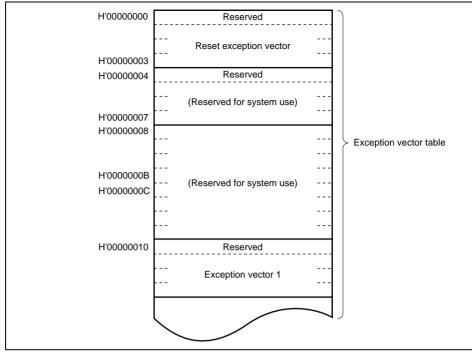

| 4.2   | Exception Sources and Exception Vector Table                         |

| 4.3   | Reset                                                                |

|       | 4.3.1 Reset Exception Handling                                       |

|       | 4.3.2 Interrupts after Reset                                         |

|       | 4.3.3 On-Chip Peripheral Modules after Reset Is Cancelled            |

| 4.4   | Interrupt Exception Handling                                         |

| 4.5   | Trap Instruction Exception Handling                                  |

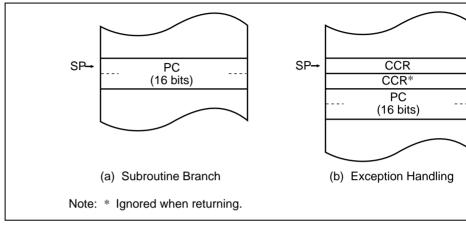

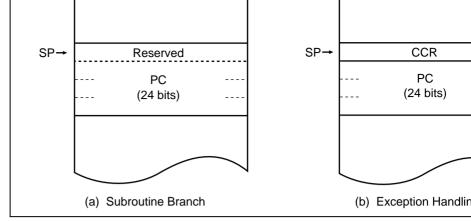

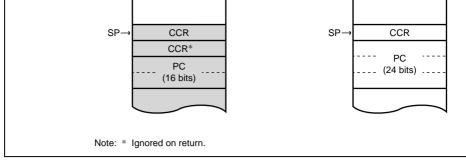

| 4.6   | Stack Status after Exception Handling                                |

| 4.7   | Usage Note                                                           |

|       | 3.2<br>3.3<br>3.4<br>Secti<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 |

Section 3 MCU Operating Modes .....

Rev. 3.00 Mar 21, 2006 page xxii of liv

5.15.2

5.3

5.3.1

5.3.25.3.3

RENESAS

Input/Output Pins .....

Register Descriptions

Interrupt Control Registers A to C (ICRA to ICRC).....

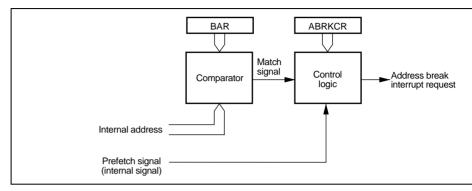

Address Break Control Register (ABRKCR).....

Break Address Registers A to C (BARA to BARC).....

| 5.7   | Addre  | ss Break                                            |

|-------|--------|-----------------------------------------------------|

|       | 5.7.1  | Features                                            |

|       | 5.7.2  | Block Diagram                                       |

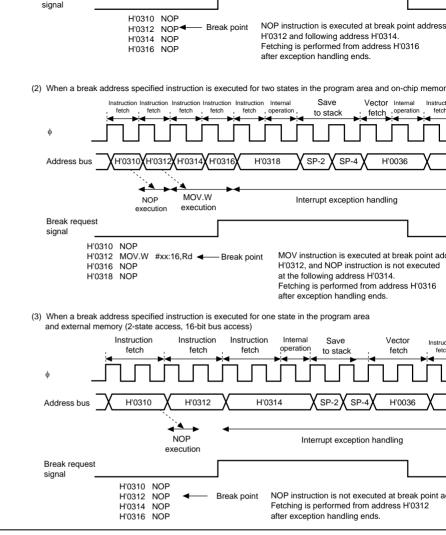

|       | 5.7.3  | Operation                                           |

|       | 5.7.4  | Usage Notes                                         |

| 5.8   | Usage  | Notes                                               |

|       | 5.8.1  | Conflict between Interrupt Generation and Disabling |

|       | 5.8.2  | Instructions that Disable Interrupts                |

|       | 5.8.3  | Interrupts during Execution of EEPMOV Instruction   |

|       | 5.8.4  | Setting on Product Incorporating DTC                |

|       | 5.8.5  | IRQ Status Register (ISR)                           |

|       |        |                                                     |

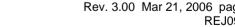

| Secti | ion 6  | Bus Controller (BSC)                                |

| 6.1   | Featur | es                                                  |

| 6.2   | Input/ | Output Pins                                         |

| 6.3   | Regist | er Descriptions                                     |

|       | 6.3.1  | Bus Control Register (BCR)                          |

|       | 6.3.2  | Wait State Control Register (WSCR)                  |

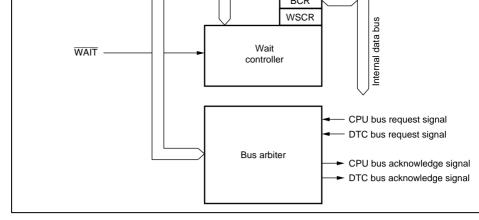

| 6.4   | Bus C  | ontrol                                              |

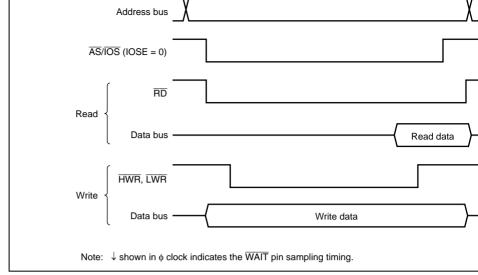

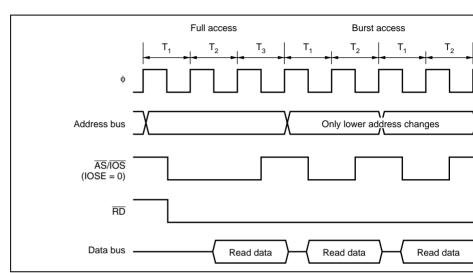

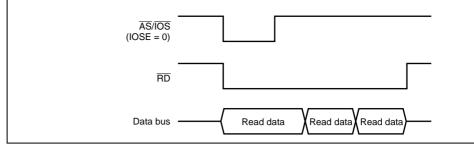

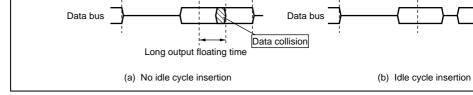

|       | 6.4.1  | Bus Specifications                                  |

|       | 6.4.2  | Advanced Mode                                       |

|       | 6.4.3  | Normal Mode                                         |

|       | 6.4.4  | I/O Select Signals                                  |

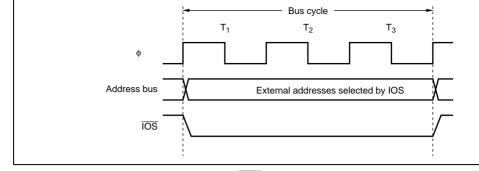

| 6.5   | Basic  | Bus Interface                                       |

|       | 6.5.1  | Data Size and Data Alignment                        |

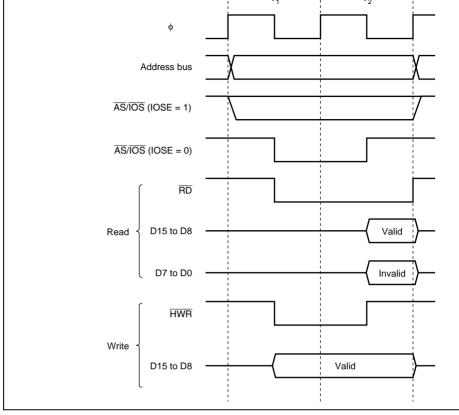

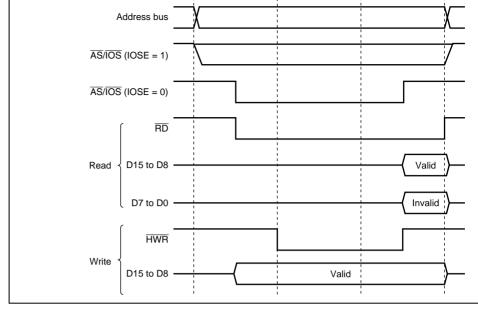

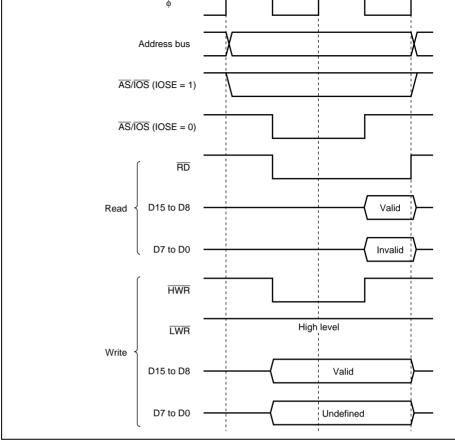

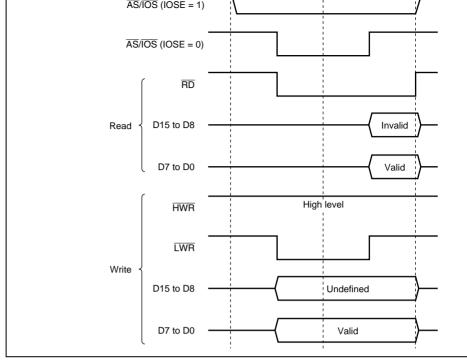

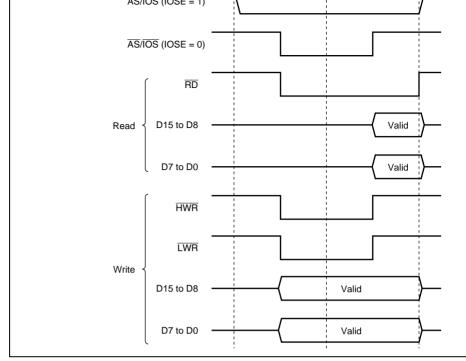

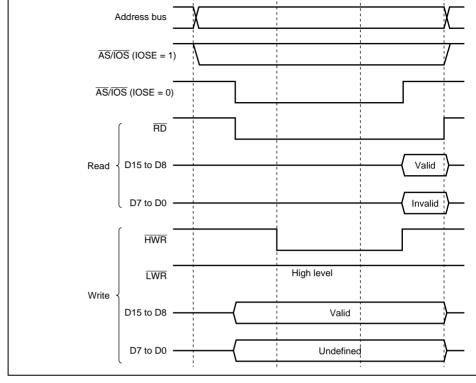

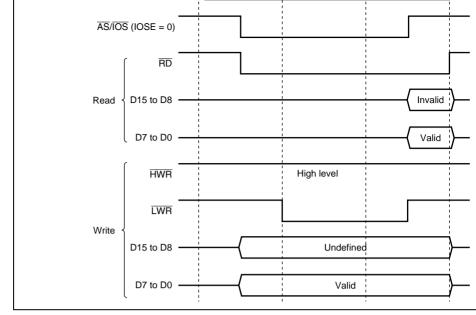

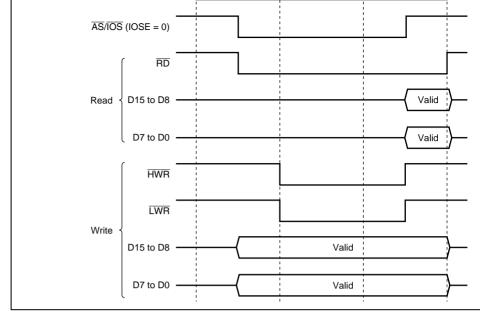

|       | 6.5.2  | Valid Strobes                                       |

|       |        | Rev. 3.00 Mar 21, 2006 pa                           |

|       |        | _                                                   |

|       |        | RENESAS                                             |

|       |        |                                                     |

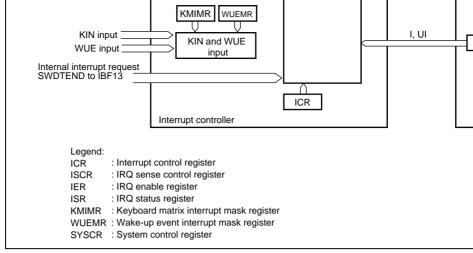

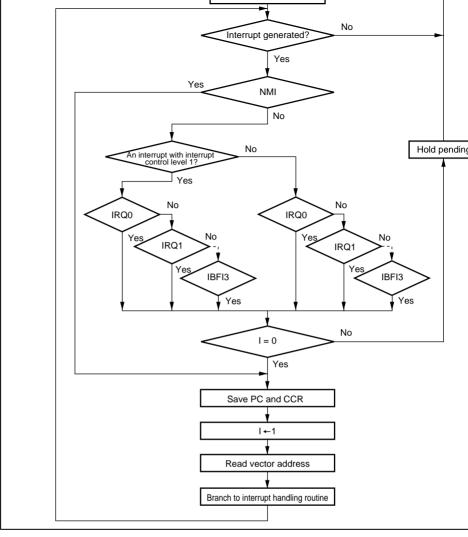

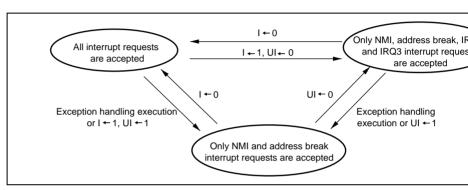

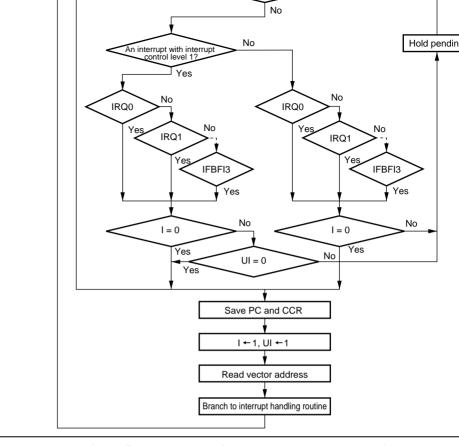

Interrupt Control Modes and Interrupt Operation.....

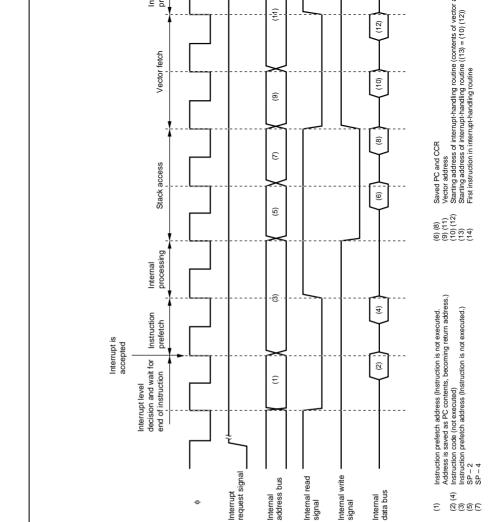

Interrupt Exception Handling Sequence .....

Interrupt Response Times .....

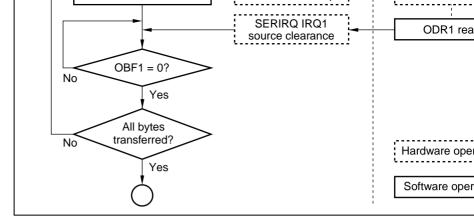

DTC Activation by Interrupt.....

5.6

5.6.1

5.6.2 5.6.3

5.6.4

5.6.5

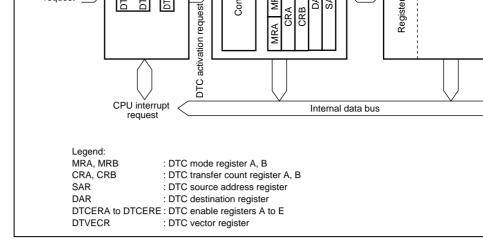

| /.1 | reatures  |                                                 |  |  |  |  |

|-----|-----------|-------------------------------------------------|--|--|--|--|

| 7.2 | Registe   | er Descriptions                                 |  |  |  |  |

|     | 7.2.1     | DTC Mode Register A (MRA)                       |  |  |  |  |

|     | 7.2.2     | DTC Mode Register B (MRB)                       |  |  |  |  |

|     | 7.2.3     | DTC Source Address Register (SAR)               |  |  |  |  |

|     | 7.2.4     | DTC Destination Address Register (DAR)          |  |  |  |  |

|     | 7.2.5     | DTC Transfer Count Register A (CRA)             |  |  |  |  |

|     | 7.2.6     | DTC Transfer Count Register B (CRB)             |  |  |  |  |

|     | 7.2.7     | DTC Enable Registers (DTCER)                    |  |  |  |  |

|     | 7.2.8     | DTC Vector Register (DTVECR)                    |  |  |  |  |

| 7.3 | Activa    | tion Sources                                    |  |  |  |  |

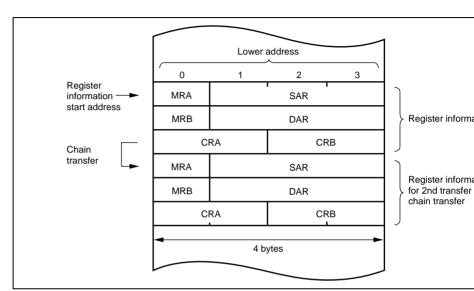

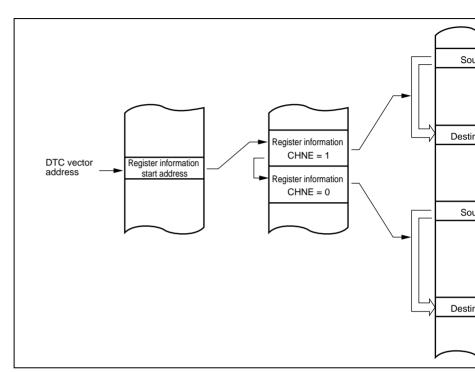

| 7.4 | Locati    | on of Register Information and DTC Vector Table |  |  |  |  |

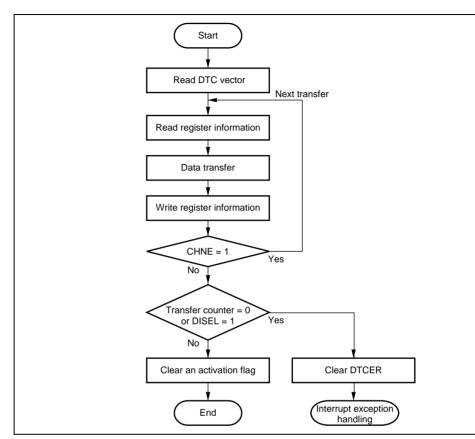

| 7.5 | Operation |                                                 |  |  |  |  |

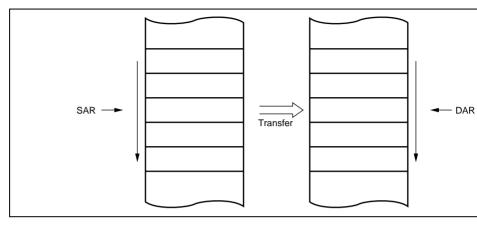

|     | 7.5.1     | Normal Mode                                     |  |  |  |  |

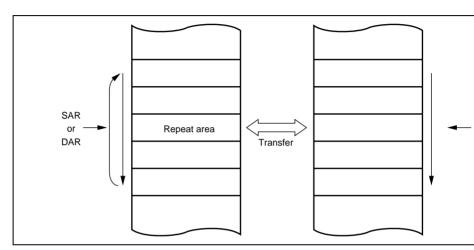

|     | 7.5.2     | Repeat Mode                                     |  |  |  |  |

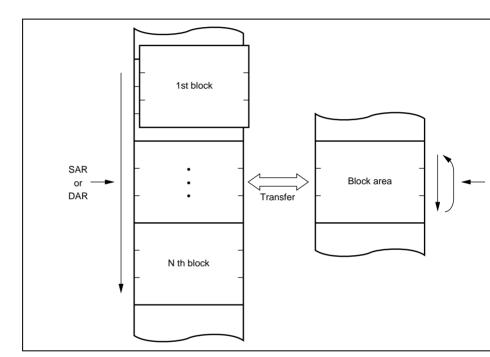

|     | 7.5.3     | Block Transfer Mode                             |  |  |  |  |

|     | 7.5.4     | Chain Transfer                                  |  |  |  |  |

|     | 7.5.5     | Interrupts                                      |  |  |  |  |

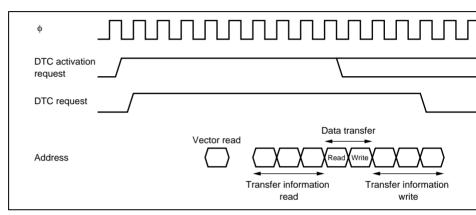

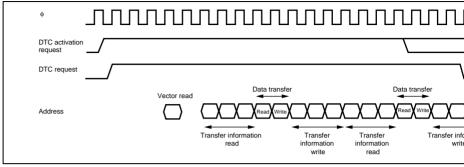

|     | 7.5.6     | Operation Timing                                |  |  |  |  |

|     | 7.5.7     | Number of DTC Execution States                  |  |  |  |  |

| 7.6 | Proced    | lures for Using DTC                             |  |  |  |  |

|     | 7.6.1     | Activation by Interrupt                         |  |  |  |  |

|     | 7.6.2     | Activation by Software                          |  |  |  |  |

| 7.7 | Examp     | oles of Use of DTC                              |  |  |  |  |

|     | 7.7.1     | Normal Mode                                     |  |  |  |  |

|     | 7.7.2     | Software Activation                             |  |  |  |  |

| 7.8 | Usage     | Notes                                           |  |  |  |  |

Section 7 Data Transfer Controller (DTC).....

Rev. 3.00 Mar 21, 2006 page xxiv of liv

7.8.1

7.8.2

7.8.3

Module Stop Mode Setting .....

On-Chip RAM

DTCE Bit Setting.....

|     | 8.3.3   | Port 2 Pull-Up MOS Control Register (P2PCR) |

|-----|---------|---------------------------------------------|

|     | 8.3.4   | Pin Functions                               |

|     | 8.3.5   | Port 2 Input Pull-Up MOS                    |

| 8.4 | Port 3  |                                             |

|     | 8.4.1   | Port 3 Data Direction Register (P3DDR)      |

|     | 8.4.2   | Port 3 Data Register (P3DR)                 |

|     | 8.4.3   | Port 3 Pull-Up MOS Control Register (P3PCR) |

|     | 8.4.4   | Pin Functions                               |

|     | 8.4.5   | Port 3 Input Pull-Up MOS                    |

| 8.5 | Port 4  |                                             |

|     | 8.5.1   | Port 4 Data Direction Register (P4DDR)      |

|     | 8.5.2   | Port 4 Data Register (P4DR)                 |

|     | 8.5.3   | Pin Functions                               |

| 8.6 | Port 5  |                                             |

|     | 8.6.1   | Port 5 Data Direction Register (P5DDR)      |

|     | 8.6.2   | Port 5 Data Register (P5DR)                 |

|     | 8.6.3   | Pin Functions                               |

| 8.7 | Port 6. |                                             |

|     | 8.7.1   | Port 6 Data Direction Register (P6DDR)      |

|     | 8.7.2   | Port 6 Data Register (P6DR)                 |

|     | 8.7.3   | Port 6 Pull-Up MOS Control Register (KMPCR) |

|     | 8.7.4   | Pin Functions                               |

|     | 8.7.5   | Port 6 Input Pull-Up MOS                    |

| 8.8 | Port 7  |                                             |

|     | 8.8.1   | Port 7 Input Data Register (P7PIN)          |

|     | 8.8.2   | Pin Functions                               |

|     |         |                                             |

|     |         | Rev. 3.00 Mar 21, 2006 p                    |

|     |         | Nev. 3.00 Mai 21, 2000 p                    |

|     |         | RENESAS                                     |

Pin Functions

Port 1 Input Pull-Up MOS .....

Port 2 Data Direction Register (P2DDR).....

Port 2 Data Register (P2DR).....

Port 2

8.2.4

8.2.5

8.3.1

8.3.2

8.3

|      | 0.12.1 Told B Butta Birection Register (1 BBBR)                   |

|------|-------------------------------------------------------------------|

|      | 8.12.2 Port B Output Data Register (PBODR)                        |

|      | 8.12.3 Port B Input Data Register (PBPIN)                         |

|      | 8.12.4 Pin Functions                                              |

|      | 8.12.5 Port B Input Pull-Up MOS                                   |

| 8.13 | Additional Overview for H8S/2160B and H8S/2161B                   |

| 8.14 | Ports C, D                                                        |

|      | 8.14.1 Port C and Port D Data Direction Registers (PCDDR, PDDDR)  |

|      | 8.14.2 Port C and Port D Output Data Registers (PCODR, PDODR)     |

|      | 8.14.3 Port C and Port D Input Data Registers (PCPIN, PDPIN)      |

|      | 8.14.4 Port C and Port D Nch-OD Control Register (PCNOCR, PDNOCR) |

|      | 8.14.5 Pin Functions                                              |

|      | 8.14.6 Input Pull-Up MOS in Ports C and D                         |

| 8.15 | Ports E, F.                                                       |

|      | 8.15.1 Port E and Port F Data Direction Registers (PEDDR, PFDDR)  |

|      | 8.15.2 Port E and Port F Output Data Registers (PEODR, PFODR)     |

|      | 8.15.3 Port E and Port F Input Data Registers (PEPIN, PFPIN)      |

|      | 8.15.4 Port E and Port F Nch-OD Control Register (PENOCR, PFNOCR) |

|      | 8.15.5 Pin Functions                                              |

|      | 8.15.6 Input Pull-Up MOS in Ports E and F                         |

| 8.16 | Port G                                                            |

|      | 8.16.1 Port G Data Direction Register (PGDDR)                     |

|      | 8.16.2 Port G Output Data Register (PGODR)                        |

|      | 8.16.3 Port G Input Data Register (PGPIN)                         |

|      | 8.16.4 Port G Nch-OD Control Register (PGNOCR)                    |

|      | 8.16.5 Pin Functions                                              |

|      |                                                                   |

Rev. 3.00 Mar 21, 2006 page xxvi of liv

8.11.1 Port A Data Direction Register (PADDR)..... 8.11.2 Port A Output Data Register (PAODR)..... 8.11.3 Port A Input Data Register (PAPIN)..... 8.11.4 Pin Functions 8.11.5 Port A Input Pull-Up MOS ..... 8.12 Port B ..... 8.12.1 Port B Data Direction Register (PBDDR).....

RENESAS

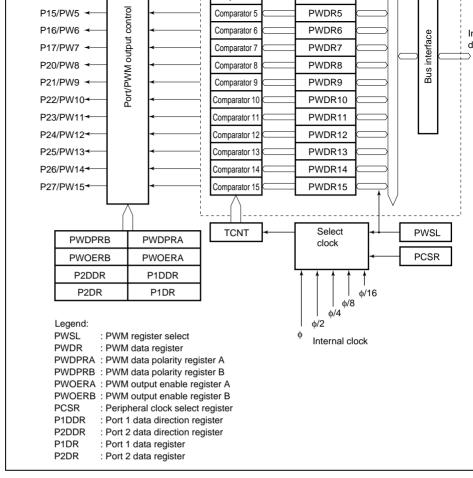

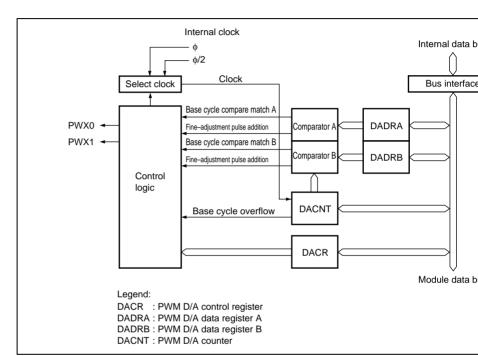

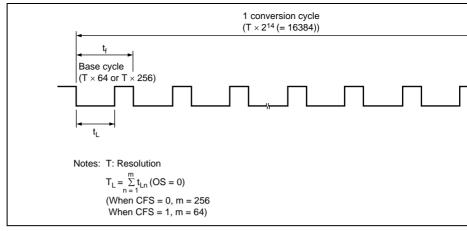

| Sect | ion 10 14-Bit PWM Timer (PWMX)                           |  |  |  |  |  |

|------|----------------------------------------------------------|--|--|--|--|--|

| 10.1 | Features                                                 |  |  |  |  |  |

| 10.2 | Input/Output Pins                                        |  |  |  |  |  |

| 10.3 | Register Descriptions                                    |  |  |  |  |  |

|      | 10.3.1 PWM (D/A) Counters H and L (DACNTH, DACNTL)       |  |  |  |  |  |

|      | 10.3.2 PWM (D/A) Data Registers A and B (DADRA, DADRB)   |  |  |  |  |  |

|      | 10.3.3 PWM (D/A) Control Register (DACR)                 |  |  |  |  |  |

| 10.4 | Bus Master Interface                                     |  |  |  |  |  |

| 10.5 | Operation                                                |  |  |  |  |  |

| 10.6 | Usage Note                                               |  |  |  |  |  |

|      | 10.6.1 Module Stop Mode Setting                          |  |  |  |  |  |

| _    |                                                          |  |  |  |  |  |

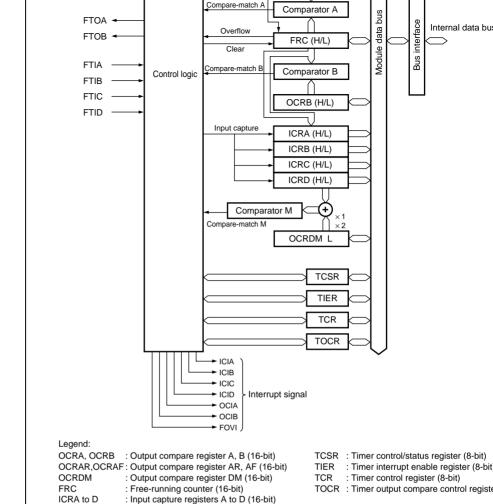

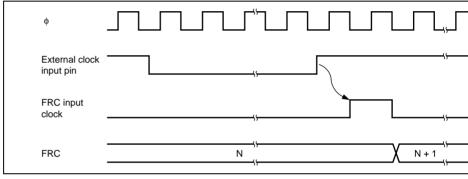

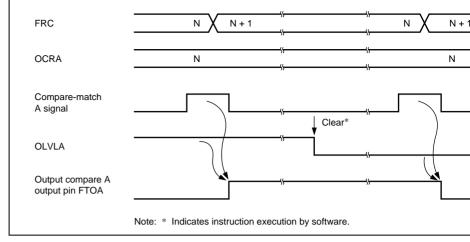

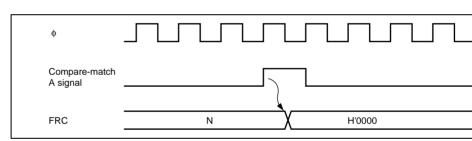

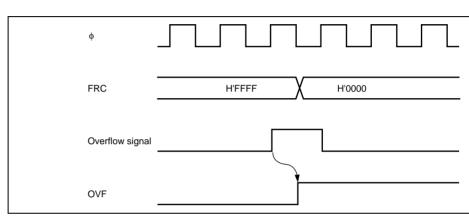

|      | ion 11 16-Bit Free-Running Timer (FRT)                   |  |  |  |  |  |

| 11.1 | Features                                                 |  |  |  |  |  |

| 11.2 | Input/Output Pins                                        |  |  |  |  |  |

| 11.3 | Register Descriptions                                    |  |  |  |  |  |

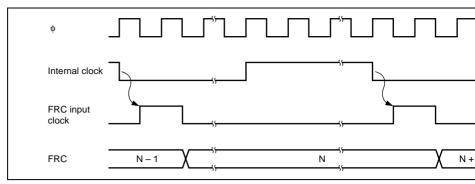

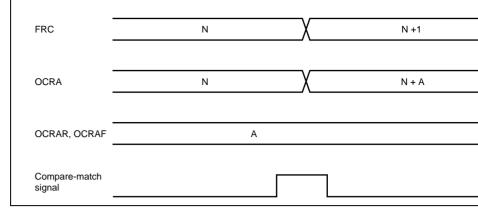

|      | 11.3.1 Free-Running Counter (FRC)                        |  |  |  |  |  |

|      | 11.3.2 Output Compare Registers A and B (OCRA, OCRB)     |  |  |  |  |  |

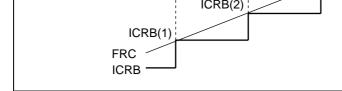

|      | 11.3.3 Input Capture Registers A to D (ICRA to ICRD)     |  |  |  |  |  |

|      | 11.3.4 Output Compare Registers AR and AF (OCRAR, OCRAF) |  |  |  |  |  |

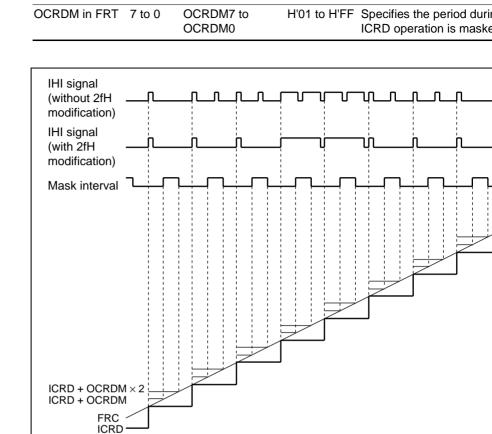

|      | 11.3.5 Output Compare Register DM (OCRDM)                |  |  |  |  |  |

|      | 11.3.6 Timer Interrupt Enable Register (TIER)            |  |  |  |  |  |

|      | 11.3.7 Timer Control/Status Register (TCSR)              |  |  |  |  |  |

|      | 11.3.8 Timer Control Register (TCR)                      |  |  |  |  |  |

|      | 11.3.9 Timer Output Compare Control Register (TOCR)      |  |  |  |  |  |

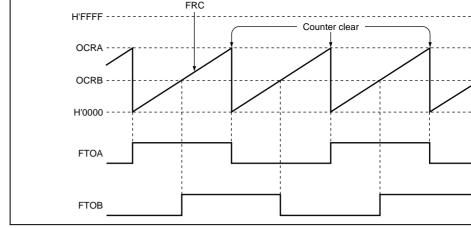

| 11.4 | Operation                                                |  |  |  |  |  |

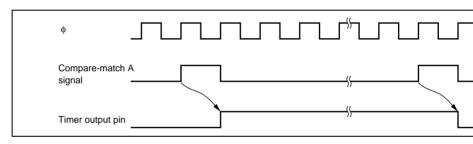

|      | 11.4.1 Pulse Output                                      |  |  |  |  |  |

| 11.5 | Operation Timing                                         |  |  |  |  |  |

|      | Rev. 3.00 Mar 21, 2006 p                                 |  |  |  |  |  |

|      | RENESAS                                                  |  |  |  |  |  |

Operation .....

Usage Note....

Module Stop Mode Setting .....

9.4

9.5

9.5.1

| 11.6 | Interrupt Sources |                                                  |  |  |  |  |

|------|-------------------|--------------------------------------------------|--|--|--|--|

| 11.7 | Usage N           | Totes                                            |  |  |  |  |

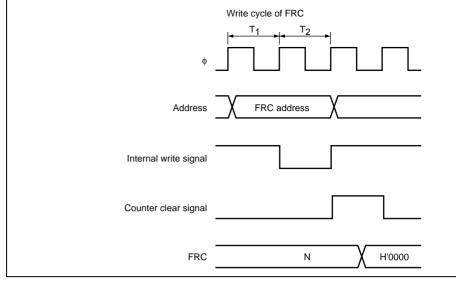

|      | 11.7.1            | Conflict between FRC Write and Clear             |  |  |  |  |

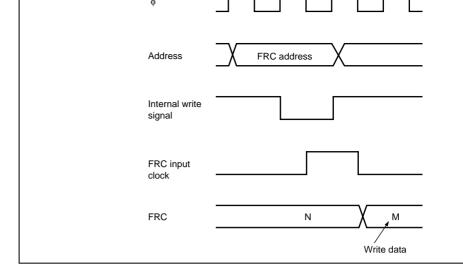

|      | 11.7.2            | Conflict between FRC Write and Increment         |  |  |  |  |

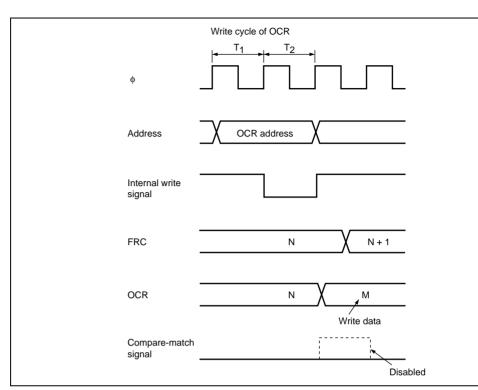

|      | 11.7.3            | Conflict between OCR Write and Compare-Match     |  |  |  |  |

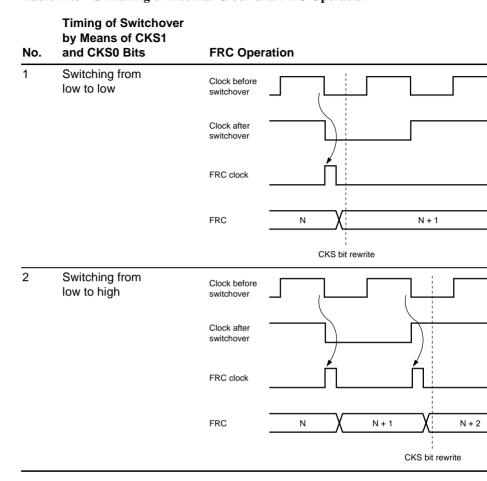

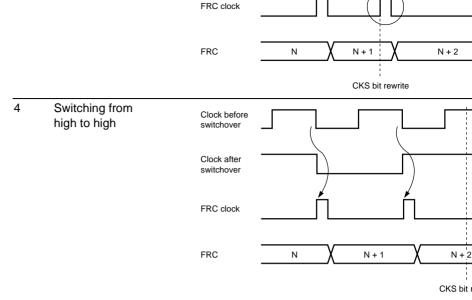

|      | 11.7.4            | Switching of Internal Clock and FRC Operation    |  |  |  |  |

|      | 11.7.5            | Module Stop Mode Setting                         |  |  |  |  |

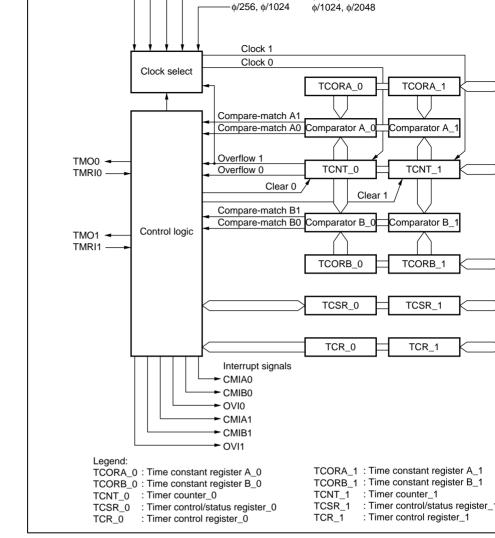

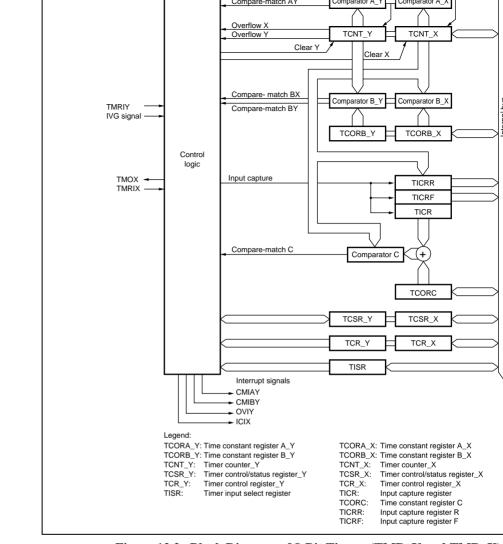

| Sect | ion 12            | 8-Bit Timer (TMR)                                |  |  |  |  |

| 12.1 | Features          |                                                  |  |  |  |  |

| 12.2 | Input/Ou          | ıtput Pins                                       |  |  |  |  |

| 12.3 | Register          | Descriptions                                     |  |  |  |  |

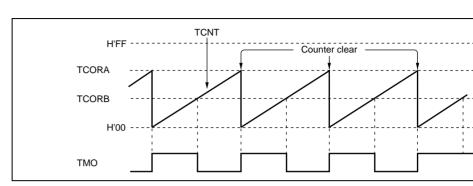

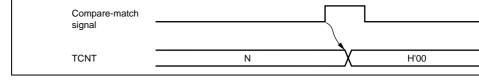

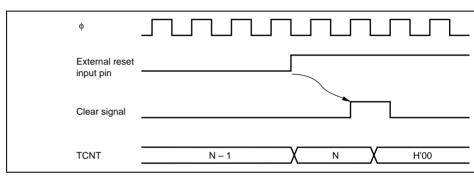

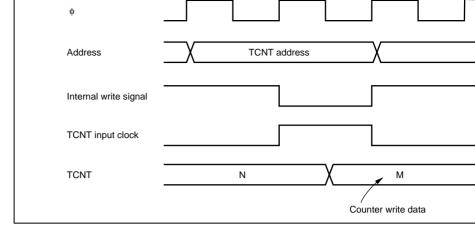

|      | 12.3.1            | Timer Counter (TCNT)                             |  |  |  |  |

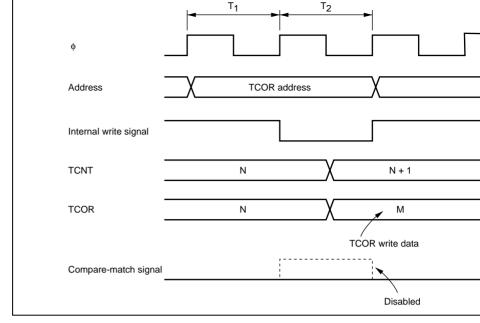

|      | 12.3.2            | Time Constant Register A (TCORA)                 |  |  |  |  |

|      | 12.3.3            | Time Constant Register B (TCORB)                 |  |  |  |  |

|      | 12.3.4            | Timer Control Register (TCR)                     |  |  |  |  |

|      | 12.3.5            | Timer Control/Status Register (TCSR)             |  |  |  |  |

|      | 12.3.6            | Input Capture Register (TICR)                    |  |  |  |  |

|      | 12.3.7            | Time Constant Register (TCORC)                   |  |  |  |  |

|      | 12.3.8            | Input Capture Registers R and F (TICRR, TICRF)   |  |  |  |  |

|      | 12.3.9            | Timer Input Select Register (TISR)               |  |  |  |  |

| 12.4 | Operatio          | on                                               |  |  |  |  |

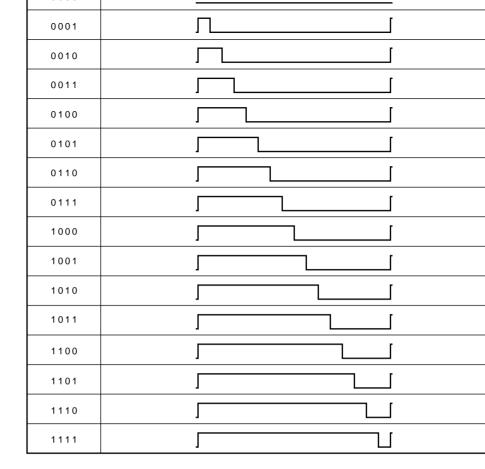

|      | 12.4.1            | Pulse Output                                     |  |  |  |  |

| 12.5 | Operatio          | on Timing                                        |  |  |  |  |

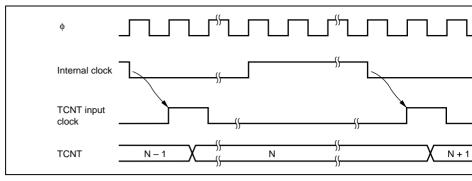

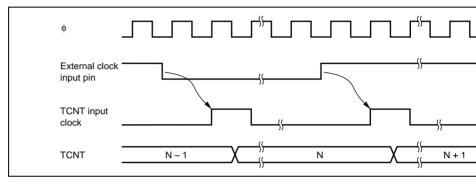

|      | 12.5.1            | TCNT Count Timing                                |  |  |  |  |

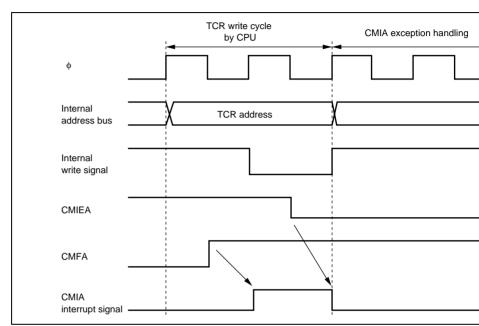

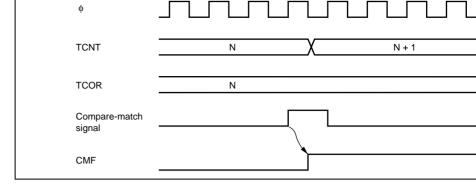

|      | 12.5.2            | Timing of CMFA and CMFB Setting at Compare-Match |  |  |  |  |

|      |                   |                                                  |  |  |  |  |

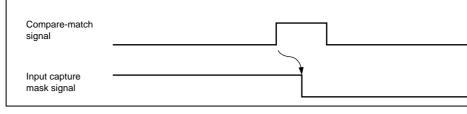

11.5.10 Mask Signal Generation Timing.....

Rev. 3.00 Mar 21, 2006 page xxviii of liv

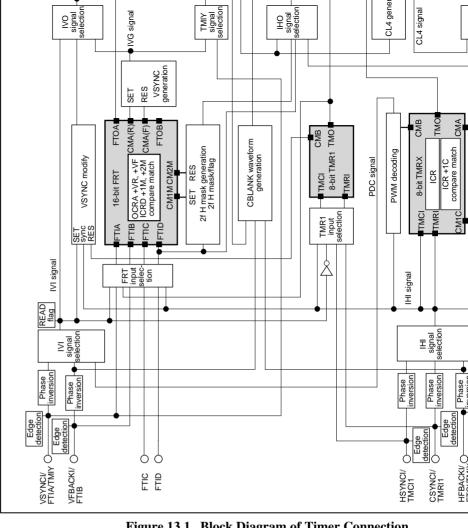

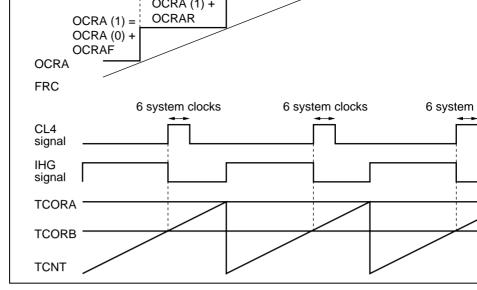

| Sect | ion 13  | Timer Connection                                               |

|------|---------|----------------------------------------------------------------|

| 13.1 | Feature | S                                                              |

| 13.2 |         | Output Pins                                                    |

| 13.3 | _       | er Descriptions                                                |

|      | 13.3.1  | Timer Connection Register I (TCONRI)                           |

|      | 13.3.2  | Timer Connection Register O (TCONRO)                           |

|      |         | Timer Connection Register S (TCONRS)                           |

|      | 13.3.4  | Edge Sense Register (SEDGR)                                    |

| 13.4 |         | ion                                                            |

|      | 13.4.1  | PWM Decoding (PDC Signal Generation)                           |

|      |         | Clamp Waveform Generation (CL1/CL2/CL3 Signal Generation)      |

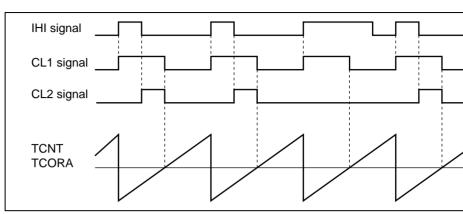

|      | 13.4.3  | Measurement of 8-Bit Timer Divided Waveform Period             |

|      | 13.4.4  | 2fH Modification of IHI Signal                                 |

|      | 13.4.5  | IVI Signal Fall Modification and IHI Synchronization           |

|      | 13.4.6  | Internal Synchronization Signal Generation (IHG/IVG/CL4 Signal |

|      |         | Generation)                                                    |

|      | 13.4.7  | HSYNCO Output                                                  |

|      | 13.4.8  | VSYNCO Output                                                  |

|      | 13.4.9  | CBLANK Output                                                  |

| 13.5 | Usage 1 | Note                                                           |

|      | 13.5.1  | Module Stop Mode Setting                                       |

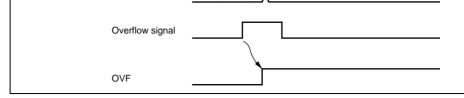

| Sect | ion 14  | Watchdog Timer (WDT)                                           |

| 14.1 |         | es                                                             |

| 14.2 |         | Output Pins                                                    |

| 14.3 |         | er Descriptions                                                |

| 14.5 | _       | Timer Counter (TCNT)                                           |

|      |         | Timer Control/Status Register (TCSR)                           |

|      | 11.3.2  | Timer Condon States Register (TCSR)                            |

|      |         | Rev. 3.00 Mar 21, 2006 pa                                      |

|      |         |                                                                |

12.9.5 Switching of Internal Clocks and TCNT Operation.

12.9.6 Mode Setting with Cascaded Connection.

12.9.7 Module Stop Mode Setting.

|      | 14.6.4                                | Switching between Watchdog Timer Mode and Interval Timer Mode     |  |  |  |  |

|------|---------------------------------------|-------------------------------------------------------------------|--|--|--|--|

|      | 14.6.5                                | System Reset by RESO Signal                                       |  |  |  |  |

|      | 14.6.6                                | Counter Values during Transitions between High-Speed, Sub-Active, |  |  |  |  |

|      |                                       | and Watch Modes                                                   |  |  |  |  |

|      |                                       |                                                                   |  |  |  |  |

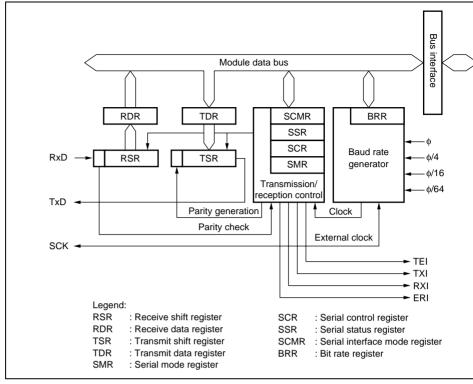

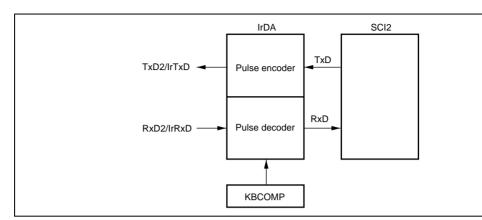

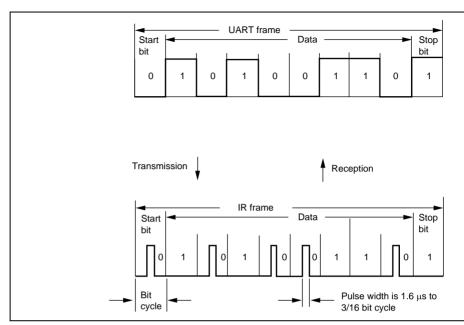

| Sect | ion 15                                | Serial Communication Interface (SCI and IrDA)                     |  |  |  |  |

| 15.1 | Feature                               | es                                                                |  |  |  |  |

| 15.2 | Input/C                               | Output Pins                                                       |  |  |  |  |

| 15.3 | Registe                               | Register Descriptions                                             |  |  |  |  |

|      | 15.3.1                                | Receive Shift Register (RSR)                                      |  |  |  |  |

|      | 15.3.2                                | Receive Data Register (RDR)                                       |  |  |  |  |

|      | 15.3.3                                | Transmit Data Register (TDR)                                      |  |  |  |  |

|      | 15.3.4                                | Transmit Shift Register (TSR)                                     |  |  |  |  |

|      | 15.3.5                                | Serial Mode Register (SMR)                                        |  |  |  |  |

|      | 15.3.6                                | Serial Control Register (SCR)                                     |  |  |  |  |

|      | 15.3.7                                | Serial Status Register (SSR)                                      |  |  |  |  |

|      | 15.3.8                                | Serial Interface Mode Register (SCMR)                             |  |  |  |  |

|      | 15.3.9                                | Bit Rate Register (BRR)                                           |  |  |  |  |

|      | 15.3.10                               | Keyboard Comparator Control Register (KBCOMP)                     |  |  |  |  |

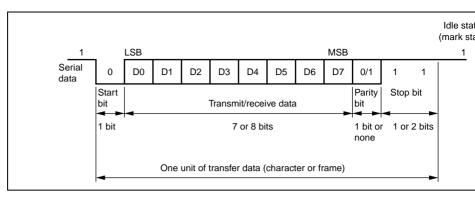

| 15.4 | Operation in Asynchronous Mode        |                                                                   |  |  |  |  |

|      | 15.4.1                                | Data Transfer Format                                              |  |  |  |  |

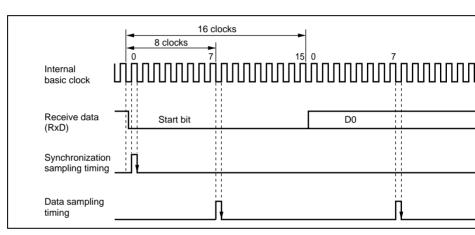

|      | 15.4.2                                | Receive Data Sampling Timing and Reception Margin in Asynchronous |  |  |  |  |

|      |                                       | Mode                                                              |  |  |  |  |

|      | 15.4.3                                | Clock                                                             |  |  |  |  |

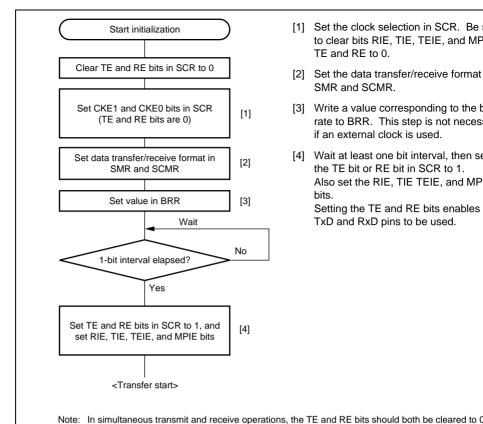

|      | 15.4.4                                | SCI Initialization (Asynchronous Mode)                            |  |  |  |  |

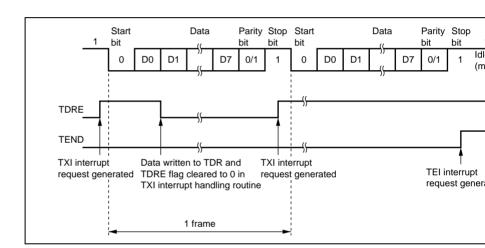

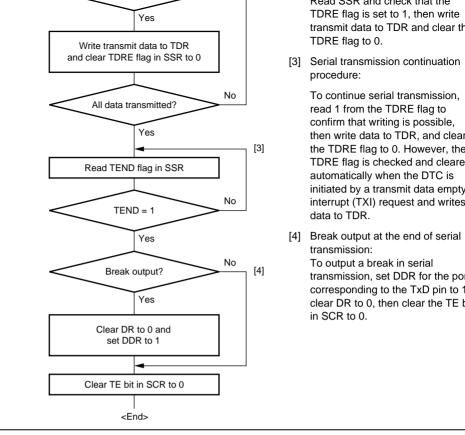

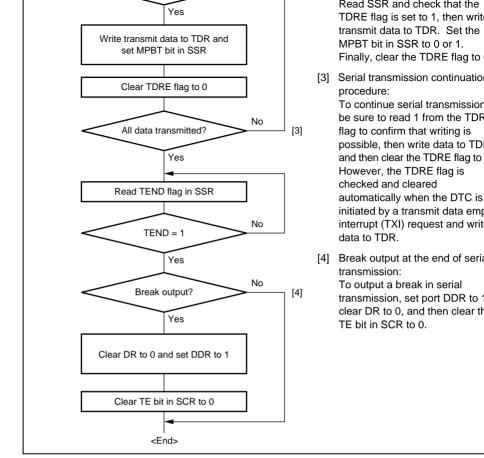

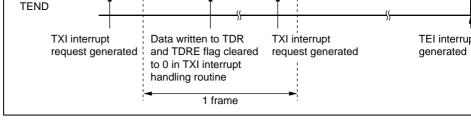

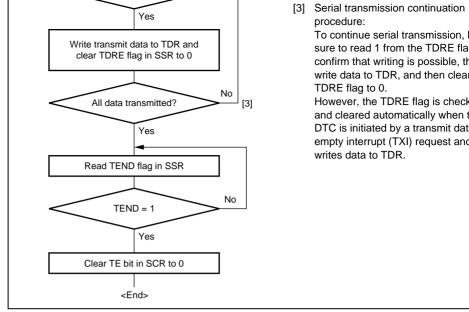

|      | 15.4.5                                | Data Transmission (Asynchronous Mode)                             |  |  |  |  |

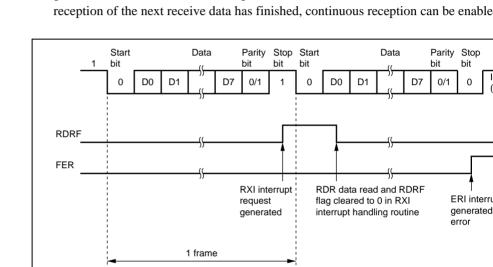

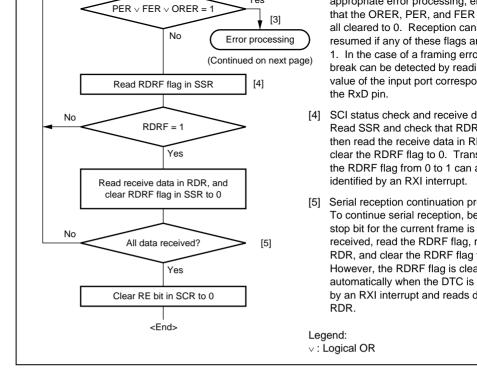

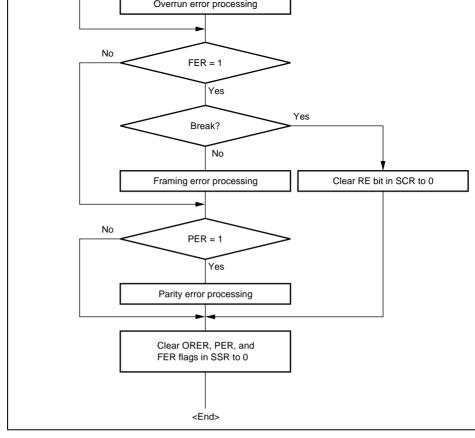

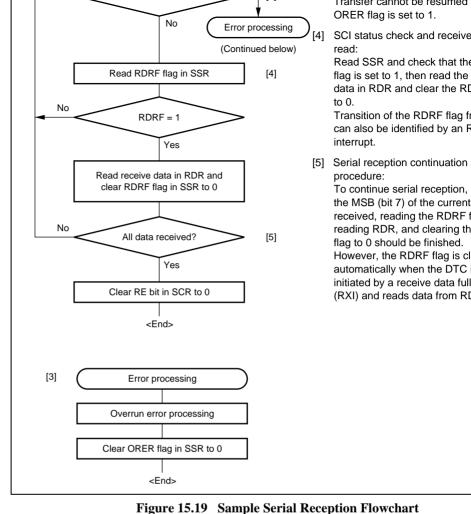

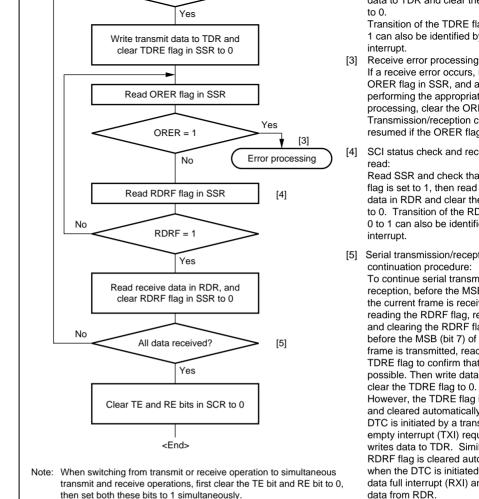

|      |                                       | Serial Data Reception (Asynchronous Mode)                         |  |  |  |  |

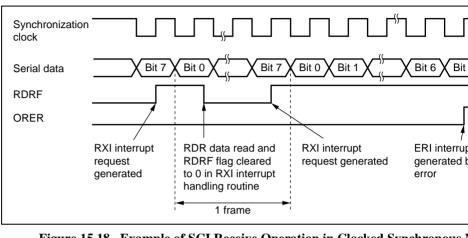

| 15.5 |                                       |                                                                   |  |  |  |  |

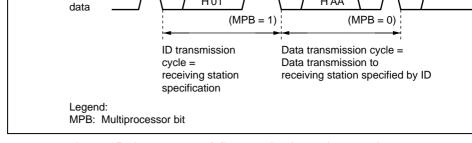

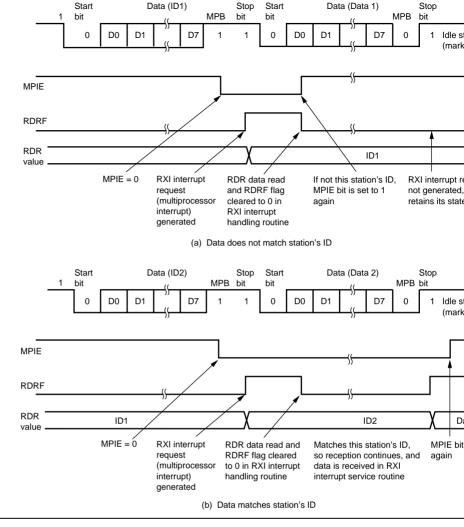

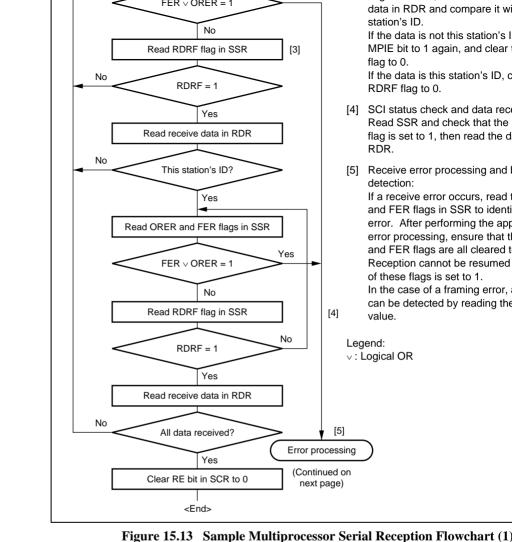

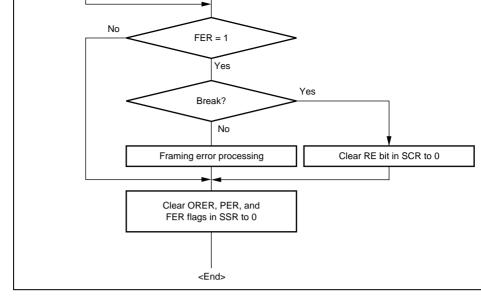

|      | Transprocessor Communication Lanction |                                                                   |  |  |  |  |

Rev. 3.00 Mar 21, 2006 page xxx of liv

15.6

RENESAS

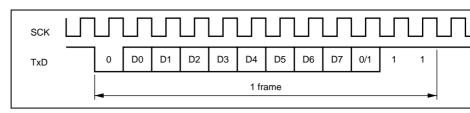

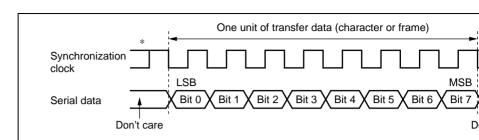

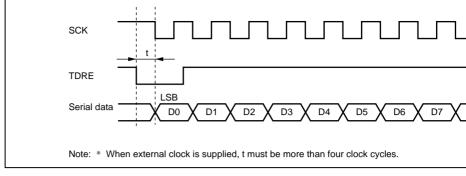

15.6.1 Clock

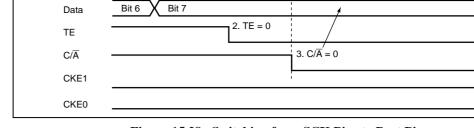

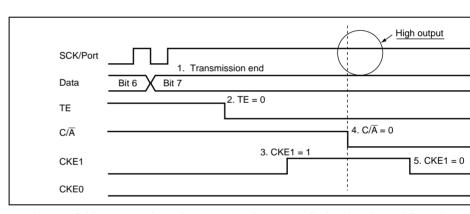

|      | 15.9.7  | SCI Operations during Mode Transitions                                  |

|------|---------|-------------------------------------------------------------------------|

|      | 15.9.8  | Notes on Switching from SCK Pins to Port Pins                           |

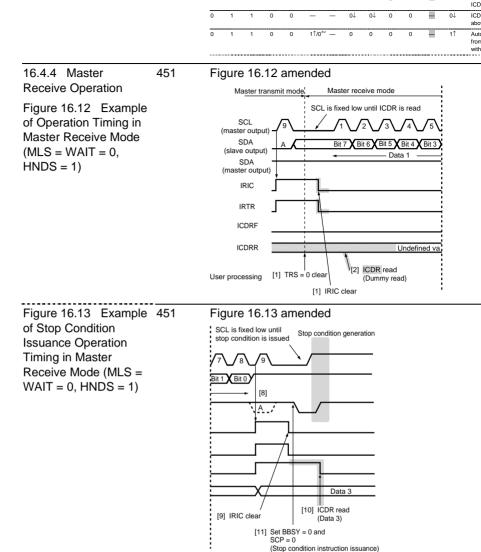

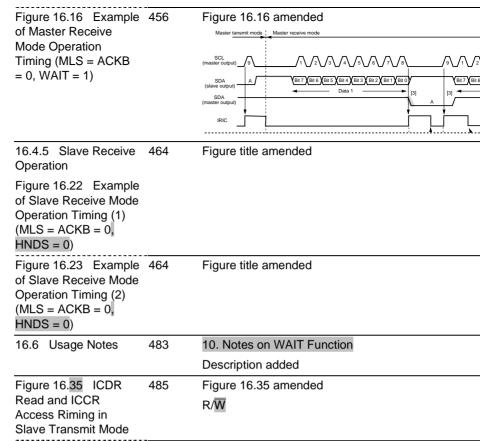

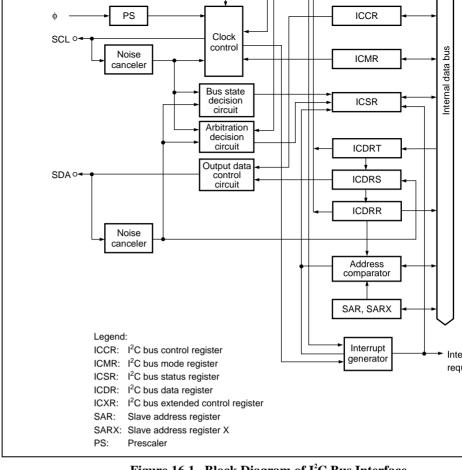

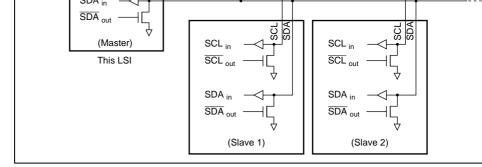

| Sec  | tion 16 | I <sup>2</sup> C Bus Interface (IIC) (Optional)                         |

| 16.1 |         | 28                                                                      |

| 16.2 | Input/C | Output Pins                                                             |

| 16.3 | Registe | er Descriptions                                                         |

|      | 16.3.1  | I <sup>2</sup> C Bus Data Register (ICDR)                               |

|      | 16.3.2  | Slave Address Register (SAR)                                            |

|      | 16.3.3  | Second Slave Address Register (SARX)                                    |

|      | 16.3.4  | I <sup>2</sup> C Bus Mode Register (ICMR)                               |

|      |         | I <sup>2</sup> C Bus Control Register (ICCR)                            |

|      | 16.3.6  | I <sup>2</sup> C Bus Status Register (ICSR)                             |

|      | 16.3.7  | DDC Switch Register (DDCSWR)                                            |

|      | 16.3.8  | I <sup>2</sup> C Bus Extended Control Register (ICXR)                   |

| 16.4 |         | ion                                                                     |

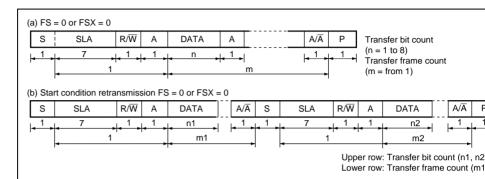

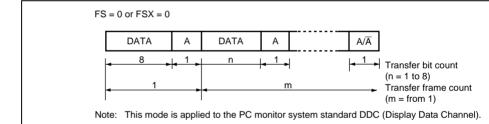

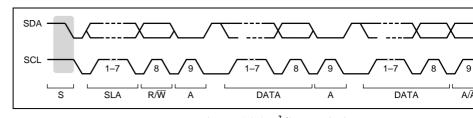

|      | 16.4.1  | I <sup>2</sup> C Bus Data Format                                        |

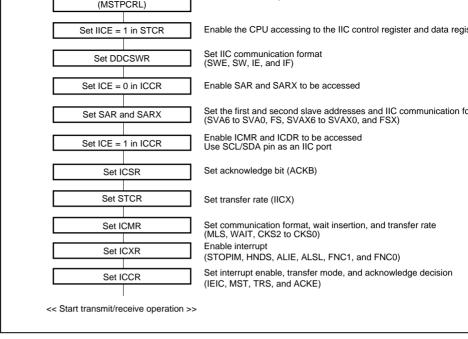

|      | 16.4.2  | Initialization                                                          |

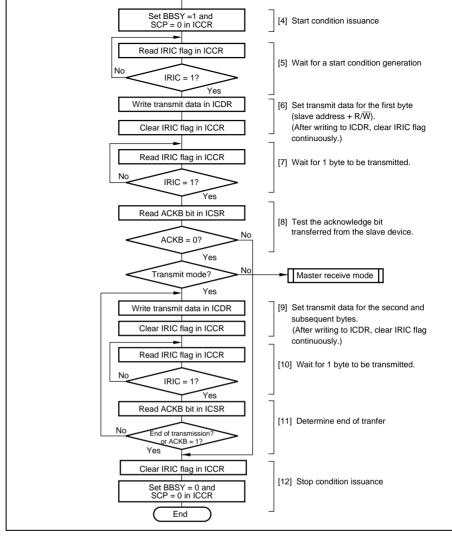

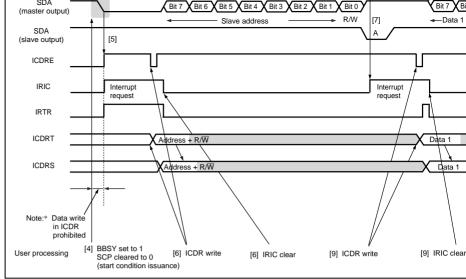

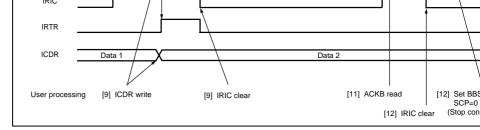

|      | 16.4.3  | Master Transmit Operation                                               |

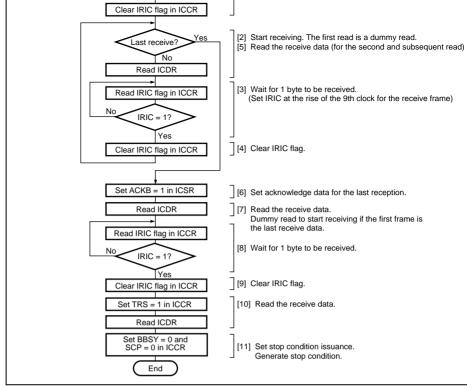

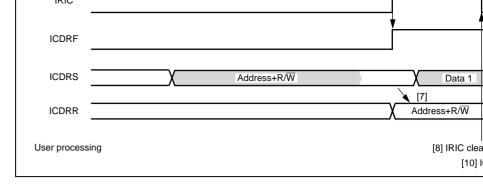

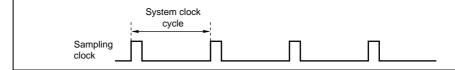

|      | 16.4.4  | Master Receive Operation                                                |

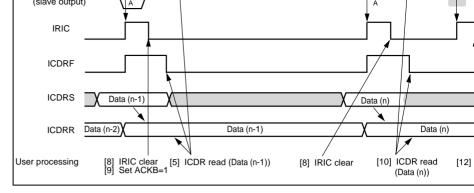

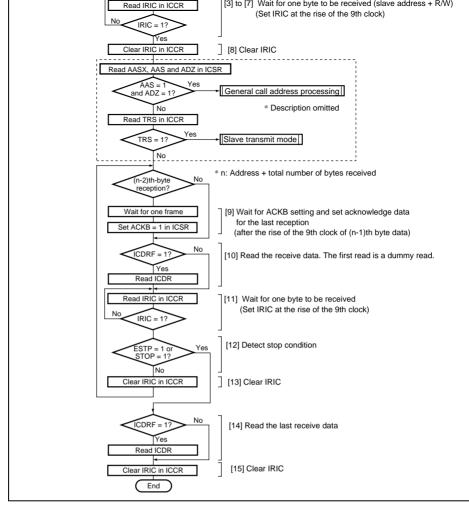

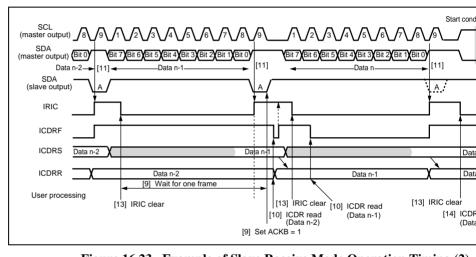

|      | 16.4.5  | Slave Receive Operation                                                 |

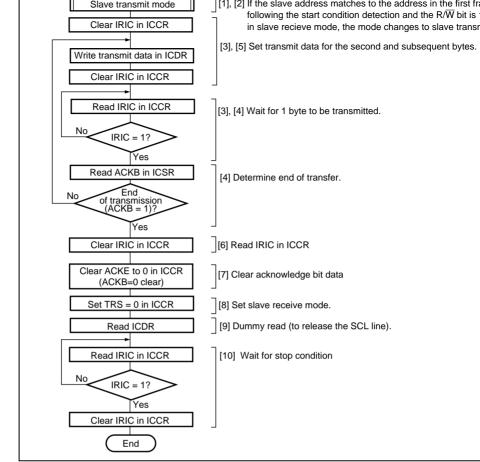

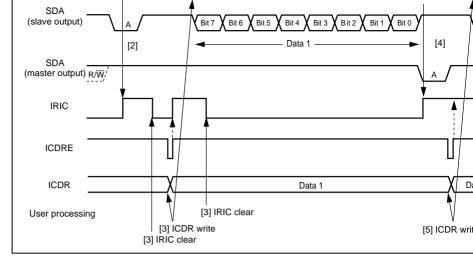

|      | 16.4.6  | Slave Transmit Operation                                                |

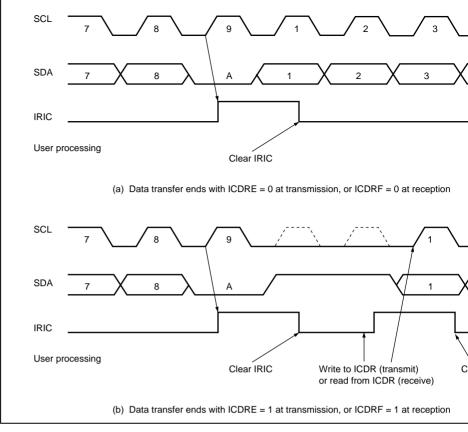

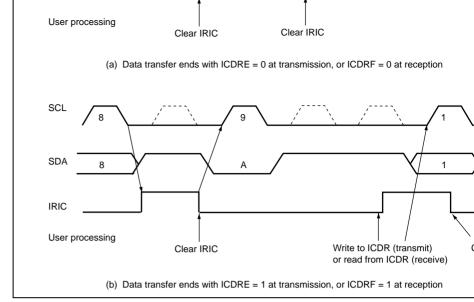

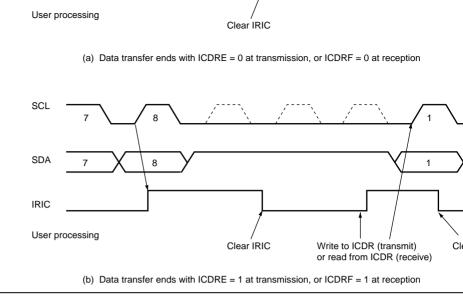

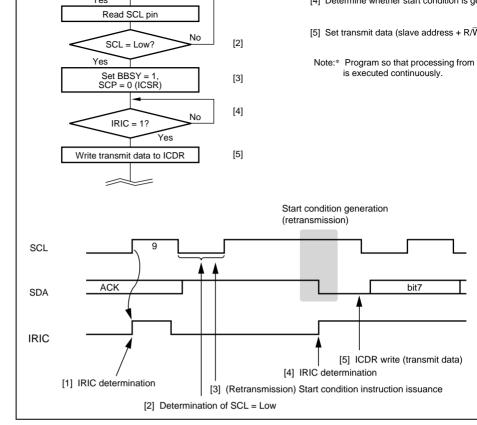

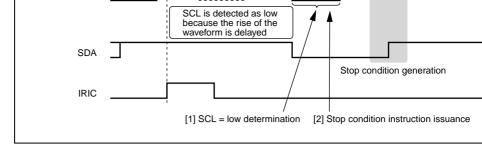

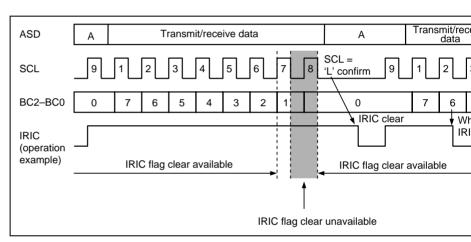

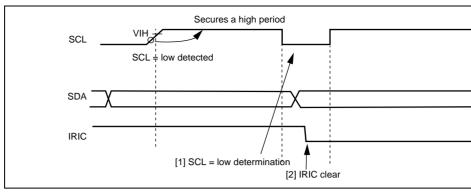

|      |         | IRIC Setting Timing and SCL Control                                     |

|      | 16.4.8  | Automatic Switching from Formatless Mode to I <sup>2</sup> C Bus Format |

|      | 16.4.9  | Operation Using DTC                                                     |

|      | 16.4.10 | Noise Canceler                                                          |

|      |         |                                                                         |

|      |         | Rev. 3.00 Mar 21, 2006 p                                                |

|      |         | RENESAS                                                                 |

|      |         |                                                                         |

(Clocked Synchronous Mode Only)

15.9.4 Receive Error Flags and Transmit Operations

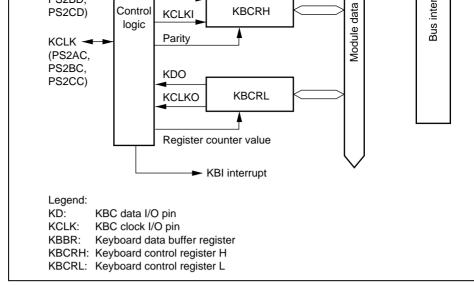

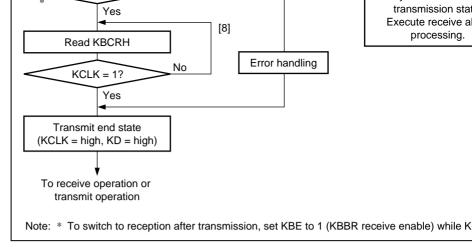

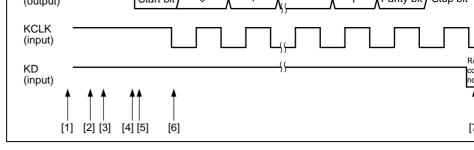

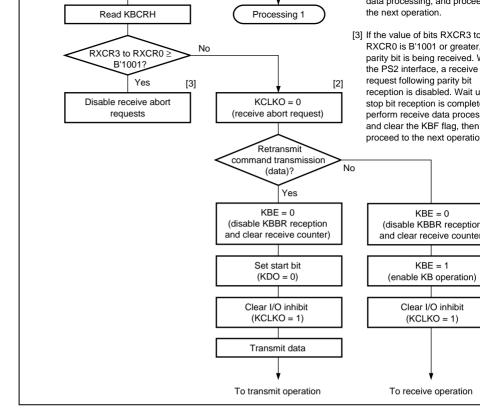

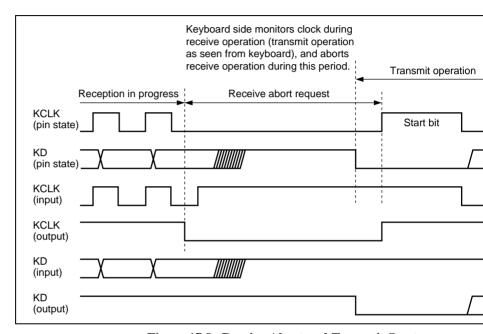

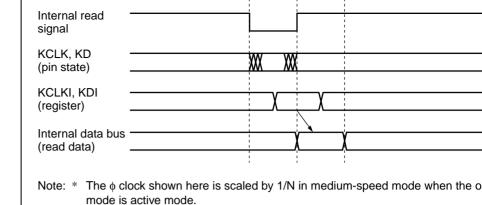

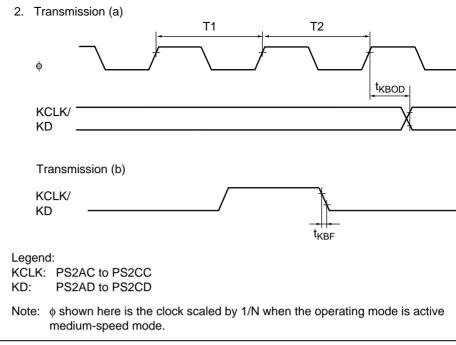

|      | 17.4.4  | KCLKI and KDI Read Timing                                              |

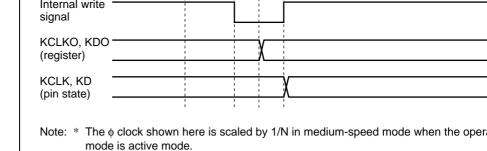

|------|---------|------------------------------------------------------------------------|

|      |         | KCLKO and KDO Write Timing                                             |

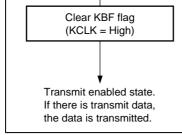

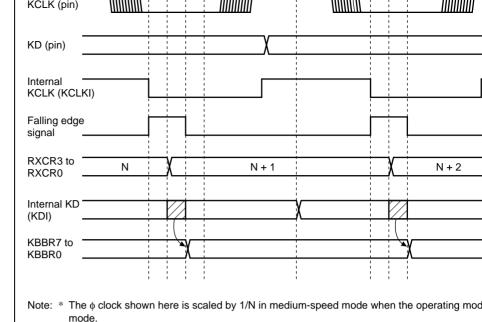

|      |         | KBF Setting Timing and KCLK Control                                    |

|      |         | Receive Timing                                                         |

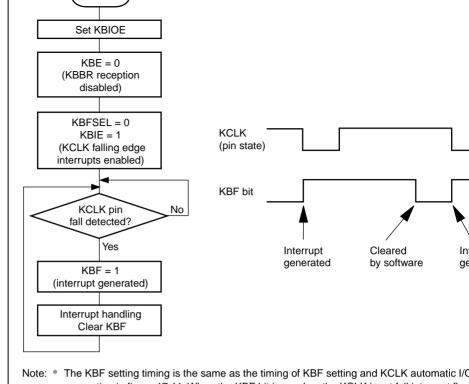

|      |         | KCLK Fall Interrupt Operation                                          |

| 17.5 |         | Notes                                                                  |

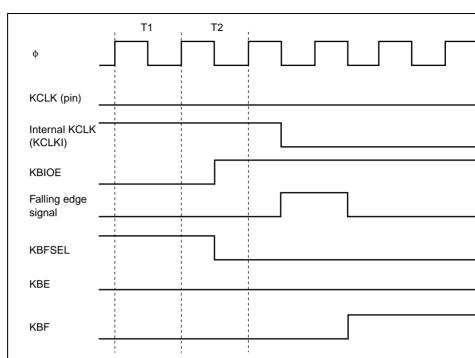

|      |         | KBIOE Setting and KCLK Falling Edge Detection                          |

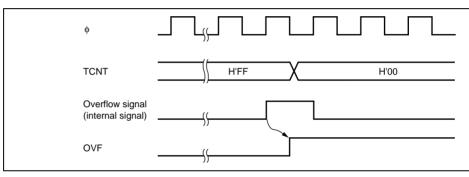

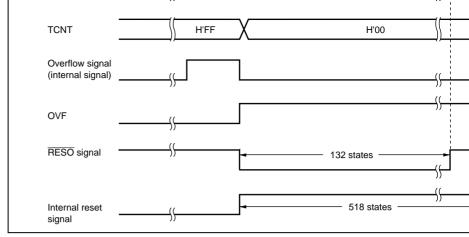

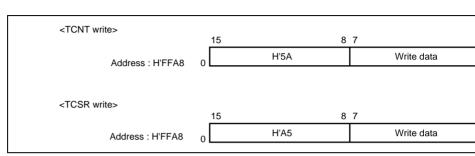

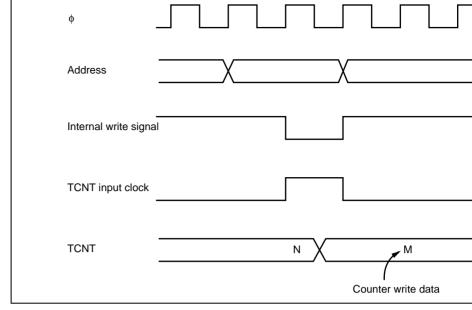

|      |         | Module Stop Mode Setting                                               |