## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

## Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## H8S/2345 Group, H8S/2345 F-ZTAT™

Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2300 Series

> H8S/2345 HD6432345, HD6472345, HD64F2345 H8S/2344 HD6432344 H8S/2341 HD6432341 H8S/2340 HD64F2340

- Technology Corp. product best suited to the customer's application; they do not convey any under any intellectual property rights, or any other rights, belonging to Renesas Technology

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of a party's rights, originating in the use of any product data, diagrams, charts, programs, algoriti circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, progra algorithms represents information on products at the time of publication of these materials, subject to change by Renesas Technology Corp. without notice due to product improvemen other reasons. It is therefore recommended that customers contact Renesas Technology C

an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corp. by various

including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.co 4. When using any or all of the information contained in these materials, including product data

- diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a system before making a final decision on the applicability of the information and products. F Technology Corp. assumes no responsibility for any damage, liability or other loss resulting information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a system that is used under circumstances in which human life is potentially at stake. Please Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor

- considering the use of a product contained herein for any specific purposes, such as appara systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater us 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduc-

- whole or in part these materials. 7. If these products or technologies are subject to the Japanese export control restrictions, the be exported under a license from the Japanese government and cannot be imported into a

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/o country of destination is prohibited. 8. Please contact Renesas Technology Corp. for further details on these materials or the production

Rev. 4.00 Feb 15, 2006 page ii of xxiv

contained therein.

other than the approved destination.

Treatment of Unused Input Pins

Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. In are in their open states, intermediate levels are induced by noise in the vicinity through current flows internally, and a malfunction may occur.

## 3. Processing before Initialization

When power is first supplied, the product's state is undefined. The states of in circuits are undefined until full power is supplied throughout the chip and a lo input on the reset pin. During the period where the states are undefined, the re settings and the output state of each pin are also undefined. Design your syste does not malfunction because of processing while it is in this undefined state.

been turned on.

4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test may have been be allocated to these address. Do not access these registers: the operation is not guaranteed if they are accessed.

products which have a reset function, reset the LSI immediately after the pow

Rev. 4.00 Feb 15, 2006 p

Rev. 4.00 Feb 15, 2006 page iv of xxiv

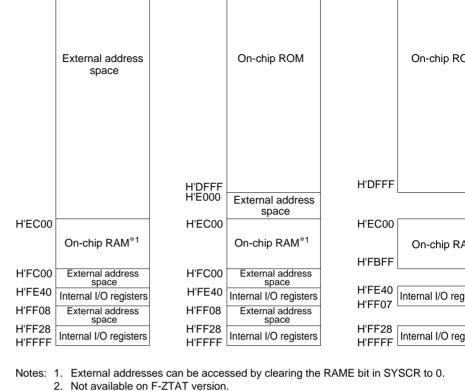

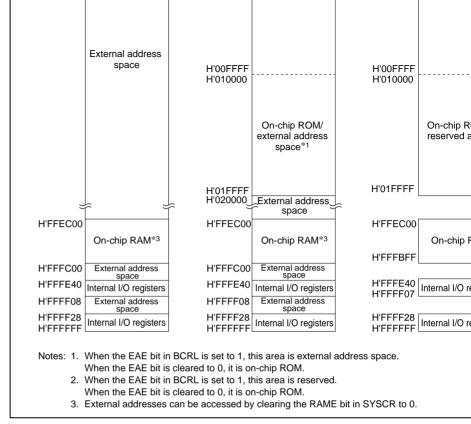

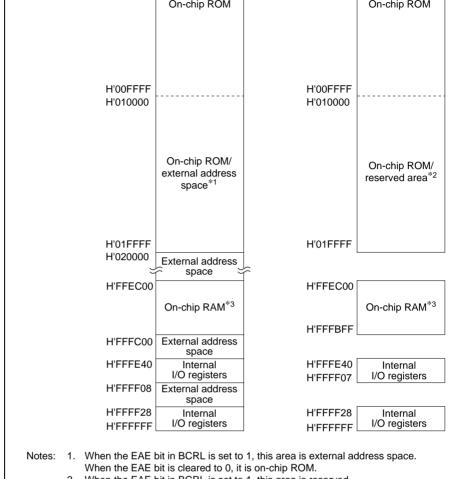

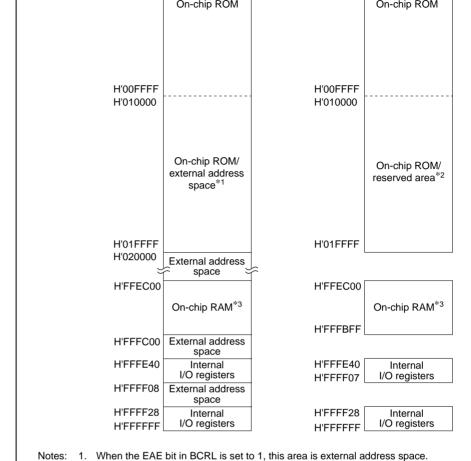

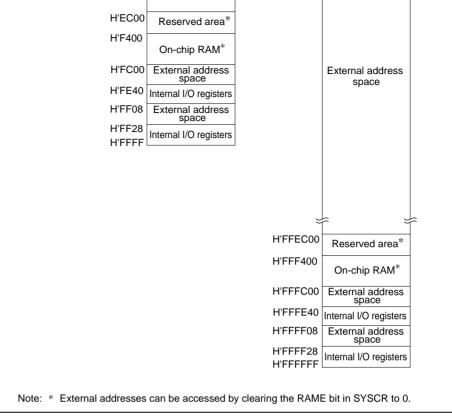

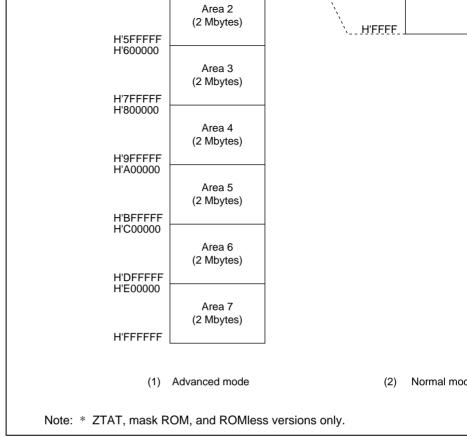

The address space is divided into eight areas. The data bus width and access states car

for each of these areas, and various kinds of memory can be connected fast and easily

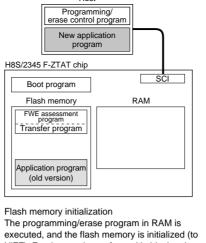

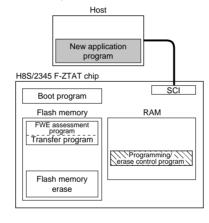

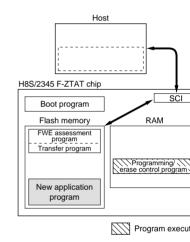

On-chip memory consists of large-capacity ROM and RAM. With regard to on-chip F single power supply flash memory (F-ZTAT<sup>TM\*2</sup>), PROM (ZTAT<sup>®\*2</sup>), and mask RO are available, providing a quick and flexible response to conditions from ramp-up throscale volume production, even for applications with frequently changing specification

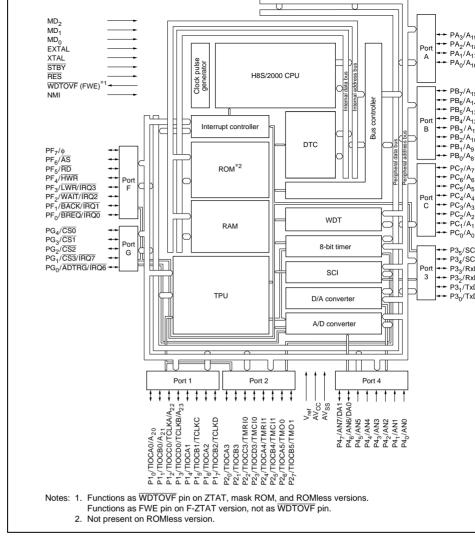

On-chip supporting functions include a 16-bit timer pulse unit (TPU), 8-bit timers, wa (WDT), serial communication interface (SCI), A/D converter, D/A converter, and I/O

An on-chip data transfer controller (DTC) is also provided, enabling high-speed data without CPU intervention.

Use of the H8S/2345 Group enables compact, high-performance systems to be implereasily.

This manual describes the hardware of the H8S/2345 Group. Refer to the H8S/2600 S H8S/2000 Series Programming Manual for a detailed description of the instruction set

Notes: 1. The H8S/2345, H8S/2344, H8S/2343, and H8S/2341 have on-chip ROM. The H8S/2340 does not have on-chip ROM.

2. F-ZTAT (Flexible-ZTAT) is a trademark of Renesas Technology Corp. ZTAT is a registered trademark of Renesas Technology Corp.

Rev. 4.00 Feb 15, 2006 p

Rev. 4.00 Feb 15, 2006 page vi of xxiv

|                                           |     | <ol><li>Reference value for 25°C (as a guideline, rewriting<br/>normally function up to this value).</li></ol>                  |

|-------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------|

|                                           |     | <ol><li>Data retention characteristic when rewriting is per<br/>within the specification range, including the minimum</li></ol> |

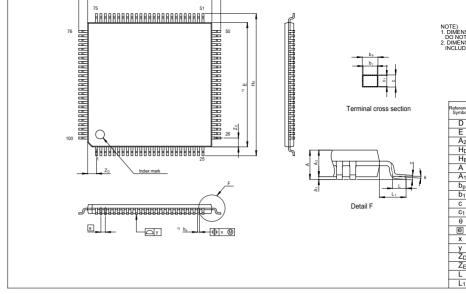

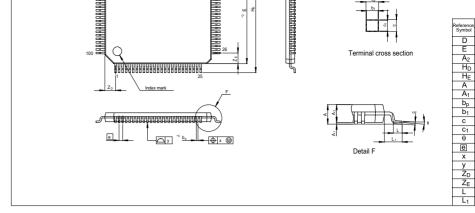

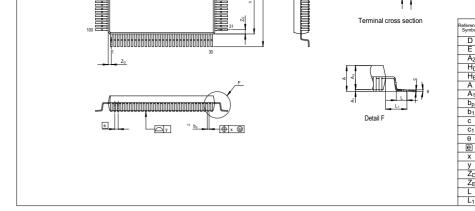

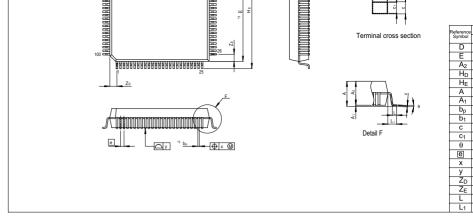

| Appendix G Package Dimensions             | 897 | Figure G.1 replaced                                                                                                             |

| Figure G.1 TFP-100B<br>Package Dimensions |     |                                                                                                                                 |

| Figure G.2 TFP-100G<br>Package Dimensions | 898 | Figure G.2 replaced                                                                                                             |

| Figure G.3 FP-100A<br>Package Dimensions  | 899 | Figure G.3 replaced                                                                                                             |

| Figure G.4 FP-100B<br>Package Dimensions  | 900 | Figure G.4 replaced                                                                                                             |

minimum value.)

Notes: 7. Minimum number of times for which all character guaranteed after rewriting. (Guarantee range is

Rev. 4.00 Feb 15, 2006 page viii of xxiv

| 2.1 |                   | ew                                                |  |  |

|-----|-------------------|---------------------------------------------------|--|--|

|     | 2.1.1             | Features                                          |  |  |

|     | 2.1.2             | Differences between H8S/2600 CPU and H8S/2000 CPU |  |  |

|     | 2.1.3             | Differences from H8/300 CPU                       |  |  |

|     | 2.1.4             | Differences from H8/300H CPU                      |  |  |

| 2.2 | CPU O             | perating Modes                                    |  |  |

| 2.3 | Addres            | s Space                                           |  |  |

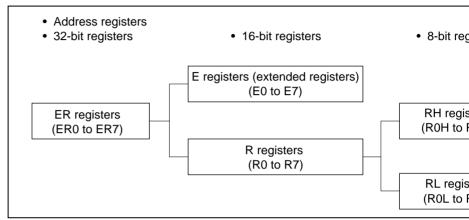

| 2.4 | Registe           | er Configuration                                  |  |  |

|     | 2.4.1             | Overview                                          |  |  |

|     | 2.4.2             | General Registers                                 |  |  |

|     | 2.4.3             | Control Registers                                 |  |  |

|     | 2.4.4             | Initial Register Values                           |  |  |

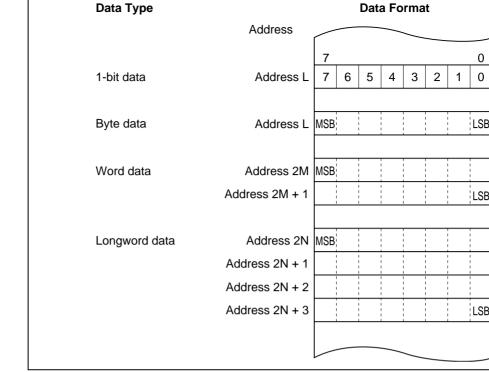

| 2.5 | Data Fo           | ormats                                            |  |  |

|     | 2.5.1             | General Register Data Formats                     |  |  |

|     | 2.5.2             | Memory Data Formats                               |  |  |

| 2.6 | Instruction Set   |                                                   |  |  |

|     | 2.6.1             | Overview                                          |  |  |

|     | 2.6.2             | Instructions and Addressing Modes                 |  |  |

|     | 2.6.3             | Table of Instructions Classified by Function      |  |  |

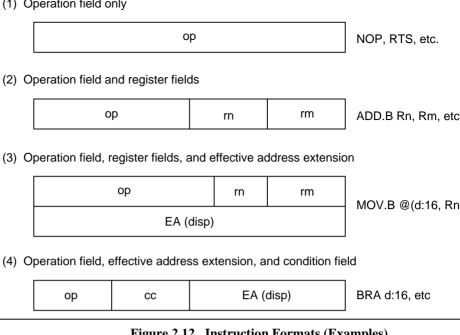

|     | 2.6.4             | Basic Instruction Formats                         |  |  |

| 2.7 | Addres            | sing Modes and Effective Address Calculation      |  |  |

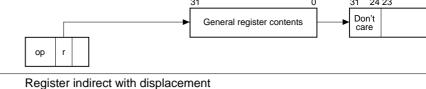

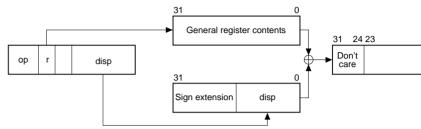

|     | 2.7.1             | Addressing Mode                                   |  |  |

|     | 2.7.2             | Effective Address Calculation                     |  |  |

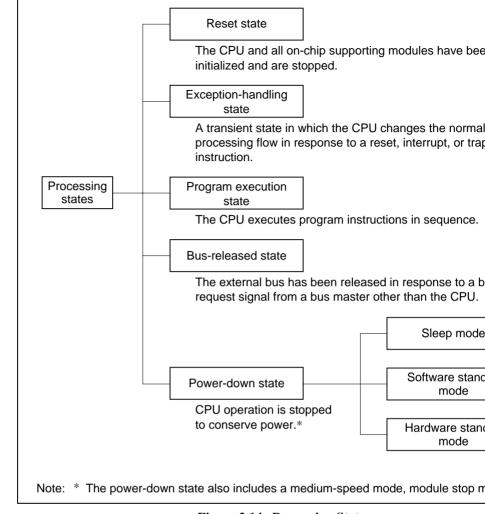

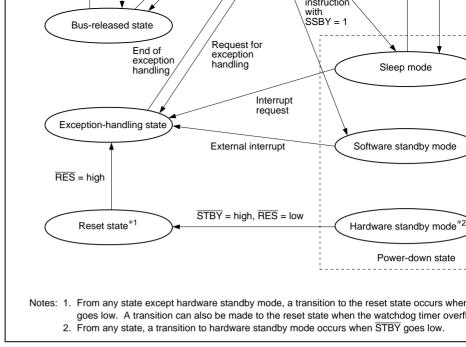

| 2.8 | Processing States |                                                   |  |  |

|     | 2.8.1             | Overview                                          |  |  |

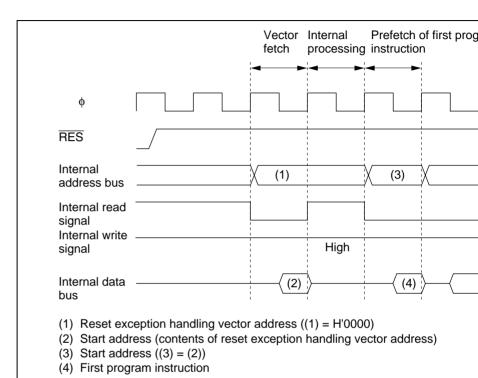

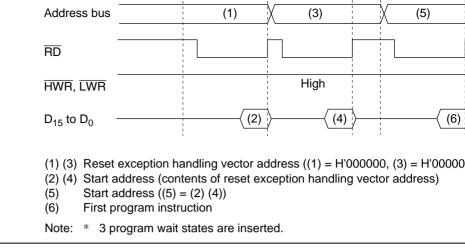

|     | 2.8.2             | Reset State                                       |  |  |

1.5.2 Fill Fullctions in Each Operating Wode ..... Pin Functions .....

1.3.3

2.8.3

2.8.4

2.8.5

Rev. 4.00 Feb 15, 2006 p

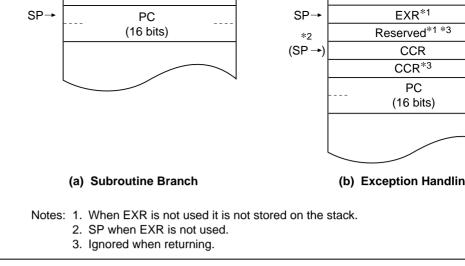

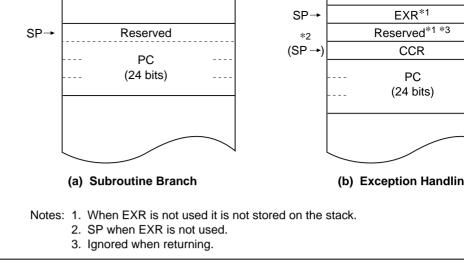

Exception-Handling State

Program Execution State..... Bus-Released State....

|      |         | · F                                                            |

|------|---------|----------------------------------------------------------------|

|      | 3.1.2   | Operating Mode Selection (ZTAT, Mask ROM, and ROMless Versions |

|      | 3.1.3   | Register Configuration                                         |

| 3.2  | Registe | er Descriptions                                                |

|      | 3.2.1   | Mode Control Register (MDCR)                                   |

|      | 3.2.2   | System Control Register (SYSCR)                                |

|      | 3.2.3   | System Control Register 2 (SYSCR2) (F-ZTAT Version Only)       |

| 3.3  | Operat  | ing Mode Descriptions                                          |

|      | 3.3.1   | Mode 1 (ZTAT, Mask ROM, and ROMless Versions Only)             |

|      | 3.3.2   | Mode 2 (ZTAT and Mask ROM Versions Only)                       |

|      | 3.3.3   | Mode 3 (ZTAT and Mask ROM Versions Only)                       |

|      | 3.3.4   | Mode 4                                                         |

|      | 3.3.5   | Mode 5                                                         |

|      | 3.3.6   | Mode 6                                                         |

|      | 3.3.7   | Mode 7                                                         |

|      | 3.3.8   | Modes 8 and 9 (F-ZTAT Version Only)                            |

|      | 3.3.9   | Mode 10 (F-ZTAT Version Only)                                  |

|      | 3.3.10  | Mode 11 (F-ZTAT Version Only)                                  |

|      | 3.3.11  | Modes 12 and 13                                                |

|      | 3.3.12  | Mode 14 (F-ZTAT Version Only)                                  |

|      |         | Mode 15 (F-ZTAT Version Only)                                  |

| 3.4  |         | nctions in Each Operating Mode                                 |

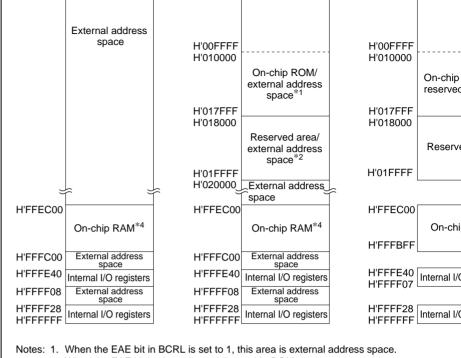

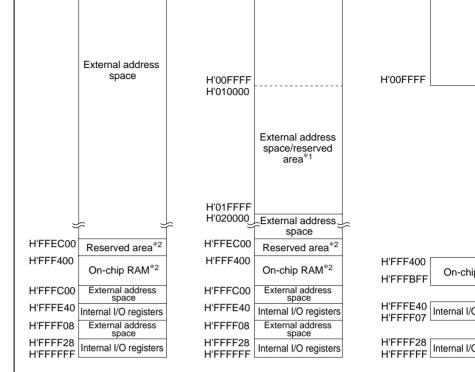

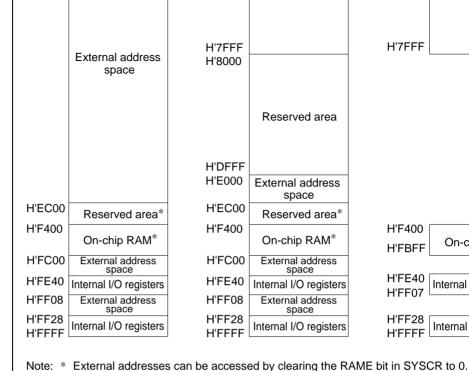

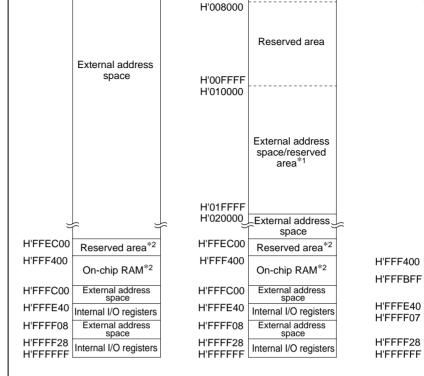

| 3.5  |         | ry Map in Each Operating Mode                                  |

|      |         |                                                                |

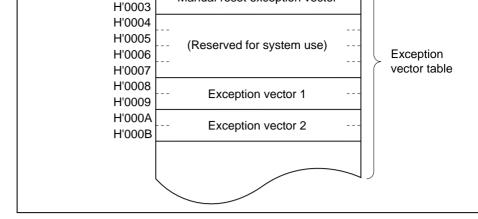

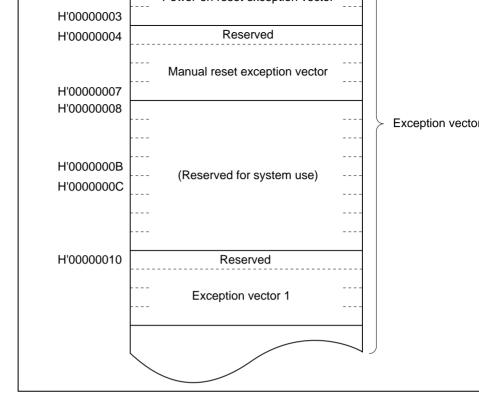

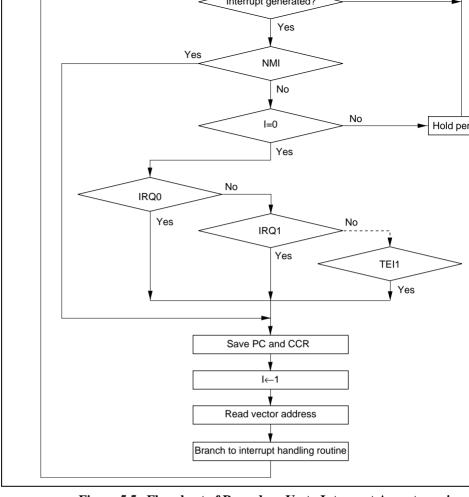

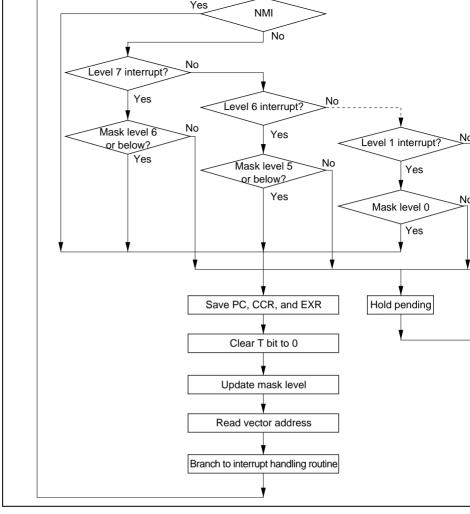

| Sect | ion 4   | Exception Handling                                             |

| 4.1  |         | ew                                                             |

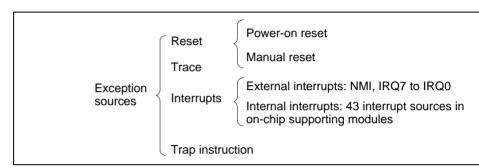

|      | 4.1.1   | Exception Handling Types and Priority                          |

|      | 4.1.2   | Exception Handling Operation.                                  |

|      | 4.1.3   | Exception Vector Table                                         |

|      |         | 1                                                              |

3.1.1

4.2

4.2.1

4.2.2

Rev. 4.00 Feb 15, 2006 page x of xxiv

RENESAS

Overview.....

Reset Types.....

Reset

Operating Mode Selection (F-ZTAT<sup>TM</sup> Version).....

|     | 5.1.3    | Pin Configuration                                     |

|-----|----------|-------------------------------------------------------|

|     | 5.1.4    | Register Configuration                                |

| 5.2 | Registe  | er Descriptions                                       |

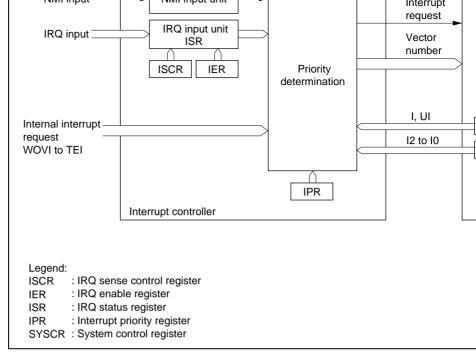

|     | 5.2.1    | System Control Register (SYSCR)                       |

|     | 5.2.2    | Interrupt Priority Registers A to K (IPRA to IPRK)    |

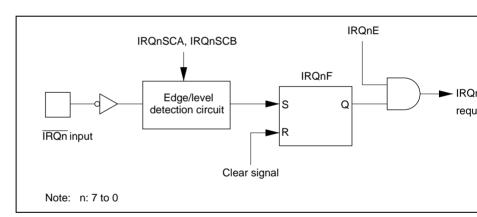

|     | 5.2.3    | IRQ Enable Register (IER)                             |

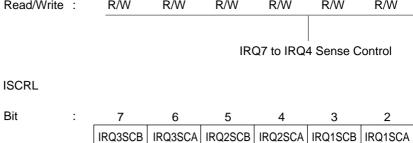

|     | 5.2.4    | IRQ Sense Control Registers H and L (ISCRH, ISCRL)    |

|     | 5.2.5    | IRQ Status Register (ISR)                             |

| 5.3 | Interruj | pt Sources                                            |

|     | 5.3.1    | External Interrupts                                   |

|     | 5.3.2    | Internal Interrupts                                   |

|     | 5.3.3    | Interrupt Exception Handling Vector Table             |

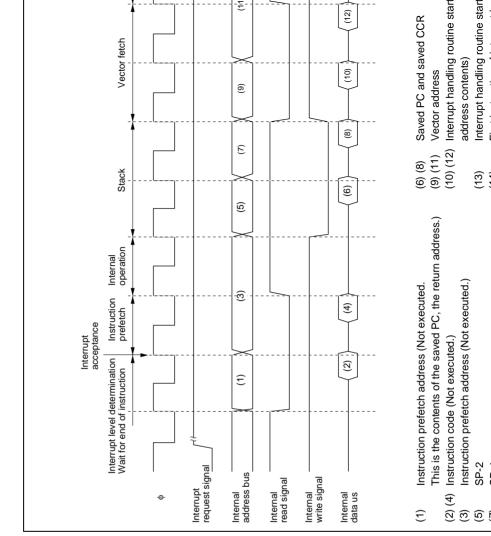

| 5.4 | Interruj | pt Operation                                          |

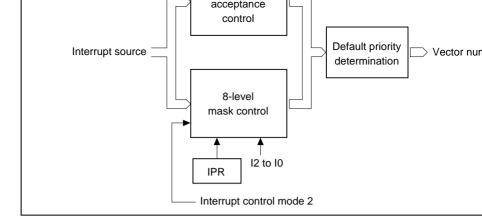

|     | 5.4.1    | Interrupt Control Modes and Interrupt Operation       |

|     | 5.4.2    | Interrupt Control Mode 0                              |

|     | 5.4.3    | Interrupt Control Mode 2                              |

|     | 5.4.4    | Interrupt Exception Handling Sequence                 |

|     | 5.4.5    | Interrupt Response Times                              |

| 5.5 | Usage 1  | Notes                                                 |

|     | 5.5.1    | Contention between Interrupt Generation and Disabling |

|     | 5.5.2    | Instructions that Disable Interrupts                  |

|     | 5.5.3    | Times when Interrupts Are Disabled                    |

|     | 5.5.4    | Interrupts during Execution of EEPMOV Instruction     |

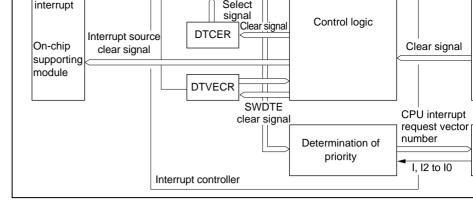

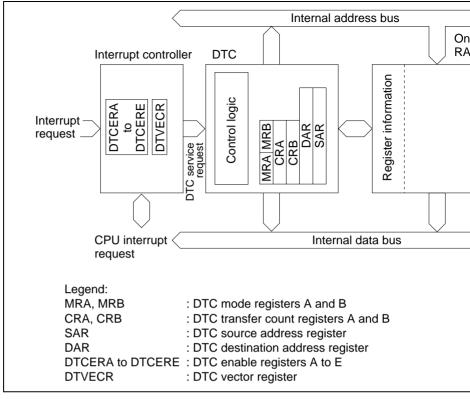

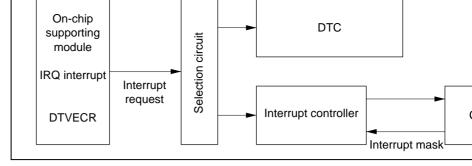

| 5.6 | DTC A    | ctivation by Interrupt                                |

|     | 5.6.1    | Overview                                              |

|     | 5.6.2    | Block Diagram                                         |

5.1.1

5.1.2

5.6.3

Section 5 Interrupt Controller

5.1 Overview......

Features

Block Diagram

Rev. 4.00 Feb 15, 2006 p

Operation .....

|     | 6.3.3     | Memory Interfaces                                             |

|-----|-----------|---------------------------------------------------------------|

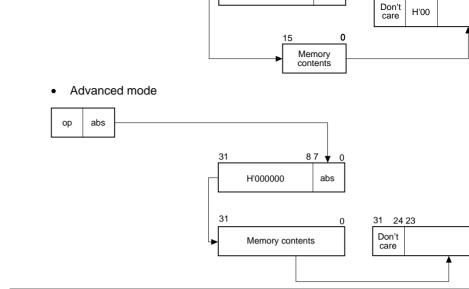

|     | 6.3.4     | Advanced Mode                                                 |

|     | 6.3.5     | Areas in Normal Mode (ZTAT, Mask ROM, and ROMless Versions Or |

|     | 6.3.6     | Chip Select Signals                                           |

| 6.4 | Basic     | Bus Interface                                                 |

|     | 6.4.1     | Overview                                                      |

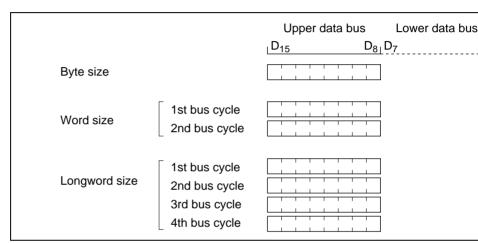

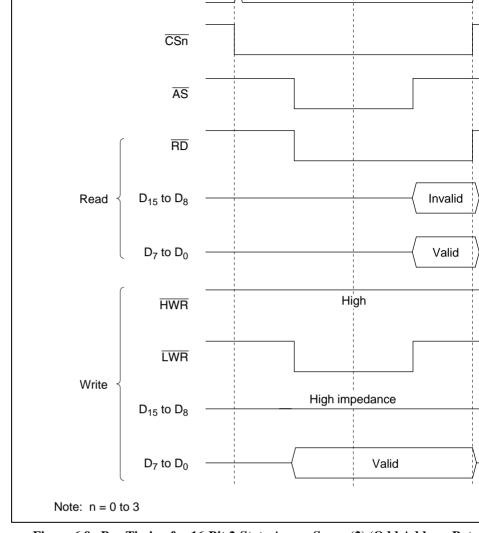

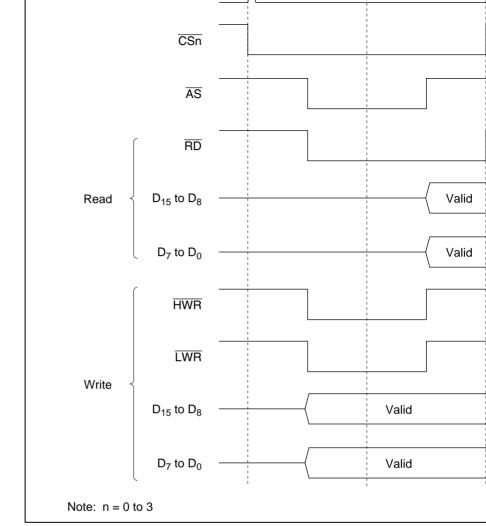

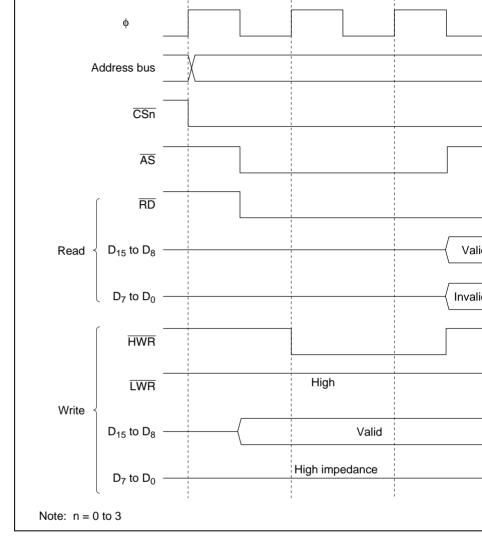

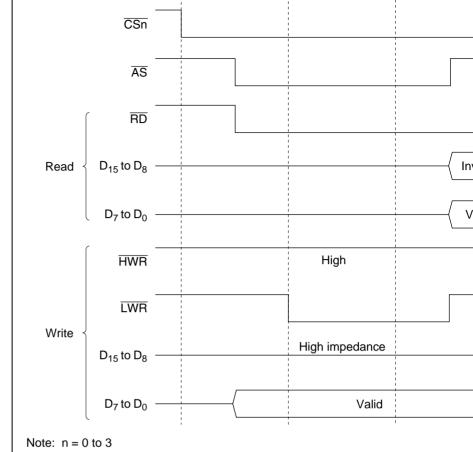

|     | 6.4.2     | Data Size and Data Alignment                                  |

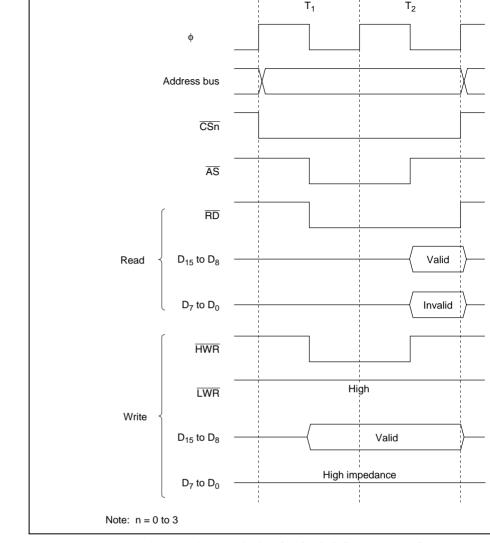

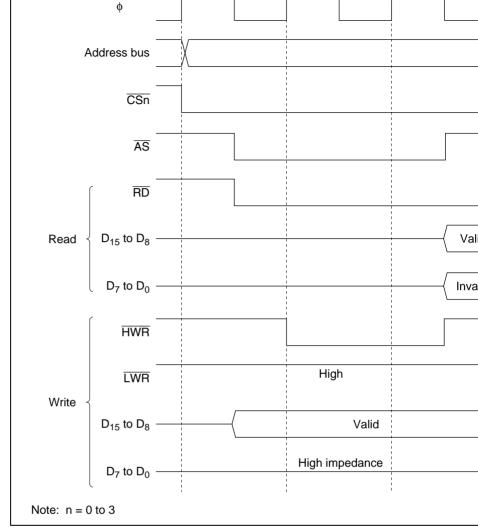

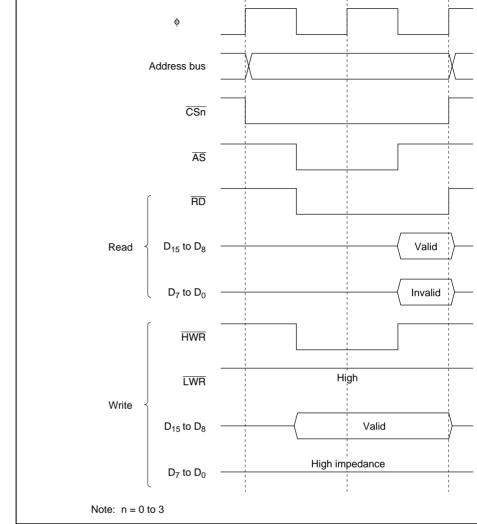

|     | 6.4.3     | Valid Strobes                                                 |

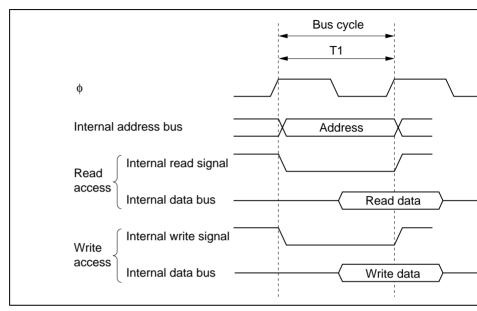

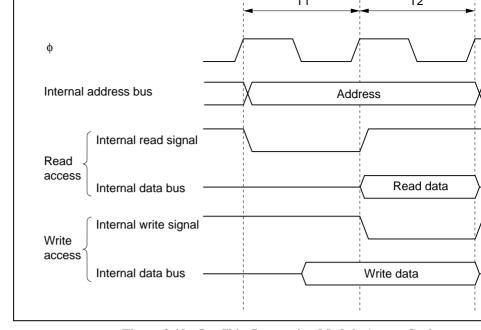

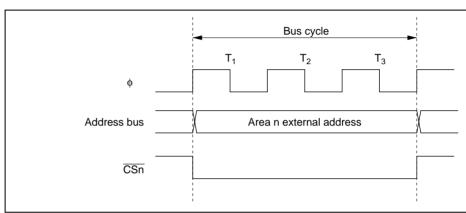

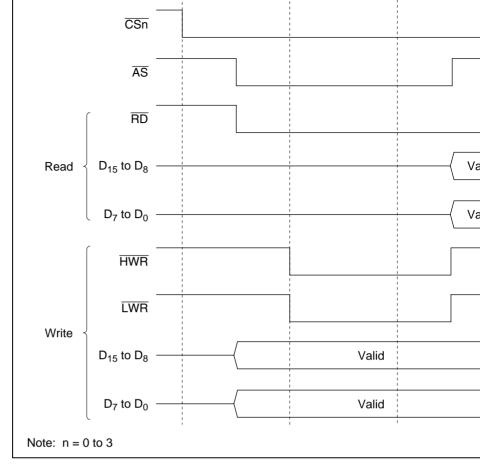

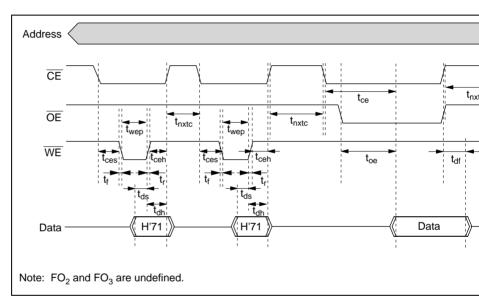

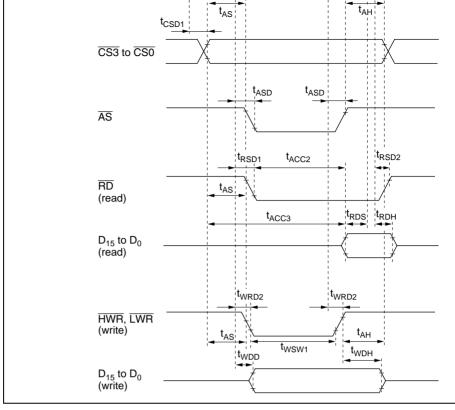

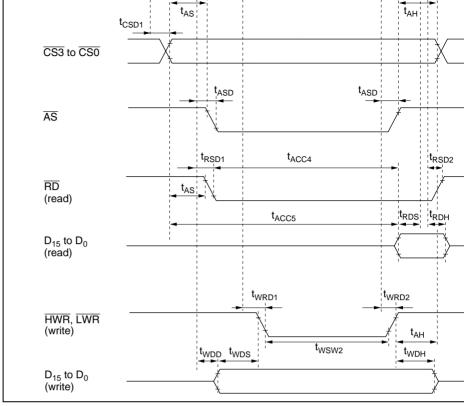

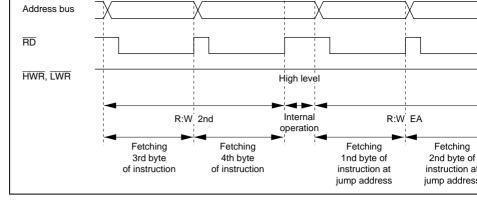

|     | 6.4.4     | Basic Timing                                                  |

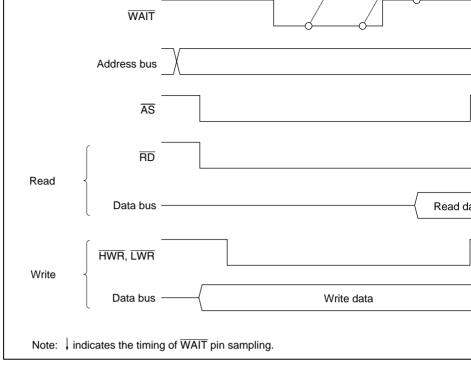

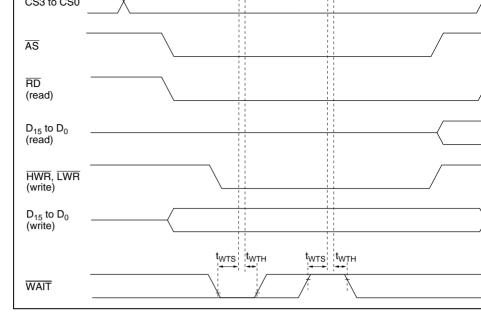

|     | 6.4.5     | Wait Control                                                  |

| 6.5 | Burst 1   | ROM Interface                                                 |

|     | 6.5.1     | Overview                                                      |

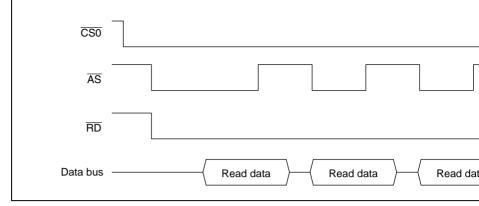

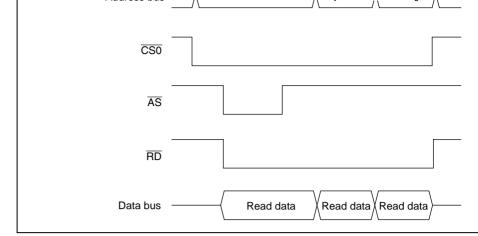

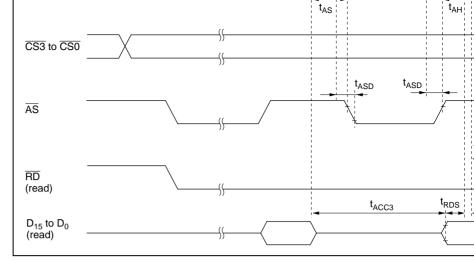

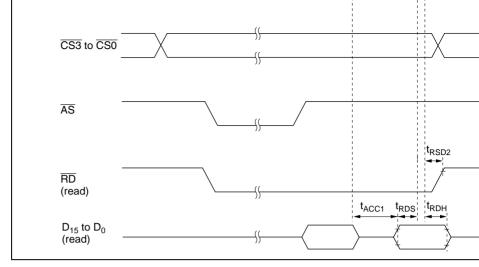

|     | 6.5.2     | Basic Timing                                                  |

|     | 6.5.3     | Wait Control                                                  |

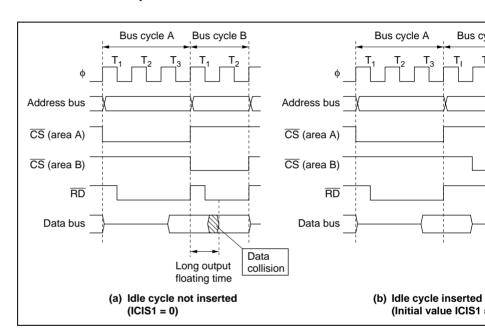

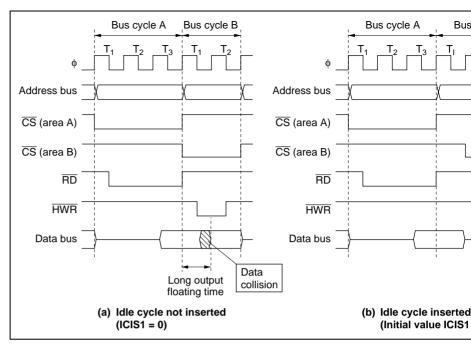

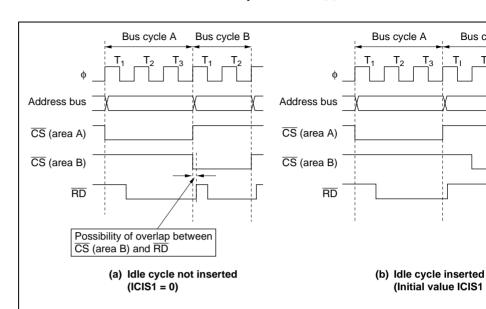

| 6.6 | Idle C    | ycle                                                          |

|     | 6.6.1     | Operation                                                     |

|     | 6.6.2     | Pin States in Idle Cycle                                      |

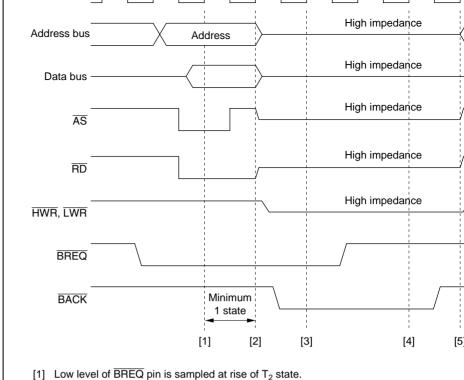

| 6.7 | Bus R     | elease                                                        |

|     | 6.7.1     | Overview                                                      |

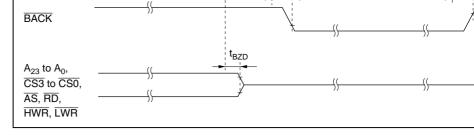

|     | 6.7.2     | Operation                                                     |

|     | 6.7.3     | Pin States in External Bus Released State                     |

|     | 6.7.4     | Transition Timing                                             |

|     | 6.7.5     | Usage Note                                                    |

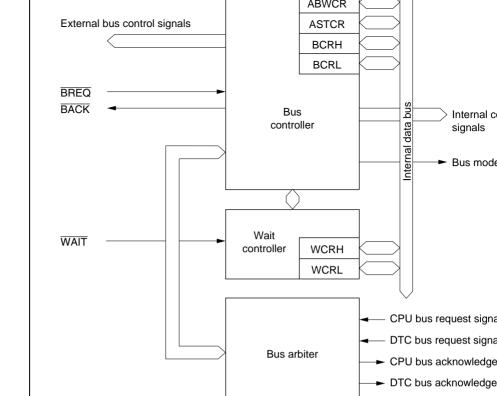

| 6.8 | Bus A     | rbitration                                                    |

|     | 6.8.1     | Overview                                                      |

|     | 6.8.2     | Operation                                                     |

|     |           | •                                                             |

| Rev | . 4.00 Fe | eb 15, 2006 page xii of xxiv                                  |

|     |           | RENESAS                                                       |

|     |           | •(ENES/15                                                     |

Wait Control Registers H and L (WCRH, WCRL).....

Bus Control

6.2.3

6.2.4

6.2.5

6.3.1

6.3.2

6.3

|      | 7.2.4  | DTC Destination Address Register (DAR)            |

|------|--------|---------------------------------------------------|

|      | 7.2.5  | DTC Transfer Count Register A (CRA)               |

|      | 7.2.6  | DTC Transfer Count Register B (CRB)               |

|      | 7.2.7  | DTC Enable Registers (DTCER)                      |

|      | 7.2.8  | DTC Vector Register (DTVECR)                      |

|      | 7.2.9  | Module Stop Control Register (MSTPCR)             |

| 7.3  | Operat | ion                                               |

|      | 7.3.1  | Overview                                          |

|      | 7.3.2  | Activation Sources                                |

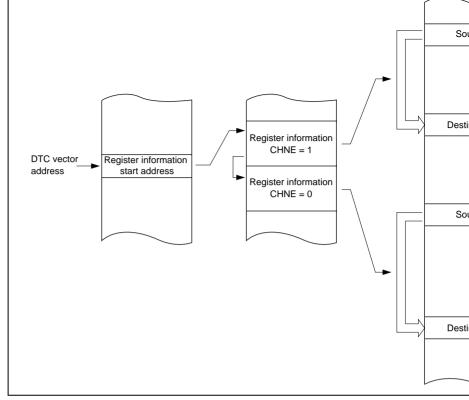

|      | 7.3.3  | DTC Vector Table                                  |

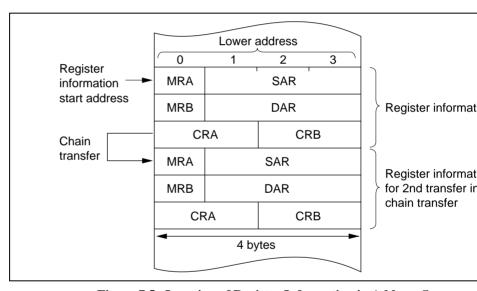

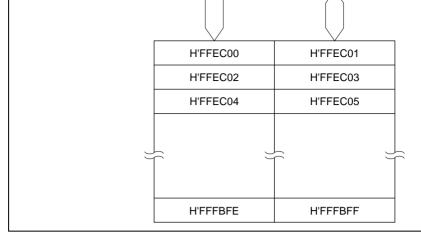

|      | 7.3.4  | Location of Register Information in Address Space |

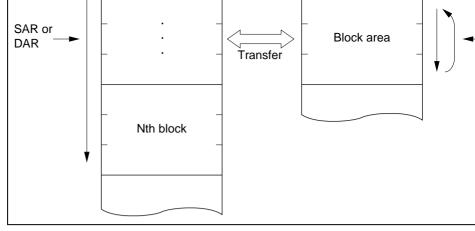

|      | 7.3.5  | Normal Mode                                       |

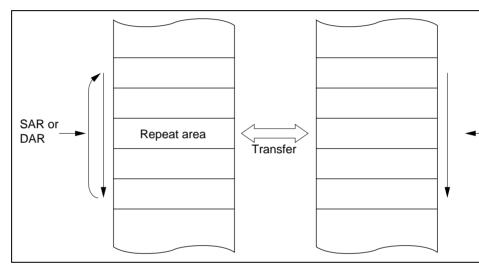

|      | 7.3.6  | Repeat Mode                                       |

|      | 7.3.7  | Block Transfer Mode                               |

|      | 7.3.8  | Chain Transfer                                    |

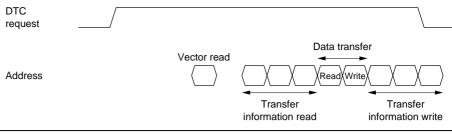

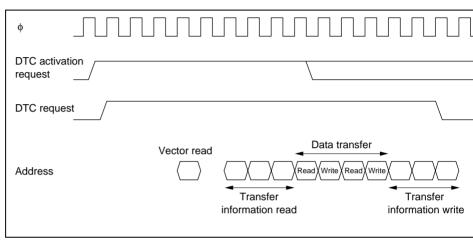

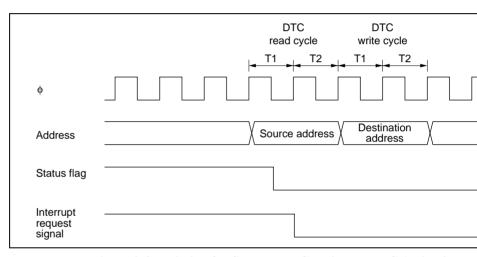

|      | 7.3.9  | Operation Timing                                  |

|      | 7.3.10 | Number of DTC Execution States                    |

|      | 7.3.11 | Procedures for Using DTC                          |

|      |        | Examples of Use of the DTC                        |

| 7.4  |        | pts                                               |

| 7.5  |        | Notes                                             |

|      |        |                                                   |

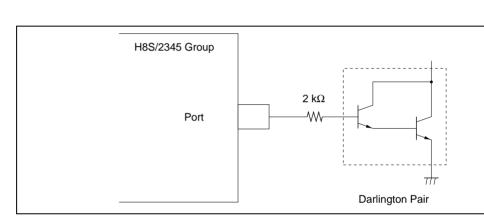

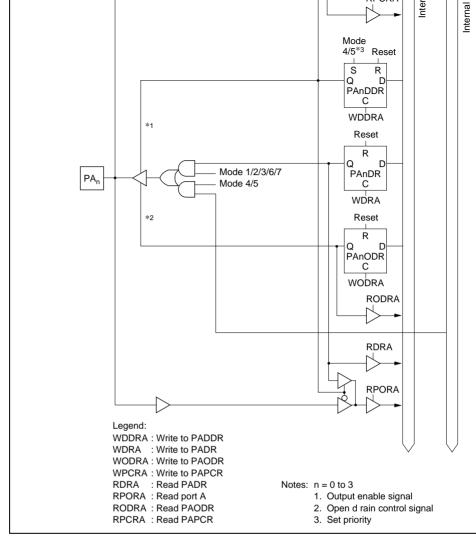

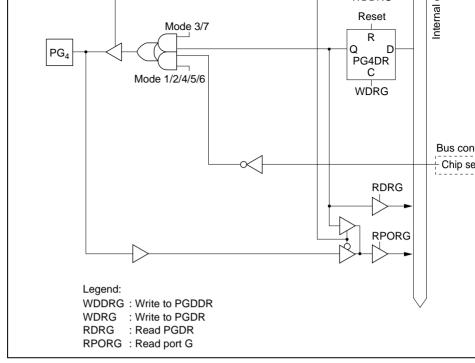

| Sect | ion 8  | I/O Ports                                         |

| 8.1  |        | ew                                                |

| 8.2  |        |                                                   |

|      | 8.2.1  | Overview                                          |

|      | 8.2.2  | Register Configuration                            |

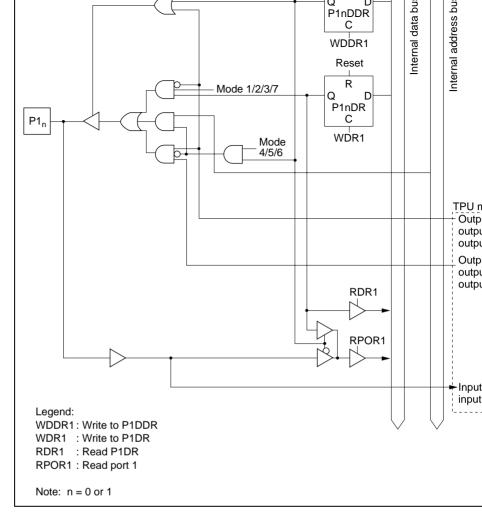

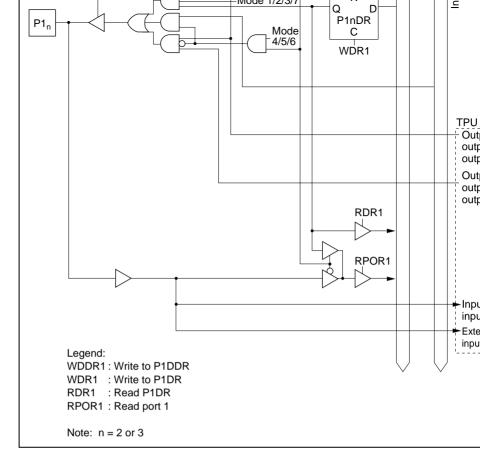

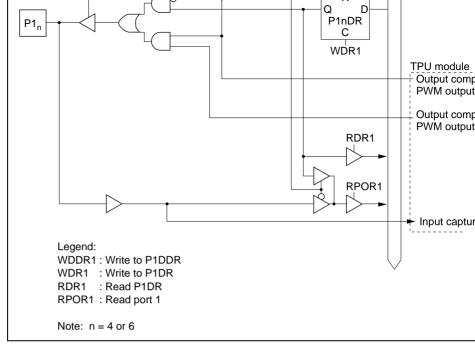

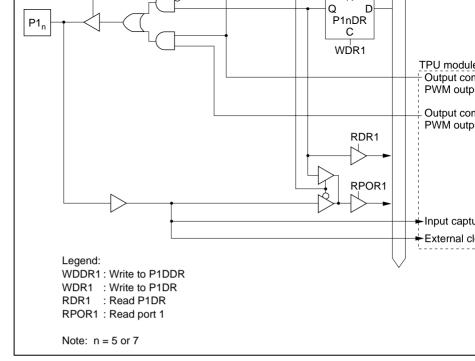

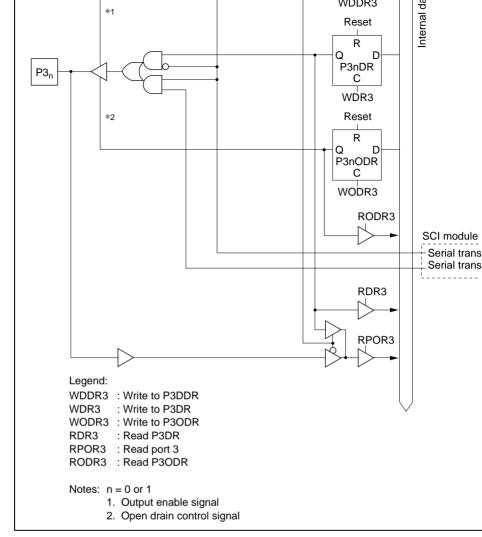

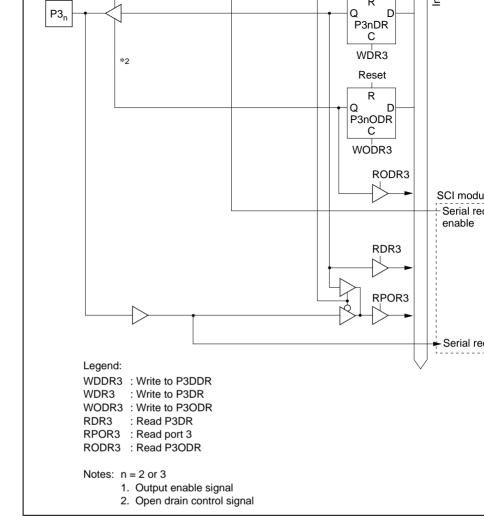

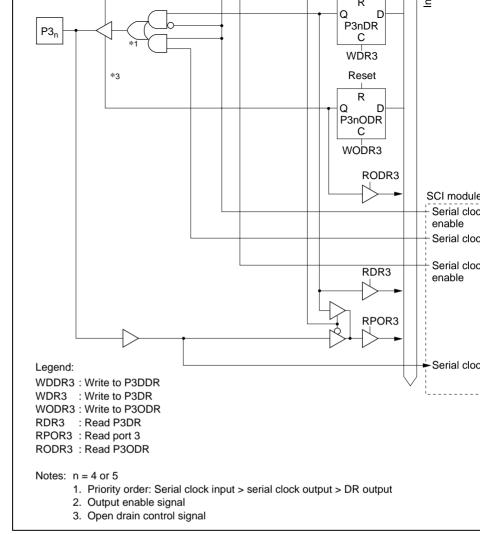

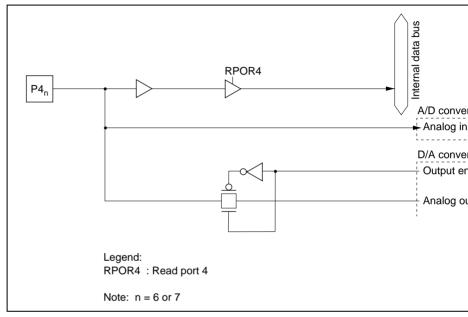

|      | 8.2.3  | Pin Functions                                     |

|      |        |                                                   |

|      |        | Rev. 4.00 Feb 15, 2006 pa                         |

|      |        | OCNICE AC                                         |

|      |        | RENESAS                                           |

|      |        |                                                   |

Register Descriptions

DTC Mode Register A (MRA)

DTC Mode Register B (MRB)......

DTC Source Address Register (SAR).....

7.2

7.2.1

7.2.2

7.2.3

|        | 8.7.3    | Pin Functions               |

|--------|----------|-----------------------------|

|        | 8.7.4    | MOS Input Pull-Up Function  |

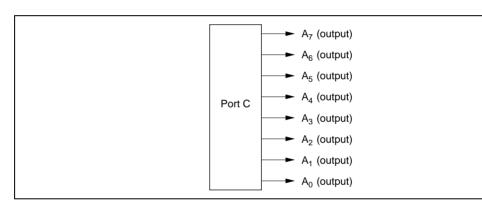

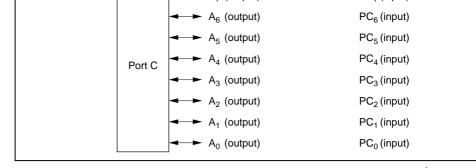

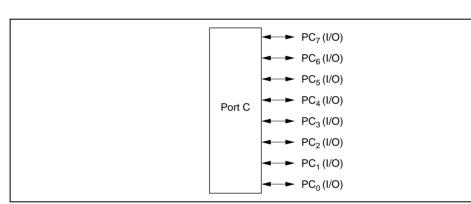

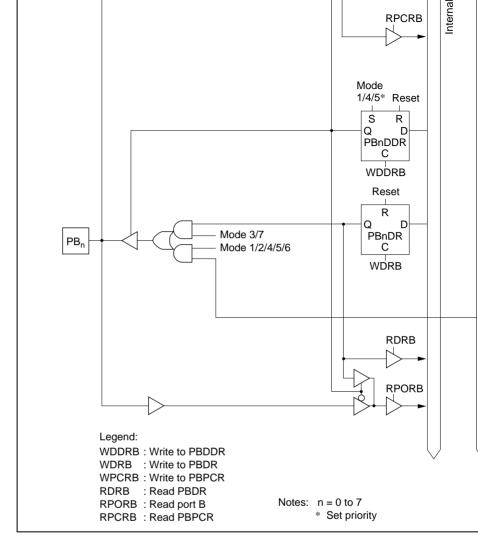

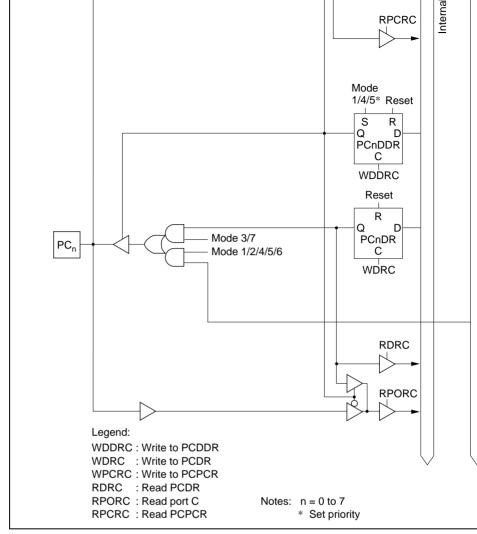

| 8.8    | Port C.  |                             |

|        | 8.8.1    | Overview                    |

|        | 8.8.2    | Register Configuration      |

|        | 8.8.3    | Pin Functions               |

|        | 8.8.4    | MOS Input Pull-Up Function  |

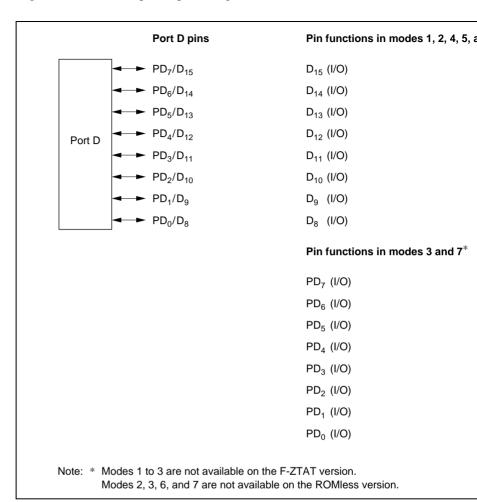

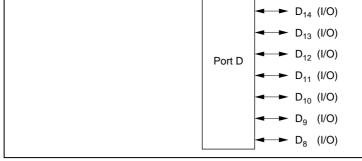

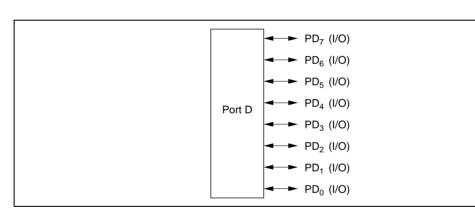

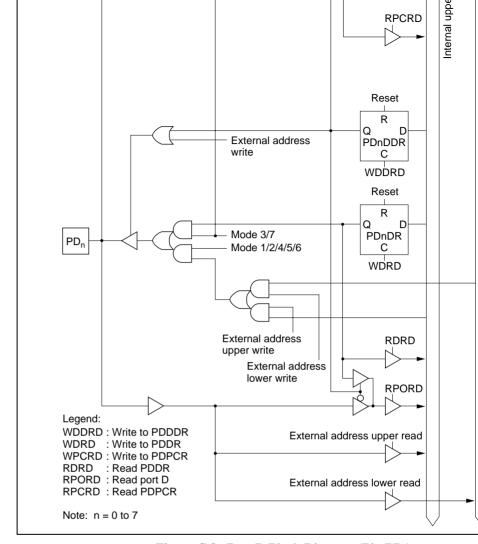

| 8.9    | Port D.  |                             |

|        | 8.9.1    | Overview                    |

|        | 8.9.2    | Register Configuration      |

|        | 8.9.3    | Pin Functions               |

|        | 8.9.4    | MOS Input Pull-Up Function  |

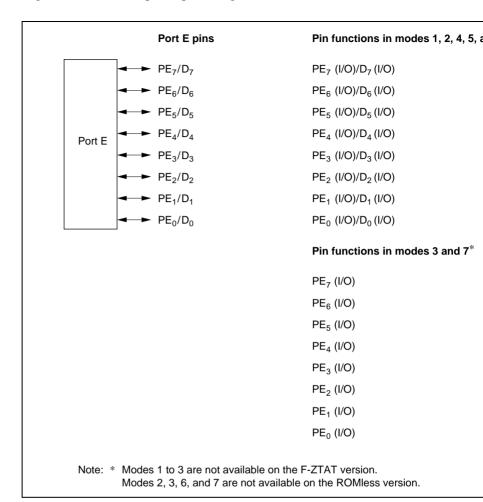

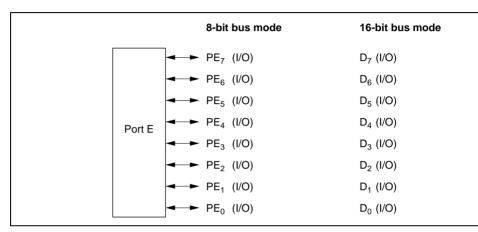

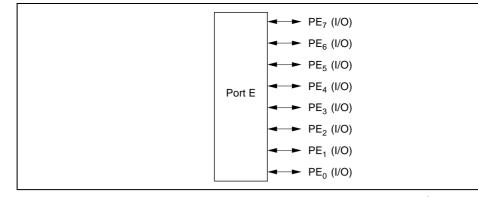

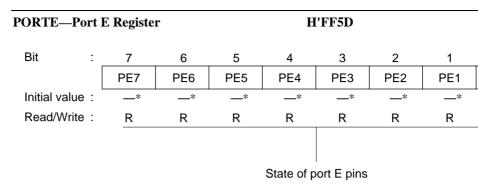

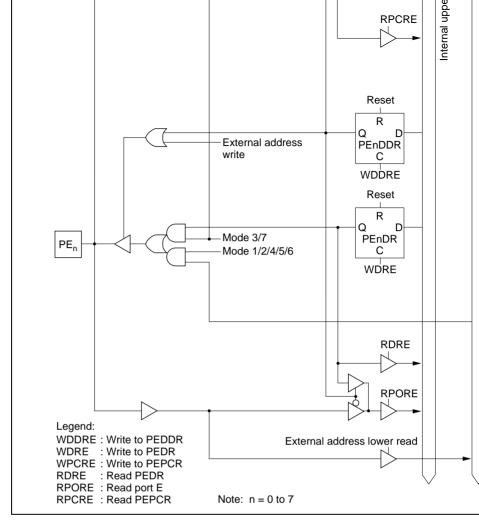

| 8.10   | Port E.  |                             |

|        | 8.10.1   | Overview                    |

|        | 8.10.2   | Register Configuration      |

|        | 8.10.3   | Pin Functions               |

|        | 8.10.4   | MOS Input Pull-Up Function  |

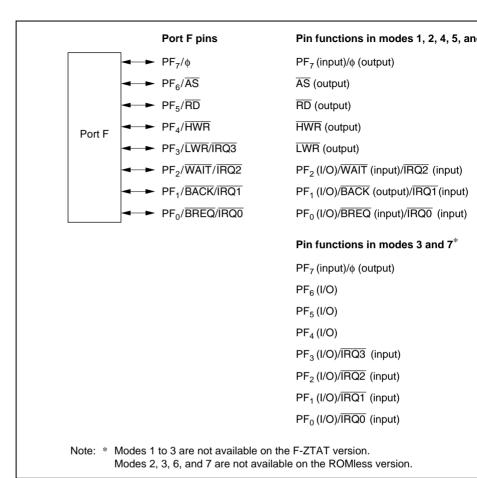

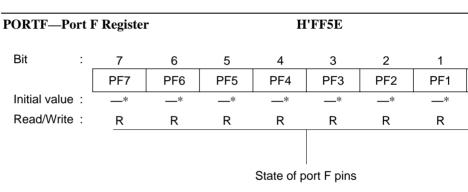

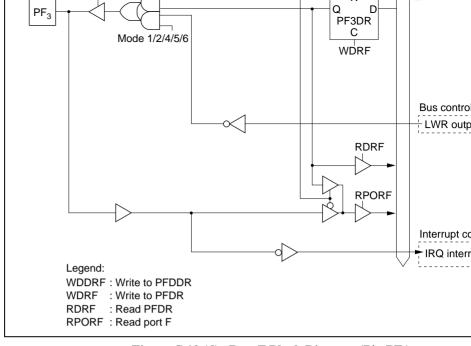

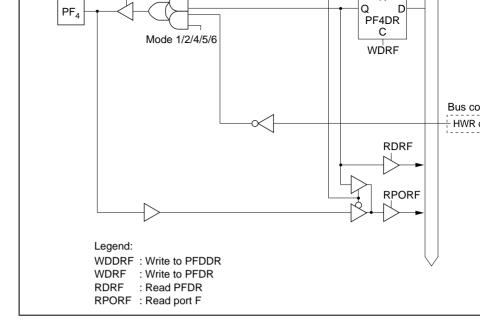

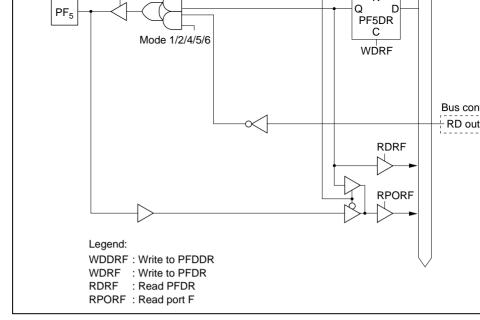

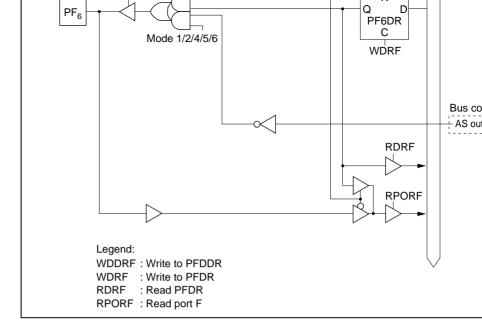

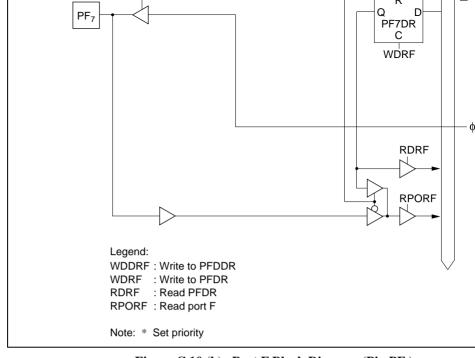

| 8.11   | Port F   |                             |

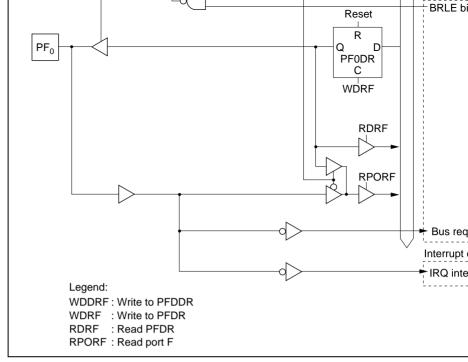

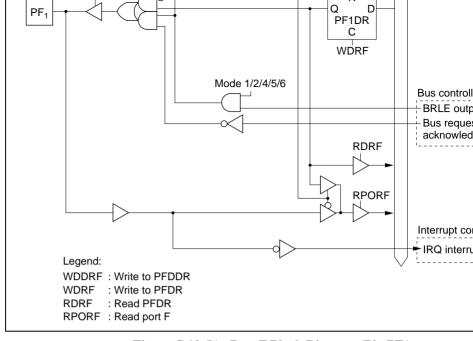

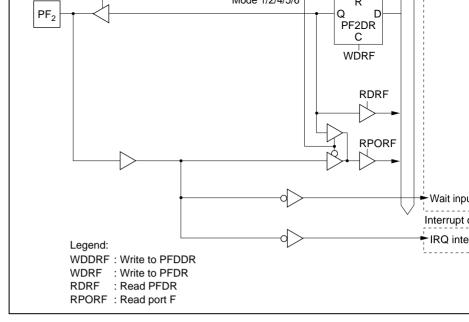

|        | 8.11.1   | Overview                    |

|        | 8.11.2   | Register Configuration      |

|        | 8.11.3   | Pin Functions               |

|        |          |                             |

| Rev. 4 | 4.00 Feb | o 15, 2006 page xiv of xxiv |

Overview.....

Register Configuration.....

Pin Functions

Overview.....

Register Configuration.....

Pin Functions MOS Input Pull-Up Function....

Overview.....

Register Configuration....

RENESAS

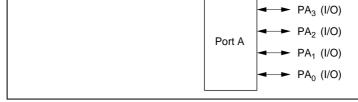

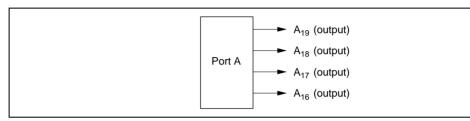

Port A.....

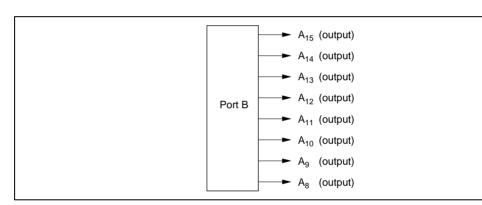

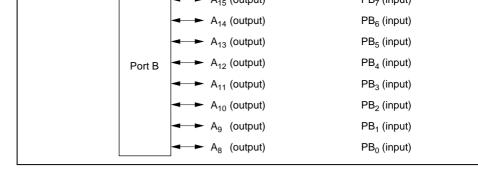

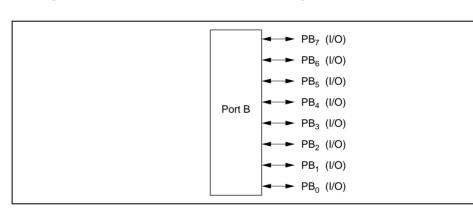

Port B

8.5.1

8.5.2

8.5.3

8.6.1

8.6.2

8.6.3

8.6.4

8.7.1

8.7.2

8.6

8.7

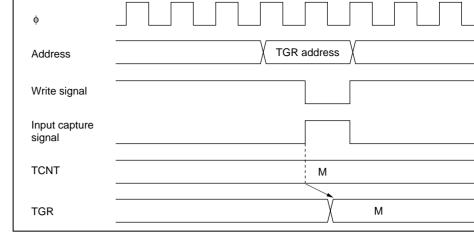

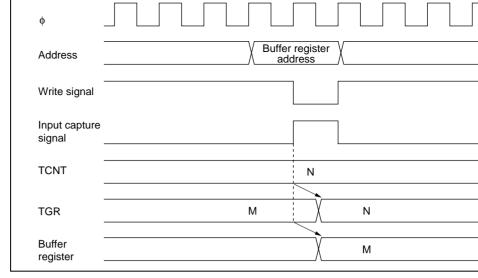

|     | 9.2.2    | Timer Mode Register (TMDR)             |

|-----|----------|----------------------------------------|

|     | 9.2.3    | Timer I/O Control Register (TIOR)      |

|     | 9.2.4    | Timer Interrupt Enable Register (TIER) |

|     | 9.2.5    | Timer Status Register (TSR)            |

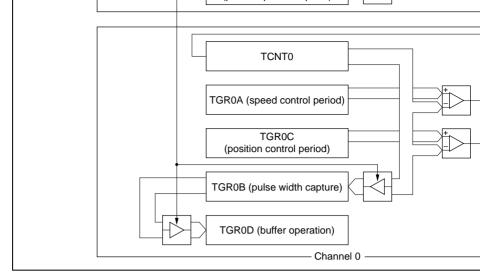

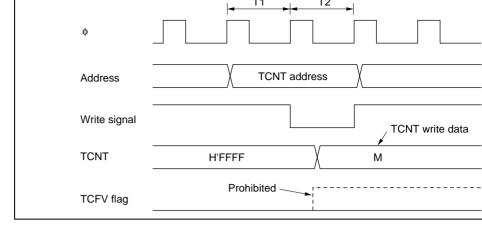

|     | 9.2.6    | Timer Counter (TCNT)                   |

|     | 9.2.7    | Timer General Register (TGR)           |

|     | 9.2.8    | Timer Start Register (TSTR)            |

|     | 9.2.9    | Timer Synchro Register (TSYR)          |

|     | 9.2.10   | Module Stop Control Register (MSTPCR)  |

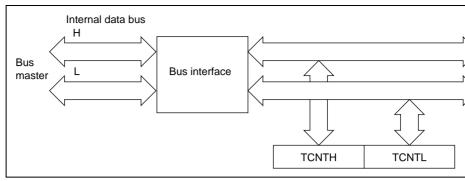

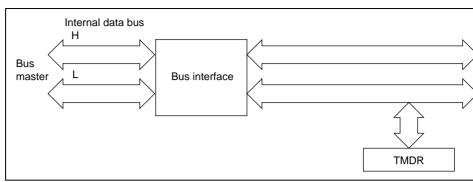

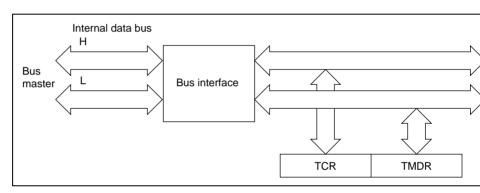

| 9.3 | Interfac | ce to Bus Master                       |

|     | 9.3.1    | 16-Bit Registers                       |

|     | 9.3.2    | 8-Bit Registers                        |

| 9.4 | Operat   | ion                                    |

|     | 9.4.1    | Overview                               |

|     | 9.4.2    | Basic Functions                        |

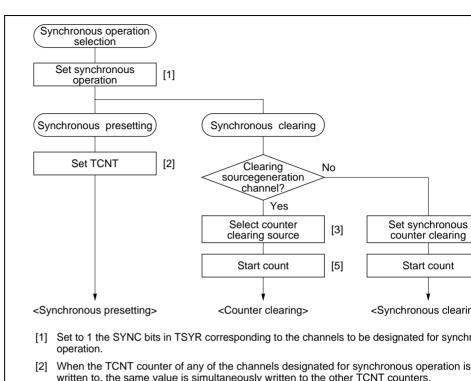

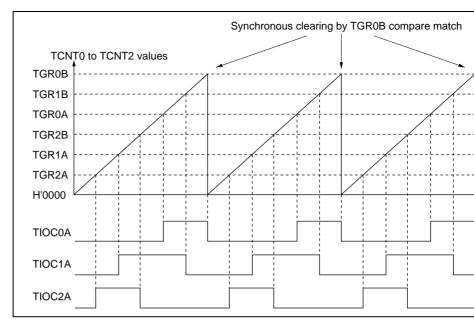

|     | 9.4.3    | Synchronous Operation                  |

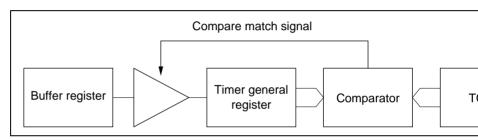

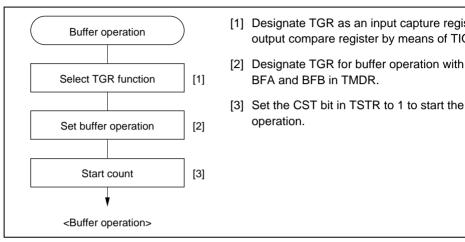

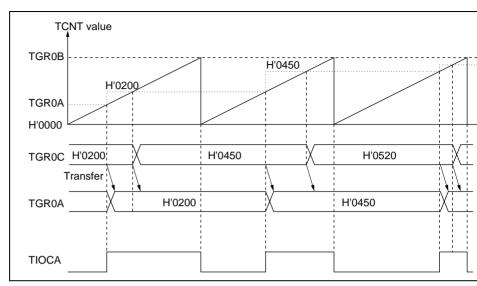

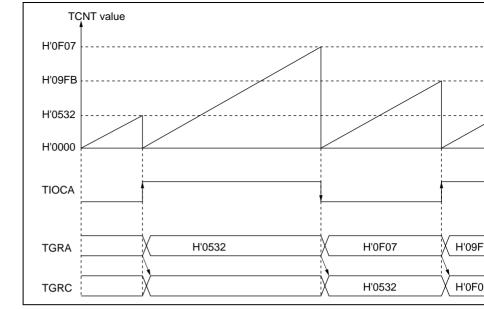

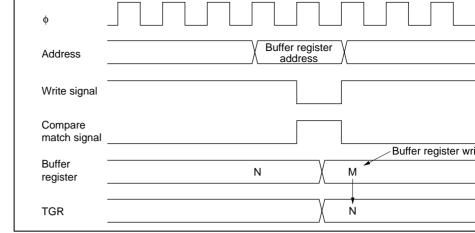

|     | 9.4.4    | Buffer Operation                       |

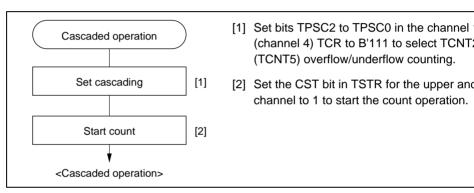

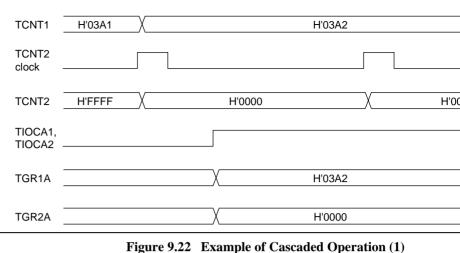

|     | 9.4.5    | Cascaded Operation                     |

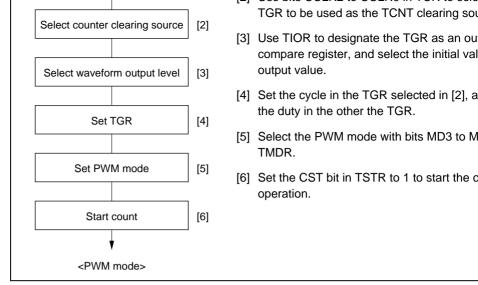

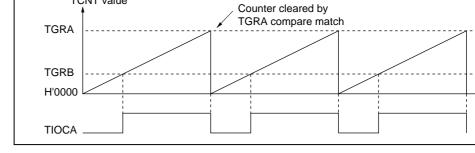

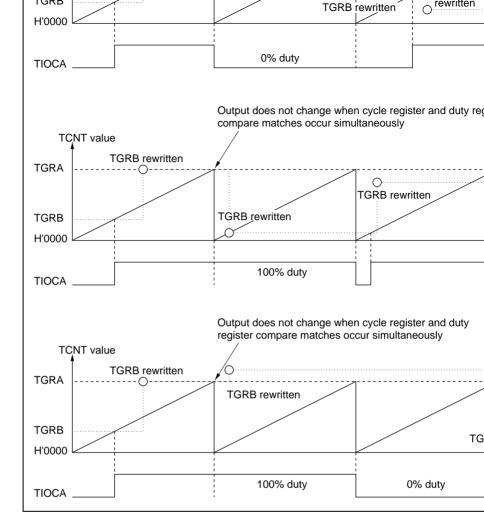

|     | 9.4.6    | PWM Modes                              |

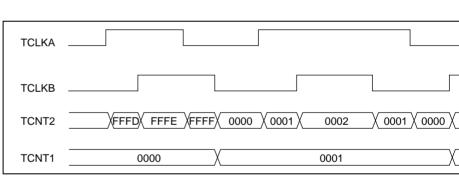

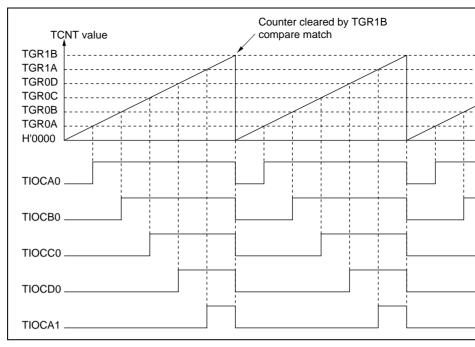

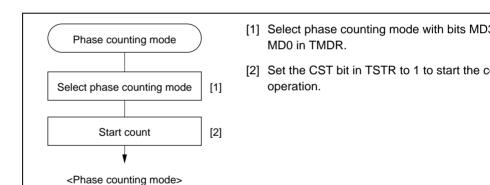

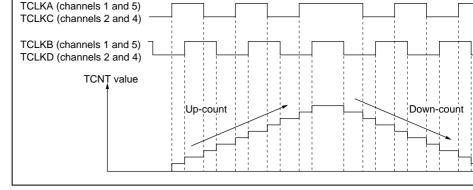

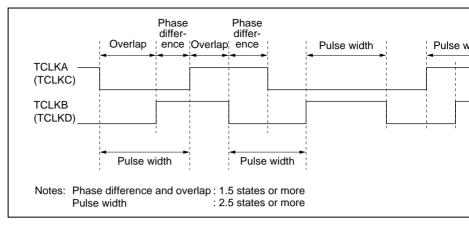

|     | 9.4.7    | Phase Counting Mode                    |

| 9.5 | Interru  | pts                                    |

|     | 9.5.1    | Interrupt Sources and Priorities       |

|     | 9.5.2    | DTC Activation                         |

|     | 9.5.3    | A/D Converter Activation               |

| 9.6 | Operat   | ion Timing                             |

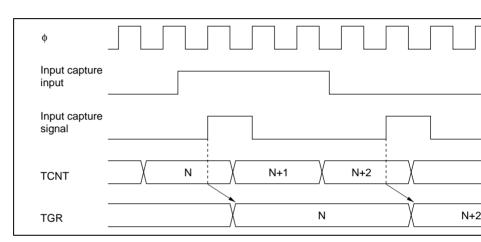

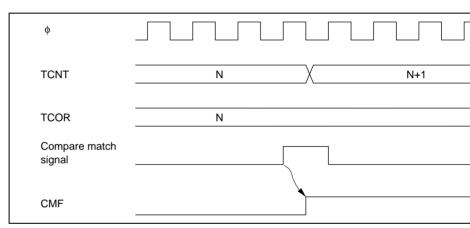

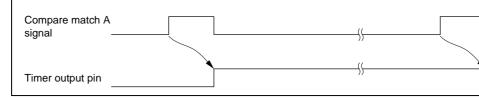

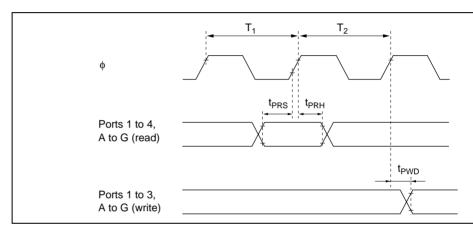

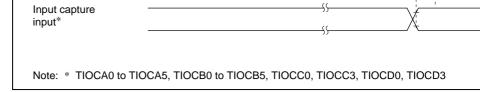

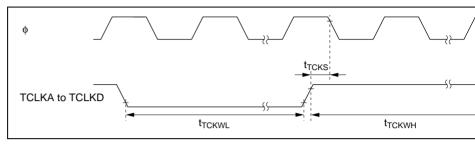

|     | 9.6.1    | Input/Output Timing                    |

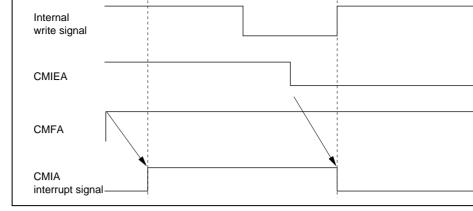

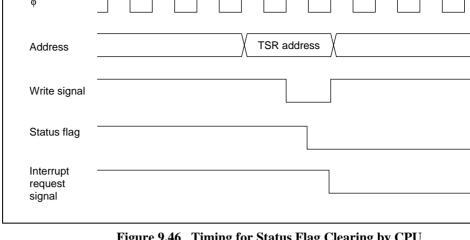

|     | 9.6.2    | Interrupt Signal Timing                |

| 9.7 | Usage    | Notes                                  |

|     |          | Rev. 4.00 Feb 15, 2006 pa              |

|     |          | ·                                      |

|     |          | RENESAS                                |

|     |          |                                        |

|     |          |                                        |

Pin Configuration.....

Register Configuration.....

Timer Control Register (TCR).....

Register Descriptions

9.1.3

9.1.4

9.2.1

9.2

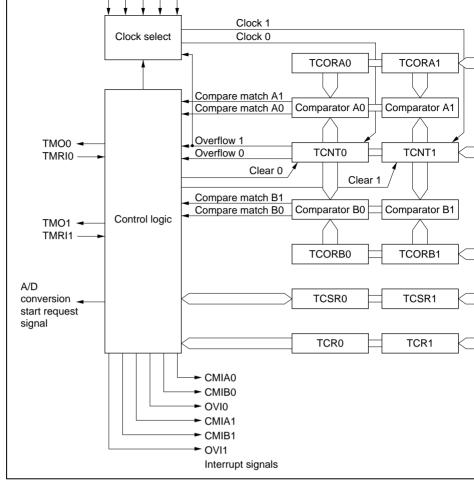

|       | 10.2.6  | Module Stop Control Register (MSTPCR)           |

|-------|---------|-------------------------------------------------|

| 10.3  |         | ion                                             |

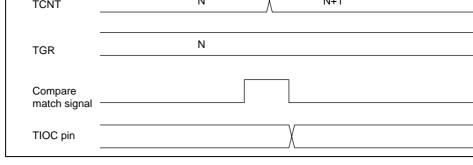

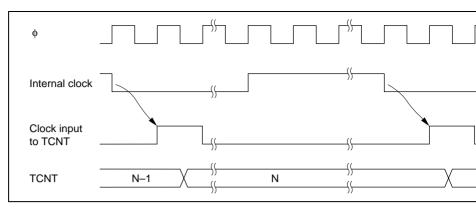

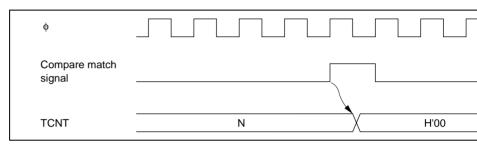

|       |         | TCNT Incrementation Timing                      |

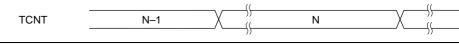

|       |         | Compare Match Timing                            |

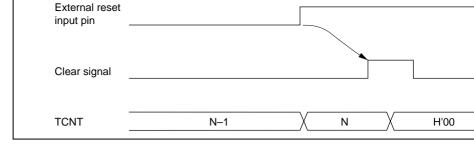

|       |         | Timing of External RESET on TCNT                |

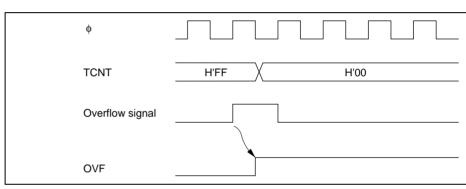

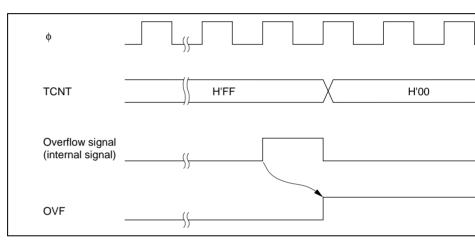

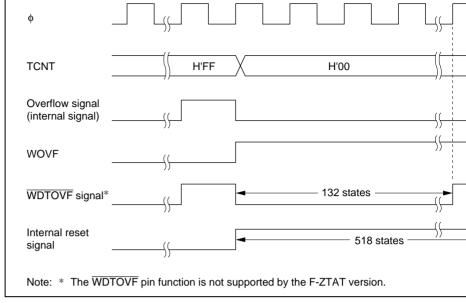

|       |         | Timing of Overflow Flag (OVF) Setting           |

|       |         | Operation with Cascaded Connection              |

| 10.4  |         | pts                                             |

|       |         | Interrupt Sources and DTC Activation            |

|       |         | A/D Converter Activation                        |

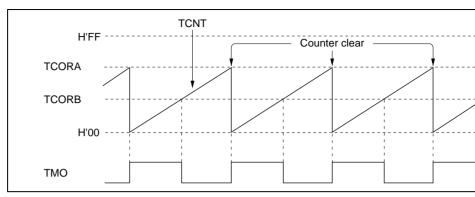

| 10.5  |         | Application                                     |

| 10.6  | Usage 1 | Notes                                           |

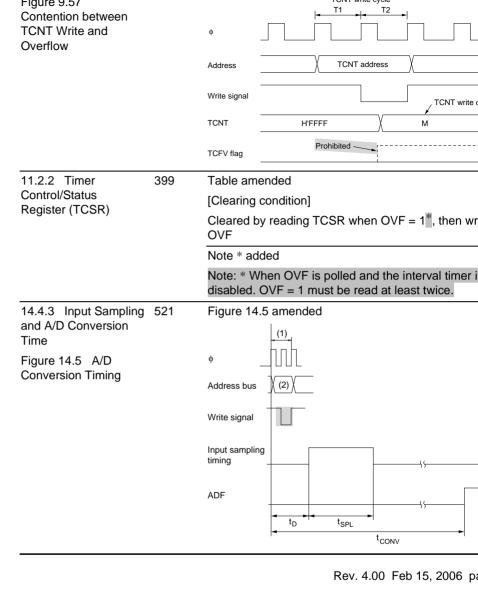

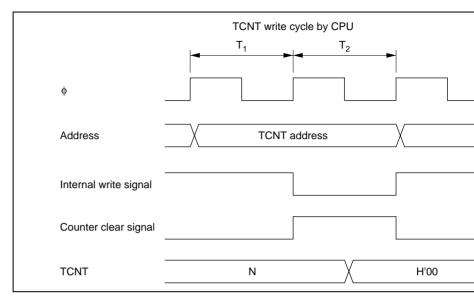

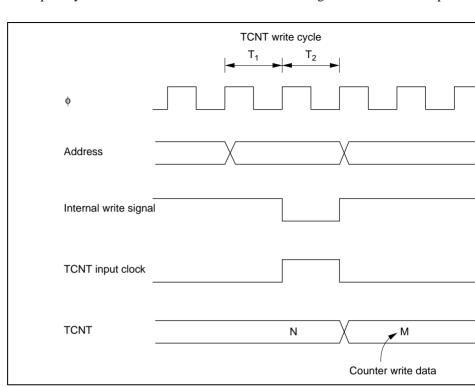

|       | 10.6.1  | Contention between TCNT Write and Clear         |

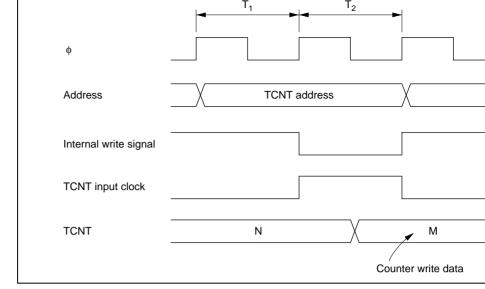

|       | 10.6.2  | Contention between TCNT Write and Increment     |

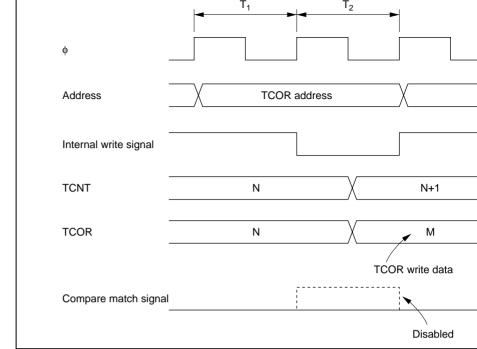

|       | 10.6.3  | Contention between TCOR Write and Compare Match |

|       | 10.6.4  | Contention between Compare Matches A and B      |

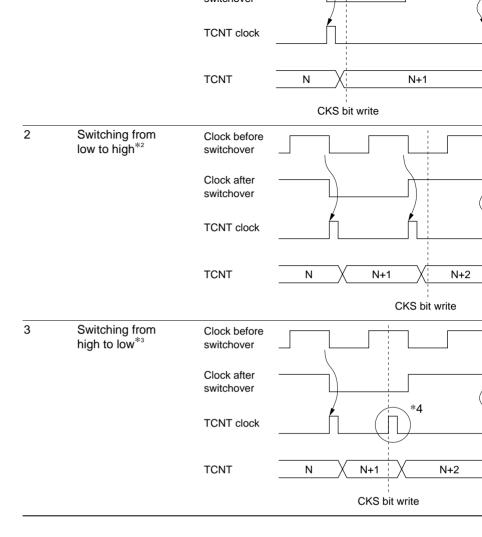

|       | 10.6.5  | Switching of Internal Clocks and TCNT Operation |

|       | 10.6.6  | Usage Note                                      |

|       |         |                                                 |

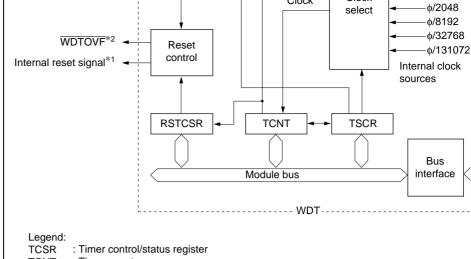

| Secti | ion 11  | Watchdog Timer                                  |

| 11.1  | Overvi  | ew                                              |

|       | 11.1.1  | Features                                        |

|       | 11.1.2  | Block Diagram                                   |

|       | 11.1.3  | Pin Configuration                               |

Rev. 4.00 Feb 15, 2006 page xvi of xxiv

10.2.3 Time Constant Registers B0 and B1 (TCORB0, TCORB1)

10.2.4 Time Control Registers 0 and 1 (TCR0, TCR1)

10.2.5 Timer Control/Status Registers 0 and 1 (TCSR0, TCSR1)

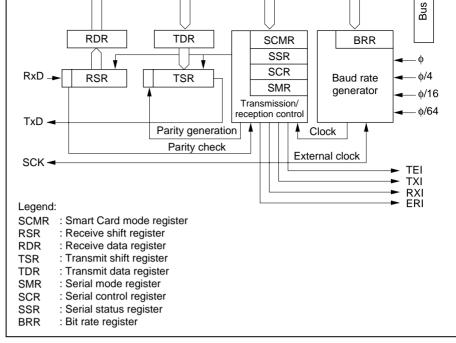

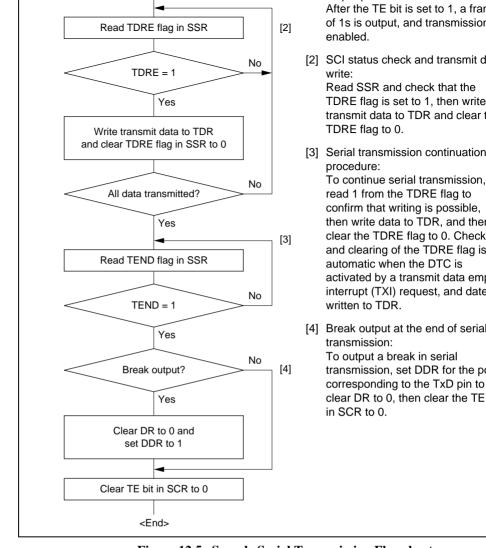

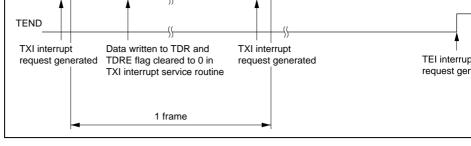

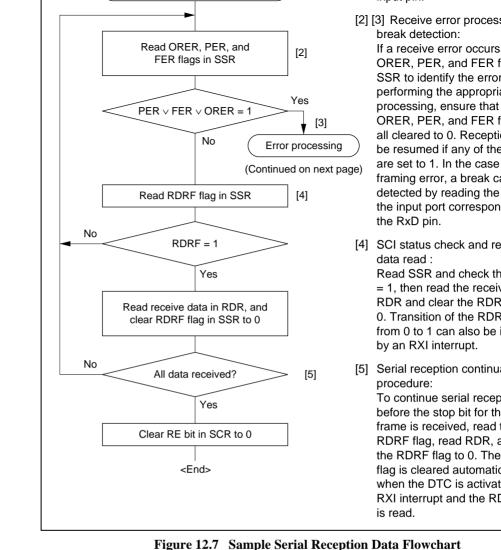

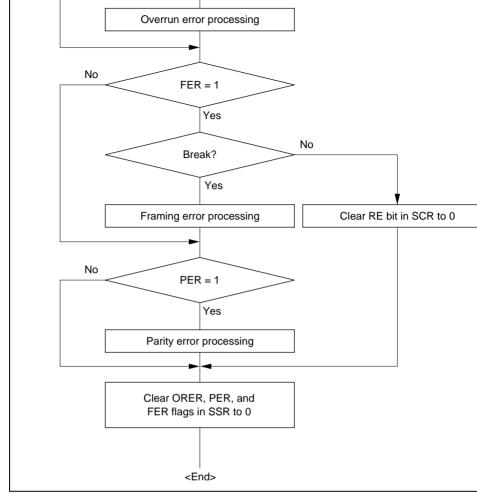

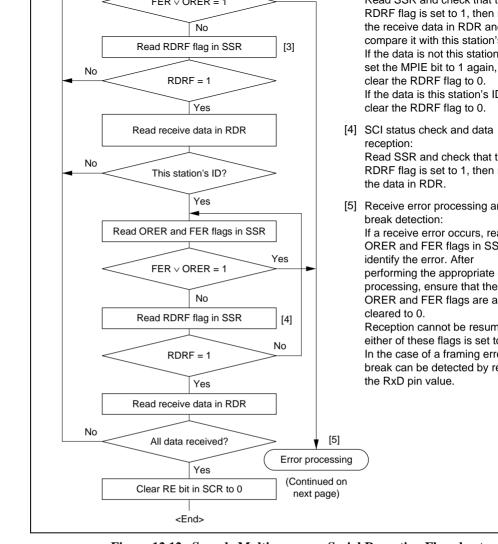

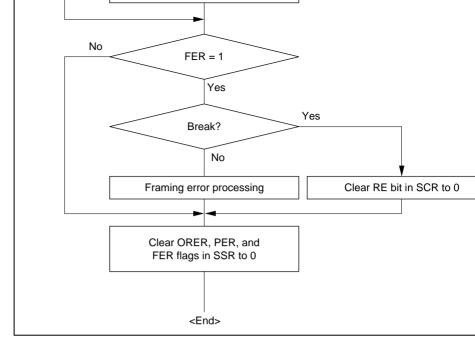

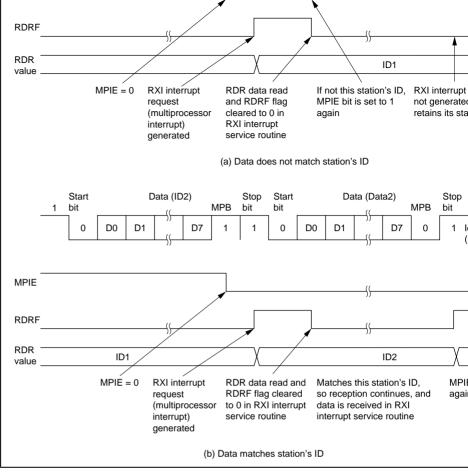

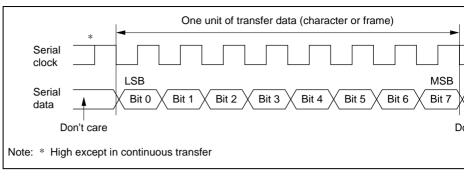

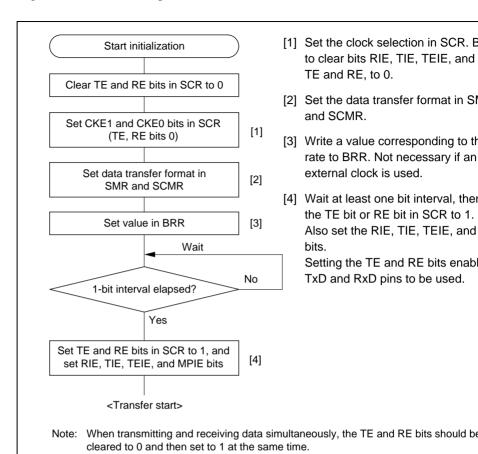

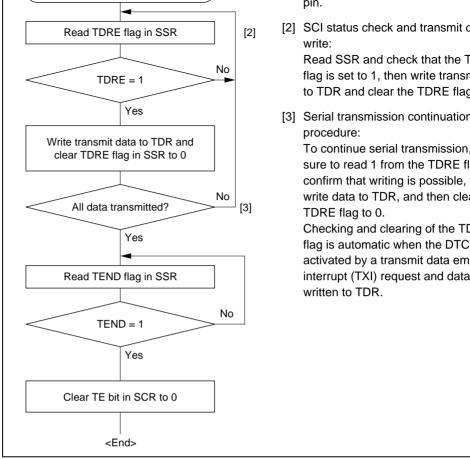

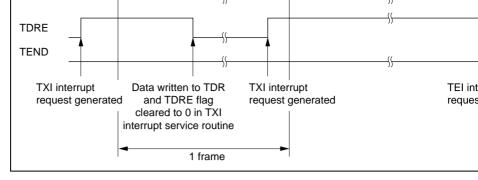

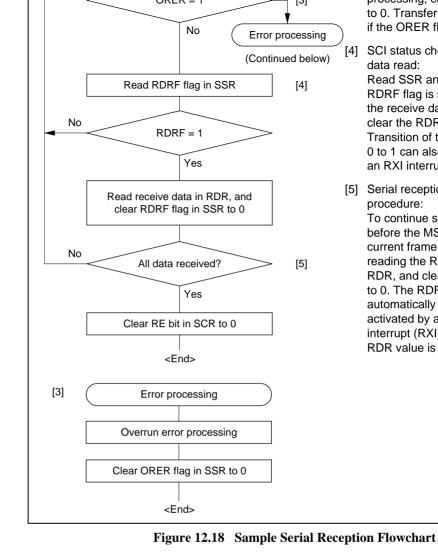

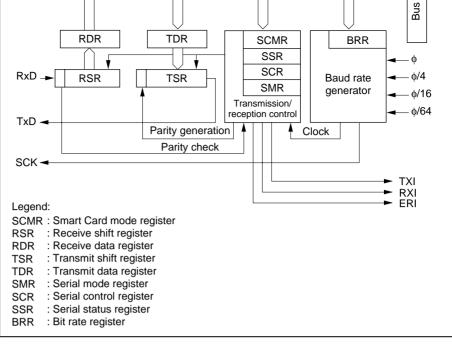

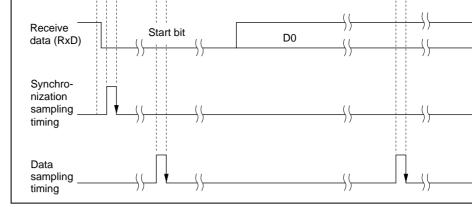

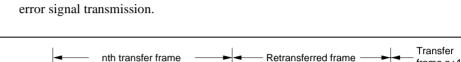

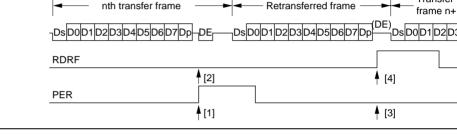

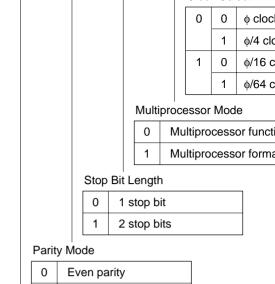

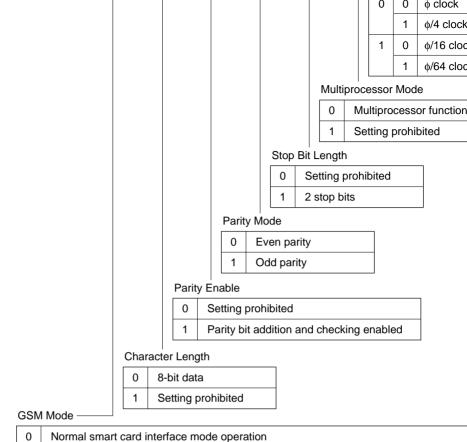

| Sect | ion 12   | Serial Communication Interface (SCI)  |

|------|----------|---------------------------------------|

| 12.1 | Overvie  | ew                                    |

|      | 12.1.1   | Features                              |

|      | 12.1.2   | Block Diagram                         |

|      | 12.1.3   | Pin Configuration                     |

|      | 12.1.4   | Register Configuration                |

| 12.2 | Registe  | r Descriptions                        |

|      | 12.2.1   | Receive Shift Register (RSR)          |

|      | 12.2.2   | Receive Data Register (RDR)           |

|      | 12.2.3   | Transmit Shift Register (TSR)         |

|      | 12.2.4   | Transmit Data Register (TDR)          |

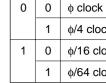

|      | 12.2.5   | Serial Mode Register (SMR)            |

|      | 12.2.6   | Serial Control Register (SCR)         |

|      | 12.2.7   | Serial Status Register (SSR)          |

|      | 12.2.8   | Bit Rate Register (BRR)               |

|      | 12.2.9   | Smart Card Mode Register (SCMR)       |

|      | 12.2.10  | Module Stop Control Register (MSTPCR) |

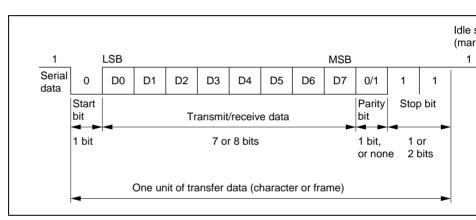

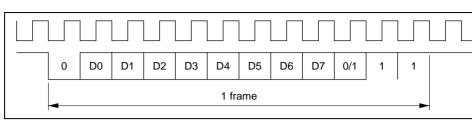

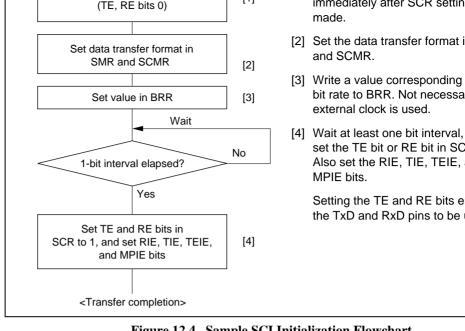

| 12.3 | Operati  | on                                    |

|      | 12.3.1   | Overview                              |

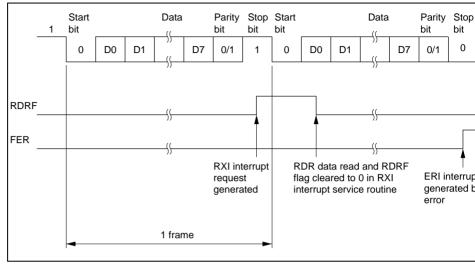

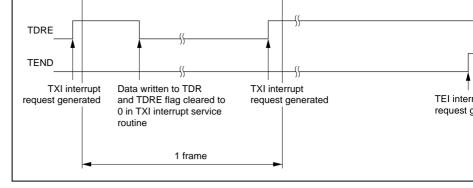

|      | 12.3.2   | Operation in Asynchronous Mode        |

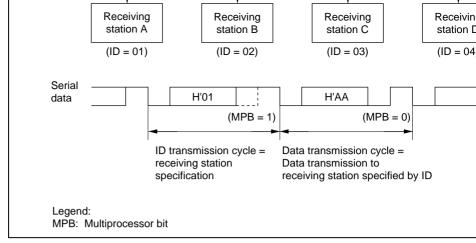

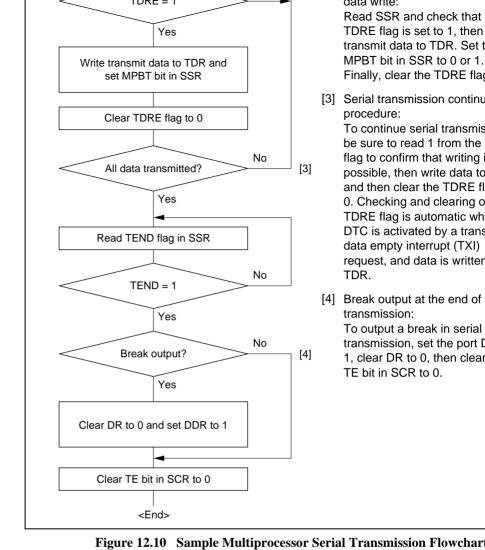

|      | 12.3.3   | Multiprocessor Communication Function |

|      | 12.3.4   | Operation in Clocked Synchronous Mode |

| 12.4 | SCI Inte | errupts                               |

| 12.5 | Usage I  | Notes                                 |

|      |          |                                       |

| Sect | ion 13   | Smart Card Interface                  |

| 13.1 | Overvie  | ew                                    |

|      |          | Day 4.00 Fab 45, 2000 ma              |

|      |          | Rev. 4.00 Feb 15, 2006 pa             |

|      |          | RENESAS                               |

|      |          |                                       |

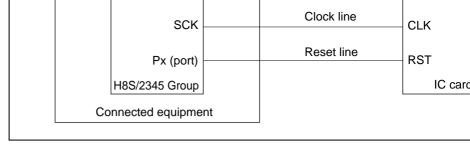

|      | 13.3.1   | Overview                                   |

|------|----------|--------------------------------------------|

|      | 13.3.2   | Pin Connections                            |

|      | 13.3.3   | Data Format                                |

|      | 13.3.4   | Register Settings                          |

|      | 13.3.5   | Clock                                      |

|      | 13.3.6   | Data Transfer Operations                   |

|      | 13.3.7   | Operation in GSM Mode                      |

| 13.4 | Usage    | Note                                       |

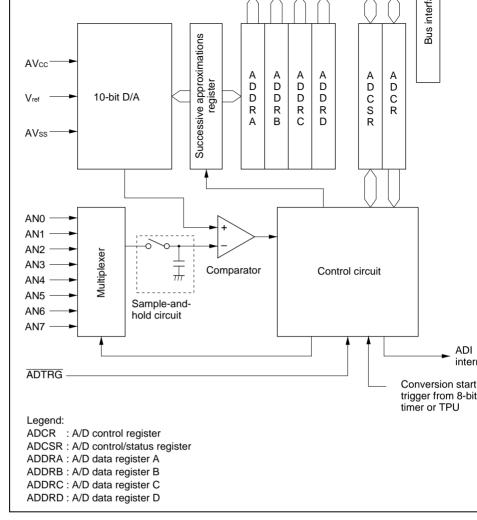

| Sect | ion 14   | A/D Converter                              |

| 14.1 | Overvi   | ew                                         |

|      | 14.1.1   | Features                                   |

|      | 14.1.2   | Block Diagram                              |

|      | 14.1.3   | Pin Configuration                          |

|      | 14.1.4   | Register Configuration                     |

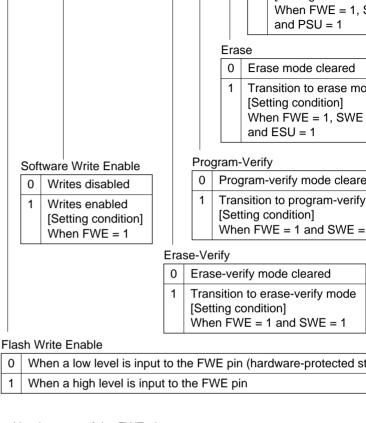

| 14.2 | Registe  | er Descriptions                            |

|      | 14.2.1   | A/D Data Registers A to D (ADDRA to ADDRD) |

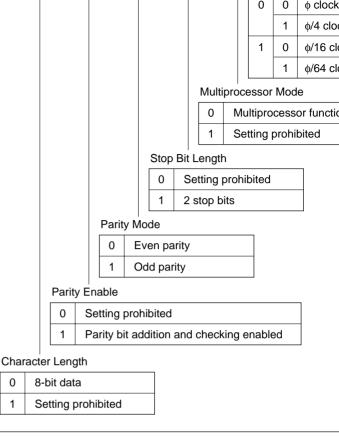

|      | 14.2.2   | A/D Control/Status Register (ADCSR)        |

|      | 14.2.3   | A/D Control Register (ADCR)                |

|      | 14.2.4   | Module Stop Control Register (MSTPCR)      |

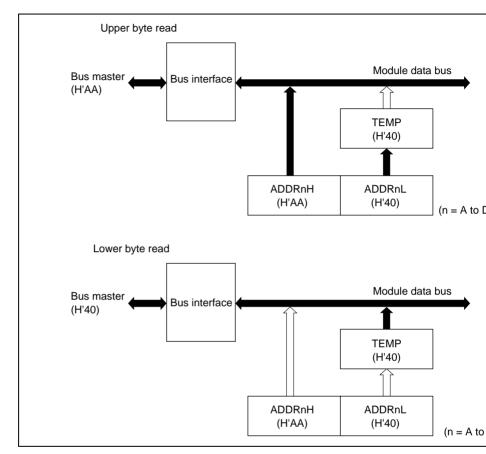

| 14.3 | Interfac | ce to Bus Master                           |

| 14.4 | Operat   | ion                                        |

|      | 14.4.1   | Single Mode (SCAN = 0)                     |

|      | 14.4.2   | Scan Mode (SCAN = 1)                       |

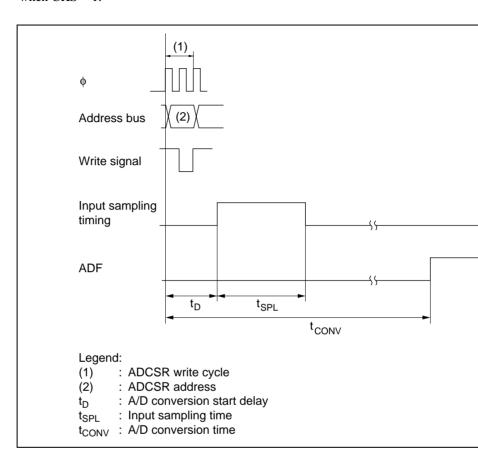

|      | 14.4.3   | Input Sampling and A/D Conversion Time     |

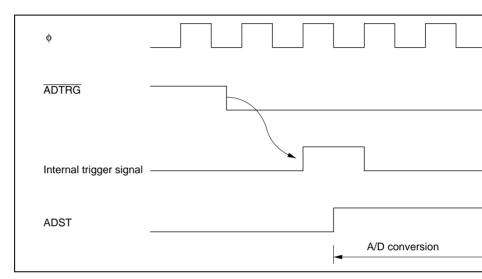

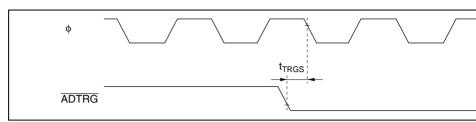

|      | 14.4.4   | External Trigger Input Timing              |

| 14.5 | Interru  | pts                                        |

| 14.6 | Usage    | Notes                                      |

|      |          |                                            |

13.3 Operation .....

Rev. 4.00 Feb 15, 2006 page xviii of xxiv

RENESAS

|      | 16.2.1  | System Control Register (SYSCR) |

|------|---------|---------------------------------|

| 16.3 | Operat  | ion                             |

| 16.4 | Usage   | Note                            |

| Sect | ion 17  | ROM                             |

| 17.1 |         | ew                              |

|      | 17.1.1  | Block Diagram                   |

|      | 17.1.2  | Register Configuration          |

| 17.2 | Registe | er Descriptions                 |

|      | 17.2.1  | Mode Control Register (MDCR)    |

|      | 17.2.2  | Bus Control Register L (BCRL)   |

| 17.3 | Operat  | ion                             |

| 17.4 | PROM    | Mode                            |

|      | 17.4.1  | PROM Mode Setting               |

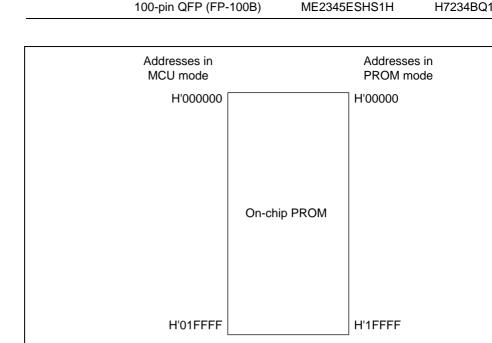

|      | 17.4.2  | Socket Adapter and Memory Map   |

| 17.5 | Program | mming                           |

|      | 17.5.1  | Overview                        |

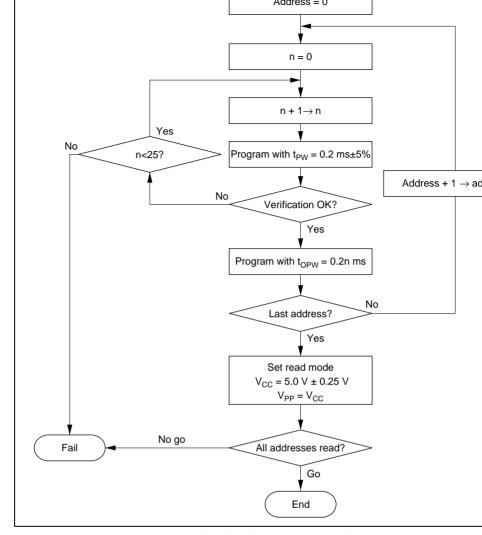

|      |         | Programming and Verification    |

|      | 17.5.3  | Programming Precautions         |

|      | 17.5.4  | Reliability of Programmed Data  |

| 17.6 | Overvi  | ew of Flash Memory              |

|      | 17.6.1  | Features                        |

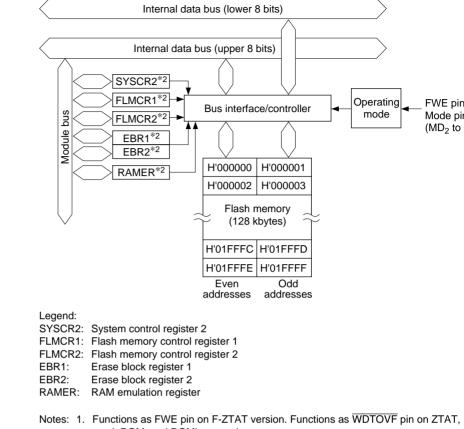

|      | 17.6.2  | Block Diagram                   |

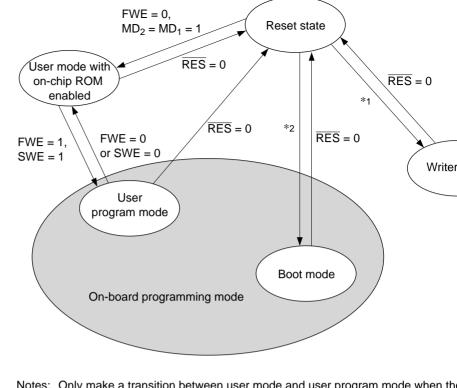

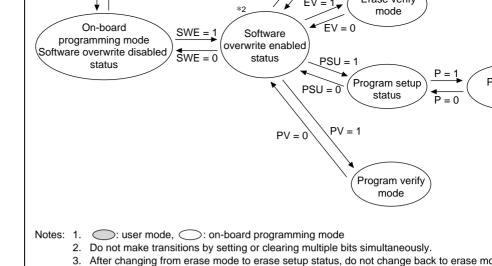

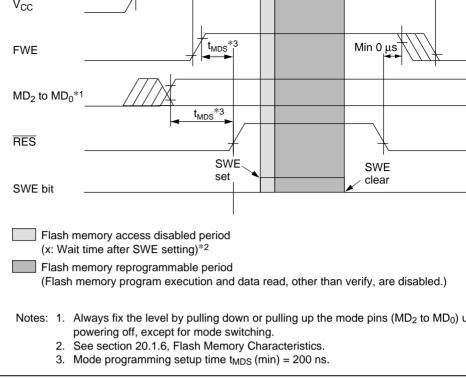

|      | 17.6.3  | Flash Memory Operating Modes    |

|      | 17.6.4  | Pin Configuration               |

|      |         | Rev. 4.00 Feb 15, 2006 pa       |

|      |         | 2-1                             |

15.4 Usage Notes .....

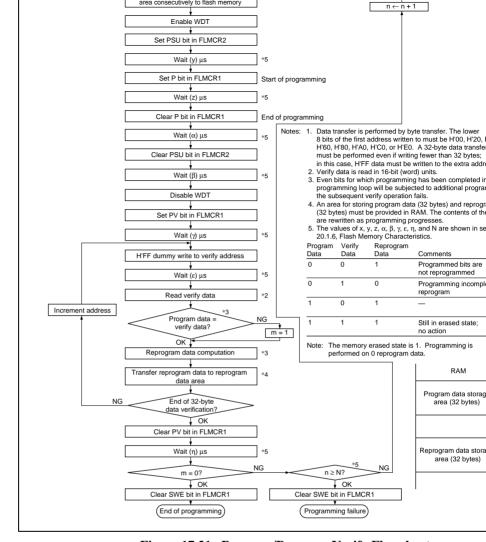

| 17.9 Programming/Erasing Flash Memory                                         |

|-------------------------------------------------------------------------------|

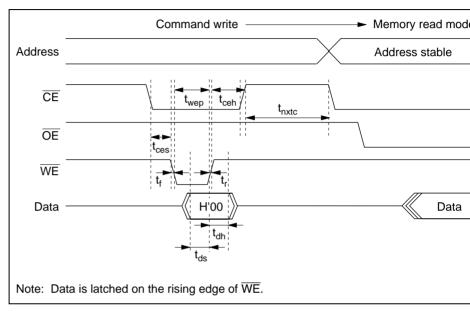

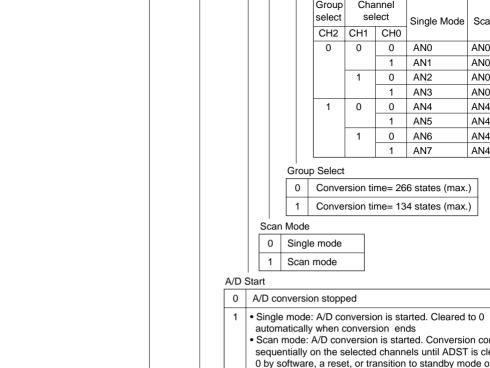

| 17.9.1 Program Mode                                                           |

| 17.9.2 Program-Verify Mode                                                    |

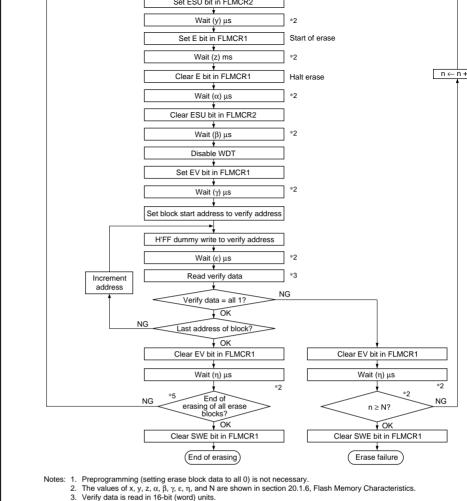

| 17.9.3 Erase Mode                                                             |

| 17.9.4 Erase-Verify Mode                                                      |

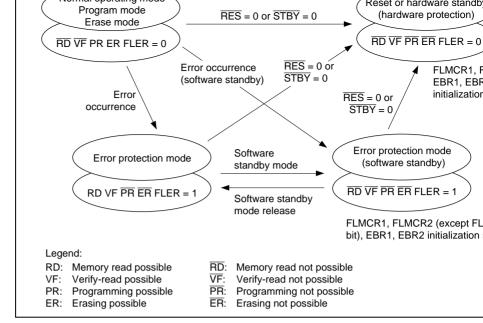

| 17.10 Flash Memory Protection                                                 |

| 17.10.1 Hardware Protection                                                   |

| 17.10.2 Software Protection                                                   |

| 17.10.3 Error Protection                                                      |

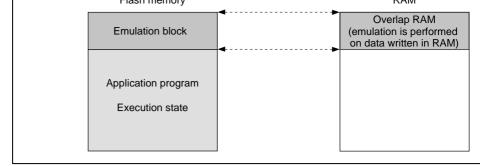

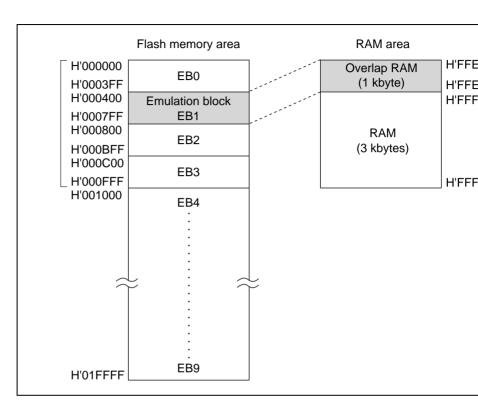

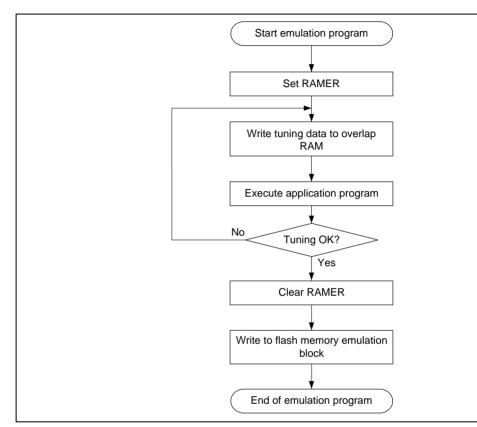

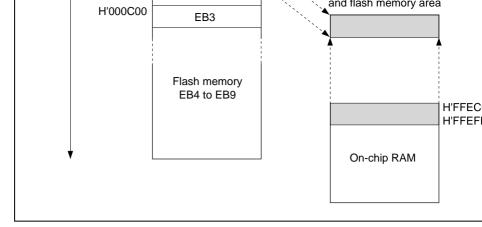

| 17.11 Flash Memory Emulation in RAM                                           |

| 17.11.1 Emulation in RAM                                                      |

| 17.11.2 RAM Overlap                                                           |

| 17.12 Interrupt Handling when Programming/Erasing Flash Memory                |

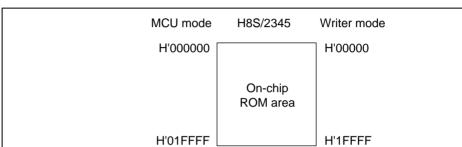

| 17.13 Flash Memory Writer Mode                                                |

| 17.13.1 Writer Mode Setting                                                   |

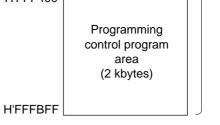

| 17.13.2 Socket Adapters and Memory Map                                        |

| 17.13.3 Writer Mode Operation                                                 |

| 17.13.4 Memory Read Mode                                                      |

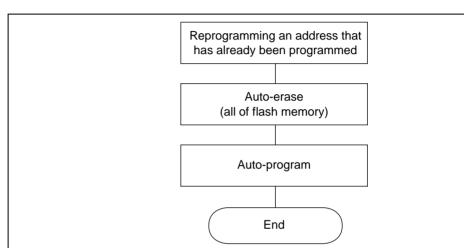

| 17.13.5 Auto-Program Mode                                                     |

| 17.13.6 Auto-Erase Mode                                                       |

| 17.13.7 Status Read Mode                                                      |

| 17.13.8 Status Polling                                                        |

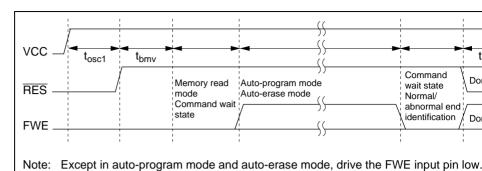

| 17.13.9 Writer Mode Transition Time                                           |

| 17.13.10 Notes On Memory Programming                                          |

| 17.14 Flash Memory Programming and Erasing Precautions                        |

| 17.15 Notes when Converting the F–ZTAT Application Software to the Mask-ROM V |

| Section 18 Clock Pulse Generator                                              |

| ~~~···································                                        |

Rev. 4.00 Feb 15, 2006 page xx of xxiv

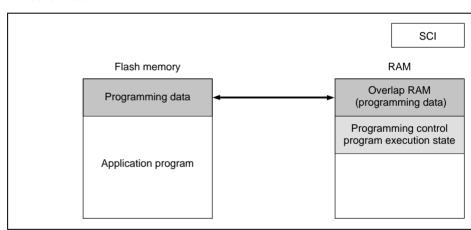

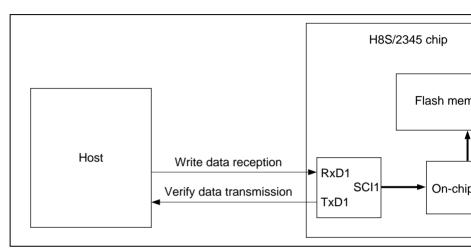

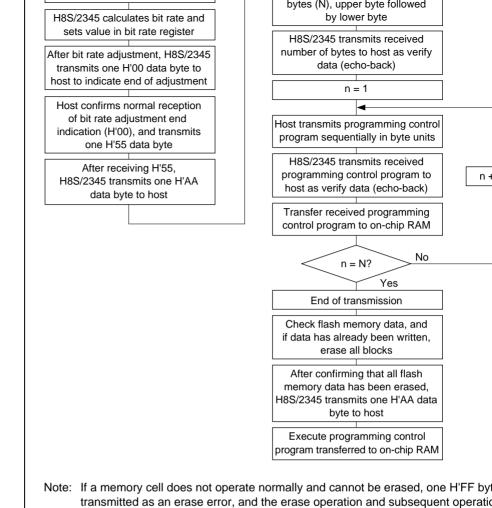

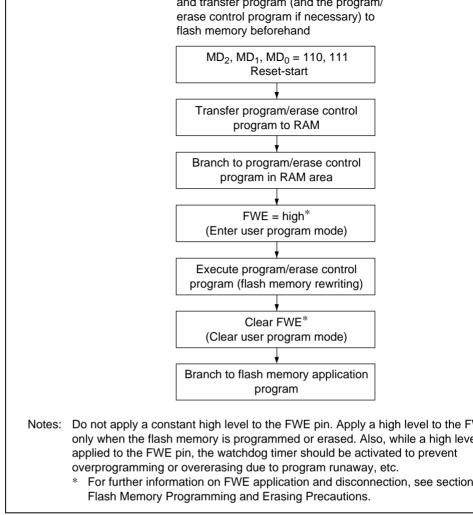

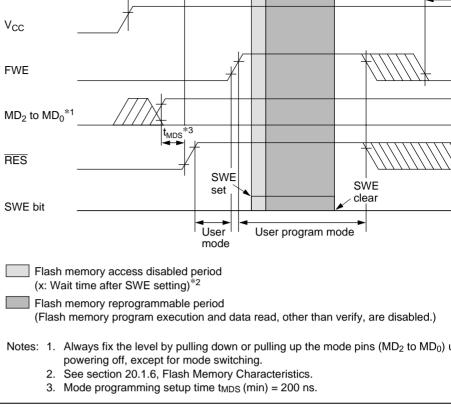

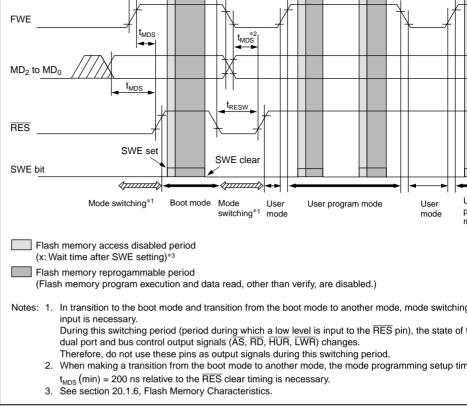

17.8.2 User Program Mode.....

RENESAS

|       | 19.2.3   | Module Stop Control Register (MSTPCR)                                  |

|-------|----------|------------------------------------------------------------------------|

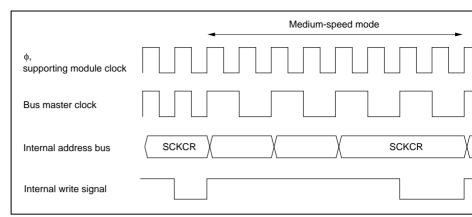

| 19.3  | Mediur   | n-Speed Mode                                                           |

| 19.4  |          | Mode                                                                   |

| 19.5  | -        | Stop Mode                                                              |

|       |          | Module Stop Mode                                                       |

|       |          | Usage Notes                                                            |

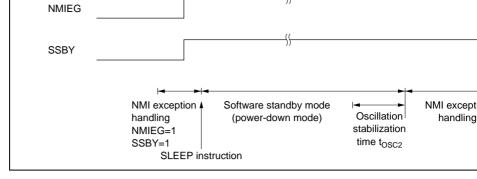

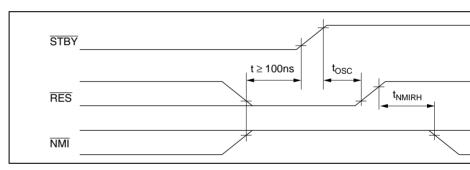

| 19.6  |          | re Standby Mode                                                        |

|       |          | Software Standby Mode                                                  |

|       |          | Clearing Software Standby Mode                                         |

|       |          | Setting Oscillation Stabilization Time after Clearing Software Standby |

|       |          | Software Standby Mode Application Example                              |

|       |          | Usage Notes                                                            |

| 19.7  |          | are Standby Mode                                                       |

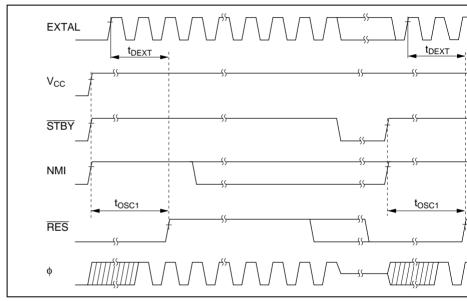

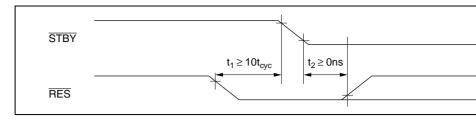

|       | 19.7.1   | Hardware Standby Mode                                                  |

|       |          | Hardware Standby Mode Timing                                           |

| 19.8  | φ Clock  | COutput Disabling Function                                             |

|       |          |                                                                        |

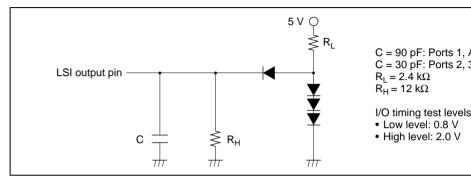

| Secti | ion 20   | Electrical Characteristics                                             |

| 20.1  | Electric | eal Characteristics of F-ZTAT Version                                  |

|       | 20.1.1   | Absolute Maximum Ratings                                               |

|       | 20.1.2   | DC Characteristics                                                     |

|       | 20.1.3   | AC Characteristics                                                     |

|       | 20.1.4   | A/D Conversion Characteristics                                         |

|       | 20.1.5   | D/A Conversion Characteristics                                         |

|       | 20.1.6   | Flash Memory Characteristics                                           |

| 20.2  | Electric | cal Characteristics of ZTAT, Mask ROM, and ROMless Versions            |

|       |          |                                                                        |

19.2

Section 19 Power-Down Modes

19.1 Overview

19.1.1 Register Configuration.

Register Descriptions

19.2.1 Standby Control Register (SBYCR)

19.2.2 System Clock Control Register (SCKCR)

Rev. 4.00 Feb 15, 2006 pa

| •••• |

|------|

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

|      |

| •••• |

|      |

|      |

20.3.4 Timing for On-Chip Supporting Modules.....

Rev. 4.00 Feb 15, 2006 page xxii of xxiv

Rev. 4.00 Feb 15, 2006 pag

Rev. 4.00 Feb 15, 2006 page xxiv of xxiv

The H8S/2000 CPU has an internal 32-bit architecture, is provided with sixteen 16-bit registers and a concise, optimized instruction set designed for high-speed operation, a address a 16-Mbyte linear address space. The instruction set is upward-compatible wi and H8/300H CPU instructions at the object-code level, facilitating migration from th

On-chip peripheral functions required for system configuration include data transfer c (DTC) bus masters, ROM and RAM, a 16-bit timer-pulse unit (TPU), an 8-bit timer, a timer (WDT), a serial communication interface (SCI), an A/D converter, a D/A conve

The on-chip ROM\*1 is either single power supply flash memory (F-ZTAT<sup>TM</sup>\*2), PRO

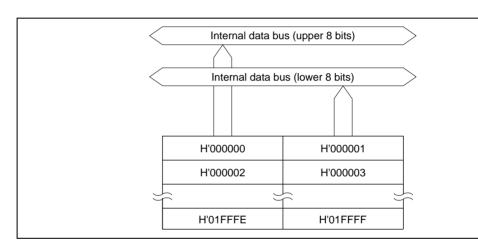

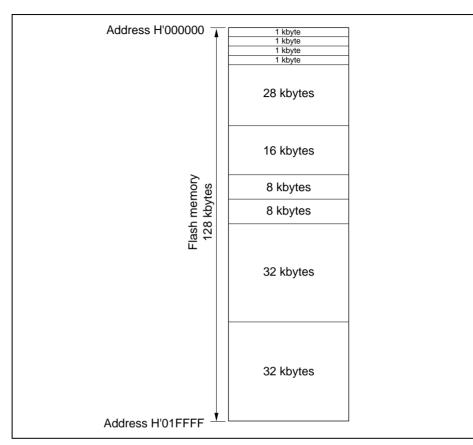

(ZTAT®\*2), or mask ROM, with a capacity of 128, 96, 64, or 32 kbytes. ROM is con-CPU via a 16-bit data bus, enabling both byte and word data to be accessed in one star Instruction fetching has been speeded up, and processing speed increased.

Seven operating modes, modes 1 to 7, are provided, and there is a choice of address specified and the choice of address specified are choice of address specified and the single-chip mode or external expansion mode.

The features of the H8S/2345 Group are shown in table 1.1.

H8/300L, or H8/300H Series.

ports.

Notes: 1. The H8S/2345, H8S/2344, H8S/2343, and H8S/2341 have on-chip ROM. H8S/2340 does not have on-chip ROM.

2. F-ZTAT is a trademark of Renesas Technology Corp.

ZTAT is a registered trademark of Renesas Technology Corp.

Rev. 4.00 Feb 15, 2006 p

REJ09

| <b>9</b>                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Sixty-five basic instructions</li> </ul>                                                                   |

| <ul> <li>8/16/32-bit move/arithmetic and logic instructions</li> </ul>                                              |

| <ul> <li>Unsigned/signed multiply and divide instructions</li> </ul>                                                |

| <ul> <li>— Powerful bit-manipulation instructions</li> </ul>                                                        |

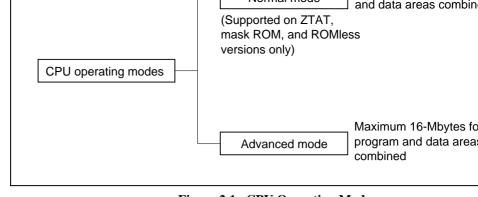

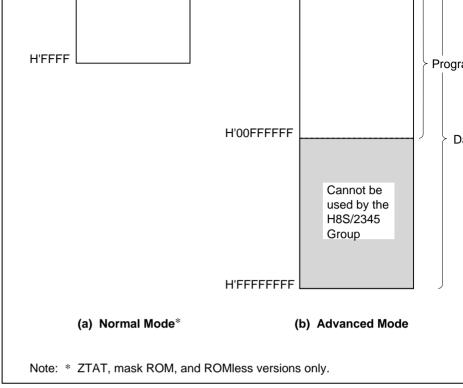

| Two CPU operating modes                                                                                             |

| <ul> <li>Normal mode: 64-kbyte address space (ZTAT, mask ROM,<br/>ROMless versions only)</li> </ul>                 |

| <ul> <li>Advanced mode: 16-Mbyte address space</li> </ul>                                                           |

| <ul> <li>Address space divided into 8 areas, with bus specifications set<br/>independently for each area</li> </ul> |

| Chip select output possible for areas 0 to 3                                                                        |

| Choice of 8-bit or 16-bit access space for each area                                                                |

| 2-state or 3-state access space can be designated for each are                                                      |

| Number of program wait states can be set for each area                                                              |

| Burst ROM directly connectable                                                                                      |

| External bus release function                                                                                       |

| _                                                                                                                   |

High-speed arithmetic operations

16 × 16-bit register-register multiply

Instruction set suitable for high-speed operation

32 ÷ 16-bit register-register divide

8/16/32-bit register-register add/subtract : 50 ns

: 1000 ns

: 1000 ns

source

Can be activated by internal interrupt or software

Multiple transfers or multiple types of transfer possible for one

Transfer is possible in repeat mode, block transfer mode, etc. Request can be sent to CPU for interrupt that activated DTC

Data transfer

controller (DTC)

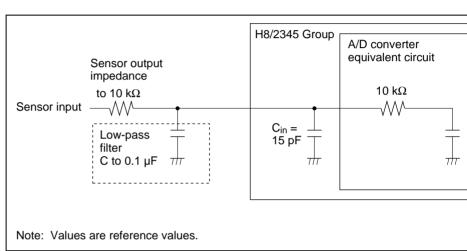

| A/D converter        | Resolution: 10 bits                                                                      |                                                                 |          |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|--|--|--|--|

|                      | Input: 8 channels                                                                        |                                                                 |          |  |  |  |  |

|                      | <ul> <li>High-speed conversion: 6.7 μs minimum conversion time (at operation)</li> </ul> |                                                                 |          |  |  |  |  |

|                      | Single or scan mode selectable                                                           |                                                                 |          |  |  |  |  |

|                      | Sample and hold circ                                                                     | cuit                                                            |          |  |  |  |  |

|                      | A/D conversion can be                                                                    | A/D conversion can be activated by external trigger or timer to |          |  |  |  |  |

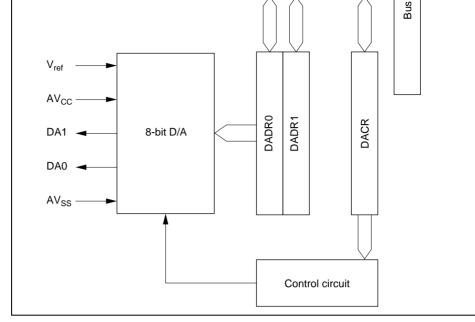

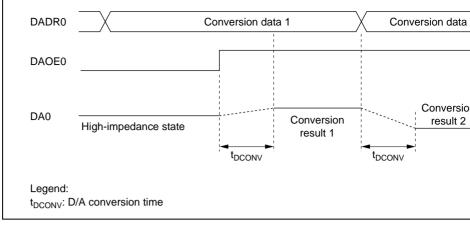

| D/A converter        | Resolution: 8 bits                                                                       |                                                                 |          |  |  |  |  |

|                      | Output: 2 channels                                                                       |                                                                 |          |  |  |  |  |

| I/O ports            | • 71 I/O pins, 8 input-o                                                                 | only pins                                                       |          |  |  |  |  |

| Memory               | Flash memory, PROI                                                                       | M, or mask ROM                                                  |          |  |  |  |  |

|                      | High-speed static RAM                                                                    |                                                                 |          |  |  |  |  |

|                      | Product Name                                                                             | ROM                                                             | RAM      |  |  |  |  |

|                      | H8S/2345                                                                                 | 128 kbytes                                                      | 4 kbytes |  |  |  |  |

|                      | H8S/2344                                                                                 | 96 kbytes                                                       | 4 kbytes |  |  |  |  |

|                      | H8S/2343                                                                                 | 64 kbytes                                                       | 2 kbyte: |  |  |  |  |

|                      | H8S/2341                                                                                 | 32 kbytes                                                       | 2 kbytes |  |  |  |  |

|                      | H8S/2340                                                                                 | _                                                               | 2 kbytes |  |  |  |  |

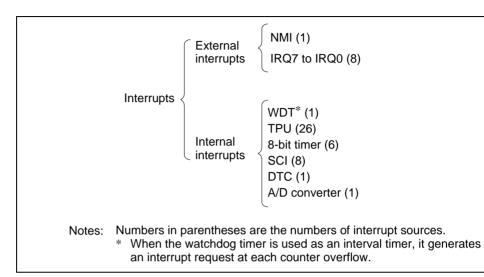

| Interrupt controller | Nine external interrupt pins (NMI, IRQ0 to IRQ7)                                         |                                                                 |          |  |  |  |  |

|                      | 43 internal interrupt sources                                                            |                                                                 |          |  |  |  |  |

|                      | Eight priority levels settable                                                           |                                                                 |          |  |  |  |  |

Watchdog timer or interval timer selectable

Multiprocessor communication function

Smart card interface function

Asynchronous mode or synchronous mode selectable

Watchdog timer

communication

interface (SCI)

2 channels A/D converter

Serial

| 9  | _            |                   |  |

|----|--------------|-------------------|--|

| 10 | Advanced     | Boot mode         |  |

| 11 | =            |                   |  |

| 12 | _            | _                 |  |

| 13 | =            |                   |  |

| 14 | Advanced     | User-programmable |  |

| 15 | <del>-</del> | mode              |  |

|    |              |                   |  |

|    |              |                   |  |

|    |              |                   |  |

**CPU**

Mode Mode

5

6

7

8

REJ09B0291-0400

Operating

Advanced

Description

On-chip ROM disabled

On-chip ROM enabled

expansion mode

expansion mode

Single-chip mode

External

Value

16 bits

8 bits

8 bits

8 bits

8 bits

On-Chip Initial

**ROM**

Disabled

Enabled

Enabled

Enabled

|                       |                                          | •               |                |                    |  |  |  |

|-----------------------|------------------------------------------|-----------------|----------------|--------------------|--|--|--|

|                       | 7*                                       | Single-chip     | mode Ena       | abled —            |  |  |  |

|                       | Note: * Not used on ROMless versions.    |                 |                |                    |  |  |  |

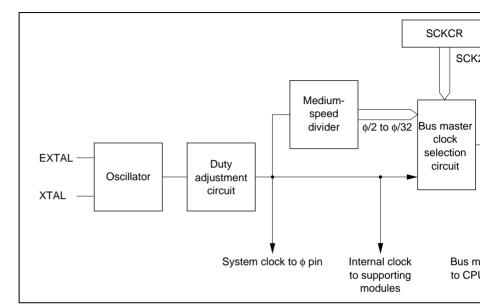

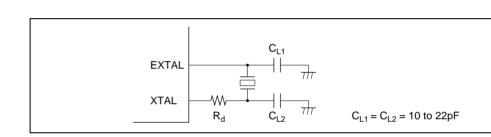

| Clock pulse generator | Built-in duty correction circuit         |                 |                |                    |  |  |  |

| Packages              | 100-pin pla                              | stic TQFP (TFP- | 100B, TFP-100G | )                  |  |  |  |

|                       | • 100-pin plastic QFP (FP-100A, FP-100B) |                 |                |                    |  |  |  |

| Product lineup        |                                          |                 |                |                    |  |  |  |

|                       | Mask ROM<br>Version                      | F-ZTAT          | ZTAT           | ROM/RAM<br>(Bytes) |  |  |  |

|                       | HD6432345                                | HD64F2345       | HD6472345      | 128 k/4 k          |  |  |  |

|                       | HD6432344                                | _               | _              | 96 k/4 k           |  |  |  |

|                       | HD6432343                                | _               | _              | 64 k/2 k           |  |  |  |

|                       | HD6432341                                | _               | _              | 32 k/2 k           |  |  |  |

|                       | HD6412340<br>(ROMless<br>versions)       | _               | _              | —/2 k              |  |  |  |

|                       |                                          |                 |                |                    |  |  |  |

|                       |                                          |                 |                |                    |  |  |  |

expansion mode

Single-chip mode

expansion mode

expansion mode

expansion mode

On-chip ROM disabled

On-chip ROM disabled

On-chip ROM enabled

Enabled

Disabled

Disabled

Enabled

16 bits

8 bits

8 bits

3\*

4

5

6\*

Advanced

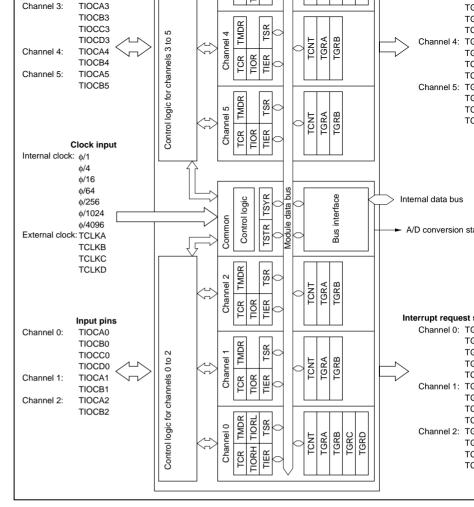

Figure 1.1 Block Diagram

Rev. 4.00 Feb 15, 2006 page 6 of 900 REJ09B0291-0400

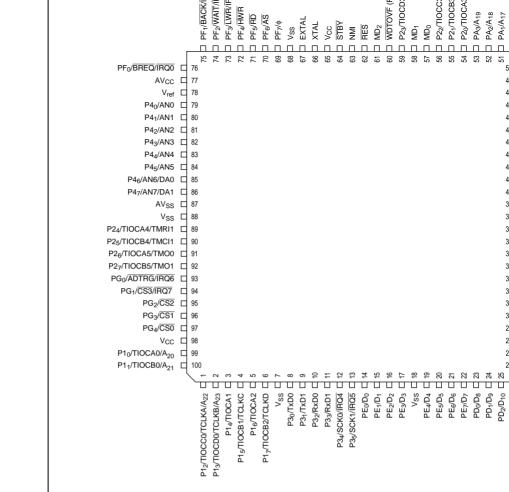

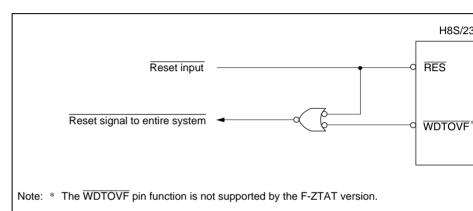

Note: \* Functions as WDTOVF pin on ZTAT, mask ROM, and ROMless versions.

Functions as FWE pin on F-ZTAT version, not as WDTOVF pin.

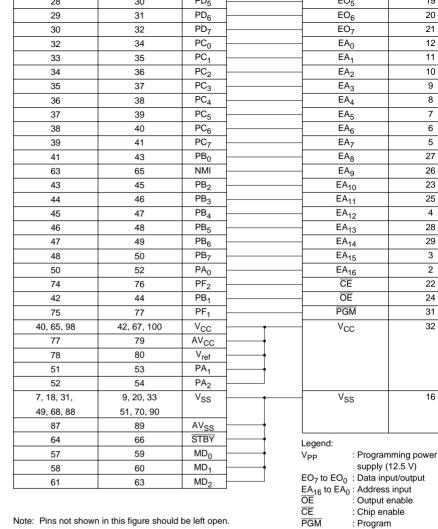

Figure 1.2 Pin Arrangement (FP-100B, TFP-100B, TFP-100G: Top Vio

RENESAS

Rev. 4.00 Feb 15, 2006 p REJ09

Functions as FWE pin on F-ZTAT version, not as WDTOVF pin.

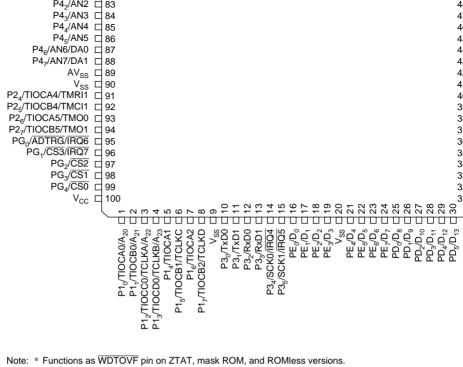

Figure 1.3 Pin Arrangement (FP-100A: Top View)

Rev. 4.00 Feb 15, 2006 page 8 of 900 REJ09B0291-0400

|    |    |                                 |                                       |                                       | A <sub>23</sub>                       | A <sub>23</sub>                       | A <sub>23</sub>                       |                                       |    |

|----|----|---------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|----|

| 3  | 5  | P1₄/<br>TIOCA1                  | P1 <sub>4</sub> /<br>TIOCA1           | P1,/<br>TIOCA1                        | P1./<br>TIOCA1                        | P1./<br>TIOCA1                        | P1./<br>TIOCA1                        | P1₄/<br>TIOCA1                        | NO |

| 4  | 6  | P1,/<br>TIOCB1/<br>TCLKC        | P1 <sub>s</sub> /<br>TIOCB1/<br>TCLKC | NO |

| 5  | 7  | P1 /<br>TIOCA2                  | P1,/<br>TIOCA2                        | P1,/<br>TIOCA2                        | P1,/<br>TIOCA2                        | P1,/<br>TIOCA2                        | P1,/<br>TIOCA2                        | P1 <sub>6</sub> /<br>TIOCA2           | NO |

| 6  | 8  | P1,/<br>TIOCB2/<br>TCLKD        | P1,/<br>TIOCB2/<br>TCLKD              | P1 <sub>-</sub> /<br>TIOCB2/<br>TCLKD | P1,/<br>TIOCB2/<br>TCLKD              | P1,/<br>TIOCB2/<br>TCLKD              | P1,/<br>TIOCB2/<br>TCLKD              | P1,/<br>TIOCB2/<br>TCLKD              | NO |

| 7  | 9  | V <sub>ss</sub>                 | V <sub>ss</sub>                       | V <sub>ss</sub>                       | V <sub>ss</sub>                       | V <sub>ss</sub>                       | V <sub>ss</sub>                       | V <sub>ss</sub>                       | Vs |

| 8  | 10 | P3 <sub>0</sub> /TxD0           | P3 <sub>0</sub> /TxD0                 | P3 <sub>0</sub> /TxD0                 | P3 <sub>0</sub> /TxD0                 | P3 <sub>0</sub> /TxD0                 | P3 <sub>0</sub> /TxD0                 | P3 <sub>0</sub> /TxD0                 | NO |

| 9  | 11 | P3 <sub>,</sub> /TxD1           | P3 <sub>1</sub> /TxD1                 | P3 <sub>1</sub> /TxD1                 | P3 <sub>1</sub> /TxD1                 | P3₁/TxD1                              | P3₁/TxD1                              | P3 <sub>1</sub> /TxD1                 | NO |

| 10 | 12 | P3 <sub>2</sub> /RxD0           | P3 <sub>2</sub> /RxD0                 | P3 <sub>2</sub> /RxD0                 | P3 <sub>2</sub> /RxD0                 | P3 <sub>2</sub> /RxD0                 | P3 <sub>2</sub> /RxD0                 | P3 <sub>2</sub> /RxD0                 | NO |

| 11 | 13 | P3 <sub>3</sub> /RxD1           | P3 <sub>3</sub> /RxD1                 | P3 <sub>3</sub> /RxD1                 | P3 <sub>3</sub> /RxD1                 | P3 <sub>3</sub> /RxD1                 | P3 <sub>3</sub> /RxD1                 | P3 <sub>3</sub> /RxD1                 | NO |

| 12 | 14 | P3₄/<br>SCK0/<br>IRQ4           | P3₄/<br>SCK0/<br>IRQ4                 | P3₄/<br>SCK0/<br>IRQ4                 | P3₄/<br>SCK0/<br>IRQ4                 | P3₄/<br>SCK0/<br>IRQ4                 | P3₄/<br>SCK0/<br>IRQ4                 | P3₄/<br>SCK0/<br>IRQ4                 | NO |

| 13 | 15 | P3¸/<br>SCK1/<br>IRQ5           | P3 <sub>s</sub> /<br>SCK1/<br>IRQ5    | NO |

| 14 | 16 | PE <sub>0</sub> /D <sub>0</sub> | PE <sub>0</sub> /D <sub>0</sub>       | PE <sub>o</sub>                       | PE <sub>0</sub> /D <sub>0</sub>       | PE <sub>0</sub> /D <sub>0</sub>       | PE <sub>0</sub> /D <sub>0</sub>       | PE <sub>o</sub>                       | NO |

| 15 | 17 | PE <sub>1</sub> /D <sub>1</sub> | PE <sub>1</sub> /D <sub>1</sub>       | PE <sub>1</sub>                       | PE <sub>1</sub> /D <sub>1</sub>       | PE <sub>1</sub> /D <sub>1</sub>       | PE <sub>1</sub> /D <sub>1</sub>       | PE,                                   | NO |

| 16 | 18 | PE <sub>2</sub> /D <sub>2</sub> | PE <sub>2</sub> /D <sub>2</sub>       | PE <sub>2</sub>                       | PE <sub>2</sub> /D <sub>2</sub>       | PE <sub>2</sub> /D <sub>2</sub>       | PE <sub>2</sub> /D <sub>2</sub>       | PE <sub>2</sub>                       | NO |

|    |    |                                 |                                       |                                       |                                       |                                       |                                       |                                       |    |

PE,

PE<sub>3</sub>/D<sub>3</sub>

TFP-100G

1

2

17

19

PE,/D,

FP-100A

3

4

1\*1

P1,/

P1,/

TIOCC0/

TIOCD0/

**TCLKB**

**TCLKA**

2\*1 \*2

P1,/

P1,/

TIOCCO/

TIOCD0/

**TCLKB**

**TCLKA**

3\*1 \*2

P1,/

P1,/

TIOCCO/

TIOCD0/

**TCLKB**

**TCLKA**

4

P1<sub>2</sub>/

$A_{22}$

P1,/

TIOCC0/

TCLKA/

TIOCD0/

TCLKB/

5

P1<sub>2</sub>/

$A_{22}$

P1,/

TIOCCO/

TCLKA/

TIOCD0/

TCLKB/

6\*2

P1,/

A<sub>22</sub>

P1./

TIOCCO/

TCLKA/

TIOCD0/

TCLKB/

7\*2

P1,/

TIOCCO/

TIOCD0/

TCLKB

**TCLKA**

P1,/

Mo

NC

NC

NC

PE,

PE,/D,

PE,/D,

PE,/D,

40 PC<sub>6</sub> A<sub>6</sub> PC<sub>6</sub>/A<sub>6</sub> A<sub>6</sub> A<sub>6</sub> 41 PC,/A, PC,  $A_7$  $A_7$ A,  $V_{\rm cc}$  $V_{\rm cc}$ 40  $V_{cc}$  $V_{\rm cc}$  $V_{\rm cc}$ 42 43 A<sub>8</sub> PB<sub>0</sub>/A<sub>8</sub> PB<sub>o</sub>  $A_8$ A<sub>8</sub> 44  $A_9$ PB<sub>1</sub>/A<sub>0</sub> PB,  $A_9$ A<sub>9</sub> 43 45 A,, PB<sub>2</sub>/A<sub>10</sub> PB, A,, A,,  $A_{11}$  $A_{11}$ 46 A,, PB<sub>3</sub>/A<sub>11</sub> PB, PB<sub>4</sub>/A<sub>12</sub> 47 A<sub>12</sub> PB<sub>4</sub> A<sub>12</sub> A,2 A<sub>13</sub> PB<sub>5</sub>/A<sub>13</sub> A<sub>13</sub> PB, A<sub>13</sub>

PB<sub>6</sub>/A<sub>14</sub>

PB<sub>7</sub>/A<sub>15</sub>

$V_{ss}$

PA<sub>o</sub>

A,4

A<sub>15</sub>

$V_{ss}$

$\mathrm{V}_{\mathrm{ss}}$  $A_{\scriptscriptstyle 0}$ A,

A<sub>2</sub>

$A_3$

$A_4$

A,

$A_{14}$

A,5

$V_{ss}$

$A_{16}$

PE,/D,

$\mathsf{D}_{_{8}}$

D<sub>o</sub>

D,

D,,

D<sub>12</sub>

D<sub>13</sub>

$D_{14}$

D<sub>15</sub>

PE,/D,

D<sub>g</sub>

D<sub>o</sub>

D,

D,,

D<sub>12</sub>

D<sub>13</sub>

D<sub>14</sub>

D<sub>15</sub>

${\rm V}_{\rm ss}$

PC<sub>0</sub>/A<sub>0</sub>

PC<sub>3</sub>/A<sub>3</sub>

PC<sub>4</sub>/A<sub>4</sub>

PC<sub>5</sub>/A<sub>5</sub>

PC<sub>6</sub>/A<sub>6</sub>

PC,/A,

PB<sub>0</sub>/A<sub>8</sub>

PB<sub>1</sub>/A<sub>0</sub>

PB<sub>2</sub>/A<sub>10</sub>

PB<sub>3</sub>/A<sub>11</sub>

PB<sub>4</sub>/A<sub>12</sub>

PB<sub>2</sub>/A<sub>13</sub>

PB<sub>6</sub>/A<sub>14</sub>

PB/A

PA/A

$V_{ss}$

$\rm V_{\rm cc}$

PE,

PD<sub>0</sub>

PD,

PD,

PD.

$PD_{A}$

PD,

PD,

PD,

$\mathsf{V}_{\mathrm{ss}}$

PC.

PC,

PC,/A, PC<sub>2</sub>/A<sub>2</sub>

PC, PC<sub>3</sub> PC,

PC,

PC<sub>6</sub>

PC,

$V_{\rm cc}$

PB,

PB,

PB,

PB<sub>3</sub>

PB,

PB,

PB<sub>6</sub>

PB,

$\mathsf{V}_{\mathrm{ss}}$

PA<sub>o</sub>

EA<sub>6</sub> EA,  $V_{\rm cc}$

> $\mathsf{EA}_8$ ŌĒ

EA,

EA,

EA,12

EA,

EA,

EA,  ${\rm V}_{\rm ss}$

EA,

EA,

EA<sub>3</sub> EA, EA,

NC

EO,

EO,

EO,

EO<sub>3</sub>

EO<sub>4</sub>

EO<sub>5</sub>

EO<sub>6</sub>

EO,

$\mathrm{V}_{\mathrm{ss}}$

EA,

PC<sub>2</sub>/A<sub>2</sub>

PC<sub>3</sub>/A<sub>3</sub>

PC<sub>4</sub>/A<sub>4</sub>

PC<sub>5</sub>/A<sub>5</sub>

PE,/D,

D<sub>8</sub>

D<sub>o</sub>

D,

D,,

D<sub>12</sub>

D<sub>13</sub>

$D_{14}$

D<sub>15</sub>

$V_{ss}$

PE,

PD<sub>0</sub>

PD,

PD,

PD,

$PD_{4}$

PD,

PD.

PD,

$\mathrm{V}_{\mathrm{ss}}$

PC<sub>o</sub>

PC,

PC,

PC<sub>3</sub>

PC<sub>4</sub>

PC,

PB<sub>6</sub>

PB,

$V_{ss}$

PA<sub>o</sub>

PE,/D,

D<sub>8</sub>

D<sub>o</sub>

D,

D<sub>11</sub>

D,,

D<sub>13</sub>

D<sub>14</sub> D<sub>15</sub>

$\mathrm{V}_{\mathrm{ss}}$

$A_0$

A,

$A_{2}$

$A_3$

$A_4$

$A_{_{5}}$

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

39

41

42

44

45

46

47

48

49

50

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

49

50

51

52

REJ09B0291-0400

PE,/D,

D,

D<sub>o</sub>

D,

D,,

D<sub>12</sub>

D<sub>13</sub>

D<sub>14</sub>

D<sub>15</sub>

$V_{ss}$

$A_0$

A,

A<sub>2</sub>

$A_3$

$A_4$

A<sub>5</sub>

A,4

A,5

$V_{ss}$

PA<sub>o</sub>

Rev. 4.00 Feb 15, 2006 page 10 of 900

| 61 | 63 | $MD_{\scriptscriptstyle 2}$        | $MD_{\scriptscriptstyle 2}$        | $MD_{\scriptscriptstyle 2}$ | $MD_2$                             |  |

|----|----|------------------------------------|------------------------------------|-----------------------------|------------------------------------|--|

| 62 | 64 | RES                                | RES                                | RES                         | RES                                |  |

| 63 | 65 | NMI                                | NMI                                | NMI                         | NMI                                |  |

| 64 | 66 | STBY                               | STBY                               | STBY                        | STBY                               |  |

| 65 | 67 | V <sub>cc</sub>                    | V <sub>cc</sub>                    | V <sub>cc</sub>             | V <sub>cc</sub>                    |  |

| 66 | 68 | XTAL                               | XTAL                               | XTAL                        | XTAL                               |  |

| 67 | 69 | EXTAL                              | EXTAL                              | EXTAL                       | EXTAL                              |  |

| 68 | 70 | $V_{\rm ss}$                       | $V_{ss}$                           | $V_{\rm ss}$                | V <sub>ss</sub>                    |  |

| 69 | 71 | PF <sub>7</sub> /φ                 | PF <sub>7</sub> /φ                 | PF <sub>7</sub> /φ          | PF₁/φ                              |  |

| 70 | 72 | ĀS                                 | ĀS                                 | PF <sub>6</sub>             | ĀS                                 |  |

| 71 | 73 | RD                                 | RD                                 | PF <sub>5</sub>             | RD                                 |  |

| 72 | 74 | HWR                                | HWR                                | PF <sub>4</sub>             | HWR                                |  |

| 73 | 75 | LWR                                | LWR                                | PF <sub>3</sub> /IRQ3       | LWR                                |  |

| 74 | 76 | PF <sub>2</sub> /<br>WAIT/<br>IRQ2 | PF <sub>2</sub> /<br>WAIT/<br>IRQ2 | PF <sub>2</sub> /IRQ2       | PF <sub>2</sub> /<br>WAIT/<br>IRQ2 |  |

| 75 | 77 | PF₁/<br>BACK/<br>IRQ1              | PF₁/<br>BACK/<br>IRQ1              | PF₁/ĪRQ1                    | PF <sub>1</sub> /<br>BACK/<br>IRQ1 |  |

55

56

57

58

59

60

57

58

59

60

61

62

P2,/

P2,/

MD<sub>o</sub>

MD,

P2./

TIOCD3/

**WDTOVF**

TMC<sub>10</sub>

TIOCB3

TIOCC3/

TMR<sub>I0</sub>

P2,/

P2,/

TIOCB3

TIOCC3/

TMRI0

MD<sub>o</sub>

MD,

P2./

TIOCD3/

WDTOVF

TMCI0

P2,/

P2,/

MD<sub>o</sub>

MD,

P2./

TIOCD3/

**WDTOVF**

TMCI0

TIOCB3

TIOCC3/

TMRI0

P2,/

P2,/

MD<sub>o</sub>

MD,

P2./

TIOCD3/

**WDTOVF**

(FWE\*5)

TMCI0

TIOCB3

TIOCC3/

TMRI0

P2,/

P2,/

MD<sub>o</sub>

MD,

P2./

TIOCD3/

**WDTOVF**

(FWE\*5)

MD,

RES

NMI

$V_{cc}$

$\mathrm{V}_{\mathrm{ss}}$

ĀS

$\overline{\mathsf{RD}}$

**HWR**

**LWR**

PF,/

WAIT/

**IRQ2**

PF./

BACK/

**IRQ1**

PF,/φ

STBY

**XTAL**

**EXTAL**

TMC<sub>10</sub>

TIOCB3

TIOCC3/

TMRI0

P2,/

P2,/

MD<sub>o</sub>

MD,

P2./

TIOCD3/

**WDTOVF**

(FWE\*5)

MD<sub>2</sub>

RES

NMI

$V_{cc}$

$\mathsf{V}_{\mathrm{ss}}$

ĀS

$\overline{\text{RD}}$

**HWR**

**LWR**

PF,/

WAIT/

**IRQ2**

PF./

BACK/

**IRQ1**

PF,/φ

**XTAL**

**EXTAL**

STBY

TMCI0

TIOCB3

TIOCC3/

TMRI0

P2,/

P2,/

MD<sub>o</sub>

MD,

P2./

TIOCD3/

**WDTOVF**

(FWE\*5)

MD<sub>2</sub>

RES

NMI

**STBY**

XTAL

**EXTAL**

$V_{cc}$

$V_{ss}$

PF,/ø

PF<sub>6</sub>

PF,

PF,

PF<sub>3</sub>/IRQ3

PF<sub>2</sub>/IRQ2

PF,/IRQ1

TMCI0

TIOCB3

TIOCC3/

TMRI0

NO

NO

Vs

$V_{s}$

NC

NC

$V_{s}$

$V_{P}$

ΕA

Vs

$V_{c}$

NO

$V_{s}$

NO

NO

NO

NO

NC CE

PC

| 88 | 90  | $V_{ss}$                              | $V_{ss}$                              | $V_{ss}$                              | $V_{ss}$                             | $V_{ss}$                              |

|----|-----|---------------------------------------|---------------------------------------|---------------------------------------|--------------------------------------|---------------------------------------|

| 89 | 91  | P2 <sub>4</sub> /<br>TIOCA4/<br>TMRI1 | P2 <sub>4</sub> /<br>TIOCA4/<br>TMRI1 | P2./<br>TIOCA4/<br>TMRI1              | P2₄/<br>TIOCA4/<br>TMRI1             | P2 <sub>4</sub> /<br>TIOCA4/<br>TMRI1 |

| 90 | 92  | P2₅/<br>TIOCB4/<br>TMCI1              | P2 <sub>5</sub> /<br>TIOCB4/<br>TMCI1 | P2 <sub>s</sub> /<br>TIOCB4/<br>TMCI1 | P2,/<br>TIOCB4/<br>TMCI1             | P2 <sub>s</sub> /<br>TIOCB4/<br>TMCI1 |

| 91 | 93  | P2 <sub>s</sub> /<br>TIOCA5/<br>TMO0  | P2 <sub>e</sub> /<br>TIOCA5/<br>TMO0  | P2 <sub>e</sub> /<br>TIOCA5/<br>TMO0  | P2 <sub>e</sub> /<br>TIOCA5/<br>TMO0 | P2 <sub>e</sub> /<br>TIOCA5/<br>TMO0  |

| 92 | 94  | P2 <sub>,</sub> /<br>TIOCB5/<br>TMO1  | P2,/<br>TIOCB5/<br>TMO1               | P2,/<br>TIOCB5/<br>TMO1               | P2,/<br>TIOCB5/<br>TMO1              | P2,/<br>TIOCB5/<br>TMO1               |

| 93 | 95  | PG <sub>0</sub> /<br>IRQ6/<br>ADTRG   | PG√<br>IRQ6/<br>ADTRG                 | PG <sub>0</sub> /<br>IRQ6/<br>ADTRG   | PG√<br>IRQ6/<br>ADTRG                | PG√<br>IRQ6/<br>ADTRG                 |

| 94 | 96  | PG <sub>1</sub> /IRQ7                 | PG <sub>1</sub> /IRQ7                 | PG <sub>1</sub> /IRQ7                 | PG,/CS3/<br>IRQ7                     | PG,/CS3/<br>IRQ7                      |

| 95 | 97  | $PG_{2}$                              | $PG_{2}$                              | $PG_{2}$                              | PG <sub>2</sub> /CS2                 | PG <sub>2</sub> /CS2                  |

| 96 | 98  | $PG_{_3}$                             | PG₃                                   | PG₃                                   | PG <sub>3</sub> /CS1                 | PG <sub>3</sub> /CS1                  |

| 97 | 99  | PG <sub>₄</sub> /CS0                  | PG <sub>4</sub> /CS0                  | PG <sub>4</sub>                       | PG₄/CS0                              | PG <sub>4</sub> /CS0                  |

| 98 | 100 | V <sub>cc</sub>                       | V <sub>cc</sub>                       | V <sub>cc</sub>                       | V <sub>cc</sub>                      | V <sub>cc</sub>                       |

79

80

81

82

83

84

85

86

87

81

82

83

84

85

86

87

88

89

P4<sub>0</sub>/AN0

P4,/AN1

P4<sub>2</sub>/AN2

P4<sub>3</sub>/AN3

P4,/AN4

P4<sub>c</sub>/AN5

P4<sub>c</sub>/AN6/

P4\_/AN7/

DA<sub>0</sub>

DA1

$AV_{ss}$

P4<sub>0</sub>/AN0

P4,/AN1

P4<sub>2</sub>/AN2

P4<sub>3</sub>/AN3

P4,/AN4

P4<sub>-</sub>/AN5

P4<sub>c</sub>/AN6/

P4\_/AN7/

DA0

DA1

$\mathsf{AV}_{\mathsf{ss}}$

P4/AN0

P4<sub>4</sub>/AN1

P4,/AN2

P4,/AN3

P4,/AN4

P4/AN5

P4./AN6/

P4\_/AN7/

DA<sub>0</sub>

DA1

$AV_{ss}$

P4/AN0

P4,/AN1

P4,/AN2

P4,/AN3

P4,/AN4

P4\_/AN5

P4./AN6/

P4\_/AN7/

DA0

DA1

$AV_{ss}$

P4<sub>0</sub>/AN0

P4,/AN1

P4<sub>2</sub>/AN2

P4<sub>3</sub>/AN3

P4,/AN4

P4<sub>-</sub>/AN5

P4<sub>c</sub>/AN6/

P4\_/AN7/

DA0

DA1

$AV_{ss}$

P4<sub>o</sub>/AN0

P4,/AN1

P4<sub>2</sub>/AN2

P4<sub>3</sub>/AN3

P4,/AN4

P4\_/AN5

P4<sub>c</sub>/AN6/

P4\_/AN7/

DA0

DA1

$\mathsf{AV}_{\mathsf{ss}}$

$V_{ss}$

P2,/

P2<sub>c</sub>/

TIOCA4/

TIOCB4/

TIOCA5/ TMO0

TIOCB5/

TMO1

PG<sub>0</sub>/

ĪRQ6/

ĪRQ7

**ADTRG**

PG/CS3/

PG,/CS2

PG<sub>3</sub>/CS1

PG<sub>4</sub>/CS0

$V_{cc}$

TMCI1

P2,/

P2,/

TMRI1

Rev. 4.00 Feb 15, 2006 page 12 of 900 REJ09B0291-0400

RENESAS

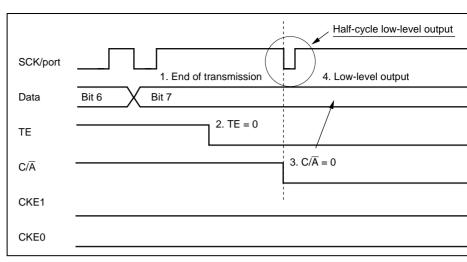

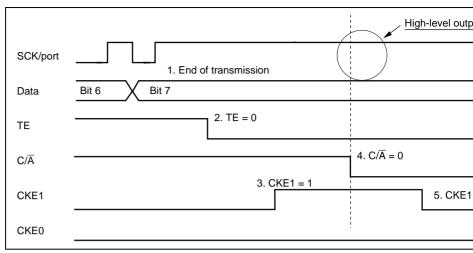

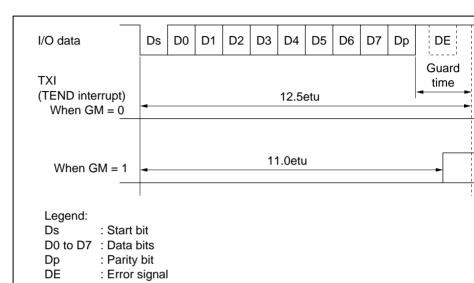

NC