#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

16

## H8S/2556 Group, H8S/2552 Group, H8S/2506 Group Hardware Manual

# Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2500 Series

| H8S/2556 | HD64F2556 |

|----------|-----------|

| H8S/2552 | HD64F2552 |

| H8S/2551 | HD64F2551 |

| H8S/2506 | HD64F2506 |

| H8S/2505 | HD64F2505 |

Renesas Electronics

Rev.6.00 2009.09

- document, please confirm the latest product information with a Renesas sales office. Also, please pay and careful attention to additional and different information to be disclosed by Renesas such as that di through our website. (http://www.renesas.com )

- Renesas has used reasonable care in compiling the information included in this document, but Renesa assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the info included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the informatilight of the total system before deciding about the applicability of such information to the intended appl Renesas makes no representations, warranties or guaranties regarding the suitability of its products for particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure malfunction of which may cause a direct threat to human life or create a risk of human injury or which i especially high quality and reliability such as safety systems, or equipment or systems for transportatic traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea comm transmission. If you are considering the use of our products for such purposes, please contact a Rene sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth all

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes liste

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchase elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless I Technology Corp., its affiliated companies and their officers, directors, and employees against any and damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with r to the maximum rating, operating supply voltage range, movement power voltage range, heat radiatior characteristics, installation and other product characteristics. Renesas shall have no liability for malfun damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specharacteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical in injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design hardware and software including but not limited to redundancy, fire control and malfunction prevention appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final prodisystem manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesa products are attached or affixed, the risk of accident such as swallowing by infants and small children i high. You should implement safety measures so that Renesas products may not be easily detached from products. Renesas shall have no liability for damages arising out of such detachment.

- This document may not be reproduced or duplicated, in any form, in whole or in part, without prior writ approval from Renesas.

- Please contact a Renesas sales office if you have any questions regarding the information contained in document, Renesas semiconductor products, or if you have any other inquiries.

Rev. 6.00 Sep. 24, 2009 Page ii of xlvi

REJ09B0099-0600

malfunctions may occur due to the false recognition of the pin state as an input Unused pins should be handled as described under Handling of Unused Pins in manual.

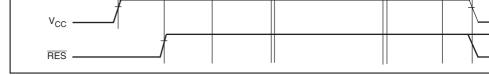

2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of regis settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, t states of pins are not guaranteed from the moment when power is supplied unti reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power reset function are not guaranteed from the moment when power is supplied untipower reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functi not access these addresses; the correct operation of LSI is not guaranteed if the accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal ha become stable. When switching the clock signal during program execution, wait unt target clock signal has stabilized.

- When the clock signal is generated with an external resonator (or from an extern oscillator) during a reset, ensure that the reset line is only released after full stal of the clock signal. Moreover, when switching to a clock signal produced with ar external resonator (or by an external oscillator) while program execution is in pr wait until the target clock signal is stable.

- 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number confirm that the change will not lead to problems.

The characteristics of MPU/MCU in the same group but having different type numay differ because of the differences in internal memory capacity and layout pa When changing to products of different type numbers, implement a system-eval test for each of the products.

RENESAS

Rev. 6.00 Sep. 24, 2009 P REJ09

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Eac includes notes in relation to the descriptions given, and usage notes are given, as required final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions for This Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier vers. This does not include all of the revised contents. For details, see the actual locations in the manual.

11. Index

Rev. 6.00 Sep. 24, 2009 Page iv of xlvi REJ09B0099-0600

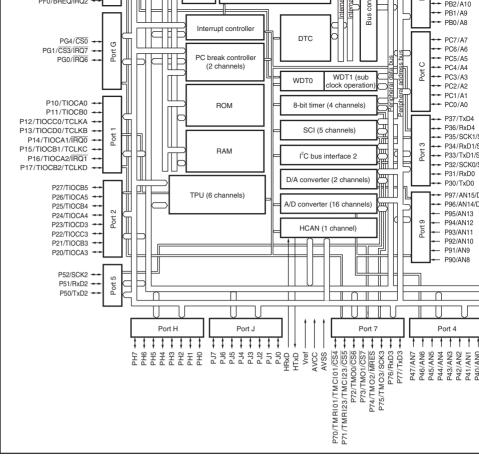

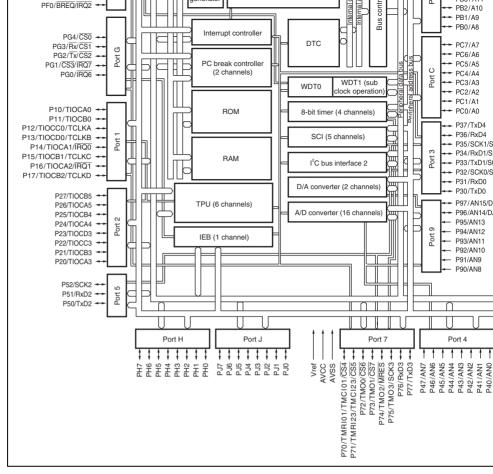

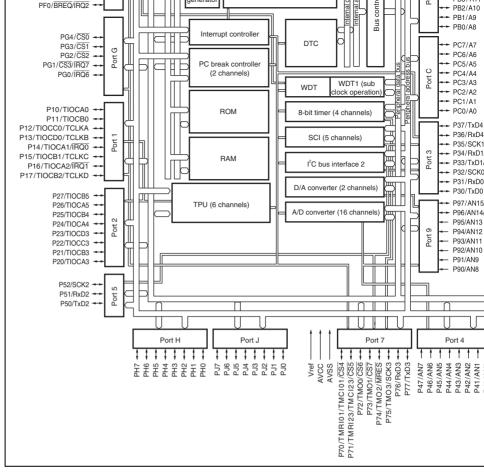

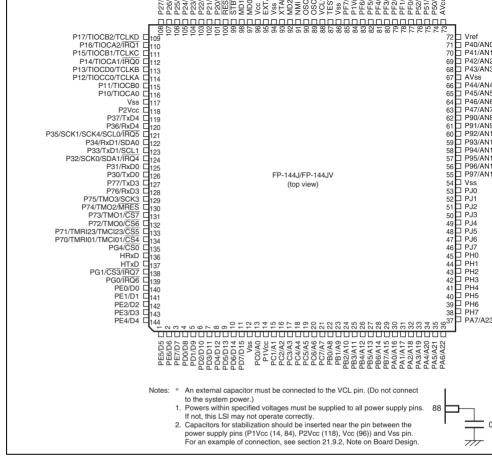

List of on-chip peripheral functions:

| Group Name                                         | H8S/2556 Group | H8S/2552 Group | H8S/250   |

|----------------------------------------------------|----------------|----------------|-----------|

|                                                    |                | H8S/2552       | H8S/250   |

| Product Name                                       | H8S/2556       | H8S/2551       | H8S/250   |

| Bus controller                                     | O (16 bits)    | O (16 bits)    | O (16 bit |

| Data transfer controller (DTC)                     | 0              | 0              | 0         |

| PC break controller (PBC)                          | 0              | 0              | 0         |

| 16-bit timer pulse unit (TPU)                      | × 6            | × 6            | × 6       |

| 8-bit timer (TMR)                                  | × 4            | × 4            | × 4       |

| Watch dog timer (WDT)                              | × 2            | × 2            | × 2       |

| Serial communication interface (SCI)               | × 5            | × 5            | × 5       |

| I <sup>2</sup> C bus interface 2 (IIC2)            | × 2            | × 2            | × 2       |

| IEBus <sup>™</sup> * <sup>2</sup> controller (IEB) |                | × 1            |           |

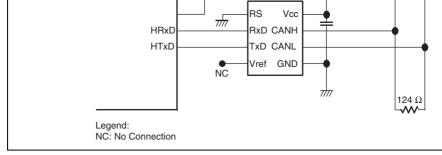

| Controller area network (HCAN)                     | × 1            |                |           |

| D/A converter                                      | × 2            | × 2            | × 2       |

| A/D converter                                      | × 16           | × 16           | × 16      |

Notes: 1. F-ZTAT is a trademark of Renesas Technology Corp.

2. IEBus is a trademark of NEC Electronics Corporation.

RENESAS

Rev. 6.00 Sep. 24, 2009 F REJ09

- In order to understand the overall functions of the chip Read the manual according to the contents. This manual can be roughly categorized in on the CPU, system control functions, peripheral functions and electrical characteristi

- In order to understand the details of the CPU's functions Read the H8S/2600 Series, H8S/2000 Series Software Manual.

- In order to understand the details of a register when its name is known Read the index that is the final part of the manual to find the page number of the entry register. The addresses, bits, and initial values of the registers are summarized in section List of Registers.

| -         |                  |                                                                                                                 |

|-----------|------------------|-----------------------------------------------------------------------------------------------------------------|

| Examples: | Register name:   | The following notation is used for cases when the sa<br>similar function, e.g. 16-bit timer pulse unit or seria |

|           |                  | communication, is implemented on more than one c                                                                |

|           |                  | · •                                                                                                             |

|           |                  | XXX_N (XXX is the register name and N is the cha                                                                |

|           |                  | number)                                                                                                         |

|           | Bit order:       | The MSB is on the left and the LSB is on the right.                                                             |

|           | Number notation: | Binary is B'xxxx, hexadecimal is H'xxxx, decimal                                                                |

|           | Signal notation: | An overbar is added to a low-active signal: $\overline{xxxx}$                                                   |

|           |                  |                                                                                                                 |

Related Manuals: The latest versions of all related manuals are available from our web si ensure you have the latest versions of all documents you require. http://www.renesas.com/

Rev. 6.00 Sep. 24, 2009 Page vi of xlvi REJ09B0099-0600

| oomplier r dokuge | VCI.0.01 03013 Manual |  |

|-------------------|-----------------------|--|

|                   |                       |  |

H8S, H8/300 Series Simulator/Debugger User's Manual

H8S, H8/300 Series High-performance Embedded Workshop User's Manual REJ10J20

Renesas

Rev. 6.00 Sep. 24, 2009 Pa REJ09

REJ10B02

All trademarks and registered trademarks are the property of their respective owners.

Rev. 6.00 Sep. 24, 2009 Page viii of xlvi REJ09B0099-0600

| Secti | ion 2 C                                            | PU                                                                 |  |

|-------|----------------------------------------------------|--------------------------------------------------------------------|--|

| 2.1   | Features                                           |                                                                    |  |

|       | 2.1.1                                              | Differences between H8S/2600 CPU and H8S/2000 CPU                  |  |

|       | 2.1.2                                              | Differences from H8/300 CPU                                        |  |

|       | 2.1.3                                              | Differences from H8/300H CPU                                       |  |

| 2.2   | CPU O                                              | perating Modes                                                     |  |

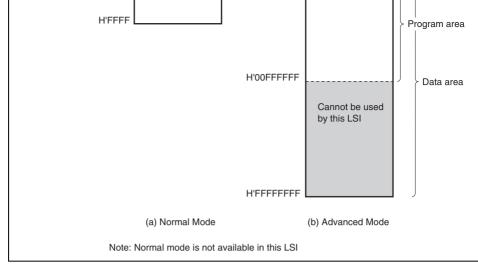

|       | 2.2.1                                              | Normal Mode                                                        |  |

|       | 2.2.2                                              | Advanced Mode                                                      |  |

| 2.3   | Addres                                             | s Space                                                            |  |

| 2.4   | Registe                                            | er Configuration                                                   |  |

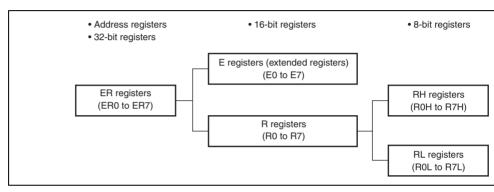

|       | 2.4.1                                              | General Registers                                                  |  |

|       | 2.4.2                                              | Program Counter (PC)                                               |  |

|       | 2.4.3                                              | Extended Control Register (EXR)                                    |  |

|       | 2.4.4                                              | Condition-Code Register (CCR)                                      |  |

|       | 2.4.5                                              | Initial Values of CPU Registers                                    |  |

|       |                                                    | ormats                                                             |  |

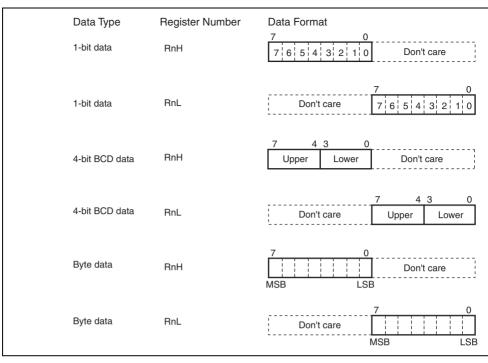

|       | 2.5.1                                              | General Register Data Formats                                      |  |

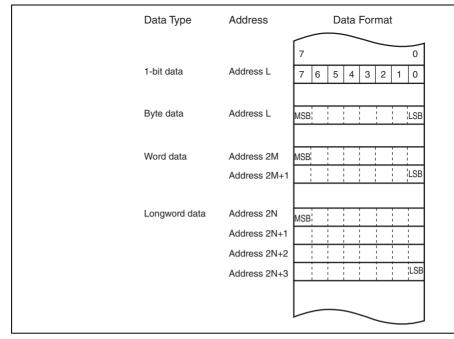

|       | 2.5.2                                              | Memory Data Formats                                                |  |

| 2.6   | Instruc                                            | tion Set                                                           |  |

|       | 2.6.1                                              | Table of Instructions Classified by Function                       |  |

|       | 2.6.2                                              | Basic Instruction Formats                                          |  |

| 2.7   | Addressing Modes and Effective Address Calculation |                                                                    |  |

|       | 2.7.1                                              | Register Direct—Rn                                                 |  |

|       | 2.7.2                                              | Register Indirect—@ERn                                             |  |

|       | 2.7.3                                              | Register Indirect with Displacement-@(d:16, ERn) or @(d:32, ERn)   |  |

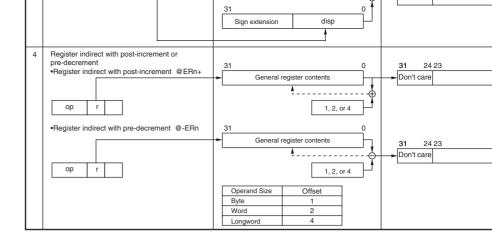

|       | 2.7.4                                              | Register Indirect with Post-Increment or Pre-Decrement-@ERn+ or @- |  |

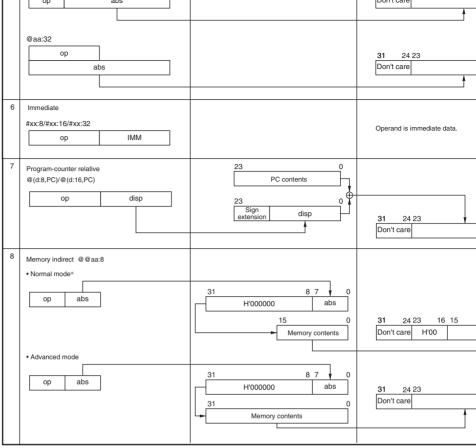

|       | 2.7.5                                              | Absolute Address—@aa:8, @aa:16, @aa:24, or @aa:32                  |  |

|       | 2.7.6                                              | Immediate—#xx:8, #xx:16, or #xx:32                                 |  |

|       |                                                    |                                                                    |  |

RENESAS

Rev. 6.00 Sep. 24, 2009 P REJ09

| 3.1  | Operating Mode Selection                                              |  |  |

|------|-----------------------------------------------------------------------|--|--|

| 3.2  | Register Descriptions                                                 |  |  |

|      | 3.2.1 Mode Control Register (MDCR)                                    |  |  |

|      | 3.2.2 System Control Register (SYSCR)                                 |  |  |

| 3.3  | Operating Mode                                                        |  |  |

|      | 3.3.1 Mode 6                                                          |  |  |

|      | 3.3.2 Mode 7                                                          |  |  |

|      | 3.3.3 Pin Functions                                                   |  |  |

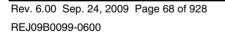

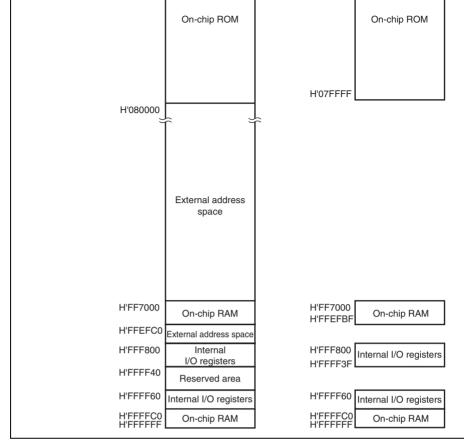

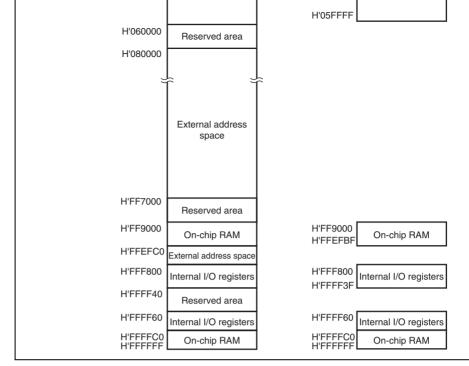

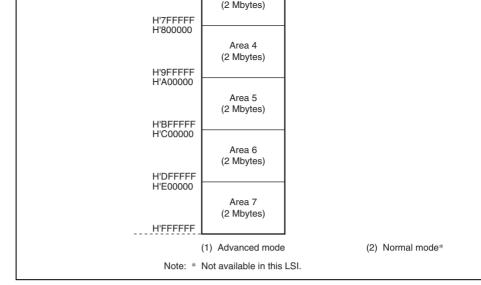

| 3.4  | Address Map in Each Operating Mode                                    |  |  |

|      |                                                                       |  |  |

| Sect | on 4 Exception Handling                                               |  |  |

| 4.1  | Exception Handling Types and Priority                                 |  |  |

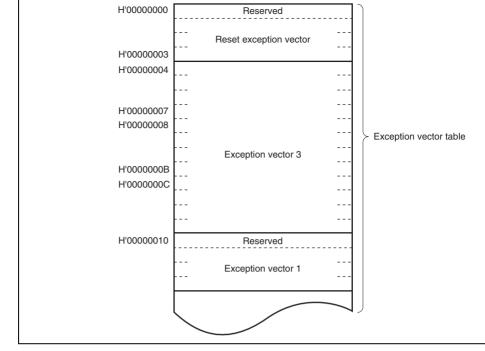

| 4.2  | Exception Sources and Exception Vector Table                          |  |  |

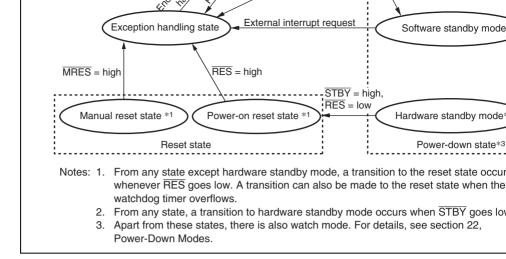

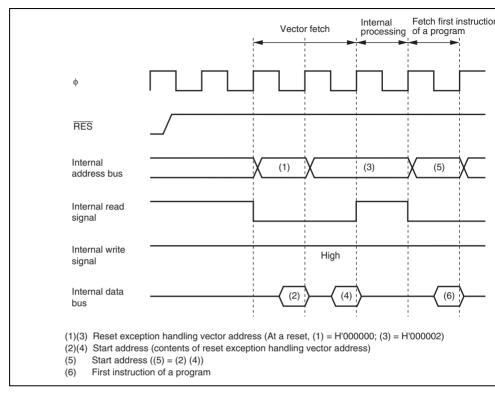

| 4.3  | Reset                                                                 |  |  |

|      | 4.3.1 Types of Reset                                                  |  |  |

|      | 4.3.2 Reset Exception Handling                                        |  |  |

|      | 4.3.3 Interrupts after Reset                                          |  |  |

|      | 4.3.4 State of On-Chip Peripheral Modules after Reset Release         |  |  |

| 4.4  | Trace Exception Handling                                              |  |  |

| 4.5  | Interrupt Exception Handling                                          |  |  |

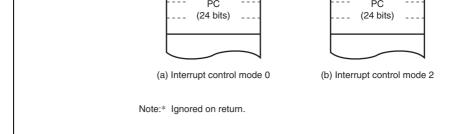

| 4.6  | Trap Instruction Exception Handling                                   |  |  |

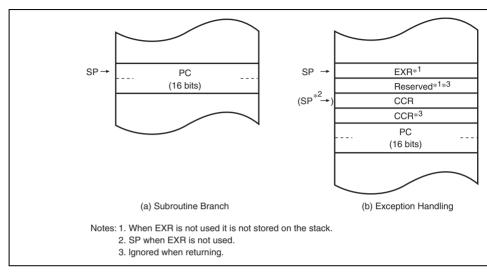

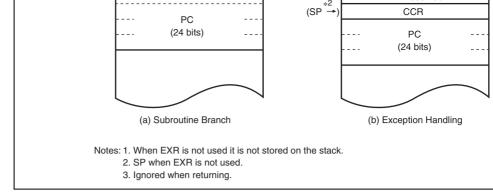

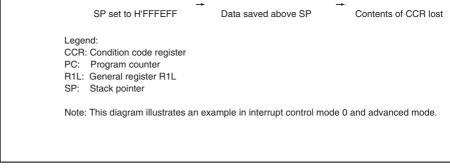

| 4.7  | Stack State after Exception Handling                                  |  |  |

| 4.8  | Usage Note                                                            |  |  |

|      | -                                                                     |  |  |

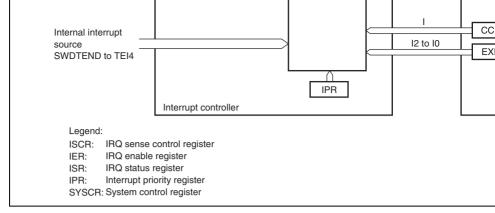

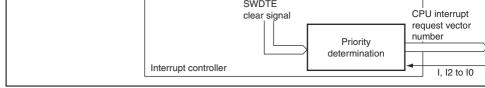

| Sect | on 5 Interrupt Controller                                             |  |  |

| 5.1  | Features                                                              |  |  |

| 5.2  | Input/Output Pins                                                     |  |  |

| 5.3  | Register Descriptions                                                 |  |  |

|      | 5.3.1 Interrupt Priority Registers A to M, and O (IPRA to IPRM, IPRO) |  |  |

|      |                                                                       |  |  |

Rev. 6.00 Sep. 24, 2009 Page x of xlvi REJ09B0099-0600

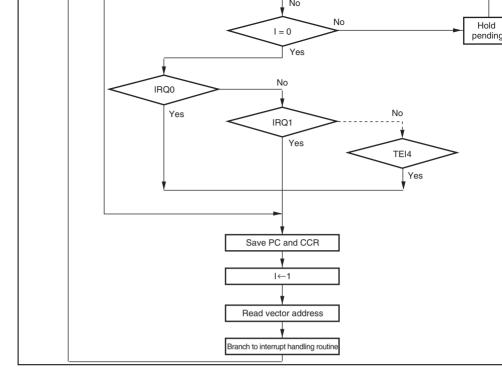

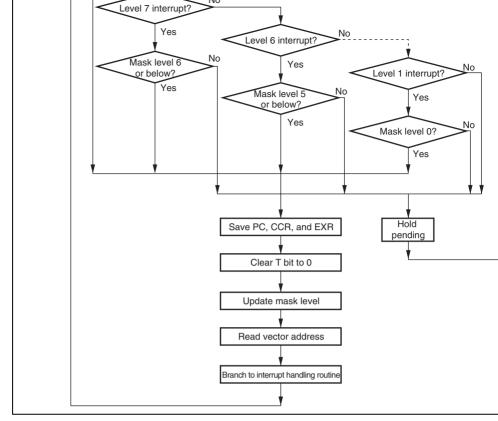

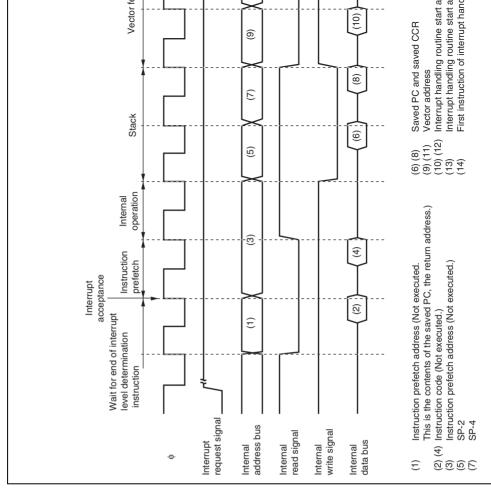

|      | 5.5.4   | Interrupt Exception Handling Sequence                 |

|------|---------|-------------------------------------------------------|

|      | 5.5.5   | Interrupt Response Times                              |

|      | 5.5.6   | DTC Activation by Interrupt                           |

| 5.6  | Usage   | Notes                                                 |

|      | 5.6.1   | Contention between Interrupt Generation and Disabling |

|      | 5.6.2   | Instructions That Disable Interrupts                  |

|      | 5.6.3   | When Interrupts Are Disabled                          |

|      | 5.6.4   | Interrupts during Execution of EEPMOV Instruction     |

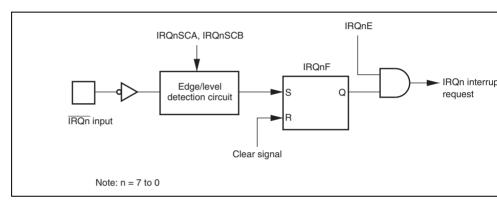

|      | 5.6.5   | IRQ Interrupt                                         |

|      | 5.6.6   | NMI Interrupt Usage Notes                             |

|      |         |                                                       |

| Sect | ion 6 P | C Break Controller (PBC)                              |

| 6.1  | Feature | es                                                    |

| 6.2  | Regist  | er Descriptions                                       |

|      | 6.2.1   | Break Address Register A (BARA)                       |

|      | 6.2.2   | Break Address Register B (BARB)                       |

|      | 6.2.3   | Break Control Register A (BCRA)                       |

|      | 6.2.4   | Break Control Register B (BCRB)                       |

| 6.3  | Operat  | ion                                                   |

|      | 6.3.1   | PC Break Interrupt Due to Instruction Fetch           |

|      | 6.3.2   | PC Break Interrupt Due to Data Access                 |

|      | 6.3.3   | Notes on PC Break Interrupt Handling                  |

|      | 6.3.4   | Operation in Transitions to Power-Down Modes          |

|      | 6.3.5   | When Instruction Execution Is Delayed by One State    |

| 6.4  | Usage   | Notes                                                 |

|      | 6.4.1   | Module Stop Mode Setting                              |

|      | 6.4.2   | PC Break Interrupts                                   |

|      | 6.4.3   | CMFA and CMFB                                         |

|      | 6.4.4   | PC Break Interrupt when DTC Is Bus Master             |

|      |         | 1                                                     |

RENESAS

Rev. 6.00 Sep. 24, 2009 P REJ09

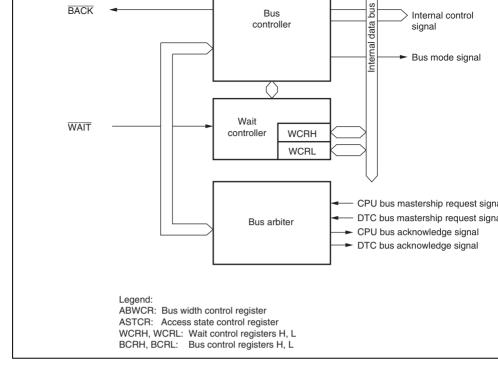

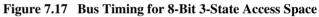

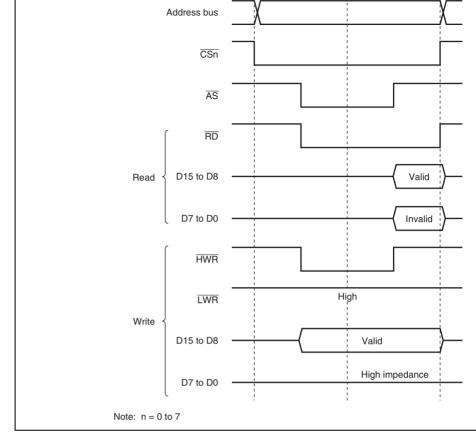

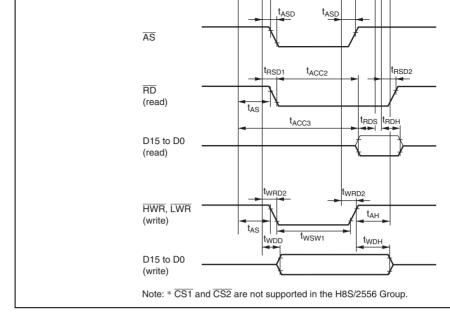

|      | 7.3.1       | Bus Width Control Register (ABWCR)          |

|------|-------------|---------------------------------------------|

|      | 7.3.2       | Access State Control Register (ASTCR)       |

|      | 7.3.3       | Wait Control Registers H and L (WCRH, WCRL) |

|      | 7.3.4       | Bus Control Register H (BCRH)               |

|      | 7.3.5       | Bus Control Register L (BCRL)               |

|      | 7.3.6       | Pin Function Control Register (PFCR)        |

| 7.4  | Bus Co      | ontrol                                      |

|      | 7.4.1       | Area Divisions                              |

|      | 7.4.2       | Bus Specifications                          |

|      | 7.4.3       | Bus Interface for Each Area                 |

|      | 7.4.4       | Chip Select Signals                         |

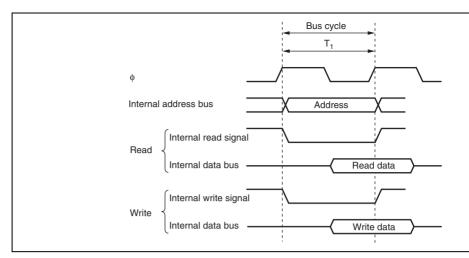

| 7.5  | Basic 7     | Fiming                                      |

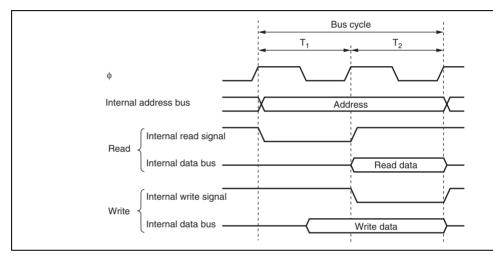

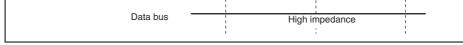

|      | 7.5.1       | On-Chip Memory (ROM, RAM) Access Timing     |

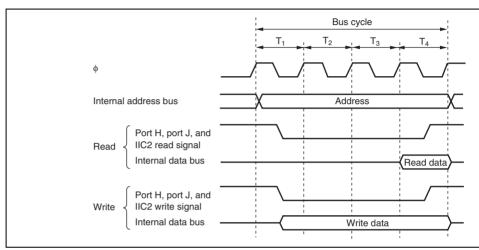

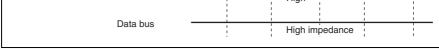

|      | 7.5.2       | On-Chip Peripheral Module Access Timing     |

|      | 7.5.3       | External Address Space Access Timing        |

| 7.6  | Basic H     | Bus Interface                               |

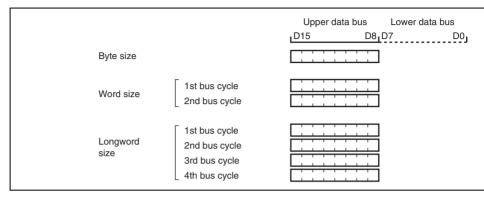

|      | 7.6.1       | Data Size and Data Alignment                |

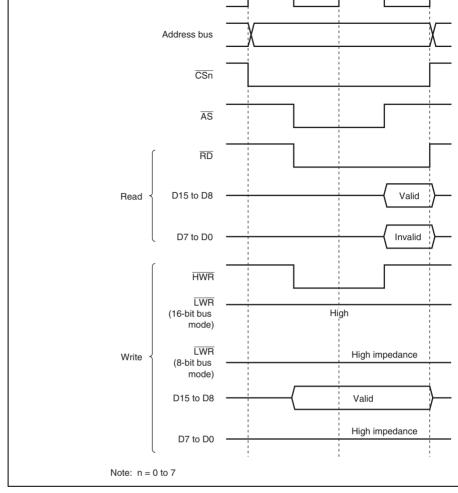

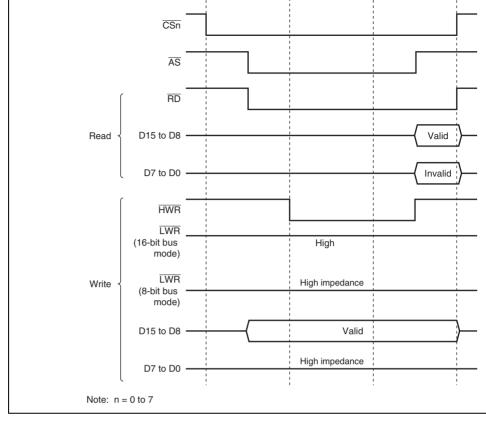

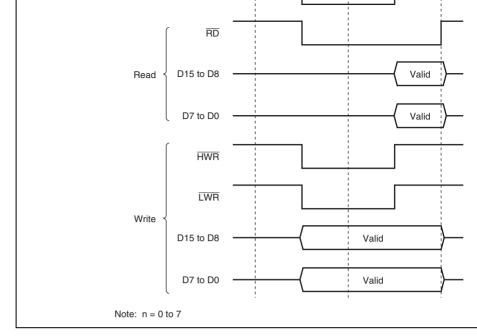

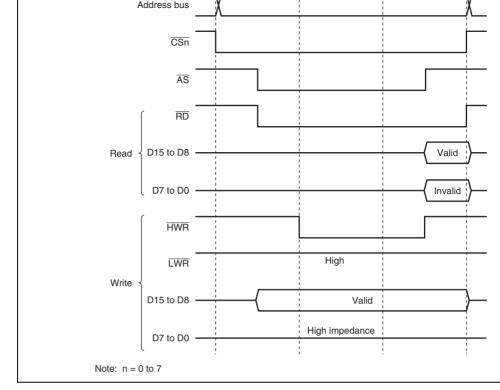

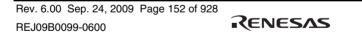

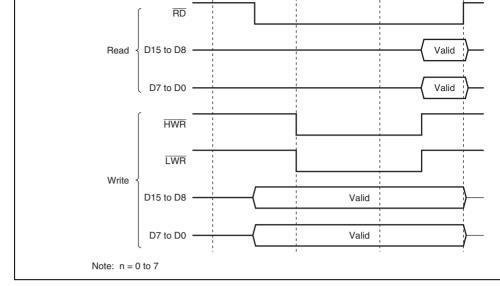

|      | 7.6.2       | Valid Strobes                               |

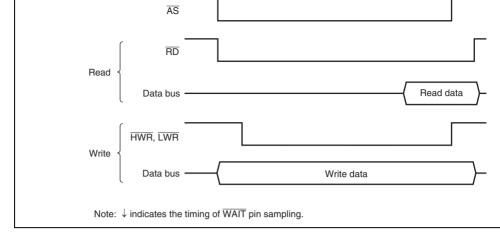

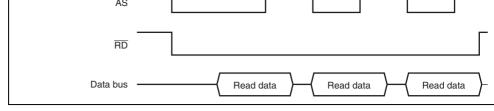

|      | 7.6.3       | Basic Timing                                |

|      | 7.6.4       | Wait Control                                |

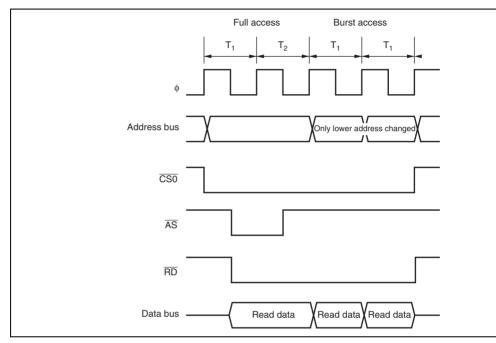

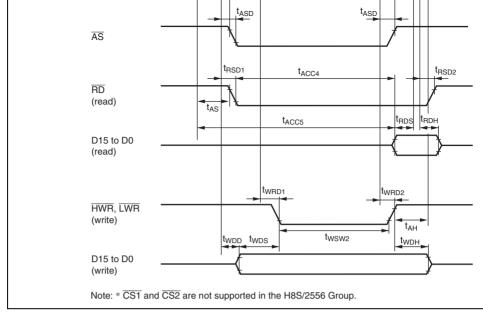

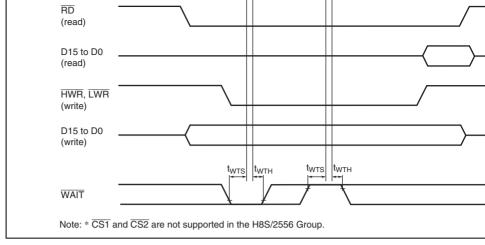

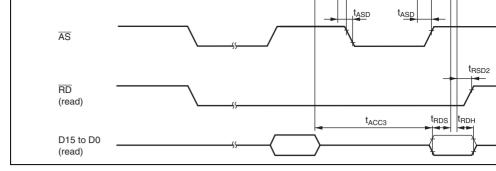

| 7.7  | Burst F     | ROM Interface                               |

|      | 7.7.1       | Basic Timing                                |

|      | 7.7.2       | Wait Control                                |

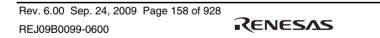

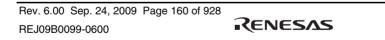

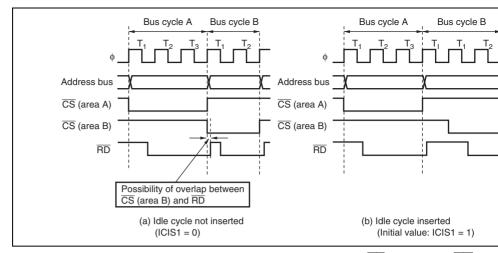

| 7.8  | Idle Cy     | /cle                                        |

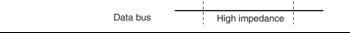

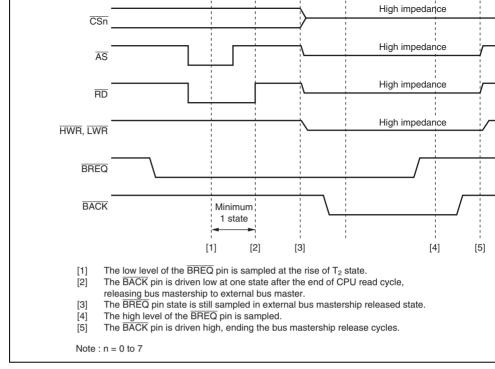

| 7.9  | Bus Release |                                             |

|      | 7.9.1       | Usage Note for Bus Mastership Release       |

| 7.10 | Bus Ar      | bitration                                   |

|      |             | Operation                                   |

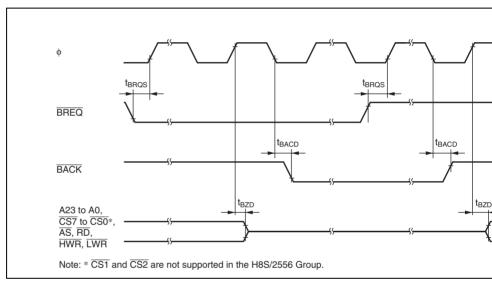

|      |             | Bus Mastership Transfer Timing              |

|      |             | -                                           |

Rev. 6.00 Sep. 24, 2009 Page xii of xlvi

REJ09B0099-0600

RENESAS

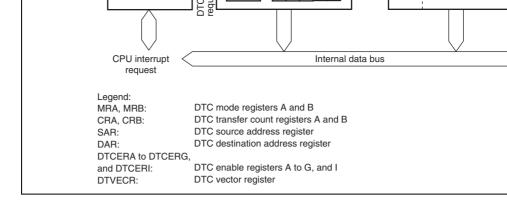

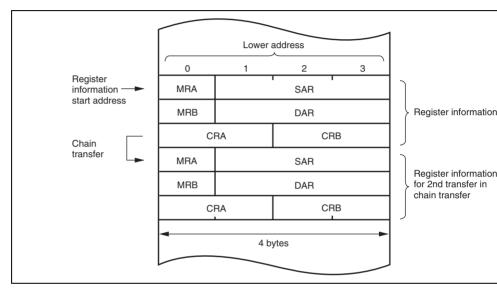

|      | 8.2.6    | DTC Transfer Count Register B (CRB)                            |

|------|----------|----------------------------------------------------------------|

|      | 8.2.7    | DTC Enable Registers A to G, and I (DTCERA to DTCERG, and DTCE |

|      | 8.2.8    | DTC Vector Register (DTVECR)                                   |

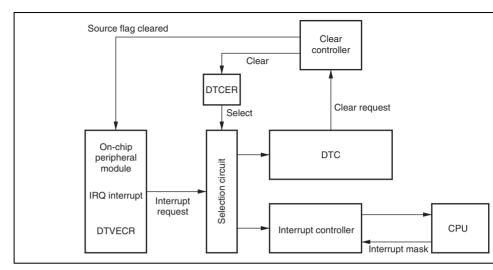

| 8.3  | Activa   | tion Sources                                                   |

| 8.4  | Locati   | on of Register Information and DTC Vector Table                |

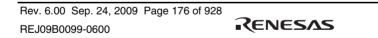

| 8.5  | Operat   | ion                                                            |

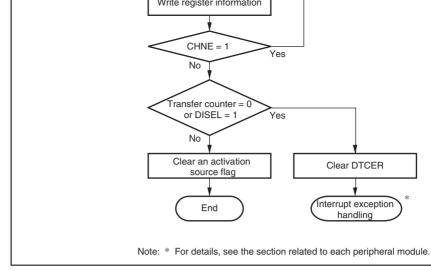

|      | 8.5.1    | Normal Mode                                                    |

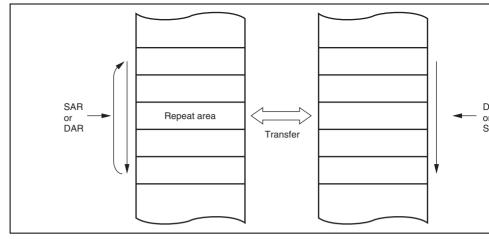

|      | 8.5.2    | Repeat Mode                                                    |

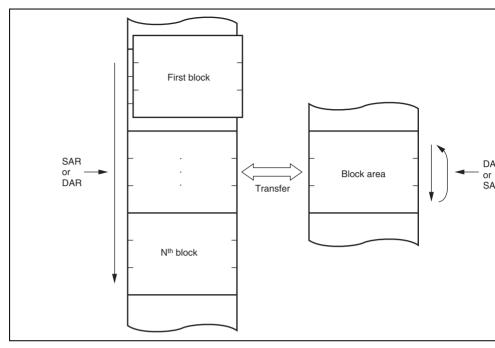

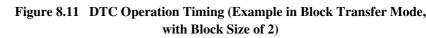

|      | 8.5.3    | Block Transfer Mode                                            |

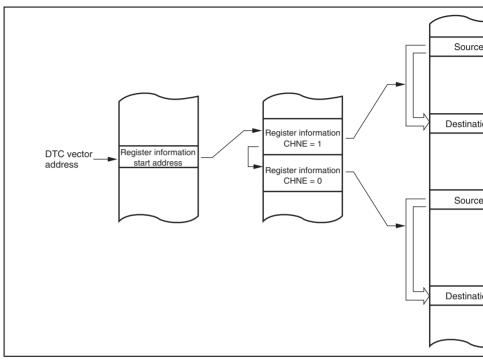

|      | 8.5.4    | Chain Transfer                                                 |

|      | 8.5.5    | Interrupts                                                     |

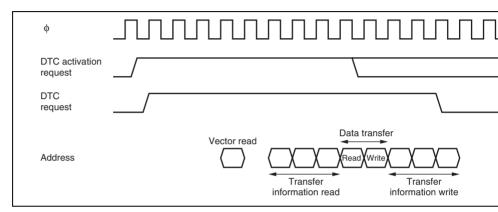

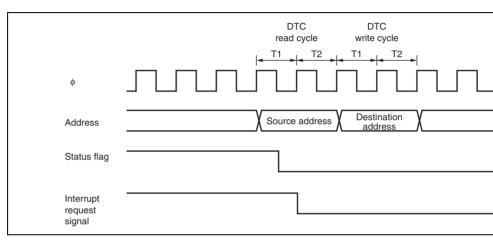

|      | 8.5.6    | Operation Timing                                               |

|      | 8.5.7    | Number of DTC Execution States                                 |

| 8.6  | Proced   | lures for Using DTC                                            |

|      | 8.6.1    | Activation by Interrupt                                        |

|      | 8.6.2    | Activation by Software                                         |

| 8.7  | Examp    | bles of Use of the DTC                                         |

|      | 8.7.1    | Normal Mode                                                    |

|      | 8.7.2    | Software Activation                                            |

| 8.8  | Usage    | Notes                                                          |

|      | 8.8.1    | Module Stop Mode Setting                                       |

|      | 8.8.2    | On-Chip RAM                                                    |

|      | 8.8.3    | DTCE Bit Setting                                               |

|      |          |                                                                |

| Sect | ion 9 I/ | O Ports                                                        |

| 9.1  | Port 1.  |                                                                |

|      | 9.1.1    | Port 1 Data Direction Register (P1DDR)                         |

|      | 9.1.2    | Port 1 Data Register (P1DR)                                    |

|      | 9.1.3    | Port 1 Register (PORT1)                                        |

|      |          |                                                                |

Renesas

Rev. 6.00 Sep. 24, 2009 Pa REJ09

|     | 9.3.5   | Pin Functions                               |

|-----|---------|---------------------------------------------|

| 9.4 | Port 4. |                                             |

|     | 9.4.1   | Port 4 Register (PORT4)                     |

|     | 9.4.2   | Pin Functions                               |

| 9.5 | Port 5. |                                             |

|     | 9.5.1   | Port 5 Data Direction Register (P5DDR)      |

|     | 9.5.2   | Port 5 Data Register (P5DR)                 |

|     | 9.5.3   | Port 5 Register (PORT5)                     |

|     | 9.5.4   | Pin Functions                               |

| 9.6 | Port 7. |                                             |

|     | 9.6.1   | Port 7 Data Direction Register (P7DDR)      |

|     | 9.6.2   | Port 7 Data Register (P7DR)                 |

|     | 9.6.3   | Port 7 Register (PORT7)                     |

|     | 9.6.4   | Pin Functions                               |

| 9.7 | Port 9. |                                             |

|     | 9.7.1   | Port 9 Register (PORT9)                     |

|     | 9.7.2   | Pin Functions                               |

| 9.8 | Port A  |                                             |

|     | 9.8.1   | Port A Data Direction Register (PADDR)      |

|     | 9.8.2   | Port A Data Register (PADR)                 |

|     | 9.8.3   | Port A Register (PORTA)                     |

|     | 9.8.4   | Port A Pull-Up MOS Control Register (PAPCR) |

|     | 9.8.5   | Port A Open Drain Control Register (PAODR)  |

|     | 9.8.6   | Pin Functions                               |

|     | 9.8.7   | Input Pull-Up MOS Function (Port A)         |

| 9.9 | Port B  |                                             |

|     | 9.9.1   | Port B Data Direction Register (PBDDR)      |

|     | 9.9.2   | Port B Data Register (PBDR)                 |

|     | 9.9.3   | Port B Register (PORTB)                     |

|     |         |                                             |

Rev. 6.00 Sep. 24, 2009 Page xiv of xlvi

REJ09B0099-0600

RENESAS

|      | 9.11.1  | Port D Data Direction Register (PDDDR)      |

|------|---------|---------------------------------------------|

|      | 9.11.2  | Port D Data Register (PDDR)                 |

|      | 9.11.3  | Port D Register (PORTD)                     |

|      | 9.11.4  | Port D Pull-Up MOS Control Register (PDPCR) |

|      | 9.11.5  | Pin Functions                               |

|      | 9.11.6  | Input Pull-Up MOS Function (Port D)         |

| 9.12 | Port E. |                                             |

|      | 9.12.1  | Port E Data Direction Register (PEDDR)      |

|      | 9.12.2  | Port E Data Register (PEDR)                 |

|      | 9.12.3  | Port E Register (PORTE)                     |

|      | 9.12.4  | Port E Pull-Up MOS Control Register (PEPCR) |

|      | 9.12.5  | Pin Functions                               |

|      | 9.12.6  | Input Pull-Up MOS Function (Port E)         |

| 9.13 | Port F. |                                             |

|      | 9.13.1  | Port F Data Direction Register (PFDDR)      |

|      | 9.13.2  | Port F Data Register (PFDR)                 |

|      | 9.13.3  | Port F Register (PORTF)                     |

|      | 9.13.4  | Pin Functions                               |

| 9.14 | Port G. |                                             |

|      | 9.14.1  | Port G Data Direction Register (PGDDR)      |

|      | 9.14.2  | Port G Data Register (PGDR)                 |

|      | 9.14.3  | Port G Register (PORTG)                     |

|      | 9.14.4  | Pin Functions                               |

| 9.15 | Port H. |                                             |

|      | 9.15.1  | Port H Data Direction Register (PHDDR)      |

|      | 9.15.2  | Port H Data Register (PHDR)                 |

|      | 9.15.3  | Port H Register (PORTH)                     |

|      | 9.15.4  | Pin Functions                               |

| 9.16 | Port J  |                                             |

|      |         |                                             |

RENESAS

Rev. 6.00 Sep. 24, 2009 Pa REJ09

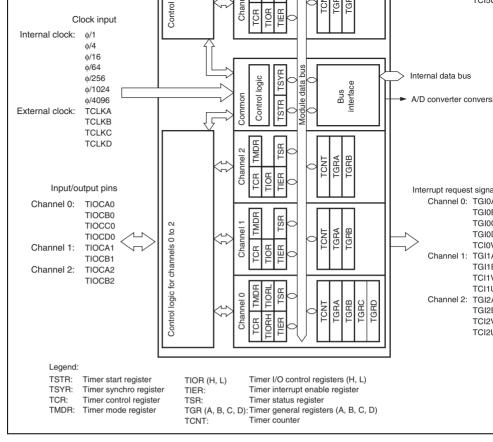

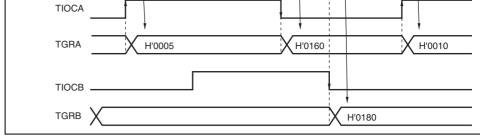

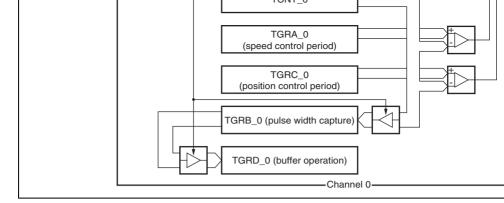

| 10.3 | Register Descriptions |                                                        |  |

|------|-----------------------|--------------------------------------------------------|--|

|      | 10.3.1                | Timer Control Register (TCR)                           |  |

|      | 10.3.2                | Timer Mode Register (TMDR)                             |  |

|      | 10.3.3                | Timer I/O Control Register (TIOR)                      |  |

|      |                       | Timer Interrupt Enable Register (TIER)                 |  |

|      | 10.3.5                | Timer Status Register (TSR)                            |  |

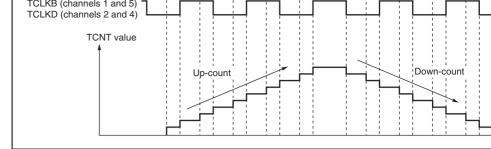

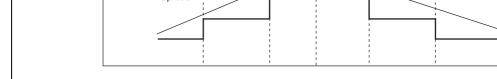

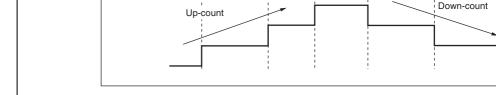

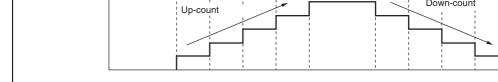

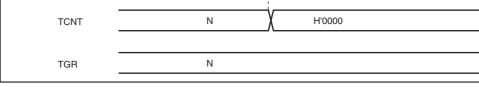

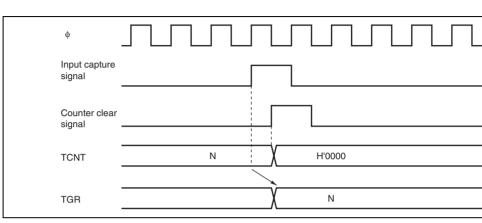

|      | 10.3.6                | Timer Counter (TCNT)                                   |  |

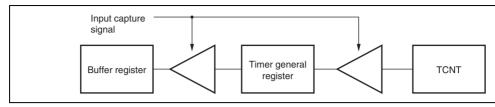

|      | 10.3.7                | Timer General Register (TGR)                           |  |

|      | 10.3.8                | Timer Start Register (TSTR)                            |  |

|      | 10.3.9                | Timer Synchro Register (TSYR)                          |  |

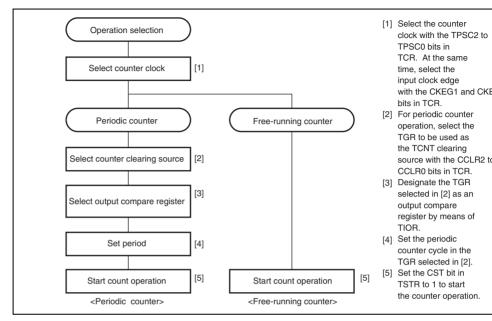

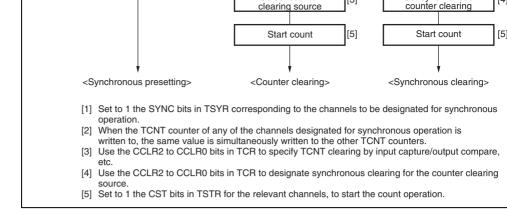

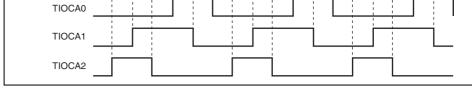

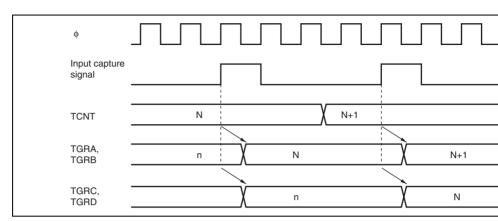

| 10.4 | Operati               | ion                                                    |  |

|      | 10.4.1                | Basic Functions                                        |  |

|      | 10.4.2                | Synchronous Operation                                  |  |

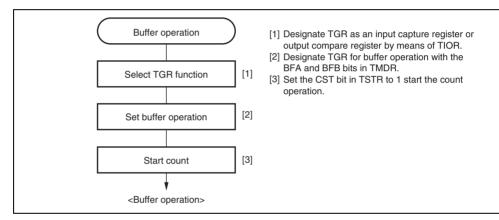

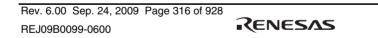

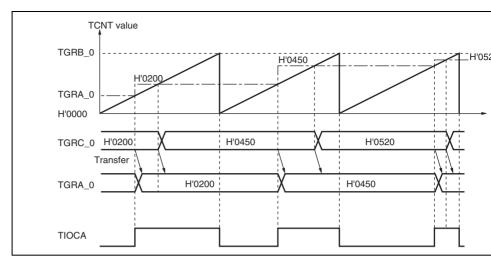

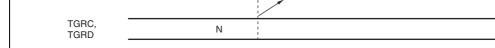

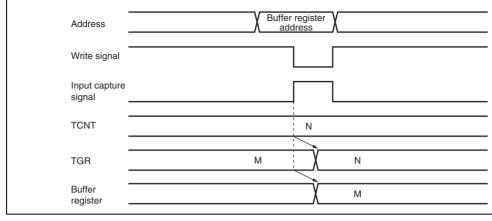

|      | 10.4.3                | Buffer Operation                                       |  |

|      |                       | Cascaded Operation                                     |  |

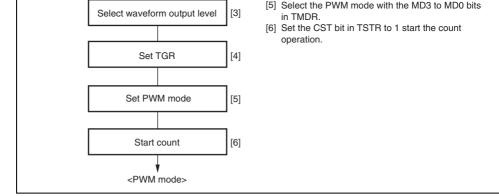

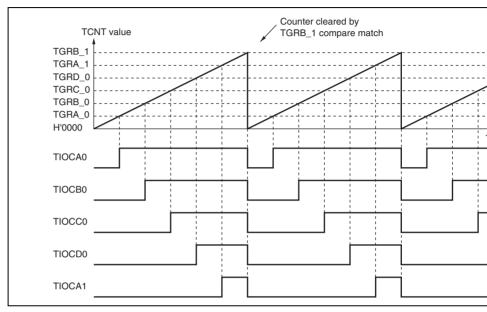

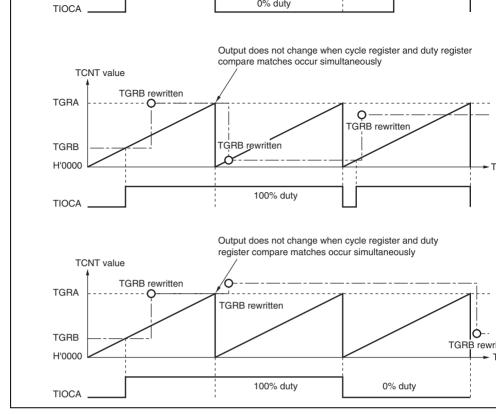

|      | 10.4.5                | PWM Modes                                              |  |

|      | 10.4.6                | Phase Counting Mode                                    |  |

| 10.5 | Interru               | pts                                                    |  |

| 10.6 | DTC A                 | ctivation                                              |  |

| 10.7 | A/D Co                | onverter Activation                                    |  |

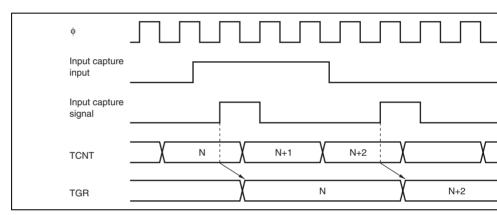

| 10.8 | Operati               | ion Timing                                             |  |

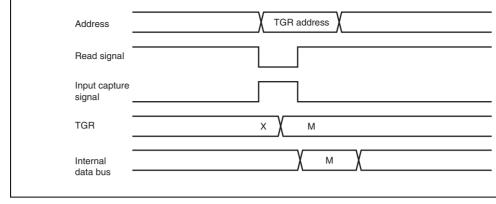

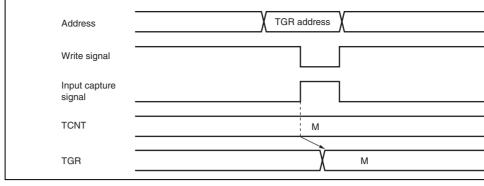

|      | 10.8.1                | Input/Output Timing                                    |  |

|      | 10.8.2                | Interrupt Signal Timing                                |  |

| 10.9 | Usage                 | Notes                                                  |  |

|      | 10.9.1                | Module Stop Mode Setting                               |  |

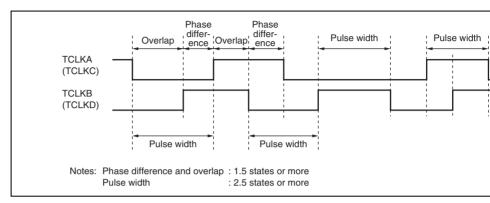

|      | 10.9.2                | Input Clock Restrictions                               |  |

|      | 10.9.3                | Caution on Period Setting                              |  |

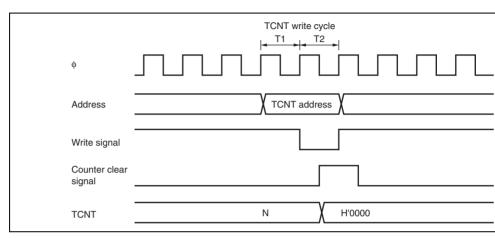

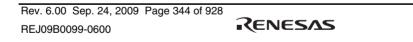

|      | 10.9.4                | Contention between TCNT Write and Clear Operations     |  |

|      | 10.9.5                | Contention between TCNT Write and Increment Operations |  |

|      |                       |                                                        |  |

Rev. 6.00 Sep. 24, 2009 Page xvi of xlvi

REJ09B0099-0600

RENESAS

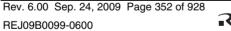

| 11.1 | Feature           | 28                                                          |

|------|-------------------|-------------------------------------------------------------|

| 11.2 | Input/Output Pins |                                                             |

| 11.3 | Registe           | er Descriptions                                             |

|      | 11.3.1            | Timer Counter (TCNT)                                        |

|      | 11.3.2            | Time Constant Register A (TCORA)                            |

|      | 11.3.3            | Time Constant Register B (TCORB)                            |

|      | 11.3.4            | Timer Control Register (TCR)                                |

|      | 11.3.5            | Timer Control/Status Register (TCSR)                        |

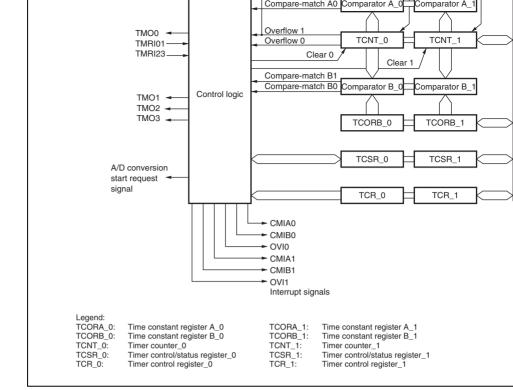

| 11.4 | Operati           | ion                                                         |

|      | 11.4.1            | Pulse Output                                                |

| 11.5 | Operati           | ion Timing                                                  |

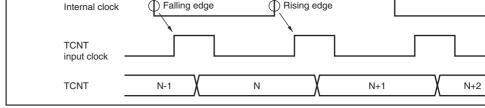

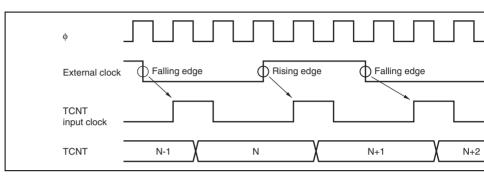

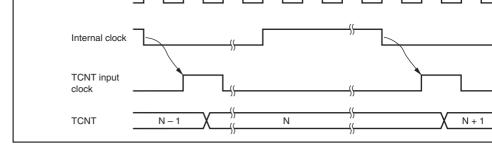

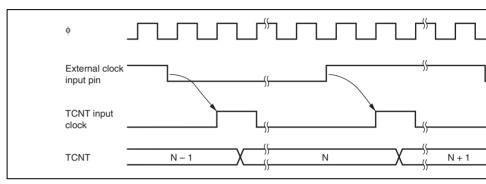

|      | 11.5.1            | TCNT Incrementation Timing                                  |

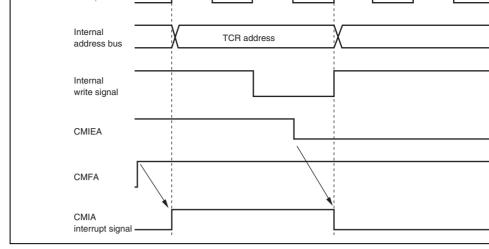

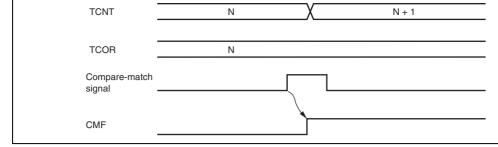

|      | 11.5.2            | Timing of CMFA and CMFB Setting When a Compare-Match Occurs |

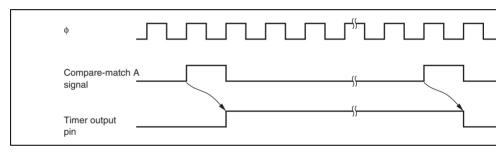

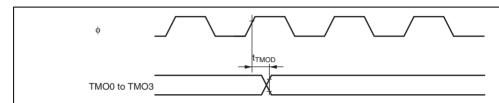

|      | 11.5.3            | Timing of Timer Output When a Compare-Match Occurs          |

|      | 11.5.4            | Timing of Compare-Match Clear When a Compare-Match Occurs   |

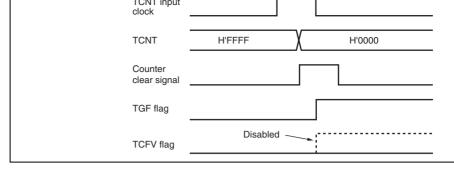

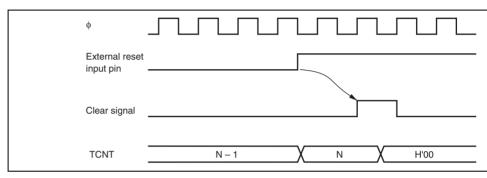

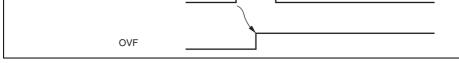

|      | 11.5.5            | TCNT External Reset Timing                                  |

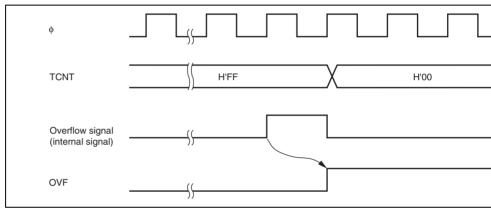

|      | 11.5.6            | Timing of Overflow Flag (OVF) Setting                       |

| 11.6 | Operati           | ion with Cascaded Connection                                |

|      | 11.6.1            | 16-Bit Count Mode                                           |

|      | 11.6.2            | Compare-Match Count Mode                                    |

| 11.7 | Interru           | pt Sources                                                  |

|      | 11.7.1            | Interrupt Sources and DTC Activation                        |

|      | 11.7.2            | A/D Converter Activation                                    |

| 11.8 | Usage             | Notes                                                       |

|      | 11.8.1            | Setting Module Stop Mode                                    |

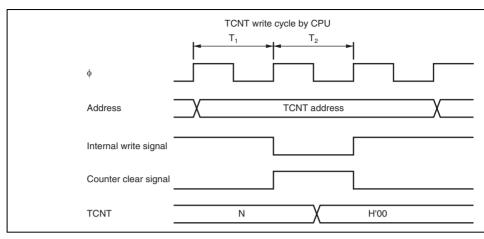

|      | 11.8.2            | Contention between TCNT Write and Clear                     |

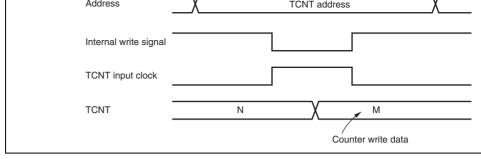

|      | 11.8.3            | Contention between TCNT Write and Increment                 |

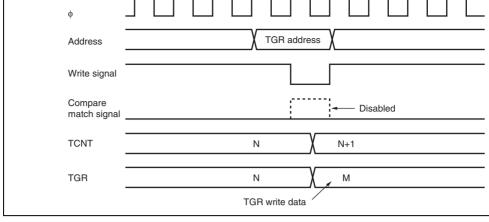

|      | 11.8.4            | Contention between TCOR Write and Compare-Match             |

|      | 11.8.5            | Contention between Compare-Matches A and B                  |

|      |                   |                                                             |

Renesas

Rev. 6.00 Sep. 24, 2009 Pag REJ09

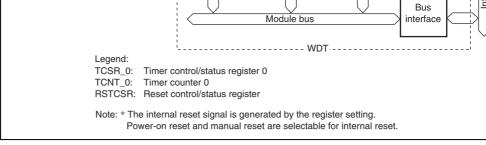

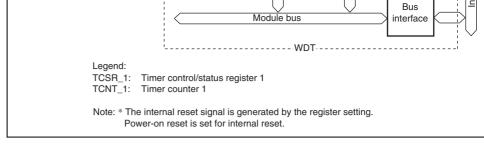

| 12.4          | 4 Operation                                                                                                             |                                                                                                                                                                                                                                                                                                        |

|---------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | 12.4.1                                                                                                                  | Watchdog Timer Mode                                                                                                                                                                                                                                                                                    |

|               | 12.4.2                                                                                                                  | Interval Timer Mode                                                                                                                                                                                                                                                                                    |

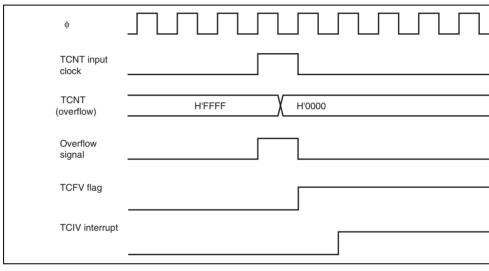

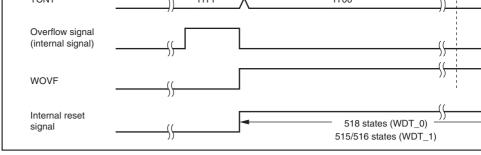

|               | 12.4.3                                                                                                                  | Timing of Setting Overflow Flag (OVF)                                                                                                                                                                                                                                                                  |

|               | 12.4.4                                                                                                                  | Timing of Setting Watchdog Timer Overflow Flag (WOVF)                                                                                                                                                                                                                                                  |

| 12.5          | Interru                                                                                                                 | pt Sources                                                                                                                                                                                                                                                                                             |

| 12.6          | Usage                                                                                                                   | Notes                                                                                                                                                                                                                                                                                                  |

|               | 12.6.1                                                                                                                  | Notes on Register Access                                                                                                                                                                                                                                                                               |

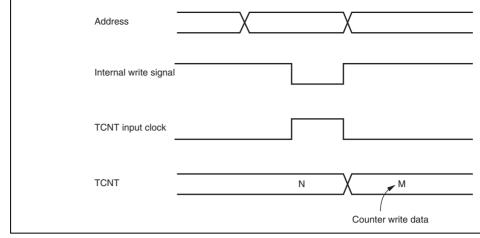

|               | 12.6.2                                                                                                                  | Contention between Timer Counter (TCNT) Write and Increment                                                                                                                                                                                                                                            |

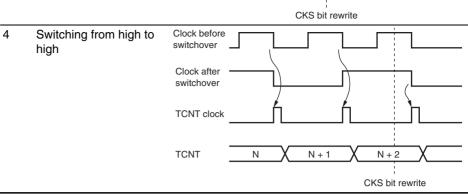

|               | 12.6.3                                                                                                                  | Changing Value of PSS or CKS2 to CKS0                                                                                                                                                                                                                                                                  |

|               | 12.6.4                                                                                                                  | Switching between Watchdog Timer Mode and Interval Timer Mode                                                                                                                                                                                                                                          |

|               |                                                                                                                         | Internal Reset in Watchdog Timer Mode                                                                                                                                                                                                                                                                  |

|               | 12.6.6                                                                                                                  | OVF Flag Clearing in Interval Timer Mode                                                                                                                                                                                                                                                               |

|               |                                                                                                                         | Initialization of TCNT by the TME Bit                                                                                                                                                                                                                                                                  |

|               |                                                                                                                         |                                                                                                                                                                                                                                                                                                        |

|               |                                                                                                                         |                                                                                                                                                                                                                                                                                                        |

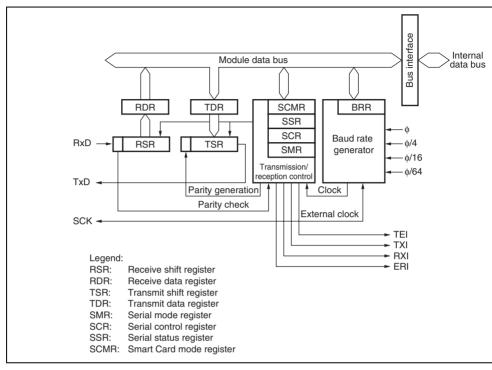

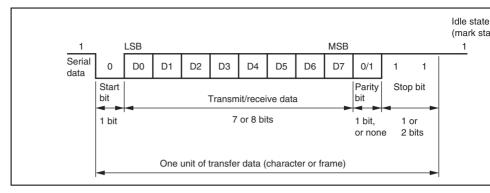

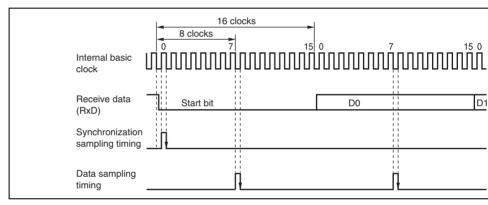

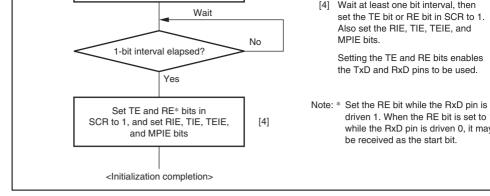

| Secti         | ion $13$                                                                                                                | Serial Communication Interface (SCI)                                                                                                                                                                                                                                                                   |

| Secti<br>13.1 |                                                                                                                         | Serial Communication Interface (SCI)                                                                                                                                                                                                                                                                   |

|               | Feature                                                                                                                 |                                                                                                                                                                                                                                                                                                        |

| 13.1          | Feature<br>Input/C                                                                                                      | S                                                                                                                                                                                                                                                                                                      |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe                                                                                           | s<br>Dutput Pins                                                                                                                                                                                                                                                                                       |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1                                                                                 | es<br>Dutput Pins<br>Pr Descriptions                                                                                                                                                                                                                                                                   |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2                                                                       | es<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)                                                                                                                                                                                                                                   |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2<br>13.3.3                                                             | S<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)<br>Receive Data Register (RDR)                                                                                                                                                                                                     |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2<br>13.3.3<br>13.3.4                                                   | Ss<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)<br>Receive Data Register (RDR)<br>Transmit Data Register (TDR)<br>Transmit Shift Register (TSR)                                                                                                                                   |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2<br>13.3.3<br>13.3.4                                                   | Ss<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)<br>Receive Data Register (RDR)<br>Transmit Data Register (TDR)                                                                                                                                                                    |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2<br>13.3.3<br>13.3.4<br>13.3.5                                         | Ss<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)<br>Receive Data Register (RDR)<br>Transmit Data Register (TDR)<br>Transmit Shift Register (TSR)<br>Serial Mode Register (SMR)<br>Serial Control Register (SCR)                                                                    |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2<br>13.3.3<br>13.3.4<br>13.3.5<br>13.3.6                               | Ss<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)<br>Receive Data Register (RDR)<br>Transmit Data Register (TDR)<br>Transmit Shift Register (TSR)<br>Serial Mode Register (SMR)<br>Serial Control Register (SCR)                                                                    |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2<br>13.3.3<br>13.3.4<br>13.3.5<br>13.3.6<br>13.3.7<br>13.3.8           | Ss<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)<br>Receive Data Register (RDR)<br>Transmit Data Register (TDR)<br>Transmit Shift Register (TSR)<br>Serial Mode Register (SMR)<br>Serial Control Register (SCR)<br>Serial Status Register (SSR)<br>Smart Card Mode Register (SCMR) |

| 13.1<br>13.2  | Feature<br>Input/C<br>Registe<br>13.3.1<br>13.3.2<br>13.3.3<br>13.3.4<br>13.3.5<br>13.3.6<br>13.3.7<br>13.3.8<br>13.3.9 | Ss<br>Dutput Pins<br>er Descriptions<br>Receive Shift Register (RSR)<br>Receive Data Register (RDR)<br>Transmit Data Register (TDR)<br>Transmit Shift Register (TSR)<br>Serial Mode Register (SMR)<br>Serial Control Register (SCR)<br>Serial Status Register (SSR)                                    |

Rev. 6.00 Sep. 24, 2009 Page xviii of xlvi REJ09B0099-0600

RENESAS

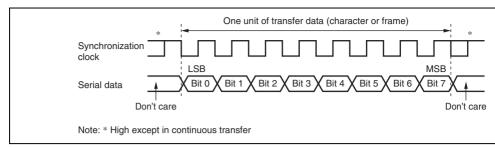

|      | 13.6.1  | Clock                                                                |  |  |

|------|---------|----------------------------------------------------------------------|--|--|

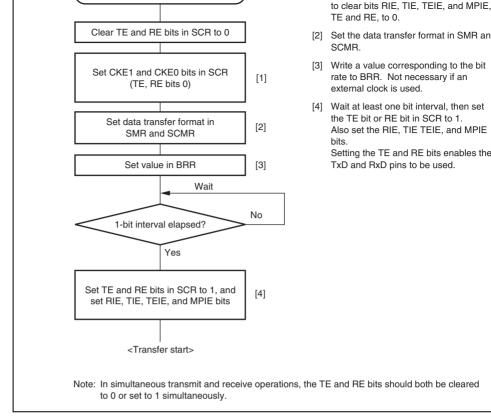

|      | 13.6.2  | SCI Initialization (Clocked Synchronous Mode)                        |  |  |

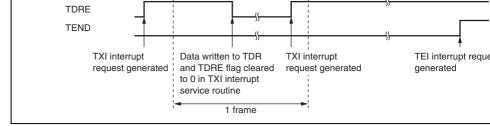

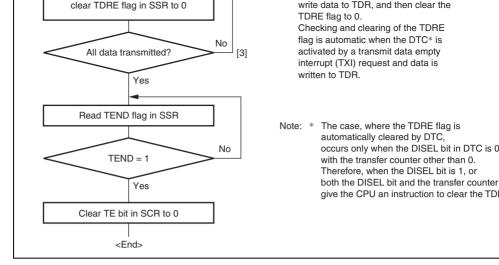

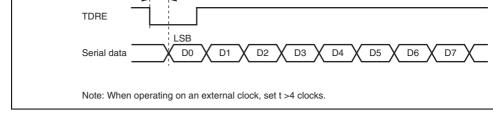

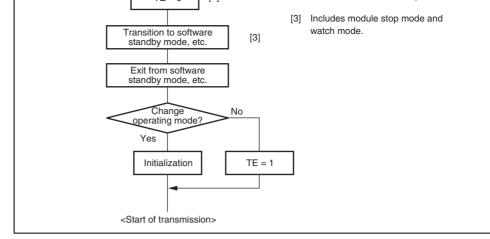

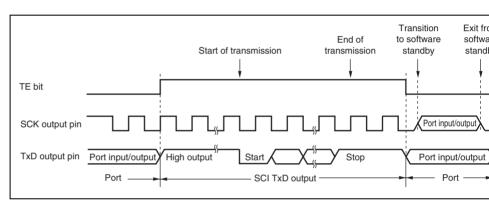

|      | 13.6.3  | Serial Data Transmission (Clocked Synchronous Mode)                  |  |  |

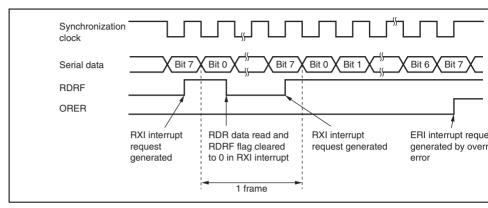

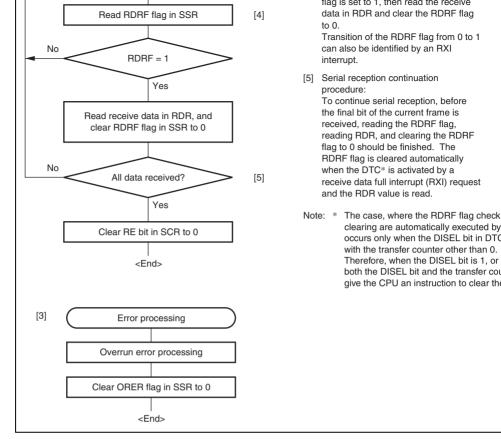

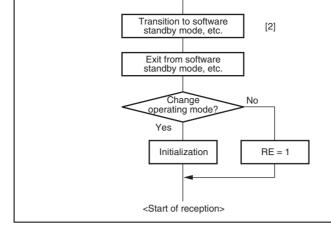

|      | 13.6.4  | Serial Data Reception (Clocked Synchronous Mode)                     |  |  |

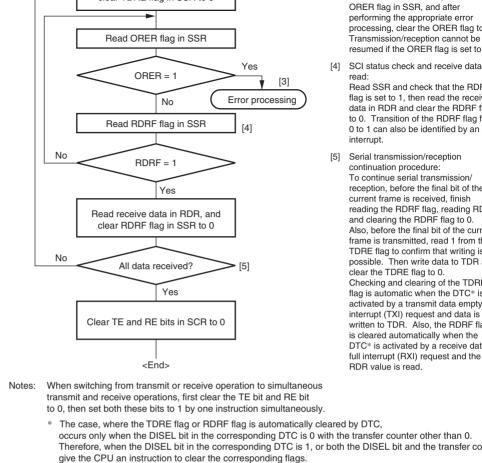

|      | 13.6.5  | Simultaneous Serial Data Transmission and Reception (Clocked Synchro |  |  |

|      |         | Mode)                                                                |  |  |

| 13.7 | Operati | Operation in Smart Card Interface                                    |  |  |

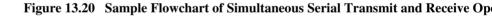

|      | 13.7.1  | Pin Connection Example                                               |  |  |

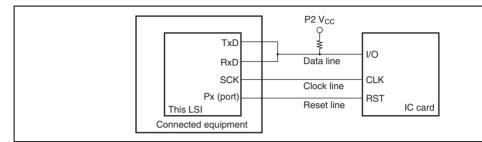

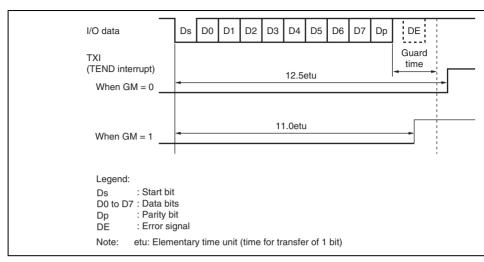

|      | 13.7.2  | Data Format (Except for Block Transfer Mode)                         |  |  |

|      | 13.7.3  | Block Transfer Mode                                                  |  |  |

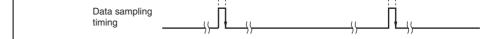

|      | 13.7.4  | Receive Data Sampling Timing and Reception Margin                    |  |  |

|      | 13.7.5  | Initialization                                                       |  |  |

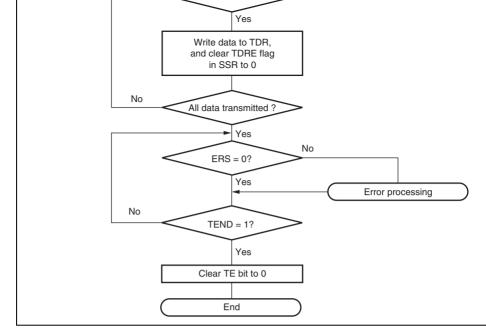

|      | 13.7.6  | Serial Data Transmission (Except for Block Transfer Mode)            |  |  |

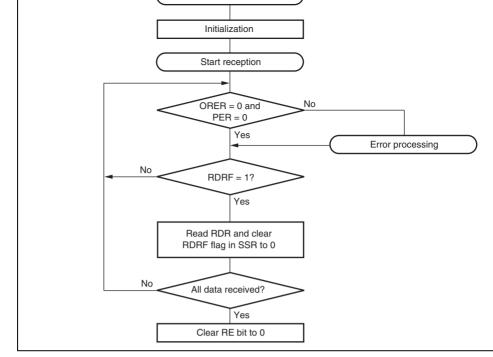

|      | 13.7.7  | Serial Data Reception (Except for Block Transfer Mode)               |  |  |

|      | 13.7.8  | Clock Output Control                                                 |  |  |

| 13.8 | Interru | ot Sources                                                           |  |  |

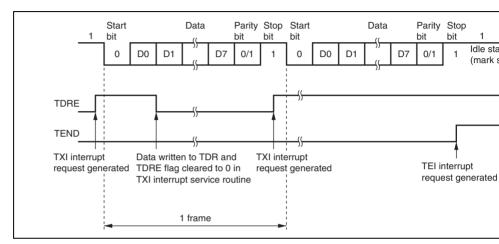

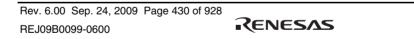

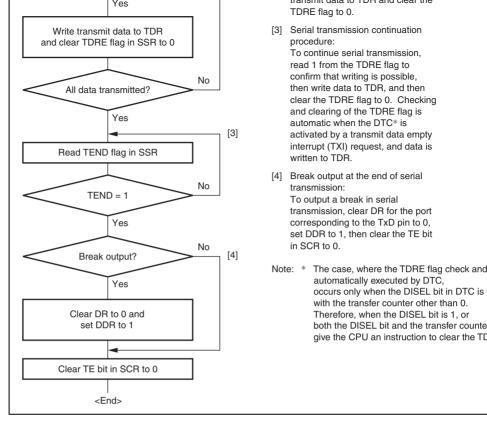

|      | 13.8.1  | Interrupts in Normal Serial Communication Interface Mode             |  |  |

|      | 13.8.2  | Interrupts in Smart Card Interface Mode                              |  |  |

| 13.9 | Usage I | Notes                                                                |  |  |

|      | 13.9.1  | Module Stop Mode Setting                                             |  |  |

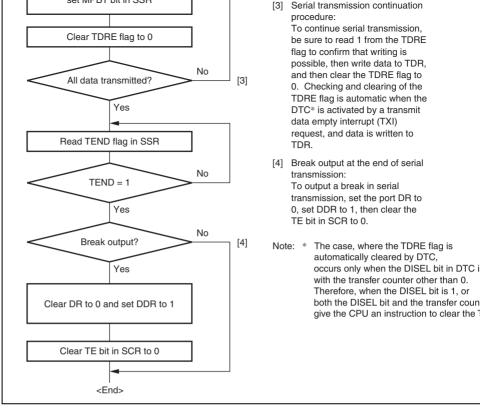

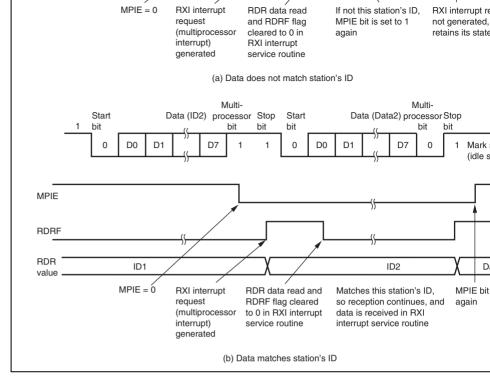

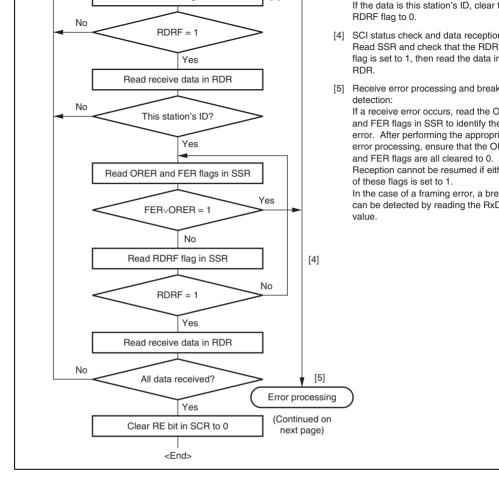

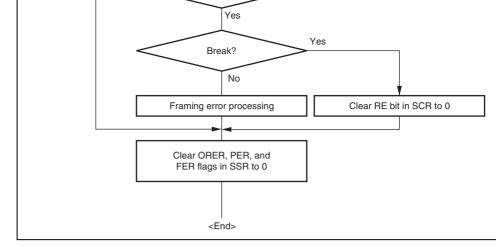

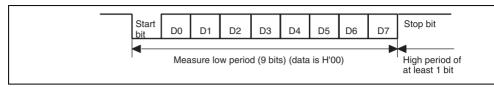

|      | 13.9.2  | Break Detection and Processing (Asynchronous Mode Only)              |  |  |

|      | 13.9.3  | Mark State and Break Detection (Asynchronous Mode Only)              |  |  |

|      | 13.9.4  | Receive Error Flags and Transmit Operations                          |  |  |

|      |         | (Clocked Synchronous Mode Only)                                      |  |  |

|      | 13.9.5  | Restrictions on Use of DTC                                           |  |  |

|      | 13.9.6  | Operation in Case of Mode Transition                                 |  |  |

|      | 13.9.7  | Notes when Switching from SCK Pin to Port Pin                        |  |  |

|      |         |                                                                      |  |  |

RENESAS

Rev. 6.00 Sep. 24, 2009 Pa REJ09

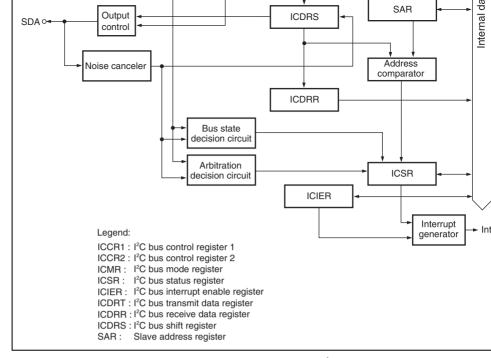

|       | 14.3.7           | I <sup>2</sup> C Bus Transmit Data Register (ICDRT)                    |

|-------|------------------|------------------------------------------------------------------------|

|       | 14.3.8           | I <sup>2</sup> C Bus Receive Data Register (ICDRR)                     |

|       | 14.3.9           | I <sup>2</sup> C Bus Shift Register (ICDRS)                            |

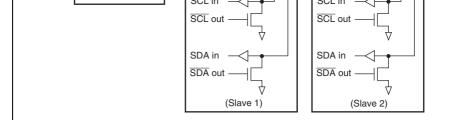

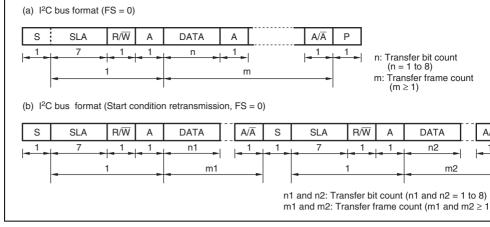

| 14.4  | Operati          | on                                                                     |

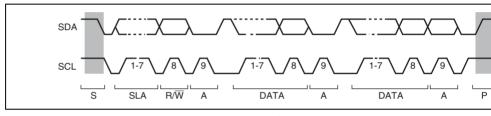

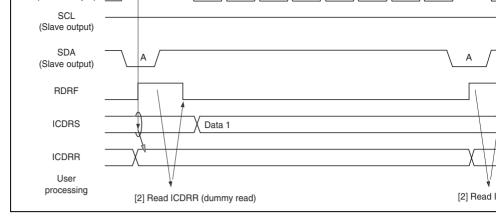

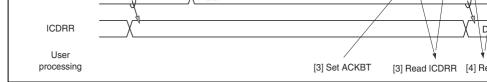

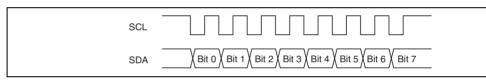

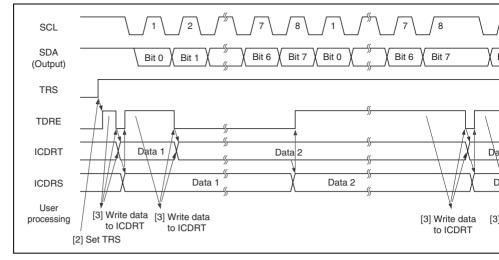

|       | 14.4.1           | I <sup>2</sup> C Bus Format                                            |

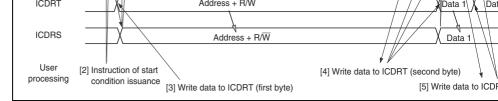

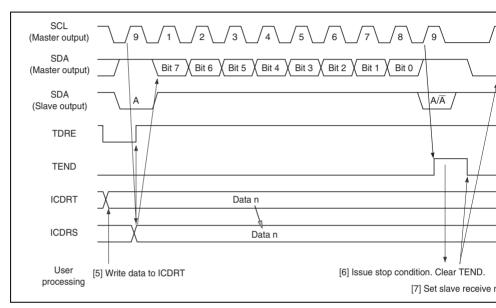

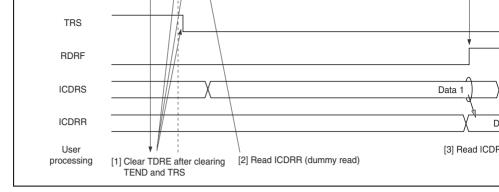

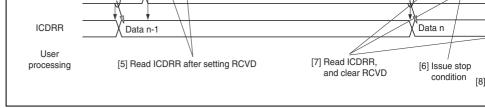

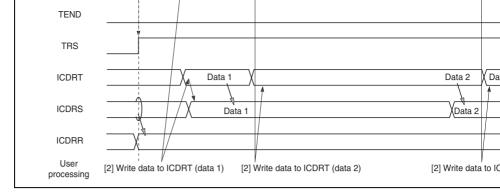

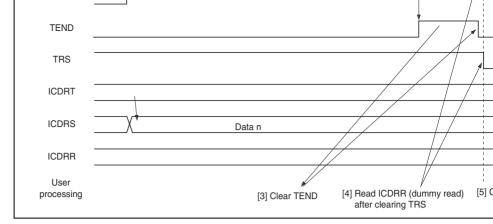

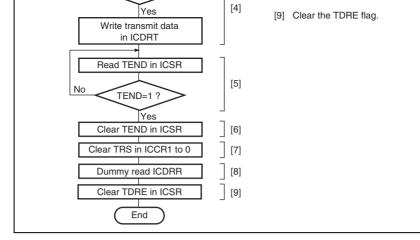

|       | 14.4.2           | Master Transmit Operation                                              |

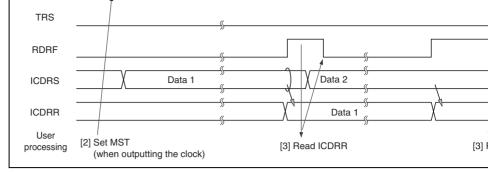

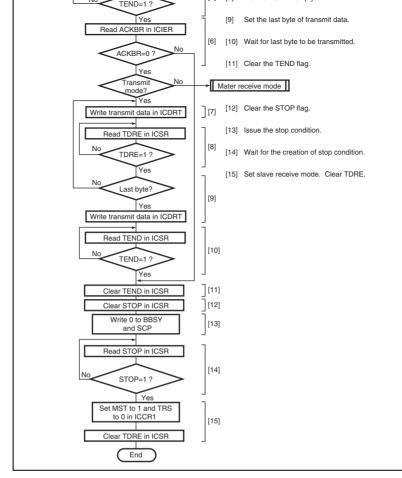

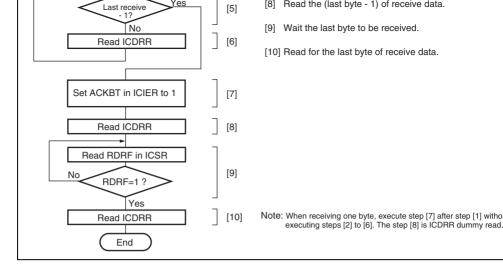

|       | 14.4.3           | Master Receive Operation                                               |

|       | 14.4.4           | Slave Transmit Operation                                               |

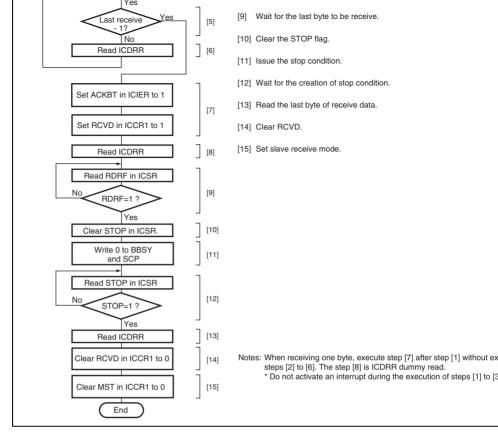

|       | 14.4.5           | Slave Receive Operation                                                |

|       | 14.4.6           | Clocked Synchronous Serial Format                                      |

|       | 14.4.7           | Noise Canceler                                                         |

|       | 14.4.8           | Example of Use                                                         |

| 14.5  | Interru          | pt Request                                                             |

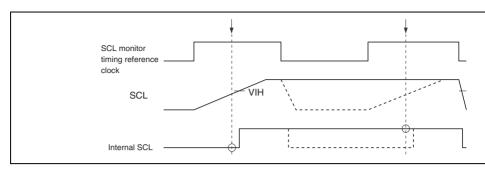

| 14.6  | Bit Syn          | chronous Circuit                                                       |

| 14.7  | Note or          | 1 Usage                                                                |

|       | 14.7.1           | Setting Module Stop Mode                                               |

|       | 14.7.2           | Issuance of Stop and Repeated Start Conditions                         |

|       | 14.7.3           | WAIT Bit in I <sup>2</sup> C Bus Mode Register (ICMR)                  |

|       | 14.7.4           | Usage Note on Master Receive Mode                                      |

|       | 14.7.5           | Restriction on Setting of Transfer Rate in Use of Multi-Master         |

|       | 14.7.6           | Restriction on Use of Bit Manipulation Instructions to Set MST and TRS |

|       |                  | Multi-Master Is Used                                                   |

|       |                  |                                                                        |

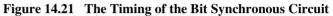

| Secti | ion 15 $\lambda$ | A/D Converter                                                          |

| 15.1  |                  | ·S                                                                     |

| 15.2  | Input/C          | Output Pins                                                            |

| 15.3  | Registe          | r Descriptions                                                         |

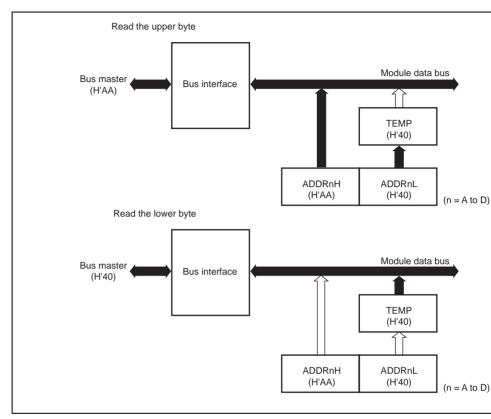

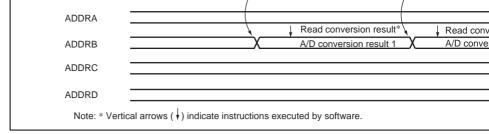

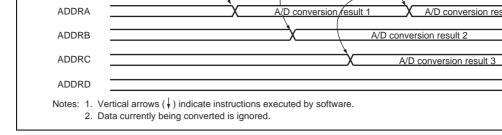

|       |                  | A/D Data Registers A to D (ADDRA to ADDRD)                             |

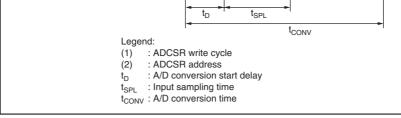

|       | 15.3.2           | A/D Control/Status Register (ADCSR)                                    |

|       |                  |                                                                        |

Rev. 6.00 Sep. 24, 2009 Page xx of xlvi REJ09B0099-0600

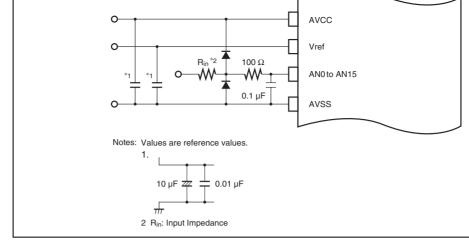

|       | 15.8.2   | Permissible Signal Source Impedance                 |

|-------|----------|-----------------------------------------------------|

|       | 15.8.3   | Influences on Absolute Accuracy                     |

|       | 15.8.4   | Range of Analog Power Supply and Other Pin Settings |

|       | 15.8.5   | Notes on Board Design                               |

|       | 15.8.6   | Notes on Noise Countermeasures                      |

|       |          |                                                     |

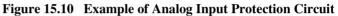

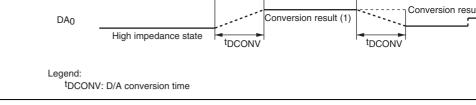

| Secti | ion 16 I | D/A Converter                                       |

| 16.1  | Feature  | S                                                   |

| 16.2  | Input/C  | Output Pins                                         |

| 16.3  | Registe  | r Descriptions                                      |

|       | 16.3.1   | D/A Data Registers 0, 1 (DADR0, DADR1)              |

|       | 16.3.2   | D/A Control Register (DACR)                         |

| 16.4  | Operati  | on                                                  |

| 16.5  | Usage I  | Notes                                               |

|       | 16.5.1   | Analog Power Supply Current in Power-Down Mode      |

|       | 16.5.2   | Setting for Module Stop Mode                        |

|       |          |                                                     |

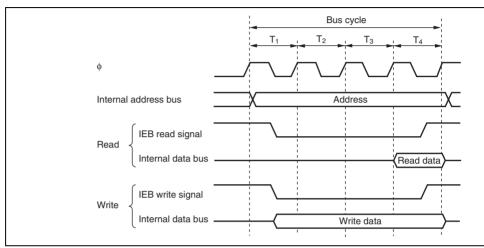

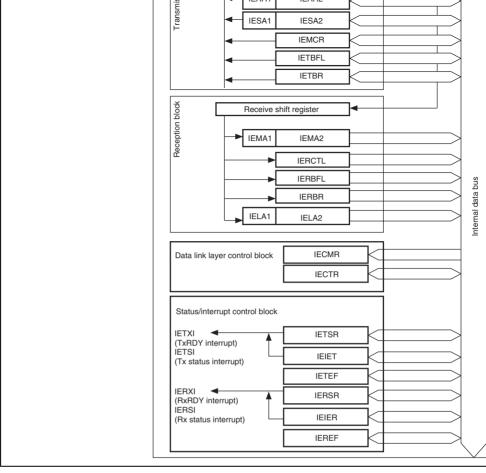

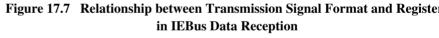

| Secti | ion 17 ] | EBus <sup>™</sup> Controller (IEB) [H8S/2552 Group] |

| 17.1  | Feature  | ·S                                                  |

|       | 17.1.1   | IEBus Communications Protocol                       |

|       | 17.1.2   | Communications Protocol                             |

|       |          | Transfer Data (Data Field Contents)                 |

|       | 17.1.4   | Bit Format                                          |

| 17.2  |          |                                                     |

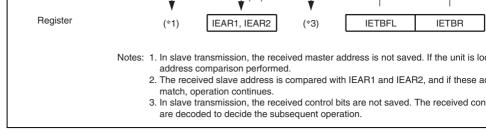

| 17.3  | Registe  | r Descriptions                                      |

|       | 17.3.1   | IEBus Control Register (IECTR)                      |

|       | 17.3.2   | IEBus Command Register (IECMR)                      |

|       | 17.3.3   | IEBus Master Control Register (IEMCR)               |

|       | 17.3.4   | IEBus Master Unit Address Register 1 (IEAR1)        |

|       |          |                                                     |

Renesas

Rev. 6.00 Sep. 24, 2009 Pa REJ09

|      | 17.3.16  | EBus Lock Address Register 2 (IELA2)                     |

|------|----------|----------------------------------------------------------|

|      | 17.3.17  | ' IEBus General Flag Register (IEFLG)                    |

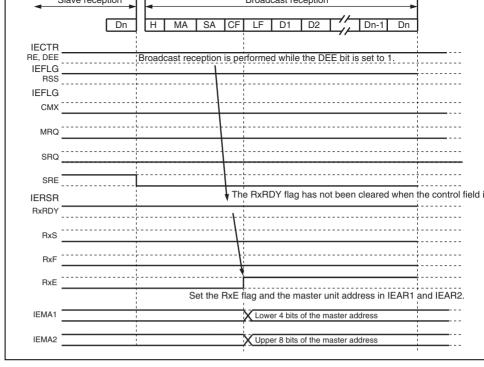

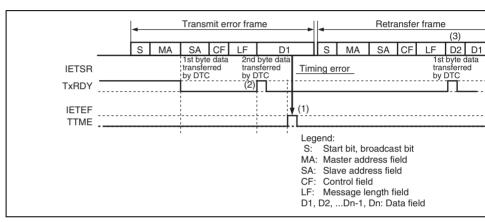

|      | 17.3.18  | EIEBus Transmit/Runaway Status Register (IETSR)          |

|      | 17.3.19  | IEBus Transmit/Runaway Interrupt Enable Register (IEIET) |

|      | 17.3.20  | IEBus Transmit Error Flag Register (IETEF)               |

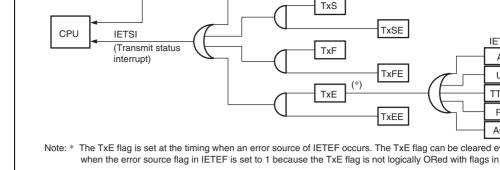

|      | 17.3.21  | IEBus Receive Status Register (IERSR)                    |

|      |          | 2 IEBus Receive Interrupt Enable Register (IEIER)        |

|      | 17.3.23  | EBus Receive Error Flag Register (IEREF)                 |

| 17.4 | Operati  | on Descriptions                                          |

|      |          | Master Transmit Operation                                |

|      |          | Slave Receive Operation                                  |

|      | 17.4.3   | Master Reception                                         |

|      |          | Slave Transmission                                       |

| 17.5 | Interruj | pt Sources                                               |

| 17.6 |          | Notes                                                    |

|      | 17.6.1   | Setting Module Stop Mode                                 |

|      |          | TxRDY Flag and Underrun Error                            |

|      | 17.6.3   | RxRDY Flag and Overrun Error                             |

|      |          | Error Flag s in the IETEF                                |

|      |          | Error Flags in IEREF                                     |

|      | 17.6.6   | Notes on Slave Transmission                              |

|      | 17.6.7   | Notes on DTC Specification                               |

|      |          | Error Handling in Transmission                           |

|      |          | Power-Down Mode Operation                                |

|      | 17.6.10  | Notes on Middle-Speed Mode                               |

|      |          | Notes on Register Access                                 |

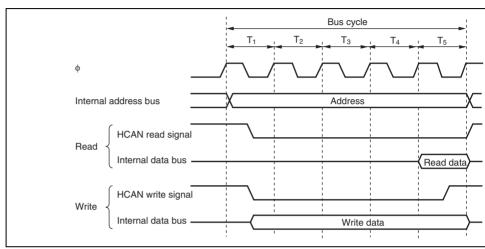

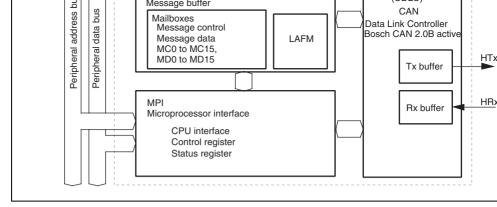

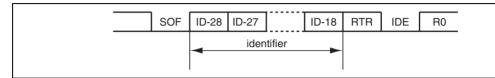

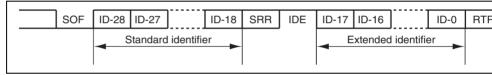

| Sect | on 18    | Controller Area Network (HCAN) [H8S/2556 Group]          |

|      |          |                                                          |

| 18.1 | геаште   | S                                                        |

Rev. 6.00 Sep. 24, 2009 Page xxii of xlvi REJ09B0099-0600

|      | 18.3.10           | Remote Request Register (RFPR)                |

|------|-------------------|-----------------------------------------------|

|      | 18.3.11           | Interrupt Register (IRR)                      |

|      | 18.3.12           | Mailbox Interrupt Mask Register (MBIMR)       |

|      | 18.3.13           | Interrupt Mask Register (IMR)                 |

|      | 18.3.14           | Receive Error Counter (REC)                   |

|      | 18.3.15           | Transmit Error Counter (TEC)                  |

|      | 18.3.16           | Unread Message Status Register (UMSR)         |

|      | 18.3.17           | Local Acceptance Filter Masks (LAFML, LAFMH)  |

|      | 18.3.18           | Message Control (MC0 to MC15)                 |

|      | 18.3.19           | Message Data (MD0 to MD15)                    |

| 18.4 | Operati           | on                                            |

|      | 18.4.1            | Hardware and Software Resets                  |

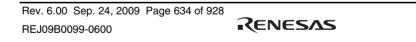

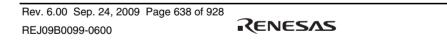

|      | 18.4.2            | Initialization after Hardware Reset           |

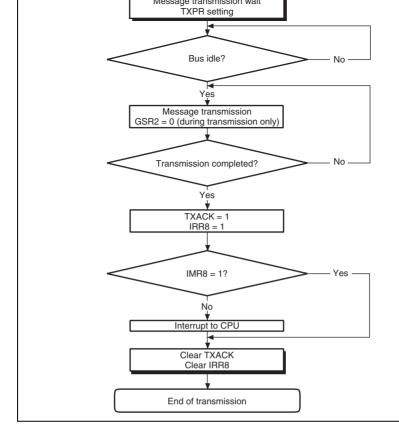

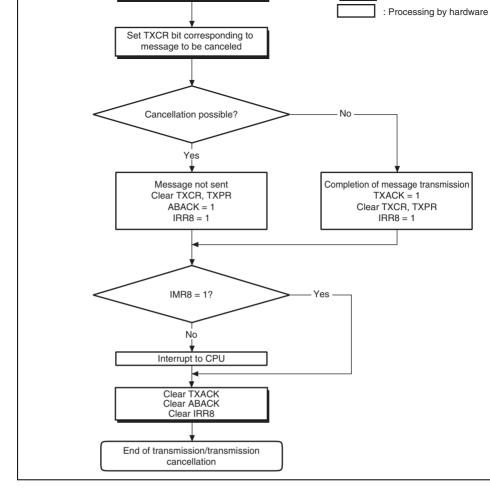

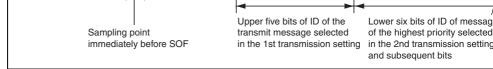

|      | 18.4.3            | Message Transmission                          |

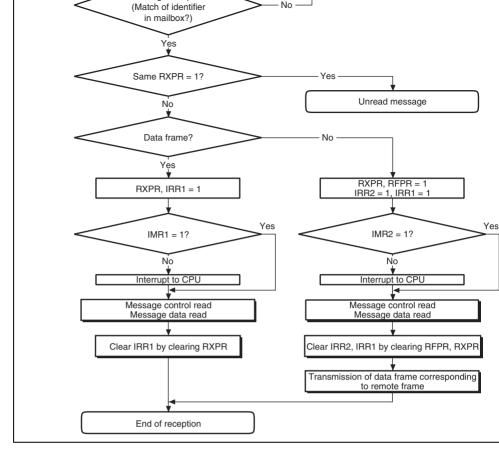

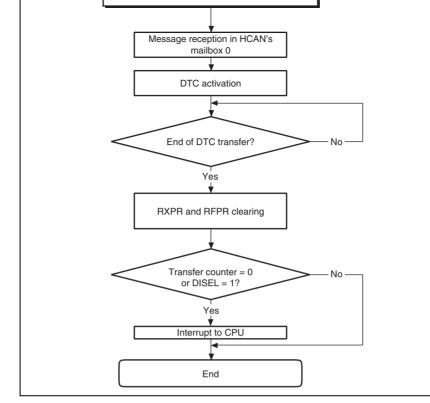

|      | 18.4.4            | Message Reception                             |

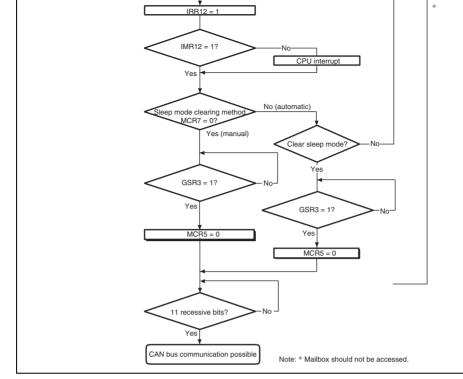

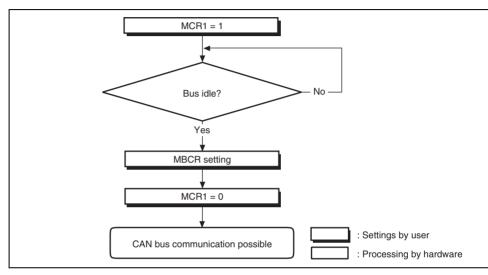

|      | 18.4.5            | HCAN Sleep Mode                               |

|      | 18.4.6            | HCAN Halt Mode                                |

| 18.5 | Interrup          | pts                                           |

| 18.6 | -                 | iterface                                      |

| 18.7 | CAN Bus Interface |                                               |

| 18.8 | Usage 1           | Notes                                         |

|      |                   | Module Stop Mode Setting                      |

|      | 18.8.2            | Reset                                         |

|      | 18.8.3            | HCAN Sleep Mode                               |

|      | 18.8.4            | Interrupts                                    |

|      | 18.8.5            | Error Counters                                |

|      | 18.8.6            | Register Access                               |

|      | 18.8.7            | HCAN Medium-Speed Mode                        |

|      | 18.8.8            | Register Hold in Standby Modes and Watch Mode |

|      |                   |                                               |

Renesas

Rev. 6.00 Sep. 24, 2009 Pag REJ09

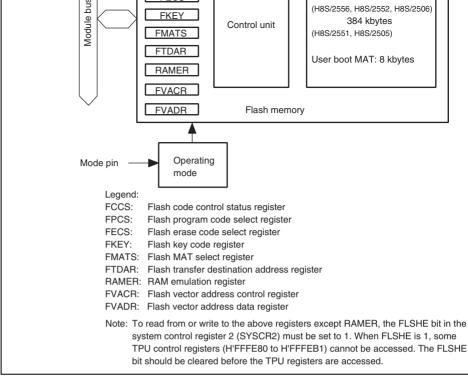

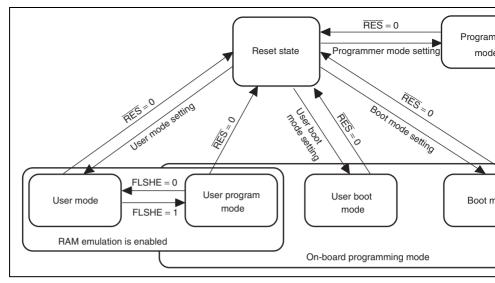

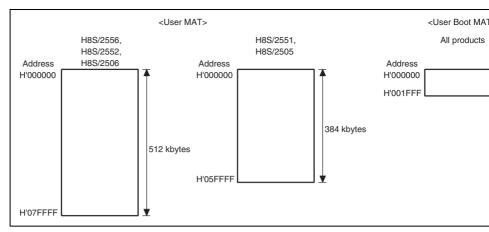

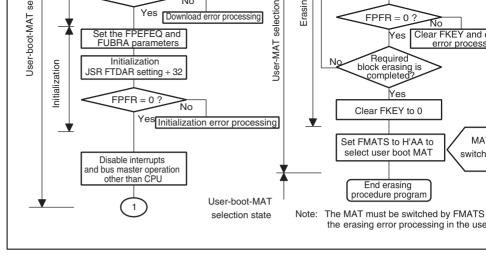

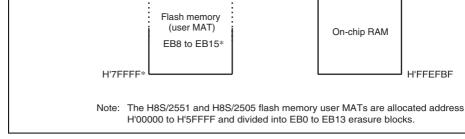

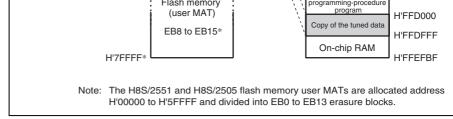

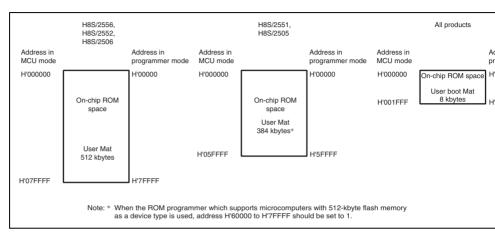

|      | 20.1.2                                       | Operating Mode                                           |

|------|----------------------------------------------|----------------------------------------------------------|

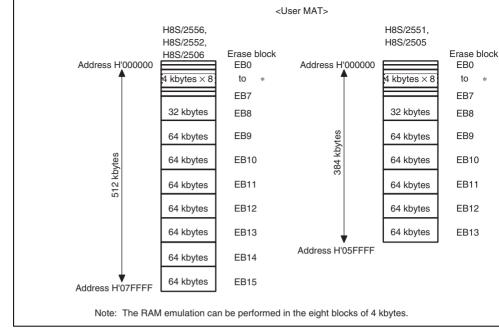

|      | 20.1.3                                       | Mode Comparison                                          |

|      | 20.1.4                                       | Flash MAT Configuration                                  |

|      | 20.1.5                                       | Block Division                                           |

|      | 20.1.6                                       | Programming/Erasing Interface                            |

| 20.2 | Pin Co                                       | nfiguration                                              |

| 20.3 | Registe                                      | r Descriptions                                           |

|      | 20.3.1                                       | Programming/Erasing Interface Register                   |

|      | 20.3.2                                       | Programming/Erasing Interface Parameter                  |

|      | 20.3.3                                       | RAM Emulation Register (RAMER)                           |

|      | 20.3.4                                       | Flash Vector Address Control Register (FVACR)            |

|      | 20.3.5                                       | Flash Vector Address Data Register (FVADR)               |

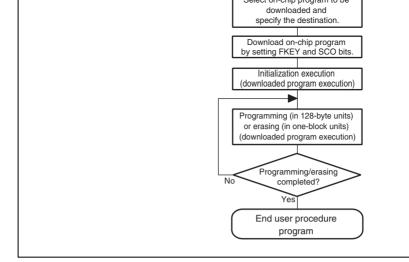

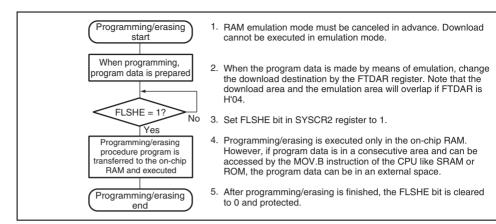

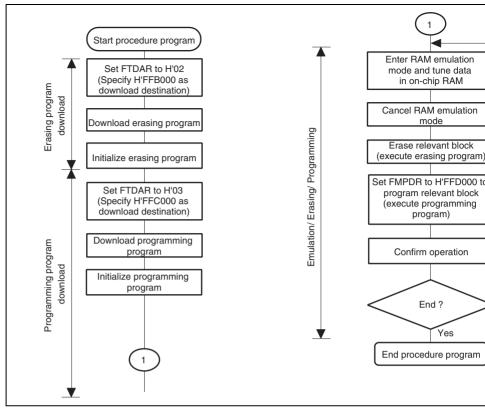

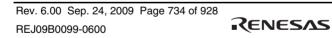

| 20.4 | On-Boa                                       | ard Programming Mode                                     |

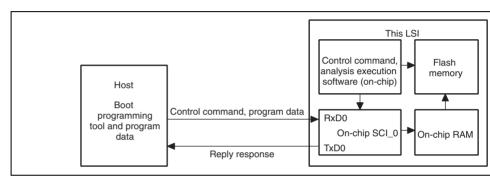

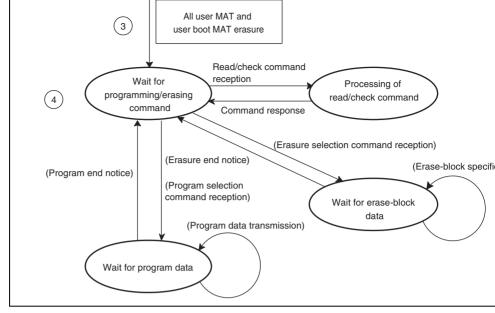

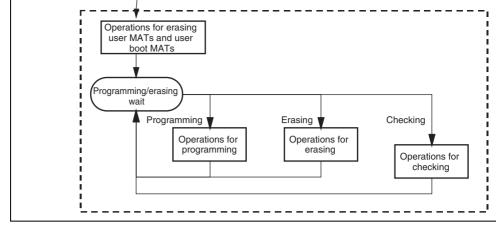

|      | 20.4.1                                       | Boot Mode                                                |

|      | 20.4.2                                       | User Program Mode                                        |

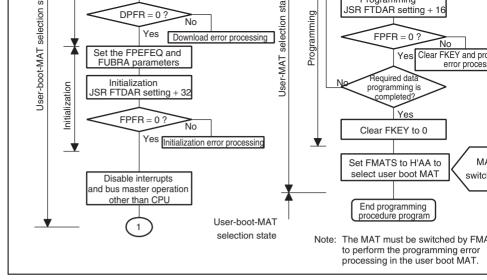

|      | 20.4.3                                       | User Boot Mode                                           |

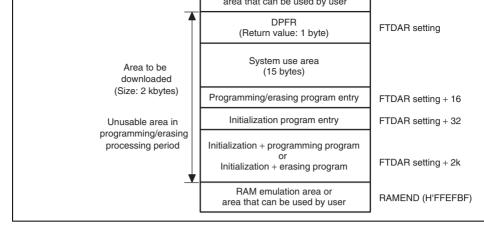

|      | 20.4.4                                       | Procedure Program and Storable Area for Programming Data |

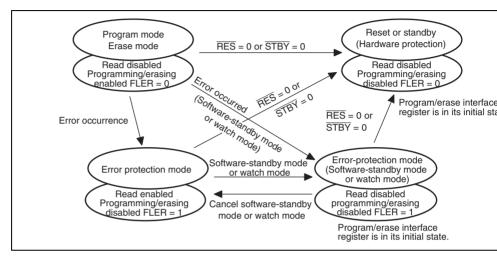

| 20.5 | Protect                                      | ion                                                      |

|      | 20.5.1                                       | Hardware Protection                                      |

|      | 20.5.2                                       | Software Protection                                      |

|      | 20.5.3                                       | Error Protection                                         |

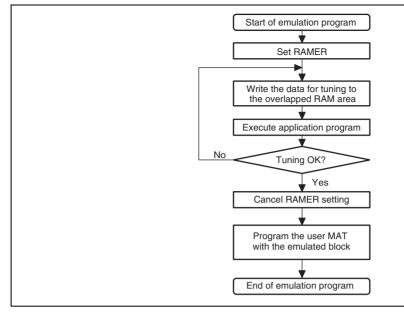

| 20.6 | Flash N                                      | Iemory Emulation in RAM                                  |

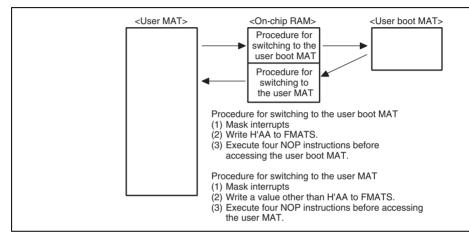

| 20.7 | Switching between User MAT and User Boot MAT |                                                          |

| 20.8 | Usage Notes                                  |                                                          |

| 20.9 | 9 Programmer Mode                            |                                                          |

|      | 20.9.1                                       | Pin Arrangement of Socket Adapter                        |

|      | 20.9.2                                       | Programmer Mode Operation                                |

|      |                                              | Memory-Read Mode                                         |

|      | 20.9.4                                       | Auto-Program Mode                                        |

|      |                                              |                                                          |

Rev. 6.00 Sep. 24, 2009 Page xxiv of xlvi

REJ09B0099-0600

RENESAS

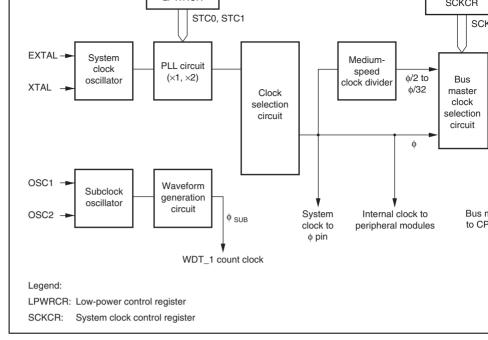

|       | 21.1.2                      | Low-Power Control Register (LPWRCR)                            |  |

|-------|-----------------------------|----------------------------------------------------------------|--|

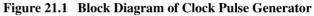

| 21.2  | System                      | Clock Oscillator                                               |  |

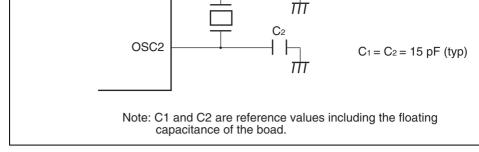

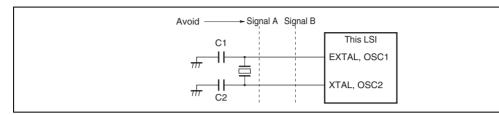

|       | 21.2.1                      | Connecting Crystal Resonator                                   |  |

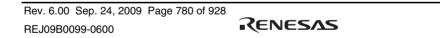

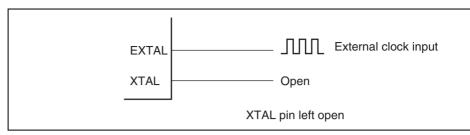

|       | 21.2.2                      | External Clock Input                                           |  |

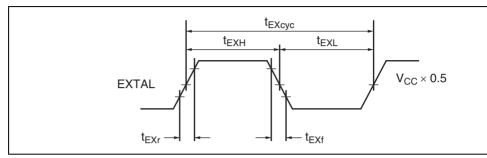

|       |                             | Notes on Switching External Clock                              |  |

| 21.3  | PLL Ci                      | rcuit                                                          |  |

| 21.4  |                             | n-Speed Clock Divider                                          |  |

| 21.5  | Bus Ma                      | aster Clock Selection Circuit                                  |  |

| 21.6  | System                      | Clock with IEBus                                               |  |

| 21.7  | Subclo                      | ck Oscillator                                                  |  |

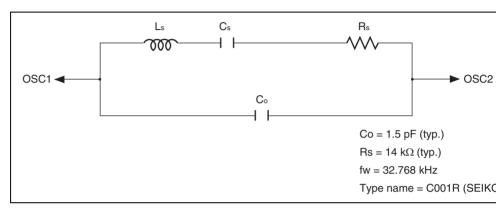

|       | 21.7.1                      | Connecting 32.768-kHz Crystal Resonator                        |  |

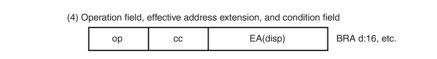

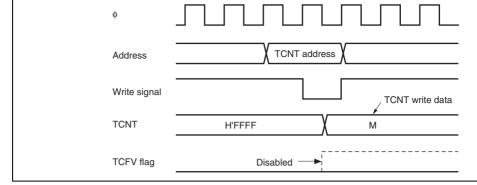

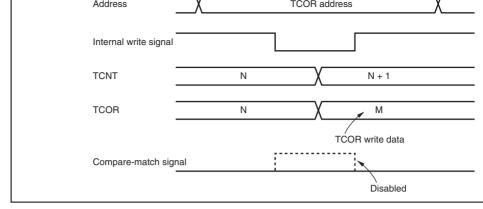

|       | 21.7.2                      | Handling Pins when Subclock Is Not Used                        |  |