## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

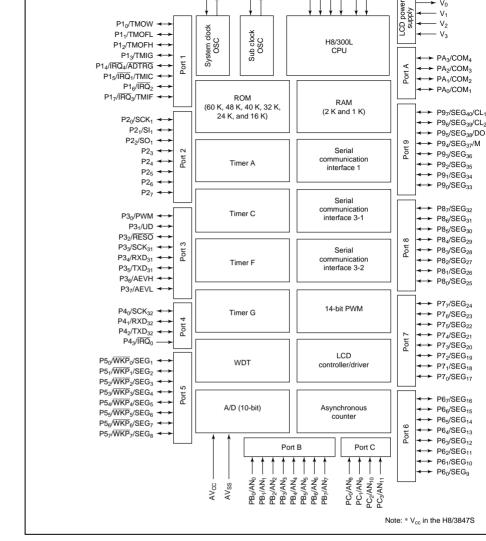

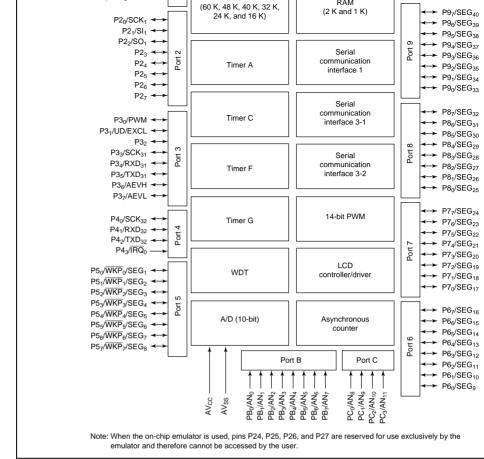

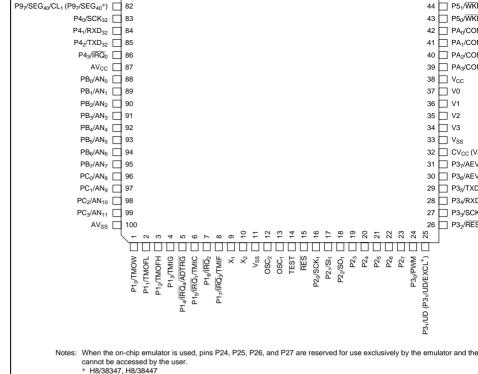

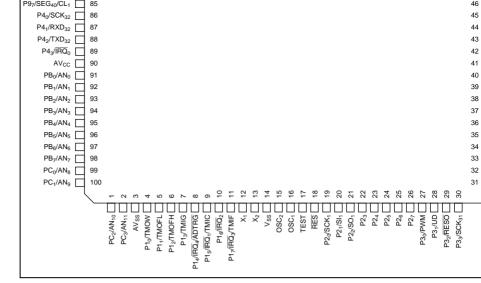

H8/3847R Group, H8/3847S Group, H8/38347 Group, H8/38447 Group

# Hardware Manual

Renesas 8-Bit Single-Chip Microcomputer H8 Family/H8/300L Super Low Power Series

| H8/3847R Group | H8/3843R<br>H8/3844R<br>H8/3845R<br>H8/3846R<br>H8/3847R | H8/38347 | Group | H8/38342<br>H8/38343<br>H8/38344<br>H8/38345<br>H8/38346<br>H8/38347 |

|----------------|----------------------------------------------------------|----------|-------|----------------------------------------------------------------------|

| H8/3847S Group | H8/3844S<br>H8/3845S<br>H8/3846S<br>H8/3847S             | H8/38447 | Group | H8/38442<br>H8/38443<br>H8/38444<br>H8/38445<br>H8/38446<br>H8/38447 |

Renesas Electronics

www.renesas.com

Rev.6.00 2006.08

- These materials are intended as a reference to assist our customers in the selection of the F Technology Corp. product best suited to the customer's application; they do not convey any under any intellectual property rights, or any other rights, belonging to Renesas Technology a third party.

- Renesas Technology Corp. assumes no responsibility for any damage, or infringement of ar party's rights, originating in the use of any product data, diagrams, charts, programs, algorith circuit application examples contained in these materials.

- circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, progra algorithms represents information on products at the time of publication of these materials, a subject to change by Renesas Technology Corp. without notice due to product improvemen other reasons. It is therefore recommended that customers contact Renesas Technology C

an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss

Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.cc

4. When using any or all of the information contained in these materials, including product data

- diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a system before making a final decision on the applicability of the information and products. F Technology Corp. assumes no responsibility for any damage, liability or other loss resulting information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a casystem that is used under circumstances in which human life is potentially at stake. Please

- system that is used under circumstances in which human life is potentially at stake. Please Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor considering the use of a product contained herein for any specific purposes, such as appara systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce whole or in part these materials

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduct whole or in part these materials.7. If these products or technologies are subject to the Japanese export control restrictions, the be exported under a license from the Japanese government and cannot be imported into a control than the control destination.

- other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/o country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the producentained therein.

€ENESAS

an ideal configuration as a microcomputer for embedding in sophisticated control syst (ZTAT<sup>TM\*1</sup>), Flash memory (F-ZTAT<sup>TM\*2</sup>) and mask ROM are available as on-chip F enabling users to respond quickly and flexibly to changing application specifications a

- Notes: 1. ZTAT is a trademark of Renesas Technology Corp.

- 2. F-ZTAT is a trademark of Renesas Technology Corp.

demands of the transition from initial to full-fledged volume production.

2. F-Z1A1 is a trademark of Renesas Technology Corp

Intended Readership: This manual is intended for users undertaking the design of an a system using the H8/3847R Group, H8/3847S Group, H8/38347 H8/38447 Group. Readers using this manual require a basic kno electrical circuits, logic circuits, and microcomputers.

Purpose: The purpose of this manual is to give users an understanding of functions and electrical characteristics of the H8/3847R Group, Group, H8/38347 Group, and H8/38447 Group. Details of execu instructions can be found in the H8/300L Series Programming N

Using this Manual:

- For an overall understanding of the H8/3847R Group, H8/3847S Group, H8/3834'

H8/38447 Group's functions

Follow the Table of Contents. This manual is broadly divided into sections on the

- control functions, peripheral functions, and electrical characteristics.

For a detailed understanding of CPU functions

- Refer to the separate publication H8/300L Series Programming Manual.

Note on bit notation: Bits are shown in high-to-low order from left to right.

Rev. 6.00 Aug 04, 2006 pa

which should be read in conjunction with the present manual.

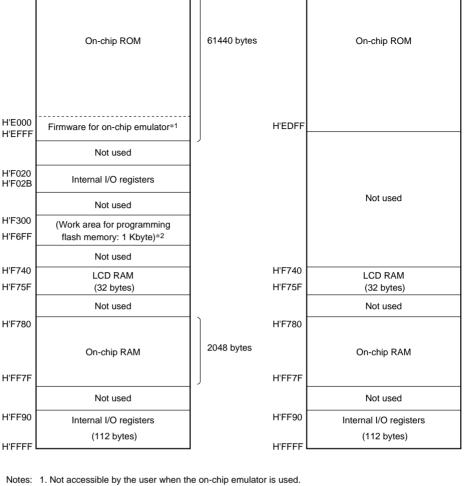

- cannot be accessed by the user. 4. The address area from H'F300 to H'F6FF must not be accessed under any circumstances.

- 5. When the on-chip emulator is used, pin P24 functions as an I/O pin, pins P2

- function as input pins, and pin P27 functions as an output pin. 6. During a break, the watchdog timer continues to operate. Therefore, an inter-

- generated if an overflow occurs during the break.

Related Material: The latest information is available at our Web Site. Please make you have the most up-to-date information available. (http://www.renesas.com/)

| (map.// www.renesus.com/)                                                         |           |  |  |  |  |

|-----------------------------------------------------------------------------------|-----------|--|--|--|--|

| User's Manuals on the H8/3847:                                                    |           |  |  |  |  |

| Manual Title                                                                      | Document  |  |  |  |  |

| H8/3847R Group, H8/3847S Group, H8/38347 Group, H8/38447 Group<br>Hardware Manual | This manu |  |  |  |  |

| H8/300L Series Programming Manual                                                 | REJ09B02  |  |  |  |  |

|                                                                                   |           |  |  |  |  |

User's manuals for development tools:

**Manual Title**

H8S, H8/300 Series Simulator/Debugger User's Manual

High-Performance Embedded Workshop User's Manual

High-Performance Debugging Interface User's Manual

H8S, H8/300 Series High-Performance Embedded Workshop.

C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual

Rev. 6.00 Aug 04, 2006 page iv of xxxvi

Documen

**REJ10B01**

**REJ10B02**

ADE-702-2

ADE-702-2

Rev. 6.00 Aug 04, 2006 pa

RENESAS

Rev. 6.00 Aug 04, 2006 page vi of xxxvi

RENESAS

|                      |     |                                                                                                           | ore, an ir<br>the breal                            | iternal re                                                  | set is ge                    | enerated                         | if an ov                                        | erflov                    |

|----------------------|-----|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|------------------------------|----------------------------------|-------------------------------------------------|---------------------------|

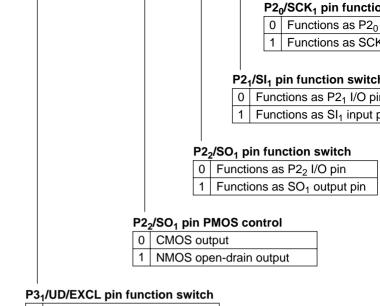

| 1.3.2 Pin Functions  | 33  | Table a                                                                                                   | mended                                             |                                                             |                              |                                  |                                                 |                           |

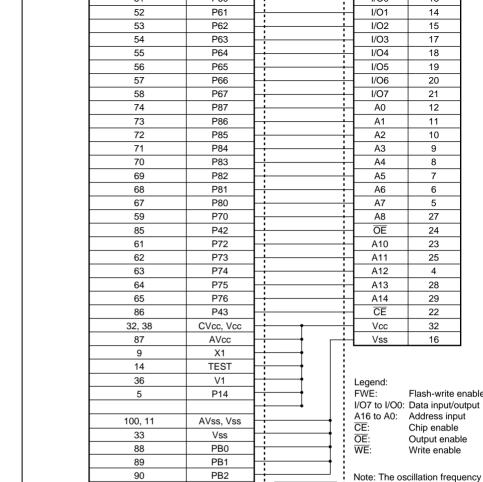

| Table 1.6 Pin        |     |                                                                                                           |                                                    | Pin No.                                                     |                              | <u>—</u>                         |                                                 |                           |

| Tunctions            |     | Type<br>System<br>control                                                                                 | <b>Symbol</b><br>TEST                              | TFP-100B<br>TFP-100G                                        | <b>FP-100A</b><br>17         | I/O<br>Intput                    | Name and<br>Test pin:<br>cannot be<br>connected | This pin<br>used. I       |

| 8.3.1 Overview       | 213 | Descrip                                                                                                   | tion ame                                           | ended                                                       |                              |                                  |                                                 |                           |

|                      |     |                                                                                                           |                                                    | it I/O por                                                  | t. Figure                    | 8.2 sho                          | ws its p                                        | in cor                    |

|                      |     | after the hardwa                                                                                          | e reset is<br>re; it car<br>be consi<br>/. Note th | period. I<br>s cleared<br>not be m<br>dered wh<br>nat the m | . The punanipulation         | II-up MC<br>ted by a<br>ing conr | OS is coluser pro<br>nections                   | ntrolle<br>ogran<br>to ex |

| 8.3.4 Pin States     | 218 | Table a                                                                                                   | ind notes                                          | amende                                                      | ed                           |                                  |                                                 |                           |

| Table 8.7 Port 2 Pin |     | Pins                                                                                                      | Reset                                              | Sleep                                                       | Subsleep                     | Standby                          | Watch                                           | Suba                      |

| States               |     | P2 <sub>7</sub> to P2 <sub>5</sub>                                                                        | High-<br>impedance                                 | Retains<br>previous<br>state                                | Retains<br>previous<br>state | High-<br>impedance               | Retains<br>previous<br>state                    | Functi                    |

|                      |     | P2 <sub>4</sub> *1                                                                                        | Pull-up<br>MOS on                                  | _ olato                                                     | ciaio                        |                                  | olato                                           |                           |

|                      |     | P2 <sub>4</sub> *2<br>P2 <sub>3</sub>                                                                     | High-<br>impedance                                 |                                                             |                              |                                  |                                                 |                           |

|                      |     | P2 <sub>2</sub> /SO <sub>1</sub><br>P2 <sub>1</sub> /SI <sub>1</sub><br>P2 <sub>0</sub> /SCK <sub>1</sub> | High-<br>impedance                                 |                                                             |                              |                                  |                                                 |                           |

|                      |     | Notes: 1.<br>2.                                                                                           | Applies to F                                       | ne F-ZTAT ve<br>18/3847R Gro<br>ne H8/38347                 | oup and H8/3                 | 8847S Group                      | o. Also appli                                   |                           |

Rev. 6.00 Aug 04, 2006 pa

|                                                                                                                                                                                                   |             | Vs                                    | ss with an                | external resistor                                                                                                                                                                 | of approximately 1 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| 15.8.2 DC<br>Characteristics                                                                                                                                                                      | 519,<br>525 | Table and notes amended               |                           |                                                                                                                                                                                   |                    |  |

| Table 15.26 DC                                                                                                                                                                                    |             | Item                                  | Symbol                    | Applicable Pins                                                                                                                                                                   | 1<br>1<br>1        |  |

| Characteristics                                                                                                                                                                                   |             | Pull-up<br>MOS<br>current             | —I <sub>p</sub>           | P1 <sub>0</sub> to P1 <sub>7</sub> ,<br>P2 <sub>4</sub> *6,<br>P3 <sub>0</sub> to P3 <sub>7</sub> ,<br>P5 <sub>0</sub> to P5 <sub>7</sub> ,<br>P6 <sub>0</sub> to P6 <sub>7</sub> |                    |  |

|                                                                                                                                                                                                   |             | Notes:                                |                           |                                                                                                                                                                                   |                    |  |

|                                                                                                                                                                                                   |             | 4. Except                             | current w                 | hich flows to the                                                                                                                                                                 | pull-up MOS or ou  |  |

|                                                                                                                                                                                                   |             | 5. Voltage maintained in standby mode |                           |                                                                                                                                                                                   |                    |  |

|                                                                                                                                                                                                   |             |                                       | s to the F-z<br>ce values |                                                                                                                                                                                   | e specified values |  |

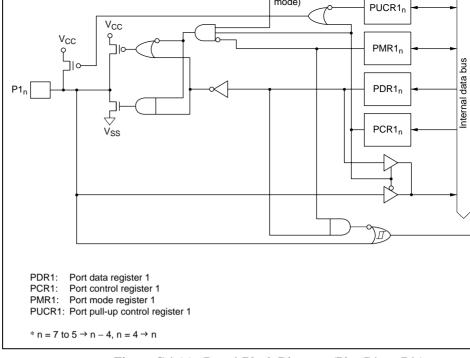

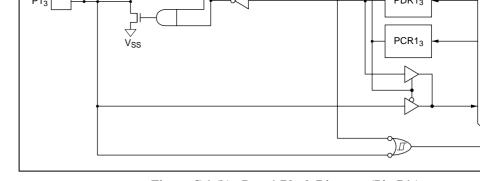

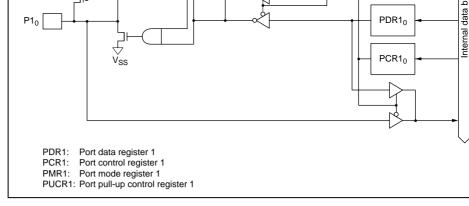

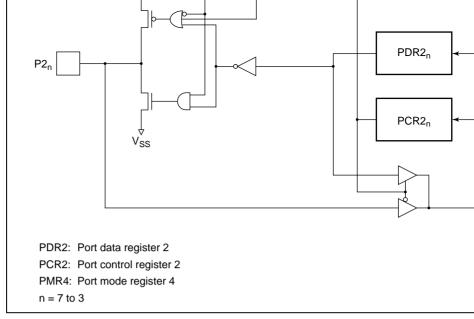

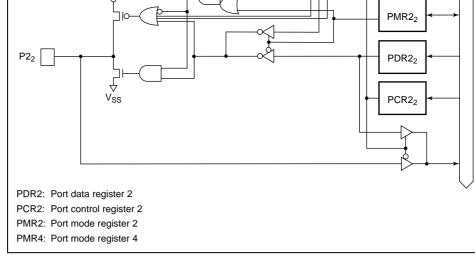

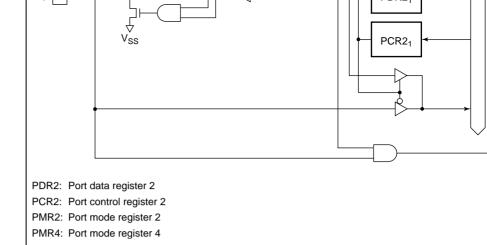

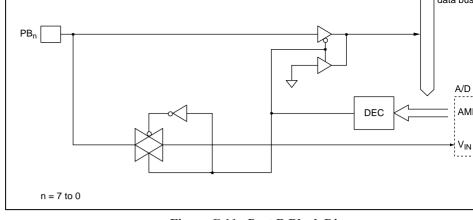

| C.2 Block Diagrams of Port 2                                                                                                                                                                      | 634         | Figure titl                           | e amende                  | d                                                                                                                                                                                 |                    |  |

| Figure C.2 (a-1)<br>Port 2 Block Diagram<br>(Pins P2 <sub>7</sub> to P2 <sub>3</sub> , Not<br>Including P2 <sub>4</sub> in the F-<br>ZTAT Version of the<br>H8/38347 Group and<br>H8/38447 Group) |             |                                       |                           |                                                                                                                                                                                   |                    |  |

Newly added

Rev. 6.00 Aug 04, 2006 page viii of xxxvi

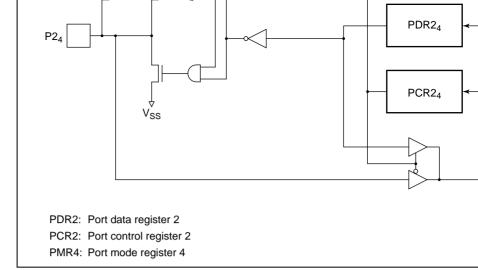

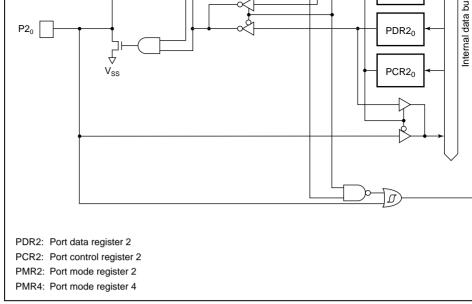

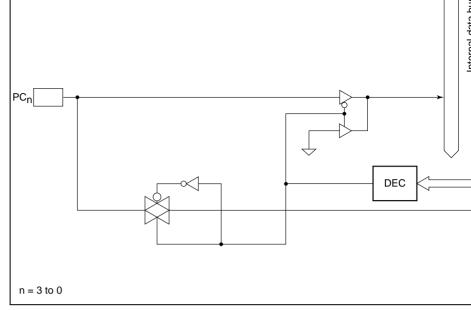

635

Figure C.2 (a-2)

Version of the H8/38347 Group and H8/38447 Group)

Port 2 Block Diagram (Pin P2<sub>4</sub> in the F-ZTAT

3. On-chip pull-up MOS turns on for pin P24 only (F-Z of the H8/38347 Group and H8/38447 Group).

Rev. 6.00 Aug 04, 2006 pa

RENESAS

Rev. 6.00 Aug 04, 2006 page x of xxxvi

RENESAS

|     | 2.2.2   | Control Registers                    |  |  |  |  |  |

|-----|---------|--------------------------------------|--|--|--|--|--|

|     | 2.2.3   | Initial Register Values              |  |  |  |  |  |

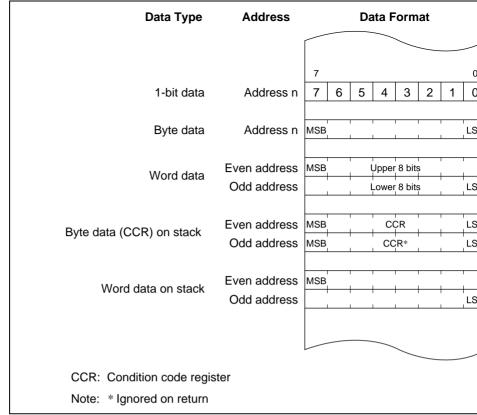

| 2.3 | Data F  | Data Formats                         |  |  |  |  |  |

|     | 2.3.1   | Data Formats in General Registers    |  |  |  |  |  |

|     | 2.3.2   | Memory Data Formats                  |  |  |  |  |  |

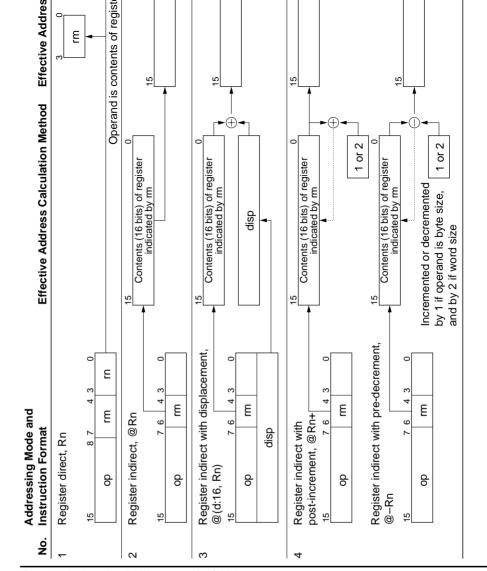

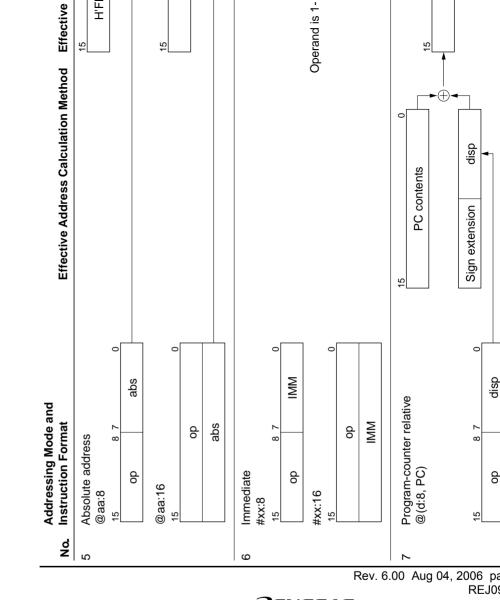

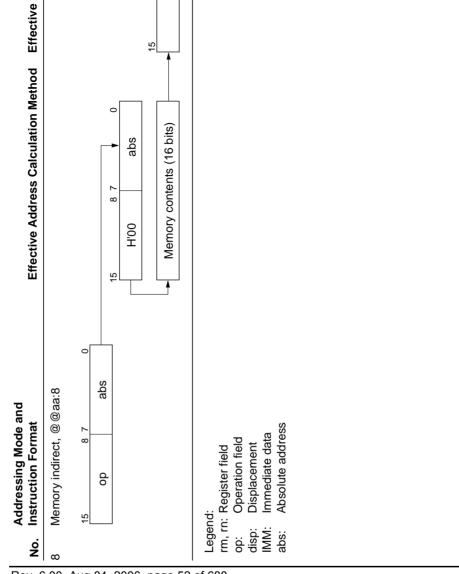

| 2.4 | Addres  | ssing Modes                          |  |  |  |  |  |

|     | 2.4.1   | Addressing Modes                     |  |  |  |  |  |

|     | 2.4.2   | Effective Address Calculation        |  |  |  |  |  |

| 2.5 | Instruc | tion Set                             |  |  |  |  |  |

|     | 2.5.1   | Data Transfer Instructions           |  |  |  |  |  |

|     | 2.5.2   | Arithmetic Operations                |  |  |  |  |  |

|     | 2.5.3   | Logic Operations                     |  |  |  |  |  |

|     | 2.5.4   | Shift Operations                     |  |  |  |  |  |

|     | 2.5.5   | Bit Manipulations                    |  |  |  |  |  |

|     | 2.5.6   | Branching Instructions               |  |  |  |  |  |

|     | 2.5.7   | System Control Instructions          |  |  |  |  |  |

|     | 2.5.8   | Block Data Transfer Instruction      |  |  |  |  |  |

| 2.6 | Basic ( | Operational Timing                   |  |  |  |  |  |

|     | 2.6.1   | Access to On-Chip Memory (RAM, ROM)  |  |  |  |  |  |

|     | 2.6.2   | Access to On-Chip Peripheral Modules |  |  |  |  |  |

| 2.7 | CPU S   | tates                                |  |  |  |  |  |

Pin Functions

Features

Address Space

Register Configuration

General Registers

Section 2 CPU

Overview.....

Register Descriptions

2.1

2.2

2.7.1

2.7.2

2.1.2

2.1.3

2.2.1

Overview..... Program Execution State

Rev. 6.00 Aug 04, 2006 pa

| Se  | ction 3 | Exception Handling                |  |  |  |  |  |

|-----|---------|-----------------------------------|--|--|--|--|--|

| 3.1 | Overv   | Overview                          |  |  |  |  |  |

| 3.2 | Reset   | Reset                             |  |  |  |  |  |

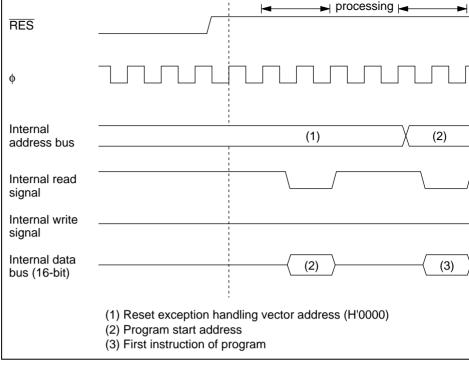

|     |         | Overview                          |  |  |  |  |  |

|     | 3.2.2   | Reset Sequence                    |  |  |  |  |  |

|     | 3.2.3   | Interrupt Immediately after Reset |  |  |  |  |  |

| 3.3 | Interr  | upts                              |  |  |  |  |  |

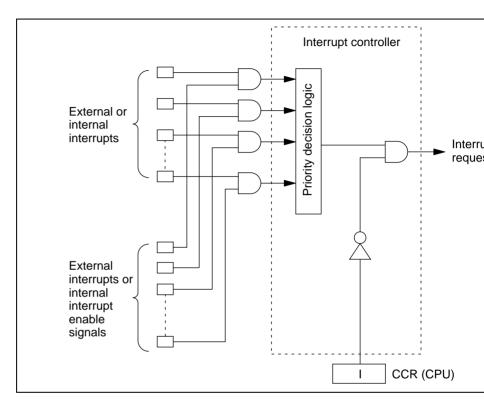

|     | 3.3.1   | Overview                          |  |  |  |  |  |

|     | 3.3.2   | Interrupt Control Registers       |  |  |  |  |  |

|     | 3.3.3   | External Interrupts               |  |  |  |  |  |

|     | 3.3.4   | Internal Interrupts               |  |  |  |  |  |

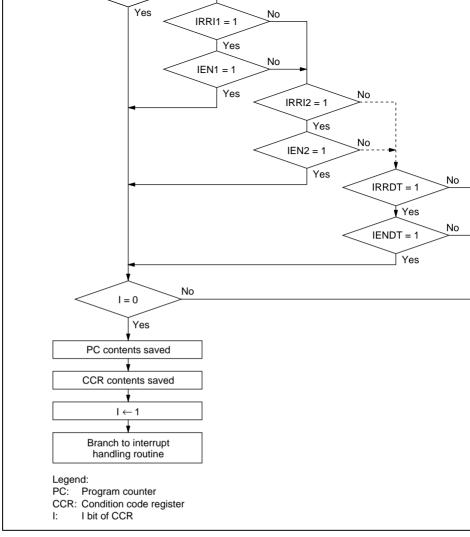

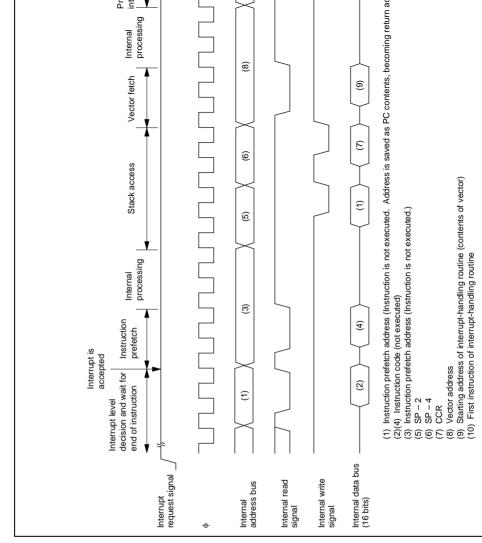

|     | 3.3.5   | Interrupt Operations              |  |  |  |  |  |

|     | 3.3.6   | Interrupt Response Time           |  |  |  |  |  |

| 3.4 | Appli   | cation Notes                      |  |  |  |  |  |

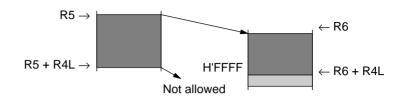

|     |         | Notes on Stack Area Use           |  |  |  |  |  |

3.4.2 Notes on Rewriting Port Mode Registers.3.4.3 Method for Clearing Interrupt Request Flags

4.1.1 Block Diagram

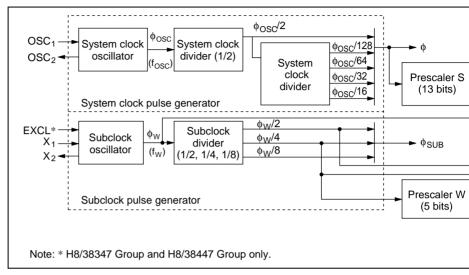

4.1.2 System Clock and Subclock

4.2 System Clock Generator

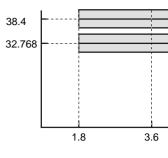

4.3 Subclock Generator

4.3 Subclock Generator4.4 Prescalers4.5 Note on Oscillators

Rev. 6.00 Aug 04, 2006 page xii of xxxvi

RENESAS

Element)....

| 5.4 | water   | i Mode                                                                |

|-----|---------|-----------------------------------------------------------------------|

|     | 5.4.1   | Transition to Watch Mode                                              |

|     | 5.4.2   | Clearing Watch Mode                                                   |

|     | 5.4.3   | Oscillator Settling Time after Watch Mode is Cleared                  |

|     | 5.4.4   | Notes on External Input Signal Changes before/after Watch Mode        |

| 5.5 | Subsle  | eep Mode                                                              |

|     | 5.5.1   | Transition to Subsleep Mode                                           |

|     | 5.5.2   | Clearing Subsleep Mode                                                |

| 5.6 | Subac   | tive Mode                                                             |

|     | 5.6.1   | Transition to Subactive Mode                                          |

|     | 5.6.2   | Clearing Subactive Mode                                               |

|     | 5.6.3   | Operating Frequency in Subactive Mode                                 |

| 5.7 | Active  | e (Medium-Speed) Mode                                                 |

|     | 5.7.1   | Transition to Active (Medium-Speed) Mode                              |

|     | 5.7.2   | Clearing Active (Medium-Speed) Mode                                   |

|     | 5.7.3   | Operating Frequency in Active (Medium-Speed) Mode                     |

| 5.8 | Direct  | Transfer                                                              |

|     | 5.8.1   | Overview of Direct Transfer                                           |

|     | 5.8.2   | Direct Transition Times                                               |

|     | 5.8.3   | Notes on External Input Signal Changes before/after Direct Transition |

| 5.9 |         | le Standby Mode                                                       |

|     | 5.9.1   | Setting Module Standby Mode                                           |

|     | 5.9.2   | Clearing Module Standby Mode                                          |

|     | 5.9.3   | Usage Note                                                            |

| Sec | ction 6 | ROM                                                                   |

| 6.1 |         | iew                                                                   |

|     |         | Rev. 6.00 Aug 04, 2006 pa                                             |

|     |         | 110v. 0.00 Aug 04, 2000 pa                                            |

|     |         | RENESAS                                                               |

|     |         |                                                                       |

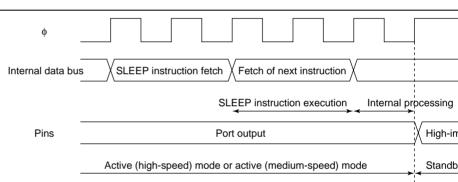

Transition to Standby Mode.....

Clearing Standby Mode .....

Notes on External Input Signal Changes before/after Standby Mode.....

3.3.1

5.3.2

5.3.3

5.3.4 5.3.5

|      | 6.7.2                                | Programming/Erasing in User Program Mode                 |  |

|------|--------------------------------------|----------------------------------------------------------|--|

| 6.8  | 6.8 Flash Memory Programming/Erasing |                                                          |  |

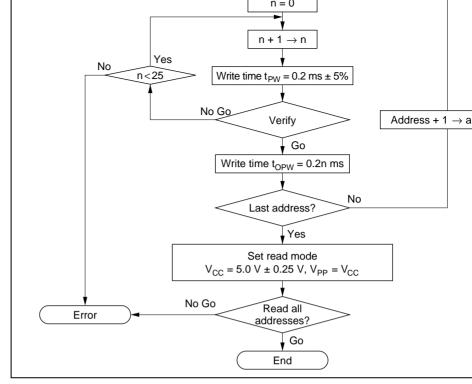

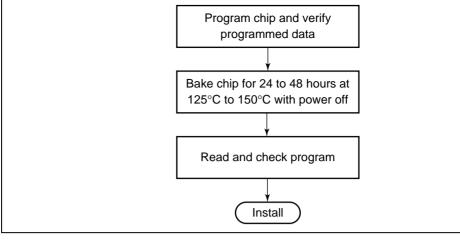

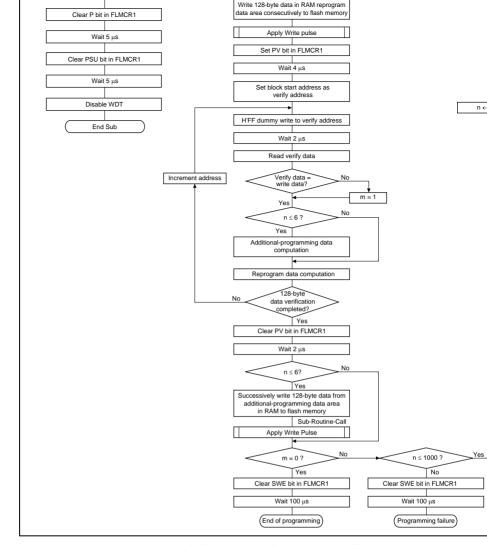

|      | 6.8.1                                | Program/Program-Verify                                   |  |

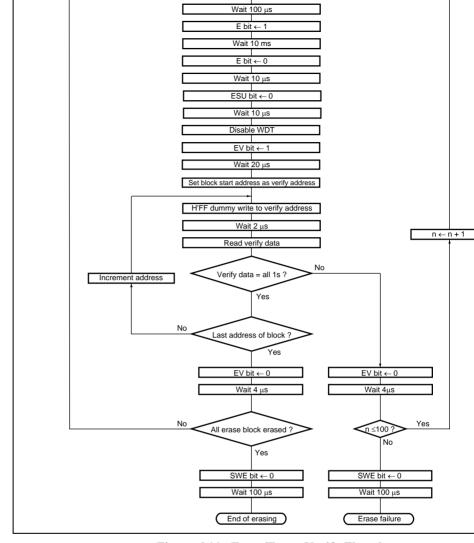

|      | 6.8.2                                | Erase/Erase-Verify                                       |  |

|      | 6.8.3                                | Interrupt Handling when Programming/Erasing Flash Memory |  |

| 6.9  | Prograi                              | m/Erase Protection                                       |  |

|      | 6.9.1                                | Hardware Protection                                      |  |

|      | 6.9.2                                | Software Protection                                      |  |

|      | 6.9.3                                | Error Protection                                         |  |

| 6.10 | Prograi                              | mmer Mode                                                |  |

|      | 6.10.1                               | Socket Adapter                                           |  |

|      | 6.10.2                               | Programmer Mode Commands                                 |  |

|      | 6.10.3                               | Memory Read Mode                                         |  |

|      | 6.10.4                               | Auto-Program Mode                                        |  |

|      | 6.10.5                               | Auto-Erase Mode                                          |  |

|      | 6.10.6                               | Status Read Mode                                         |  |

|      | 6.10.7                               | Status Polling                                           |  |

|      | 6.10.8                               | Programmer Mode Transition Time                          |  |

|      | 6.10.9                               | Notes on Memory Programming                              |  |

|      |                                      |                                                          |  |

| Rev. | 6.00 Au                              | g 04, 2006 page xiv of xxxvi                             |  |

|      |                                      | •                                                        |  |

|      |                                      | RENESAS                                                  |  |

Features

Block Diagram

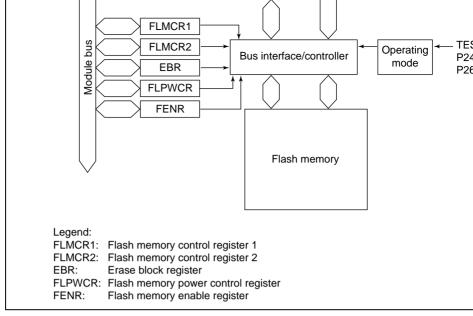

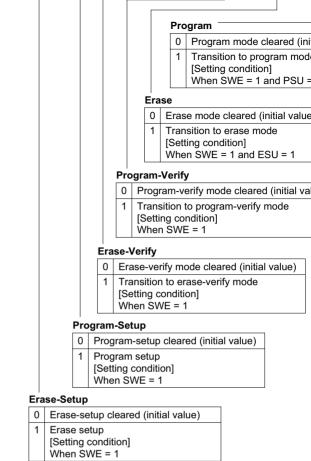

Flash Memory Control Register 1 (FLMCR1)....

Flash Memory Control Register 2 (FLMCR2).....

Flash Memory Enable Register (FENR)

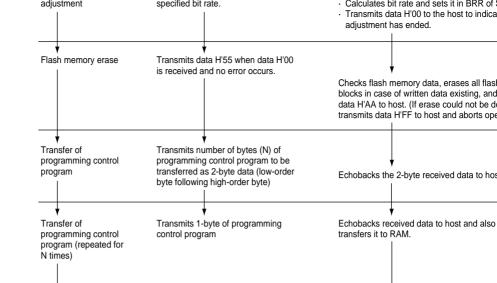

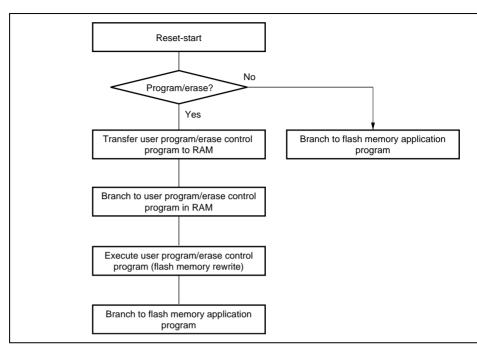

Boot Mode .....

Descriptions of Registers of the Flash Memory....

On-Board Programming Modes

6.5.1

6.5.2

6.5.3

6.5.4

6.6.1

6.6.2

6.6.3

6.6.4

6.6.5

6.7.1

6.6

6.7

| 8.2.5               | MOS Input Pull-Up                      |

|---------------------|----------------------------------------|

| 8.3 Port 2          |                                        |

| 8.3.1               | Overview                               |

| 8.3.2               | Register Configuration and Description |

| 8.3.3               | Pin Function                           |

| 8.3.4               | Pin States                             |

| *****               | 3                                      |

| 8.4.1               | Overview                               |

| 8.4.2               | Register Configuration and Description |

| 8.4.3               | Pin Functions                          |

| 8.4.4               | Pin States                             |

| 8.4.5               | MOS Input Pull-Up                      |

|                     | l                                      |

| 8.5.1               | Overview                               |

| 8.5.2               | Register Configuration and Description |

| 8.5.3               | Pin Functions                          |

| 8.5.4               | Pin States                             |

| *****               | 5                                      |

| 8.6.1               | Overview                               |

| 8.6.2               | Register Configuration and Description |

| 8.6.3               | Pin Functions                          |

| 8.6.4<br>8.6.4      | Pin States                             |

| 8.6.5               | MOS Input Pull-Up                      |

|                     | MOS Input Pull-Op                      |

| 8.7 Port 6<br>8.7.1 |                                        |

|                     | Overview                               |

| 8.7.2               | Register Configuration and Description |

| 8.7.3               | Pin Functions                          |

|                     |                                        |

|                     | Rev. 6.00 Aug 04, 2006 pag             |

|                     | RENESAS                                |

|                     | I/CINC3/72                             |

8.2.1

8.2.2 8.2.3

8.2.4

Pin Functions

Pin States.

|      | 8.10.2 Register Configuration and Description               |

|------|-------------------------------------------------------------|

|      | 8.10.3 Pin Functions                                        |

|      | 8.10.4 Pin States                                           |

| 8.11 | Port A                                                      |

|      | 8.11.1 Overview                                             |

|      | 8.11.2 Register Configuration and Description               |

|      | 8.11.3 Pin Functions                                        |

|      | 8.11.4 Pin States                                           |

| 8.12 | Port B                                                      |

|      | 8.12.1 Overview                                             |

|      | 8.12.2 Register Configuration and Description               |

| 8.13 |                                                             |

|      | 8.13.1 Overview                                             |

|      | 8.13.2 Register Configuration and Description               |

| 8.14 |                                                             |

|      | 8.14.1 Overview                                             |

|      | 8.14.2 Register Configuration and Descriptions              |

|      | 8.14.3 Note on Modification of Serial Port Control Register |

| 8.15 | _                                                           |

|      | 8.15.1 The Management of the Un-Use Terminal                |

|      | •                                                           |

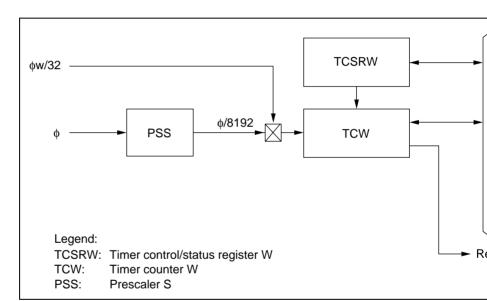

| Sec  | tion 9 Timers                                               |

| 9.1  | Overview                                                    |

| 9.2  | Timer A                                                     |

|      | 9.2.1 Overview                                              |

|      | 9.2.2 Register Descriptions                                 |

|      | -6                                                          |

Rev. 6.00 Aug 04, 2006 page xvi of xxxvi

8.9.2

8.9.3

8.9.4

RENESAS

Register Configuration and Description.

.....

.....

.....

.....

.....

.....

.....

|    | , , , , , | - T F                                      |

|----|-----------|--------------------------------------------|

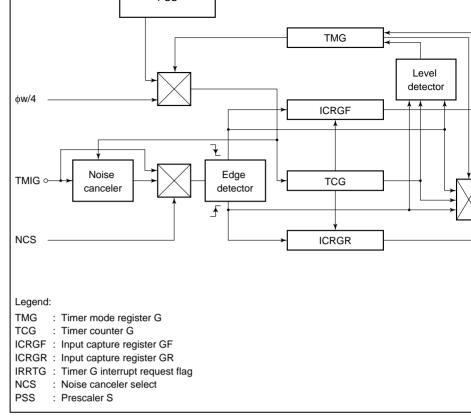

| 9. | .5 Timer  | G                                          |

|    | 9.5.1     | Overview                                   |

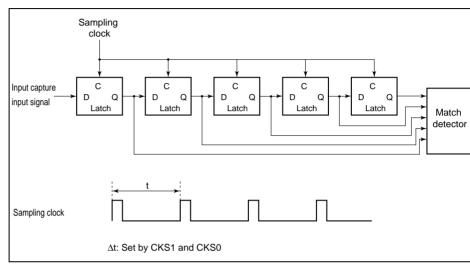

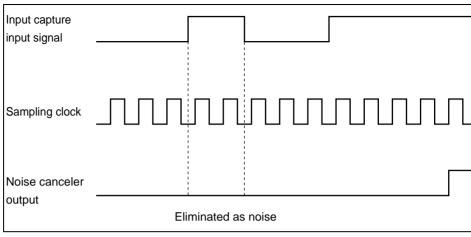

|    | 9.5.2     | Register Descriptions                      |

|    | 9.5.3     | Noise Canceler                             |

|    | 9.5.4     | Operation                                  |

|    | 9.5.5     | Application Notes                          |

|    | 9.5.6     | Timer G Application Example                |

| 9. | .6 Watch  | dog Timer                                  |

|    | 9.6.1     | Overview                                   |

|    | 9.6.2     | Register Descriptions                      |

|    | 9.6.3     | Timer Operation                            |

|    | 9.6.4     | Watchdog Timer Operation States            |

| 9. | .7 Async  | hronous Event Counter (AEC)                |

|    | 9.7.1     | Overview                                   |

|    | 9.7.2     | Register Descriptions                      |

|    | 9.7.3     | Operation                                  |

|    | 9.7.4     | Asynchronous Event Counter Operation Modes |

|    | 9.7.5     | Application Notes                          |

| S  | ection 10 | Serial Communication Interface             |

|    |           | iew                                        |

| 10 |           |                                            |

|    |           | Overview                                   |

|    |           | Register Descriptions                      |

|    |           | Operation                                  |

|    |           | - r                                        |

|    |           | Rev. 6.00 Aug 04, 2006 pag                 |

|    |           |                                            |

|    |           | RENESAS                                    |

9.4

9.4.1 9.4.2

9.4.3

9.4.4

945

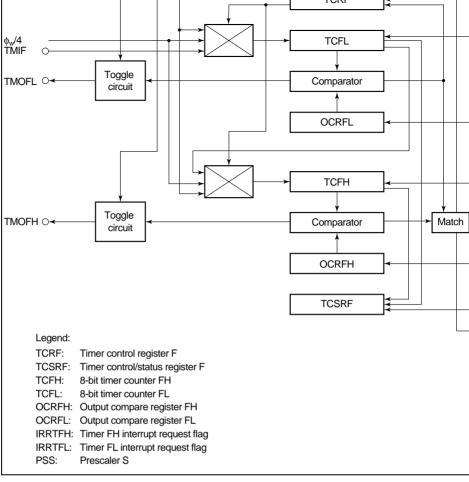

Timer F.

Overview.....

Register Descriptions

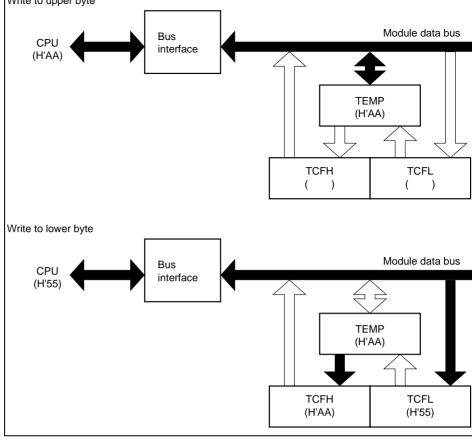

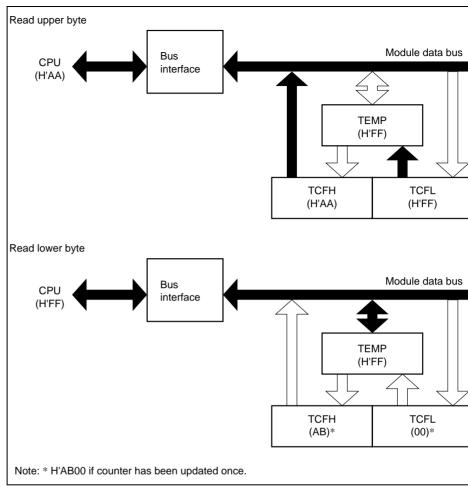

CPU Interface

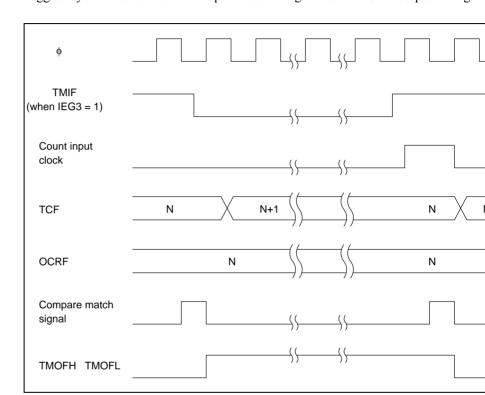

Operation .....

Application Notes

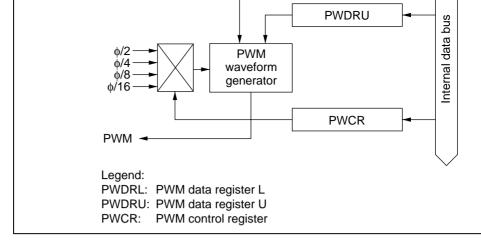

| Sect | ion 11 | 14-Bit PWM                                |

|------|--------|-------------------------------------------|

| 11.1 |        | ew                                        |

|      | 11.1.1 | Features                                  |

|      | 11.1.2 | Block Diagram                             |

|      |        | Pin Configuration                         |

|      |        | Register Configuration                    |

| 11.2 |        | er Descriptions                           |

|      |        | PWM Control Register (PWCR)               |

|      |        | PWM Data Registers U and L (PWDRU, PWDRL) |

|      |        | Clock Stop Register 2 (CKSTPR2)           |

| 11.3 |        | ion                                       |

|      |        | Operation                                 |

|      |        | PWM Operation Modes                       |

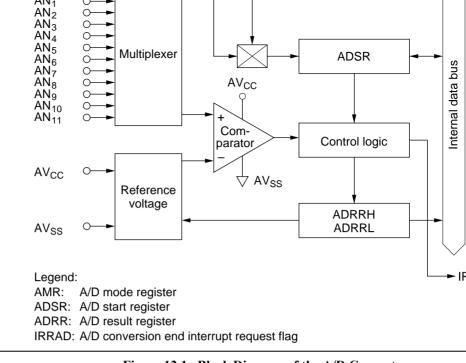

| Sect | ion 12 | A/D Converter                             |

|      |        | ew                                        |

| 12.1 |        | Features                                  |

|      |        | Block Diagram                             |

|      |        | Pin Configuration                         |

|      |        | Register Configuration                    |

| 12.2 |        | er Descriptions                           |

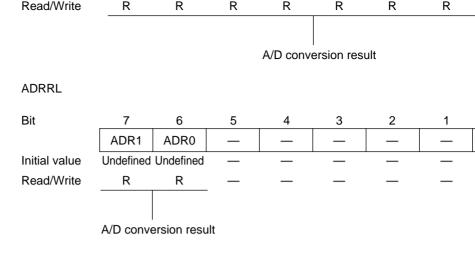

| 14.4 | _      | A/D Result Registers (ADRRH, ADRRL)       |

|      | 12.2.1 | TVD Result Registers (ADRECT, ADRECT)     |

10.5.5 Application Notes .....

Rev. 6.00 Aug 04, 2006 page xviii of xxxvi

12.3

12.4

RENESAS

12.2.2 A/D Mode Register (AMR)12.2.3 A/D Start Register (ADSR)12.2.4 Clock Stop Register 1 (CKSTPR1)

Interrupts .....

|      | 13.2.3 LCD Control Register 2 (LCR2)                             |

|------|------------------------------------------------------------------|

|      | 13.2.4 Clock Stop Register 2 (CKSTPR2)                           |

| 13.3 |                                                                  |

|      | 13.3.1 Settings up to LCD Display                                |

|      | 13.3.2 Relationship between LCD RAM and Display                  |

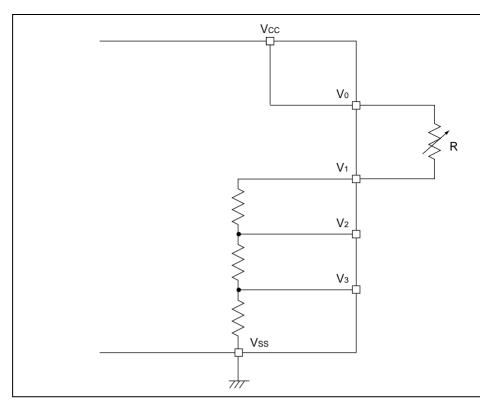

|      | 13.3.3 Luminance Adjustment Function (V <sub>0</sub> Pin)        |

|      | 13.3.4 Low-Power-Consumption LCD Drive System                    |

|      | 13.3.5 Operation in Power-Down Modes                             |

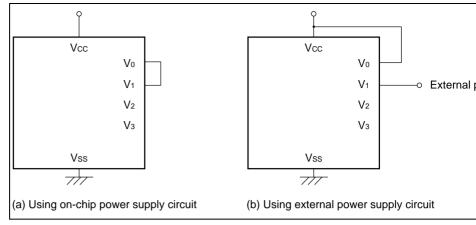

|      | 13.3.6 Boosting the LCD Drive Power Supply                       |

|      | 13.3.7 Connection to HD66100                                     |

|      |                                                                  |

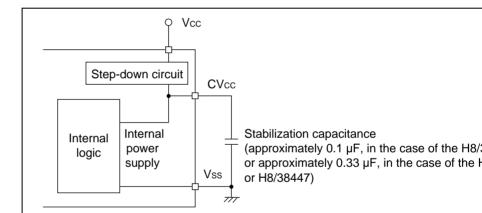

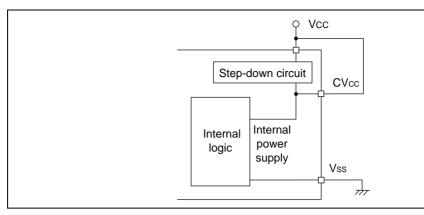

| Sect | ion 14 Power Supply Circuit                                      |

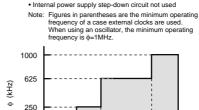

| 14.1 | Overview                                                         |

| 14.2 | When Using Internal Power Supply Step-Down Circuit               |

| 14.3 | When Not Using Internal Power Supply Step-Down Circuit           |

| 14.4 | H8/3847S Group                                                   |

| 14.5 | Notes on Switching from the H8/3847R to the H8/38347 or H8/38447 |

|      |                                                                  |

| Sect | ion 15 Electrical Characteristics                                |

| 15.1 | H8/3847R Group Absolute Maximum Ratings (Regular Specifications) |

| 15.2 | H8/3847R Electrical Characteristics (Regular Specifications)     |

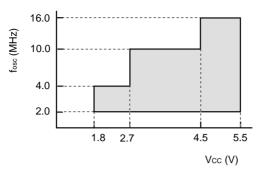

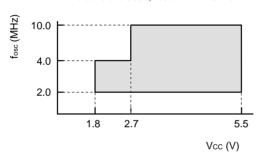

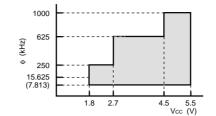

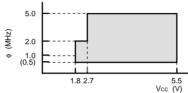

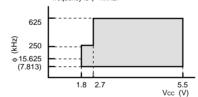

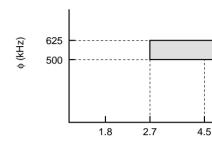

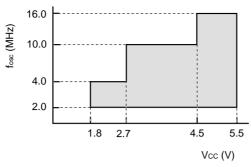

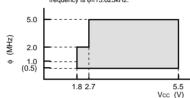

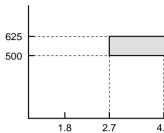

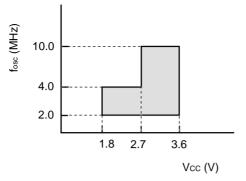

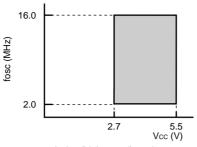

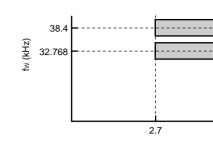

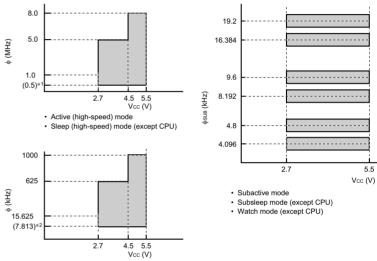

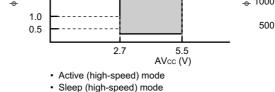

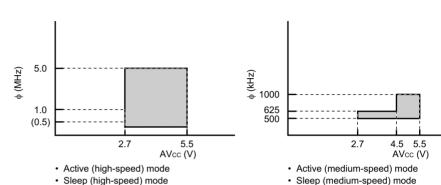

|      | 15.2.1 Power Supply Voltage and Operating Range                  |

|      | 15.2.2 DC Characteristics                                        |

|      | 15.2.3 AC Characteristics                                        |

|      | 15.2.4 A/D Converter Characteristics                             |

|      |                                                                  |

|      | Rev. 6.00 Aug 04, 2006 pa                                        |

|      |                                                                  |

RENESAS

13.1.1 Features

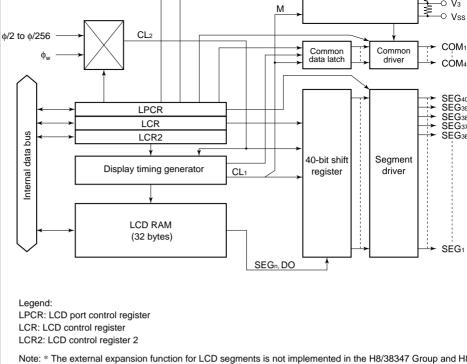

13.1.2 Block Diagram

13.1.3 Pin Configuration

13.1.4 Register Configuration

13.2 Register Descriptions

13.2.1 LCD Port Control Register (LPCR)

13.2.2 LCD Control Register (LCR)

|   | 15.6.1 Power Supply Voltage and Operating Range                     |

|---|---------------------------------------------------------------------|

|   | 15.6.2 DC Characteristics                                           |

|   | 15.6.3 AC Characteristics                                           |

|   | 15.6.4 A/D Converter Characteristics                                |

|   | 15.6.5 LCD Characteristics                                          |

| 1 | 5.7 Absolute Maximum Ratings of H8/38347 Group and H8/38447 Group   |

| 1 | 5.8 Electrical Characteristics of H8/38347 Group and H8/38447 Group |

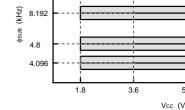

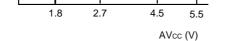

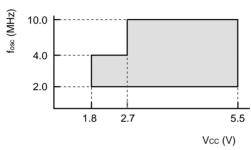

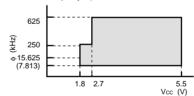

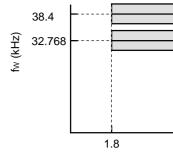

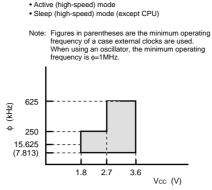

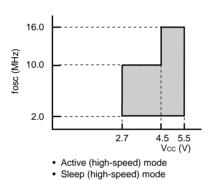

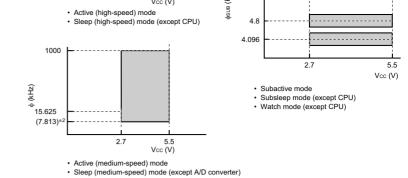

|   | 15.8.1 Power Supply Voltage and Operating Ranges                    |

|   | 15.8.2 DC Characteristics                                           |

|   | 15.8.3 AC Characteristics                                           |

|   | 15.8.4 A/D Converter Characteristics                                |

|   | 15.8.5 LCD Characteristics                                          |

|   | 15.8.6 Flash Memory Characteristics                                 |

| 1 | 5.9 Operation Timing                                                |

|   | 5.10 Output Load Circuit                                            |

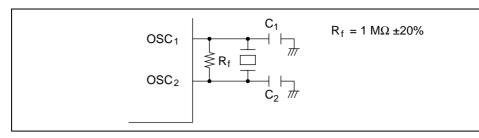

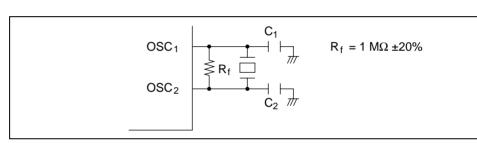

|   | 5.11 Resonator                                                      |

|   | 5.12 Usage Note                                                     |

|   |                                                                     |

| A | Appendix A CPU Instruction Set                                      |

|   | 11 Instructions                                                     |

| A | A.2 Operation Code Map                                              |

| A | A.3 Number of Execution States                                      |

|   |                                                                     |

| A | Appendix B Internal I/O Registers                                   |

|   | 3.1 Addresses                                                       |

15.6 H8/3847S Group Electrical Characteristics

Rev. 6.00 Aug 04, 2006 page xx of xxxvi

B.2

C.1

C.2

Functions

Appendix C I/O Port Block Diagrams.....

| Appendix D | Port States in the Different Processing States |

|------------|------------------------------------------------|

| Appendix E | List of Product Codes                          |

| Appendix F | Package Dimensions                             |

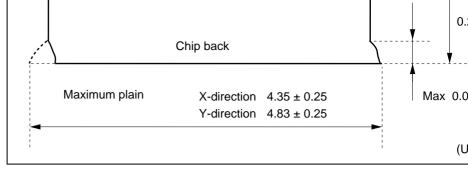

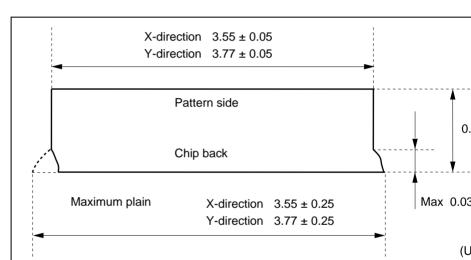

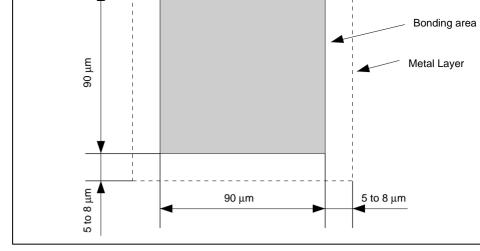

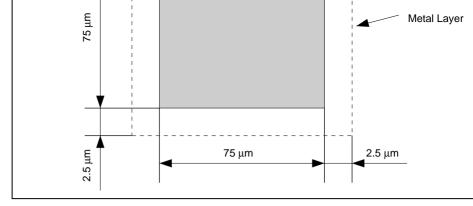

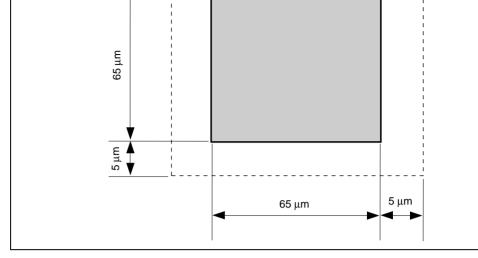

| Appendix G | Specifications of Chip Form                    |

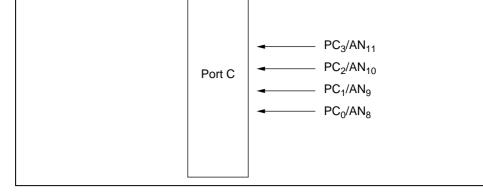

C.12 Block Diagram of Port C

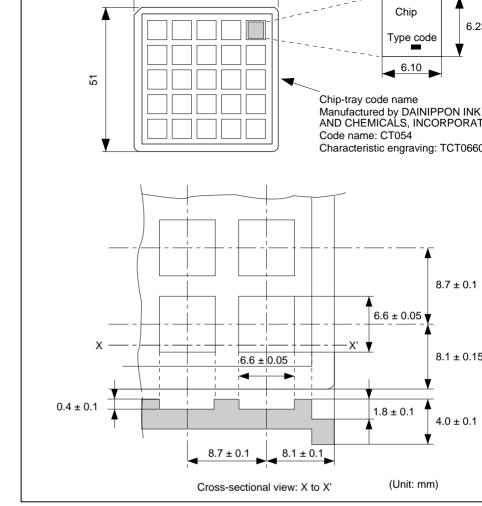

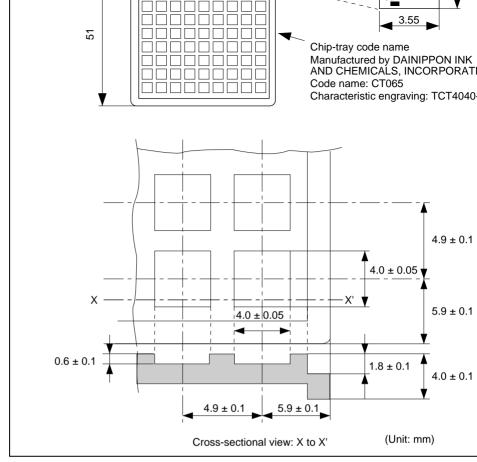

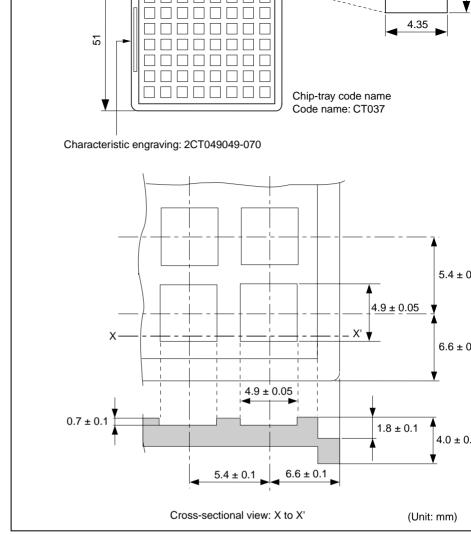

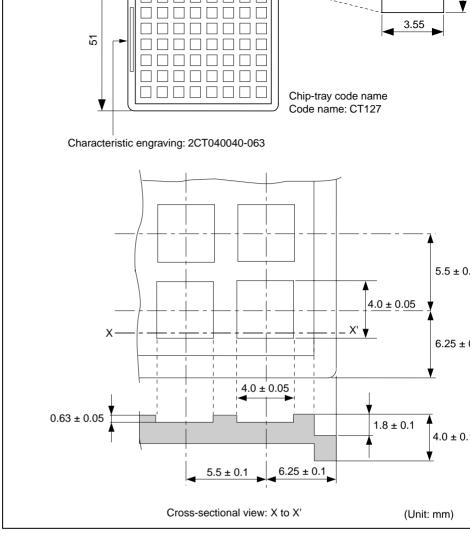

Appendix I Specifications of Chip Tray

Appe

Rev. 6.00 Aug 04, 2006 pag

RENESAS

|              | (10p view)                                                    |

|--------------|---------------------------------------------------------------|

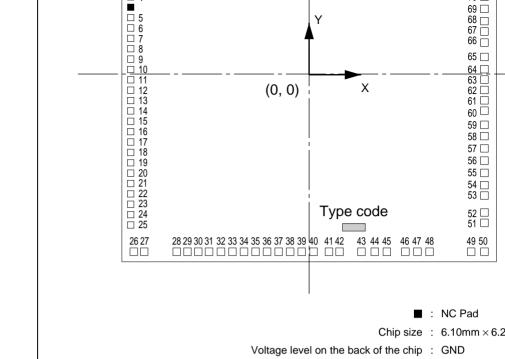

| Figure 1.6   | Bonding Pad Location Diagram of HCD64F38347 and HCD64F38447   |

|              | (Top View)                                                    |

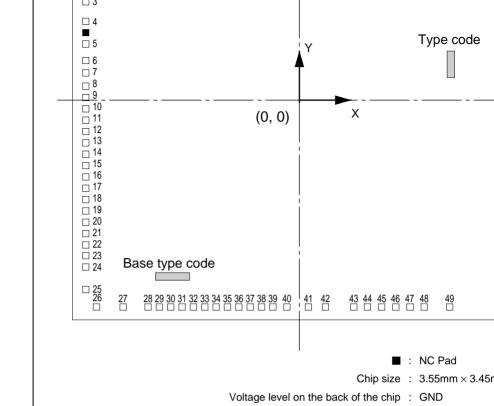

| Figure 1.7   | Bonding Pad Location Diagram of H8/38347 Group (Mask ROM Vers |

|              | and H8/38447 Group (Mask ROM Version) (Top View)              |

| Section 2 Cl | PU                                                            |

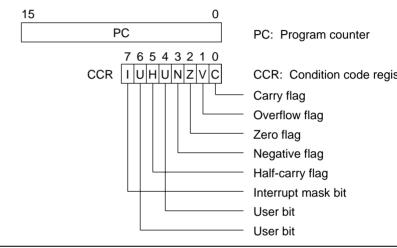

| Figure 2.1   | CPU Registers                                                 |

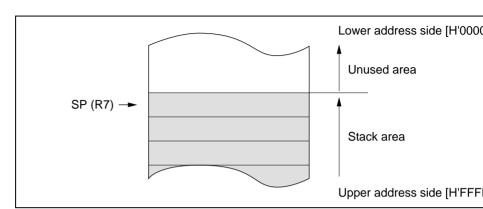

| Figure 2.2   | Stack Pointer                                                 |

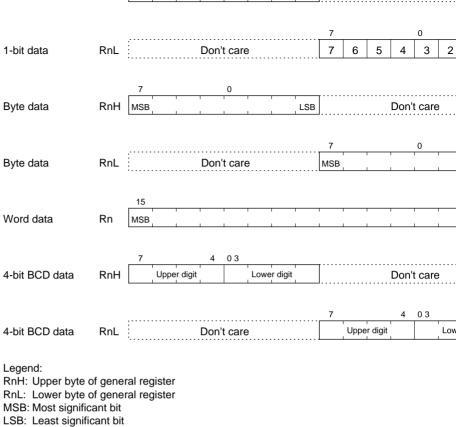

| Figure 2.3   | Register Data Formats                                         |

| Figure 2.4   | Memory Data Formats                                           |

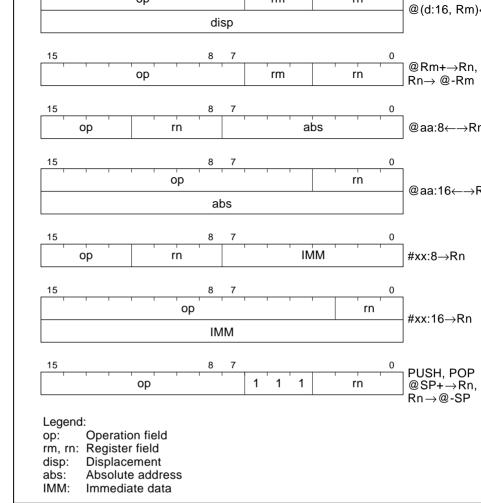

| Figure 2.5   | Data Transfer Instruction Codes                               |

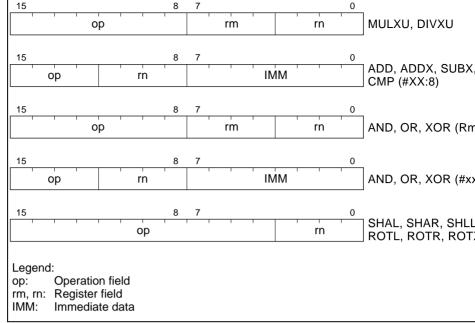

| Figure 2.6   | Arithmetic, Logic, and Shift Instruction Codes                |

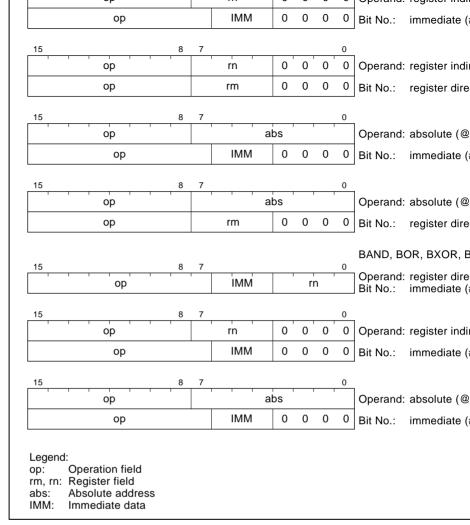

| Figure 2.7   | Bit Manipulation Instruction Codes                            |

| Figure 2.8   | Branching Instruction Codes                                   |

| Figure 2.9   | System Control Instruction Codes                              |

| Figure 2.10  | Block Data Transfer Instruction Code                          |

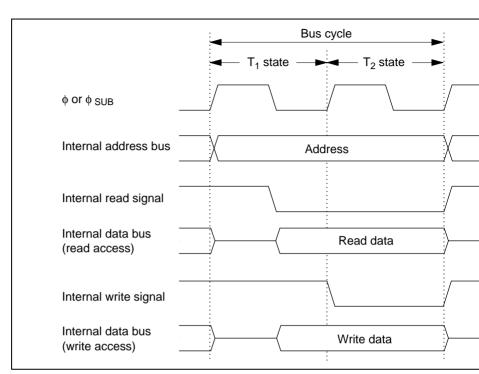

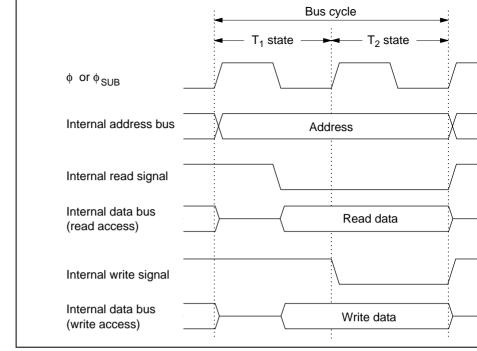

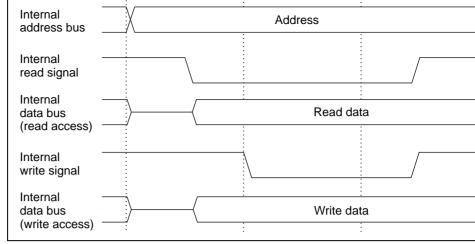

| Figure 2.11  | On-Chip Memory Access Cycle                                   |

|              |                                                               |

Bonding Pad Location Diagram of H8/3847R Group (Mask ROM Ver

(Top View)

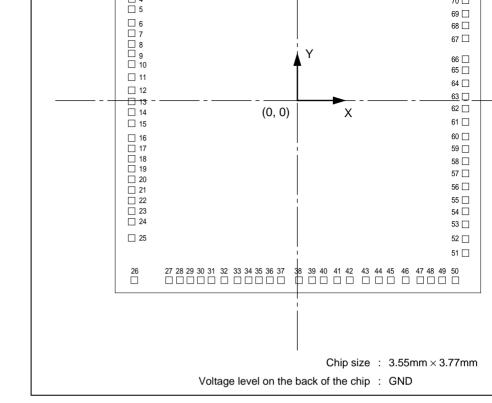

Bonding Pad Location Diagram of H8/3847S Group (Mask ROM Vers (Top View) .....

Rev. 6.00 Aug 04, 2006 page xxii of xxxvi

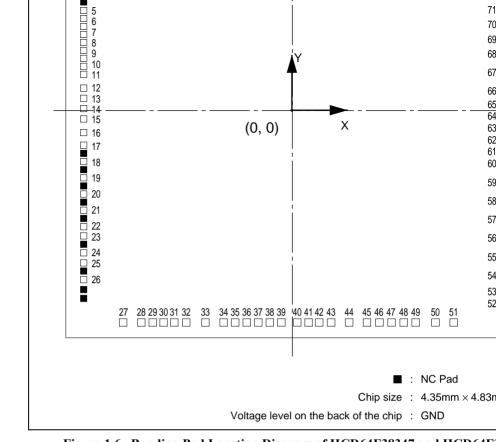

Figure 1.4

Figure 1.5

Figure 2.12

Figure 2.13

Figure 2.14 Figure 2.15

On-Chip Peripheral Module Access Cycle (2-State Access).....

On-Chip Peripheral Module Access Cycle (3-State Access).....

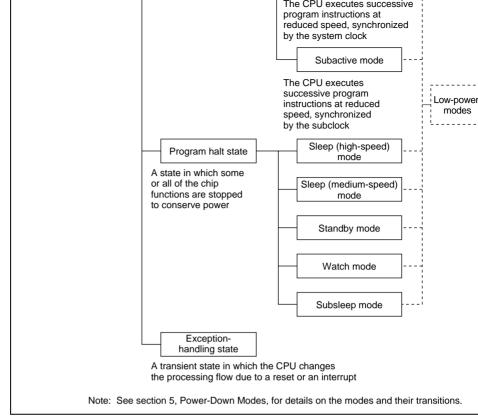

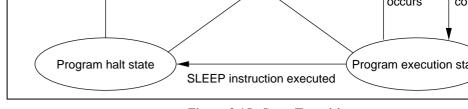

CPU Operation States

State Transitions

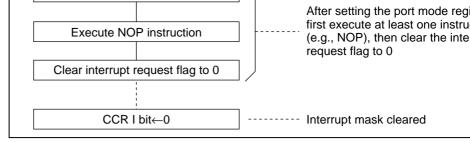

| Figure 3.7     | Port Mode Register Setting and Interrupt Request Flag Clearing Proc |

|----------------|---------------------------------------------------------------------|

| Section 4 Clo  | ock Pulse Generators                                                |

| Figure 4.1     | Block Diagram of Clock Pulse Generators                             |

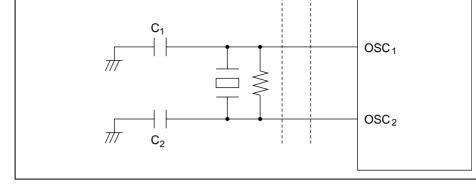

| Figure 4.2     | Typical Connection to Crystal Oscillator                            |

| Figure 4.3     | Typical Connection to Ceramic Oscillator                            |

| Figure 4.4     | Board Design of Oscillator Circuit                                  |

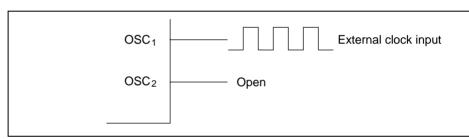

| Figure 4.5     | External Clock Input (Example)                                      |

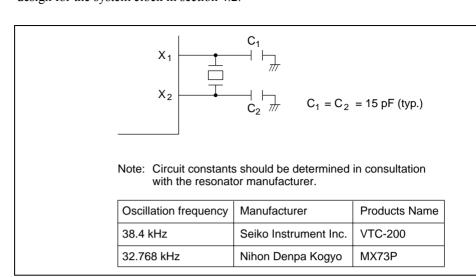

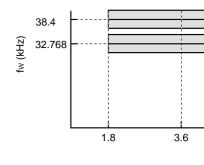

| Figure 4.6     | Typical Connection to 32.768 kHz/38.4 kHz Crystal Oscillator (Subc  |

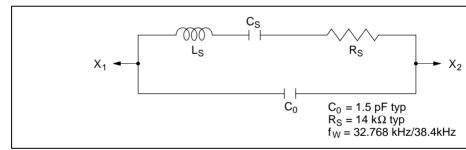

| Figure 4.7     | Equivalent Circuit of 32.768 kHz/38.4 kHz Crystal Oscillator        |

| Figure 4.8     | Pin Connection when not Using Subclock                              |

| Figure 4.9 (a) | Pin Connection when Inputting External Clock                        |

|                | (H8/38347R Group and H8/3847S Group)                                |

| Figure 4.9 (b) | Pin Connection when Inputting External Clock                        |

|                | (H8/38347 Group and H8/38447 Group)                                 |

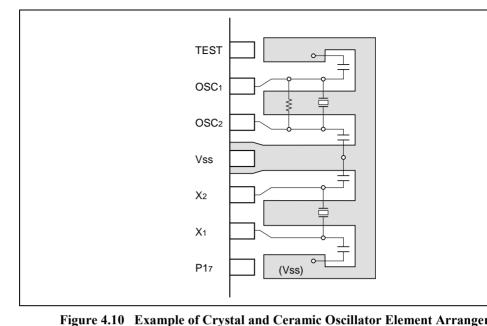

| Figure 4.10    | Example of Crystal and Ceramic Oscillator Element Arrangement       |

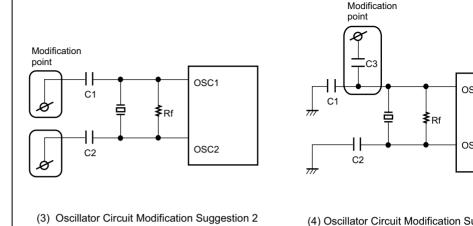

| Figure 4.11    | Negative Resistance Measurement and Circuit Modification Suggesti   |

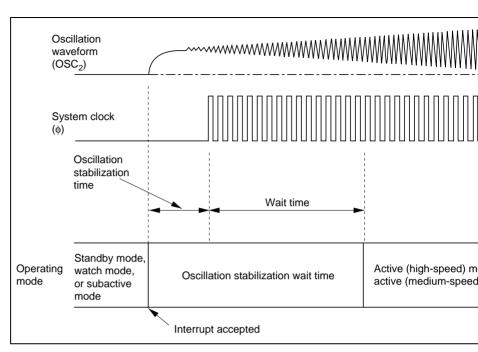

| Figure 4.12    | Oscillation Stabilization Wait Time                                 |

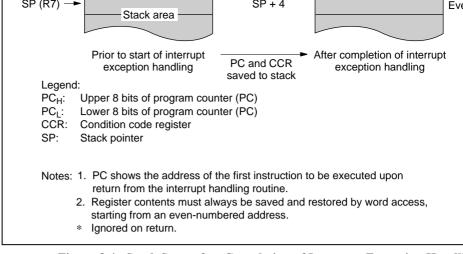

Stack State after Completion of Interrupt Exception Handling ......

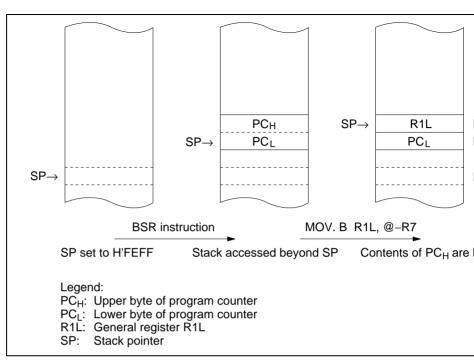

Interrupt Sequence Operation when Odd Address is Set in SP

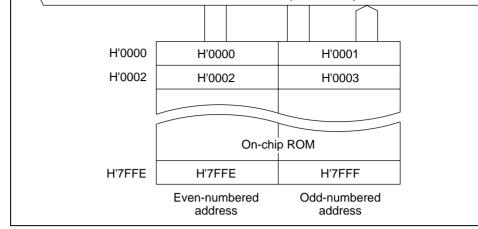

ROM Block Diagram (H8/3844R, H8/3844S, H8/38344 and H8/3844

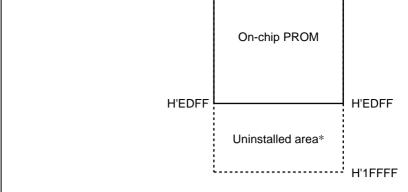

Socket Adapter Pin Correspondence (with HN27C101) ..... H8/3847R Memory Map in PROM Mode.....

RENESAS

Rev. 6.00 Aug 04, 2006 page

Figure 5.1

rigule 3.4

Figure 3.5

Figure 3.6

Section 6 ROM Figure 6.1

Figure 6.2

Figure 6.3

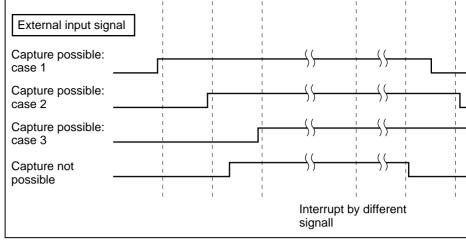

Standby Mode Transition and Pin States..... Figure 5.2 Figure 5.3 External Input Signal Capture when Signal Changes before/after Standby Mode or Watch Mode.....

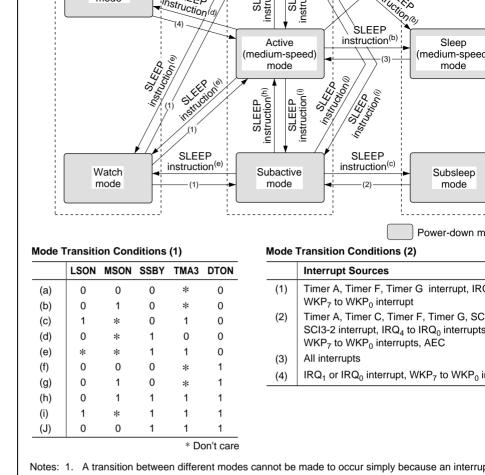

Mode Transition Diagram.

| rigule 0.12               | Socket Adapter Fin Correspondence Diagram                      |

|---------------------------|----------------------------------------------------------------|

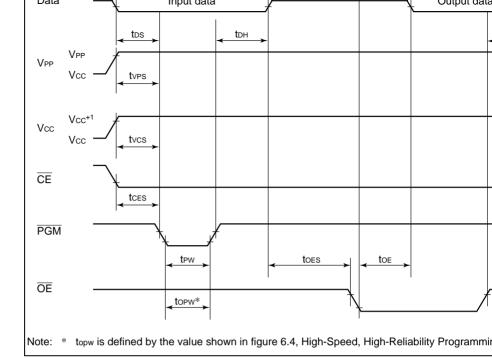

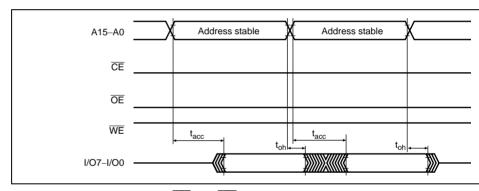

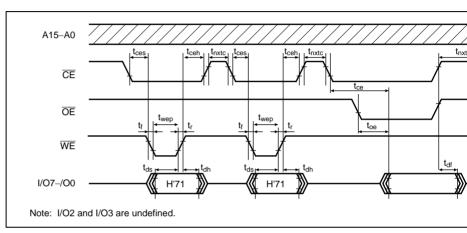

| Figure 6.13               | Timing Waveforms for Memory Read after Memory Write            |

| Figure 6.14               | Timing Waveforms in Transition from Memory Read Mode to Anothe |

|                           | Mode                                                           |

| Figure 6.15               | CE and OE Enable State Read Timing Waveforms                   |

| Figure 6.16               | CE and OE Clock System Read Timing Waveforms                   |

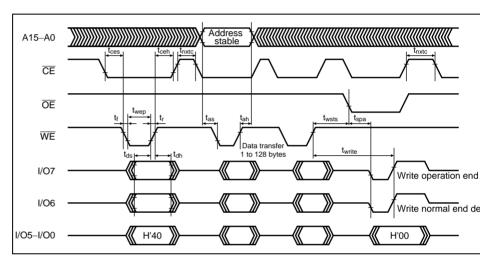

| Figure 6.17               | Auto-Program Mode Timing Waveforms                             |

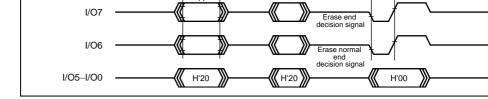

| Figure 6.18               | Auto-Erase Mode Timing Waveforms                               |

| Figure 6.19               | Status Read Mode Timing Waveforms                              |

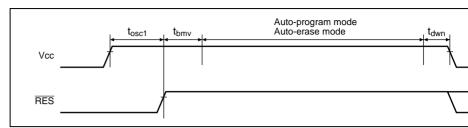

| Figure 6.20               | Oscillation Stabilization Time, Boot Program Transfer Time,    |

|                           | and Power-Down Sequence                                        |

|                           |                                                                |

| Section 7 R               | AM                                                             |

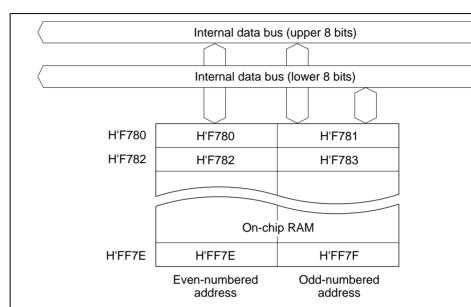

| Figure 7.1                | RAM Block Diagram (H8/3844R, H8/3844S, H8/38344 and H8/38444   |

|                           |                                                                |

| Section 8 I/O             |                                                                |

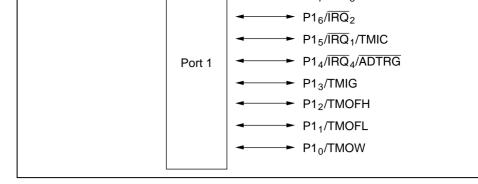

| Figure 8.1                | Port 1 Pin Configuration                                       |

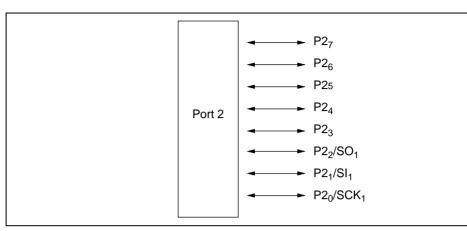

| Figure 8.2                | Port 2 Pin Configuration                                       |

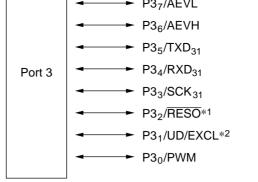

| Figure 8.3                | Port 3 Pin Configuration                                       |

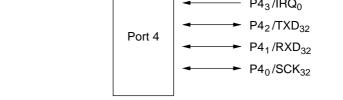

| Figure 8.4                | Port 4 Pin Configuration                                       |

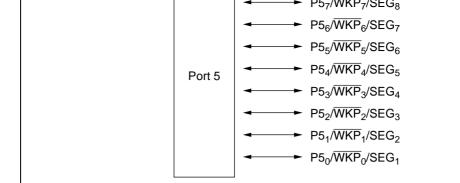

| Figure 8.5                | Port 5 Pin Configuration                                       |

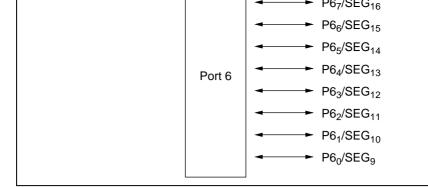

| Figure 8.6                | Port 6 Pin Configuration                                       |

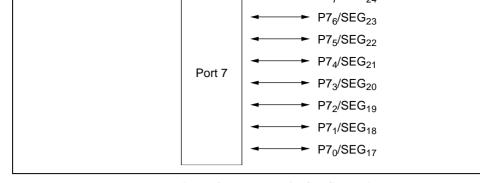

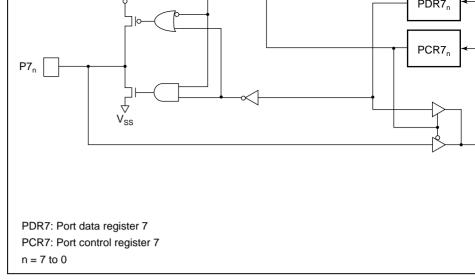

| Figure 8.7                | Port 7 Pin Configuration                                       |

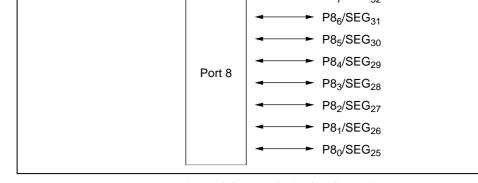

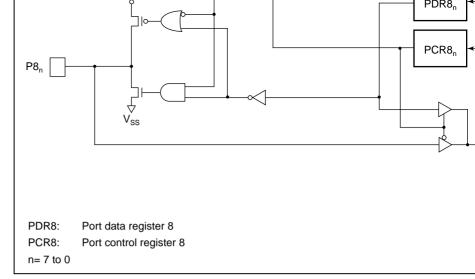

| Figure 8.8                | Port 8 Pin Configuration                                       |

|                           |                                                                |

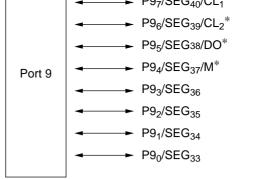

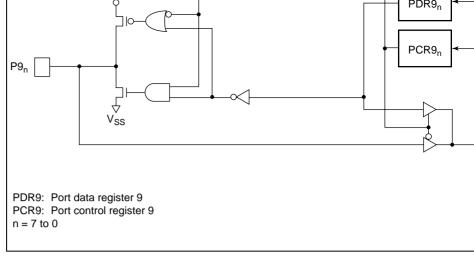

| Figure 8.9                | Port 9 Pin Configuration                                       |

| _                         |                                                                |

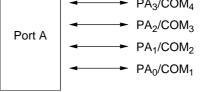

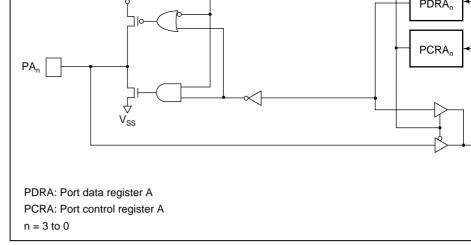

| Figure 8.9                | Port A Pin Configuration                                       |

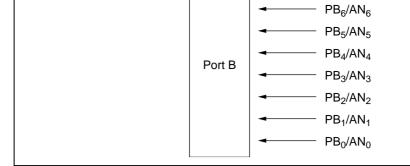

| Figure 8.9<br>Figure 8.10 |                                                                |

Block Diagram of Timer A.... Figure 9.1

Figure 8.13

**Section 9 Timers**

Rev. 6.00 Aug 04, 2006 page xxiv of xxxvi

RENESAS

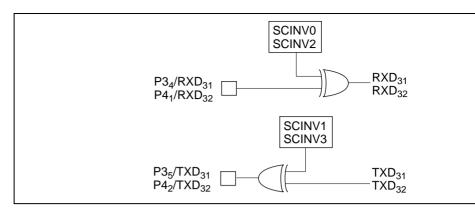

Input/Output Data Inversion Function.....

|     |               | Procedure                                                      |

|-----|---------------|----------------------------------------------------------------|

| Fig | gure 9.16     | Timer G Application Example                                    |

| Fig | gure 9.17     | Block Diagram of Watchdog Timer                                |

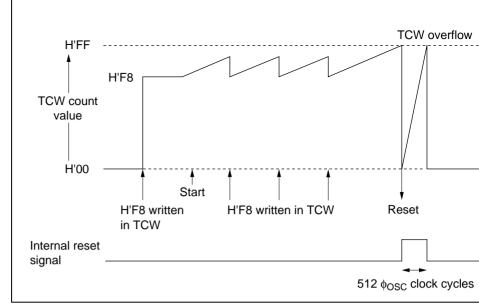

| Fig | gure 9.18     | Typical Watchdog Timer Operations (Example)                    |

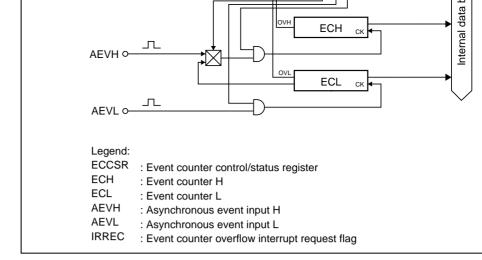

| Fig | gure 9.19     | Block Diagram of Asynchronous Event Counter                    |

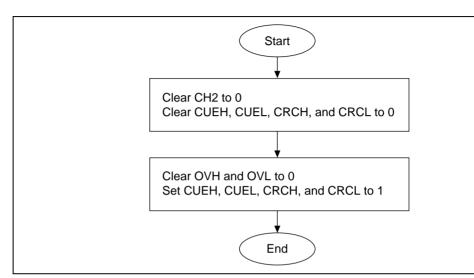

| Fig | gure 9.20     | Example of Software Processing when Using ECH and ECL as 16-Bi |

|     |               | Event Counter                                                  |

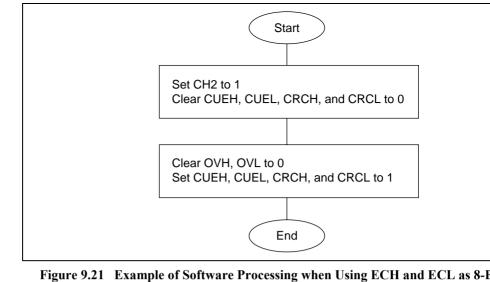

| Fig | gure 9.21     | Example of Software Processing when Using ECH and ECL as 8-Bit |

|     |               | Counters                                                       |

|     |               |                                                                |

| Se  | ction 10 Ser  | ial Communication Interface                                    |

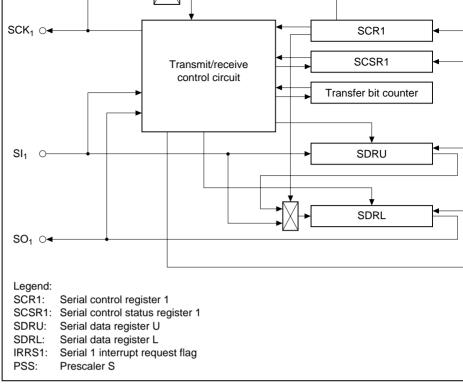

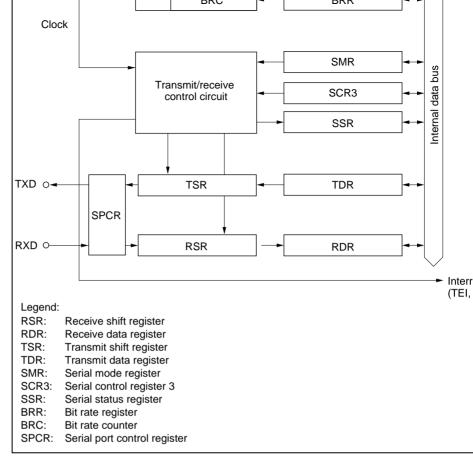

| Fig | gure 10.1     | SCI1 Block Diagram                                             |

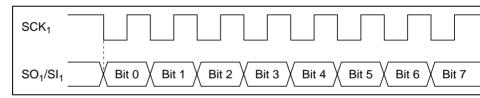

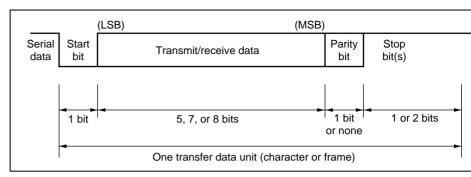

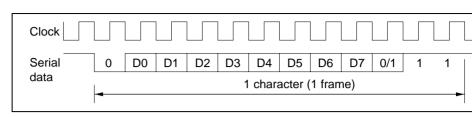

| Fig | gure 10.2     | Transfer Format                                                |

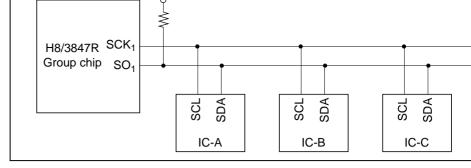

| Fig | gure 10.3     | Example of SSB Connections.                                    |

| Fig | gure 10.4     | Transfer Format (When $SNC1 = 0$ , $SNC0 = 1$ , $MRKON = 1$ )  |

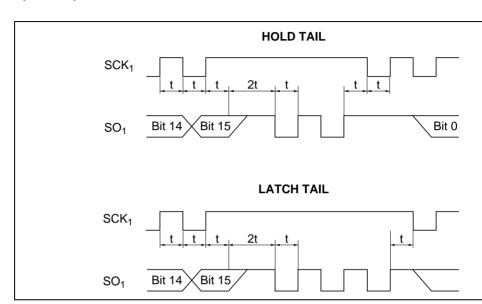

| Fig | gure 10.5     | HOLD TAIL and LATCH TAIL Output Waveforms                      |

| Fig | gure 10.6     | SCI3 Block Diagram                                             |

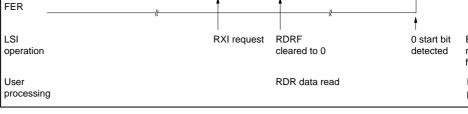

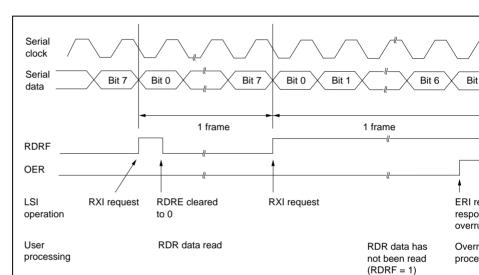

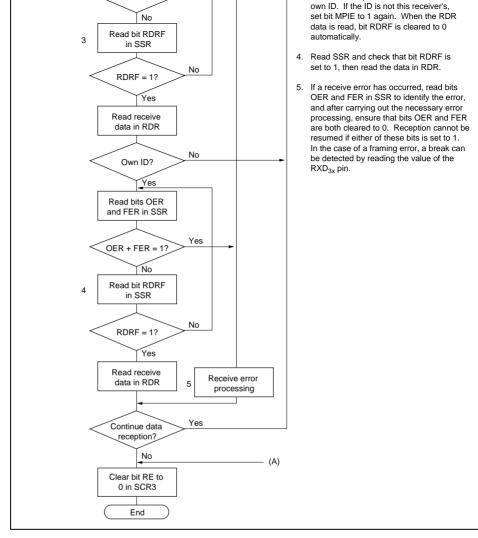

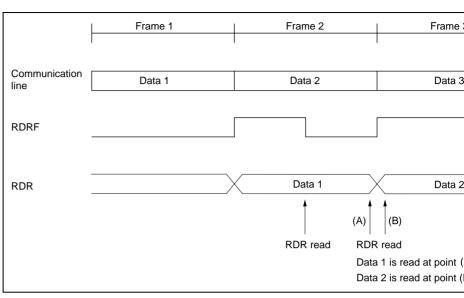

| Fig | gure 10.7 (a) | RDRF Setting and RXI Interrupt                                 |

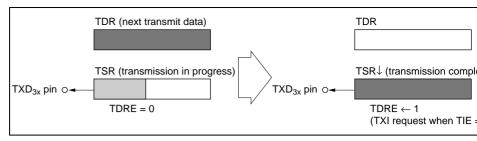

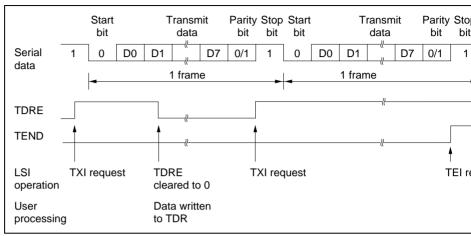

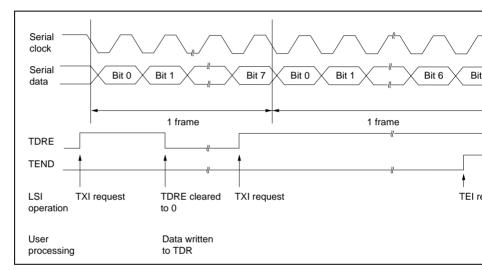

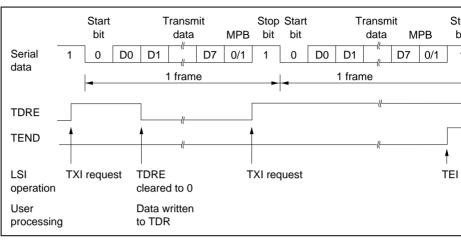

|     |               | TDRE Setting and TXI Interrupt                                 |

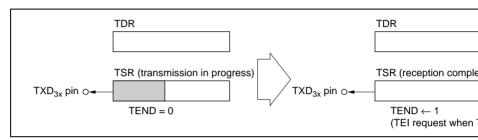

| Fig | gure 10.7 (c) | TEND Setting and TEI Interrupt                                 |

|     |               |                                                                |

riguie 9.9

Figure 9.10

Figure 9.11

Figure 9.12

Figure 9.13

Figure 9.14

Figure 9.15

Figure 10.8

Figure 10.9

Figure 10.10

Figure 10.11

Rev. 6.00 Aug 04, 2006 pag

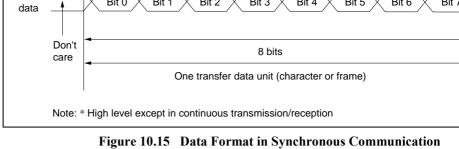

Data Format in Asynchronous Communication .....

(Asynchronous Mode) (8-bit data, parity, 2 stop bits).....

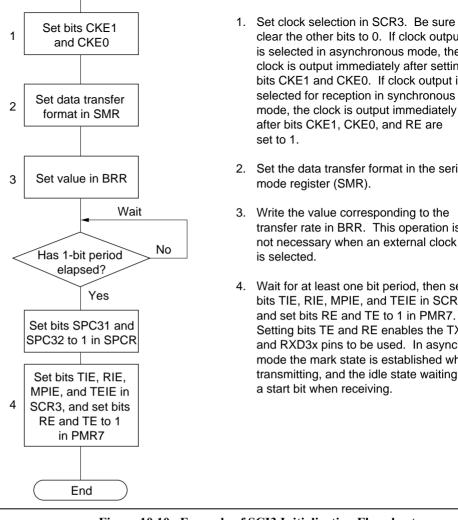

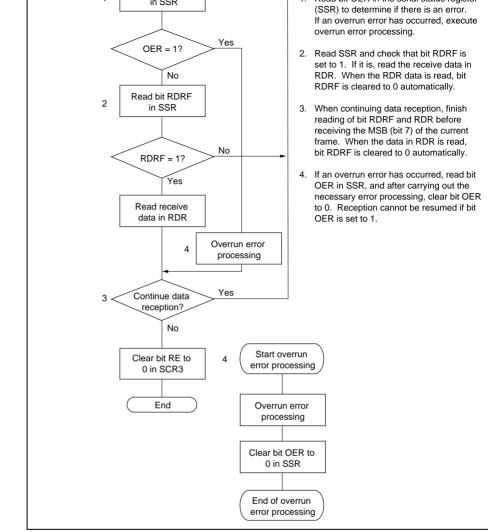

Example of SCI3 Initialization Flowchart.....

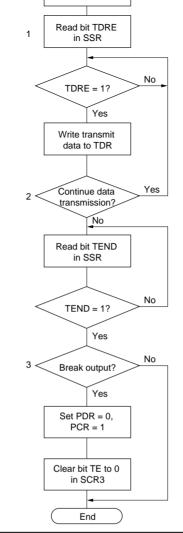

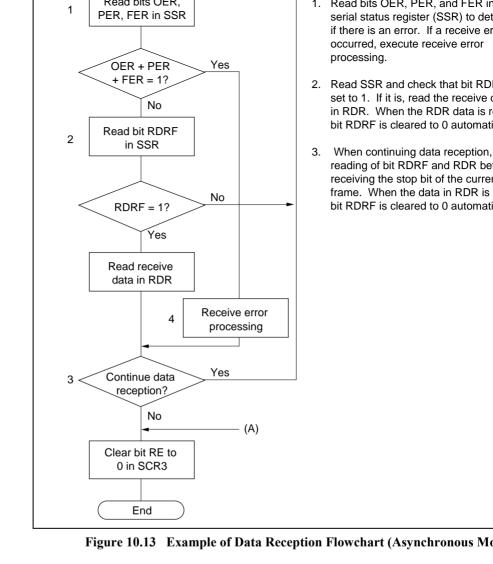

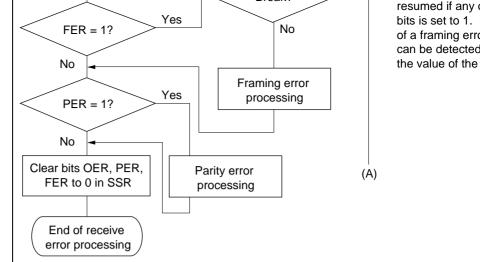

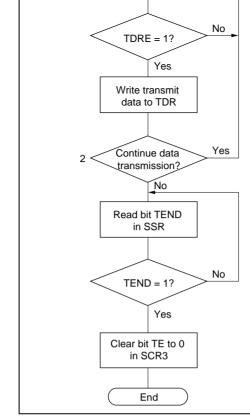

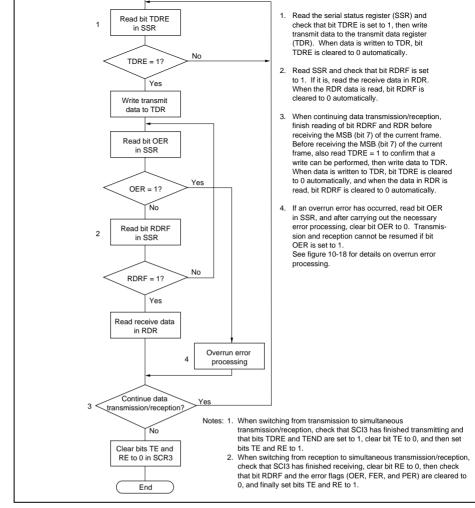

Example of Data Transmission Flowchart (Asynchronous Mode).....

Phase Relationship between Output Clock and Transfer Data

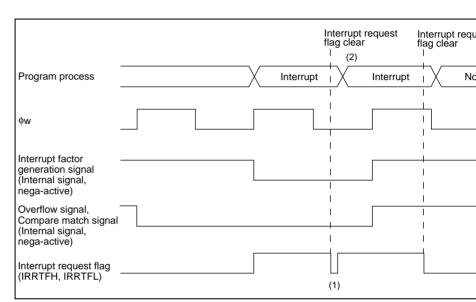

Noise Cancelei Diock Diagram .....

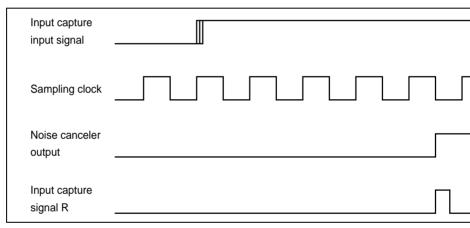

Noise Canceler Timing (Example)

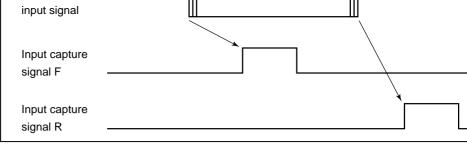

Input Capture Input Timing (without Noise Cancellation Function)....

Input Capture Input Timing (with Noise Cancellation Function).......

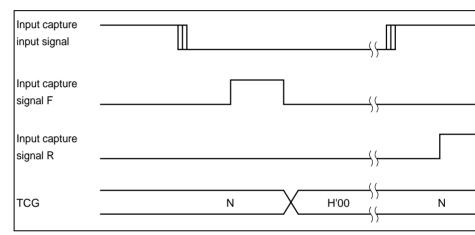

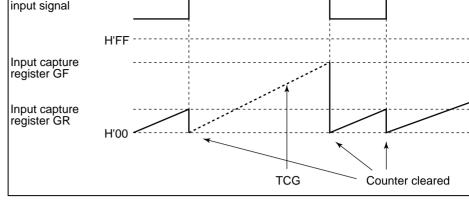

Timing of Input Capture by Input Capture Input.....

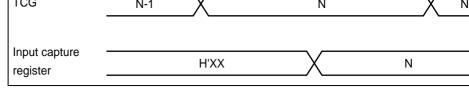

TCG Clear Timing

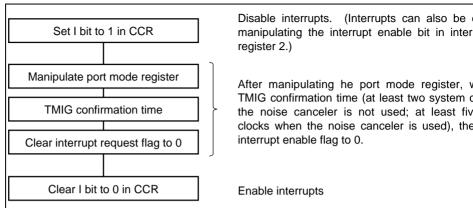

Port Mode Register Manipulation and Interrupt Enable Flag Clearing

| riguie 10.16  | Example of Data Reception Flowchaft (Synchronous Mode)            |

|---------------|-------------------------------------------------------------------|

| Figure 10.19  | Example of Operation when Receiving in Synchronous Mode           |

| Figure 10.20  | Example of Simultaneous Data Transmission/Reception Flowchart     |

|               | (Synchronous Mode)                                                |

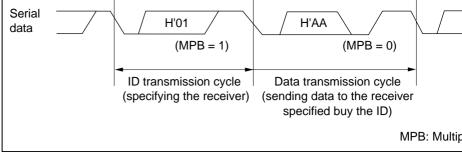

| Figure 10.21  | Example of Inter-Processor Communication Using Multiprocessor For |

|               | (Sending data H'AA to receiver A)                                 |

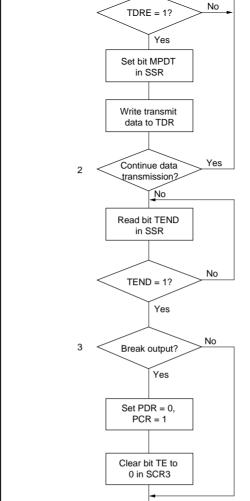

| Figure 10.22  | Example of Multiprocessor Data Transmission Flowchart             |

| Figure 10.23  | Example of Operation when Transmitting Using Multiprocessor Forma |

|               | (8-bit data, multiprocessor bit, 1 stop bit)                      |

| Figure 10.24  | Example of Multiprocessor Data Reception Flowchart                |

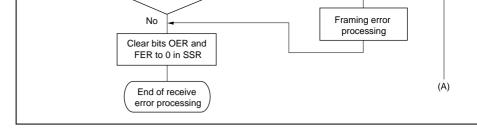

| Figure 10.25  | Example of Operation when Receiving Using Multiprocessor Format   |

|               | (8-bit data, multiprocessor bit, 1 stop bit)                      |

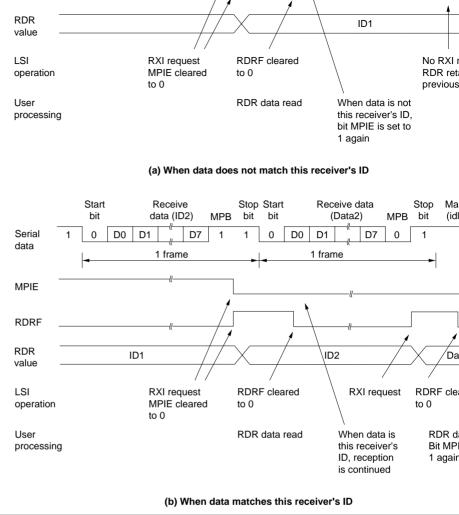

| Figure 10.26  | Receive Data Sampling Timing in Asynchronous Mode                 |

| Figure 10.27  | Relation between RDR Read Timing and Data                         |

|               |                                                                   |

| Section 11 14 | -Bit PWM                                                          |

| Figure 11.1   | Block Diagram of the 14 bit PWM                                   |

| Figure 11.2   | PWM Output Waveform                                               |

|               |                                                                   |

| Section 12 A/ | D Converter                                                       |

|               |                                                                   |

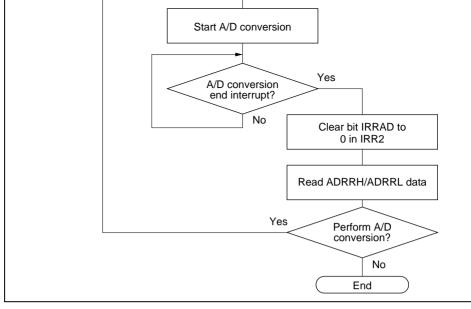

Flow Chart of Procedure for Using A/D Converter (Interrupts Used)....

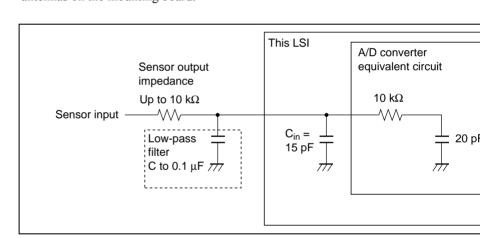

Analog Input Circuit Example

Block Diagram of LCD Controller/Driver.....

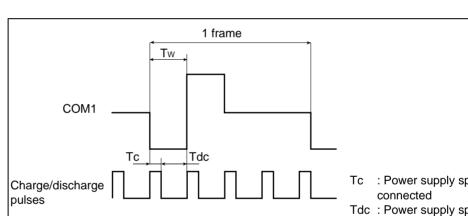

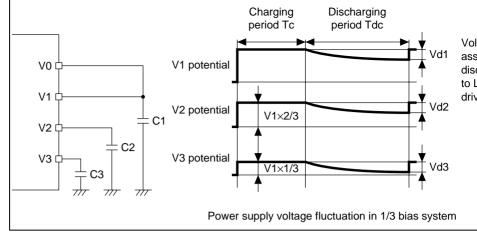

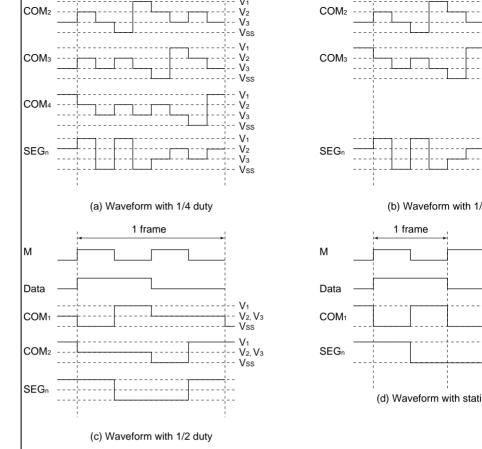

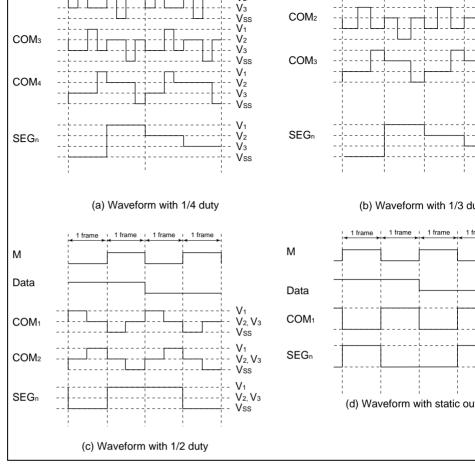

Example of A Waveform with 1/2 Duty and 1/2 Bias.....

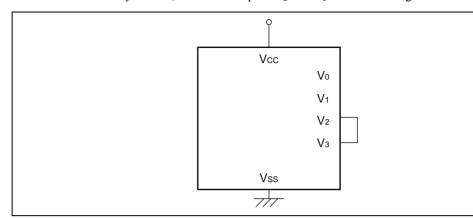

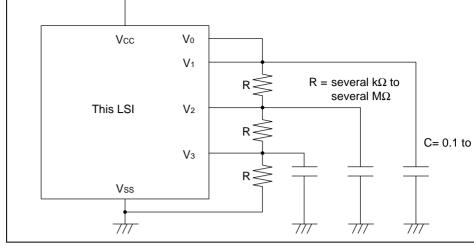

Handling of LCD Drive Power Supply when Using 1/2 Duty.....

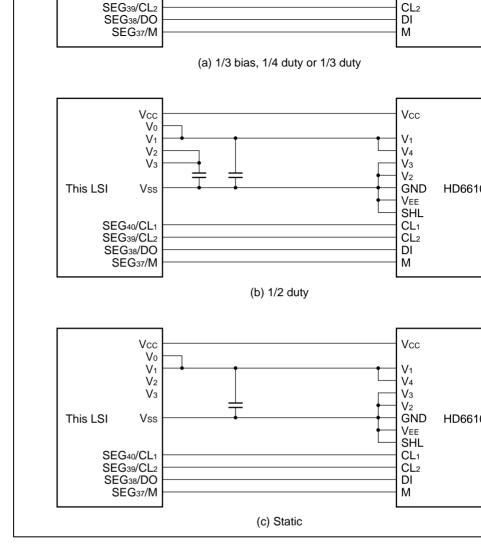

Examples of LCD Power Supply Pin Connections.....

RENESAS

## Figure 12.1

## Block Diagram of the A/D Converter....

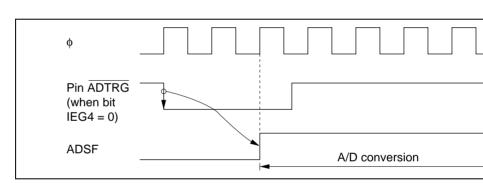

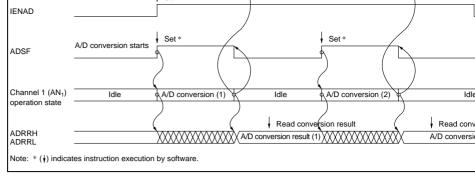

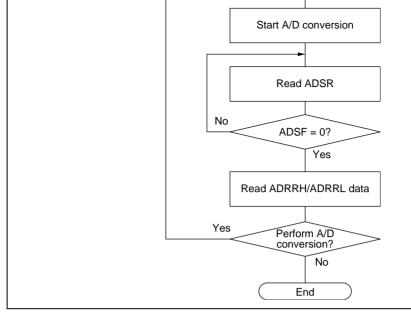

External Trigger Input Timing. Typical A/D Converter Operation Timing..... Figure 12.3 Flow Chart of Procedure for Using A/D Converter (Polling by Softwar

Section 13 LCD Controller/Driver

Rev. 6.00 Aug 04, 2006 page xxvi of xxxvi

Figure 12.2

Figure 12.4 Figure 12.5

Figure 12.6

Figure 13.1

Figure 13.2

Figure 13.3

Figure 13.4

| C              | 1 1                                                              |

|----------------|------------------------------------------------------------------|

| Figure 13.15   | Output Waveforms for Each Duty Cycle (A Waveform)                |

| Figure 13.16   | Output Waveforms for Each Duty Cycle (B Waveform)                |

| Figure 13.17   | Connection of External Split-Resistance                          |

| Figure 13.18   | Connection to HD66100                                            |

| Section 14 Po  | ower Supply Circuit                                              |

| Figure 14.1    | Power Supply Connection when Internal Step-Down Circuit is Used  |

| Figure 14.2    | Power Supply Connection when Internal Step-Down Circuit is Not U |

| Section 15 El  | lectrical Characteristics                                        |

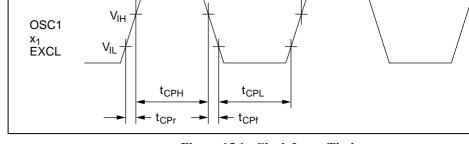

| Figure 15.1    | Clock Input Timing                                               |

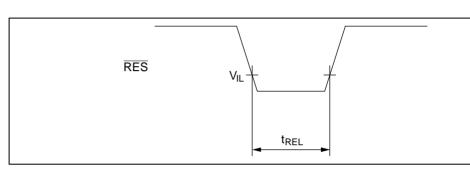

| Figure 15.2    | RES Low Width                                                    |

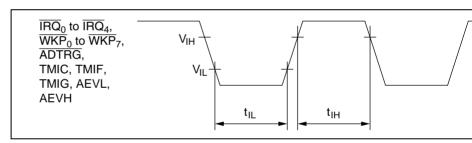

| Figure 15.3    | Input Timing                                                     |

| Figure 15.4    | UD Pin Minimum Modulation Width Timing                           |

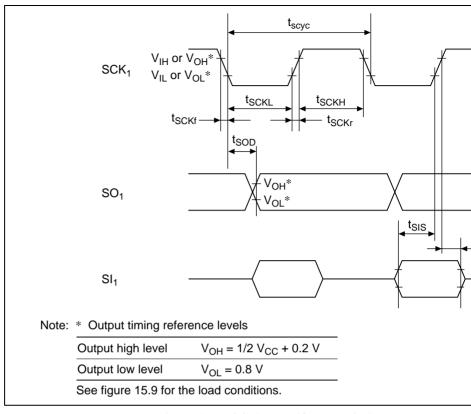

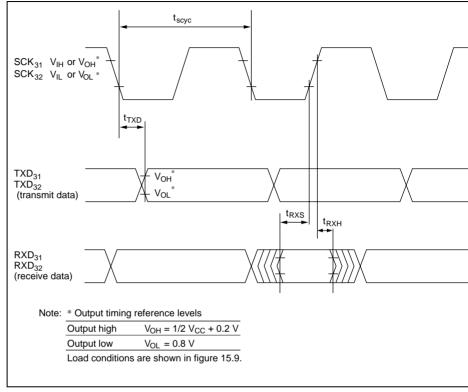

| Figure 15.5    | SCI1 Input/Output Timing.                                        |

| Figure 15.6    | SCK3 Input Clock Timing                                          |

| Figure 15.7    | SCI3 Synchronous Mode Input/Output Timing                        |

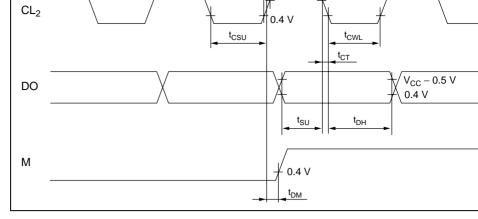

| Figure 15.8    | Segment Expansion Signal Timing                                  |

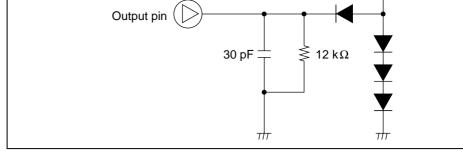

| Figure 15.9    | Output Load Condition                                            |

| Figure 15.10   | Resonator Equivalent Circuit                                     |

| Figure 15.11   | Recommended Resonators.                                          |

|                |                                                                  |

|                | I/O Port Block Diagrams                                          |

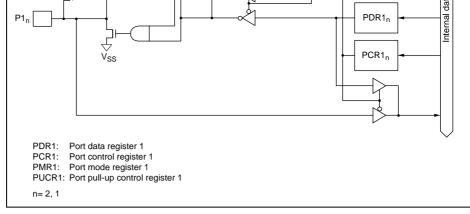

| Figure C.1 (a) |                                                                  |

| Figure C.1 (b) |                                                                  |

| Figure C.1 (c) | Port 1 Block Diagram (Pin P1 <sub>2</sub> , P1 <sub>1</sub> )    |

|                |                                                                  |

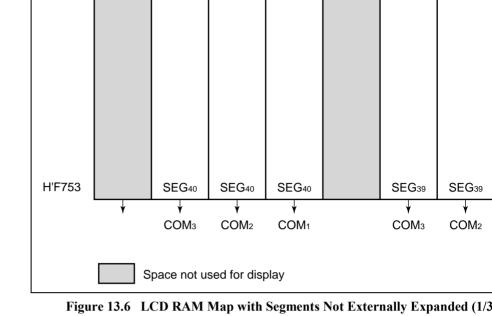

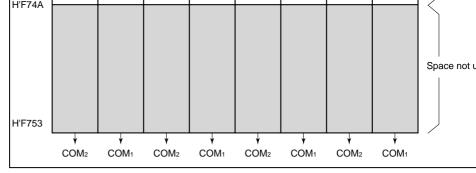

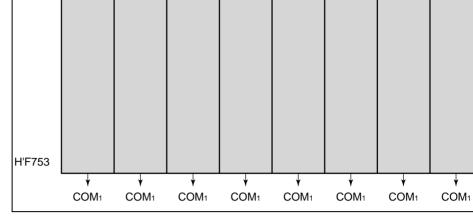

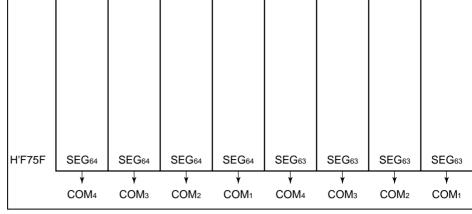

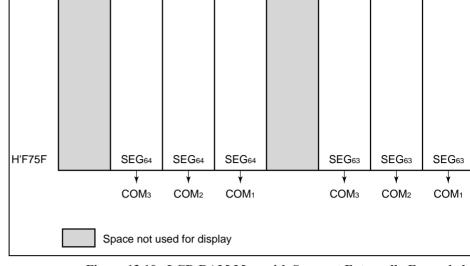

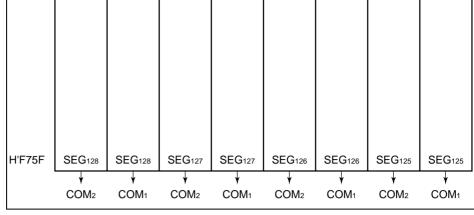

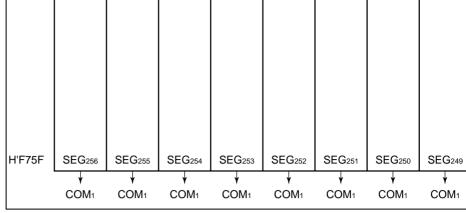

LCD KAM Map with Segment Externally Expanded

LCD RAM Map with Segment Externally Expanded

(SGX = "1", SGS3 to SGS0 = "0000" 1/2 duty).....

(SGX = "1", SGS3 to SGS0 = "0000" static).....

LCD Drive Power Supply Unit.....

Example of Low-Power-Consumption LCD Drive Operation ......

RENESAS

Rev. 6.00 Aug 04, 2006 page

rigule 13.11

Figure 13.12

Figure 13.13

Figure 13.14

|   | •                | S ( )                                                                         |

|---|------------------|-------------------------------------------------------------------------------|

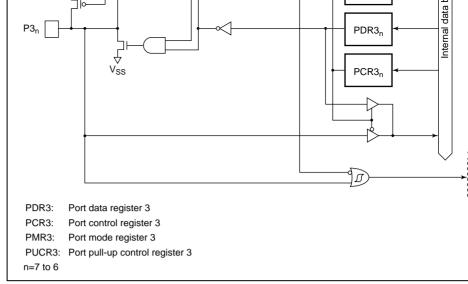

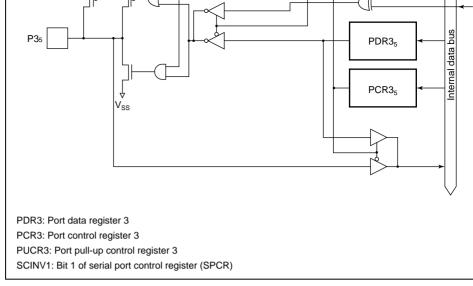

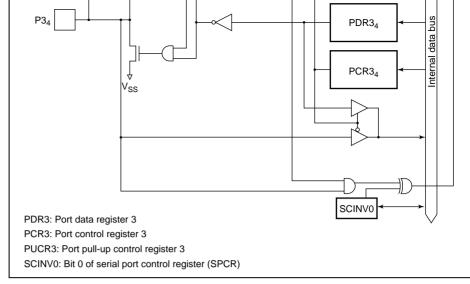

| ] | Figure C.3 (c)   | Port 3 Block Diagram (Pin P3 <sub>4</sub> )                                   |

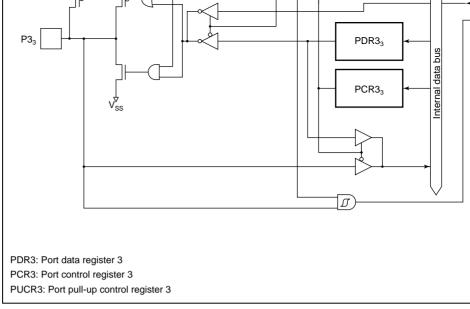

| ] | Figure C.3 (d)   | Port 3 Block Diagram (Pin P3 <sub>3</sub> )                                   |

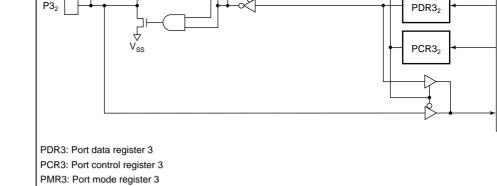

| ] | Figure C.3 (e-1) | Port 3 Block Diagram (Pin P32, H8/3847R Group and H8/3847S Group              |

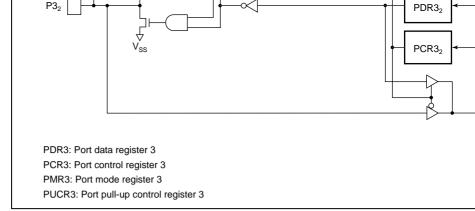

| ] | Figure C.3 (e-2) | Port 3 Block Diagram (Pin P32, H8/38347 Group and H8/38447 Group              |

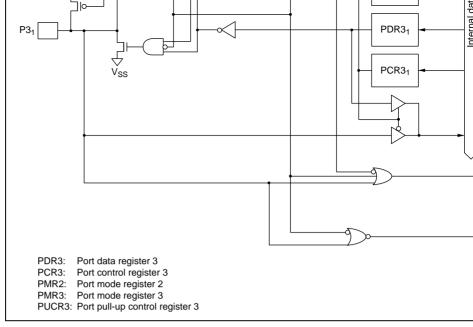

| ] | Figure C.3 (f-1) | Port 3 Block Diagram (Pin P3 <sub>1</sub> , H8/3847R Group and H8/3847S Group |

|   | • • •            | Port 3 Block Diagram (Pin P3 <sub>1</sub> , H8/38347 Group and H8/38447 Group |

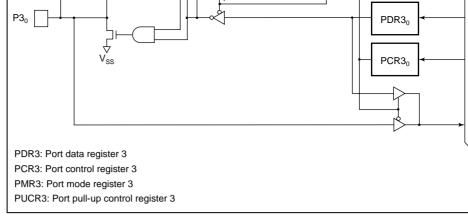

|   | • , ,            | Port 3 Block Diagram (Pin P3 <sub>0</sub> )                                   |

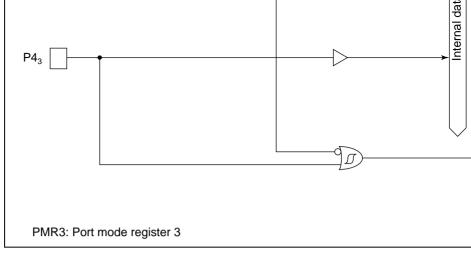

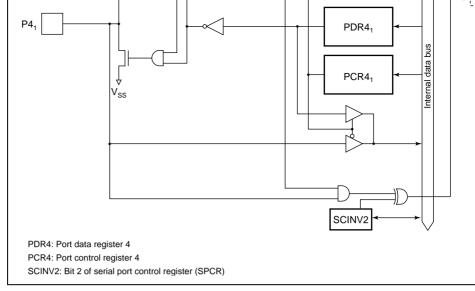

|   |                  | Port 4 Block Diagram (Pin P4 <sub>3</sub> )                                   |

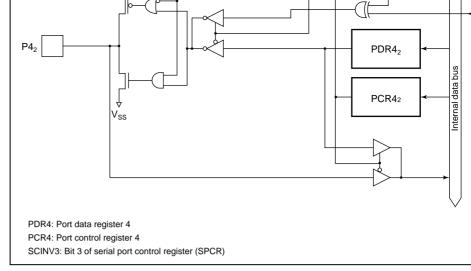

|   | •                | Port 4 Block Diagram (Pin P4 <sub>2</sub> )                                   |

|   | • , ,            | Port 4 Block Diagram (Pin P4 <sub>1</sub> )                                   |

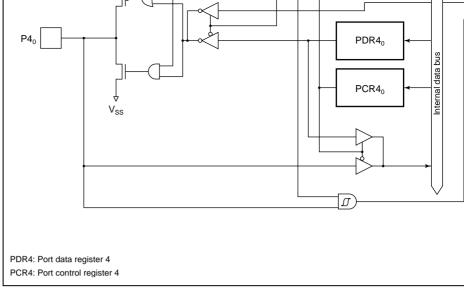

|   | • , ,            | Port 4 Block Diagram (Pin P4 <sub>0</sub> )                                   |

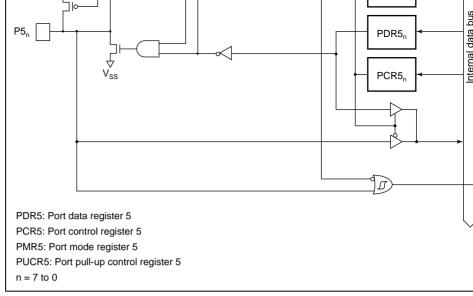

|   |                  | Port 5 Block Diagram                                                          |

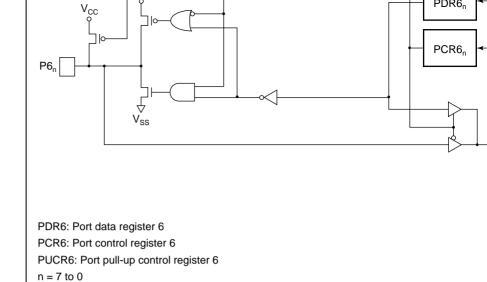

|   | •                | Port 6 Block Diagram                                                          |

|   | •                | Port 7 Block Diagram                                                          |

|   | •                | Port 8 Block Diagram                                                          |

|   | •                | Port 9 Block Diagram                                                          |

|   |                  | Port A Block Diagram                                                          |

|   | •                | Port B Block Diagram                                                          |

|   | · ·              | Port C Block Diagram                                                          |

| • | 1 15410 0.12     | Toll C Block Diagram                                                          |

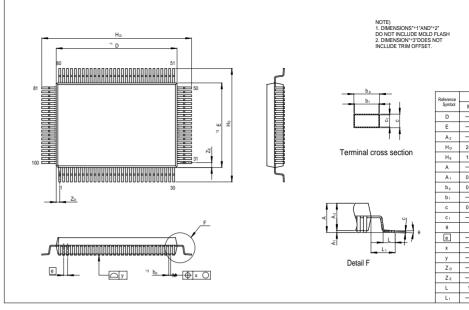

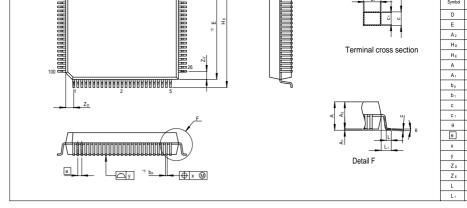

| , | Annendix F P     | ackage Dimensions                                                             |

| - | -pponum -        |                                                                               |

###

Rev. 6.00 Aug 04, 2006 page xxviii of xxxvi

**Specifications of Chip Form**

Figure F.1

Figure F.2

Figure F.3

Figure F.4

Appendix G

Figure G.1

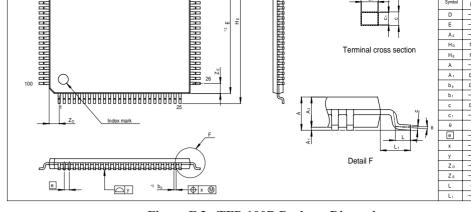

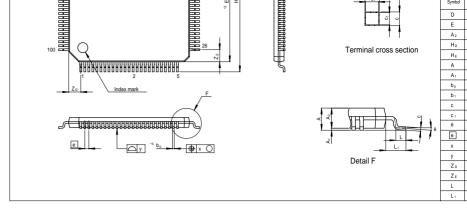

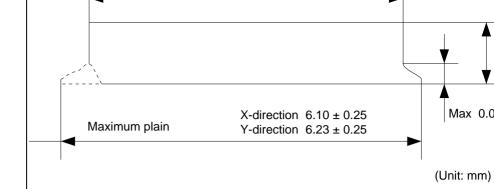

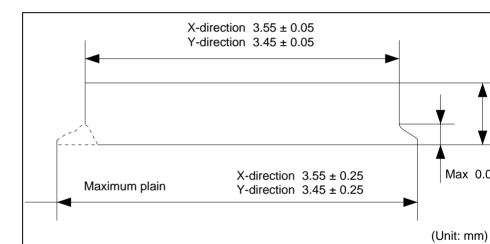

FP-100A Package Dimensions

FP-100B Package Dimensions

TFP-100B Package Dimensions

TFP-100G Package Dimensions

Chip Sectional Figure

Figure I.2 Specifications of Chip Tray.

Figure I.3 Specifications of Chip Tray.

Figure I.4 Specifications of Chip Tray.

Specifications of Chip Tray.

| Section 2   | CPU                           |

|-------------|-------------------------------|

| Table 2.1   | Addressing Modes              |

| Table 2.2   | Effective Address Calculation |

| Table 2.3   | Instruction Set               |

| Table 2.4   | Data Transfer Instructions    |

| Table 2.5   | Arithmetic Instructions       |

| Table 2.6   | Logic Operation Instructions  |

| Table 2.7   | Shift Instructions            |

| Table 2.8   | Bit-Manipulation Instructions |

| Table 2.9   | Branching Instructions        |

| Table 2.10  | -                             |

| Table 2.11  | -                             |

| Table 2.12  |                               |

| Table 2.13  | -                             |

| 1 4010 2.13 | 100 min 1110 on j Dio         |

|             |                               |

Bonding Pad Coordinates of H8/38347 Group (Mask ROM Version)

and H8/38447 Group (Mask ROM Version).....

### Table 3.2 Interrupt Sources and Their Priorities Table 3.3 Interrupt Control Registers

Table 3.1

Table 3.4

**Section 3 Exception Handling**

Table 1.5

Table 1.6

Pin Functions

Interrupt Wait States..... Table 3.5 Conditions Under which Interrupt Request Flag is Set to 1 .....

| S | Section | 5 | Power- | Down | Mode |

|---|---------|---|--------|------|------|

|   |         |   |        |      |      |

| Section 5 | Power-Down Modes |

|-----------|------------------|

| Table 5.1 | Operating Modes  |

Internal State in Each Operating Mode Table 5.2 Table 5.3 System Control Registers

Table 5.4 Clock Frequency and Settling Time (Times are in ms).....

Setting and Clearing Module Standby Mode by Clock Stop Register..... Table 5.5

Rev. 6.00 Aug 04, 2006 page xxx of xxxvi

RENESAS

Exception Handling Types and Priorities.....

| 14010 0.15             | 1 Togramming 1 mile                                               |

|------------------------|-------------------------------------------------------------------|

| Table 6.14             | Command Sequence in Programmer Mode                               |

| Table 6.15             | AC Characteristics in Transition to Memory Read Mode              |

| Table 6.16             | AC Characteristics in Transition from Memory Read Mode to Another |

| Table 6.17             | AC Characteristics in Memory Read Mode                            |

| Table 6.18             | AC Characteristics in Auto-Program Mode                           |

| Table 6.19             | AC Characteristics in Auto-Erase Mode                             |

| Table 6.20             | AC Characteristics in Status Read Mode                            |

| Table 6.21             | Status Read Mode Return Codes                                     |

| Table 6.22             | Status Polling Output Truth Table                                 |

| Table 6.23             | Stipulated Transition Times to Command Wait State                 |

| Table 6.24             | Flash Memory Operating States                                     |

|                        |                                                                   |

| Section 8 I            | I/O Ports                                                         |

| Table 8.1              | Port Functions                                                    |

| Table 8.2              | Port 1 Registers                                                  |

| Table 8.3              | Port 1 Pin Functions                                              |

| Table 8.4              | Port 1 Pin States                                                 |

| Table 8.5              | Port 2 Registers                                                  |

| Table 8.6              | Port 2 Pin Functions                                              |

|                        |                                                                   |

| Table 8.7              | Port 2 Pin States                                                 |

| Table 8.7<br>Table 8.8 | Port 2 Pin States                                                 |

|                        | Port 3 Registers                                                  |

| Table 8.8              |                                                                   |

| Table 8.8<br>Table 8.9 | Port 3 Registers                                                  |

Table 0.8

Table 6.9

Table 6.10

Table 6.11 Table 6.12

Table 6.13

Setting Flogramming Wodes.....

Additional-Program Data Computation Table .....

Programming Time.

| Table 8.23 | Port 8 Registers         |

|------------|--------------------------|

| Table 8.24 | Port 8 Pin Functions     |

| Table 8.25 | Port 8 Pin States        |

| Table 8.26 | Port 9 Registers         |

| Table 8.27 | Port 9 Pin Functions     |

| Table 8.28 | Port 9 Pin States        |

| Table 8.29 | Port A Registers         |

| Table 8.30 | Port A Pin Functions     |

| Table 8.31 | Port A Pin States        |

| Table 8.32 | Port B Register          |

| Table 8.33 | Port C Register          |

| Table 8.34 | Register Configuration   |

|            |                          |

| Section 9  | Timers                   |

| Table 9.1  | Timer Functions          |

| Table 9.2  | Pin Configuration        |

| Table 9.3  | Timer A Registers        |

| Table 9.4  | Timer A Operation States |

| Table 9.5  | Pin Configuration        |

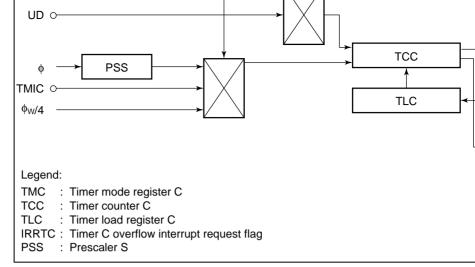

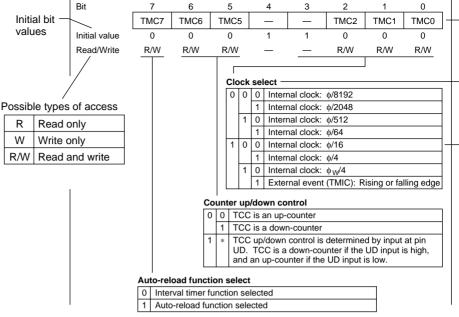

| Table 9.6  | Timer C Registers        |

| Table 9.7  | Timer C Operation States |

| Table 9.8  | Pin Configuration        |

| Table 9.9  | Timer F Registers        |

| Table 9.10 | Timer F Operation Modes  |

|            |                          |

Table 8.22 Port 7 Pin States

Rev. 6.00 Aug 04, 2006 page xxxii of xxxvi

Table 9.11 Table 9.12

Table 9.13

Table 9.14 Table 9.15

RENESAS

Pin Configuration

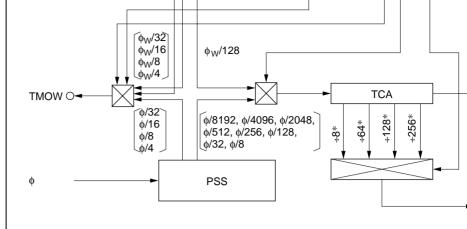

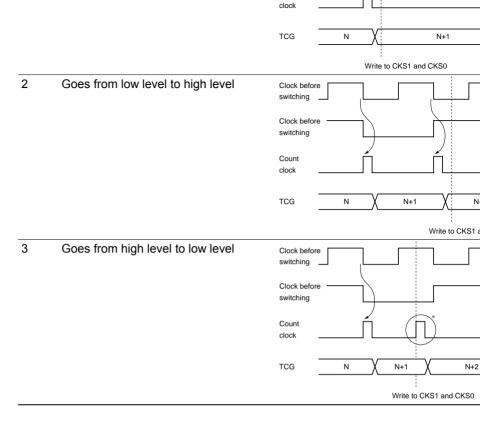

Internal Clock Switching and TCG Operation

Input Capture Input Signal Input Edges Due to Input Capture Input Pin Stand Conditions for Their Occurrence

| 1 abic 10.2 | Seri i ili collinguration                                           |

|-------------|---------------------------------------------------------------------|

| Table 10.3  | Registers                                                           |

| Table 10.4  | Pin Configuration                                                   |

| Table 10.5  | Registers                                                           |

| Table 10.6  | Examples of BRR Settings for Various Bit Rates (Asynchronous Mode)  |

| Table 10.6  | Examples of BRR Settings for Various Bit Rates (Asynchronous Mode)  |

| Table 10.7  | Relation between n and Clock                                        |

| Table 10.8  | Maximum Bit Rate for Each Frequency (Asynchronous Mode)             |

| Table 10.9  | Examples of BRR Settings for Various Bit Rates (Synchronous Mode) ( |

| Table 10.9  | Examples of BRR Settings for Various Bit Rates (Synchronous Mode) ( |

| Table 10.10 | Relation between n and Clock                                        |

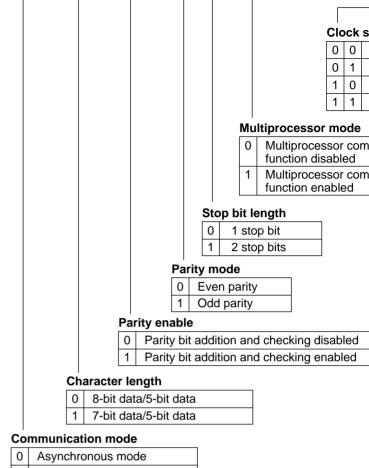

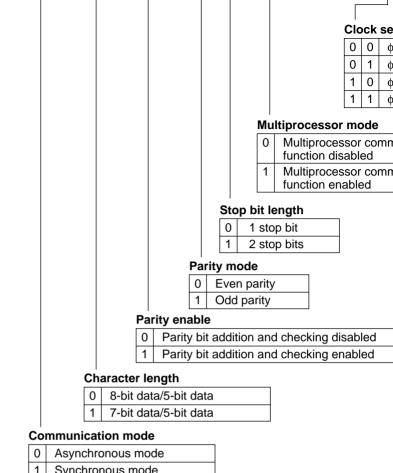

| Table 10.11 | SMR Settings and Corresponding Data Transfer Formats                |

| Table 10.12 | SMR and SCR3 Settings and Clock Source Selection                    |

| Table 10.13 | Transmit/Receive Interrupts                                         |

|             |                                                                     |

Overview of SCI Functions

Table 10.16 SCI3 Interrupt Requests Table 10.17 SSR Status Flag States and Receive Data Transfer

Section 11 14-Bit PWM Table 11.1

Table 11.2

Table 12.2 Table 12.3

Table 11.3

Section 12 A/D Converter

Table 12.1 Pin Configuration