## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

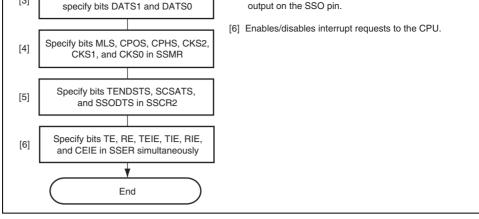

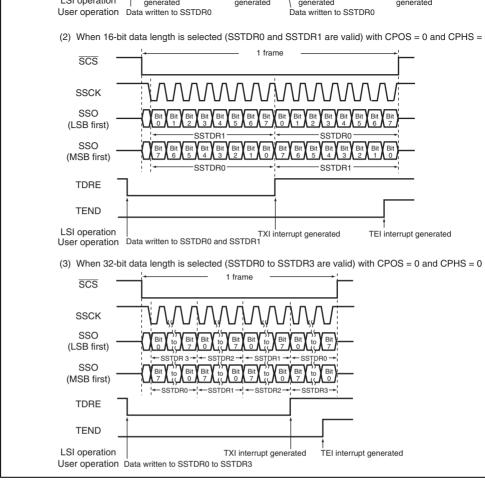

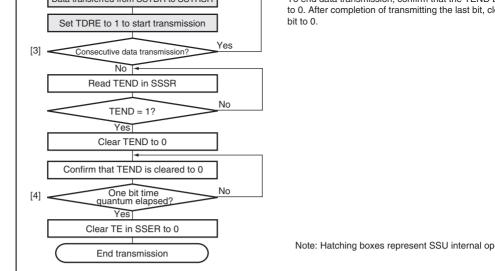

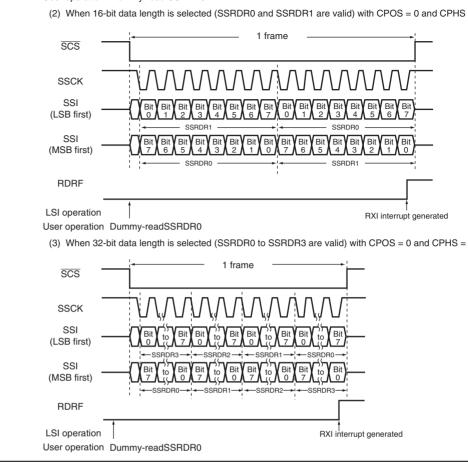

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

32

# SH7137 Group

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family

| SH7131 |  |

|--------|--|

| SH7132 |  |

| SH7136 |  |

| SH7137 |  |

Renesas Electronics

www.renesas.com

Rev.3.00

document, please confirm the latest product information with a Renesas sales office. Also, please pay r and careful attention to additional and different information to be disclosed by Renesas such as that disc through our website. (http://www.renesas.com ) 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the inform included in this document. When using or otherwise relying on the information in this document, you should evaluate the informatio light of the total system before deciding about the applicability of such information to the intended applica-Renesas makes no representations, warranties or quaranties regarding the suitability of its products for

particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products. 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which re-

especially high quality and reliability such as safety systems, or equipment or systems for transportation traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea commur transmission. If you are considering the use of our products for such purposes, please contact a Renesa sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth abo 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed (1) artificial life support devices or systems

damages arising out of the use of Renesas products beyond such specified ranges.

document, Renesas semiconductor products, or if you have any other inquiries.

(2) surgical implantations (3) healthcare intervention (e.g., excision, administration of medication, etc.)

(4) any other purposes that pose a direct threat to human life Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Re Technology Corp., its affiliated companies and their officers, directors, and employees against any and a damages arising out of such applications.

evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final produ system manufactured by you. 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is high. You should implement safety measures so that Renesas products may not be easily detached from products. Renesas shall have no liability for damages arising out of such detachment.

Rev. 3.00 Jan. 18, 2010 Page ii of xxiv RENESAS

You should use the products described herein within the range specified by Renesas, especially with res to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunct

10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have spec characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical inju injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the

12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior writte

13. Please contact a Renesas sales office if you have any questions regarding the information contained in

approval from Renesas.

induced in the vicinity of LSI, an associated shoot-through current flows internal malfunctions may occur due to the false recognition of the pin state as an input Unused pins should be handled as described under Handling of Unused Pins in manual. 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

— The states of internal circuits in the LSI are indeterminate and the states of regions.

- settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, states of pins are not guaranteed from the moment when power is supplied unti-

- reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip powe

- reset function are not guaranteed from the moment when power is supplied unt power reaches the level at which resetting has been specified. 3. Prohibition of Access to Reserved Addresses

- Access to reserved addresses is prohibited.

- - The reserved addresses are provided for the possible future expansion of function not access these addresses; the correct operation of LSI is not guaranteed if the accessed. 4. Clock Signals

- After applying a reset, only release the reset line after the operating clock signal ha become stable. When switching the clock signal during program execution, wait un target clock signal has stabilized. — When the clock signal is generated with an external resonator (or from an external resonator). oscillator) during a reset, ensure that the reset line is only released after full sta

- of the clock signal. Moreover, when switching to a clock signal produced with a external resonator (or by an external oscillator) while program execution is in pr wait until the target clock signal is stable. Differences between Products

- Before changing from one product to another, i.e. to one with a different type numb confirm that the change will not lead to problems.

- RENESAS

test for each of the products.

The characteristics of MPU/MCU in the same group but having different type nu may differ because of the differences in internal memory capacity and layout pa When changing to products of different type numbers, implement a system-eval

Rev. 3.00 Jan. 18, 2010 P.

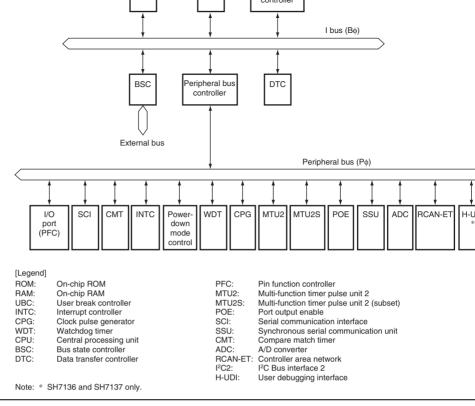

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each includes notes in relation to the descriptions given, and usage notes are given, as required final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions for This Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier ver This does not include all of the revised contents. For details, see the actual locations in the manual.

11. Index

Rev. 3.00 Jan. 18, 2010 Page iv of xxiv

REJ09B0402-0300

This manual was written to explain the hardware functions and electrical Objective: characteristics of the SH7131, SH7132, SH7136, and SH7137 Group to the

users. Refer to the SH-1/SH-2/SH-DSP Software Manual for a detailed descripti instruction set.

### Notes on reading this manual:

Examples:

In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized on the CPU, system control functions, peripheral functions and electrical characteris

• In order to understand the details of the CPU's functions Read the SH-1/SH-2/SH-DSP Software Manual.

Register name:

- In order to understand the details of a register when its name is known Read the index that is the final part of the manual to find the page number of the enti-

register. The addresses, bits, and initial values of the registers are summarized in sec List of Registers.

XXX\_N (XXX is the register name and N is the number) Bit order: The MSB is on the left and the LSB is on the right Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decima

Signal notation: An overbar is added to a low-active signal: xxxx

REJ09

The following notation is used for cases when the similar function, e.g. serial communication interf

implemented on more than one channel:

| SuperH <sup>™</sup> RISC engine C/C++ Compiler, Assembler,<br>Optimizing Linkage Editor Compiler Package V.9.00 User's Manual | REJ10B015  |

|-------------------------------------------------------------------------------------------------------------------------------|------------|

| SuperH <sup>™</sup> RISC engine High-performance Embedded Workshop 3<br>User's Manual                                         | REJ10B0028 |

| SuperH RISC engine High-performance Embedded Workshop 3 Tutorial                                                              | REJ10B0023 |

Document N

Application note:

**Document Title**

| Document Title                                             | Document N |

|------------------------------------------------------------|------------|

| SuperH RISC engine C/C++ Compiler Package Application Note | REJ05B0463 |

|                                                            |            |

RENESAS

All trademarks and registered trademarks are the property of their respective owners.

REJ09B0402-0300

Rev. 3.00 Jan. 18, 2010 Page vi of xxiv

|       | 2.2.4   | Initial Values of Registers       |

|-------|---------|-----------------------------------|

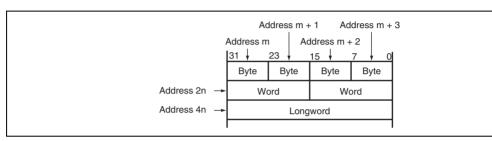

| 2.3   | Data F  | ormats                            |

|       | 2.3.1   | Register Data Format              |

|       | 2.3.2   | Memory Data Formats               |

|       | 2.3.3   | Immediate Data Formats            |

| 2.4   | Feature | es of Instructions                |

|       | 2.4.1   | RISC Type                         |

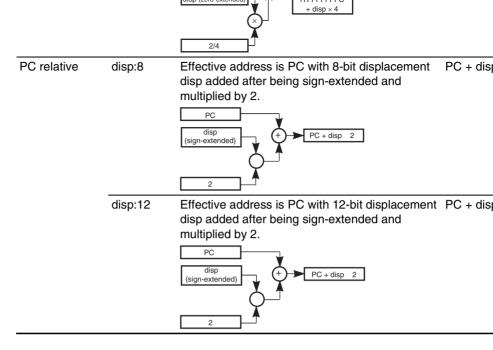

|       | 2.4.2   | Addressing Modes                  |

|       | 2.4.3   | Instruction Formats               |

| 2.5   | Instruc | tion Set                          |

|       | 2.5.1   | Instruction Set by Type           |

|       | 2.5.2   | Data Transfer Instructions        |

|       | 2.5.3   | Arithmetic Operation Instructions |

|       | 2.5.4   | Logic Operation Instructions      |

|       | 2.5.5   | Shift Instructions                |

|       | 2.5.6   | Branch Instructions               |

|       | 2.5.7   | System Control Instructions       |

| 2.6   | Process | sing States                       |

|       |         |                                   |

| Secti | on 3    | MCU Operating Modes               |

| 3.1   | Selecti | on of Operating Modes             |

| 3.2   | Input/C | Output Pins                       |

| 3.3   | Operat  | ing Modes                         |

|       | 3.3.1   | Mode 0 (MCU Extension Mode 0)     |

|       | 3.3.2   | Mode 2 (MCU Extension Mode 2)     |

2.2.1

2.2.2

2.2.3

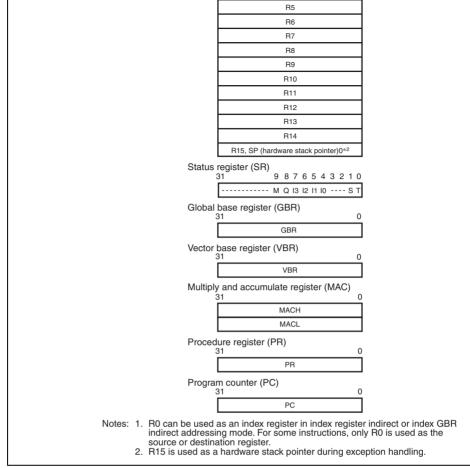

Register Configuration.....

General Registers (Rn).....

Control Registers

System Registers

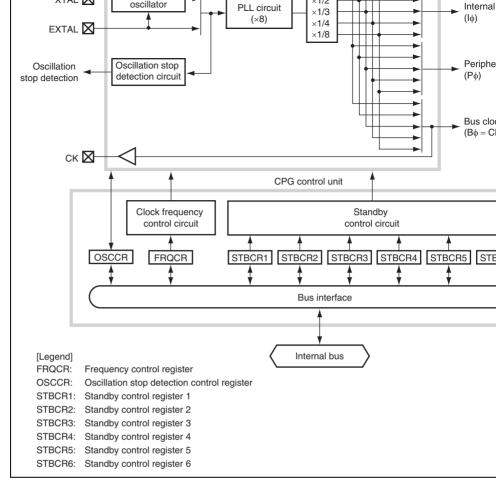

|      | 4.4.2              | Oscillation Stop Detection Control Register (OSCCR) |  |  |

|------|--------------------|-----------------------------------------------------|--|--|

| 4.5  | Changing Frequency |                                                     |  |  |

| 4.6  | Oscillator         |                                                     |  |  |

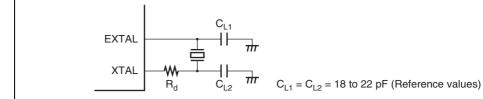

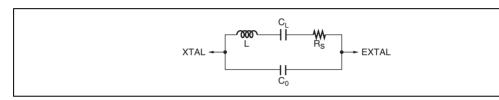

|      | 4.6.1              | Connecting Crystal Resonator                        |  |  |

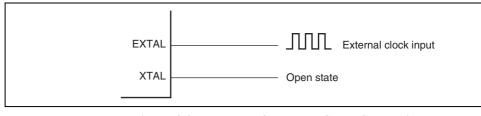

|      | 4.6.2              | External Clock Input Method                         |  |  |

| 4.7  | Functi             | on for Detecting Oscillator Stop                    |  |  |

| 4.8  | Usage              | Notes                                               |  |  |

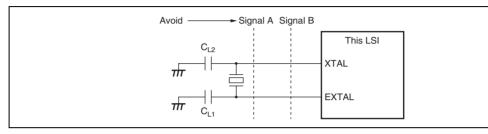

|      | 4.8.1              | Note on Crystal Resonator                           |  |  |

|      | 4.8.2              | Notes on Board Design                               |  |  |

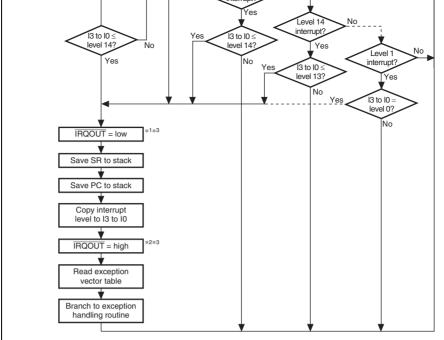

| Sect | ion 5              | Exception Handling                                  |  |  |

| 5.1  |                    | iew                                                 |  |  |

|      | 5.1.1              | Types of Exception Handling and Priority            |  |  |

|      | 5.1.2              | Exception Handling Operations                       |  |  |

|      | 5.1.3              | Exception Handling Vector Table                     |  |  |

| 5.2  | Resets             |                                                     |  |  |

|      | 5.2.1              | Types of Resets                                     |  |  |

|      | 5.2.2              | Power-On Reset                                      |  |  |

|      | 5.2.3              | Manual Reset                                        |  |  |

| 5.3  | Address Errors     |                                                     |  |  |

|      | 5.3.1              | Address Error Sources                               |  |  |

|      | 5.3.2              | Address Error Exception Source                      |  |  |

| 5.4  | Interrupts         |                                                     |  |  |

|      | 5.4.1              | Interrupt Sources                                   |  |  |

|      | 5.4.2              | Interrupt Priority                                  |  |  |

|      | 5.4.3              | Interrupt Exception Handling                        |  |  |

| 5.5  | Excep              | tions Triggered by Instructions                     |  |  |

|      | 5.5.1              | Types of Exceptions Triggered by Instructions       |  |  |

|      | 5.5.2              | Trap Instructions                                   |  |  |

|      |                    |                                                     |  |  |

RENESAS

Rev. 3.00 Jan. 18, 2010 Page viii of xxiv

REJ09B0402-0300

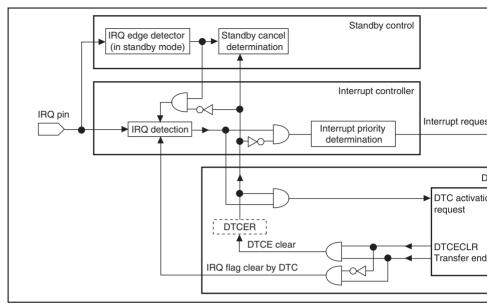

| 6.3 | Regist  | ter Descriptions                                                                         |

|-----|---------|------------------------------------------------------------------------------------------|

|     | 6.3.1   | Interrupt Control Register 0 (ICR0)                                                      |

|     | 6.3.2   | IRQ Control Register (IRQCR)                                                             |

|     | 6.3.3   | IRQ Status register (IRQSR)                                                              |

|     | 6.3.4   | Interrupt Priority Registers A, D to F, and H to M (IPRA, IPRD to IPRF,                  |

|     |         | and IPRH to IPRM)                                                                        |

| 6.4 | Interru | ıpt Sources                                                                              |

|     | 6.4.1   | External Interrupts                                                                      |

|     | 6.4.2   | On-Chip Peripheral Module Interrupts                                                     |

|     | 6.4.3   | User Break Interrupt (SH7136 and SH7137 only)                                            |

| 6.5 | Interru | upt Exception Handling Vector Table                                                      |

| 6.6 | Interru | upt Operation                                                                            |

|     | 6.6.1   | Interrupt Sequence                                                                       |

|     | 6.6.2   | Stack after Interrupt Exception Handling                                                 |

| 6.7 | Interru | upt Response Time                                                                        |

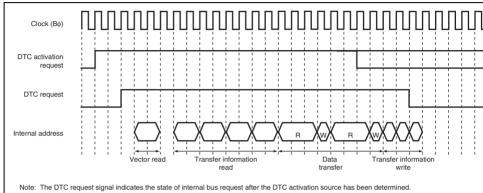

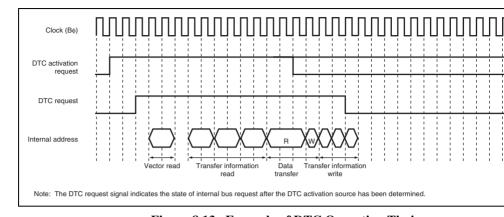

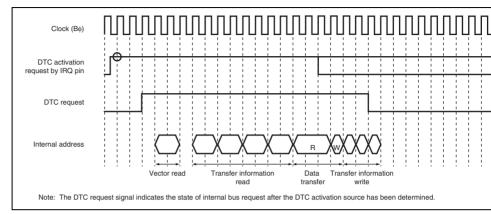

| 6.8 | Data 7  | Fransfer with Interrupt Request Signals                                                  |

|     | 6.8.1   | Handling Interrupt Request Signals as Sources for DTC Activation and CPU Interrupts      |

|     | 6.8.2   | Handling Interrupt Request Signals as Sources for DTC Activation, but Not CPU Interrupts |

|     | 6.8.3   | Handling Interrupt Request Signals as Sources for CPU Interrupts, but Not DTC Activation |

| 6.9 | Usage   | Note                                                                                     |

| 0.7 | Osage   | 1100                                                                                     |

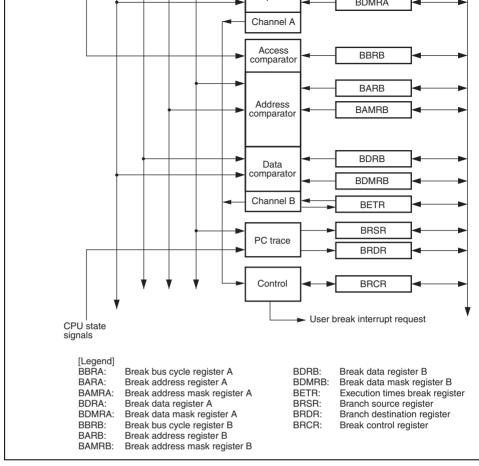

Section 7 User Break Controller (UBC) (SH7136 and SH7137 only) .....

Features.....

Input/Output Pins.....

RENESAS

Rev. 3.00 Jan. 18, 2010 Page 1

REJ09

Features....

Input/Output Pins .....

6.1

6.2

7.1

7.2

|            | 7.3.12                                                                            | Execution Times Break Register (BETR)                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 7.3.13                                                                            | Branch Source Register (BRSR)                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                                                                                   | Branch Destination Register (BRDR)                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.4        |                                                                                   | on                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | 7.4.1                                                                             | Flow of the User Break Operation                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | 7.4.2                                                                             | User Break on Instruction Fetch Cycle                                                                                                                                                                                                                                                                                                                                                                                                    |

|            | 7.4.3                                                                             | Break on Data Access Cycle                                                                                                                                                                                                                                                                                                                                                                                                               |

|            | 7.4.4                                                                             | Sequential Break                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | 7.4.5                                                                             | Value of Saved Program Counter                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | 7.4.6                                                                             | PC Trace                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 7.4.7                                                                             | Usage Examples                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.5        | Usage 1                                                                           | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|            |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Sect       | ion 8                                                                             | Data Transfer Controller (DTC)                                                                                                                                                                                                                                                                                                                                                                                                           |

| Sect       |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            | Feature                                                                           | r Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8.1        | Feature                                                                           | r Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8.1        | Feature<br>Registe                                                                | DTC Mode Register A (MRA)                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.1        | Feature<br>Registe<br>8.2.1                                                       | DTC Mode Register B (MRB)                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.1        | Feature<br>Registe<br>8.2.1<br>8.2.2                                              | DTC Mode Register A (MRA)                                                                                                                                                                                                                                                                                                                                                                                                                |

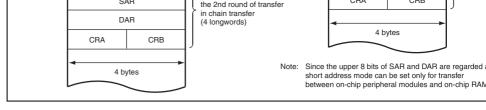

| 8.1        | Feature<br>Registe<br>8.2.1<br>8.2.2<br>8.2.3                                     | DTC Mode Register A (MRA)  DTC Mode Register B (MRB)  DTC Source Address Register (SAR).  DTC Destination Address Register (DAR).  DTC Transfer Count Register A (CRA).                                                                                                                                                                                                                                                                  |

| 8.1        | Feature<br>Registe<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4                            | DTC Mode Register A (MRA)  DTC Mode Register B (MRB)  DTC Source Address Register (SAR).  DTC Destination Address Register (DAR).  DTC Transfer Count Register A (CRA).                                                                                                                                                                                                                                                                  |

| 8.1        | Feature<br>Registe<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5                   | DTC Mode Register A (MRA)                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.1        | Feature<br>Register<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6         | DTC Mode Register A (MRA)  DTC Mode Register B (MRB)  DTC Source Address Register (SAR)  DTC Destination Address Register (DAR)  DTC Transfer Count Register A (CRA)  DTC Transfer Count Register B (CRB)  DTC Enable Registers A to E (DTCERA to DTCERE)  DTC Control Register (DTCCR)                                                                                                                                                  |

| 8.1        | Feature<br>Registe<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7 | DTC Mode Register A (MRA)  DTC Mode Register B (MRB)  DTC Source Address Register (SAR)  DTC Destination Address Register (DAR)  DTC Transfer Count Register A (CRA)  DTC Transfer Count Register B (CRB)  DTC Enable Registers A to E (DTCERA to DTCERE)  DTC Control Register (DTCCR)                                                                                                                                                  |

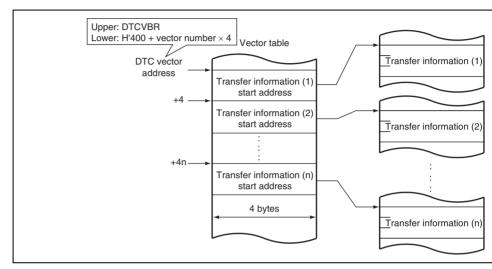

| 8.1        | Register 8.2.1 8.2.2 8.2.3 8.2.4 8.2.5 8.2.6 8.2.7 8.2.8 8.2.9 8.2.10             | DTC Mode Register A (MRA)  DTC Mode Register B (MRB)  DTC Source Address Register (SAR)  DTC Destination Address Register (DAR)  DTC Transfer Count Register A (CRA)  DTC Transfer Count Register B (CRB)  DTC Enable Registers A to E (DTCERA to DTCERE)  DTC Control Register (DTCCR)  DTC Vector Base Register (DTCVBR)  Bus Function Extending Register (BSCEHR)                                                                     |

| 8.1<br>8.2 | Register 8.2.1 8.2.2 8.2.3 8.2.4 8.2.5 8.2.6 8.2.7 8.2.8 8.2.9 8.2.10 Activat     | Data Transfer Controller (DTC)  SS.  DTC Descriptions  DTC Mode Register A (MRA)  DTC Mode Register B (MRB)  DTC Source Address Register (SAR)  DTC Destination Address Register (DAR)  DTC Transfer Count Register A (CRA)  DTC Transfer Count Register B (CRB)  DTC Enable Registers A to E (DTCERA to DTCERE)  DTC Control Register (DTCCR)  DTC Vector Base Register (DTCVBR)  Bus Function Extending Register (BSCEHR)  ion Sources |

| 8.1        | Register 8.2.1 8.2.2 8.2.3 8.2.4 8.2.5 8.2.6 8.2.7 8.2.8 8.2.9 8.2.10 Activat     | DTC Mode Register A (MRA)  DTC Mode Register B (MRB)  DTC Source Address Register (SAR)  DTC Destination Address Register (DAR)  DTC Transfer Count Register A (CRA)  DTC Transfer Count Register B (CRB)  DTC Enable Registers A to E (DTCERA to DTCERE)  DTC Control Register (DTCCR)  DTC Vector Base Register (DTCVBR)  Bus Function Extending Register (BSCEHR)                                                                     |

Rev. 3.00 Jan. 18, 2010 Page x of xxiv

REJ09B0402-0300

7.3.11 Break Control Register (BRCR)

RENESAS

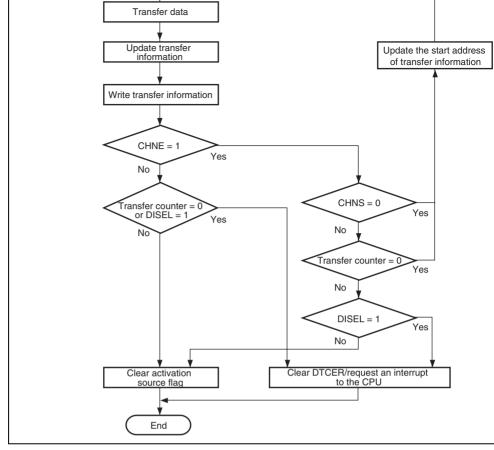

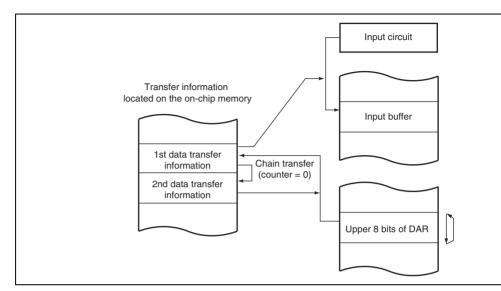

|       | 8.7.2   | Chain Transfer when Counter = 0                                      |

|-------|---------|----------------------------------------------------------------------|

| 8.8   | Interru | pt Sources                                                           |

| 8.9   | Usage   | Notes                                                                |

|       | 8.9.1   | Module Standby Mode Setting                                          |

|       | 8.9.2   | On-Chip RAM                                                          |

|       | 8.9.3   | DTCE Bit Setting                                                     |

|       | 8.9.4   | Chain Transfer                                                       |

|       | 8.9.5   | Transfer Information Start Address, Source Address, and Destination  |

|       |         | Address                                                              |

|       | 8.9.6   | Access to DTC Registers through DTC                                  |

|       | 8.9.7   | Notes on IRQ Interrupt as DTC Activation Source                      |

|       | 8.9.8   | Notes on SCI as DTC Activation Sources                               |

|       | 8.9.9   | Clearing Interrupt Source Flag                                       |

|       | 8.9.10  | Conflict between NMI Interrupt and DTC Activation                    |

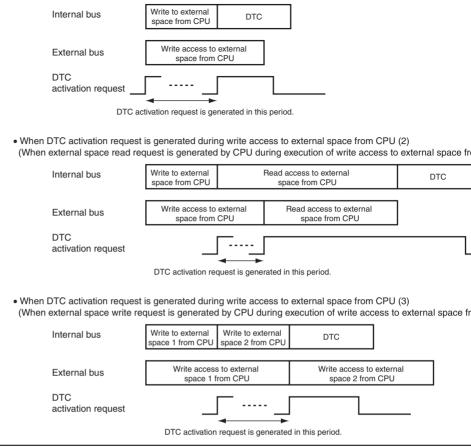

|       | 8.9.11  | Operation When a DTC Activation Request is Cancelled While in Progre |

|       |         |                                                                      |

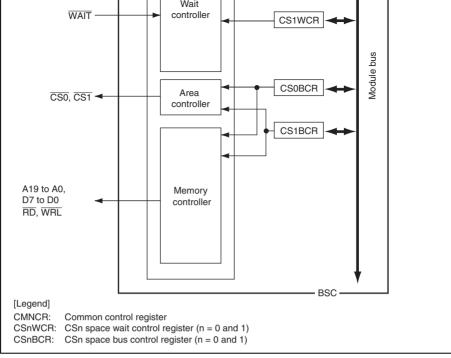

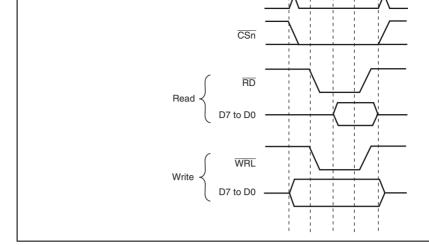

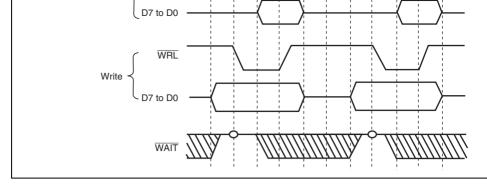

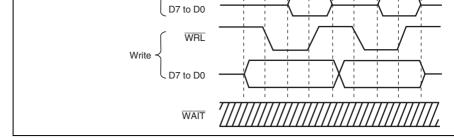

| Secti | ion 9   | Bus State Controller (BSC)                                           |

| 9.1   | Feature | es                                                                   |

| 9.2   | Input/C | Output Pins                                                          |

| 9.3   | Area O  | verview                                                              |

|       | 9.3.1   | Area Division                                                        |

|       |         |                                                                      |

Chain Transfer when Counter = 0

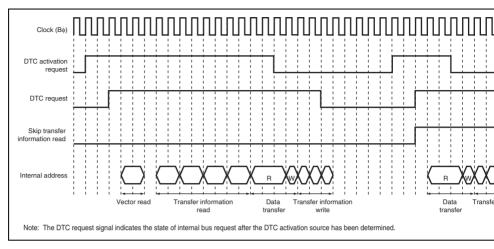

DTC Activation by Interrupt.....

Examples of Use of the DTC.....

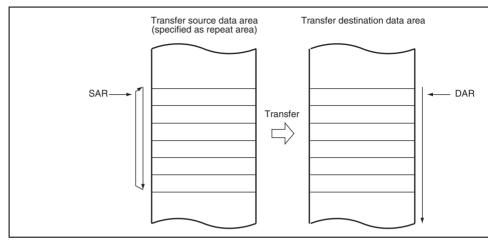

Normal Transfer Mode

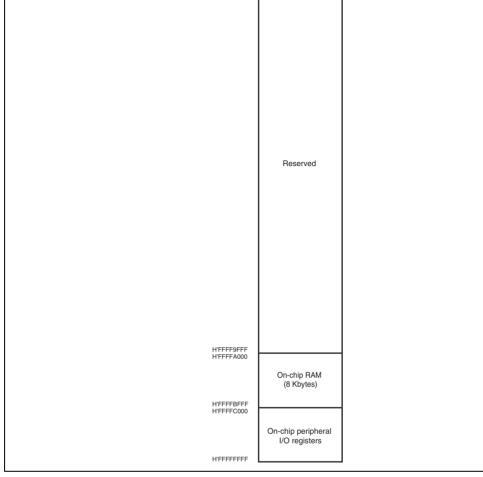

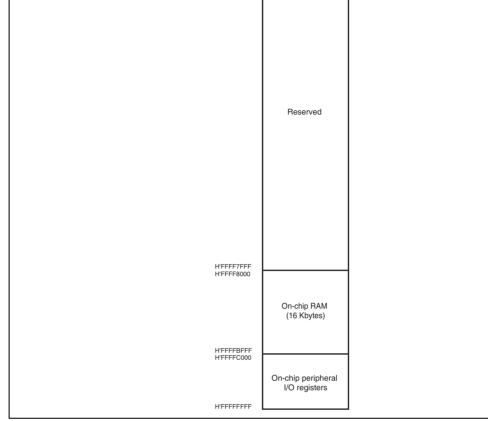

Address Map.....

Common Control Register (CMNCR)

CSn Space Bus Control Register (CSnBCR) (n = 0 and 1).....

CSn Space Wait Control Register (CSnWCR) (n = 0 and 1).....

RENESAS

Rev. 3.00 Jan. 18, 2010 Page 1

REJ09

Register Descriptions

8.6

8.7

872

9.3.2

9.4.1

9.4.2

9.4.3

9.4

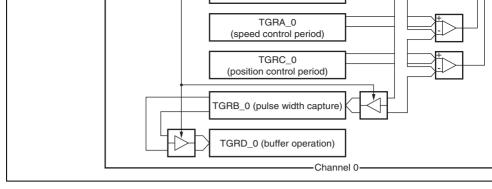

| Sect | ion 10 | Multi-Function Timer Pulse Unit 2 (MTU2)                   |

|------|--------|------------------------------------------------------------|

|      |        | S                                                          |

| 10.2 |        | output Pins                                                |

| 10.3 |        | r Descriptions                                             |

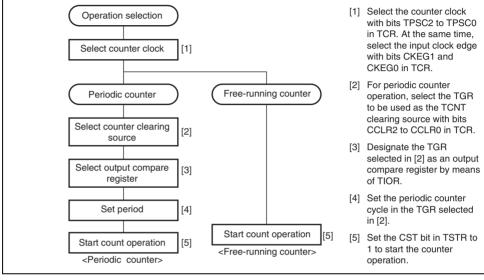

|      | -      | Timer Control Register (TCR)                               |

|      |        | Timer Mode Register (TMDR)                                 |

|      |        | Timer I/O Control Register (TIOR)                          |

|      |        | Timer Compare Match Clear Register (TCNTCMPCLR)            |

|      | 10.3.5 | Timer Interrupt Enable Register (TIER)                     |

|      |        | Timer Status Register (TSR)                                |

|      |        | Timer Buffer Operation Transfer Mode Register (TBTM)       |

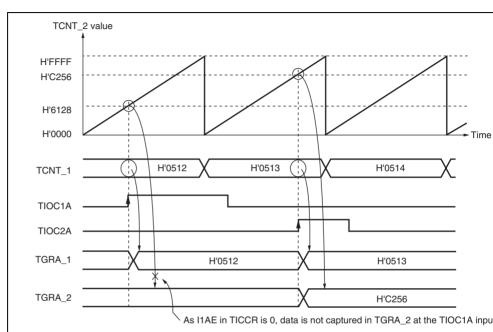

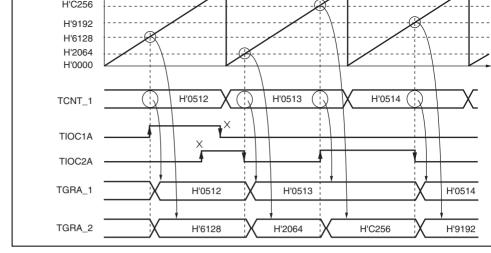

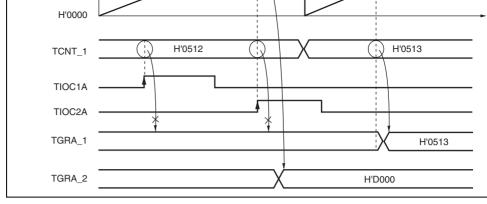

|      |        | Timer Input Capture Control Register (TICCR)               |

|      |        | Timer Synchronous Clear Register (TSYCR)                   |

|      |        | Timer A/D Converter Start Request Control Register (TADCR) |

10.3.11 Timer A/D Converter Start Request Cycle Set Registers

10.3.12 Timer A/D Converter Start Request Cycle Set Buffer Registers

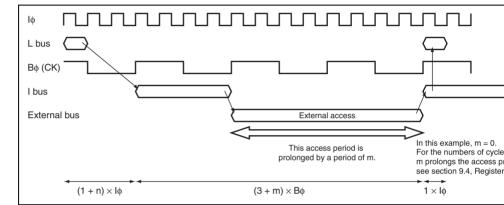

9.5.10 Access to External Memory by CPU .....

RENESAS

(TADCORA\_4 and TADCORB\_4).....

(TADCOBRA 4 and TADCOBRB 4) .....

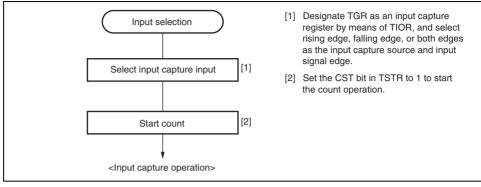

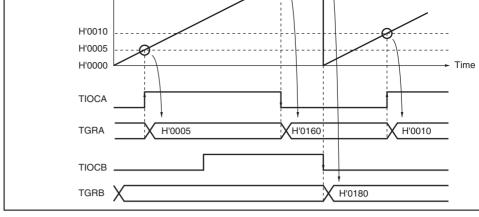

|      | 10.4.1 Basic Functions                                                     |

|------|----------------------------------------------------------------------------|

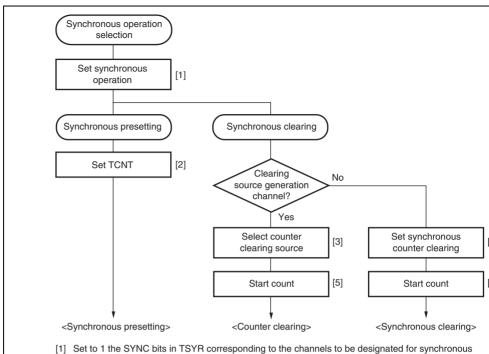

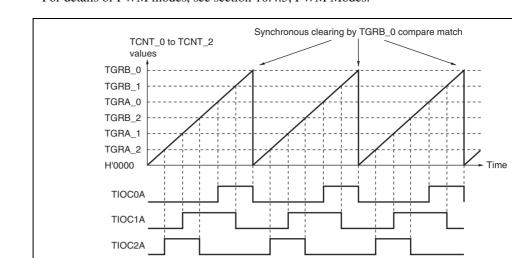

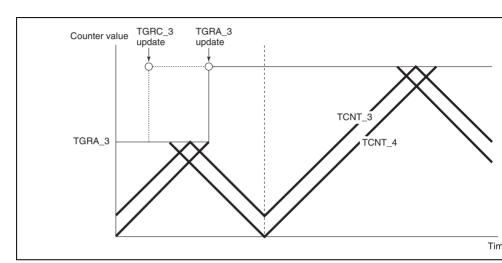

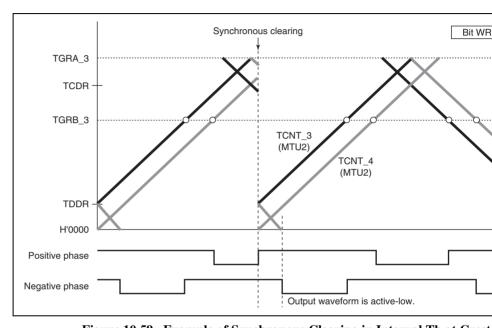

|      | 10.4.2 Synchronous Operation                                               |

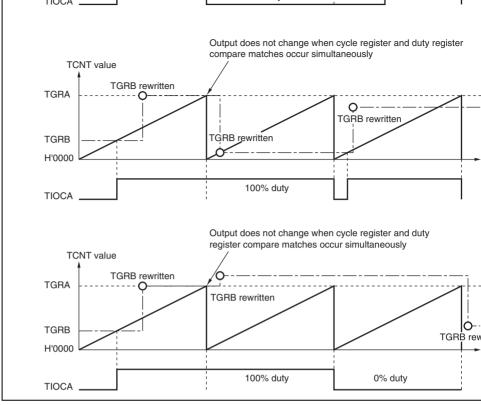

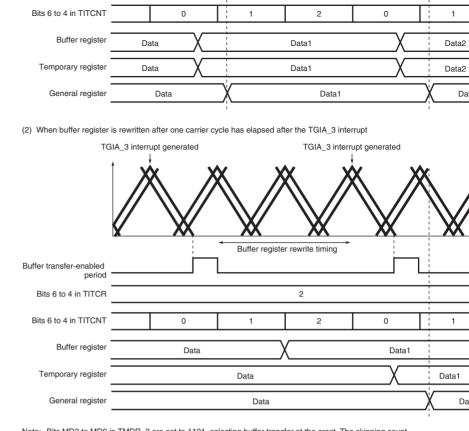

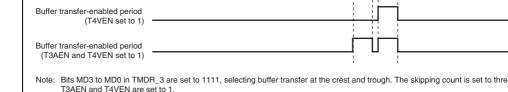

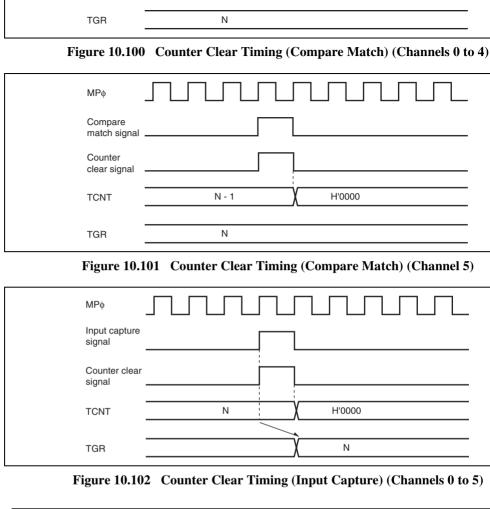

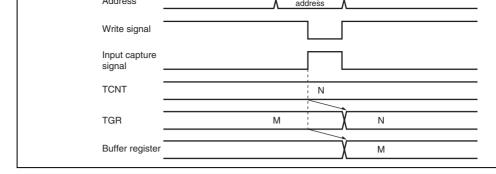

|      | 10.4.3 Buffer Operation                                                    |

|      | 10.4.4 Cascaded Operation                                                  |

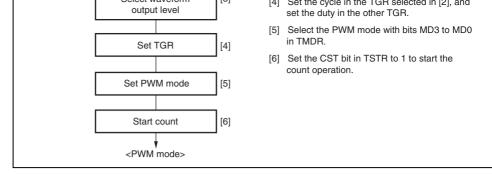

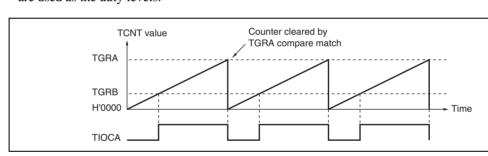

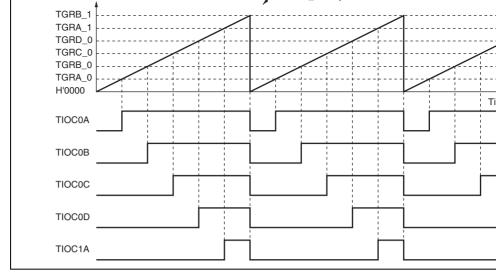

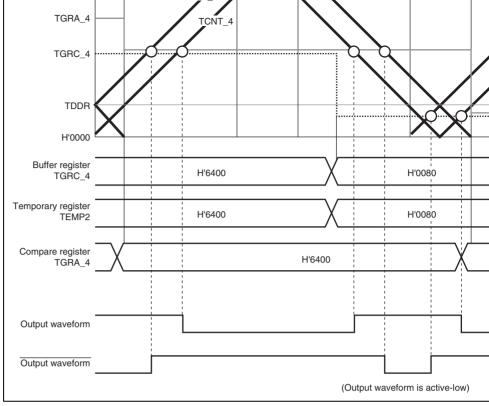

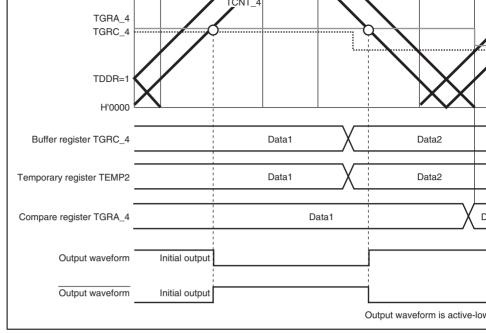

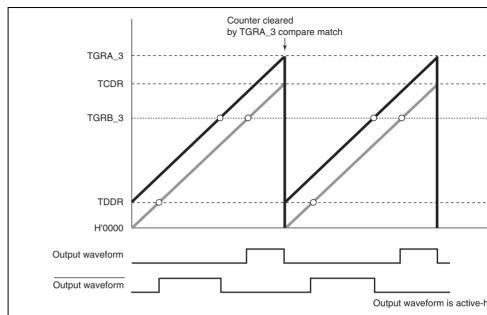

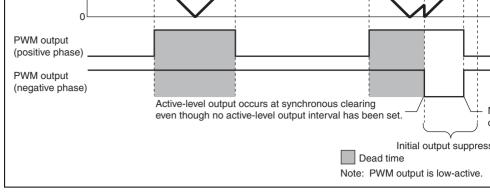

|      | 10.4.5 PWM Modes                                                           |

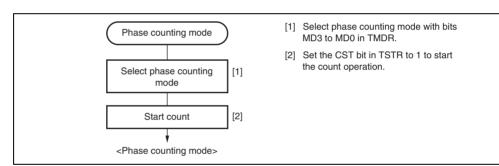

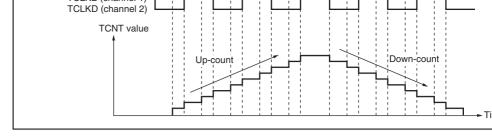

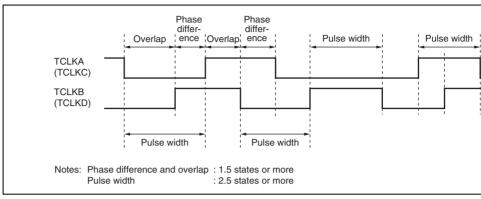

|      | 10.4.6 Phase Counting Mode                                                 |

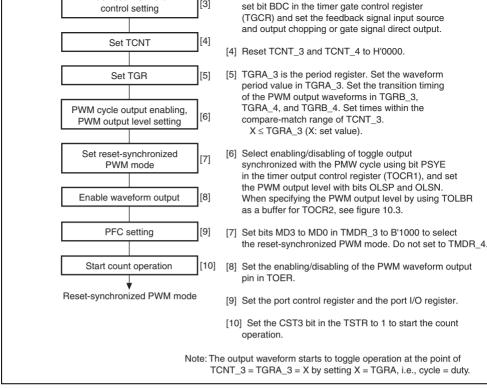

|      | 10.4.7 Reset-Synchronized PWM Mode                                         |

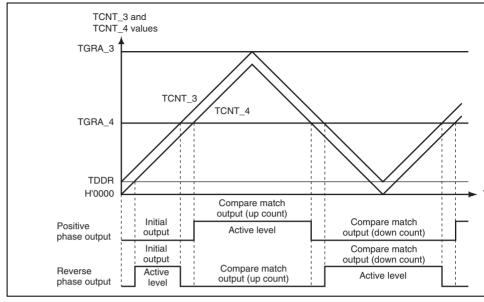

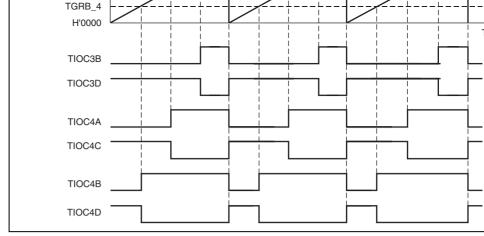

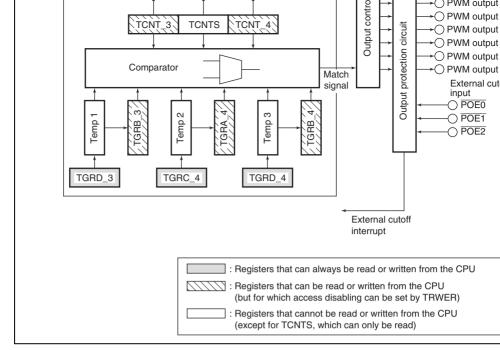

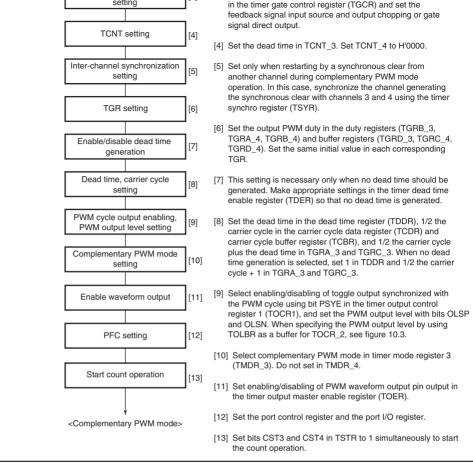

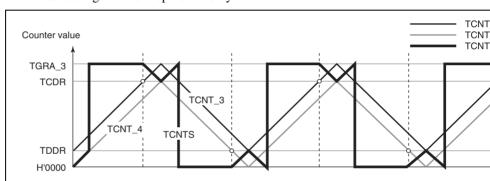

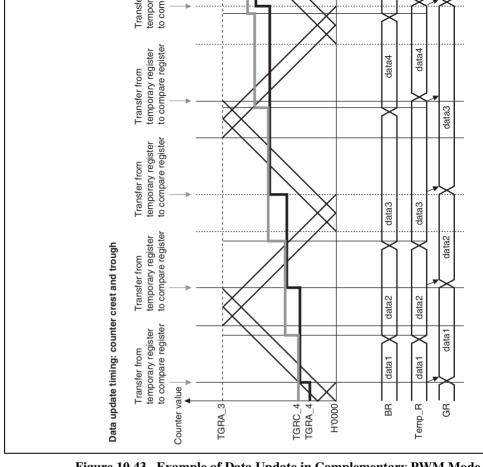

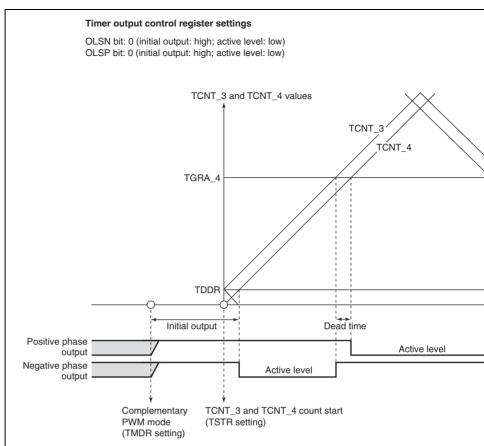

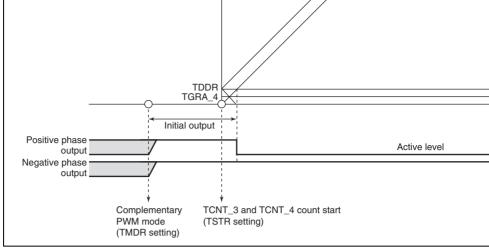

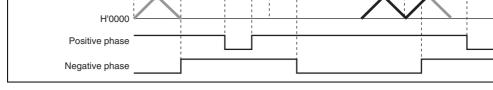

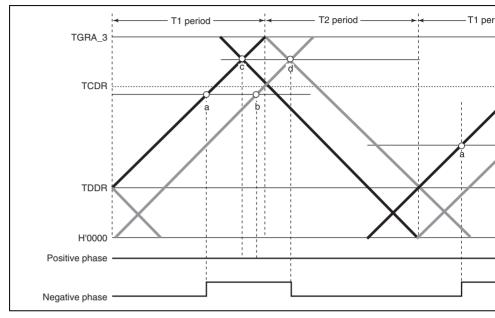

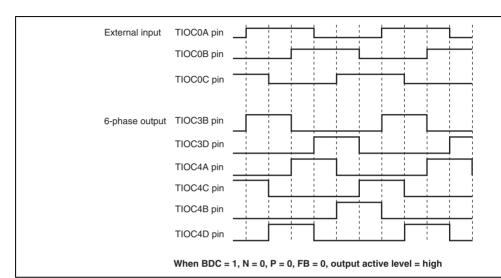

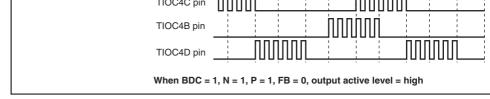

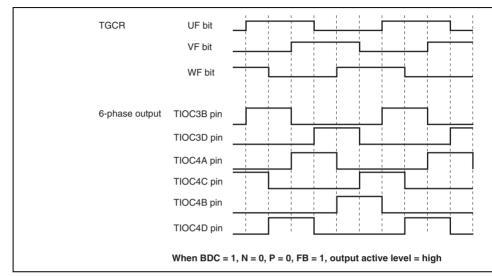

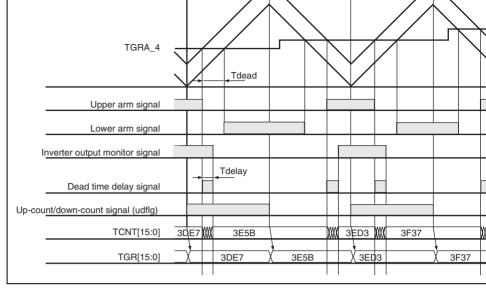

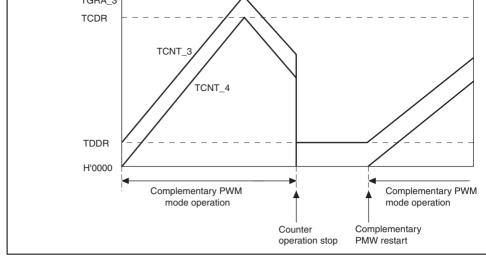

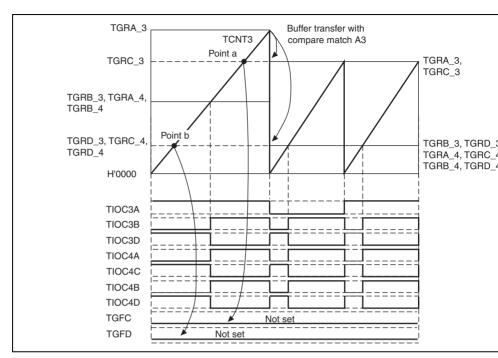

|      | 10.4.8 Complementary PWM Mode                                              |

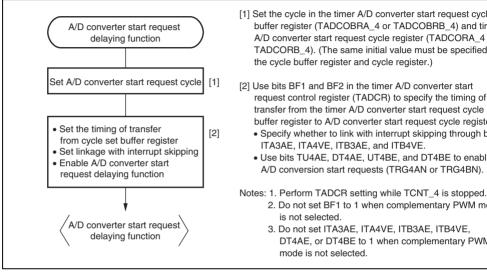

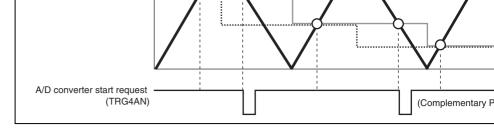

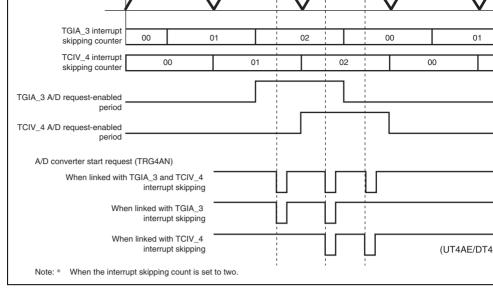

|      | 10.4.9 A/D Converter Start Request Delaying Function                       |

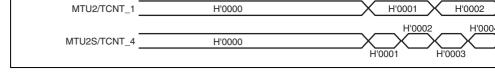

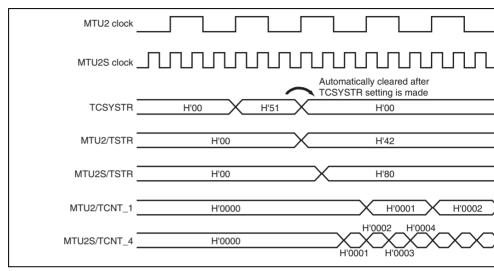

|      | 10.4.10 MTU2–MTU2S Synchronous Operation                                   |

|      | 10.4.11 External Pulse Width Measurement                                   |

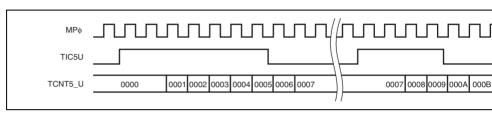

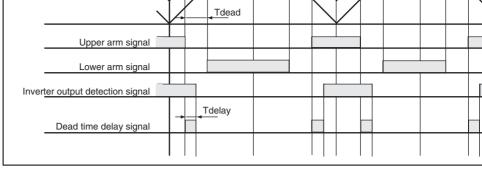

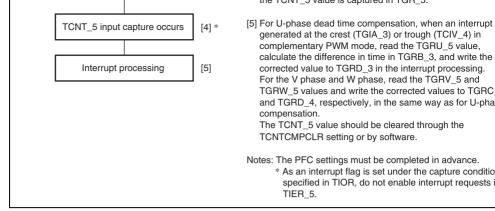

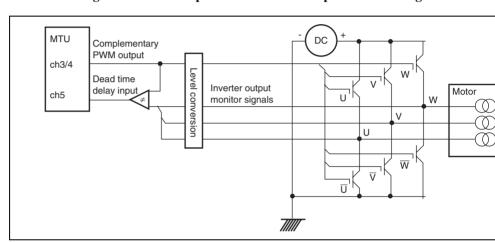

|      | 10.4.12 Dead Time Compensation                                             |

|      | 10.4.13 TCNT Capture at Crest and/or Trough in Complementary PWM Operation |

| 10.5 | Interrupt Sources                                                          |

|      | 10.5.1 Interrupt Sources and Priorities                                    |

|      | 10.5.2 DTC Activation                                                      |

|      | 10.5.3 A/D Converter Activation                                            |

| 10.6 | Operation Timing                                                           |

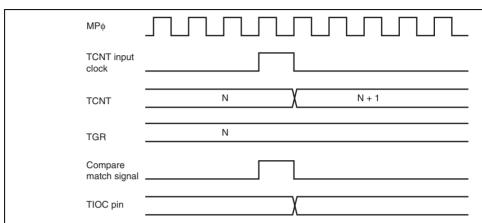

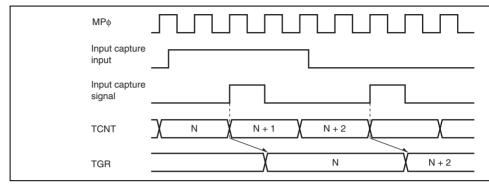

|      | 10.6.1 Input/Output Timing                                                 |

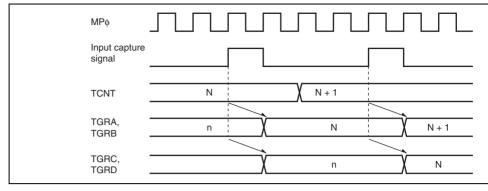

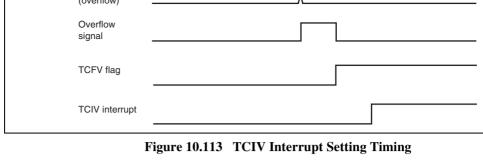

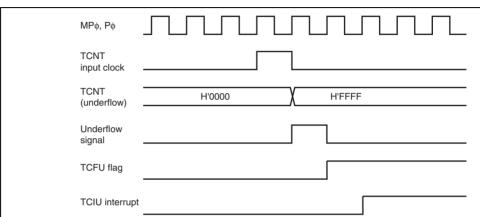

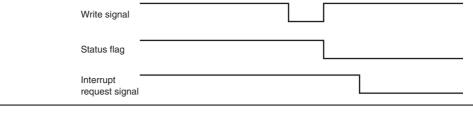

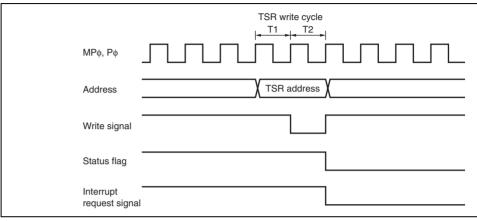

|      | 10.6.2 Interrupt Signal Timing                                             |

| 10.7 | Usage Notes                                                                |

|      | 10.7.1 Module Standby Mode Setting                                         |

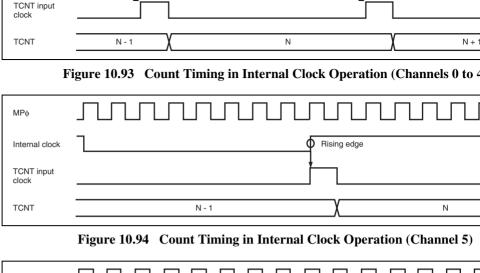

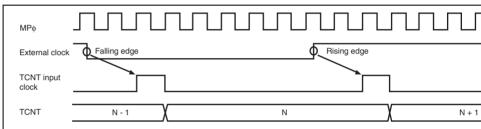

|      | 10.7.2 Input Clock Restrictions                                            |

|      | 10.7.3 Caution on Period Setting                                           |

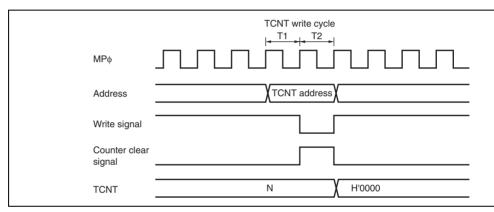

|      | 10.7.4 Contention between TCNT Write and Clear Operations                  |

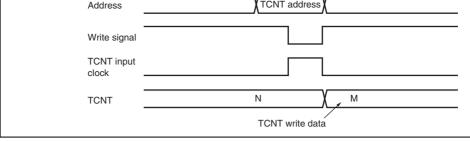

|      | 10.7.5 Contention between TCNT Write and Increment Operations              |

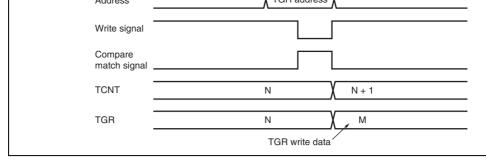

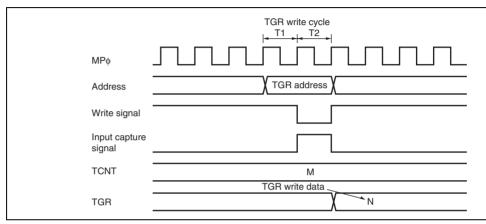

|      | 10.7.6 Contention between TGR Write and Compare Match                      |

|      |                                                                            |

10.3.33 Bus Master Interface

RENESAS

Rev. 3.00 Jan. 18, 2010 Pa

REJ09

10.4 Operation .....

|      | 10.7.20 | Output Level in Complementary PWM Mode and Reset-Synchronized         |

|------|---------|-----------------------------------------------------------------------|

|      |         | PWM Mode                                                              |

|      | 10.7.21 | Interrupts in Module Standby Mode                                     |

|      | 10.7.22 | Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       |

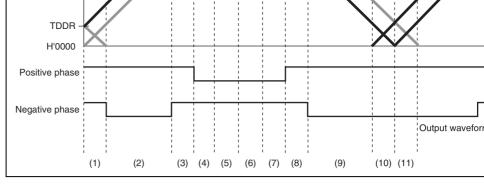

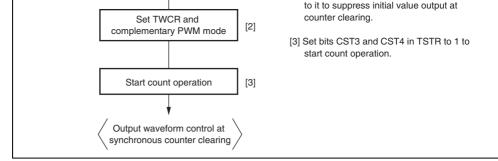

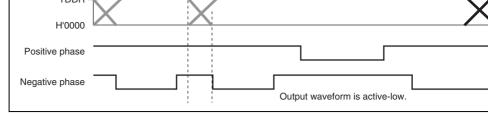

|      | 10.7.23 | Notes on Output Waveform Control During Synchronous Counter           |

|      |         | Clearing in Complementary PWM Mode                                    |

| 10.8 | MTU2    | Output Pin Initialization                                             |

|      | 10.8.1  | Operating Modes                                                       |

|      | 10.8.2  | Reset Start Operation                                                 |

|      | 10.8.3  | Operation in Case of Re-Setting Due to Error During Operation, etc    |

|      | 10.8.4  | Overview of Initialization Procedures and Mode Transitions in Case of |

|      |         | Error during Operation, etc.                                          |

Section 11 Multi-Function Timer Pulse Unit 2S (MTU2S)..... Input/Output Pins..... Register Descriptions

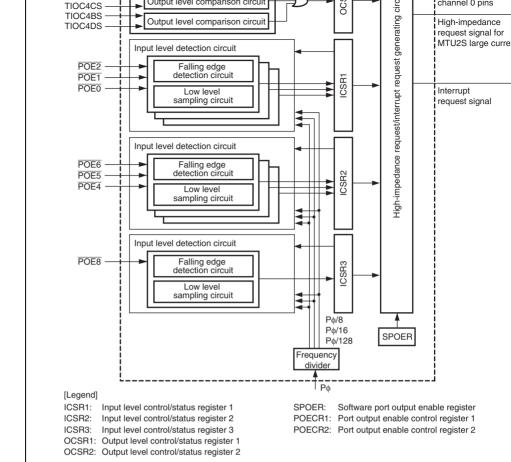

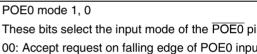

Section 12 Port Output Enable (POE)..... Features

Input/Output Pins.....

Register Descriptions

12.3.3 Input Level Control/Status Register 2 (ICSR2)..... 12.3.4 Output Level Control/Status Register 2 (OCSR2).....

10.7.18 Contention between TCNT Write and Overflow/Underflow..... 10.7.19 Cautions on Transition from Normal Operation or PWM Mode 1 to

Reset-Synchronized PWM Mode .....

### 12.3.1 Input Level Control/Status Register 1 (ICSR1)..... Output Level Control/Status Register 1 (OCSR1).....

12.2

12.3

12.3.5 Input Level Control/Status Register 3 (ICSR3).....

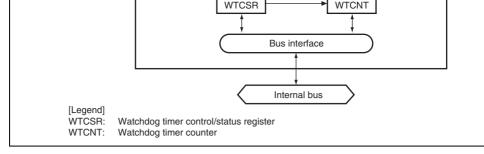

| 13.2  | Input/C               | Input/Output Pin for WDT                       |  |  |  |  |

|-------|-----------------------|------------------------------------------------|--|--|--|--|

| 13.3  | Register Descriptions |                                                |  |  |  |  |

|       | _                     | Watchdog Timer Counter (WTCNT)                 |  |  |  |  |

|       |                       | Watchdog Timer Control/Status Register (WTCSR) |  |  |  |  |

|       |                       | Notes on Register Access                       |  |  |  |  |

| 13.4  |                       | on                                             |  |  |  |  |

|       |                       | Revoking Software Standbys                     |  |  |  |  |

|       |                       | Using Watchdog Timer Mode                      |  |  |  |  |

|       |                       | Using Interval Timer Mode                      |  |  |  |  |

| 13.5  |                       | ot Source                                      |  |  |  |  |

|       |                       | Note                                           |  |  |  |  |

|       | _                     | WTCNT Setting Value                            |  |  |  |  |

|       |                       | C                                              |  |  |  |  |

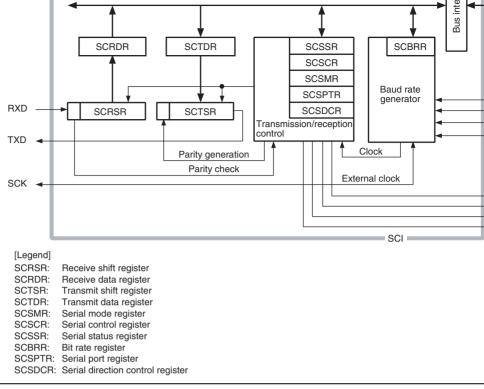

| Secti | ion 14                | Serial Communication Interface (SCI)           |  |  |  |  |

| 14.1  |                       | 28                                             |  |  |  |  |

| 14.2  |                       | Output Pins                                    |  |  |  |  |

|       |                       | r Descriptions                                 |  |  |  |  |

| 1     |                       | Receive Shift Register (SCRSR)                 |  |  |  |  |

|       | 1                     | 110001.0 5111011051001 (5 611511)              |  |  |  |  |

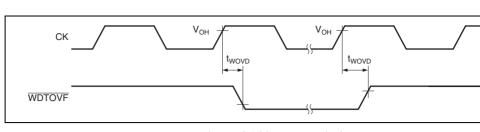

Section 13 Watchdog Timer (WDT)..... Features

14.3.2 Receive Data Register (SCRDR)..... 14.3.3 Transmit Shift Register (SCTSR)..... 14.3.4 Transmit Data Register (SCTDR)..... 14.3.5 Serial Mode Register (SCSMR)..... 14.3.6 Serial Control Register (SCSCR)..... 14.3.7 Serial Status Register (SCSSR)..... 14.3.8 Serial Port Register (SCSPTR).....

REJ09

Rev. 3.00 Jan. 18, 2010 Pa

|      | 14.7.2    | Multiple Receive Error Occurrence                                  |

|------|-----------|--------------------------------------------------------------------|

|      | 14.7.3    | Break Detection and Processing                                     |

|      | 14.7.4    | Sending a Break Signal                                             |

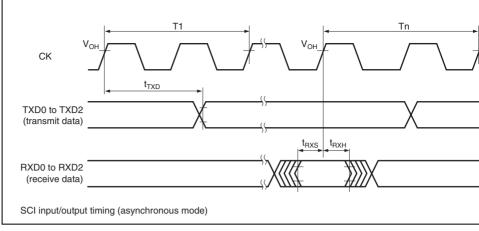

|      | 14.7.5    | Receive Data Sampling Timing and Receive Margin (Asynchronous Mode |

|      | 14.7.6    | Note on Using DTC                                                  |

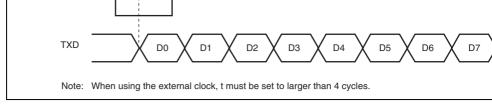

|      | 14.7.7    | Note on Using External Clock in Clock Synchronous Mode             |

|      | 14.7.8    | Module Standby Mode Setting                                        |

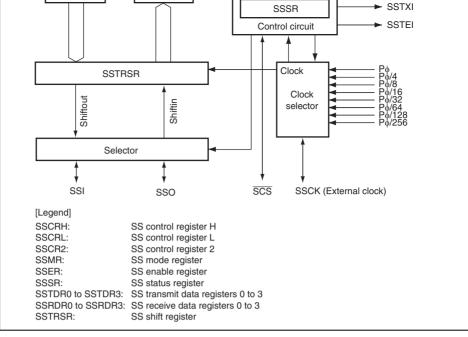

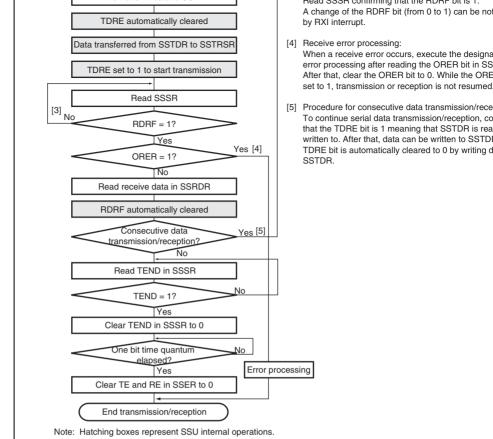

| Sec  | tion 15   | Synchronous Serial Communication Unit (SSU)                        |

| 15.1 |           | 28                                                                 |

| 15.2 | . Input/C | Output Pins                                                        |

| 15.3 | Registe   | er Descriptions                                                    |

|      | 15.3.1    | SS Control Register H (SSCRH)                                      |

|      | 15.3.2    | SS Control Register L (SSCRL)                                      |

|      | 15.3.3    | SS Mode Register (SSMR)                                            |

|      | 15.3.4    | SS Enable Register (SSER)                                          |

|      | 15.3.5    | SS Status Register (SSSR)                                          |

|      | 15.3.6    | SS Control Register 2 (SSCR2)                                      |

|      | 15.3.7    | SS Transmit Data Registers 0 to 3 (SSTDR0 to SSTDR3)               |

|      | 15.3.8    | SS Receive Data Registers 0 to 3 (SSRDR0 to SSRDR3)                |

|      | 15.3.9    | SS Shift Register (SSTRSR)                                         |

| 15.4 |           | ion                                                                |

|      | 15.4.1    | Transfer Clock                                                     |

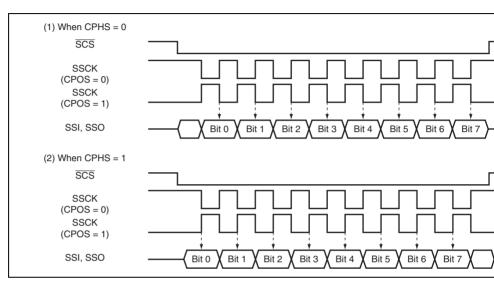

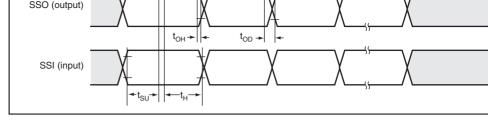

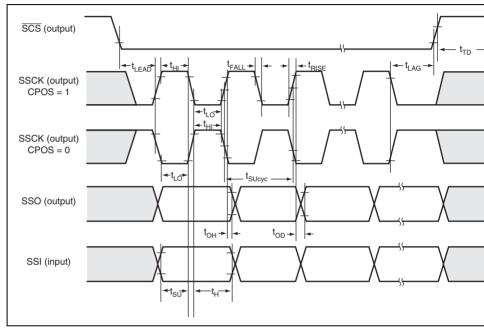

|      | 15.4.2    | Relationship of Clock Phase, Polarity, and Data                    |

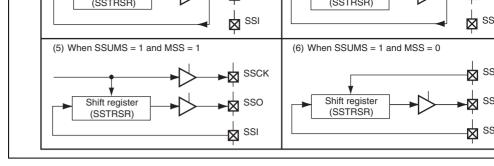

|      | 15.4.3    | Relationship between Data Input/Output Pins and Shift Register     |

|      | 15.4.4    | Communication Modes and Pin Functions                              |

|      |           | SSU Mode                                                           |

|      | 15.4.6    | SCS Pin Control and Conflict Error                                 |

|      | 15 / 7    | Clock Synchronous Communication Mode                               |

RENESAS

Rev. 3.00 Jan. 18, 2010 Page xvi of xxiv

REJ09B0402-0300

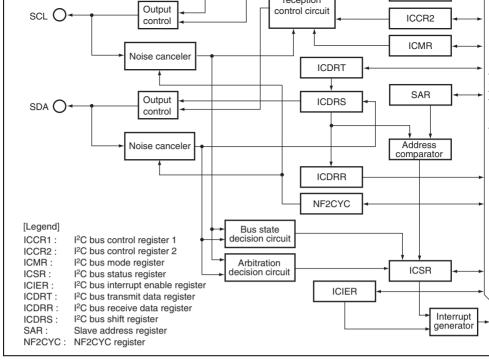

|      | 16.3.1 I'C Bus Control Register 1 (ICCR1)                           |

|------|---------------------------------------------------------------------|

|      | 16.3.2 I <sup>2</sup> C Bus Control Register 2 (ICCR2)              |

|      | 16.3.3 I <sup>2</sup> C Bus Mode Register (ICMR)                    |

|      | 16.3.4 I <sup>2</sup> C Bus Interrupt Enable Register (ICIER)       |

|      | 16.3.5 I <sup>2</sup> C Bus Status Register (ICSR)                  |

|      | 16.3.6 I <sup>2</sup> C Bus Slave Address Register (SAR)            |

|      | 16.3.7 I <sup>2</sup> C Bus Transmit Data Register (ICDRT)          |

|      | 16.3.8 I <sup>2</sup> C Bus Receive Data Register (ICDRR)           |

|      | 16.3.9 I <sup>2</sup> C Bus Shift Register (ICDRS)                  |

|      | 16.3.10 NF2CYC Register (NF2CYC)                                    |

| 16.4 | Operation                                                           |

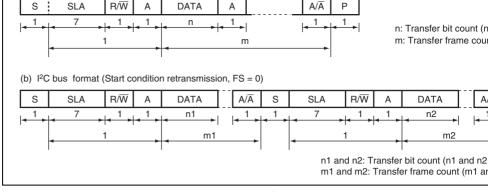

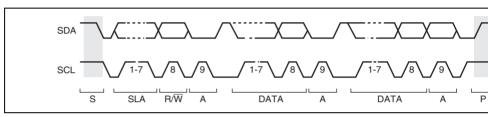

|      | 16.4.1 I <sup>2</sup> C Bus Format                                  |

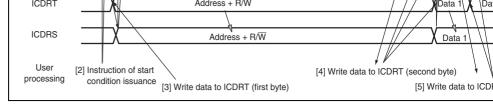

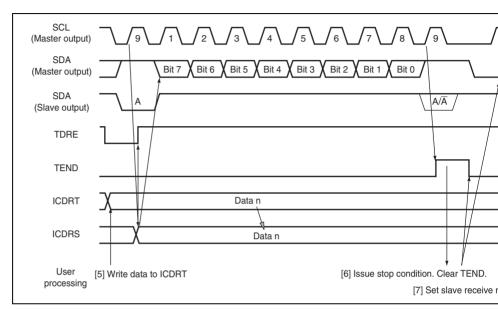

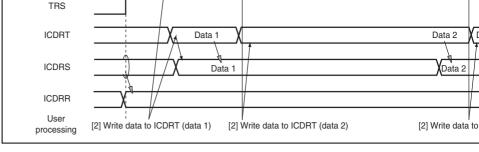

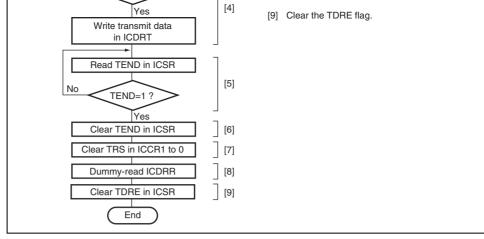

|      | 16.4.2 Master Transmit Operation                                    |

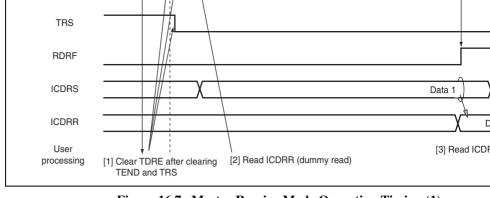

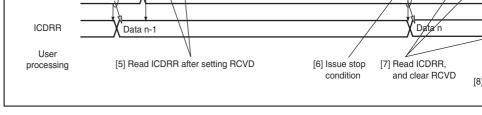

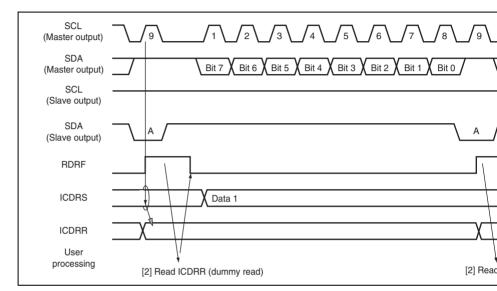

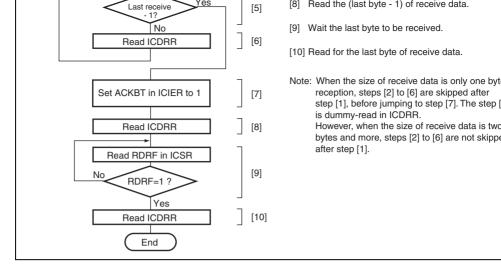

|      | 16.4.3 Master Receive Operation                                     |

|      | 16.4.4 Slave Transmit Operation                                     |

|      | 16.4.5 Slave Receive Operation                                      |

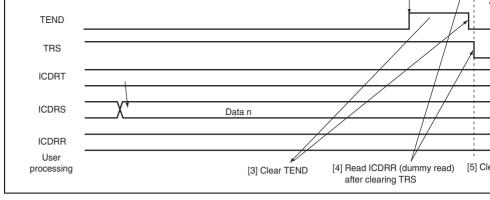

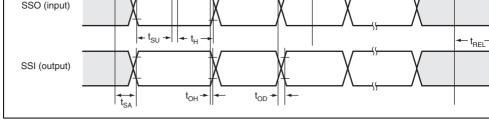

|      | 16.4.6 Clock Synchronous Serial Format                              |

|      | 16.4.7 Noise Filter                                                 |

|      | 16.4.8 Example of Use                                               |

| 16.5 | I <sup>2</sup> C2 Interrupt Sources                                 |

| 16.6 | Operation Using the DTC                                             |

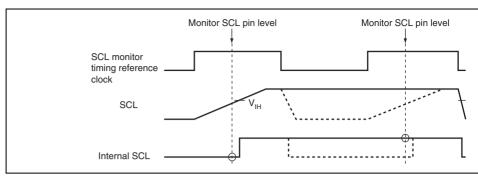

| 16.7 | Bit Synchronous Circuit                                             |

| 16.8 | Usage Note                                                          |

|      | 16.8.1 Module Standby Mode Setting                                  |

|      | 16.8.2 Issuance of Stop Condition and Repeated Start Condition      |

|      | 16.8.3 Issuance of a Start Condition and Stop Condition in Sequence |

|      | 16.8.4 Settings for Multi-Master Operation                          |

16.2 Input/Output Pins.....

16.3 Register Descriptions

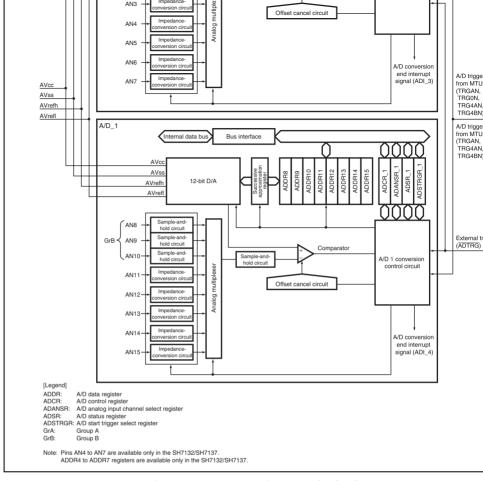

|       | 17.4.1  | Single-Cycle Scan Mode                                          |

|-------|---------|-----------------------------------------------------------------|

|       |         | Continuous Scan Mode                                            |

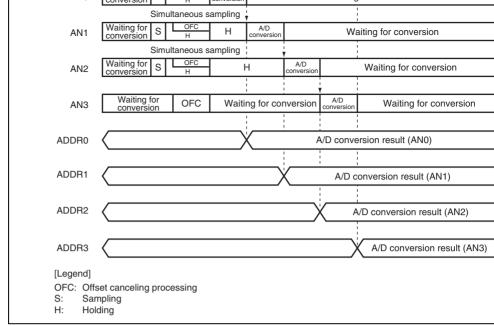

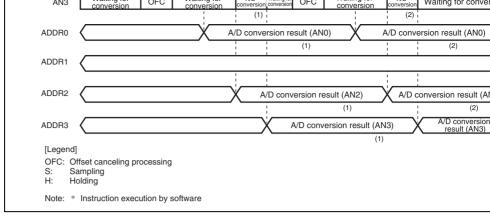

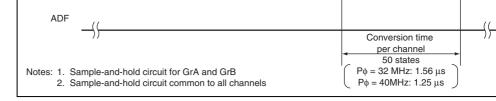

|       | 17.4.3  | Input Sampling and A/D Conversion Time                          |

|       | 17.4.4  | A/D Converter Activation by MTU2 and MTU2S                      |

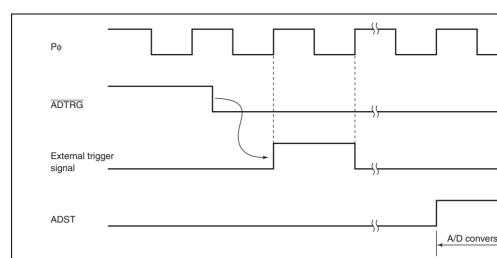

|       | 17.4.5  | External Trigger Input Timing                                   |

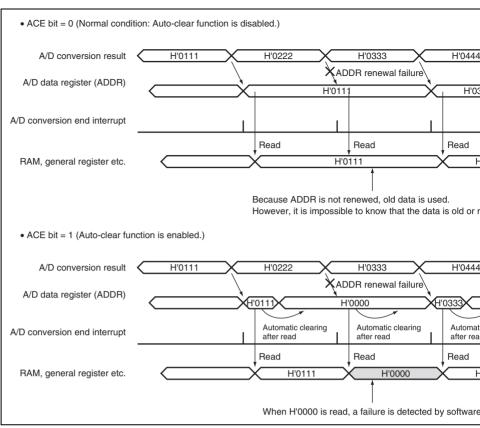

|       |         | Example of ADDR Auto-Clear Function                             |

| 17.5  |         | pt Sources and DTC Transfer Requests                            |

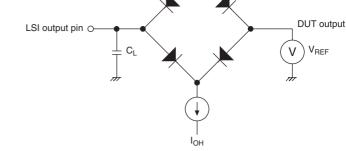

|       | -       | ions of A/D Conversion Accuracy                                 |

| 17.7  |         | Notes                                                           |

|       |         | Analog Input Voltage Range                                      |

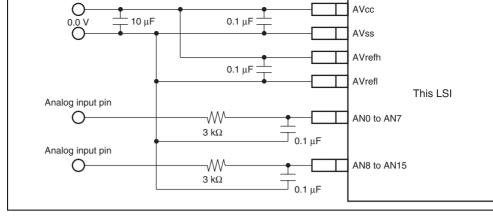

|       |         | Relationship between AVcc, AVss and Vcc, Vss                    |

|       | 17.7.3  | Range of AV <sub>reft</sub> and AV <sub>reft</sub> Pin Settings |

|       |         | Notes on Board Design                                           |

|       |         | Notes on Noise Countermeasures                                  |

|       | 17.7.6  | Notes on Register Setting                                       |

|       |         |                                                                 |

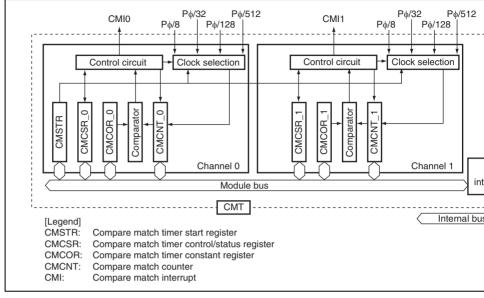

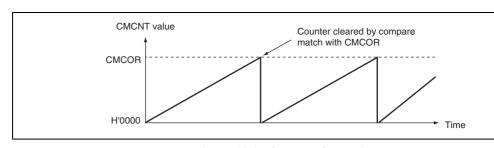

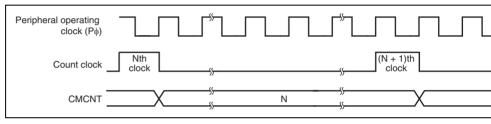

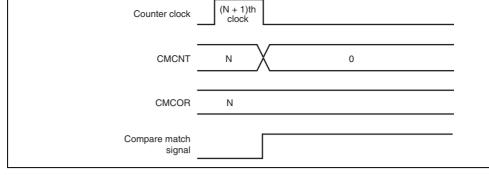

| Secti | ion 18  | Compare Match Timer (CMT)                                       |

|       |         | 28                                                              |

| 18.2  | Registe | er Descriptions                                                 |

|       | 18.2.1  | Compare Match Timer Start Register (CMSTR)                      |

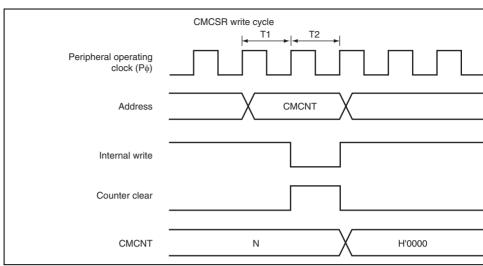

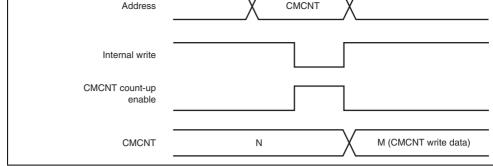

|       |         | Compare Match Timer Control/Status Register (CMCSR)             |

|       |         | Compare Match Counter (CMCNT)                                   |

|       |         | Compare Match Constant Register (CMCOR)                         |

Rev. 3.00 Jan. 18, 2010 Page xviii of xxiv

REJ09B0402-0300

17.3.4 A/D Analog Input Channel Select Registers\_0 and \_1

17.4

(ADANSR\_0 and ADANSR\_1).....

Operation .....

Operation .....

RENESAS

| Section 19 |        | Controller Area Network (RCAN-ET) |  |  |

|------------|--------|-----------------------------------|--|--|

| 19.1 Summ  |        | ıry                               |  |  |

|            |        | Overview                          |  |  |

|            | 19.1.2 | Scope                             |  |  |

|            |        | Audience                          |  |  |

|            |        | References                        |  |  |

|            |        | Features                          |  |  |

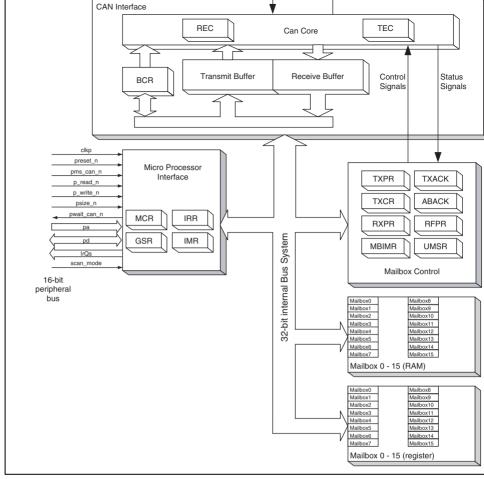

| 19.2       |        | cture                             |  |  |

| 19.3       |        | mming Model – Overview            |  |  |

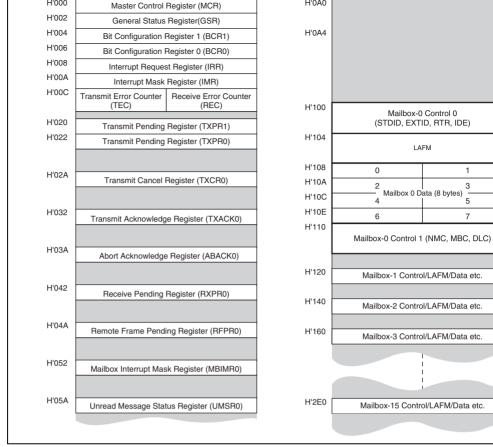

|            | -      | Memory Map                        |  |  |

|            |        | Mailbox Structure                 |  |  |

|            |        | RCAN-ET Control Registers         |  |  |

|            |        | RCAN-ET Mailbox Registers         |  |  |

| 19.4       |        | ation Note                        |  |  |

|            |        |                                   |  |  |

19.5

19.8

18.5.5 Compare Match between CMCNT and CMCOR .....

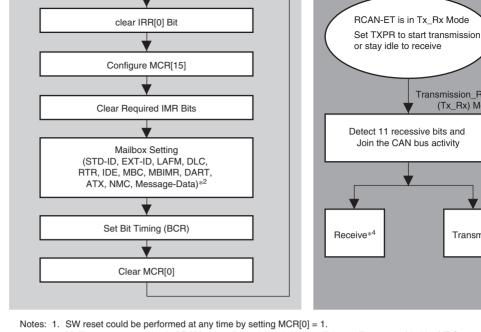

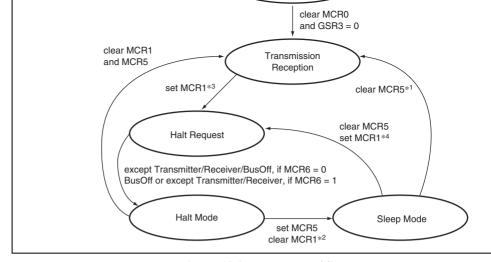

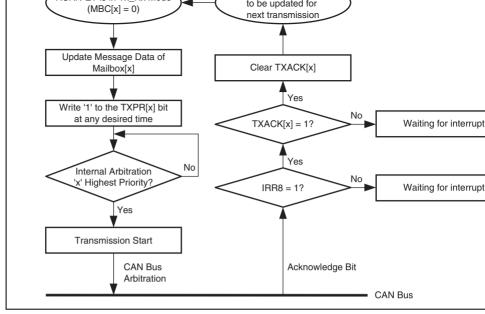

19.4.1 Test Mode Settings ..... 19.4.2 Configuration of RCAN-ET ..... 19.4.3 Message Transmission Sequence..... 19.4.4 Message Receive Sequence ...... 19.4.5 Reconfiguration of Mailbox.....

Interrupt Sources..... 19.6 DTC Interface 19.7 CAN Bus Interface..... Usage Notes.....

19.8.1 Module Stop Mode ..... 19.8.2 Reset ..... 19.8.3 CAN Sleep Mode.....

Rev. 3.00 Jan. 18, 2010 Pa

|         | PECRH1, PECRH2)                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20.10   | IRQOUT Function Control Register (IFCR)                                                                                                              |

|         | Notes                                                                                                                                                |

| C       |                                                                                                                                                      |

| on 21   | I/O Ports                                                                                                                                            |

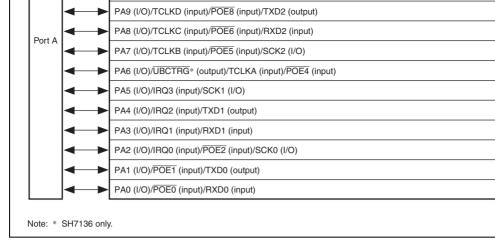

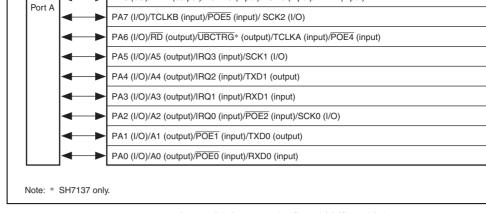

| Port A. |                                                                                                                                                      |

| 21.1.1  | Register Descriptions                                                                                                                                |

| 21.1.2  | Port A Data Register L (PADRL)                                                                                                                       |

| 21.1.3  | Port A Port Register L (PAPRL)                                                                                                                       |

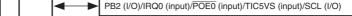

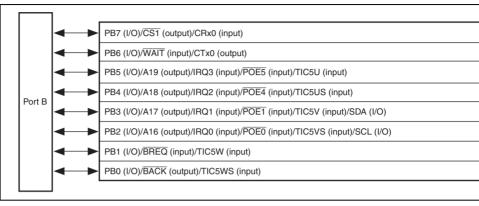

| Port B. |                                                                                                                                                      |

| 21.2.1  | Register Descriptions                                                                                                                                |

| 21.2.2  | Port B Data Register L (PBDRL)                                                                                                                       |

| 21.2.3  | Port B Port Register L (PBPRL)                                                                                                                       |

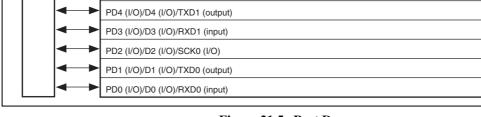

| Port D  | (SH7132/SH7137 Only)                                                                                                                                 |

|         | Register Descriptions                                                                                                                                |

| 21.3.2  | Port D Data Register L (PDDRL)                                                                                                                       |

| 21.3.3  | Port D Port Register L (PDPRL)                                                                                                                       |

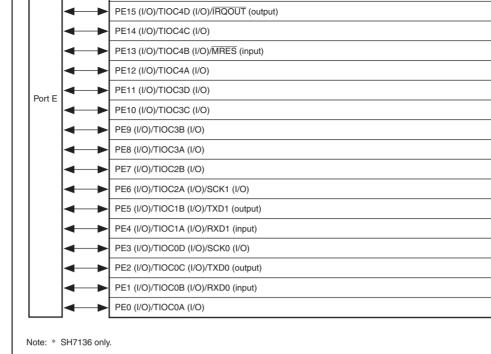

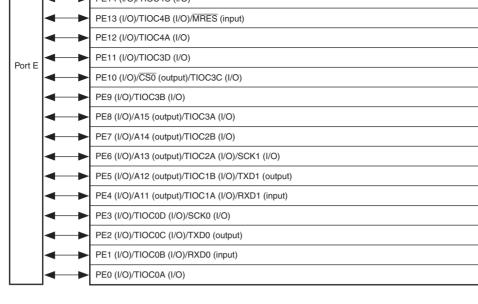

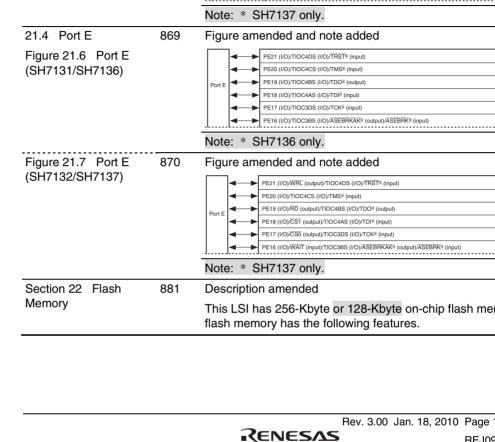

| Port E. |                                                                                                                                                      |

| 21.4.1  | Register Descriptions                                                                                                                                |

| 21.4.2  | Port E Data Registers H and L (PEDRH and PEDRL)                                                                                                      |

| 21.4.3  | Port E Port Registers H and L (PEPRH and PEPRL)                                                                                                      |

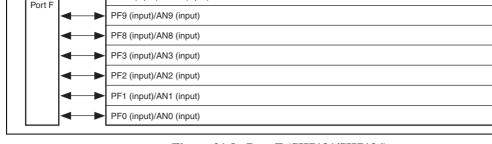

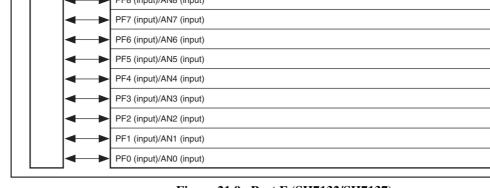

| Port F. |                                                                                                                                                      |

| 21.5.1  | Register Descriptions                                                                                                                                |

| 21.5.2  | Port F Data Register L (PFDRL)                                                                                                                       |

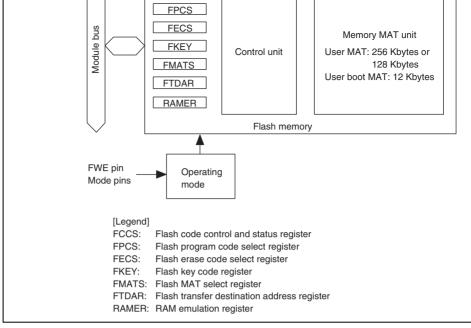

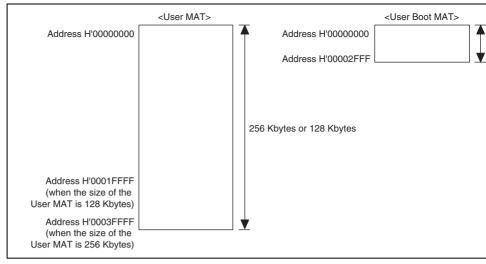

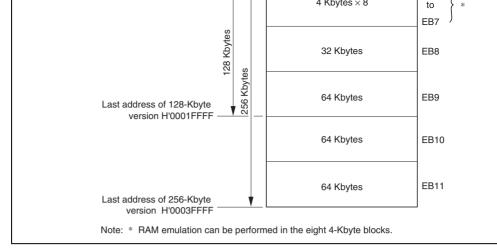

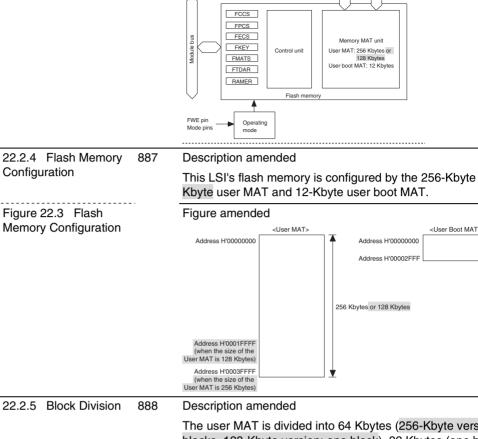

| on 22   | Flash Memory                                                                                                                                         |

|         | S                                                                                                                                                    |

|         | On 21 Port A. 21.1.1 21.1.2 21.1.3 Port B. 21.2.1 21.2.2 21.2.3 Port D 21.3.1 21.3.2 21.3.3 Port E. 21.4.1 21.4.2 21.4.3 Port F. 21.5.1 21.5.2 On 22 |

REJ09B0402-0300

20.1.7 Port E I/O Registers L, H (PEIORL, PEIORH).....

RENESAS

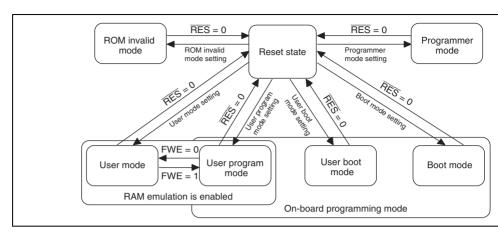

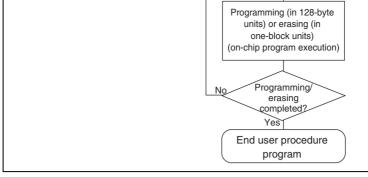

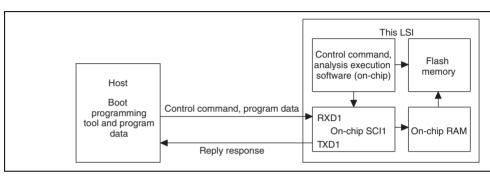

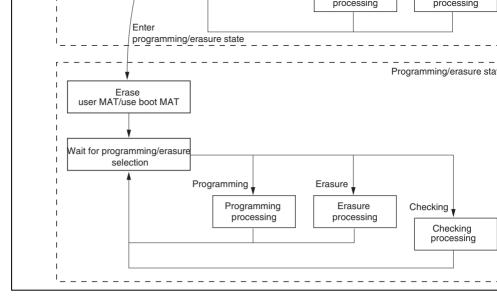

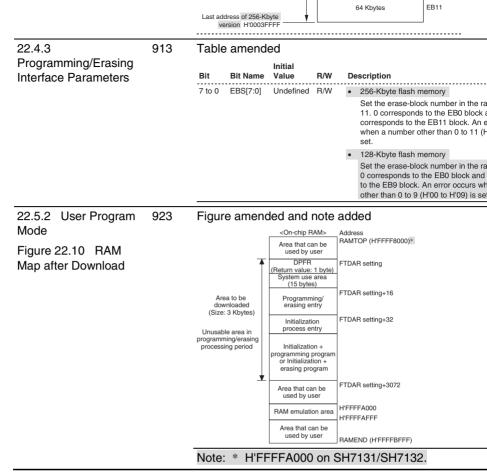

| 22.5  | .5 On-Board Programming Mode |                                                                       |  |

|-------|------------------------------|-----------------------------------------------------------------------|--|

|       | 22.5.1                       | Boot Mode                                                             |  |

|       | 22.5.2                       | User Program Mode                                                     |  |

|       | 22.5.3                       | User Boot Mode                                                        |  |

| 22.6  | Protect                      | ion                                                                   |  |

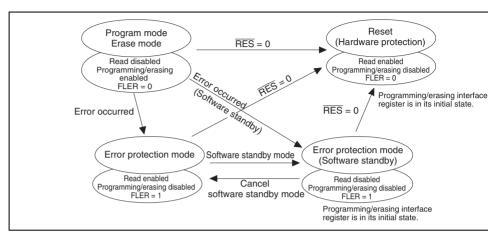

|       | 22.6.1                       | Hardware Protection                                                   |  |

|       | 22.6.2                       | Software Protection                                                   |  |

|       | 22.6.3                       | Error Protection.                                                     |  |

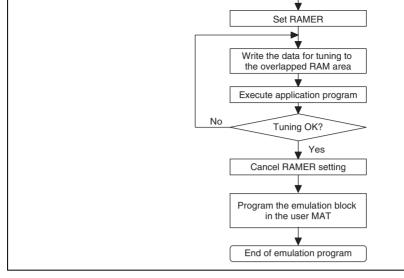

| 22.7  | Flash N                      | Memory Emulation in RAM                                               |  |

| 22.8  | Usage 1                      | Notes                                                                 |  |

|       | 22.8.1                       | Switching between User MAT and User Boot MAT                          |  |

|       | 22.8.2                       | Interrupts during Programming/Erasing                                 |  |

|       | 22.8.3                       | Other Notes                                                           |  |

| 22.9  | Supple                       | mentary Information                                                   |  |

|       | 22.9.1                       | Specifications of the Standard Serial Communications Interface        |  |

|       |                              | in Boot Mode                                                          |  |

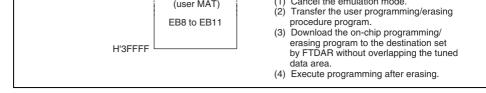

|       |                              | Areas for Storage of the Procedural Program and Data for Programming. |  |

| 22.10 | Prograi                      | mmer Mode                                                             |  |

| Secti | on 23                        | RAM                                                                   |  |

| 23.1  | Usage 1                      | Notes                                                                 |  |

|       | _                            | Module Standby Mode Setting                                           |  |

|       |                              | Address Error                                                         |  |

|       |                              | Initial Values in RAM                                                 |  |

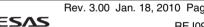

| Secti | on 24                        | Power-Down Modes                                                      |  |

24.1 Features

RENESAS

Rev. 3.00 Jan. 18, 2010 Pa

REJ09

|      | 24.4.1 Transition to Sleep Mode                                           |

|------|---------------------------------------------------------------------------|

|      | 24.4.2 Canceling Sleep Mode                                               |

| 24.5 |                                                                           |

|      | 24.5.1 Transition to Software Standby Mode                                |

|      | 24.5.2 Canceling Software Standby Mode                                    |

| 24.6 | Deep Software Standby Mode (SH7136 and SH7137 only)                       |

|      | 24.6.1 Transition to Deep Software Standby Mode                           |

|      | 24.6.2 Canceling Deep Software Standby Mode                               |

| 24.7 | Module Standby Mode                                                       |

|      | 24.7.1 Transition to Module Standby Mode                                  |

|      | 24.7.2 Canceling Module Standby Function                                  |

| 24.8 | Usage Note                                                                |

|      | 24.8.1 Current Consumption while Waiting for Oscillation to be Stabilized |

|      | 24.8.2 Executing the SLEEP Instruction                                    |

|      |                                                                           |

| Sect | ion 25 List of Registers                                                  |

| 25.1 | Register Address Table (In the Order of Addresses)                        |

| 25.2 | Register Bit List                                                         |

| 25.3 | Register States in Each Operating Mode                                    |

|      |                                                                           |

| Sect | ion 26 Electrical Characteristics                                         |

| 26.1 | Absolute Maximum Ratings                                                  |

| 26.2 | DC Characteristics                                                        |

| 26.3 | AC Characteristics                                                        |

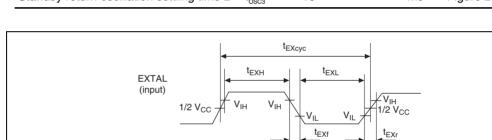

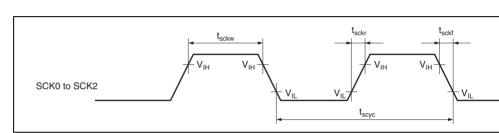

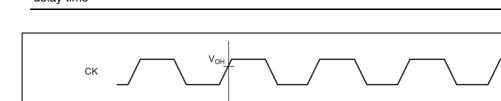

|      | 26.3.1 Clock Timing                                                       |

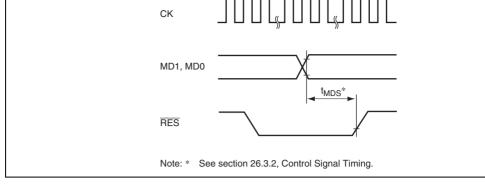

|      | 26.3.2 Control Signal Timing                                              |

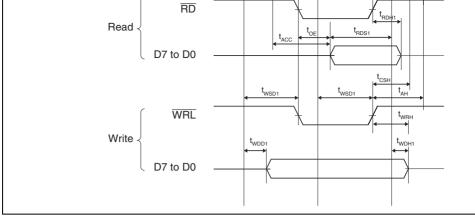

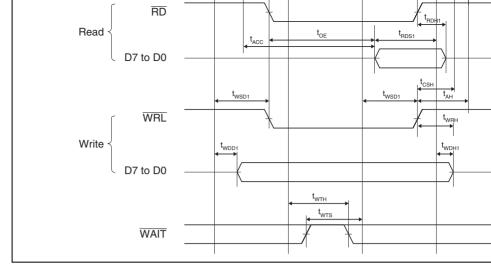

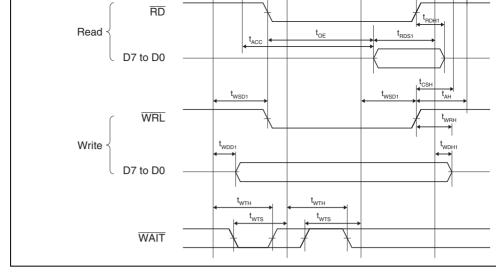

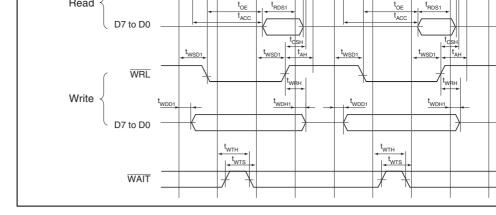

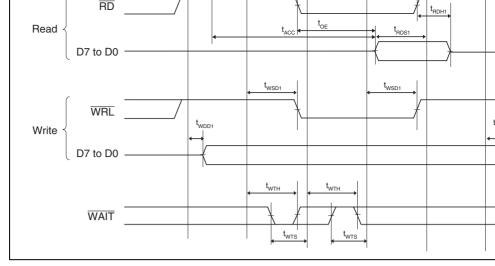

|      | 26.3.3 AC Bus Timing                                                      |

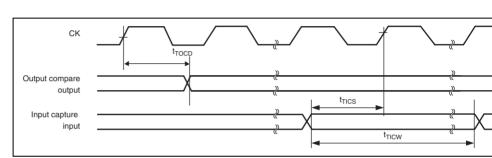

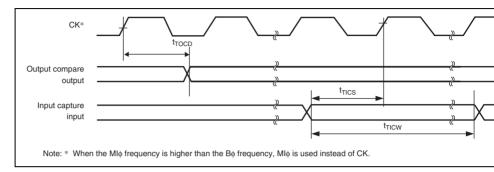

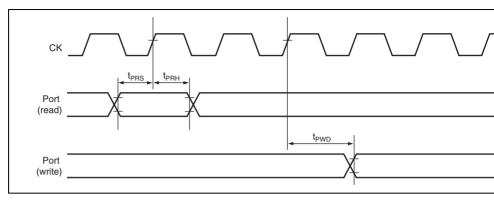

|      | 26.3.4 Multi Function Timer Pulse Unit 2 (MTU2) Timing                    |

|      | 26.3.5 Multi Function Timer Pulse Unit 2S (MTU2S) Timing                  |

RENESAS

Rev. 3.00 Jan. 18, 2010 Page xxii of xxiv

REJ09B0402-0300

| 26.6 | Usage Note                                           |

|------|------------------------------------------------------|

|      | 26.6.1 Notes on Connecting V <sub>CL</sub> Capacitor |

|      |                                                      |

| App  | endix                                                |

| A.   | Pin States                                           |

| B.   | Processing of Unused Pins                            |

| C.   | Pin States of Bus Related Signals                    |

| D.   | Product Code Lineup                                  |

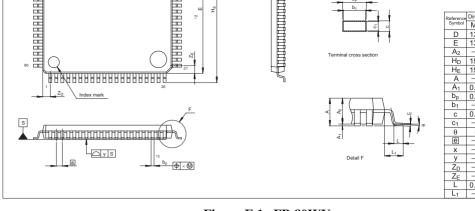

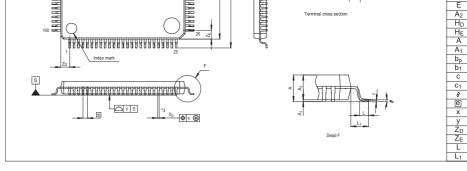

| E.   | Package Dimensions                                   |

Index

26.5 Flash Memory Characteristics .....

Rev. 3.00 Jan. 18, 2010 Page xxiv of xxiv

REJ09B0402-0300

possible to assemble low-cost, high-performance, and high-functioning systems, even for applications that were previously impossible with microcomputers, such as real-time cowhich demands high speeds.

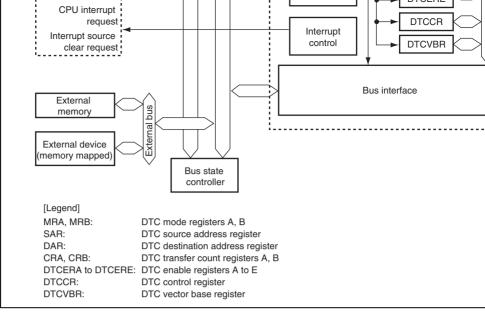

In addition, this LSI includes on-chip peripheral functions necessary for system configurable such as large-capacity ROM and RAM, a data transfer controller (DTC), timers, a serial communication interface (SCI), a synchronous serial communication unit (SSU), an A/I converter, an interrupt controller (INTC), I/O ports, I<sup>2</sup>C bus interface 2 (I<sup>2</sup>C2), and controller (RCAN-ET).

This LSI also provides an external memory access support function to enable direct convarious memory devices or peripheral LSIs (available only with the SH7132 and SH713

These on-chip functions significantly reduce costs of designing and manufacturing appl systems.

The version of on-chip ROM is F-ZTAT<sup>TM</sup> (Flexible Zero Turn Around Time)\* that inc memory. The flash memory can be programmed with a programmer that supports program this LSI, and can also be programmed and erased by software. This enables LSI chip to programmed at a user-site while mounted on a board.

The features of this LSI are listed in table 1.1.

Note: \* F-ZTAT is a trademark of Renesas Technology Corp.

- On-chip multiplier: Multiplication operations (32 bits × 32 bits executed in two to five cycles C language-oriented 62 basic instructions Some specifications on slot illegal instruction exception in this LSI differ from those of the conventional SH-2. For see section 5.8.4, Notes on Slot Illegal Instruction Exception Handling.

- Operating modes Operating modes Single chip mode

- - Extended ROM enabled mode (Only in SH7132/SH7137)

- Extended ROM disabled mode (Only in SH7132/SH7137)

- Operating states

- Program execution state Exception handling state

- Bus release state (Only in SH7132/SH7137)

- Power-down modes

break conditions

Two break channels

- Sleep mode

Module standby mode

- Software standby mode (Only in SH7136/SH7137)

Addresses, data values, type of access, and data size can all

- Deep software standby mode (Only in SH7136/SH7137)

- Supports a sequential break function

User break controller

(SH7132 and SH7137 •

(UBC)

only)

| Data transfer controller (DTC) | <ul> <li>Data transfer activated by an on-chip peripheral module inter<br/>be done independently of the CPU transfer.</li> </ul> |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                                | <ul> <li>Transfer mode selectable for each interrupt source (transfer specified in memory)</li> </ul>                            |

|                                | Multiple data transfer enabled for one activation source                                                                         |

|                                | Various transfer modes                                                                                                           |

Normal mode, repeat mode, or block transfer mode can be s

Data transfer size can be specified as byte, word, or longwor The interrupt that activated the DTC can be issued to the CP

A CPU interrupt can be requested after one data transfer completion.

A CPU interrupt can be requested after all specified data completion.

Five external interrupt pins (NMI and IRQ3 to IRQ0) On-chip peripheral interrupts: Priority level set for each modu

Vector addresses: A vector address for each interrupt source

Outputs a chip select signal according to the target area

Interrupt controller

(INTC)

|                                          | <ul> <li>MTU2S clock: Maximum 80 MHz</li> </ul>                                                                               |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Watchdog timer<br>(WDT)                  | On-chip one-channel watchdog timer                                                                                            |

|                                          | Interrupt generation is supported                                                                                             |

| Multi-function timer pulse unit 2 (MTU2) | <ul> <li>Maximum 16 lines of pulse input/output and 3 lines of pulse in<br/>based on six channels of 16-bit timers</li> </ul> |

|                                          | 21 output compare and input capture registers                                                                                 |

|                                          | <ul> <li>A total of 21 independent comparators</li> </ul>                                                                     |

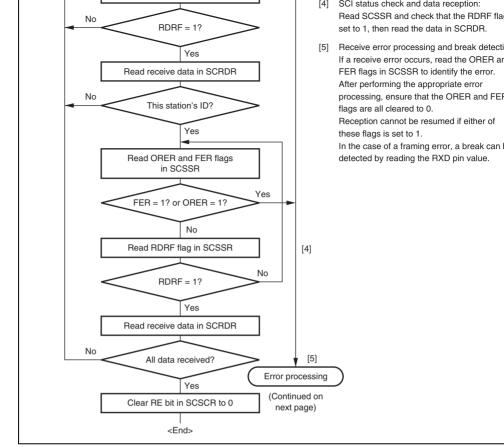

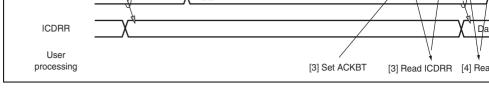

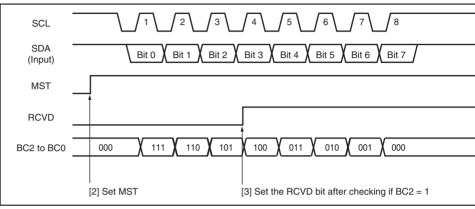

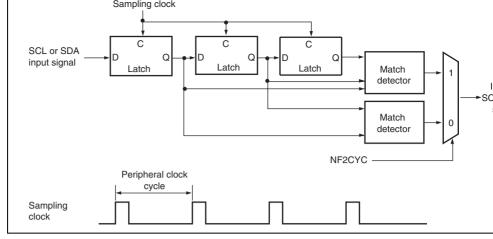

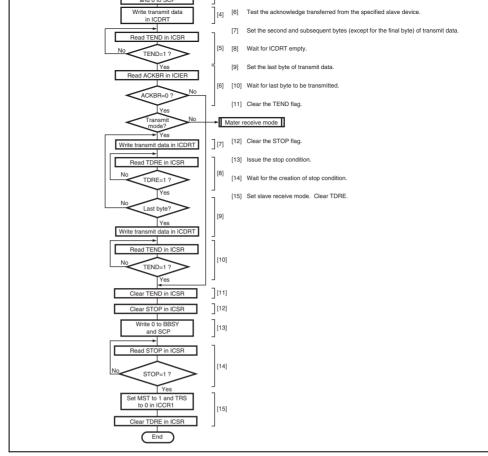

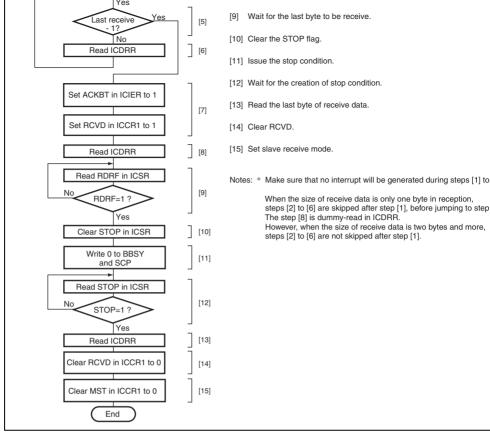

|                                          | Selection of eight counter input clocks                                                                                       |