## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# 32

# SH7211 Group

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family

> SH7211 R5F72115D160FPV R5F72114D160FPV

document, piedse commit me idlest product imornation, with a nemesas sales office. Also, piedse pay r and careful attention to additional and different information to be disclosed by Renesas such as that disc through our website. (http://www.renesas.com )

(2) surgical implantations

system manufactured by you.

approval from Renesas.

Rev. 3.00 Mar. 04, 2009 Page ii of xxiv

REJ09B0344-0300

damages arising out of such applications.

5. Renesas has used reasonable care in compiling the information included in this document, but Renesas

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the inform included in this document. When using or otherwise relying on the information in this document, you should evaluate the informatio

information in this document or Renesas products.

(3) healthcare intervention (e.g., excision, administration of medication, etc.)

damages arising out of the use of Renesas products beyond such specified ranges.

products. Renesas shall have no liability for damages arising out of such detachment.

document, Renesas semiconductor products, or if you have any other inquiries.

(4) any other purposes that pose a direct threat to human life

especially high quality and reliability such as safety systems, or equipment or systems for transportation traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea commur transmission. If you are considering the use of our products for such purposes, please contact a Renesa sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth abo Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed (1) artificial life support devices or systems

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Re Technology Corp., its affiliated companies and their officers, directors, and employees against any and a

9. You should use the products described herein within the range specified by Renesas, especially with res to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunct

10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have spec characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical inju injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final produ

11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is high. You should implement safety measures so that Renesas products may not be easily detached from

12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written

13. Please contact a Renesas sales office if you have any questions regarding the information contained in

RENESAS

light of the total system before deciding about the applicability of such information to the intended applicability of such information to the Renesas makes no representations, warranties or quaranties regarding the suitability of its products for particular application and specifically disclaims any liability arising out of the application and use of the 7. With the exception of products specified by Renesas as suitable for automobile applications. Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which reare in their open states, intermediate levels are induced by noise in the vicinity, through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied through chip and a low level is input on the reset pin. During the period where the states undefined, the register settings and the output state of each pin are also undefine your system so that it does not malfunction because of processing while it is in t undefined state. For those products which have a reset function, reset the LSI in after the power supply has been turned on.

4. Prohibition of Access to Undefined or Reserved Addresses

Access to undefined or reserved addresses is prohibited. The undefined or reserved addresses may be used to expand functions, or test re may have been be allocated to these addresses. Do not access these registers; the operation is not guaranteed if they are accessed.

- **CPU** and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according t module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each includes notes in relation to the descriptions given, and usage notes are given, as required final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- Product Type, Package Dimensions, etc.

- 10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier ver This does not include all of the revised contents. For details, see the actual locations in th manual.

11. Index

RENESAS

characteristics of this LSI to the target users.

Refer to the SH-2A, SH2A-FPU Software Manual for a detailed description instruction set.

### Notes on reading this manual:

- In order to understand the overall functions of the chip

- Read the manual according to the contents. This manual can be roughly categorized on the CPU, system control functions, peripheral functions and electrical characteris

- In order to understand the details of the CPU's functions

- Read the SH-2A, SH2A-FPU Software Manual.

- In order to understand the details of a register when its name is known Read the index that is the final part of the manual to find the page number of the entiregister. The addresses, bits, and initial values of the registers are summarized in sec List of Registers.

(3) Numbers

Binary numbers are given as B'xxxx, hexadecimal are given as H'xxxx, and decimal are given as xxxx.

Examples: B'11 or 11, H'EFA0, 1234

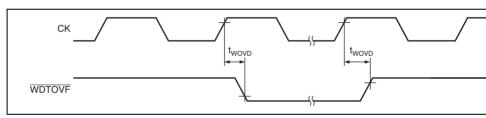

### (4) Symbols

An overbar is added to the names of active-low signals.

Example: WDTOVF

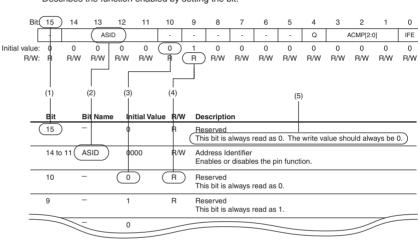

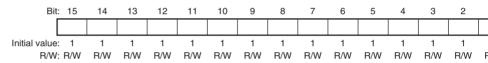

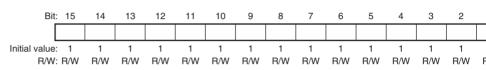

Note: The bit names and sentences in the above figure are examples, and have nothing to do with the contents of this manual.

Rev. 3.00 Mar. 04, 2009 Page vi of xxiv

REJ09B0344-0300

RENESAS

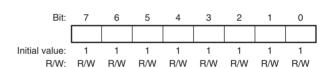

instead of a bit name, a blank is used for some bits, such as those of timer counters. (3) Initial Value Indicates the value of each bit after a power-on reset, i.e., the initial value. 0: Initial value is 0 1: Initial value is 1 -: Initial value is undefined Indicates whether each bit is readable or writable, or either writing to or reading from the bit is prohibited. The notation is as follows: R/W: Bit or field is readable and writable. R/(W): Bit or field is readable and writable. However, writing is only performed to clear the flag.

R: Bit or field is readable and writable.

However, "R" is indicated for all reserved bits. When writing to the bit is required, write the value stated in the bit table or the initial value. W: Bit or field is readable and writable.

However, only the value in the bit table is guaranteed when reading from the bit.

(5) Description Describes the function enabled by setting the bit.

All trademarks and registered trademarks are the property of their respective owners.

manual

Note: The bit names and sentences in the above figure are examples, and have nothing to do with the contents of this

Rev. 3.00 Mar. 04, 2009 Pa REJ09

Rev. 3.00 Mar. 04, 2009 Page viii of xxiv

REJ09B0344-0300

RENESAS

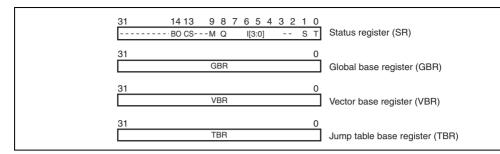

|      | 2 1 2   | Control Desistans                 |

|------|---------|-----------------------------------|

|      | 2.1.2   | Control Registers                 |

|      | 2.1.3   | System Registers                  |

|      | 2.1.4   | Register Banks                    |

|      | 2.1.5   | Initial Values of Registers       |

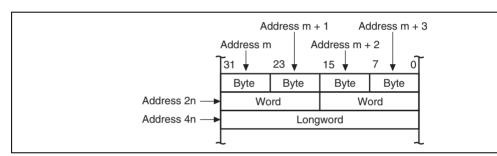

| 2.2  | Data F  | ormats                            |

|      | 2.2.1   | Data Format in Registers          |

|      | 2.2.2   | Data Formats in Memory            |

|      | 2.2.3   | Immediate Data Format             |

| 2.3  | Instruc | tion Features                     |

|      | 2.3.1   | RISC-Type Instruction Set         |

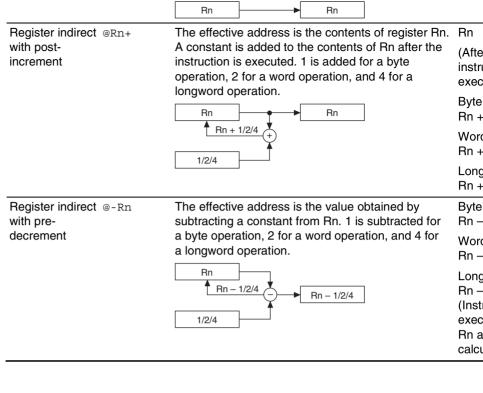

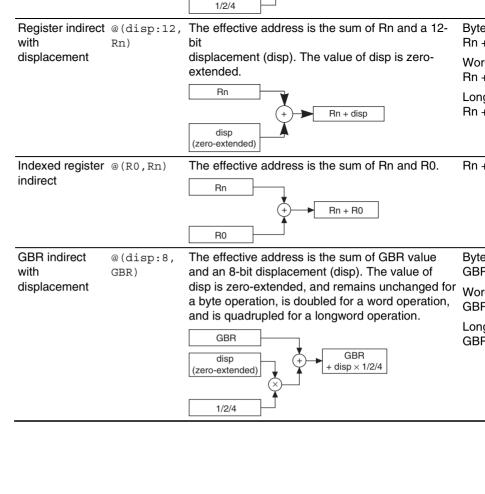

|      | 2.3.2   | Addressing Modes                  |

|      | 2.3.3   | Instruction Format                |

| 2.4  | Instruc | tion Set                          |

|      | 2.4.1   | Instruction Set by Classification |

|      | 2.4.2   | Data Transfer Instructions        |

|      | 2.4.3   | Arithmetic Operation Instructions |

|      | 2.4.4   | Logic Operation Instructions      |

|      | 2.4.5   | Shift Instructions                |

|      | 2.4.6   | Branch Instructions               |

|      | 2.4.7   | System Control Instructions       |

|      | 2.4.8   | Bit Manipulation Instructions     |

| 2.5  | Proces  | sing States                       |

|      |         |                                   |

| Sect | ion 3 N | ACU Operating Modes               |

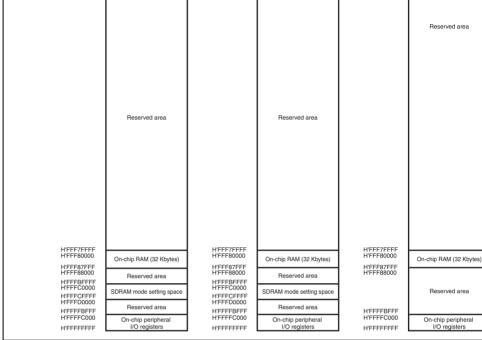

| 3.1  | Selecti | on of Operating Modes             |

| 3.2  | Input/0 | Output Pins                       |

| 3.3  | -       | ing Modes                         |

|      |         |                                   |

2.1.1

Rev. 3.00 Mar. 04, 2009 Pa

REJ09

Register Configuration.....

General Registers

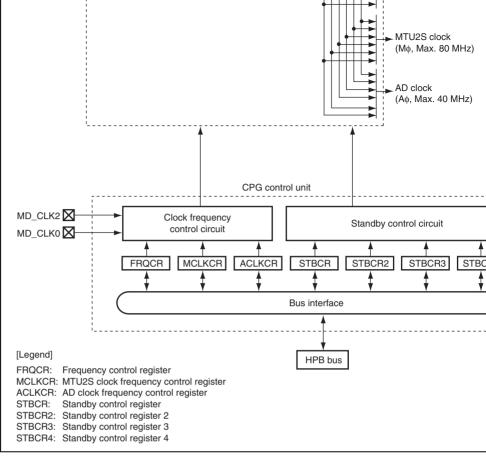

| 4.3        | Clock Operating Modes                                                      |  |  |

|------------|----------------------------------------------------------------------------|--|--|

| 4.4        | Register Descriptions                                                      |  |  |

|            | 4.4.1 Frequency Control Register (FRQCR)                                   |  |  |

|            | 4.4.2 MTU2S Clock Frequency Control Register (MCLKCR)                      |  |  |

|            | 4.4.3 AD Clock Frequency Control Register (ACLKCR)                         |  |  |

| 4.5        | Changing the Frequency                                                     |  |  |

|            | 4.5.1 Changing the Multiplication Rate                                     |  |  |

|            | 4.5.2 Changing the Division Ratio                                          |  |  |

| 4.6        | Notes on Board Design                                                      |  |  |

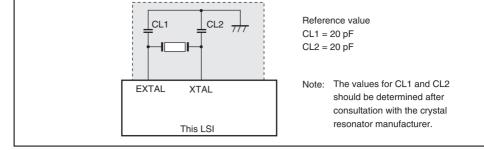

|            | 4.6.1 Note on Using an External Crystal Resonator                          |  |  |

|            | 4.6.2 Note on Bypass Capacitor                                             |  |  |

|            | 4.6.3 Note on Using a PLL Oscillation Circuit                              |  |  |

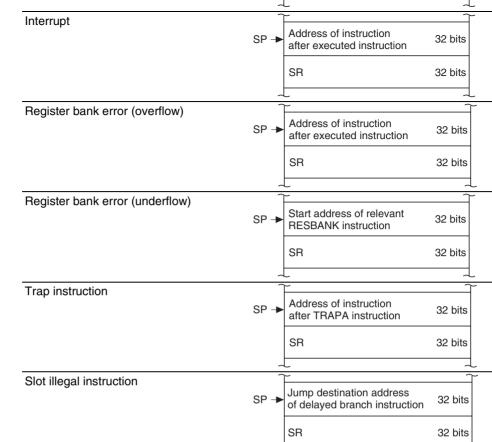

| Sect       | tion 5 Exception Handling                                                  |  |  |

| 5.1        | Overview                                                                   |  |  |

| 5.1        | 5.1.1 Types of Exception Handling and Priority                             |  |  |

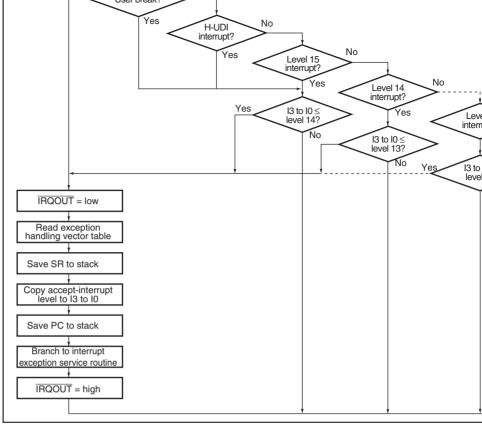

|            | 5.1.2 Exception Handling Operations                                        |  |  |

|            | 5.1.2 Exception Handling Operations  5.1.3 Exception Handling Vector Table |  |  |

| 5.2        | Resets                                                                     |  |  |

| 3.2        | 5.2.1 Types of Reset                                                       |  |  |

|            | 5.2.1 Types of Reset                                                       |  |  |

|            |                                                                            |  |  |

| 5.3        | 5.2.3 Manual Reset                                                         |  |  |

| 3.3        |                                                                            |  |  |

|            |                                                                            |  |  |

| <i>5</i> 1 | r                                                                          |  |  |

| 5.4        | Register Bank Errors                                                       |  |  |

|            | 5.4.1 Register Bank Error Sources.                                         |  |  |

|            | 5.4.2 Register Bank Error Exception Handling                               |  |  |

| 5.5        | Interrupts                                                                 |  |  |

| Rev.       | 3.00 Mar. 04, 2009 Page x of xxiv                                          |  |  |

|            | 9B0344-0300 <b>RENESAS</b>                                                 |  |  |

|            |                                                                            |  |  |

|      | 5.9.3                 | Address Errors Caused by Stacking of Address Error Exception Handling     |  |  |  |  |

|------|-----------------------|---------------------------------------------------------------------------|--|--|--|--|

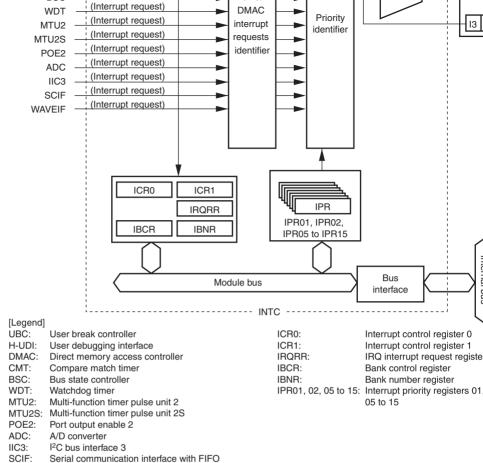

| Sect | tion 6 I              | nterrupt Controller (INTC)                                                |  |  |  |  |

| 6.1  | Featur                | eatures                                                                   |  |  |  |  |

| 6.2  |                       | nput/Output Pins                                                          |  |  |  |  |

| 6.3  | Register Descriptions |                                                                           |  |  |  |  |

|      | 6.3.1                 | Interrupt Priority Registers 01, 02, 05 to 15 (IPR01, IPR02, IPR05 to IPR |  |  |  |  |

|      | 6.3.2                 | Interrupt Control Register 0 (ICR0)                                       |  |  |  |  |

|      | 6.3.3                 | Interrupt Control Register 1 (ICR1)                                       |  |  |  |  |

|      | 6.3.4                 | IRQ Interrupt Request Register (IRQRR)                                    |  |  |  |  |

|      | 6.3.5                 | Bank Control Register (IBCR)                                              |  |  |  |  |

|      | 6.3.6                 | Bank Number Register (IBNR)                                               |  |  |  |  |

| 6.4  | Interru               | pt Sources                                                                |  |  |  |  |

|      | 6.4.1                 | NMI Interrupt                                                             |  |  |  |  |

|      | 6.4.2                 | User Break Interrupt                                                      |  |  |  |  |

Usage Notes

Value of Stack Pointer (SP)

Value of Vector Base Register (VBR).....

User Break Interrupt

H-UDI Interrupt

IRQ Interrupts

On-Chip Peripheral Module Interrupts .....

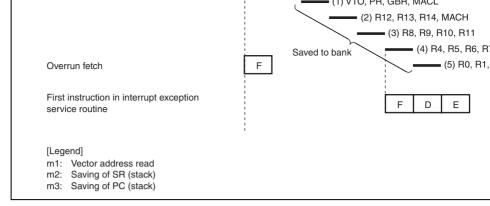

Interrupt Operation Sequence ..... Stack after Interrupt Exception Handling .....

Banked Register and Input/Output of Banks .....

Bank Save and Restore Operations.....

Interrupt Exception Handling Vector Table and Priority.....

Operation .....

Interrupt Response Time.....

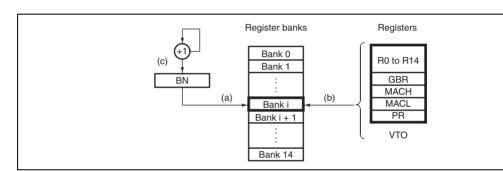

Register Banks

5.9

5.9.1

5.9.2

6.4.3

6.4.4

6.4.5

6.6.1

6.6.2

6.8.1

6.8.2

6.5

6.6

6.7

6.8

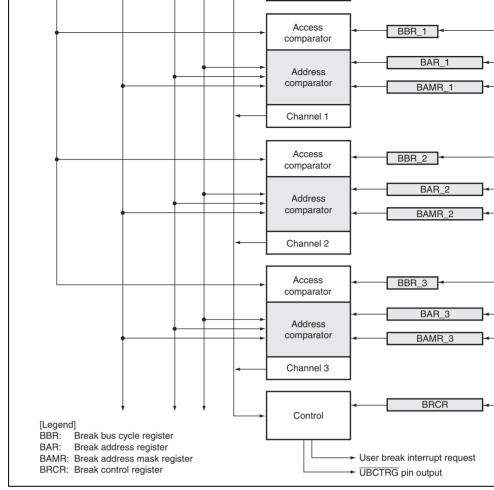

| Sect | ion 7 U | ser Break Controller (UBC)             |

|------|---------|----------------------------------------|

| 7.1  | Feature | ·s                                     |

| 7.2  | Input/C | Output Pin                             |

| 7.3  | Registe | r Descriptions                         |

|      | 7.3.1   | Break Address Register_0 (BAR_0)       |

|      | 7.3.2   | Break Address Mask Register_0 (BAMR_0) |

|      | 7.3.3   | Break Bus Cycle Register_0 (BBR_0)     |

|      | 7.3.4   | Break Address Register_1 (BAR_1)       |

|      | 7.3.5   | Break Address Mask Register_1 (BAMR_1) |

|      | 7.3.6   | Break Bus Cycle Register_1 (BBR_1)     |

|      | 7.3.7   | Break Address Register_2 (BAR_2)       |

|      | 7.3.8   | Break Address Mask Register_2 (BAMR_2) |

|      | 7.3.9   | Break Bus Cycle Register_2 (BBR_2)     |

|      | 7.3.10  | Break Address Register_3 (BAR_3)       |

|      | 7.3.11  | Break Address Mask Register_3 (BAMR_3) |

|      | 7.3.12  | Break Bus Cycle Register_3 (BBR_3)     |

|      | 7.3.13  | Break Control Register (BRCR)          |

| 7.4  | Operati | on                                     |

|      | 7.4.1   | Flow of the User Break Operation       |

|      | 7.4.2   | Break on Instruction Fetch Cycle       |

|      | 7.4.3   | Break on Data Access Cycle             |

|      | 7.4.4   | Value of Saved Program Counter         |

|      | 7.4.5   | Usage Examples                         |

| 7.5  | Usage 1 | Notes                                  |

| _    |         |                                        |

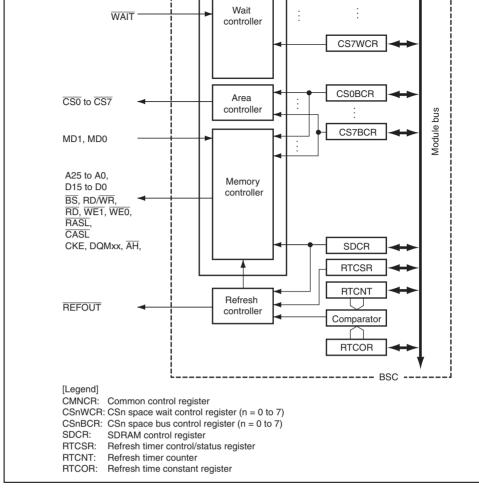

| Sect |         | us State Controller (BSC)              |

| 8.1  |         | ·S                                     |

| 8.2  | -       | Output Pins                            |

| 8.3  | Area O  | verview                                |

RENESAS

Rev. 3.00 Mar. 04, 2009 Page xii of xxiv

REJ09B0344-0300

|      | 8.5.5    | MPX-I/O Interface                        |  |

|------|----------|------------------------------------------|--|

|      | 8.5.6    | SDRAM Interface                          |  |

|      |          | Burst ROM (Clock Asynchronous) Interface |  |

|      | 8.5.8    | SRAM Interface with Byte Selection       |  |

|      | 8.5.9    | Burst ROM (Clock Synchronous) Interface  |  |

|      | 8.5.10   | Wait between Access Cycles               |  |

|      |          | Bus Arbitration                          |  |

|      | 8.5.12   | Others                                   |  |

| 8.6  | Usage    | Notes                                    |  |

|      | 8.6.1    | Burst ROM Interface                      |  |

|      |          |                                          |  |

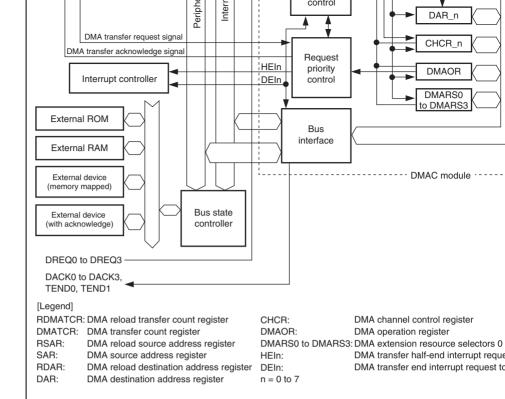

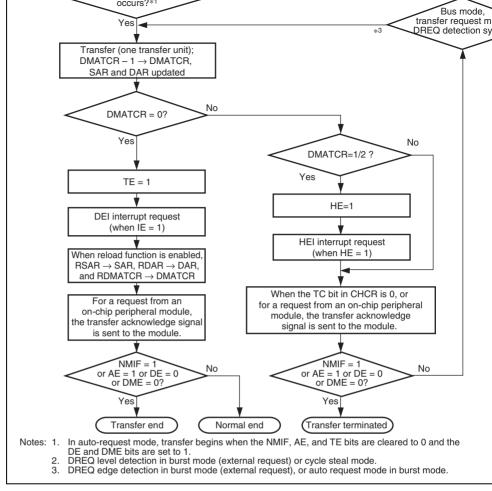

| Sect | tion 9 D | rirect Memory Access Controller (DMAC)   |  |

| 9.1  | Feature  | PS                                       |  |

| 9.2  | Input/C  | Input/Output Pins                        |  |

| 9.3  | Registe  | er Descriptions                          |  |

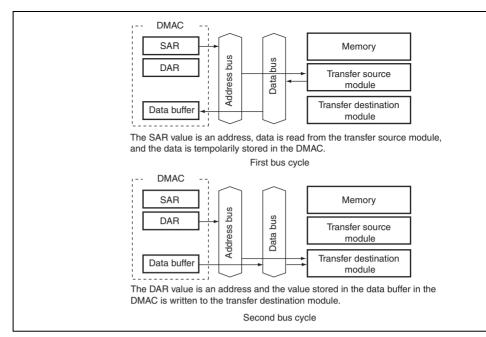

|      | 9.3.1    | DMA Source Address Registers (SAR)       |  |

|      | 9.3.2    | DMA Destination Address Registers (DAR)  |  |

|      |          |                                          |  |

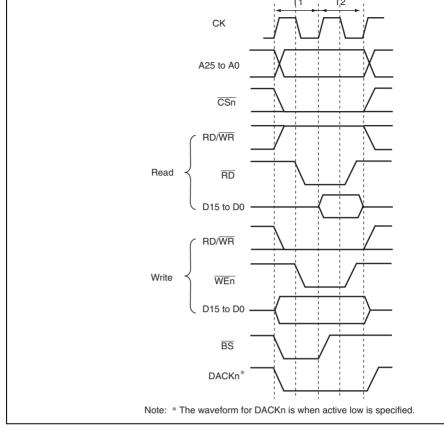

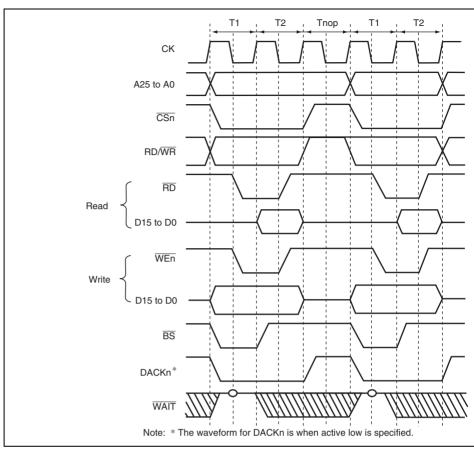

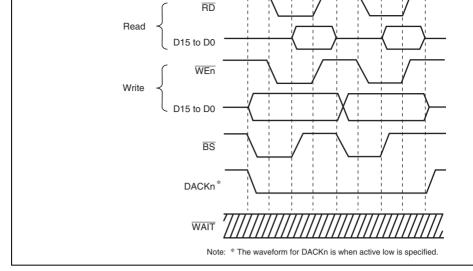

8.5.1

8.5.2

8.5.3

8.5.4

9.3.3 9.3.4

9.3.5

9.3.6

9.3.7

9.3.8

9.3.9

9.4

DMA Transfer Count Registers (DMATCR)

DMA Channel Control Registers (CHCR)

DMA Reload Source Address Registers (RSAR).....

DMA Reload Destination Address Registers (RDAR).....

DMA Reload Transfer Count Registers (RDMATCR).....

DMA Operation Register (DMAOR) .....

Endian/Access Size and Data Alignment.....

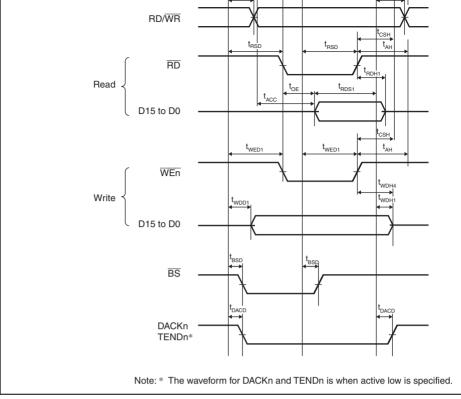

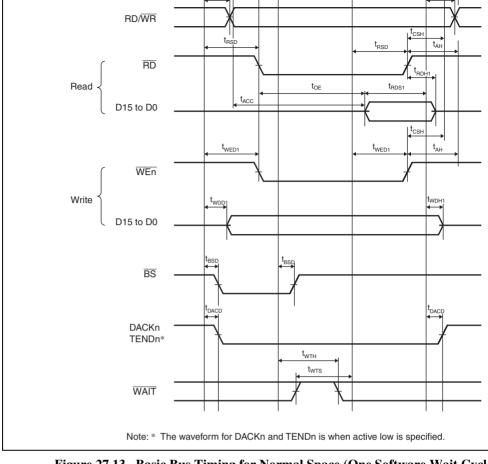

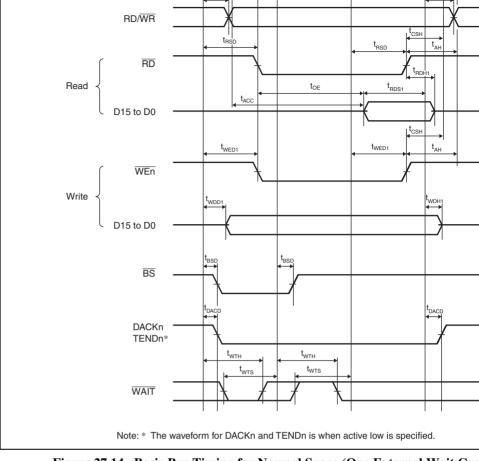

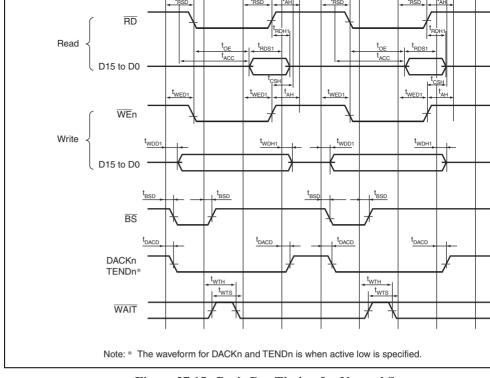

Normal Space Interface.....

Access Wait Control CSn Assert Period Expansion.....

REJ09

Rev. 3.00 Mar. 04, 2009 Pa

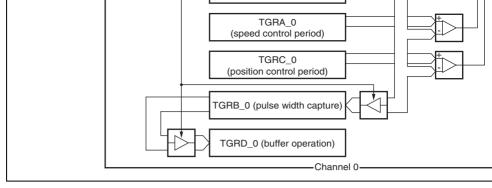

| 10.3.3  | Timer I/O Control Register (TIOR)                            |

|---------|--------------------------------------------------------------|

| 10.3.4  | Timer Compare Match Clear Register (TCNTCMPCLR)              |

| 10.3.5  | Timer Interrupt Enable Register (TIER)                       |

| 10.3.6  | Timer Status Register (TSR)                                  |

| 10.3.7  | Timer Buffer Operation Transfer Mode Register (TBTM)         |

| 10.3.8  | Timer Input Capture Control Register (TICCR)                 |

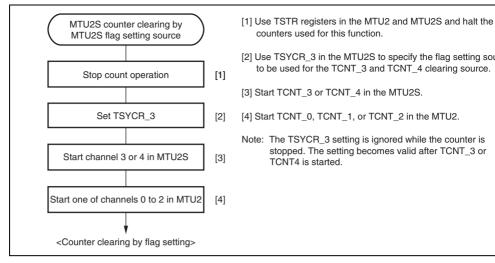

| 10.3.9  | Timer Synchronous Clear Register (TSYCR)                     |

| 10.3.10 | Timer A/D Converter Start Request Control Register (TADCR)   |

| 10.3.11 | Timer A/D Converter Start Request Cycle Set Registers        |

|         | (TADCORA_4 and TADCORB_4)                                    |

| 10.3.12 | Timer A/D Converter Start Request Cycle Set Buffer Registers |

|         | (TADCOBRA_4 and TADCOBRB_4)                                  |

| 10.3.13 | Timer Counter (TCNT)                                         |

| 10.3.14 | Timer General Register (TGR)                                 |

| 10.3.15 | Timer Start Register (TSTR)                                  |

| 10.3.16 | Timer Synchronous Register (TSYR)                            |

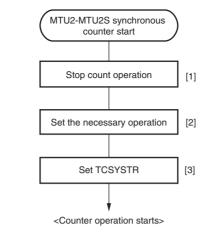

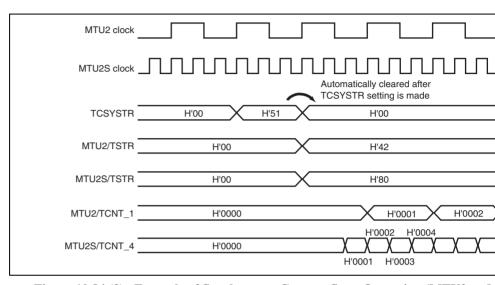

| 10.3.17 | Timer Counter Synchronous Start Register (TCSYSTR)           |

| 10.3.18 | Timer Read/Write Enable Register (TRWER)                     |

| 10.3.19 | Timer Output Master Enable Register (TOER)                   |

| 10.3.20 | Timer Output Control Register 1 (TOCR1)                      |

| 10.3.21 | Timer Output Control Register 2 (TOCR2)                      |

Rev. 3.00 Mar. 04, 2009 Page xiv of xxiv

REJ09B0344-0300

10.3.22 Timer Output Level Buffer Register (TOLBR)

10.3.23 Timer Gate Control Register (TGCR)

10.3.24 Timer Subcounter (TCNTS)

10.3.25 Timer Dead Time Data Register (TDDR).

10.3.26 Timer Cycle Data Register (TCDR)

RENESAS

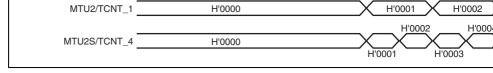

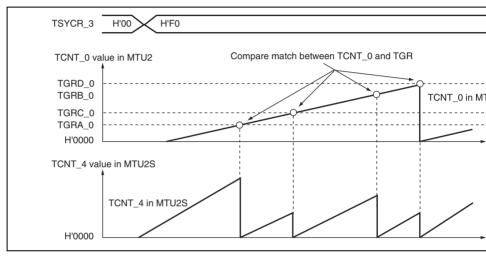

|      | 10.4.10 MTU2–MTU2S Synchronous Operation                                   |

|------|----------------------------------------------------------------------------|

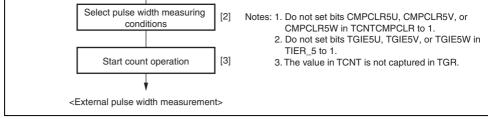

|      | 10.4.11 External Pulse Width Measurement                                   |

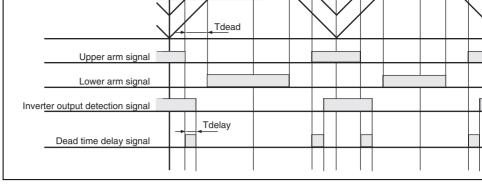

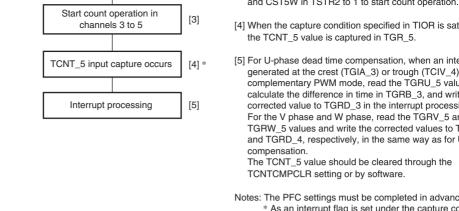

|      | 10.4.12 Dead Time Compensation                                             |

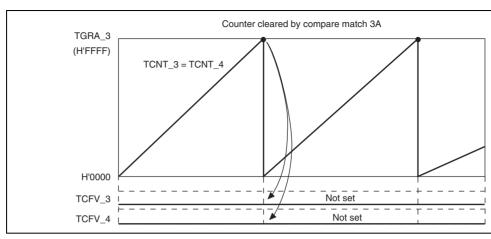

|      | 10.4.13 TCNT Capture at Crest and/or Trough in Complementary PWM Operation |

| 10.5 | Interrupt Sources                                                          |

|      | 10.5.1 Interrupt Sources and Priorities                                    |

|      | 10.5.2 DMAC Activation                                                     |

|      | 10.5.3 A/D Converter Activation                                            |

| 10.6 | Operation Timing                                                           |

|      | 10.6.1 Input/Output Timing                                                 |

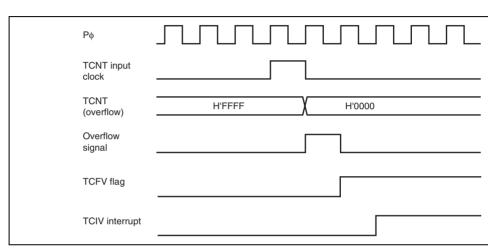

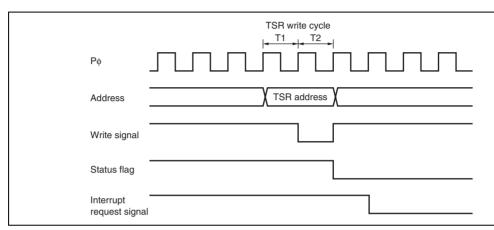

|      | 10.6.2 Interrupt Signal Timing                                             |

| 10.7 | Usage Notes                                                                |

|      | 10.7.1 Module Standby Mode Setting                                         |

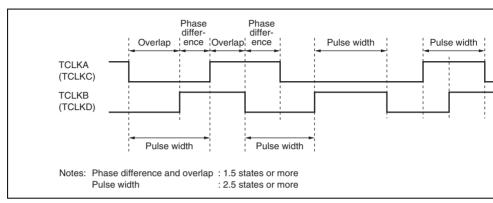

|      | 10.7.2 Input Clock Restrictions                                            |

|      | 10.7.3 Caution on Period Setting                                           |

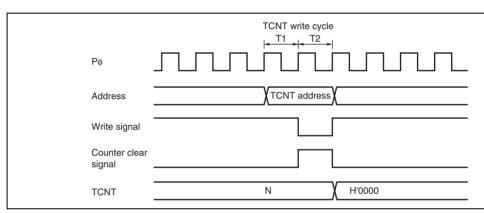

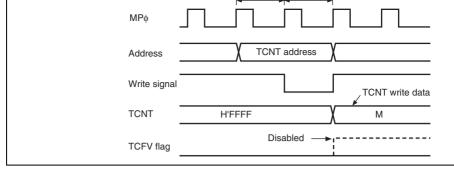

|      | 10.7.4 Contention between TCNT Write and Clear Operations                  |

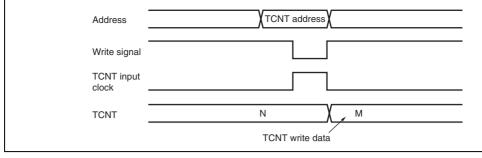

|      | 10.7.5 Contention between TCNT Write and Increment Operations              |

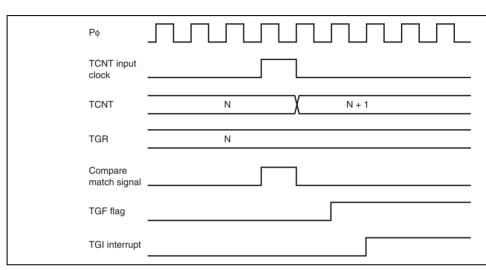

|      | 10.7.6 Contention between TGR Write and Compare Match                      |

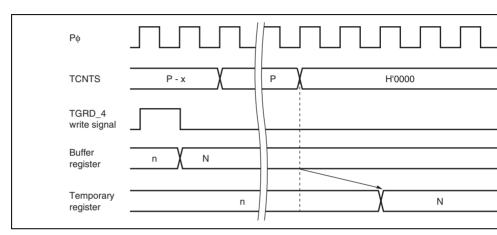

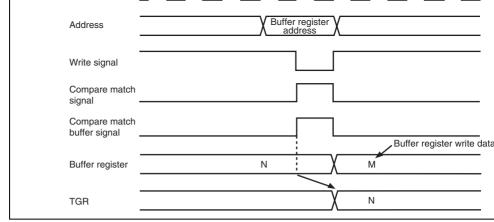

|      | 10.7.7 Contention between Buffer Register Write and Compare Match          |

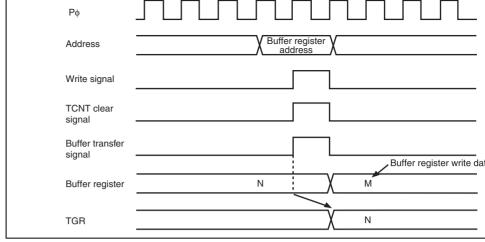

|      | 10.7.8 Contention between Buffer Register Write and TCNT Clear             |

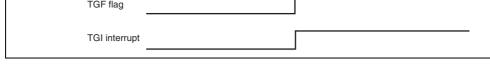

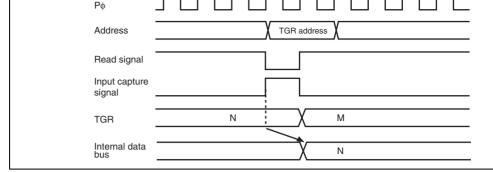

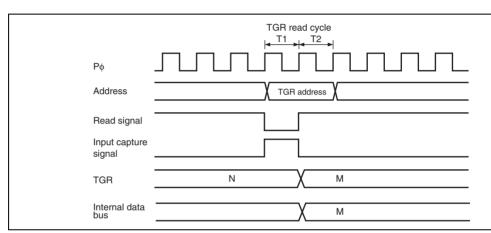

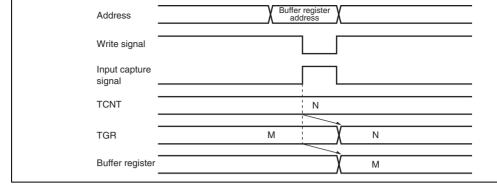

|      | 10.7.9 Contention between TGR Read and Input Capture                       |

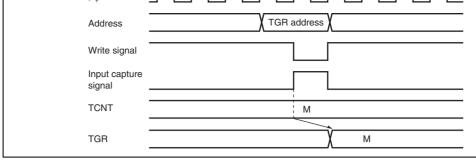

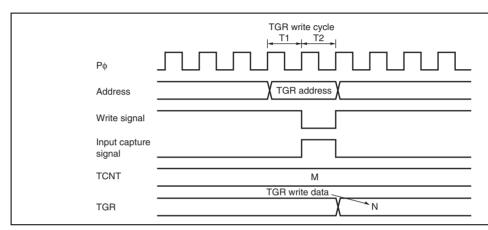

|      | 10.7.10 Contention between TGR Write and Input Capture                     |

|      | 10.7.11 Contention between Buffer Register Write and Input Capture         |

|      |                                                                            |

|      | Rev. 3.00 Mar. 04, 2009 Pa                                                 |

|      | REJOS REJOS                                                                |

|      |                                                                            |

|      |                                                                            |

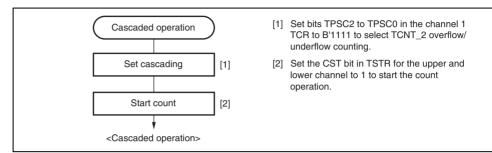

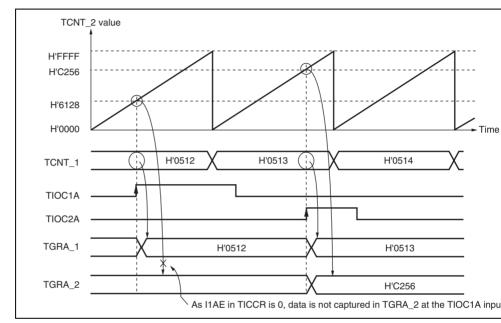

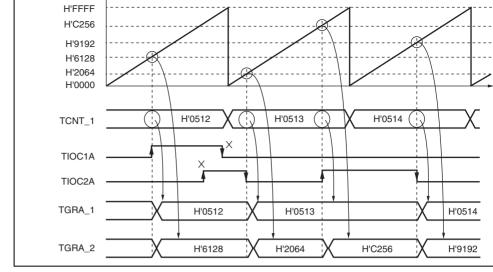

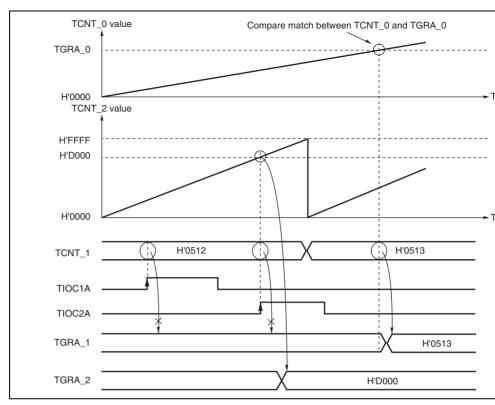

10.4.4 Cascaded Operation

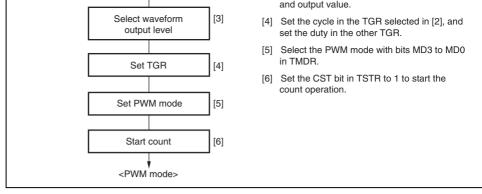

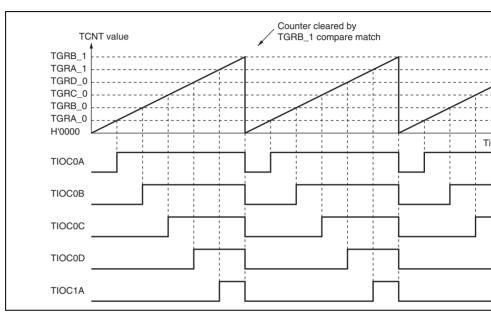

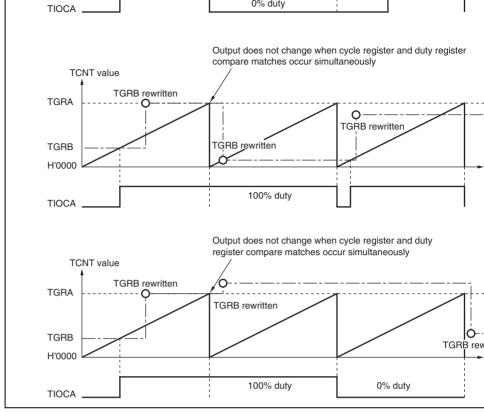

10.4.5 PWM Modes

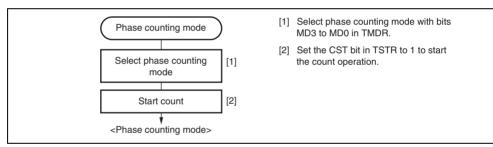

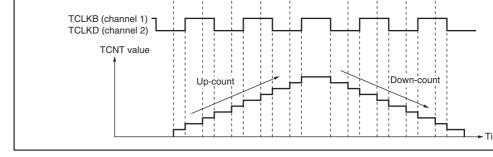

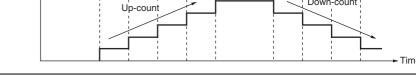

10.4.6 Phase Counting Mode

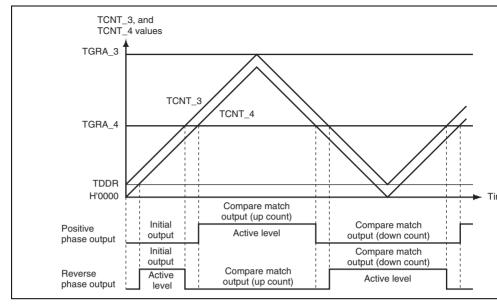

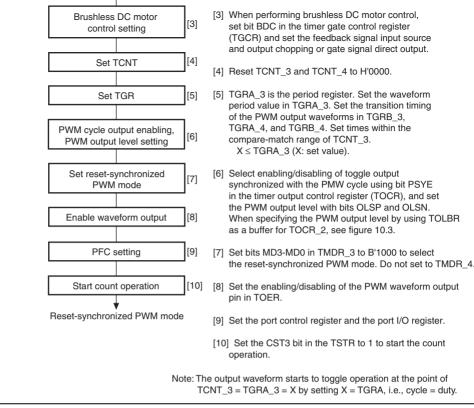

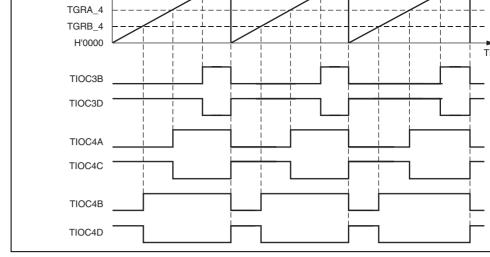

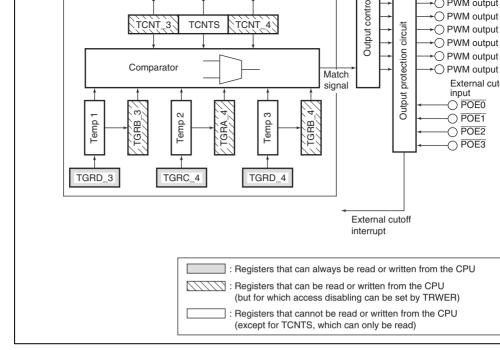

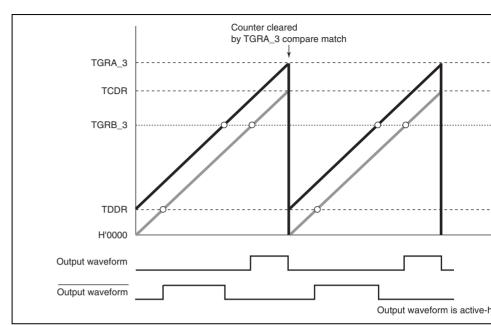

10.4.7 Reset-Synchronized PWM Mode

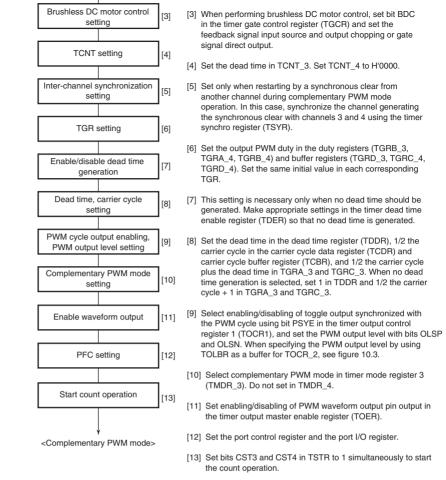

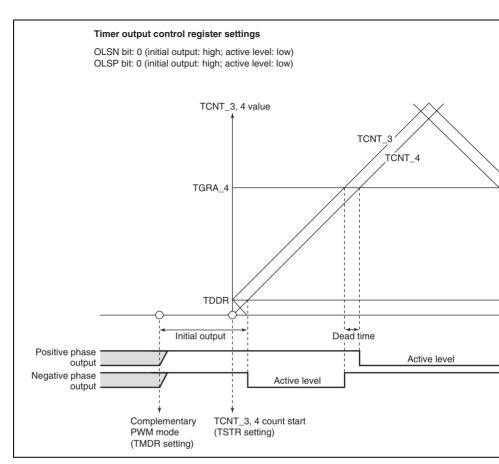

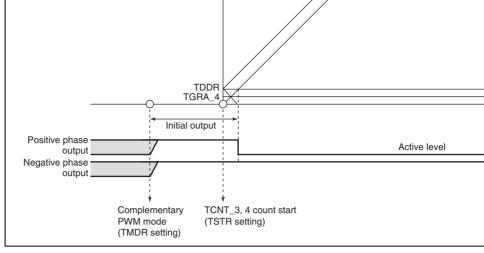

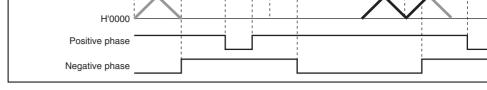

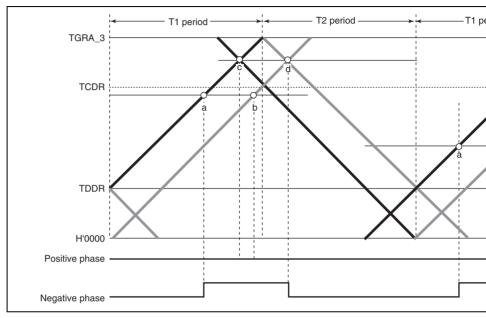

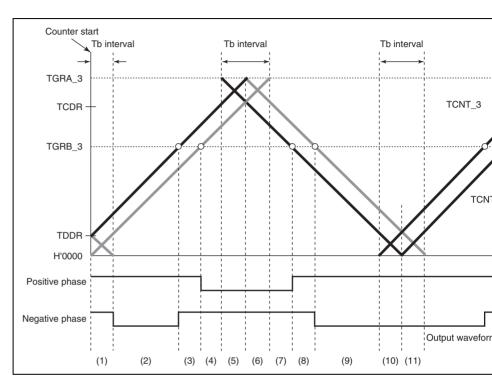

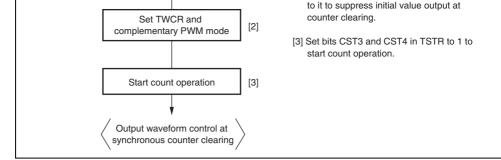

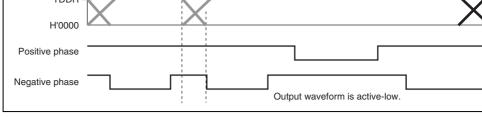

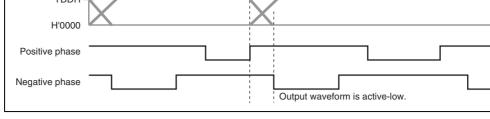

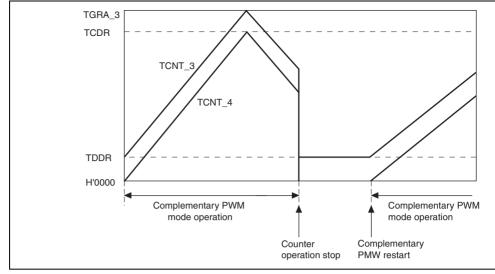

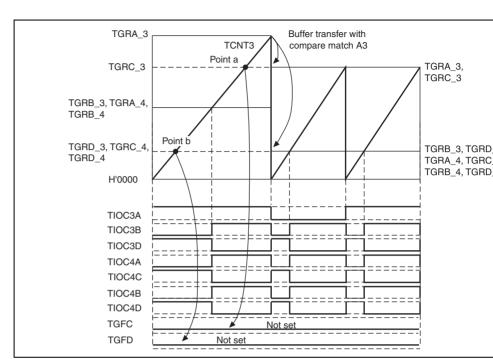

10.4.8 Complementary PWM Mode

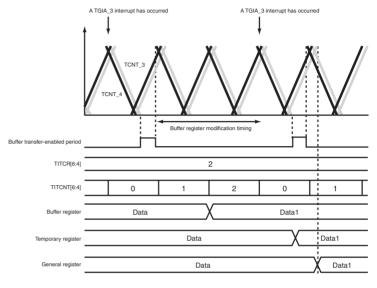

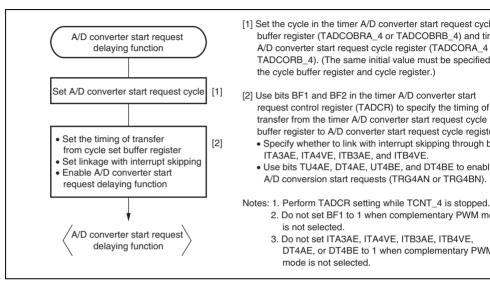

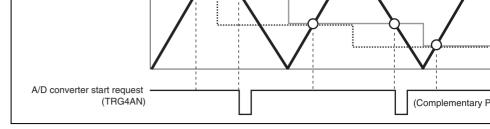

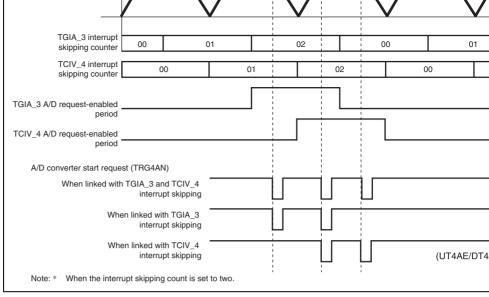

10.4.9 A/D Converter Start Request Delaying Function

|      | 10.7.22 Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection                                |

|------|--------------------------------------------------------------------------------------------------------|

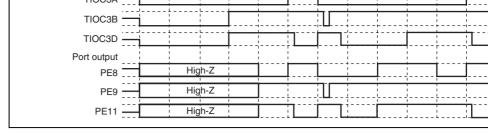

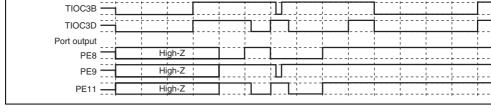

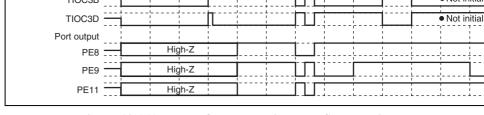

| 10.8 | MTU2 Output Pin Initialization                                                                         |

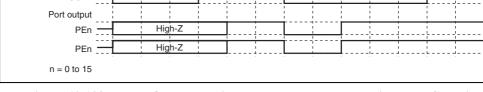

|      | 10.8.1 Operating Modes                                                                                 |

|      | 10.8.2 Reset Start Operation                                                                           |

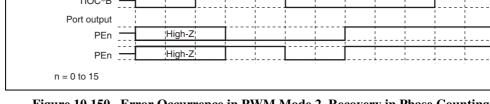

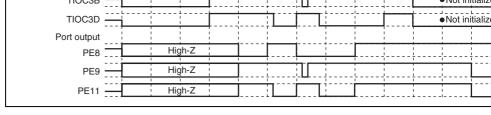

|      | 10.8.3 Operation in Case of Re-Setting Due to Error During Operation, etc                              |

|      | 10.8.4 Overview of Initialization Procedures and Mode Transitions in Case of Er during Operation, etc. |

| Sect | ion 11 Multi-Function Timer Pulse Unit 2S (MTU2S)                                                      |

|      | Input/Output Pins                                                                                      |

|      | Register Descriptions                                                                                  |

| 11.2 | Register Descriptions                                                                                  |

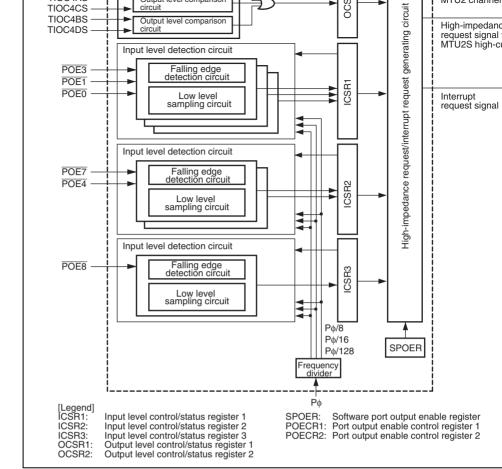

| Sect | ion 12 Port Output Enable 2 (POE2)                                                                     |

| 12.1 | Features                                                                                               |

| 12.2 |                                                                                                        |

| 12.3 |                                                                                                        |

|      | 12.3.1 Input Level Control/Status Register 1 (ICSR1)                                                   |

|      | 12.3.2 Output Level Control/Status Register 1 (OCSR1)                                                  |

|      | 12.3.3 Input Level Control/Status Register 2 (ICSR2)                                                   |

|      | · · · · · · · · · · · · · · · · · · ·                                                                  |

10.7.21 Interrupts in Module Standby Mode.....

12.3.4 Output Level Control/Status Register 2 (OCSR2)

12.3.5 Input Level Control/Status Register 3 (ICSR3)

12.3.6 Software Port Output Enable Register (SPOER)

RENESAS

Rev. 3.00 Mar. 04, 2009 Page xvi of xxiv

REJ09B0344-0300

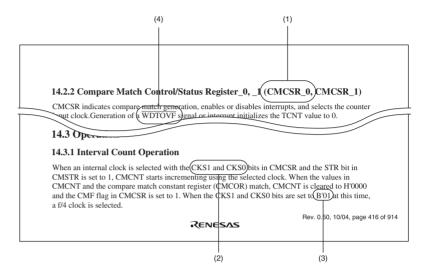

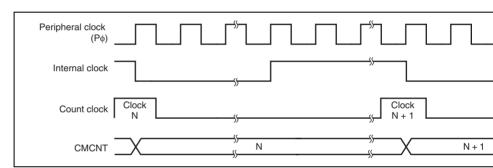

|                      | 13.3.2 CMCNT Count Timing                                                                                                                                                                                                                                                                                        | • • • • • • • |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 13.4                 | Interrupts                                                                                                                                                                                                                                                                                                       |               |

|                      | 13.4.1 Interrupt Sources and DMA Transfer Requests                                                                                                                                                                                                                                                               |               |

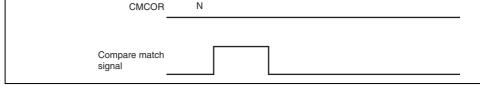

|                      | 13.4.2 Timing of Compare Match Flag Setting                                                                                                                                                                                                                                                                      |               |

|                      | 13.4.3 Timing of Compare Match Flag Clearing                                                                                                                                                                                                                                                                     |               |

| 13.5                 | Usage Notes                                                                                                                                                                                                                                                                                                      |               |

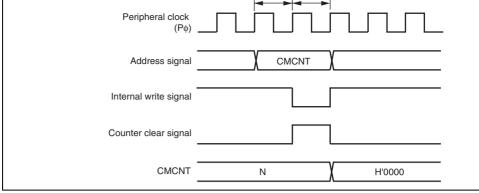

|                      | 13.5.1 Conflict between Write and Compare-Match Processes of CMCNT.                                                                                                                                                                                                                                              |               |

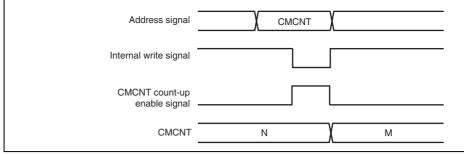

|                      | 13.5.2 Conflict between Word-Write and Count-Up Processes of CMCNT.                                                                                                                                                                                                                                              |               |

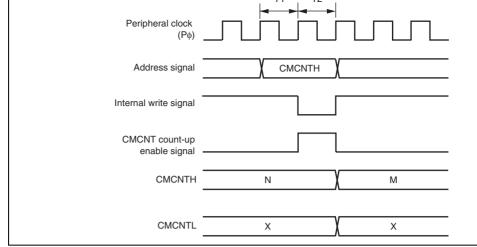

|                      | 13.5.3 Conflict between Byte-Write and Count-Up Processes of CMCNT                                                                                                                                                                                                                                               |               |

|                      | 13.5.4 Compare Match Between CMCNT and CMCOR                                                                                                                                                                                                                                                                     |               |

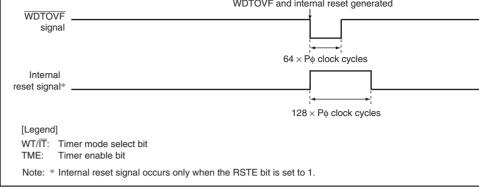

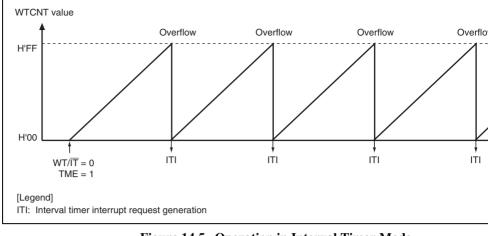

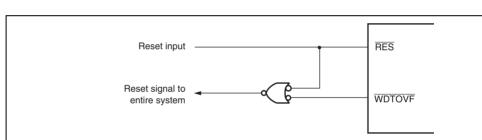

| Sect                 | ion 14 Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                      |               |

| 14.1                 |                                                                                                                                                                                                                                                                                                                  |               |

| 14.1                 | Features                                                                                                                                                                                                                                                                                                         |               |

|                      | Features Input/Output Pin                                                                                                                                                                                                                                                                                        |               |

| 14.1<br>14.2         | Features                                                                                                                                                                                                                                                                                                         |               |

| 14.1<br>14.2         | Features Input/Output Pin Register Descriptions                                                                                                                                                                                                                                                                  |               |

| 14.1<br>14.2         | Features                                                                                                                                                                                                                                                                                                         |               |

| 14.1<br>14.2         | Features                                                                                                                                                                                                                                                                                                         |               |

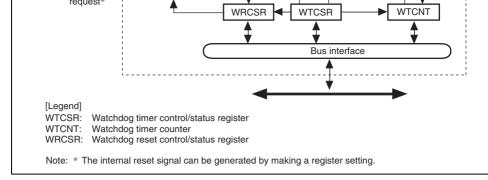

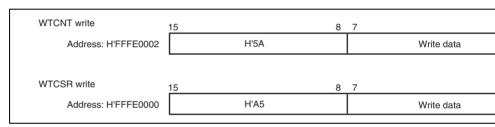

| 14.1<br>14.2<br>14.3 | Features Input/Output Pin Register Descriptions 14.3.1 Watchdog Timer Counter (WTCNT) 14.3.2 Watchdog Timer Control/Status Register (WTCSR) 14.3.3 Watchdog Reset Control/Status Register (WRCSR) 14.3.4 Notes on Register Access                                                                                |               |

| 14.1<br>14.2         | Features                                                                                                                                                                                                                                                                                                         |               |

| 14.1<br>14.2<br>14.3 | Features                                                                                                                                                                                                                                                                                                         |               |

| 14.1<br>14.2<br>14.3 | Features Input/Output Pin Register Descriptions 14.3.1 Watchdog Timer Counter (WTCNT) 14.3.2 Watchdog Timer Control/Status Register (WTCSR) 14.3.3 Watchdog Reset Control/Status Register (WRCSR) 14.3.4 Notes on Register Access WDT Usage 14.4.1 Canceling Software Standby Mode 14.4.2 Changing the Frequency |               |

| 14.1<br>14.2<br>14.3 | Features                                                                                                                                                                                                                                                                                                         |               |

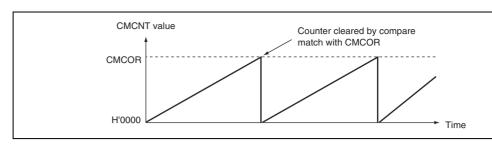

13.3 Operation ..... 13.3.1 Interval Count Operation .....

14.5 Usage Notes..... 14.5.1 Timer Variation..... 14.5.2 Prohibition against Setting H'FF to WTCNT.....

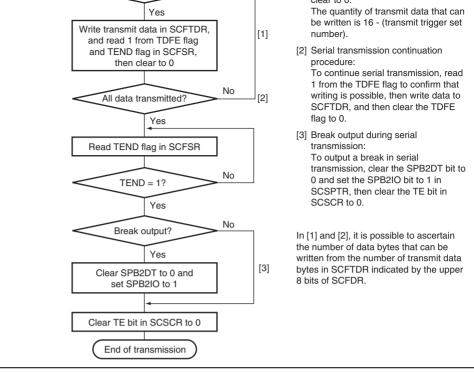

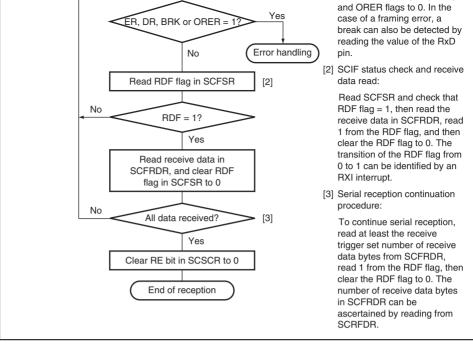

|        | 15.3.7 Serial Status Register (SCFSR)                                    |

|--------|--------------------------------------------------------------------------|

|        | 15.3.8 Bit Rate Register (SCBRR)                                         |

|        | 15.3.9 FIFO Control Register (SCFCR)                                     |

|        | 15.3.10 FIFO Data Count Register (SCFDR)                                 |

|        | 15.3.11 Serial Port Register (SCSPTR)                                    |

|        | 15.3.12 Line Status Register (SCLSR)                                     |

|        | 15.3.13 Serial Extended Mode Register (SCSEMR)                           |

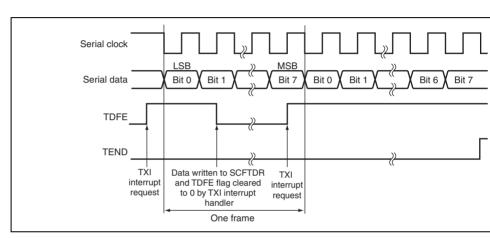

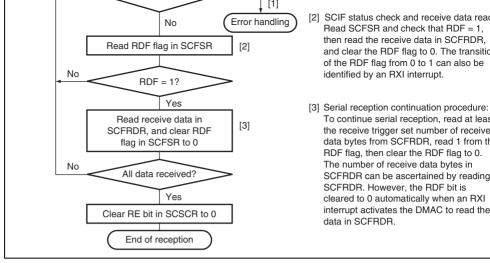

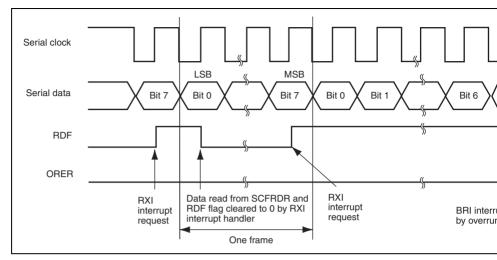

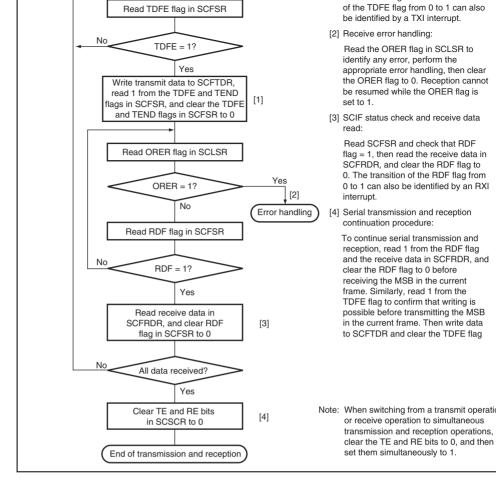

| 15.4   | Operation                                                                |

|        | 15.4.1 Overview                                                          |

|        | 15.4.2 Operation in Asynchronous Mode                                    |

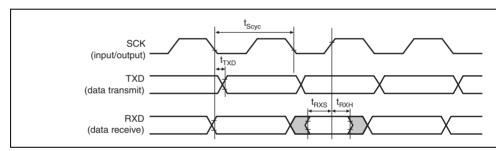

|        | 15.4.3 Operation in Clocked Synchronous Mode                             |

| 15.5   | SCIF Interrupts                                                          |

| 15.6   | Usage Notes                                                              |

|        | 15.6.1 SCFTDR Writing and TDFE Flag                                      |

|        | 15.6.2 SCFRDR Reading and RDF Flag                                       |

|        | 15.6.3 Restriction on DMAC Usage                                         |

|        | 15.6.4 Break Detection and Processing                                    |

|        | 15.6.5 Sending a Break Signal                                            |

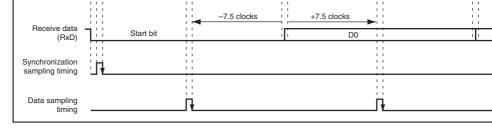

|        | 15.6.6 Receive Data Sampling Timing and Receive Margin (Asynchronous Moo |

|        | 15.6.7 FER and PER Flags in the Serial Status Register (SCFSR)           |

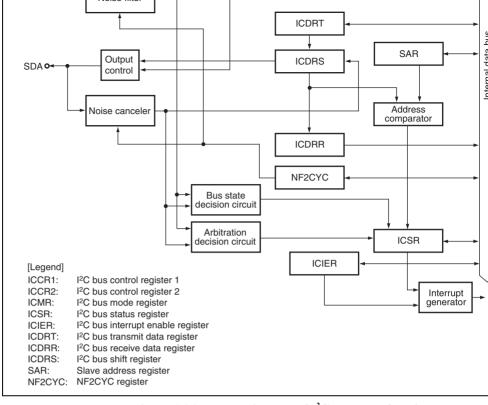

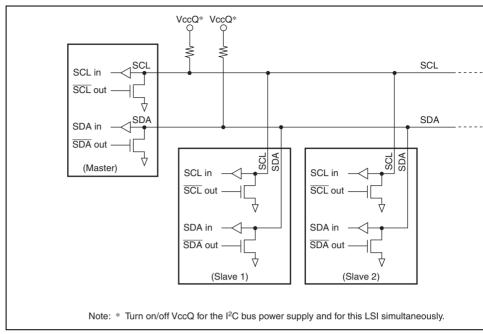

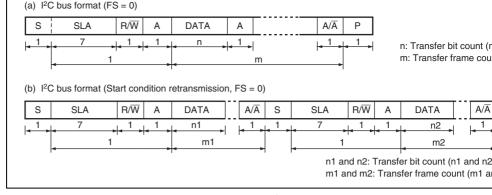

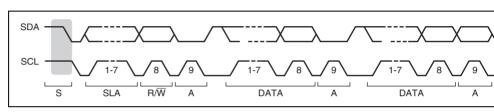

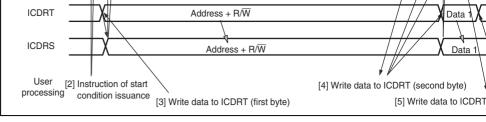

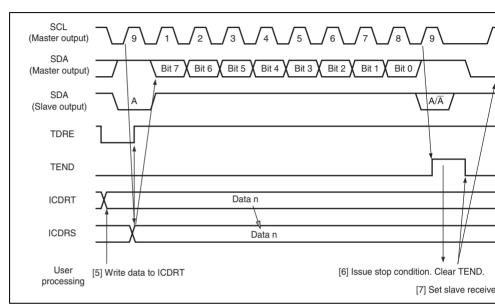

| Sect   | on 16 I <sup>2</sup> C Bus Interface 3 (IIC3)                            |

| 16.1   | Features                                                                 |

| 16.2   | Input/Output Pins                                                        |

| 16.2   | Register Descriptions                                                    |

| 10.5   | 16.3.1 I <sup>2</sup> C Bus Control Register 1 (ICCR1)                   |

|        | 16.3.2 I <sup>2</sup> C Bus Control Register 2 (ICCR2)                   |

|        | 10.3.2 1 C Dus Control Register 2 (ICCR2)                                |

| Dav. 1 | OO Mar OA 2000 Dama will of units                                        |

| Hev. 3 | 00 Mar. 04, 2009 Page xviii of xxiv                                      |

REJ09B0344-0300

RENESAS

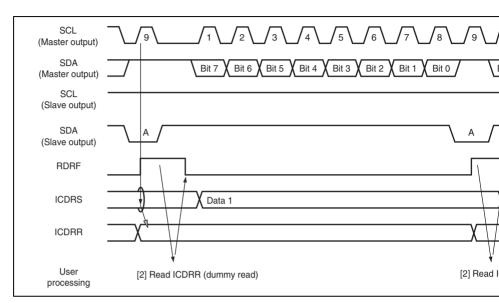

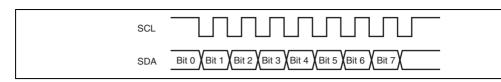

|      | 6.4.6 Clocked Synchronous   | Serial Format                             |

|------|-----------------------------|-------------------------------------------|

|      | 6.4.7 Noise Filter          |                                           |

|      |                             |                                           |

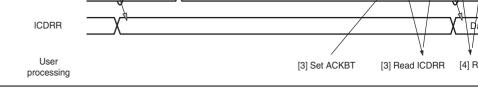

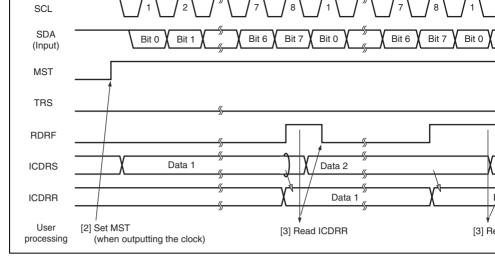

| 16.5 | nterrupt Requests           |                                           |

| 16.6 | Bit Synchronous Circuit     |                                           |

| 16.7 | Jsage Notes                 |                                           |

|      | 6.7.1 Note on Multiple Ma   | ster Usage                                |

|      | 6.7.2 Note on Master Rece   | ve Mode                                   |

|      | 6.7.3 Note on Master Rece   | ve Mode with ACKBT Setting                |

|      | 6.7.4 Note on MST and TR    | S Bit Status When an Arbitration was Lost |

|      |                             |                                           |

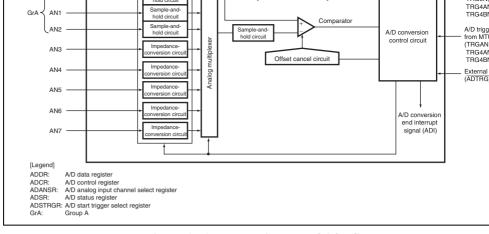

| Sect | n 17 A/D Converter (AI      | OC)                                       |

| 17.1 | Features                    |                                           |

| 17.2 | nput/Output Pins            |                                           |

| 17.3 | Register Descriptions       |                                           |

|      | 7.3.1 A/D Control Register  | (ADCR)                                    |

|      | 7.3.2 A/D Status Register ( | ADSR)                                     |

|      | 7.3.3 A/D Start Trigger Sel | ect Register (ADSTRGR)                    |

|      | 7.3.4 A/D Analog Input Ch   | annel Select Register (ADANSR)            |

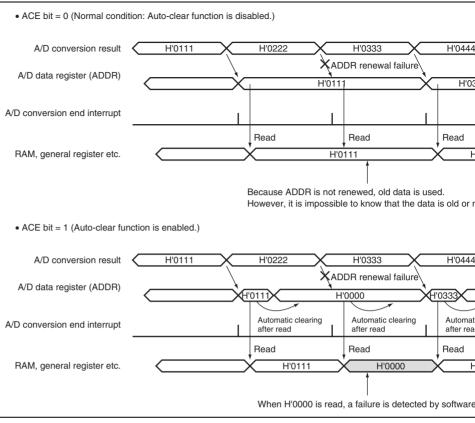

|      | 7.3.5 A/D Data Registers 0  | to 7 (ADDR0 to ADDR7)                     |

| 17.4 | Operation                   |                                           |

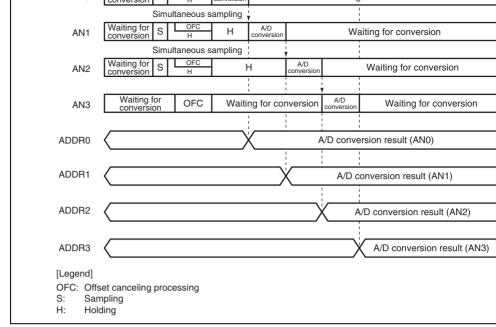

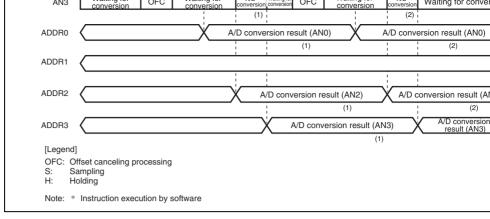

|      | 7.4.1 Single-Cycle Scan M   | ode                                       |

|      | 7.4.2 Continuous Scan Mo    | le                                        |

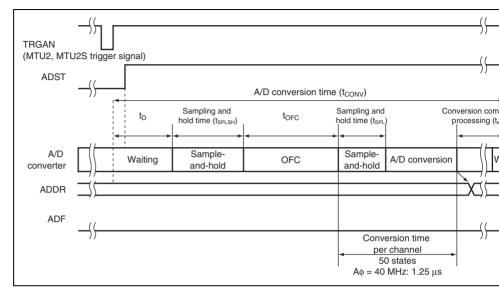

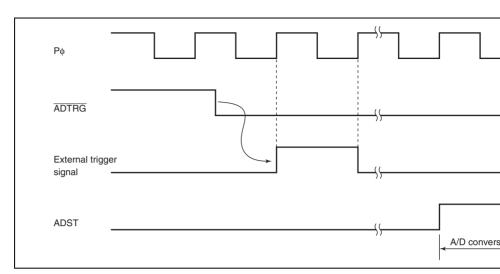

|      | 7.4.3 Input Sampling and A  | /D Conversion Time                        |

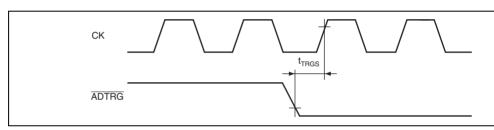

|      |                             | ation by MTU2 and MTU2S                   |

|      |                             | t Timing                                  |

|      |                             | -<br>                                     |

RENESAS

Rev. 3.00 Mar. 04, 2009 Pa

|                            | 18.2             | Input/Output Pins         |                                           |  |  |

|----------------------------|------------------|---------------------------|-------------------------------------------|--|--|

|                            | 18.3             | Register Descriptions     |                                           |  |  |

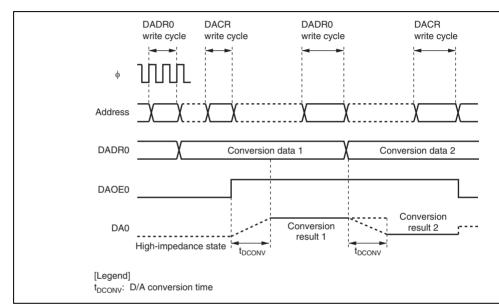

|                            |                  | 18.3.1 D/A Data Register  | s 0 and 1 (DADR0 and DADR1)               |  |  |

|                            |                  | 18.3.2 D/A Control Regis  | ter (DACR)                                |  |  |

|                            | 18.4             | Operation                 |                                           |  |  |

|                            | 18.5 Usage Notes |                           |                                           |  |  |

|                            |                  | 18.5.1 Module Standby M   | Iode Setting                              |  |  |

|                            |                  | 18.5.2 D/A Output Hold    | Function in Software Standby Mode         |  |  |

|                            |                  | 18.5.3 Setting Analog Inp | ut Voltage                                |  |  |

|                            |                  |                           |                                           |  |  |

|                            | Secti            |                           | ntroller (PFC)                            |  |  |

| 19.1 Register Descriptions |                  |                           |                                           |  |  |

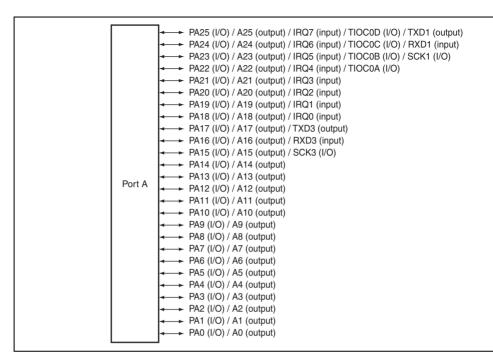

|                            |                  | 19.1.1 Port A I/O Registe | rs H, L (PAIORH, PAIORL)                  |  |  |

|                            |                  | 19.1.2 Port A Control Reg |                                           |  |  |

|                            |                  | (PACRH1 to PAC            | RH3, PACRL1 to PACRL4)                    |  |  |

|                            |                  | 19.1.3 Port B I/O Registe | rs H, L (PBIORH, PBIORL)                  |  |  |

|                            |                  | 19.1.4 Port B Control Reg | gisters H1 to H4, L1 to L4                |  |  |

|                            |                  | (PBCRH1 to PBC)           | RH4, PBCRL1 to PBCRL4)                    |  |  |

|                            |                  | 19.1.5 Port D I/O Registe | r (PDIOR)                                 |  |  |

|                            |                  |                           | gisters L1 to L4 (PDCRL1 to PDCRL4)       |  |  |

|                            |                  | 19.1.7 Port F Control Reg | sister L1 (PFCRL1)                        |  |  |

|                            |                  | 19.1.8 IRQOUT Function    | Control Register (IFCR)                   |  |  |

|                            |                  | 19.1.9 WAVE Function (    | Control Registers 1, 2 (WAVECR1, WAVECR2) |  |  |

|                            |                  |                           |                                           |  |  |

RENESAS

Rev. 3.00 Mar. 04, 2009 Page xx of xxiv

REJ09B0344-0300

|      |          | NOIE                                     |  |  |  |  |

|------|----------|------------------------------------------|--|--|--|--|

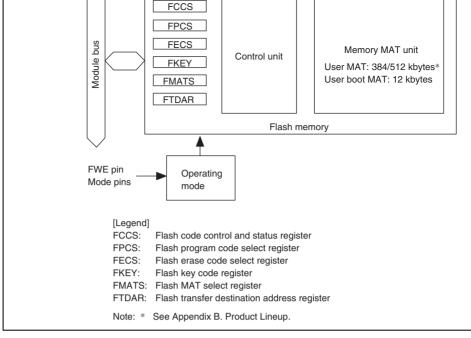

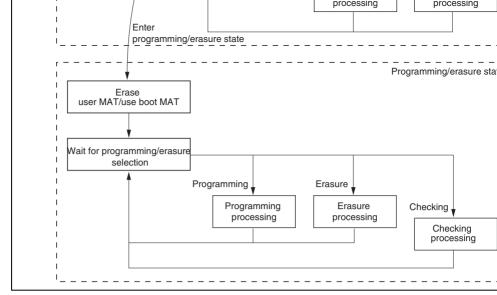

| Sect | ion 21 F | Flash Memory                             |  |  |  |  |

| 21.1 |          | S                                        |  |  |  |  |

| 21.2 | Overview |                                          |  |  |  |  |

|      |          | Block Diagram                            |  |  |  |  |

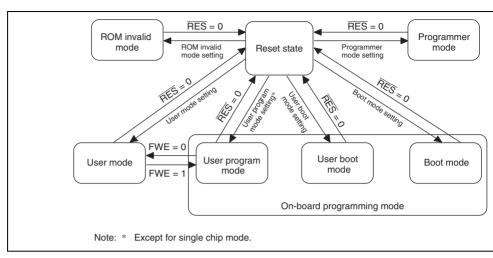

|      |          | Operating Mode                           |  |  |  |  |

|      | 21.2.3   | Mode Comparison                          |  |  |  |  |

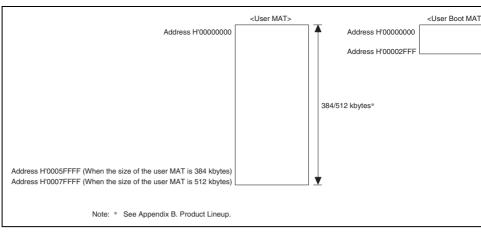

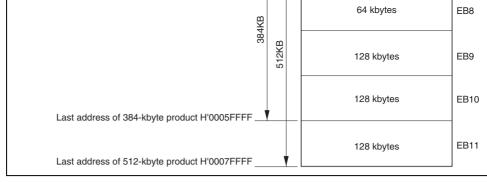

|      | 21.2.4   | Flash Memory Configuration               |  |  |  |  |

|      | 21.2.5   | Block Division                           |  |  |  |  |

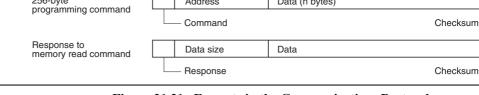

|      | 21.2.6   | Programming/Erasing Interface            |  |  |  |  |

| 21.3 | Input/O  | utput Pins                               |  |  |  |  |

| 21.4 | Register | r Descriptions                           |  |  |  |  |

|      | 21.4.1   | Registers                                |  |  |  |  |

|      | 21.4.2   | Programming/Erasing Interface Registers  |  |  |  |  |

|      | 21.4.3   | Programming/Erasing Interface Parameters |  |  |  |  |

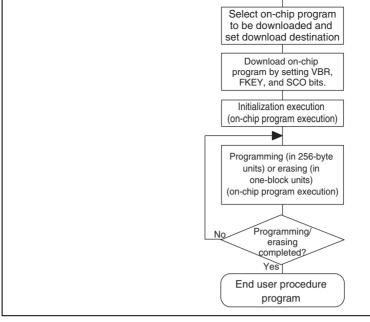

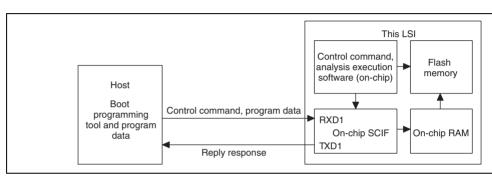

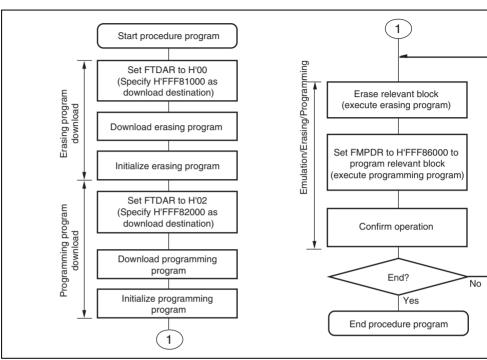

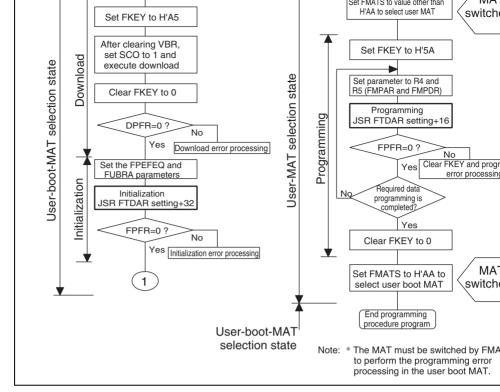

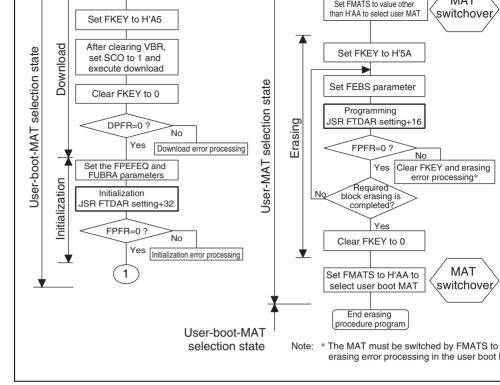

| 21.5 | On-Boa   | rd Programming Mode                      |  |  |  |  |

|      | 21.5.1   | Boot Mode                                |  |  |  |  |

|      | 21.5.2   | User Program Mode                        |  |  |  |  |

|      | 21.5.3   | User Boot Mode                           |  |  |  |  |

| 21.6 |          | on                                       |  |  |  |  |

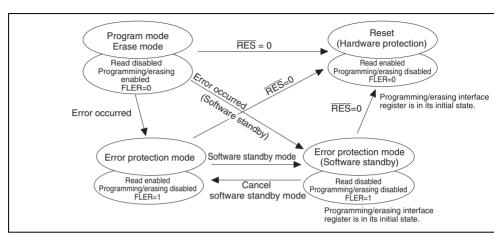

|      | 21.6.1   | Hardware Protection                      |  |  |  |  |

20.4.2 Port F Data Register (PFDR)

Rev. 3.00 Mar. 04, 2009 Pa

REJ09

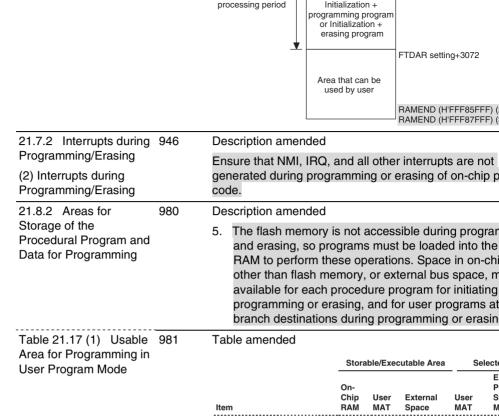

21.6.2 Software Protection..... 21.6.3 Error Protection. 21.7 Usage Notes 21.7.1 Switching between User MAT and User Boot MAT..... 21.7.2 Interrupts during Programming/Erasing ..... 21.7.3 Other Notes.....

| _                                               |                                                                                                                                              |  |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                 | S                                                                                                                                            |  |  |  |  |

|                                                 | Power-Down Modes                                                                                                                             |  |  |  |  |

|                                                 | Reset                                                                                                                                        |  |  |  |  |

| Input/Output Pins                               |                                                                                                                                              |  |  |  |  |

| Registe                                         | r Descriptions                                                                                                                               |  |  |  |  |

| 23.3.1                                          | Standby Control Register (STBCR)                                                                                                             |  |  |  |  |

| 23.3.2                                          | Standby Control Register 2 (STBCR2)                                                                                                          |  |  |  |  |

| 23.3.3                                          | Standby Control Register 3 (STBCR3)                                                                                                          |  |  |  |  |

| 23.3.4                                          | Standby Control Register 4 (STBCR4)                                                                                                          |  |  |  |  |

|                                                 | System Control Register 1 (SYSCR1)                                                                                                           |  |  |  |  |

|                                                 | System Control Register 2 (SYSCR2)                                                                                                           |  |  |  |  |

| Operati                                         | on                                                                                                                                           |  |  |  |  |

| 23.4.1                                          | Sleep Mode                                                                                                                                   |  |  |  |  |

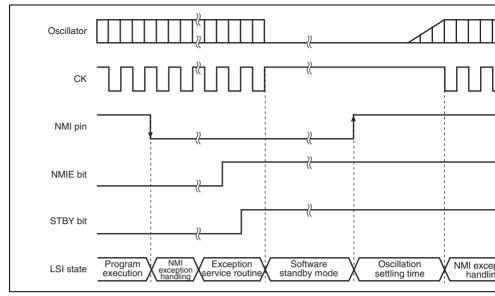

|                                                 | Software Standby Mode                                                                                                                        |  |  |  |  |

| 23.4.3                                          | Software Standby Mode Application Example                                                                                                    |  |  |  |  |

|                                                 | Module Standby Function                                                                                                                      |  |  |  |  |

|                                                 |                                                                                                                                              |  |  |  |  |

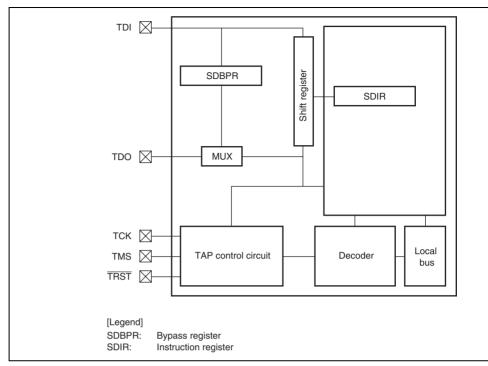

| on 24 U                                         | User Debugging Interface (H-UDI)                                                                                                             |  |  |  |  |

| Feature                                         | S                                                                                                                                            |  |  |  |  |

| Input/Output Pins                               |                                                                                                                                              |  |  |  |  |

| -                                               |                                                                                                                                              |  |  |  |  |

| Registe                                         | -                                                                                                                                            |  |  |  |  |

| _                                               | r Descriptions                                                                                                                               |  |  |  |  |

| 24.3.1                                          | r Descriptions                                                                                                                               |  |  |  |  |

| 24.3.1<br>24.3.2                                | r Descriptions  Bypass Register (SDBPR)  Instruction Register (SDIR)                                                                         |  |  |  |  |

| 24.3.1<br>24.3.2<br>Operati                     | r Descriptions                                                                                                                               |  |  |  |  |

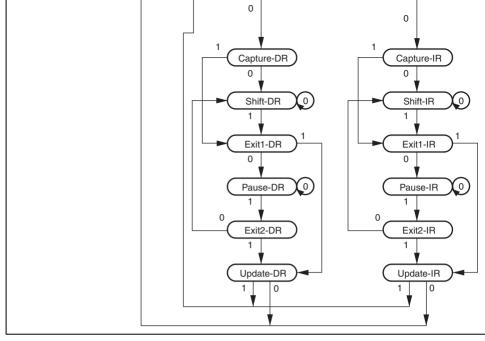

| 24.3.1<br>24.3.2<br>Operati<br>24.4.1           | r Descriptions Bypass Register (SDBPR) Instruction Register (SDIR) on TAP Controller                                                         |  |  |  |  |

| 24.3.1<br>24.3.2<br>Operati<br>24.4.1<br>24.4.2 | r Descriptions                                                                                                                               |  |  |  |  |

|                                                 | 23.1.1<br>23.1.2<br>Input/O<br>Registe<br>23.3.1<br>23.3.2<br>23.3.3<br>23.3.4<br>23.3.5<br>23.4.1<br>23.4.2<br>23.4.3<br>23.4.4<br>ion 24 U |  |  |  |  |

RENESAS

Rev. 3.00 Mar. 04, 2009 Page xxii of xxiv

REJ09B0344-0300

Section 23 Power-Down Modes

| Secti | on 27 E                     | Electrical Characteristics                |  |  |  |  |  |

|-------|-----------------------------|-------------------------------------------|--|--|--|--|--|

| 27.1  | Absolute Maximum Ratings    |                                           |  |  |  |  |  |

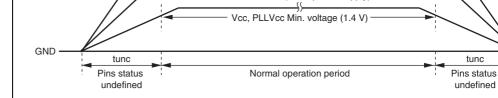

| 27.2  | Power-on/Power-off Sequence |                                           |  |  |  |  |  |

| 27.3  |                             | aracteristics                             |  |  |  |  |  |

| 27.4  |                             | aracteristics                             |  |  |  |  |  |

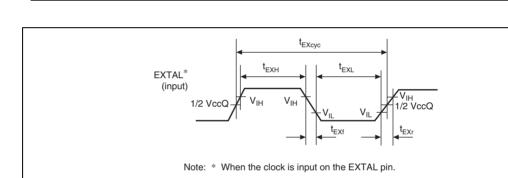

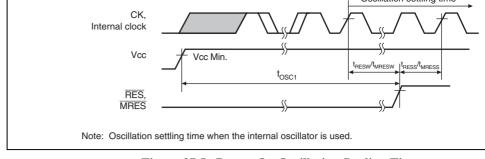

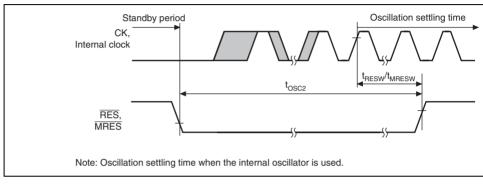

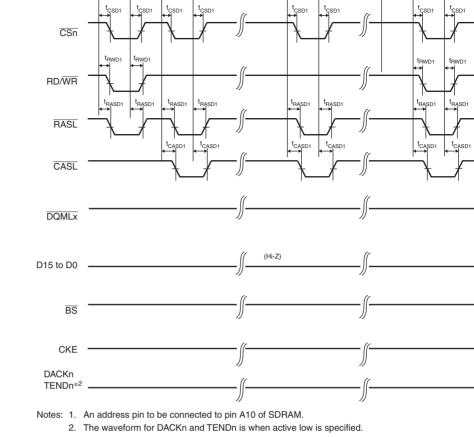

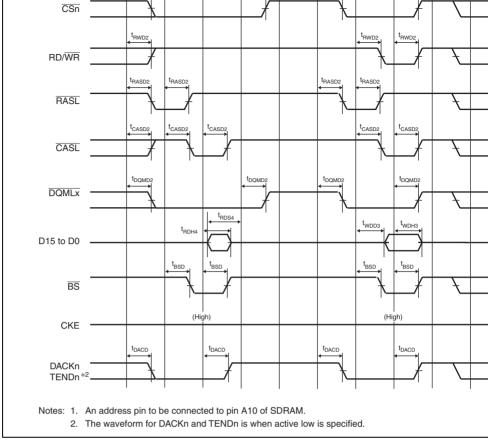

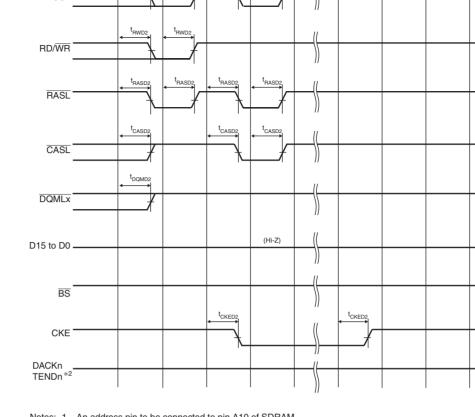

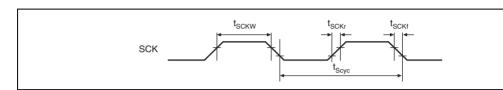

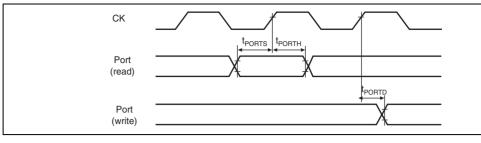

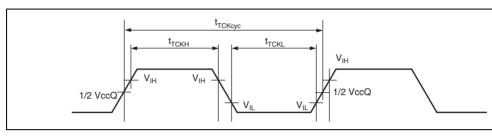

|       | 27.4.1                      | Clock Timing                              |  |  |  |  |  |

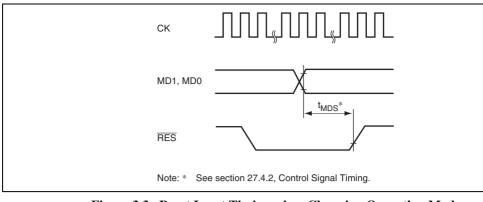

|       | 27.4.2                      | Control Signal Timing                     |  |  |  |  |  |

|       |                             | Bus Timing                                |  |  |  |  |  |

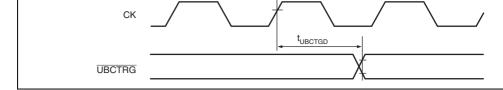

|       |                             | UBC Trigger Timing                        |  |  |  |  |  |

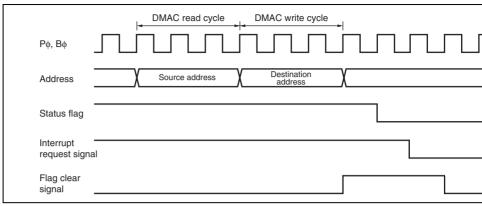

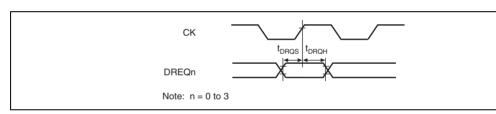

|       |                             | DMAC Module Timing                        |  |  |  |  |  |

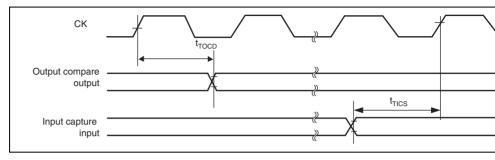

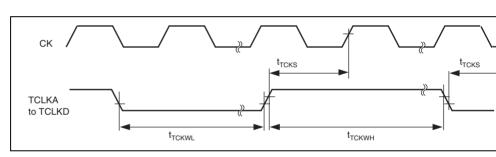

|       |                             | MTU2, MTU2S Module Timing                 |  |  |  |  |  |

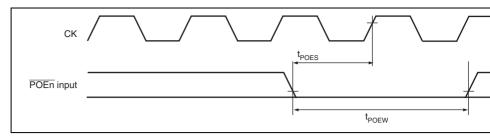

|       |                             | POE2 Module Timing                        |  |  |  |  |  |

|       | 27.4.8                      | Watchdog Timer Timing                     |  |  |  |  |  |

|       | 27.4.9                      | SCIF Module Timing                        |  |  |  |  |  |

|       |                             | IIC3 Module Timing                        |  |  |  |  |  |

|       | 27.4.11                     | A/D Trigger Input Timing                  |  |  |  |  |  |

|       | 27.4.12                     | I/O Port Timing                           |  |  |  |  |  |

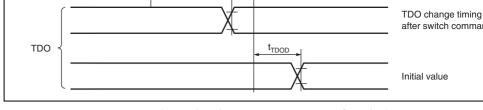

|       |                             | H-UDI Related Pin Timing                  |  |  |  |  |  |

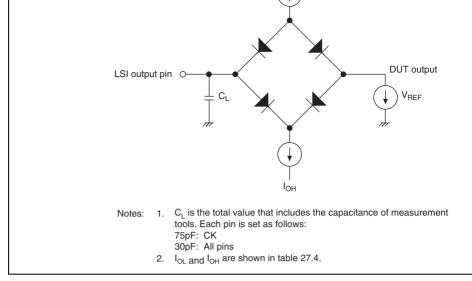

|       |                             | AC Characteristics Measurement Conditions |  |  |  |  |  |

27.5

27.7

A. B.

C.

**Appendix**

26.3 Register States in Each Operating Mode.....

Pin States....

Product Lineup.....

Package Dimensions

A/D Converter Characteristics.... 27.6 D/A Converter Characteristics Flash Memory Characteristics

.....

Rev. 3.00 Mar. 04, 2009 Page xxiv of xxiv

REJ09B0344-0300

With this CPU, it has become possible to assemble low-cost, high-performance, and high functioning systems, even for applications that were previously impossible with micropa such as realtime control, which demands high speeds.

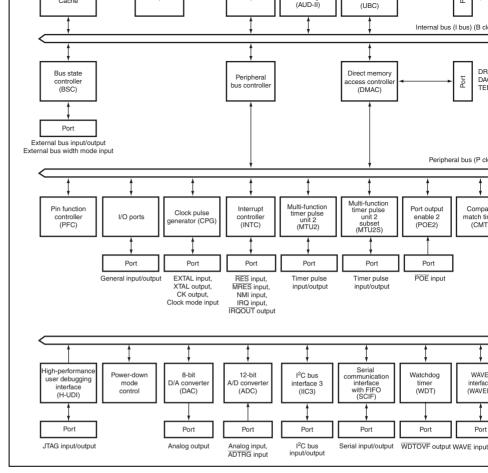

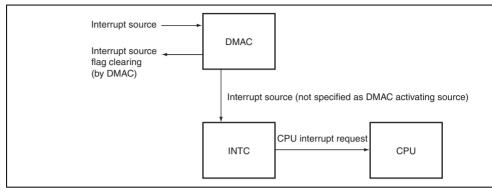

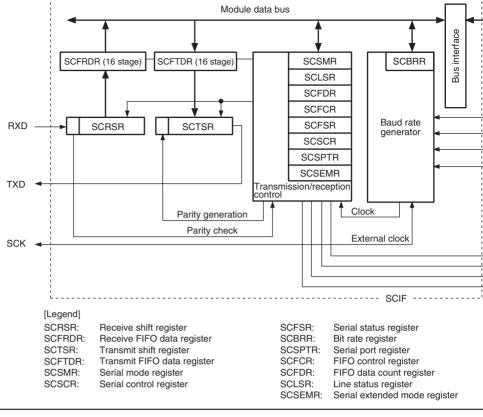

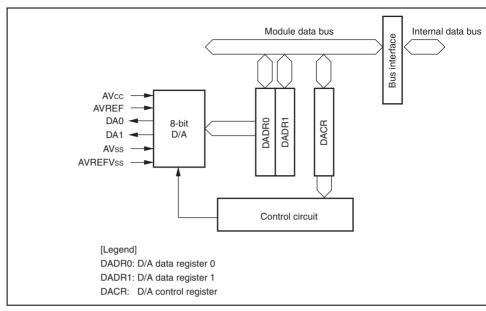

In addition, this LSI includes on-chip peripheral functions necessary for system configu such as a large-capacity ROM, a ROM cache, a RAM, a direct memory access controlle (DMAC), multi-function timer pulse units 2 (MTU2 and MTU2S), a serial communication interface with FIFO (SCIF), an A/D converter, a D/A converter, an interrupt controller ( I/O ports, and I<sup>2</sup>C bus interface 3 (IIC3).

This LSI also provides an external memory access support function to enable direct con various memory devices or peripheral LSIs.

These on-chip functions significantly reduce costs of designing and manufacturing appl systems.

The features of this LSI are listed in table 1.1.

|   | Register bank for high-speed response to interrupts                                                                                                              |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | RISC-type instruction set (upward compatible with SH series)                                                                                                     |

|   | <ul> <li>Instruction length: 16-bit fixed-length basic instructions for<br/>code efficiency and 32-bit instructions for high performanc<br/>usability</li> </ul> |

|   | <ul> <li>Load/store architecture</li> </ul>                                                                                                                      |

|   | <ul> <li>Delayed branch instructions</li> </ul>                                                                                                                  |

|   | <ul> <li>Instruction set based on C language</li> </ul>                                                                                                          |

| • | Superscalar architecture to execute two instructions at one time                                                                                                 |

| • | Instruction execution time: Up to two instructions/cycle                                                                                                         |

| • | Address space: 4 Gbytes                                                                                                                                          |

| • | Internal multiplier                                                                                                                                              |

| • | Five-stage pipeline                                                                                                                                              |

| • | Operating modes                                                                                                                                                  |

|   | Extended ROM enabled mode                                                                                                                                        |

|   | Single-chip mode                                                                                                                                                 |

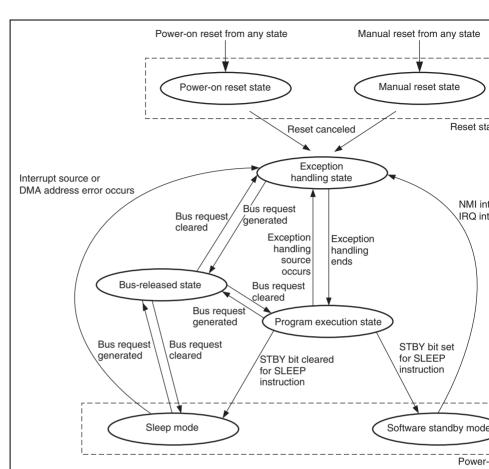

| • | Processing states                                                                                                                                                |

|   | Program execution state                                                                                                                                          |

|   | Exception handling state                                                                                                                                         |

|   | Bus mastership release state                                                                                                                                     |

| • | Power-down modes                                                                                                                                                 |

|   | Sleep mode                                                                                                                                                       |

Rev. 3.00 Mar. 04, 2009 Page 2 of 1168

Operating modes

REJ09B0344-0300 **₹ENESAS**

Software standby mode Module standby mode

| Bus state controller (BSC) | <ul> <li>Address space divided into eight areas (0 to 7), each a maximum Mbytes</li> </ul>                                               |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|                            | External bus: 8 or 16 bits                                                                                                               |

|                            | The following features settable for each area independently                                                                              |

|                            | <ul> <li>Supports both big endian and little endian for data acces</li> </ul>                                                            |

|                            | <ul> <li>Bus size (8 or 16 bits): Available sizes depend on the are</li> </ul>                                                           |

|                            | <ul> <li>Number of access wait cycles (different wait cycles can be specified for read and write access cycles in some areas)</li> </ul> |

|                            | <ul> <li>Idle wait cycle insertion (between same area access cycles)</li> </ul>                                                          |

|                            | <ul> <li>Specifying the memory to be connected to each area en</li> </ul>                                                                |

To priority levels available

processing

Register bank enabling fast register saving and restoring in in

direct connection to SRAM, SRAM with byte selection, Si and burst ROM (clocked synchronous or asynchronous). address/data multiplexed I/O (MPX) interface is also avail—

Outputs a chip select signal (CSO to CS7) according to the area (CS assert or negate timing can be selected by soft

SDRAM burst access

SDRAM refresh

Auto refresh or self refresh mode selectable

Rev. 3.00 Mar. 04, 2009 Pa

|                  |   | <ul><li>— Bus clock: Maximum 40 MHz</li><li>— Peripheral clock: Maximum 40 MHz</li></ul> |  |  |  |  |

|------------------|---|------------------------------------------------------------------------------------------|--|--|--|--|

|                  |   |                                                                                          |  |  |  |  |

|                  |   | — Timer clock: Maximum 80 MHz                                                            |  |  |  |  |

|                  |   | <ul> <li>AD clock: Maximum 40 MHz</li> </ul>                                             |  |  |  |  |

| Watchdog timer   | • | On-chip one-channel watchdog timer                                                       |  |  |  |  |

| (WDT)            | • | A counter overflow can reset the LSI                                                     |  |  |  |  |

| Power-down modes |   | Three power-down modes provided to reduce the current con in this LSI                    |  |  |  |  |

|                  |   | — Sleep mode                                                                             |  |  |  |  |

|                  |   | <ul> <li>Software standby mode</li> </ul>                                                |  |  |  |  |

|                  |   | <ul> <li>Module standby mode</li> </ul>                                                  |  |  |  |  |

— CPU clock: Maximum 160 MHz

Rev. 3.00 Mar. 04, 2009 Page 4 of 1168

|                       |   | <ul> <li>Non-overlapping waveforms output for 3-phase inverter of</li> </ul>               |

|-----------------------|---|--------------------------------------------------------------------------------------------|

|                       |   | <ul> <li>Automatic dead time setting</li> </ul>                                            |

|                       |   | — 0% to 100% PWM duty value specifiable                                                    |

|                       |   | <ul> <li>A/D conversion delaying function</li> </ul>                                       |

|                       |   | <ul> <li>Interrupt skipping at crest or trough</li> </ul>                                  |

| •                     | • | Reset-synchronized PWM mode                                                                |

|                       |   | Three-phase PWM waveforms in positive and negative phase output with a required duty value |

| •                     | • | Phase counting mode                                                                        |

|                       |   | Two-phase encoder pulse counting available                                                 |

| Multi-function timer  | • | Subset of MTU2, included in channels 3 to 5                                                |

| pulse unit 2S (MTU2S) | • | Operating at 80 MHz max.                                                                   |

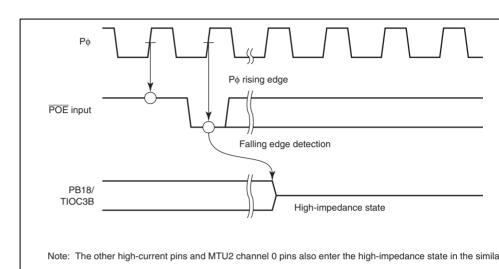

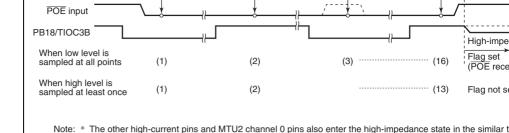

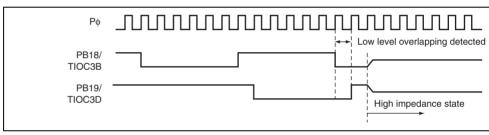

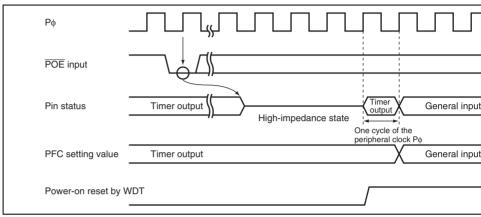

| Port output enable 2  | • | High-impedance control of high-current pins at a falling edge                              |

| (POE2)                |   | level input on the POE pin                                                                 |

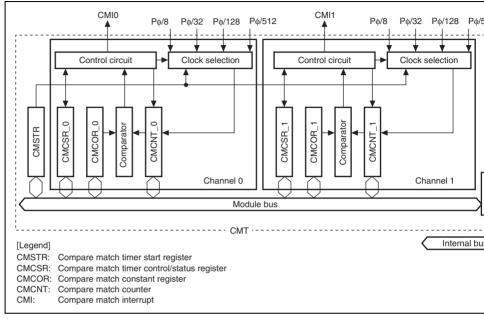

| Compare match timer   | • | Two-channel 16-bit counters                                                                |

| (CMT)                 | • | Four types of clock can be selected (P $\phi$ /8, P $\phi$ /32, P $\phi$ /128, ar          |

| •                     | • | DMA transfer request or interrupt request can be issued whe                                |

|                       |   |                                                                                            |

compare match occurs

Four channels

supported

(SCIF)

Serial communication

interface with FIFO

Dedicated baud rate generator Separate 16-byte FIFO registers for transmission and recept

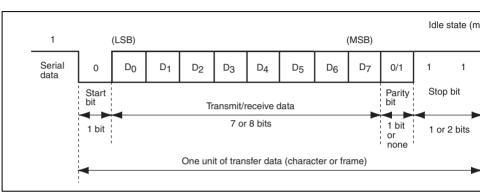

Clocked synchronous or asynchronous mode selectable

Simultaneous transmission and reception (full-duplex commu

|                            | I wo output channels                                                               |

|----------------------------|------------------------------------------------------------------------------------|

| User break controller      | Four break channels                                                                |

| (UBC)                      | Addresses, type of access, and data size can all be set as breathing.              |

|                            | conditions                                                                         |

| User debugging             | E10A emulator support                                                              |

| interface (H-UDI)          | JTAG-standard pin assignment                                                       |

|                            | Realtime branch trace                                                              |

| Advanced user              | Six output pins                                                                    |

| debugger II (AUD- II)      | Branch source address/destination address trace                                    |

|                            | Window data trace                                                                  |

|                            | Full trace                                                                         |

|                            | All trace data can be output by interrupting CPU operation                         |

|                            | Realtime trace                                                                     |

|                            | Trace data can be output within the range where CPU operation interrupted          |

| WAVE interface<br>(WAVEIF) | <ul> <li>Myway Labs realtime CPU scope "WAVE™" (WAVE1.0 Level supported</li> </ul> |

| On-chip ROM                | 384/512 Kbytes (See B. Product Lineup)                                             |

| On-chip RAM                | Three/Four pages                                                                   |

|                            | • 24/32 Kbytes (See B. Product Lineup)                                             |

| Power supply voltage       | Vcc: 1.4 to 1.6 V                                                                  |

|                            | <ul> <li>VccQ: 3.0 to 3.6 V</li> </ul>                                             |

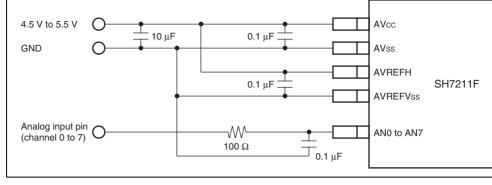

|                            | AVcc: 4.5 to 5.5 V                                                                 |

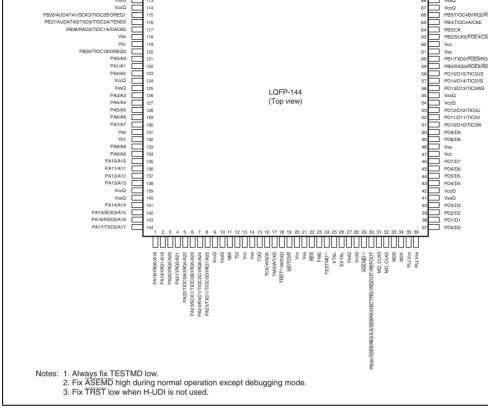

| Packages                   | • LQFP2020-144 (0.5 pitch)                                                         |

|                            |                                                                                    |

RENESAS

Rev. 3.00 Mar. 04, 2009 Page 6 of 1168

REJ09B0344-0300

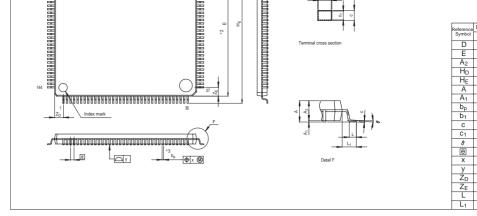

Figure 1.1 Block Diagram

RENESAS

Rev. 3.00 Mar. 04, 2009 Pa

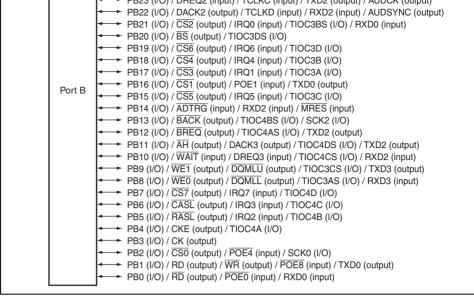

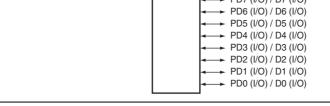

Figure 1.2 Pin Arrangement

Rev. 3.00 Mar. 04, 2009 Page 8 of 1168 REJ09B0344-0300

RENESAS

|       |        |   |                         | · · · · · · · · · · · · · · · · · · ·                                                                                       |