### Introduction

The 8T49N1012 evaluation board user guide is intended to help the user power-up and quick-start the 8T49N1012 evaluation board. The scope of the user guide is limited to the physical connectivity of the board and does not address the programming section of it.

This guide will model two set-ups: Set-up 1 will use a clock generator as input and Set-up 2 will use a crystal as input source.

### Set-up 1:

- CLK/nCLK will be used as input

- Q0/nQ0 will be used as output

### Set-up 2:

- OSCI/OSCO will be used as input

- Q0/nQ0 will be used as output

## **Board Overview**

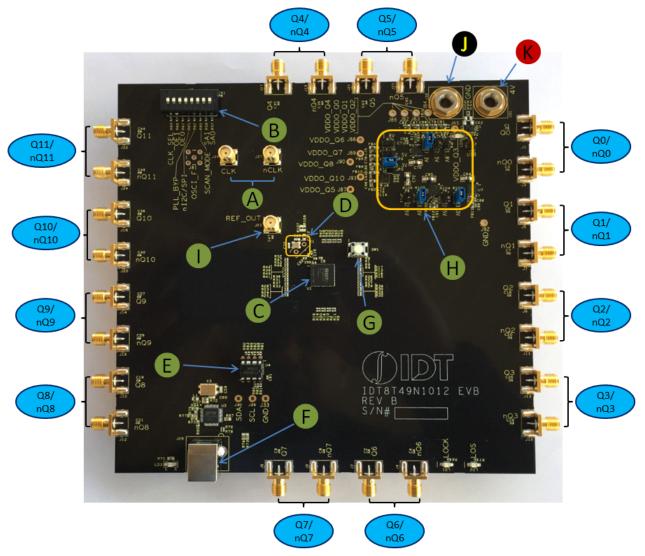

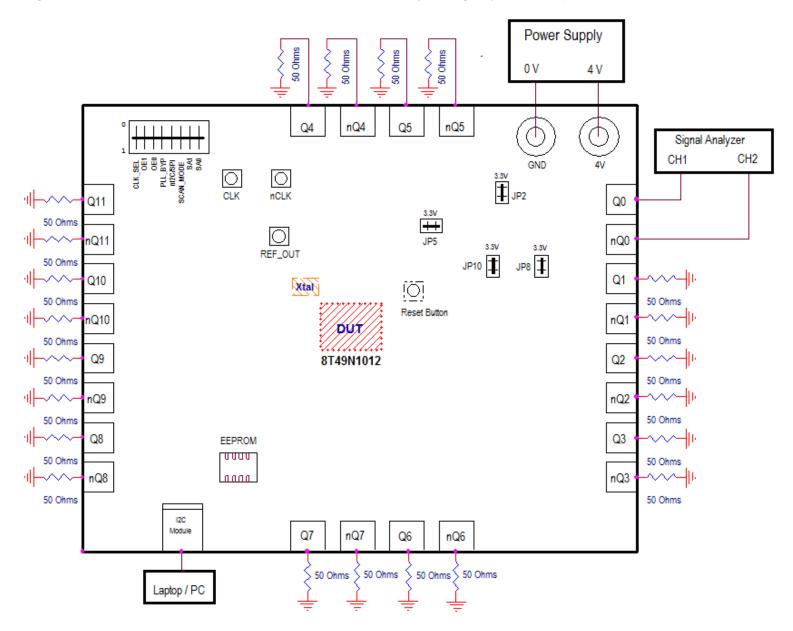

Use Figure 1 to identify the power supply jacks, input and output SMA connectors, USB connector, crystal, power selection jumpers, dip switch, device under test, EEPROM, Reset button, CLK/nCLK Inputs and Ref\_Out.

### Figure 1. 8T49N1012 Evaluation Board Top View

## Requirements

- Power supply with 4V and ~800mA rating

- Signal generator (10MHz to 600MHz Input and an amplitude from 0.4V to 0.8V) or crystal

- Signal analyzer

- Two banana plug cables (red and black) to connect the power supply source to the board

- Two SMA cables to connect the signal generator to the CLK/nCLK inputs

- Two SMA cables to connect Q0/nQ0 to the signal analyzer

- $50\Omega$  to ground terminators to terminate the unused outputs

- USB cable to connect the board to a laptop and program the device

### **DIP Switch Pin**

### Table 1: DIP Switch Pin Description

| Pin Name              | Description                                                                                                 |

|-----------------------|-------------------------------------------------------------------------------------------------------------|

| CLK_SEL               | Clock select pin. 0: CLK/nCLK; 1: XTAL (Default)                                                            |

| OE1                   | Output enable. LVCMOS/LVTTL interface levels                                                                |

| OE0                   | Output enable. LVCMOS/LVTTL interface levels.                                                               |

| PLL_BYP               | Bypass Selection. Allow PLL references to bypass PLL and appear at Q[0:3]. LVTTL / LVCMOS interface levels. |

| nl <sup>2</sup> C/SPI | Serial Interface Mode Selection. LVCMOS Input Levels: 0 = I <sup>2</sup> C Mode; 1 = SPI Mode               |

| SCAN_MODE             | (Factory Use Only)                                                                                          |

| SA1                   | I <sup>2</sup> C lower address bit A1 / SPI interface serial data input signal.                             |

| SA0                   | I <sup>2</sup> C lower address bit A0 / SPI interface chip select signal.                                   |

### Legend–Evaluation Board

### <u>Inputs</u>

CLK/nCLK Clock input lines. Can accept LVPECL, LVDS, LVHSTL, HCSL or LVCMOS input clock. OSCI/OSCO Crystal input lines.

### <u>Outputs</u>

| Q0/nQ0   | Can be a differential pair or two individual single-ended outputs. |

|----------|--------------------------------------------------------------------|

| Q1/nQ1   | Can be a differential pair or two individual single-ended outputs. |

| Q2/nQ2   | Can be a differential pair or two individual single-ended outputs. |

| Q3/nQ3   | Can be a differential pair or two individual single-ended outputs. |

| Q4/nQ4   | Can be a differential pair or two individual single-ended outputs. |

| Q5/nQ5   | Can be a differential pair or two individual single-ended outputs. |

| Q6/nQ6   | Can be a differential pair or two individual single-ended outputs. |

| Q7/nQ7   | Can be a differential pair or two individual single-ended outputs. |

| Q8/nQ8   | Can be a differential pair or two individual single-ended outputs. |

| Q9/nQ9   | Can be a differential pair or two individual single-ended outputs. |

| Q10/nQ10 | Can be a differential pair or two individual single-ended outputs. |

| Q11/nQ11 | Can be a differential pair or two individual single-ended outputs. |

# RENESAS

### **Other**

| CLK and nCLK Inputs                                        |

|------------------------------------------------------------|

| Dip Switch for DC control signals (CLK_SEL, PLL_BYP, etc). |

| Device Under Test - 8T49N1012                              |

| 3.2 x 2.5 mm SMD Fox-603-38.88-4 Crystal.                  |

| EEPROM - AT24CO4C.                                         |

| USB connector.                                             |

| RESET Button.                                              |

| Power Selection Headers and Jumpers.                       |

| REF_OUT. Single-ended 1.8V LVCMOS Output.                  |

| Ground Connection Jack.                                    |

| VDD Connection Jack.                                       |

|                                                            |

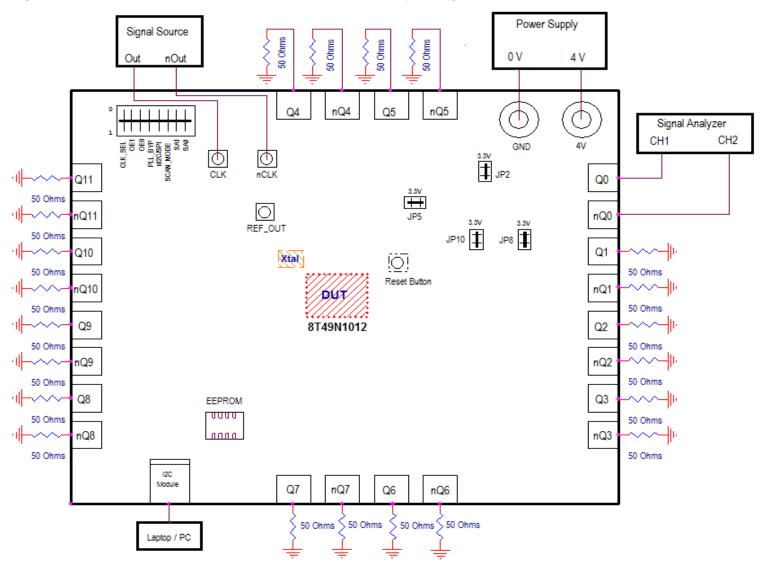

## **Quick Set-Up 1: Using Clock Generator as Input**

- 1) Set power supply to 4V, single supply and set CLK\_SEL to "0" on Dip Switch to select Clock as input.

- 2) Place jumpers on JP2, JP5, JP8 and JP10 to set VDD, VDDO and VDDA to 3.3V (if different voltage required, place jumper on the corresponding header).

- 3) Connect the black GND power supply cable to the GND connector of the 8T49N1012 board.

- 4) Connect the red 4 V power supply cable to the 4 V connector of the board.

- 5) Connect the signal generator's SMA cables to CLK/nCLK (10MHz to 600MHz Input and amplitude from 0.4V to 0.8V). 50Ω to GND termination installed on board by default.

- 6) Connect two SMA cables from the Q0/nQ0 outputs of the board to the signal analyzer.

- 7) And finally, connect the USB cable from the laptop to the board's USB connector and program the device using Timing Commander.

### Figure 2. Evaluation Board Powered Up and Connectivity Using Clock as Input

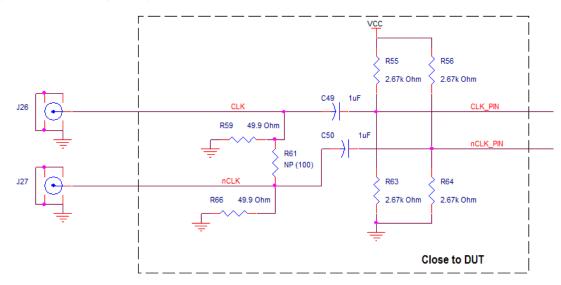

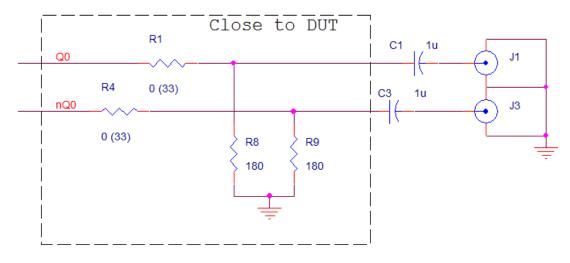

## **Schematics**

The following figures are schematics that are applicable when using a signal generator as input. The complete schematic is available in a separate document. These are the input and output termination schematics.

The input schematic is shown in Figure 3.

### Figure 3. Input Schematic (Set-up #1)

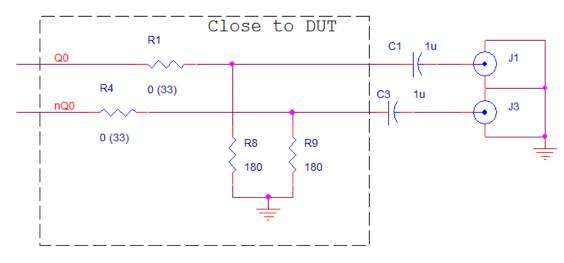

The output schematic is shown in Figure 4.

### Figure 4. Output Schematic (Set-up #1)

## Quick Set-Up 2: Using Crystal as Input

- 1) Set power supply to 4V, single supply and set CLK\_SEL to "1" on Dip Switch to select Crystal as input.

- 2) Place jumpers on JP2, JP5, JP8 and JP10 to set VDD, VDDO and VDDA to 3.3V (if different voltage required, place jumper on the corresponding header).

- 3) Connect the black GND power supply cable to the GND connector of the 8T49N1012 board.

- 4) Connect the red 4 V power supply cable to the 4 V connector of the board.

- 5) Connect two SMA cables from the Q0/nQ0 outputs of the board to the signal analyzer.

- 6) Ultimately, connect the USB cable from the laptop to the board's USB connector and program the device using Timing Commander.

### Figure 5. Evaluation Board Powered Up and Connectivity Using Crystal as Input

### **Schematics**

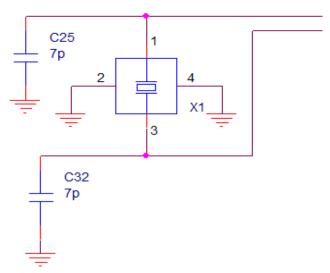

The following figures are schematics that are applicable when using the crystal as input. The complete schematic is available in a separate document. These are the input and output termination schematics.

The input schematic is shown in Figure 6.

#### Figure 6. Input Schematic (Set-Up #2)

The output schematic is shown in Figure 7.

### Figure 7. Output Schematic

\* If the output frequency is below 50MHz, increase the value of C1 and C3.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock & Timer Development Tools category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

AD9517-0A/PCBZ AD9517-2A/PCBZ AD9522-4/PCBZ AD9520-5PCBZ AD9553/PCBZ ADCLK914PCBZ LMH2180SDEVAL DSC400-0333Q0032KE1-EVB TDGL013 MAX2880EVKIT# MAX2750EVKIT MAX2752EVKIT ADCLK946PCBZ ADCLK946/PCBZ MAX2622EVKIT EKIT01-HMC1032LP6G Si5332-8IX-EVB RV-2251-C3-EVALUATION-BOARD Si5332-12IX-EVB RV-3029-C2-EVALUATION-BOARD-OPTION-B Si5332-6IX-EVB SKY72310-11-EVB EV1HMC8364LP6G RV-8263-C7-EVALUATION-BOARD EVK9FGV1002 EVK9FGV1008 EV1HMC6832ALP5L EVAL01-HMC830LP6GE EVAL01-HMC911LC4B TS3002DB 125605-HMC702LP6CE LMX2487E-EVM MIKROE-2481 2045 EKIT01-HMC835LP6G EKIT01-HMC834LP6GE TS3006DB DSC-TIMEFLASH2-KIT1 110227-HMC510LP5 110227-HMC513LP5 AD9515/PCBZ ADCLK948/PCBZ ADCLK954/PCBZ 112261-HMC739LP4 ADCLK925/PCBZ AD9522-0/PCBZ AD9520-4/PCBZ AC164147 DFR0469 LMK04133EVAL/NOPB