# DESCRIPTION

The F2915 is a high reliability, low insertion loss, 50  $\Omega$ SP5T absorptive RF switch designed for a multitude of RF applications including wireless communications. This device covers a broad frequency range from 50 MHz to 8000 MHz. In addition to providing low insertion loss, the F2915 also delivers excellent linearity and isolation performance while providing a 50  $\Omega$  termination to the unused RF input ports. The F2915 also includes a patent pending constant impedance (Kz) feature. Kz improves system hot switching ruggedness, minimizes LO pulling in VCOs, and reduces phase and amplitude variations in distribution networks. It is also ideal for dynamic switching/selection between two or more amplifiers while avoiding damage to upstream /downstream sensitive devices such as PAs and ADCs.

The F2915 uses a single positive supply voltage supporting three logic control pins using either 3.3 V or 1.8 V control logic. Connecting a negative voltage to pin 20 disables the internal negative voltage generator and becomes the negative supply.

# **COMPETITIVE ADVANTAGE**

The F2915 provides constant impedance in all RF ports during transitions improving a system's hot-switching ruggedness. The device also supports high power handling, and high isolation; particularly important for DPD receiver use.

- ✓ Constant impedance  $K_{|Z|}$  during switching transition

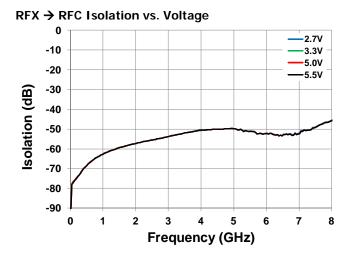

- ✓ RFX to RFC Isolation =  $50 \text{ dB}^*$

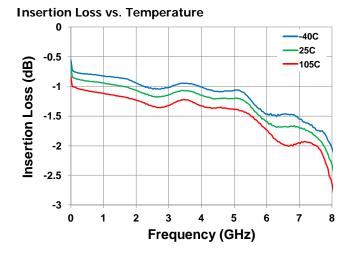

- ✓ Insertion Loss =  $1.1 \text{ dB}^*$

- ✓ IIP3: +60.5 dBm\*

- ✓ Extended temperature: -40 °C to +105 °C

- \* 4 GHz

### **A**PPLICATIONS

- Base Station 2G, 3G, 4G

- Portable Wireless

- Repeaters and E911 systems

- Digital Pre-Distortion

- Point to Point Infrastructure

- Public Safety Infrastructure

- Military Systems, JTRS radios

- Cable Infrastructure

- Test / ATE Equipment

### **FEATURES**

- Five symmetric, absorptive RF ports

- High Isolation: 50 dB @ 4000 MHz

- Low Insertion Loss: 1.1 dB @ 4000 MHz

- High Linearity:

- o IIP2 of 114 dBm @ 2000 MHz

- IIP3 of 60.5 dBm @ 4000 MHz

- High Operating Power Handling:

- 33 dBm CW on selected RF port

27 dBm on terminated ports

- Single 2.7 V to 5.5 V supply voltage

- External Negative Supply Option

- 3.3 V and 1.8 V compatible control logic

- Operating Temperature -40 °C to +105 °C

- 4 mm x 4 mm 24 pin QFN package

- Pin compatible with competitors

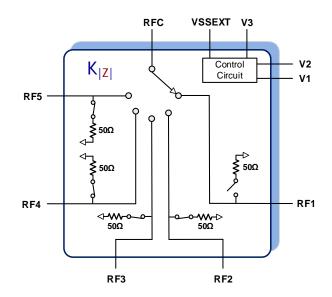

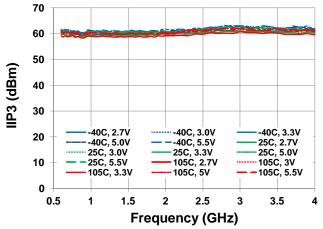

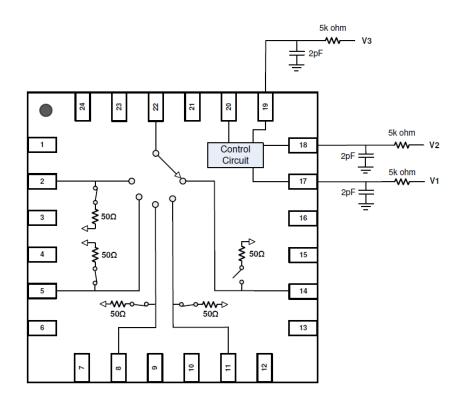

# FUNCTIONAL BLOCK DIAGRAM

### **ORDERING INFORMATION**

# Absolute Maximum Ratings

| Parameter                                                                                             | Symbol            | Min  | Max                                       | Units |

|-------------------------------------------------------------------------------------------------------|-------------------|------|-------------------------------------------|-------|

| V <sub>DD</sub> to GND                                                                                | V <sub>DD</sub>   | -0.3 | +6.0                                      | V     |

| V1, V2, V3 to GND                                                                                     | VCNTL             | -0.3 | Lower of<br>( 3.6, V <sub>DD</sub> + 0.3) | V     |

| RF1, RF2, RF3, RF4, RF5, RFC to GND                                                                   | V <sub>RF</sub>   | -0.3 | +0.3                                      | V     |

| VSSext to GND                                                                                         | VEXT              | -4.0 | +0.3                                      | V     |

| Input Power for any one selected RF through port.<br>( $V_{DD}$ applied @ 2 GHz and $T_{C} = +85$ °C) | PMAXTHRU          |      | 37                                        | dBm   |

| Input Power for any one selected RF terminated port .( $V_{DD}$ applied @ 2 GHz and $T_C = +85$ °C)   | PMAXTERM          |      | 30                                        | dBm   |

| Input Power for RFC when in the all off state.<br>( $V_{DD}$ applied @ 2 GHz and $T_{C} = +85$ °C)    | Рмахсом           |      | 33                                        | dBm   |

| Continuous Power Dissipation (T <sub>c</sub> = 95 °C Max)                                             |                   |      | 3                                         | W     |

| Maximum Junction Temperature                                                                          | T <sub>Jmax</sub> |      | +140                                      | °C    |

| Storage Temperature Range                                                                             | T <sub>ST</sub>   | -65  | +150                                      | °C    |

| Lead Temperature (soldering, 10s)                                                                     | TLEAD             |      | +260                                      | °C    |

| ESD Voltage- HBM (Per JESD22-A114)                                                                    | VESDHBM           |      | Class 1C (1500V)                          |       |

| ESD Voltage – CDM (Per JESD22-C101)                                                                   | VESDCDM           |      | Class C3 (1000V)                          |       |

$T_c$  = Temperature of the exposed paddle

Stresses above those listed above may cause permanent damage to the device. Functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# PACKAGE THERMAL AND MOISTURE CHARACTERISTICS

| $\theta_{JA}$ (Junction – Ambient)                                                 | 41 °C/W  |

|------------------------------------------------------------------------------------|----------|

| $\theta_{\text{JC}}$ (Junction – Case) [The Case is defined as the exposed paddle] | 6.4 °C/W |

| Moisture Sensitivity Rating (Per J-STD-020)                                        | MSL1     |

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                     | Symbol                                                                                 | Co                            | onditions                                      | Min                                    | Тур  | Max  | Units |

|-------------------------------|----------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------|----------------------------------------|------|------|-------|

|                               | V <sub>DD</sub>                                                                        | Pin 20 grou                   | Pin 20 grounded                                |                                        |      | 5.5  |       |

| Supply Voltage (s)            | VDD                                                                                    | Pin 20 Drive                  | en with VSSEXT                                 | 2.7                                    |      | 5.5  | V     |

|                               | VSSEXT                                                                                 | Negative Su                   | upply <sup>1</sup>                             | -3.6                                   | -3.4 | -3.2 |       |

| Operating Temp Range          | TCASE                                                                                  | Exposed Pa                    | ddle Temperature                               | -40                                    |      | +105 | °C    |

| RF Frequency Range            | Frf                                                                                    |                               |                                                | 50                                     |      | 8000 | MHz   |

| RF Continuous                 | P <sub>RF</sub>                                                                        | Selected Pc                   | ort                                            |                                        |      | 33   | dBm   |

| Input CW Power <sup>2</sup>   | - M                                                                                    | Terminated Ports <sup>3</sup> |                                                |                                        |      | 27   | ubiii |

| RF Continuous                 | Input CW Power for     PRFSW       Hot RF Switching <sup>2</sup> RF1 thru       RF5 as | RFC as                        | Switch to RF1<br>thru RF5.                     |                                        |      | 27   |       |

|                               |                                                                                        |                               | the input                                      | Switched into or out of all off state. |      |      | 24    |

| Hot RF Switching <sup>2</sup> |                                                                                        |                               | Switched to RFC or into Term <sup>3</sup> .    |                                        |      | 27   | UDITI |

|                               |                                                                                        | the inputs                    | Switch into or<br>out of all off<br>condition. |                                        |      | 27   |       |

| RF1 - 5 Port Impedance        | Z <sub>RFx</sub>                                                                       |                               |                                                |                                        | 50   |      | Ω     |

| RFC Port Impedance            | ZRFC                                                                                   |                               |                                                |                                        | 50   |      | 22    |

Note 1: For normal operation, connect  $VSS_{EXT} = 0 V$  (pin 20) to GND to enable the internal negative voltage generator. By applying  $VSS_{EXT}$  to pin 20, the negative voltage generator is disabled completely eliminating any generator spurious responses.

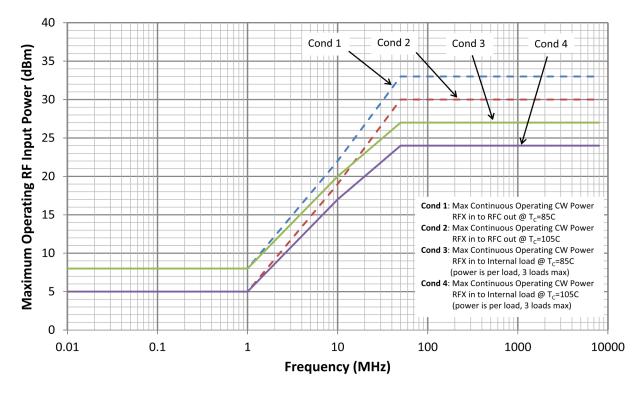

Note 2: Levels based on  $T_C \leq 85C$ . See Figure 1 power de-rating curve for higher case temperatures.

Note 3: In any of the insertion loss modes or switching into any insertion loss mode, any 3 of the 4 remaining terminated port paths may be each exposed to the maximum stated power level during continuous or hot switching operation.

Figure 1 - MAXIMUM RF OPERATING INPUT POWER vs. RF FREQUENCY

# **S**PECIFICATIONS

Typical Application Circuit, Normal mode ( $V_{DD}$ = 3.3 V, VSS<sub>EXT</sub>= 0 V) or Bypass mode ( $V_{DD}$ = 3.3 V, VSS<sub>EXT</sub>= -3.3 V), T<sub>C</sub> = +25 °C, F<sub>RF</sub> = 2000 MHz, Input power = 0 dBm, Z<sub>S</sub> = Z<sub>L</sub> = 50  $\Omega$ , RFX = one of the five input ports, PCB board trace and connector losses are de-embedded unless otherwise noted.

| Parameter                            | Symbol               |                                                                                                                                  | litions                                           | Min  | Тур    | Max                                  | Units |

|--------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|--------|--------------------------------------|-------|

| Logic Input High Threshold           | Vін                  |                                                                                                                                  |                                                   | 1.1  |        | Lower of<br>( 3.6, V <sub>DD</sub> ) | V     |

| Logic Input Low Threshold            | VIL                  |                                                                                                                                  |                                                   | -0.3 |        | 0.6                                  | V     |

| Logic Current                        | Iih, Iil             | For each control pir                                                                                                             | า                                                 | -2   |        | +2                                   | μA    |

| DC Current (VDD)                     | IDD                  |                                                                                                                                  | 3 V or 1.8V Logic                                 |      | 290    | 360                                  | μA    |

|                                      |                      | <b>3</b> 1                                                                                                                       | 3 V or 1.8V Logic                                 |      | 270    | 340                                  | -     |

| DC Current (VSS <sub>EXT</sub> )     | lvss                 | $VSS_{EXT} = -3.3 V$                                                                                                             |                                                   |      | -46    | -60                                  | μA    |

|                                      |                      | 900 MHz                                                                                                                          |                                                   |      | 0.93   | 1.4 <sup>1</sup>                     |       |

| Insertion Loss                       |                      | 2100 MHz                                                                                                                         |                                                   |      | 1.1    | 1.5                                  |       |

| RFX to RFC                           | IL                   | 2700 MHz                                                                                                                         |                                                   |      | 1.2    | 1.6                                  | dB    |

|                                      |                      | 2700 MHz – 4000 N                                                                                                                |                                                   |      | 1.1    | 1.65 <sup>2</sup>                    |       |

|                                      |                      | 4000 MHz – 8000 N                                                                                                                |                                                   |      | 2.3    |                                      |       |

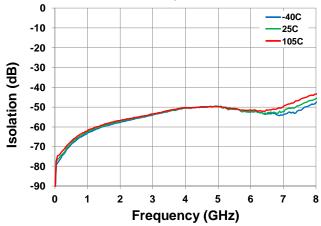

|                                      |                      | 400 MHz – 900 MHz                                                                                                                |                                                   | 57.5 | 62     |                                      |       |

| Minimum Isolation                    |                      | 900 MHz – 2100 Mł                                                                                                                |                                                   | 51   | 56     |                                      |       |

| RFX to RFC                           | ISOC                 | 2100 MHz – 2700 MHz                                                                                                              |                                                   | 49.5 | 54     |                                      | dB    |

|                                      |                      | 2700 MHz – 4000 MHz                                                                                                              |                                                   | 45   | 50     |                                      |       |

|                                      |                      | 4000 MHz – 8000 N                                                                                                                |                                                   | 31   | 36.5   |                                      |       |

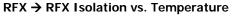

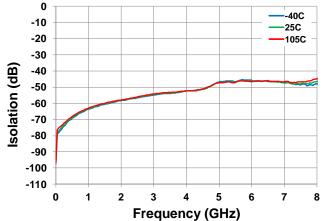

|                                      | ISOX                 | 400 MHz – 900 MHz                                                                                                                |                                                   | 56.5 | 61.5   |                                      | dB    |

| Minimum Isolation<br>RFX to RFX      |                      | 900 MHz – 2100 MHz                                                                                                               |                                                   | 50   | 55     |                                      |       |

|                                      |                      | 2100 MHz – 2700 MHz                                                                                                              |                                                   | 48   | 53     |                                      |       |

|                                      |                      | 2700 MHz – 4000 MHz                                                                                                              |                                                   | 44.5 | 49.5   |                                      |       |

|                                      |                      | 4000 MHz - 8000 N                                                                                                                | ЛНz                                               | 30.5 | 36.5   |                                      |       |

| Insertion Loss Flatness              | IL <sub>FLAT</sub>   | 400 MHz – 3800 Mł                                                                                                                |                                                   |      | 0.1    | 0.4                                  | dB    |

|                                      |                      | Any 400 MHz range                                                                                                                |                                                   |      |        |                                      |       |

| VSWR RFC                             | VSWRRFC              | RF1 through RF5 se                                                                                                               |                                                   |      | 1.25:1 | 1.78:1                               | -     |

| VSWR RFX (On Ports)                  | VSWRON               | RF1 through RF5 se                                                                                                               |                                                   |      | 1.33:1 | 1.78:1                               | -     |

| VSWR RFX (Term Ports)                | VSWRTERM             | RF1 through RF5 u                                                                                                                |                                                   |      | 1.15:1 | 1.58:1                               | -     |

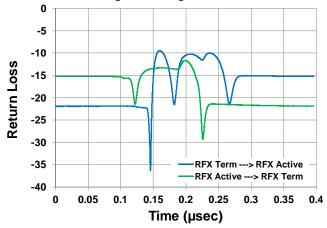

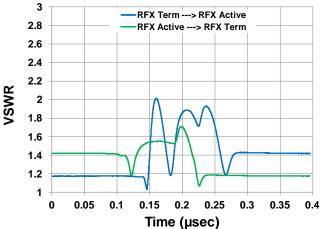

| Maximum RFX Port VSWR                | VSWR⊤                | From RFX Active to                                                                                                               |                                                   |      | 1.7:1  |                                      | -     |

| During Switching                     |                      | From RFX Term to                                                                                                                 |                                                   |      | 2:1    |                                      |       |

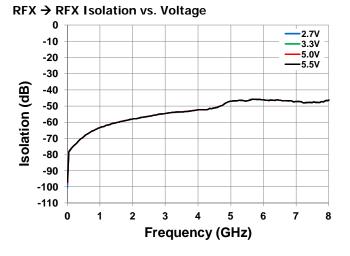

| Minimum Return Loss<br>(RFC Port)    | RFC <sub>RL</sub>    | RF1 through RF5 se<br>400 MHz – 4000 M                                                                                           |                                                   | 10   | 16     |                                      | dB    |

| Minimum Return Loss                  | RFX <sub>RL</sub>    | 400 MHz –                                                                                                                        | Active                                            | 9    | 13     |                                      | dB    |

| (RFX Port )                          | KFARL                | 4000 MHz                                                                                                                         | Terminated                                        | 11   | 15     |                                      | ив    |

| Input 1dB Compression <sup>3</sup>   | ICP <sub>1dB</sub>   |                                                                                                                                  |                                                   | 34   | 36.5   |                                      | dBm   |

| Input 0.1dB Compression <sup>3</sup> | ICP <sub>0.1dB</sub> |                                                                                                                                  |                                                   | 28   | 35     |                                      | dBm   |

| Input IP2                            | IIP2                 | $\begin{array}{l} F_{RF1} = 2000 \mbox{ MHz, F} \\ RF \mbox{ Input} = RFX, P_{IN} \\ F_{RF1} + F_{RF2} \mbox{ Term} \end{array}$ | $R_{F2} = 2010 \text{ MHz}$<br>N = +20 dBm / tone |      | 114    |                                      | dBm   |

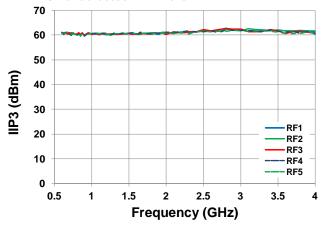

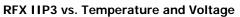

|                                      |                      | $\Delta F = 1 MHz$                                                                                                               | $F_{RF} = 400 \text{ MHz}$                        | 45   | 60.5   |                                      |       |

| Input IP3                            | IIP3                 | RF Input = RFX                                                                                                                   | $F_{RF} = 2000 \text{ MHz}$                       | 56   | 60     |                                      | dBm   |

| r                                    |                      | $P_{IN} = +20$<br>dBm/tone                                                                                                       | $F_{RF} = 4000 \text{ MHz}$                       |      | 60.5   |                                      |       |

Note 1 – Items in min/max columns in *bold italics* are Guaranteed by Test.

Note 2 – Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

- Note 3 The input 0.1dB and 1dB compression points are linearity figures of merit. Refer to Absolute Maximum

- Ratings section for the maximum RF input power and Figure 1 for maximum operating RF input power.

Typical Application Circuit, Normal mode ( $V_{DD}$  = 3.3 V, VSS<sub>EXT</sub> = 0 V) or Bypass mode ( $V_{DD}$  = 3.3 V, VSS<sub>EXT</sub> = -3.3 V),  $T_{C}$  = +25 °C,  $F_{RF}$  = 2000 MHz, Input power = 0 dBm,  $Z_{S}$  =  $Z_{L}$  = 50  $\Omega$ , RFX = one of the five input ports, PCB board trace and connector losses are de-embedded unless otherwise noted.

| Parameter                                              | Symbol              |                                     | Conditions                                                    |  | Тур  | Max | Units |

|--------------------------------------------------------|---------------------|-------------------------------------|---------------------------------------------------------------|--|------|-----|-------|

| Group Delay                                            | GD                  |                                     |                                                               |  | 0.43 | 1   | ns    |

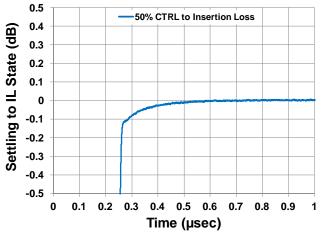

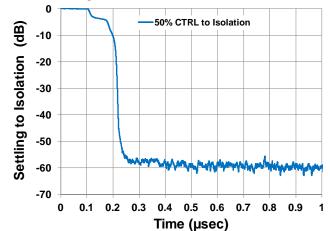

|                                                        |                     |                                     | 50% CTRL to 90% RF                                            |  | 256  | 345 |       |

| Switching Time <sup>4</sup> Tsv                        |                     | Bypass                              | 50% CTRL to 10% RF                                            |  | 256  | 345 | ns    |

|                                                        | Tsw                 | T <sub>sw</sub> Mode                | 50% CTRL to RF settled<br>within +/- 0.1 dB of I.L.<br>value. |  | 285  |     |       |

| Maximum Switching Data                                 | Patož SW/see Pin 20 |                                     | GND                                                           |  | 25   |     | kHz   |

| Maximum Switching Rate <sup>s</sup> SW <sub>RATE</sub> |                     | Pin 20 = VSS <sub>EXT</sub> applied |                                                               |  | 290  |     | КПД   |

| Maximum spurious level on any RF port <sup>e</sup>     | Spur <sub>MAX</sub> |                                     | terminated into $50\Omega$<br>nected to RFC                   |  | -120 |     | dBm   |

Note 1 – Items in min/max columns in *bold italics* are Guaranteed by Test.

Note 2 – Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

Note 3 – The input 0.1dB and 1dB compression points are linearity figures of merit. Refer to Absolute Maximum

Ratings section for the maximum RF input power and Figure 1 for maximum operating RF input power. Note  $4 - F_{RF} = 1$ GHz.

Note 5 – Minimum time required between switching of states =1/ (Maximum Switching Rate).

Note 6 – Spurious due to on-chip negative voltage generator. Typical generator fundamental frequency is 2.2 MHz.

Typical Application Circuit, Normal mode ( $V_{DD}$ = 3.3 V, VSS<sub>EXT</sub>= 0 V), T<sub>C</sub> = +105 °C, Input power = 0 dBm, Z<sub>S</sub> = Z<sub>L</sub> = 50  $\Omega$ , RFX = one of the five input ports, PCB board trace and connector losses are de-embedded unless otherwise noted.

| Parameter                          | Symbol            | Condit               | ions       | Min  | Тур  | Max | Units |

|------------------------------------|-------------------|----------------------|------------|------|------|-----|-------|

|                                    |                   | 50 MHz - 900 MHz 1.2 |            |      |      | 1.7 |       |

| Insertion Loss<br>RFX to RFC       |                   | 900 MHz - 2100 MHz   |            |      | 1.3  | 1.7 | 7     |

|                                    | IL                | 2100 MHz - 2700 MH   | Z          |      | 1.4  | 1.8 | dB    |

|                                    |                   | 2700 MHz – 4000 MH   | Z          |      | 1.4  | 2.0 |       |

|                                    |                   | 4000 MHz – 8000 MH   | Z          |      | 2.7  |     |       |

|                                    |                   | 50 MHz – 900 MHz     |            | 57   | 61.5 |     |       |

|                                    |                   | 900 MHz – 2100 MHz   |            | 50.5 | 55.5 |     | 1     |

| Minimum Isolation<br>RFX to RFC    | ISOC              | 2100 MHz – 2700 MHz  |            | 49   | 53.5 |     | dB    |

|                                    |                   | 2700 MHz – 4000 MHz  |            | 44.5 | 49.5 |     |       |

|                                    |                   | 4000 MHz – 8000 MHz  |            | 30.5 | 36   |     |       |

|                                    |                   | 50 MHz – 900 MHz     |            | 56   | 61   |     |       |

| Minimum Loolation                  |                   | 900 MHz – 2100 MHz   |            | 49.5 | 54.5 |     | dB    |

| Minimum Isolation                  | ISOX              | 2100 MHz – 2700 MHz  |            | 47.5 | 52.5 |     |       |

| RFX to RFX                         |                   | 2700 MHz – 4000 MH   | Z          | 44   | 49   |     | 7     |

|                                    |                   | 4000 MHz – 8000 MHz  |            | 30   | 36   |     |       |

| Minimum Return Loss<br>(RFC Port ) | RFC <sub>RL</sub> | 50 MHz – 4000 MHz    |            | 9    | 15   |     | dB    |

| Minimum Return Loss                | DEV               |                      | Active     | 8    | 12   |     | ٩D    |

| (RFX Port)                         | RFX <sub>RL</sub> | 50 MHz –4000 MHz     | Terminated | 10   | 14   |     | dB    |

Note – Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

| Mode    | V3 | V2 | V1 |

|---------|----|----|----|

| All off | 0  | 0  | 0  |

| RF1 on  | 0  | 0  | 1  |

| RF2 on  | 0  | 1  | 0  |

| RF3 on  | 0  | 1  | 1  |

| RF4 on  | 1  | 0  | 0  |

| RF5 on  | 1  | 0  | 1  |

| All off | 1  | 1  | 0  |

| All off | 1  | 1  | 1  |

### TABLE 1: SWITCH CONTROL TRUTH TABLE

# TYPICAL OPERATING CONDITIONS (TOC)

Unless otherwise noted for the TOC graphs on the following pages, the following conditions apply.

- $V_{DD} = 3.3 V.$

- T<sub>CASE</sub> = +25 °C (T<sub>CASE</sub> = Temperature of exposed paddle).

- $F_{RF} = 2000 \text{ MHz}.$

- RFX is the driven RF port and RFC is the output port.

- Pin = 10 dBm for all small signal tests.

- Pin = +15 dBm/tone applied to selected RFX port for two tone linearity tests.

- Two tone frequency spacing = 5 MHz.

- $Z_S = Z_L = 50$  ohms.

- All unused RF ports terminated into 50 ohms.

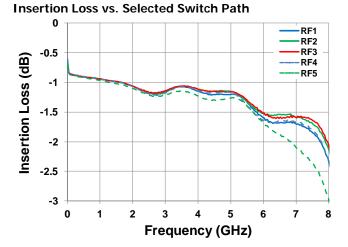

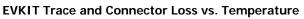

- For Insertion Loss and Isolation plots, RF trace and connector losses are de-embedded (see EVKIT Board and Connector loss plot).

- Plots for Isolation and Insertion Loss over temperature and voltage are for a typical path. For performance of a specific path, refer to the online S-Parameter file.

# **TYPICAL OPERATING CONDITIONS (-1-)**

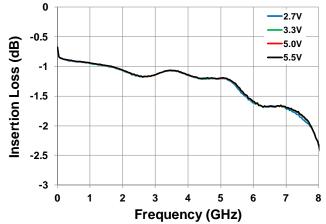

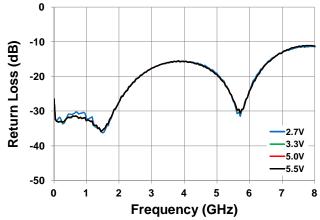

Insertion Loss vs. Voltage

# TYPICAL OPERATING CONDITIONS (- 2 -)

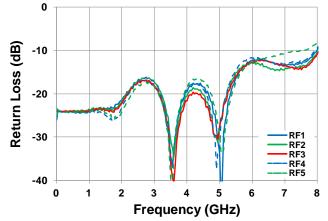

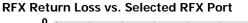

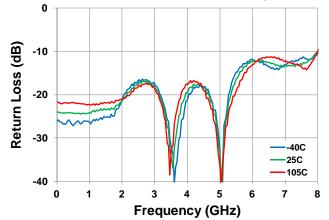

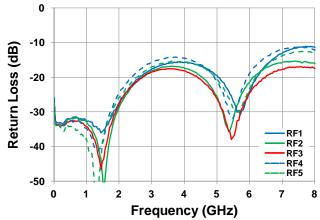

RFC Return Loss vs. Selected RFX Port

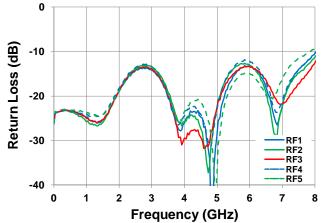

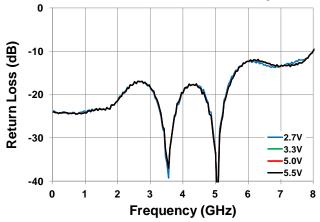

**RFX Selected Return Loss vs. Voltage**

RFC Return Loss with RFX Selected vs. Temperature

# TYPICAL OPERATING CONDITIONS (- 3 -)

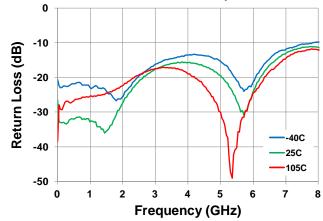

**RFX Terminated Return Loss vs. Temperature**

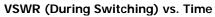

Return Loss (During Switching) vs. Time

**RFX Terminated Return Loss vs. Voltage**

# **TYPICAL OPERATING CONDITIONS (- 4 -)**

RFX Switching Time [RFX Terminated to RFX Active]

RFX Switching Time [RFX Active to RFX Terminated]

### **PIN DIAGRAM**

# **PIN DESCRIPTION**

| Pin                                             | Name               | Function                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 4, 6, 7, 9, 10, 12,<br>13, 15, 21, 23, 24 | GND                | Ground these pins as close to the device as possible.                                                                                                                                                                                                                      |

| 2                                               | RF5                | RF5 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 5                                               | RF4                | RF4 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 8                                               | RF3                | RF3 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 11                                              | RF2                | RF2 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 14                                              | RF1                | RF1 Port. Matched to 50 ohms. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                  |

| 16                                              | VDD                | Power Supply. Bypass to GND with capacitors shown in the Typical Application Circuit as close as possible to pin.                                                                                                                                                          |

| 17                                              | V1                 | Control pin to set switch state. See Table 1.                                                                                                                                                                                                                              |

| 18                                              | V2                 | Control pin to set switch state. See Table 1.                                                                                                                                                                                                                              |

| 19                                              | V3                 | Control pin to set switch state. See Table 1.                                                                                                                                                                                                                              |

| 20                                              | VSS <sub>ext</sub> | External VSS negative voltage control. Connect to ground to enable on chip negative voltage generator. To bypass and disable on chip generator connect this pin to an external VSS.                                                                                        |

| 22                                              | RFC                | RF Common Port. Matched to 50 ohms when one of the 5 RF ports is selected. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                     |

| 25                                              | — ЕР               | Exposed Pad. Internally connected to GND. Solder this exposed pad to a PCB pad that uses multiple ground vias to provide heat transfer out of the device into the PCB ground planes. These multiple ground vias are also required to achieve the specified RF performance. |

### **APPLICATIONS INFORMATION**

### Default Start-up

There are no internal pull-up or pull-down resistors on the Control pins.

### **Logic Control**

Control pins V1, V2, and V3 are used to set the state of the SP5T switch (see Table 1).

#### External Vss

The F2915 is designed with an on-chip negative voltage generator. This on-chip generator is enabled by connecting pin 20 of the device to ground. To disable the on-chip generator apply a negative voltage to pin 20 (VSSEXT) of the device within the range stated in the Recommended Operating Conditions Table.

#### **Power Supplies**

A common VDD power supply should be used for all pins requiring DC power. All supply pins should be bypassed with external capacitors to minimize noise and fast transients. Supply noise can degrade noise figure and fast transients can trigger ESD clamps and cause them to fail. Supply voltage change or transients should have a slew rate smaller than 1 V / 20  $\mu$ S. In addition, all control pins should remain at 0 V (+/-0.3 V) while the supply voltage ramps or while it returns to zero.

#### **Control Pin Interface**

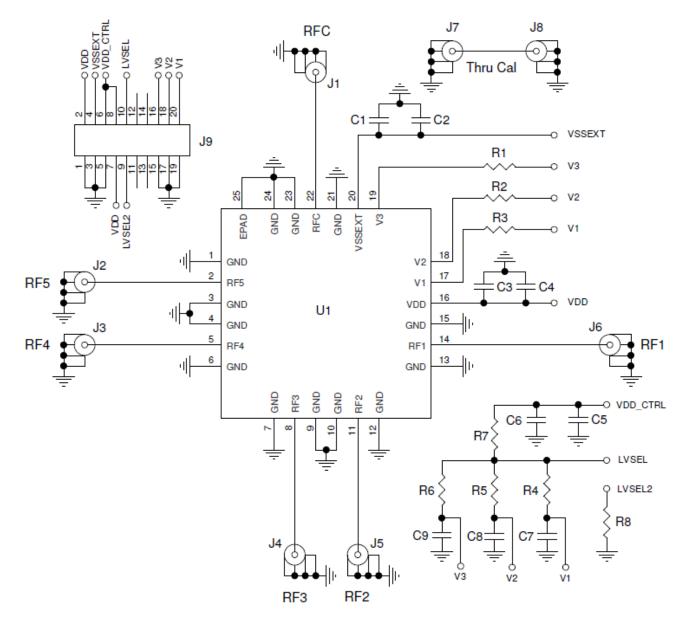

If control signal integrity is a concern and clean signals cannot be guaranteed due to overshoot, undershoot, ringing, etc., the following circuit at the input of each control pin is recommended. This applies to control pins 17, 18, and 19 as shown below.

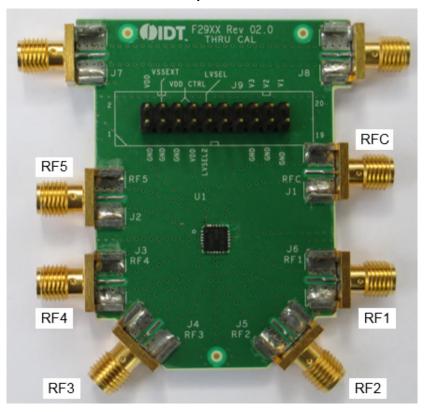

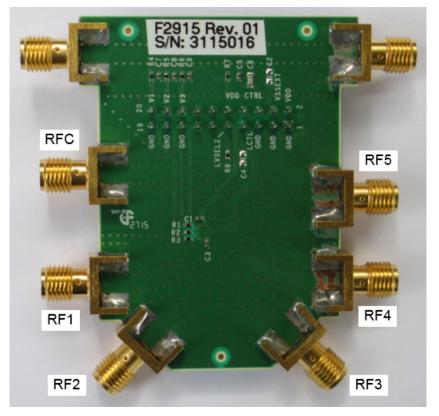

# **EVKIT PICTURES**

**Top View**

### **Bottom View**

# **EVKIT / APPLICATIONS CIRCUIT**

# **EVKIT BOM**

| Part<br>Reference         | QTY | DESCRIPTION                                         | Mfr. Part #          | Mfr.            |

|---------------------------|-----|-----------------------------------------------------|----------------------|-----------------|

| C1, C3, C5, C7,<br>C8, C9 | 6   | 100 pF $\pm$ 5%, 50V, COG Ceramic Capacitor (0402)  | GRM1555C1H101J       | Murata          |

| C2                        | 0   | Not Installed (0603)                                |                      |                 |

| C4                        | 0   | Not Installed (0603)                                |                      |                 |

| C6                        | 1   | 1000 pF $\pm$ 5%, 50V, C0G Ceramic Capacitor (0603) | GRM1885C1H102J       | Murata          |

| R1, R2, R3                | 3   | 0 Ω ±1%, 1/10W, Resistor (0402)                     | ERJ-2GE0R00X         | Panasonic       |

| R4, R5, R6                | 3   | 100 kΩ ±1%, 1/10W, Resistor (0402)                  | ERJ-2RKF1003X        | Panasonic       |

| R7                        | 1   | 15 kΩ ±1%, 1/10W, Resistor (0402)                   | ERJ-2RKF1502X        | Panasonic       |

| R8                        | 1   | 22 kΩ ±1%, 1/10W, Resistor (0402)                   | ERJ-2RKF2202X        | Panasonic       |

| J1-J8                     | 8   | Edge Launch SMA (0.375 inch pitch ground tabs)      | 142-0701-851         | Emerson Johnson |

| J9                        | 1   | CONN HEADER VERT DBL 10 X 2 POS GOLD                | 67997-120HLF         | FCI             |

| U1                        | 1   | SP5T Switch 4 mm x 4 mm QFN24-EP                    | F2915NBGK            | Renesas (IDT)   |

|                           | 1   | Printed Circuit Board                               | F29XX EVKIT Rev 02.0 | Renesas (IDT)   |

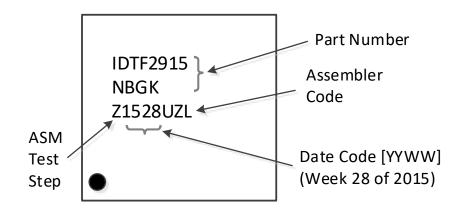

# **TOP MARKINGS**

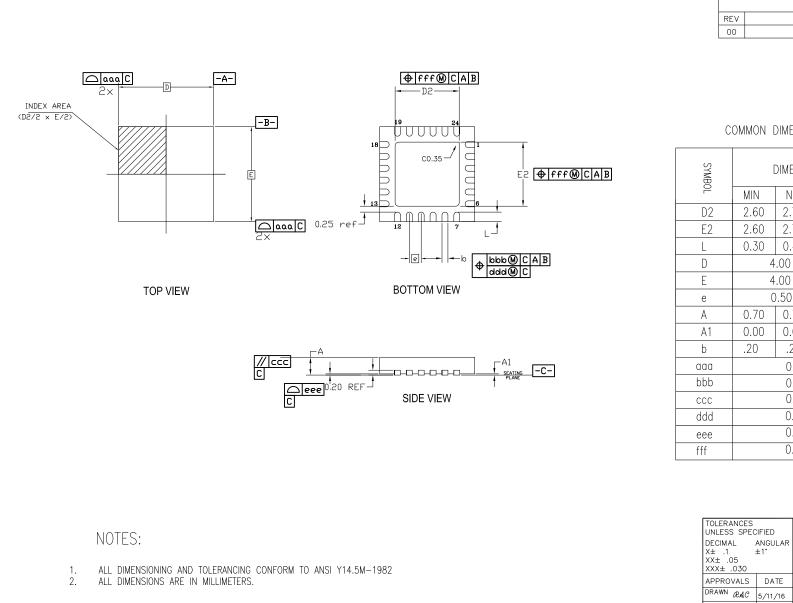

# PACKAGE OUTLINE DRAWINGS

The <u>package outline drawings</u> are located at the end of this document and are accessible from the Renesas website (see package links in Ordering Information). The package information is the most current data available and is subject to change without revision of this document.

### **EVKIT OPERATION**

### External Supply Setup

Set up a VDD power supply in the voltage range of 2.7 V to 5.5 V and disable the power supply output.

If using the on-chip negative voltage generator install a 2-pin shunt to short pins 3 and 4 of J9.

If an external negative voltage supply is to be used set its voltage within the range of -3.6 V to -3.2 V and disable it. Also, be sure there are no jumper connections on pins 3 and 4 of J9.

### Logic Control Setup

#### Using the EVKIT to manually set the control logic:

On connector J9 connect a 2-pin shunt from pin 7 (VDD) to pin 8 (VDD\_CTRL). This connection provides the VDD voltage supply to the Eval Board logic control pull up network.

On connector J9 connect a 2-pin shunt from pin 9 (LVSEL2) to pin 10 (LVSEL). This connection enables R7 (15 k $\Omega$ ) and R8 (22 k $\Omega$ ) to form a voltage divider to set the proper logic control levels to support the full voltage range of VDD. Note that when using the on-board R7 / R8 voltage divider the current draw from the VDD supply will be higher by approximately VDD / 37 k $\Omega$ .

Connector J9 has 3 logic input pins: V1 (pin 20), V2 (pin 18), and V3 (pin 16). See Table 1 for Logic Truth Table. With the pullup network enabled (as noted above), when these pins are left open a logic high will be provided through pull up resistors R4, R5, and R6. To set a logic low to V1, V2, and V3 connect 2-pin shunts from pin 16 to pin 15, pin 18 to pin 17 and pin 20 to pin 19 respectively.

#### Using external control logic:

Pins 6, 7, 8, 9, and 10 of J9 should have no connection. External logic controls can be applied to J9 pins 16 (V3), 18 (V2) and 20 (V1). See Table 1 for Logic Truth Table.

### Turn-on Procedure

Setup the supplies and Eval Board as noted in the **External Supply Setup** and **Logic Control Setup** sections above.

Connect the preset disabled VDD power supply to pin 2 (VDD) and pin 1 (GND) of J9.

If the external negative voltage source is to be used, connect the disabled supply to pin 4 (VSSEXT) and pin 3 (GND) of J9. If using on-chip negative supply be sure the 2-pin shunt is installed connecting pin 3 to pin 4.

Enable the VDD supply then enable the VSSEXT supply (if used).

Set the desired logic setting using V1, V2, and V3 to achieve the desired Table 1 setting. Note that external control logic should not be applied without VDD being applied first.

### Turn-off Procedure

If using external control logic V1, V2, V3 must be set to a logic low.

Disable any external VSSEXT supply.

Disable the VDD supply.

# **REVISION HISTORY**

| Date              | Description of Change                                                       |

|-------------------|-----------------------------------------------------------------------------|

| October 26, 2021  | Added RF performance data at 105°C                                          |

| 0000001 20, 2021  | Completed other minor changes                                               |

| June 22, 2020     | Rebranded the document and completed minor changes throughout; no technical |

| Julie 22, 2020    | updates were made                                                           |

| May 5, 2016       | Added new Guaranteed by Design parameters to specification table.           |

| February 22, 2016 | Added min/max limits. Increased frequency range. Updated ESD values.        |

| December 11, 2015 | Initial Release                                                             |

Ν

2.

.2

0

0

0

0. 0.

0.

CHECKED

| REV |   |

|-----|---|

| 00  | Ĭ |

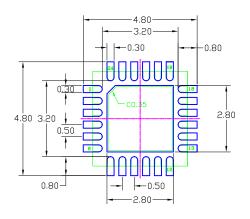

# RECOMMENDED LAND PATTERN DIMENSION

# NOTES:

- 1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW. AS VIEWED ON PCB.

- COMPONENT OUTLINE SHOWN FOR REFERENCE IN GREEN.

LAND PATTERN IN BLUE. NSMD PATTERN ASSUMED.

- 5. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

| TOLERANCES<br>UNLESS SPEC | IFIED          |   |

|---------------------------|----------------|---|

|                           | ANGULAR<br>±1' |   |

| XXX± .030                 |                |   |

| APPROVALS                 | DATE           | T |

| DRAWN RAC                 | 5/11/16        |   |

| CHECKED                   |                |   |

|                           |                |   |

|                           |                |   |

|                           |                |   |

| 1                         | 1              | 1 |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RF Development Tools category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

MAAM-011117 MAAP-015036-DIEEV2 EV1HMC1113LP5 EV1HMC6146BLC5A EV1HMC637ALP5 EVAL-ADG919EBZ ADL5363-EVALZ LMV228SDEVAL SKYA21001-EVB SMP1331-085-EVB EV1HMC618ALP3 EVAL01-HMC1041LC4 MAAL-011111-000SMB MAAM-009633-001SMB MASW-000936-001SMB 107712-HMC369LP3 107780-HMC322ALP4 SP000416870 EV1HMC470ALP3 EV1HMC520ALC4 EV1HMC244AG16 MAX2614EVKIT# 124694-HMC742ALP5 SC20ASATEA-8GB-STD MAX2837EVKIT+ MAX2612EVKIT# MAX2692EVKIT# EV1HMC629ALP4E SKY12343-364LF-EVB 108703-HMC452QS16G EV1HMC863ALC4 EV1HMC427ALP3E 119197-HMC658LP2 EV1HMC647ALP6 ADL5725-EVALZ 106815-HMC441LM1 EV1HMC1018ALP4 UXN14M9PE MAX2016EVKIT EV1HMC939ALP4 MAX2410EVKIT MAX2204EVKIT+ EV1HMC8073LP3D SIMSA868-DKL SIMSA868C-DKL SKY65806-636EK1 SKY68020-11EK1 SKY67159-396EK1 SKY66181-11-EK1 SKY65804-696EK1