#### To all our customers

Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.)

Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp.

Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

# Hitachi Single-Chip Microcomputer

# H8/3397 Series

H8/3397

HD6433397

H8/3396

HD6433396

H8/3394

HD6433394

## H8/3337 Series

H8/3337Y

HD6473337Y, HD6433337Y

H8/3336Y

HD6433336Y

H8/3334Y

HD6473334Y, HD6433334Y

H8/3337W

HD6433337W

H8/3336W

HD6433336W

## H8/3337YF-ZTAT<sup>TM</sup>

HD64F3337Y

H8/3337SF-ZTAT<sup>TM</sup>

HD64F3337S

H8/3334YF-ZTATTM

HD64F3334Y

Hardware Manual

# **HITACHI**

ADE-602-078E Rev. 6.0 3/14/02 Hitachi, Ltd.

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

#### **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

## **Preface**

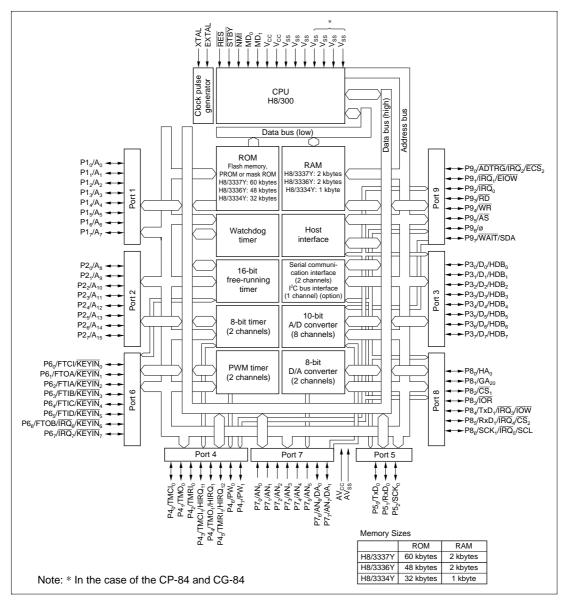

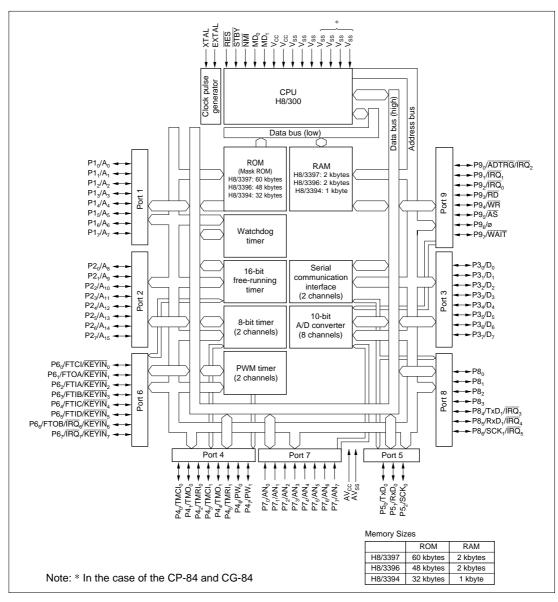

The H8/3337 Series and H8/3397 Series is a high-performance single-chip microcomputer that integrates peripheral functions necessary for system configuration with an H8/300 CPU featuring a 32-bit internal architecture as its core.

On-chip peripheral functions include ROM, RAM, four kinds of timers, a serial communication interface (SCI), host interface (HIF), keyboard controller, D/A converter, A/D converter, and I/O ports, enabling the H8/3337 Series and H8/3397 Series to be used as a microcontroller for embedding in high-speed control systems. Flash memory (F-ZTAT<sup>TM\*</sup>), PROM (ZTAT®\*), and mask ROM are available as on-chip ROM, enabling users to respond quickly and flexibly to changing application specifications and the demands of the transition from initial to full-fledged volume production.

Note: \* F-ZTAT is a trademark of Hitachi, Ltd.

ZTAT is a registered trademark of Hitachi, Ltd.

Intended Readership: This manual is intended for users undertaking the design of an application

system using a H8/3337 Series and H8/3397 Series microcomputer. Readers using this manual require a basic knowledge of electrical circuits,

logic circuits, and microcomputers.

Purpose: The purpose of this manual is to give users an understanding of the

hardware functions and electrical characteristics of the H8/3337 Series and H8/3397 Series. Details of execution instructions can be found in the H8/300 Series Programming Manual, which should be read in conjunction

with the present manual.

#### Using this Manual:

- For an overall understanding of the H8/3337 Series' and H8/3397 Series' functions

Follow the Table of Contents. This manual is broadly divided into sections on the CPU, system control functions, peripheral functions, and electrical characteristics.

- For a detailed understanding of CPU functions

Refer to the separate publication H8/300 Series Programming Manual.

- For a detailed description of a register's function when the register name is known.

Information on addresses, bit contents, and initialization is summarized in Appendix B,

Internal I/O Register.

Note on bit notation: Bits are shown in high-to-low order from left to right.

Related Material: The latest information is available at our Web Site. Please make sure that you

have the most up-to-date information available.

http://www.hitachisemiconductor.com/

## User's Manuals on the H8/3337 Series and H8/3397 Series:

| Manual Title                                      | ADE No.     |

|---------------------------------------------------|-------------|

| H8/3337 Series and H8/3397 Series Hardware Manual | This manual |

| H8/300 Series Programming Manual                  | ADE-602-025 |

## Users manuals for development tools:

| Manual Title                                                                           | ADE No.     |

|----------------------------------------------------------------------------------------|-------------|

| C/C++ Compiler, Assembler, Optimized Linkage Editor User's Manual                      | ADE-702-247 |

| Simulator Debugger Users Manual                                                        | ADE-702-282 |

| Hitachi Debugging Interface Users Manual                                               | ADE-702-161 |

| Hitachi Embedded Workshop Users Manual                                                 | ADE-702-201 |

| H8S, H8/300 Series Hitachi Embedded Workshop, Hitachi Debugging Interface Users Manual | ADE-702-231 |

# Notes on S-Mask Model (Single-Power-Supply Specification)

There are two versions of the H8/3337F with on-chip flash memory: a dual-power-supply version and a single-power-supply (S-mask) version. Points to be noted when using the H8/3337F single-power-supply S-mask model are given below.

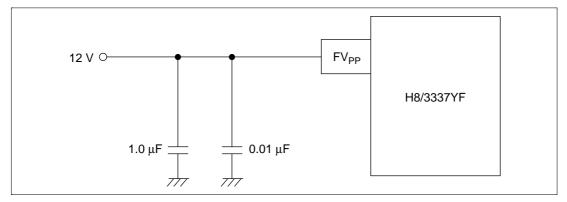

#### 1. Notes on Voltage Application

12 V must not be applied to the S-mask model (single-power-supply specification), as this may permanently damage the device.

The flash memory programming power supply for the S-mask model (single-power-supply specification) is  $V_{CC}$ . The programming power supply for the dual-power-supply model is the  $FV_{PP}$  pin (12 V), but the single-power-supply model (S-mask model) does not have an  $FV_{PP}$  pin.

Also, in boot mode, 12 V has to be applied to the MD<sub>1</sub> pin in the dual-power-supply model, but 12 V application is not necessary in the single-power-supply model (S-mask model).

The maximum rating of the  $MD_1$  pin is  $V_{\rm CC}$  +0.3 V. Applying a voltage in excess of the maximum rating will permanently damage the device.

Do not select the HN28F101 programmer setting for the S-mask model (single-power-supply specification). If this setting is made by mistake, 12 V will be applied to the STBY pin, possibly causing permanent damage to the device.

When using a PROM programmer to program the on-chip flash memory in the S-mask model (single-power-supply specification), use a PROM programmer that supports Hitachi microcomputer devices with 64-kbyte on-chip flash memory. Also, only use the specified socket adapter. Using the wrong PROM programmer or socket adapter may damage the device.

The following PROM programmers support the S-mask model (single-power-supply specification).

DATA I/O: UNISITE, 2900, 3900, etc.

Minato: 1892, 1891, 1890, etc.

## 2. Product Type Names and Markings

Table 1 shows examples of product type names and markings for the H8/3337YF (dual-power-supply specification) and H8/3337SF (single-power-supply specification), and the differences in flash memory programming power supply.

Table 1 Differences in H8/3337YF and H8/3337F S-Mask Model Markings

|                                       | Dual-Power-Supply Model: H8/3337YF            | Single-Power-Supply Model:<br>H8/3337F S-Mask Model                     |  |

|---------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------|--|

| Product type name                     | HD64F3337YF16/TF16                            | HD64F3337SF16/TF16                                                      |  |

| Sample markings                       |                                               |                                                                         |  |

|                                       | © H8/3337<br>8M3<br>HD<br>64F3337F16<br>JAPAN | © H8/3337 8M3 HD S 64F3337F16 JAPAN  "S" is printed above the type name |  |

| Flash memory programming power supply | $V_{PP}$ power supply (12.0 V ±0.6 V)         | V <sub>cc</sub> power supply (5.0 V ±10%)                               |  |

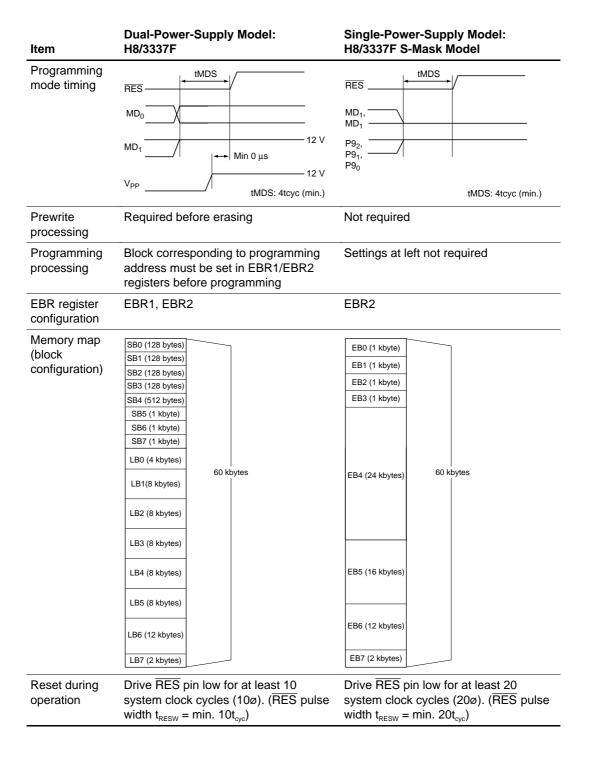

## 3. Differences in S-Mask Model

Table 2 shows the differences between the H8/3337F (dual-power-supply specification) and H8/3337SF (single-power-supply specification).

Table 2 Differences between H8/3337F and H8/3337F S-Mask Model

| Item                                                   | Dual-Power-Supply Model:<br>H8/3337F                                                                | Single-Power-Supply Model:<br>H8/3337F S-Mask Model                                                                                                                                          |  |  |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Program/                                               | 12 V must be applied from off-chip                                                                  | 12 V application not required                                                                                                                                                                |  |  |  |

| erase voltage                                          | V <sub>PP</sub> (12.0 V ±0.6 V)                                                                     | $V_{\text{cc}}$ single-power-supply programming                                                                                                                                              |  |  |  |

|                                                        |                                                                                                     | V <sub>CC</sub> (5.0 V ±10%)                                                                                                                                                                 |  |  |  |

| FV <sub>PP</sub> (FWE)<br>pin function                 | Dual function as FV <sub>PP</sub> power supply and STBY function                                    | No programming control pin                                                                                                                                                                   |  |  |  |

| Programming modes                                      | <ul> <li>Writer mode</li> <li>On-board</li> <li>Boot mode</li> <li>User programming mode</li> </ul> | (See section 21 for the use of these modes)                                                                                                                                                  |  |  |  |

| Operating<br>modes allowing<br>on-board<br>programming | <ul><li>Writer mode</li><li>Boot mode</li><li>User programming mode</li></ul>                       | (See section 21 for the use of these modes)                                                                                                                                                  |  |  |  |

| On-board programming unit                              | 1-byte-unit programming                                                                             | 32-byte-unit programming                                                                                                                                                                     |  |  |  |

| Programming with PROM programmer                       | Select Hitachi stand-alone flash<br>memory HN28F101 setting                                         | Special programming mode setting required. Use of PROM programmer that supports Hitachi microcomputer device types with 64-kbyte on-chip flash memory. (128-byte-unit fast page programming) |  |  |  |

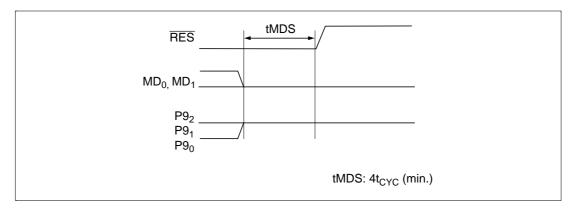

| Boot mode                                              | Reset release after MD <sub>1</sub> = FV <sub>PP</sub> /STBY =                                      | Pin   MD <sub>1</sub>   MD <sub>0</sub>   P9 <sub>2</sub>   P9 <sub>1</sub>   P9 <sub>0</sub>                                                                                                |  |  |  |

| setting<br>method                                      | 12 V application                                                                                    | Setting level 0 0 1 1 1                                                                                                                                                                      |  |  |  |

|                                                        |                                                                                                     | Reset release after above pin settings                                                                                                                                                       |  |  |  |

| User program mode setting method                       | FV <sub>PP</sub> = 12 V application                                                                 | Control bits set by software                                                                                                                                                                 |  |  |  |

| Item                       | Dual-Power-Supply Model:<br>H8/3337F                | Single-Power-Supply Model:<br>H8/3337F S-Mask Model                   |

|----------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|

| MDCR                       | 7 6 5 4 3 2 1 0<br>— — — — — — MDS1 MDS0            | 7 6 5 4 3 2 1 0 EXPE MDS1 MDS0                                        |

|                            |                                                     | Bit 7: Expanded mode enable (EXPE)                                    |

| WSCR                       | 7 6 5 4 3 2 1 0 RAMS RAMO CKDBL — WMS1 WMS0 WC1 WC0 | 7 6 5 4 3 2 1 0  - CKDBL FLSHE WMS1 WMS0 WC1 WC0                      |

|                            |                                                     | Bit 4: Flash memory control register enable (FLSHE)                   |

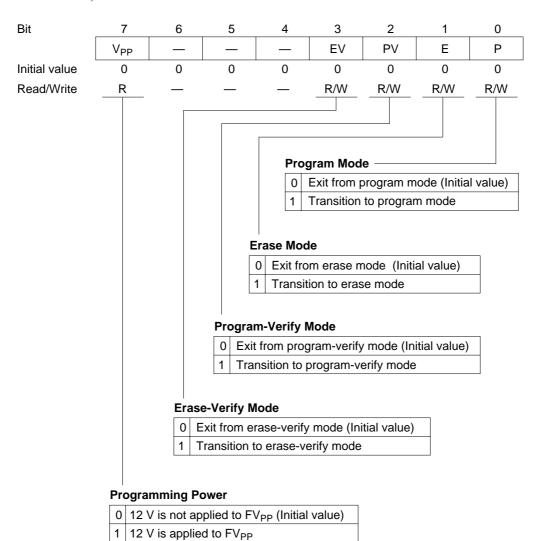

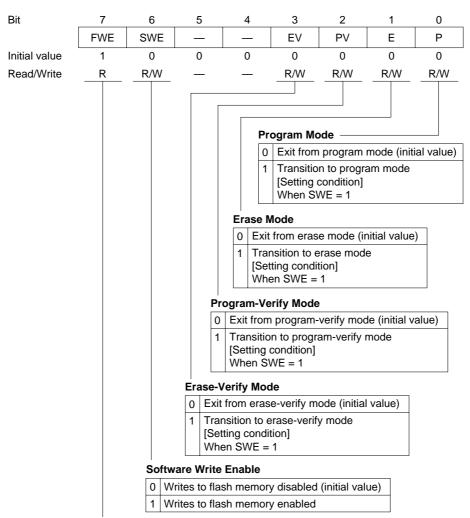

| FLMCR1                     | 7 6 5 4 3 2 1 0<br>V <sub>PP</sub> EV PV E P        | 7 6 5 4 3 2 1 0<br>FWE SWE — — EV PV E P                              |

|                            |                                                     | Bit 7: Flash write enable (FWE) Bit 6: Software write enable (SWE)    |

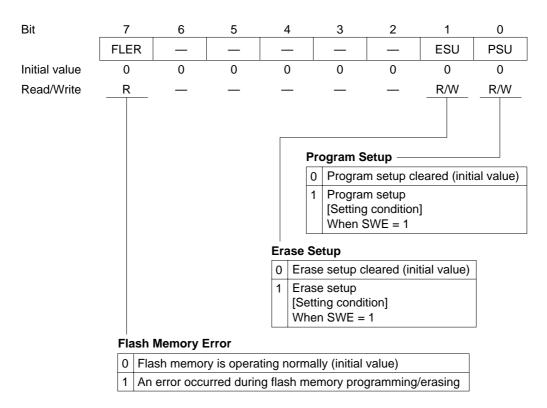

| FLMCR2                     | _                                                   | 7 6 5 4 3 2 1 0<br>FLER ESU PSU                                       |

|                            |                                                     | Bit 7: Flash memory error (FLER) Bit 1: Erase setup (ESU)             |

|                            |                                                     | Bit 0: Program setup (PSU)                                            |

| EBR1                       | 7 6 5 4 3 2 1 0<br>LB7 LB6 LB5 LB4 LB3 LB2 LB1 LB0  | _                                                                     |

|                            | LB7 LB6 LB5 LB4 LB3 LB2 LB1 LB0                     | This address is not used.                                             |

| EBR2                       | 7 6 5 4 3 2 1 0<br>SB7 SB6 SB5 SB4 SB3 SB2 SB1 SB0  | 7 6 5 4 3 2 1 0<br>EB7 EB6 EB5 EB4 EB3 EB2 EB1 EB0                    |

|                            |                                                     | Erase block register (EBR2)                                           |

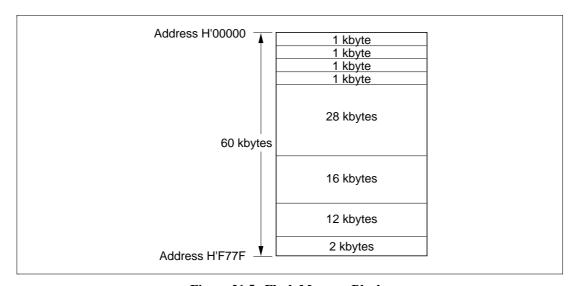

|                            |                                                     | EB0 (1 kbyte): H'0000 to H'03FF                                       |

|                            |                                                     | EB1 (1 kbyte): H'0400 to H'07FF<br>EB2 (1 kbyte): H'0800 to H'0BFF    |

|                            |                                                     | EB3 (1 kbyte): H'0C00 to H'0FFF                                       |

|                            |                                                     | EB4 (28 kbytes): H'1000 to H'7FFF                                     |

|                            |                                                     | EB5 (16 kbytes): H'8000 to H'BFFF                                     |

|                            |                                                     | EB6 (12 kbytes): H'C000 to H'EF7F<br>EB7 (2 kbytes): H'EF00 to H'F77F |

| Details                    | See section 20, ROM (Dual-Power-                    | See section 21, ROM (Single-Power-                                    |

| concerning flash memory    | Supply 60-Kbyte Flash Memory Version)               | Supply 60-Kbyte Flash Memory Version)                                 |

| Electrical characteristics | See section 23, Electrical<br>Characteristics       | See section 23, Electrical<br>Characteristics                         |

| Registers                  | See Appendix B, Registers                           | See Appendix B, Registers                                             |

Table 3 shows differences in the development environments of the H8/3337YF (dual-power-supply specification) and H8/3337SF (single-power-supply specification).

Table 3 H8/3337YF and H8/3337F S-Mask Model Development Environments

| Item                       |               | Dual-Power-Supply Model:<br>H8/3337YF | Single-Power-Supply Model: H8/3337F S-Mask Model |

|----------------------------|---------------|---------------------------------------|--------------------------------------------------|

| E6000<br>emulator          | Emulator unit | Hitachi<br>HS3008EPI60H               | Hitachi<br>HS3008EPI60H                          |

|                            | User<br>cable | Hitachi<br>HS3437ECH61H               | Hitachi<br>HS3437ECH61H                          |

| Programming socket adapter |               | Hitachi<br>HS3434ESHF1H               | Minato<br>DATA I/O                               |

| Adapter board              |               | Hitachi<br>HS0008EASF1H/2H            | Hitachi<br>HS0008EASF3H                          |

| Windows interface software |               | Hitachi<br>HS6400FWIW2SF              | Hitachi<br>HS6400FWIW2SF                         |

Table 4 shows differences in the pin settings of the H8/3337YF (dual-power-supply specification) and H8/3337SF (single-power-supply specification).

Table 4 H8/3337YF and H8/3337F S-Mask Model Pin Settings

| Dual-Power-Supply Model:<br>Item H8/3337YF |                                                         | Single-Power-Supply Model:<br>H8/3337F S-Mask Model                                                                            |

|--------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Boot mode                                  | H8/3337YF                                               | H8/3337SF                                                                                                                      |

|                                            | 0 12 V<br>8 FV <sub>PP</sub> /STBY<br>5 MD <sub>1</sub> | V <sub>CC</sub> (5 V)  23  P9 <sub>2</sub> P9 <sub>1</sub> P9 <sub>0</sub> S  MD <sub>1</sub> MD <sub>0</sub>                  |

| User programming mode                      | H8/3337YF  O 12 V  8  FV <sub>PP</sub> /STBY            | There are no state transitions due to pin states. Transitions should be implemented by means of register settings by software. |

# List of Items Revised or Added for This Version

| Section                                                                        | Page       | Item                                                                                   | Description (see Manual for details)                                              |

|--------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Notes on S-Mask Model<br>(Single-Power-Supply<br>Specification)                |            | Table 1 Differences in<br>H8/3337YF and H8/3337F S-<br>Mask Model Markings             | Single-Power-Supply<br>Model: H8/3337F S-<br>mask model sample<br>marking amended |

| 1.1 Overview                                                                   | 1          |                                                                                        | Comment added to note                                                             |

|                                                                                | 3          | Table 1.1 Features                                                                     | "Other features" specifications amended.                                          |

|                                                                                | 4          |                                                                                        | H8/3337Y ZTAT<br>HD6473337YCG16<br>deleted from series<br>lineup item             |

|                                                                                | 5          | _                                                                                      | H8/3334F-ZTAT ROM amended in "Series Lineup" specifications.                      |

|                                                                                |            |                                                                                        | Notes 1, 3 deleted                                                                |

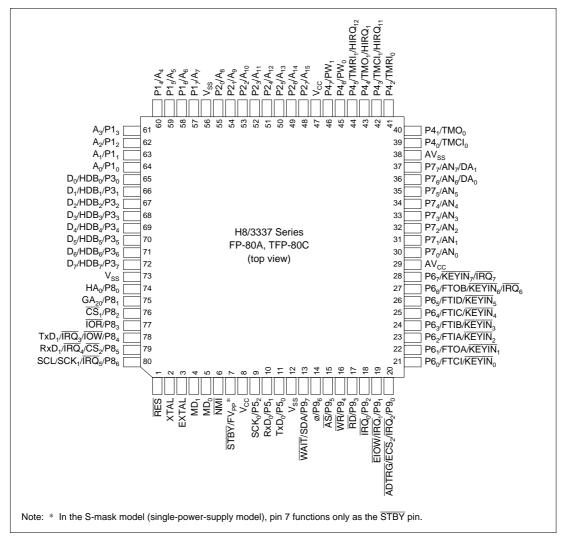

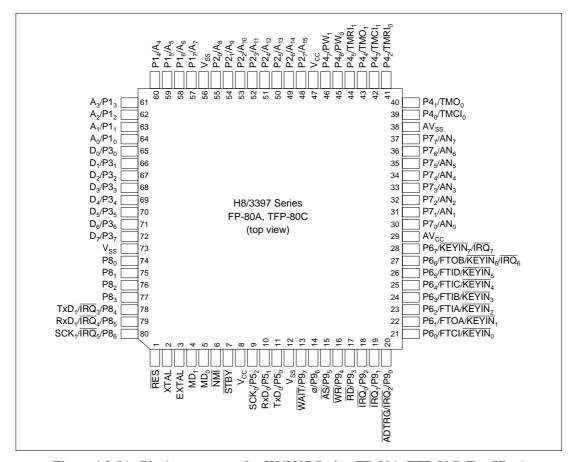

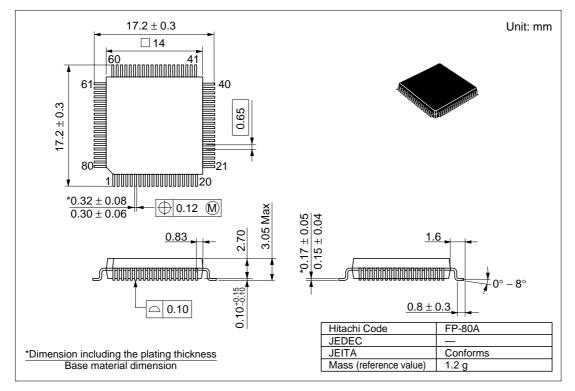

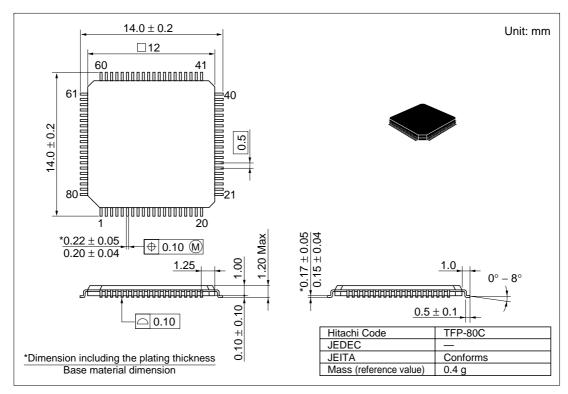

| 1.3.1 Pin Arrangement                                                          | 8          | Figure 1.2 (a) Pin<br>Arrangement for H8/3337<br>Series (FP-80A, TFP-80C, Top<br>View) | Rotated 90 degrees to the left, so that pin 1 is at the bottom left.              |

|                                                                                | 9          | Figure 1.2 (b) Pin<br>Arrangement for H8/3397<br>Series (FP-80A, TFP-80C, Top<br>View) |                                                                                   |

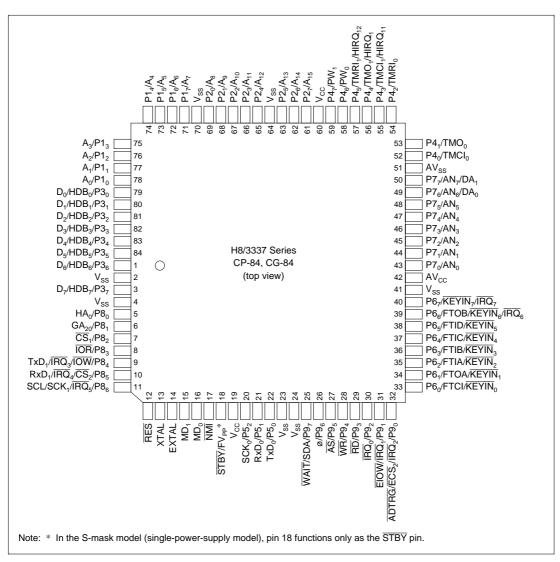

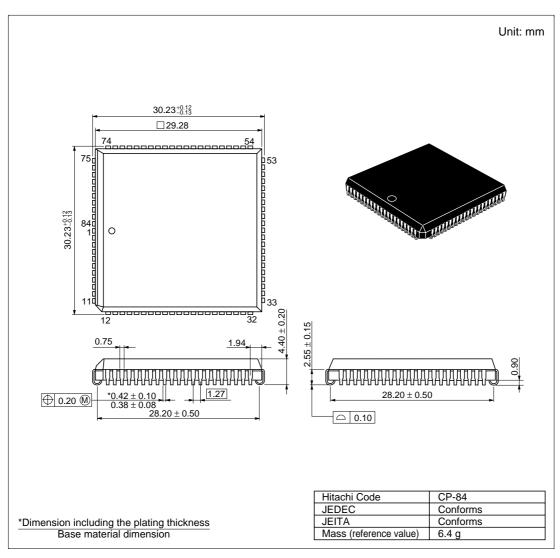

|                                                                                | 10         | Figure 1.3 (a) Pin<br>Arrangement for H8/3337<br>Series (CP-84, CG-84, Top<br>View)    | -                                                                                 |

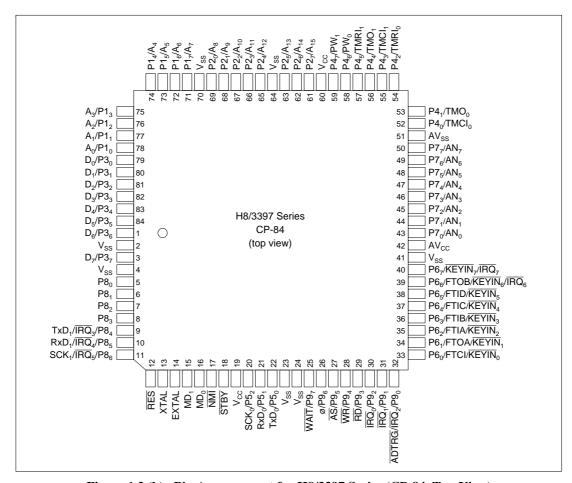

|                                                                                | 11         | Figure 1.3 (b) Pin<br>Arrangement for H8/3397<br>Series (CP-84, Top View)              | -                                                                                 |

| 4.3.1 Overview                                                                 | 75         | Table 4.2 Interrupts                                                                   | Note numbers amended                                                              |

| 6.2.2 Oscillator Circuit (H8/3337SF)                                           | 101 to 105 |                                                                                        | Added                                                                             |

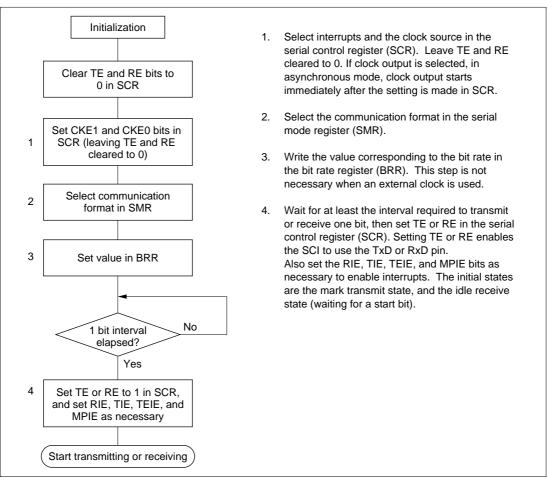

| 12.3.2 Asynchronous<br>Mode                                                    | 263        | Figure 12.5 Sample Flowchart for Transmitting Serial Data                              | <ul><li>Flowchart amended.</li><li>Procedure 1<br/>description added.</li></ul>   |

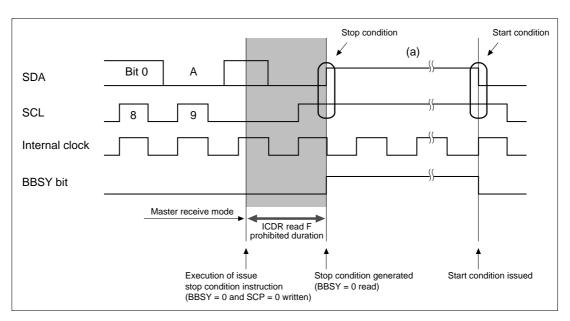

| Section 13 I <sup>2</sup> C Bus<br>Interface (H8/3337 Series<br>Only) [Option] | 281        |                                                                                        | Descriptions 1 and 3 deleted                                                      |

| Section                                      | Page       | Item                                                                       | Description (see Manual for details) |

|----------------------------------------------|------------|----------------------------------------------------------------------------|--------------------------------------|

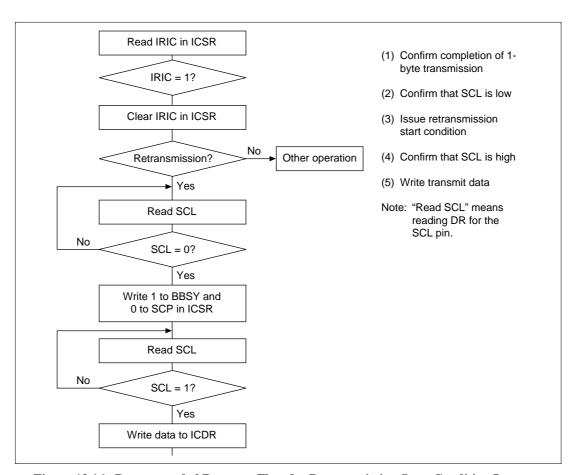

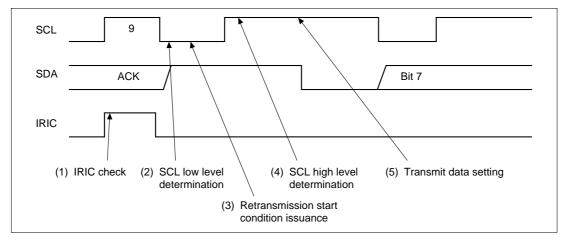

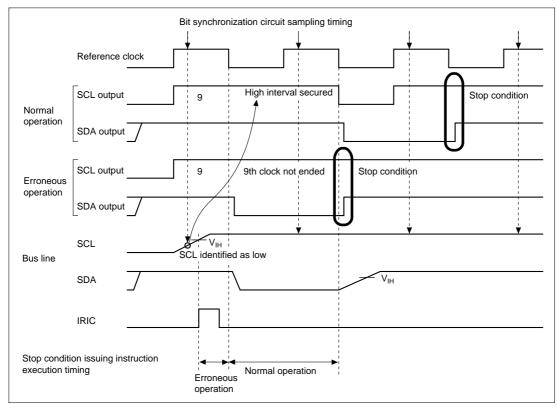

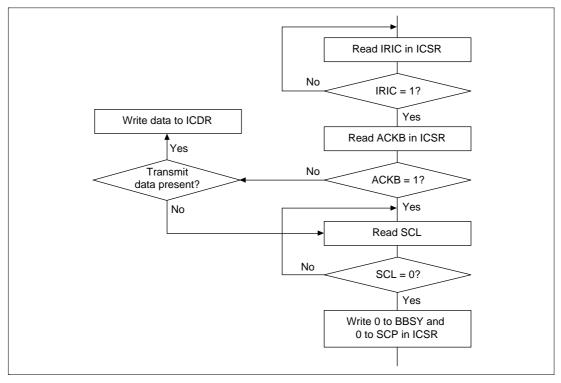

| 13.4 Application Notes                       | 309        | Note on Issuance of     Retransmission Start     Condition                 | Added                                |

|                                              |            | 5. Note on Issuance of Stop Condition                                      |                                      |

|                                              |            | 6. Countermeasure                                                          |                                      |

|                                              |            | 7. Additional Note                                                         |                                      |

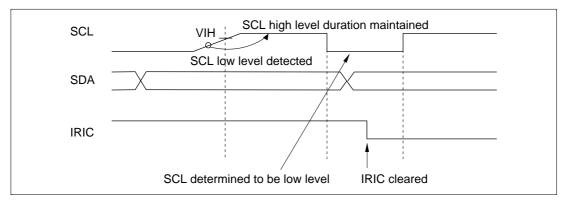

|                                              |            | Precautions when Clearing<br>the IRIC Flag when Using<br>the Wait Function |                                      |

| 15.6.6 Effect on Absolute<br>Accuracy        | 352        | Figure 15.10 Example of Analog Input Circuit                               | Figure amended                       |

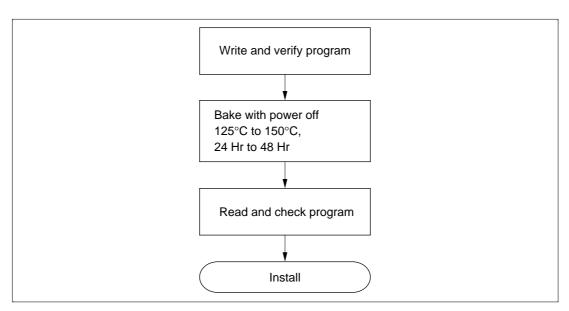

| 18.3.2 Notes on Programming                  | 371        |                                                                            | (1) description added.               |

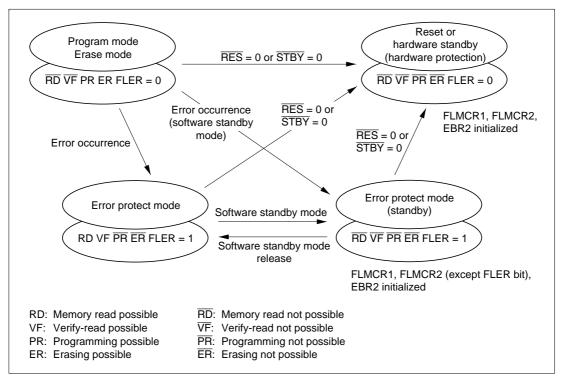

| 21.1.7 Flash Memory<br>Operating Modes       | 500        | Figure 21.2 Flash Memory<br>Related State Transitions                      | "SWE" amended to "FLSHE".            |

|                                              | 501        | Figure 21.3 Boot Mode                                                      | Procedure 2 amended.                 |

|                                              | 502        | Figure 21.4 User<br>Programming Mode (Example)                             | Procedure 2 amended.                 |

| 21.2.3 Erase Block<br>Register 2 (EBR2)      | 507        |                                                                            | Bit 7 * and Note description added.  |

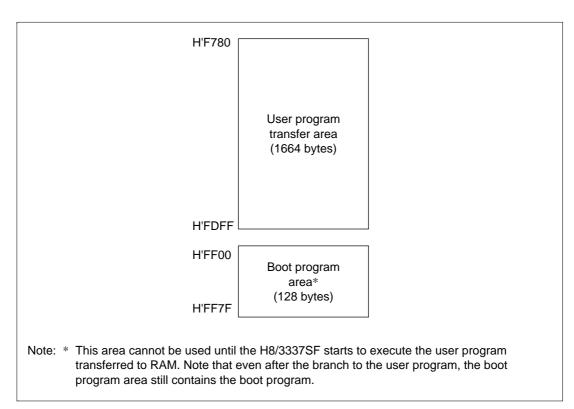

| 21.3.1 Boot Mode                             | 512        | RAM Area Allocation in Boot<br>Mode                                        | Description amended.                 |

|                                              | 513        | Figure 21.9 RAM Areas in Boot Mode                                         | Amended                              |

|                                              |            | Notes on Use of Boot Mode                                                  | 5 description amended.               |

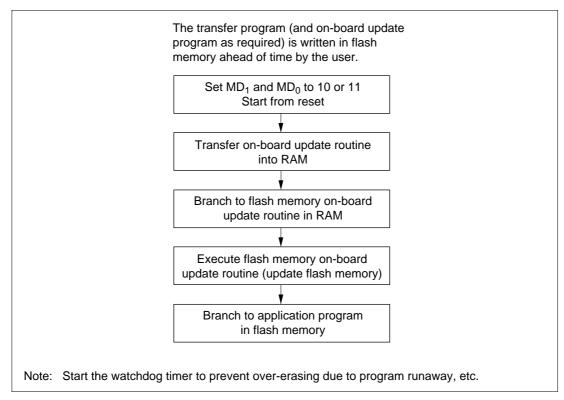

| 21.4 to 21.4.4                               | 516 to 520 |                                                                            | Entire description amended.          |

| 21.5.1 Writer Mode<br>Setting                | 524        |                                                                            | * and Note description added.        |

| 21.5.3 Operation in Writer Mode              | 534        | Figure 21.22 Status Read<br>Mode Timing Waveforms                          | Note amended                         |

|                                              |            | Table 21.19 Status Read<br>Mode Return Codes                               |                                      |

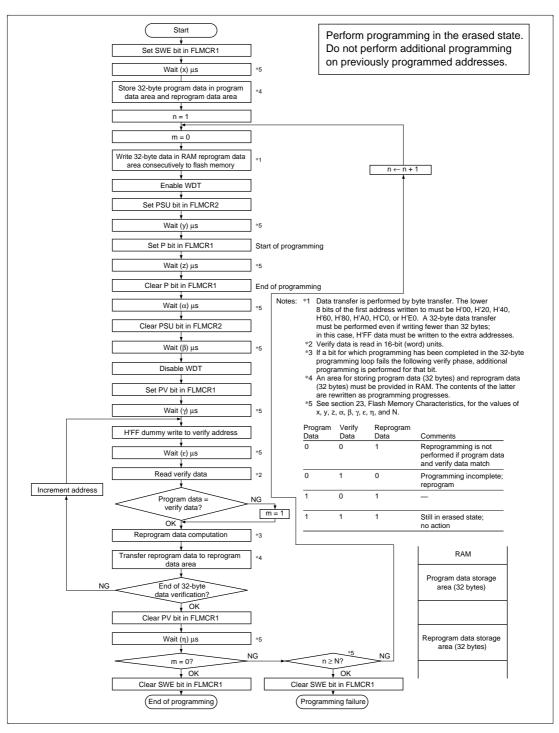

| 21.6 Flash Memory<br>Programming and Erasing | 536        | (1) Program with the specified voltage and timing                          | Description amended.                 |

| Precautions                                  | 537        | Table 21.22 Area Accessed in Each Mode with FLSHE = 0 and FLSHE = 1        | FLSHE = 1 mode 2 amended             |

| Section                                                                  | Page       | Item                                                                                          | Description (see Manual for details) |

|--------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------|--------------------------------------|

| 22.3.5 Application Notes                                                 | 546        |                                                                                               | 2 description deleted.               |

| 23 Electrical<br>Characteristics                                         | 549 to 596 |                                                                                               | Heading number amended               |

| 23.3 Absolute Maximum<br>Ratings (H8/3337SF Low-<br>Voltage Version      | 573        |                                                                                               | Newly added                          |

| 23.4 Electrical<br>Characteristics<br>(H8/3337SF Low-Voltage<br>Version) | 574 to 586 |                                                                                               | Newly added                          |

| B.2 Function                                                             | 661        | I <sup>2</sup> C Bus Control Register<br>Bit 2 to 0: I <sup>2</sup> C Transfer Rate<br>Select | Table amended and note added         |

# Contents

| Sect | ion 1            | Overview                                                  | 1  |  |

|------|------------------|-----------------------------------------------------------|----|--|

| 1.1  | Overv            | iew                                                       | 1  |  |

| 1.2  | .2 Block Diagram |                                                           | 6  |  |

| 1.3  | Pin As           | ssignments and Functions                                  | 8  |  |

|      | 1.3.1            | Pin Arrangement                                           | 8  |  |

|      | 1.3.2            | Pin Functions                                             | 12 |  |

| Sect | ion 2            | CPU                                                       | 25 |  |

| 2.1  | Overv            | iew                                                       | 25 |  |

|      | 2.1.1            | Features                                                  | 25 |  |

|      | 2.1.2            | Address Space                                             | 26 |  |

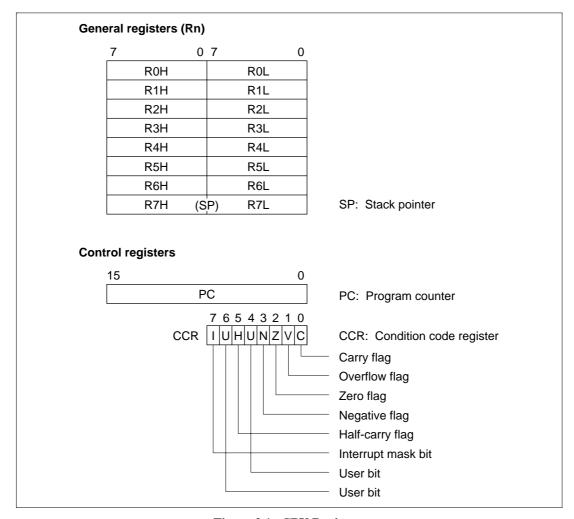

|      | 2.1.3            | Register Configuration                                    | 26 |  |

| 2.2  | Regist           | er Descriptions                                           | 27 |  |

|      | 2.2.1            | General Registers                                         | 27 |  |

|      | 2.2.2            | Control Registers                                         | 27 |  |

|      | 2.2.3            | Initial Register Values                                   | 28 |  |

| 2.3  | Data F           | Formats                                                   | 29 |  |

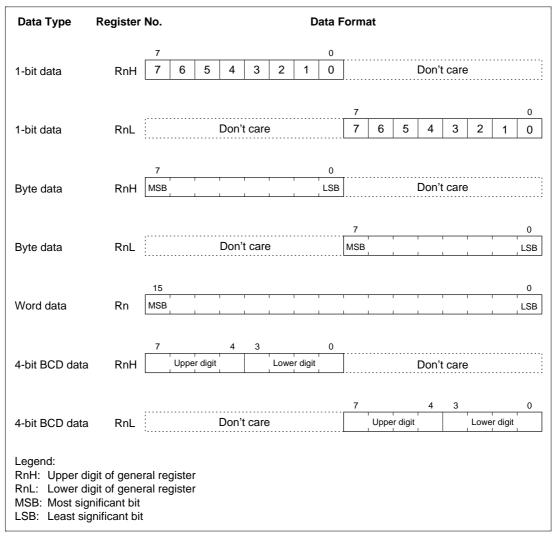

|      | 2.3.1            | Data Formats in General Registers                         | 30 |  |

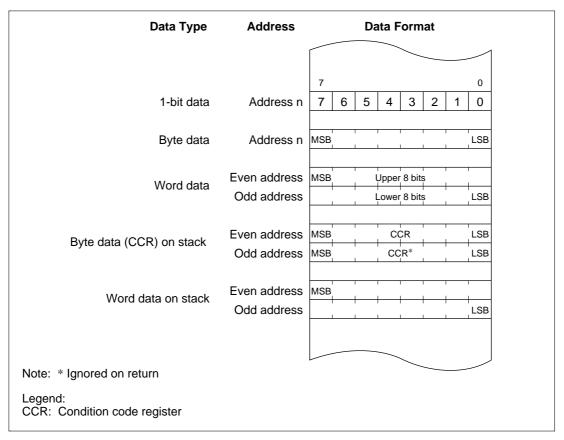

|      | 2.3.2            | Memory Data Formats                                       | 31 |  |

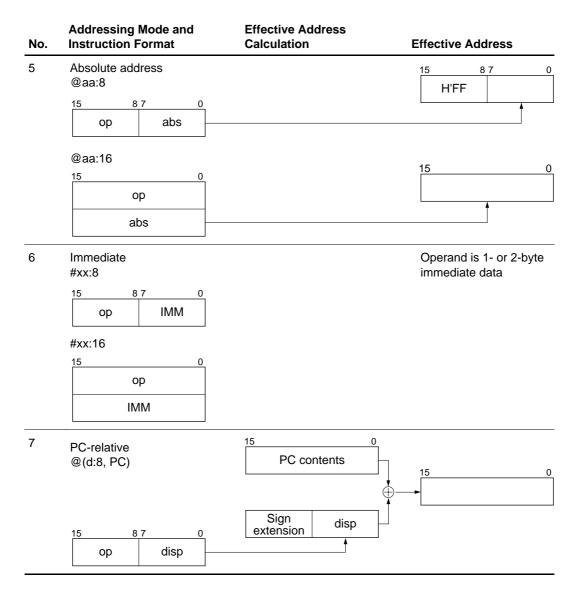

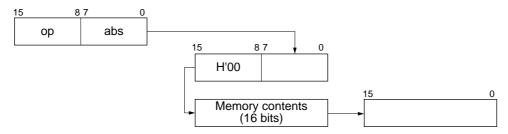

| 2.4  | Addre            | Addressing Modes                                          |    |  |

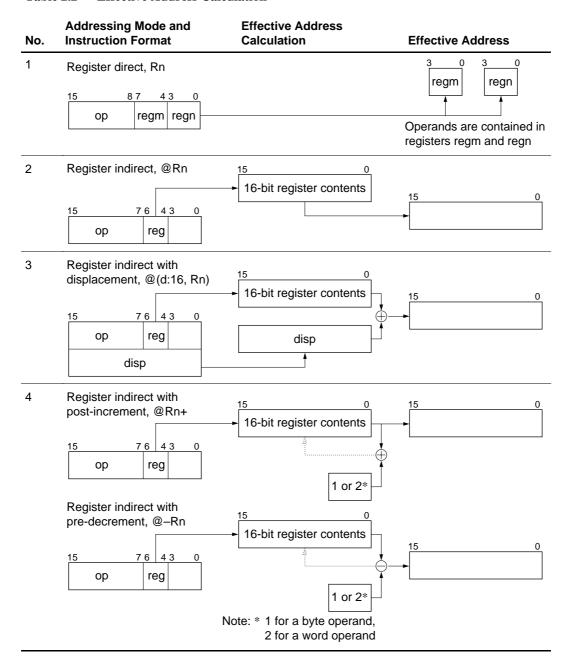

|      | 2.4.1            | Addressing Mode                                           | 32 |  |

|      | 2.4.2            | Calculation of Effective Address                          | 34 |  |

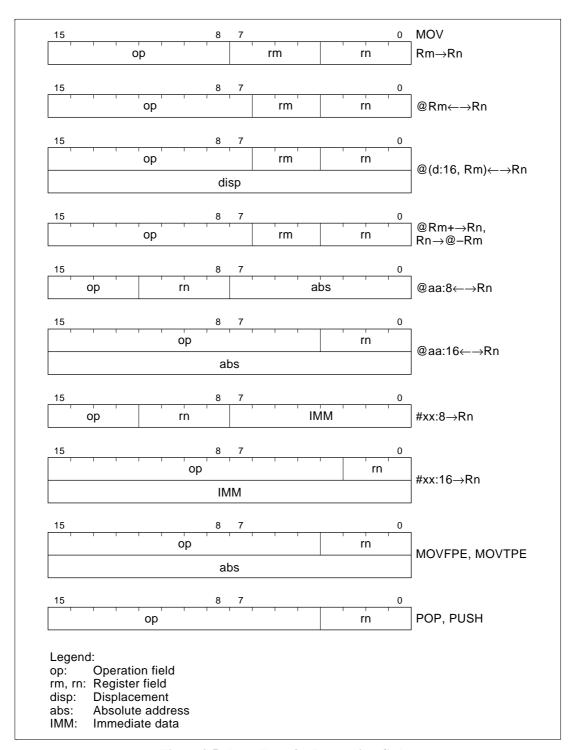

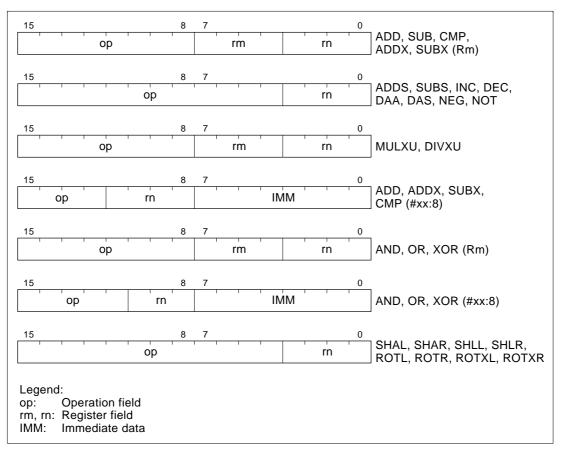

| 2.5  | Instruc          | ction Set                                                 | 38 |  |

|      | 2.5.1            | Data Transfer Instructions                                | 40 |  |

|      | 2.5.2            | Arithmetic Operations                                     | 42 |  |

|      | 2.5.3            | Logic Operations                                          | 43 |  |

|      | 2.5.4            | Shift Operations                                          | 43 |  |

|      | 2.5.5            | Bit Manipulations                                         | 45 |  |

|      | 2.5.6            | Branching Instructions                                    | 50 |  |

|      | 2.5.7            | System Control Instructions                               | 52 |  |

|      | 2.5.8            | Block Data Transfer Instruction.                          | 53 |  |

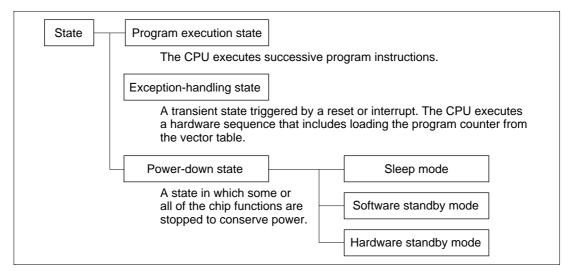

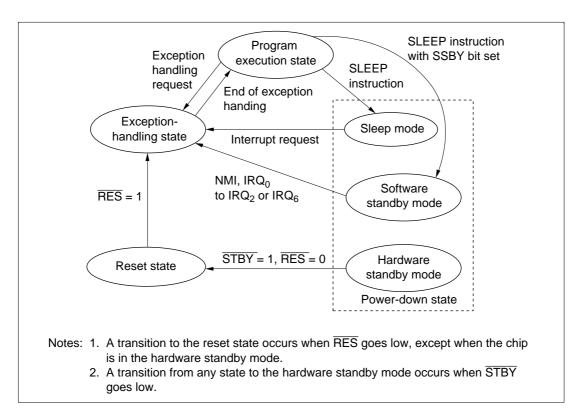

| 2.6  | CPU S            | States                                                    | 55 |  |

|      | 2.6.1            | Overview                                                  | 55 |  |

|      | 2.6.2            | Program Execution State                                   | 56 |  |

|      | 2.6.3            | Exception-Handling State                                  | 56 |  |

|      | 2.6.4            | Power-Down State                                          | 57 |  |

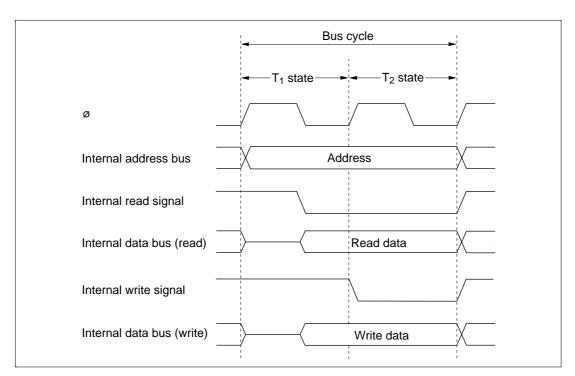

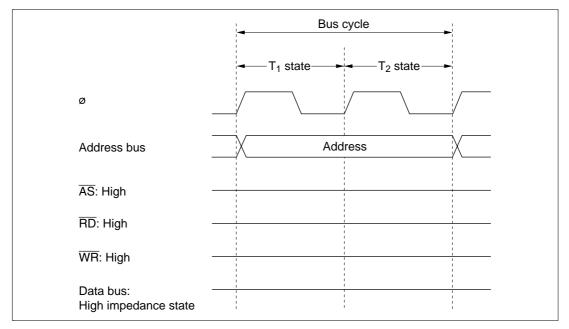

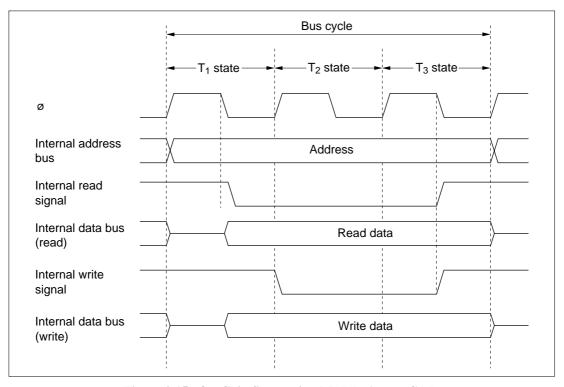

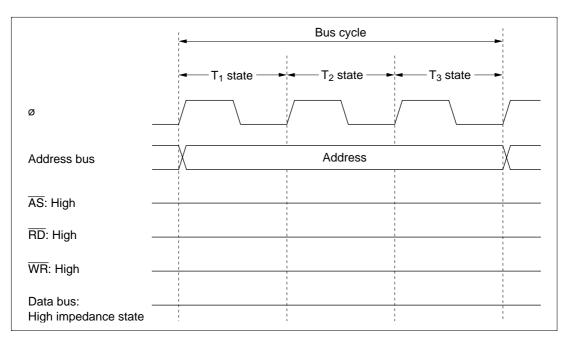

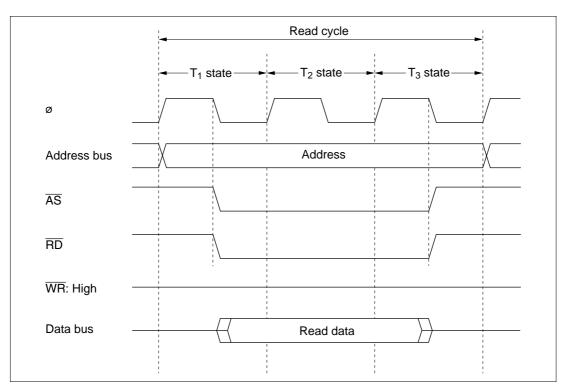

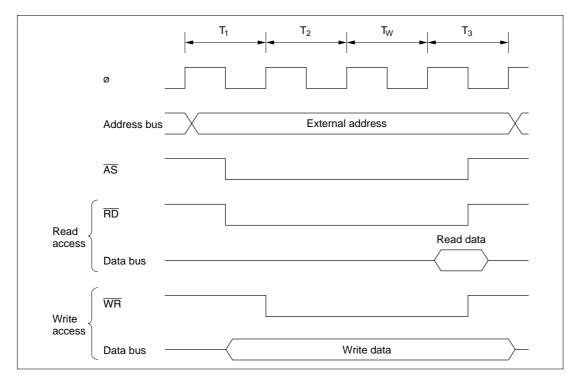

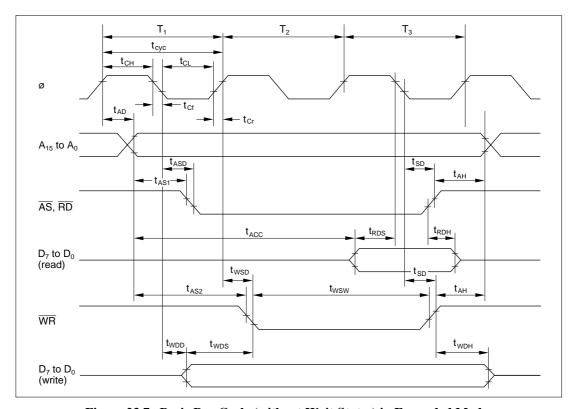

| 2.7  | Acces            | s Timing and Bus Cycle                                    | 57 |  |

|      | 2.7.1            | Access to On-Chip Memory (RAM and ROM)                    |    |  |

|      | 2.7.2            | Access to On-Chip Supporting Modules and External Devices |    |  |

|      |                  | - 11 <del>-</del> <del>-</del>                            |    |  |

i

| Sect | ion 3  | MCU Operating Modes and Address Space | 63  |

|------|--------|---------------------------------------|-----|

| 3.1  | Overv  | riew                                  | 63  |

|      | 3.1.1  | Mode Selection                        | 63  |

|      | 3.1.2  | Mode and System Control Registers     | 63  |

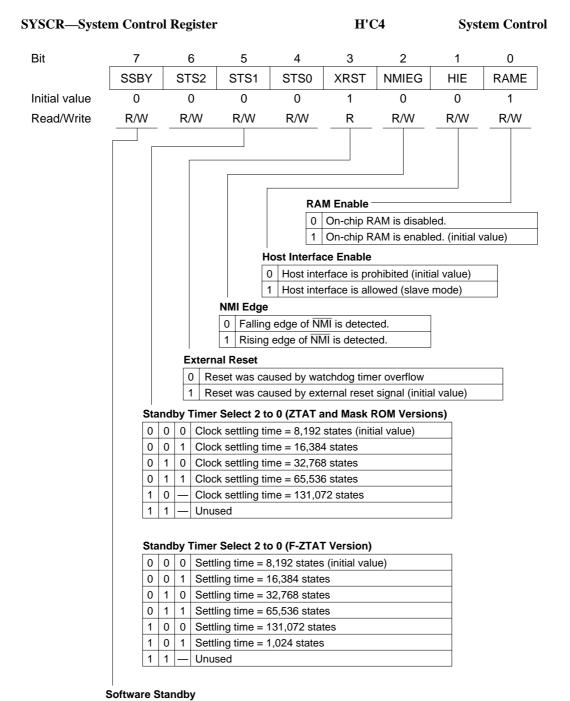

| 3.2  | Syste  | m Control Register (SYSCR)            | 64  |

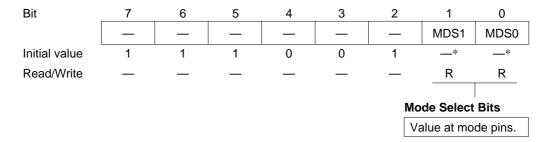

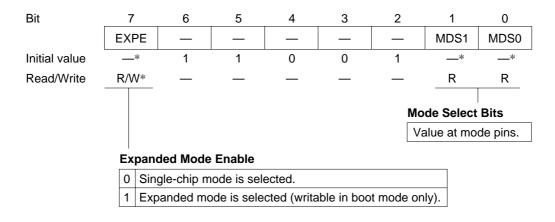

| 3.3  | Mode   | Control Register (MDCR)               | 66  |

| 3.4  | Addre  | ess Space Map in Each Operating Mode  | 66  |

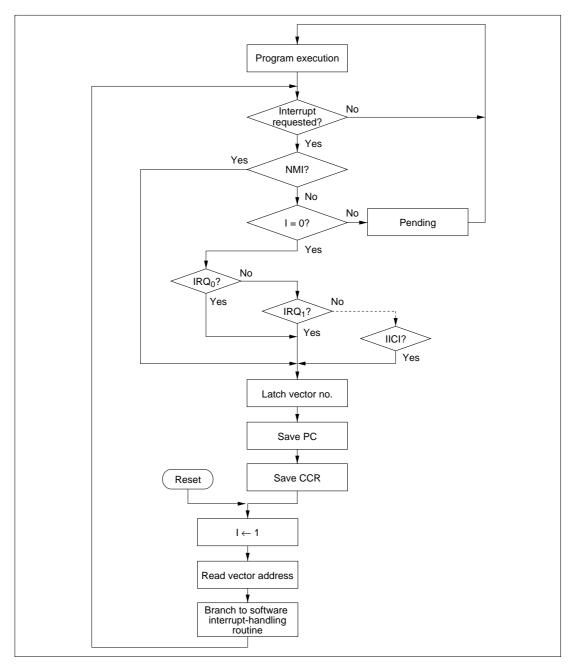

| Sect | ion 4  | Exception Handling                    | 71  |

| 4.1  | Overv  | view                                  | 71  |

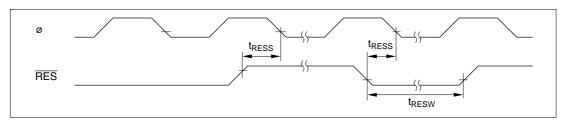

| 4.2  | Reset  |                                       | 71  |

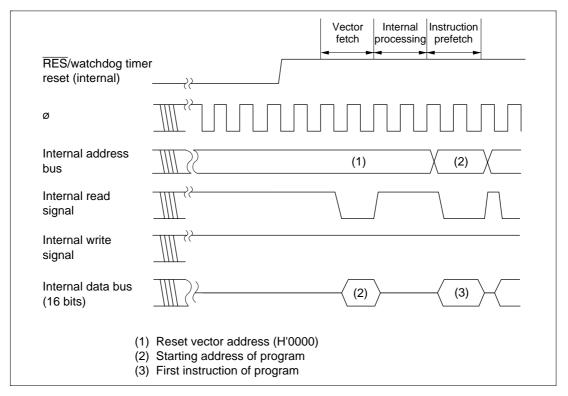

|      | 4.2.1  | Overview                              | 71  |

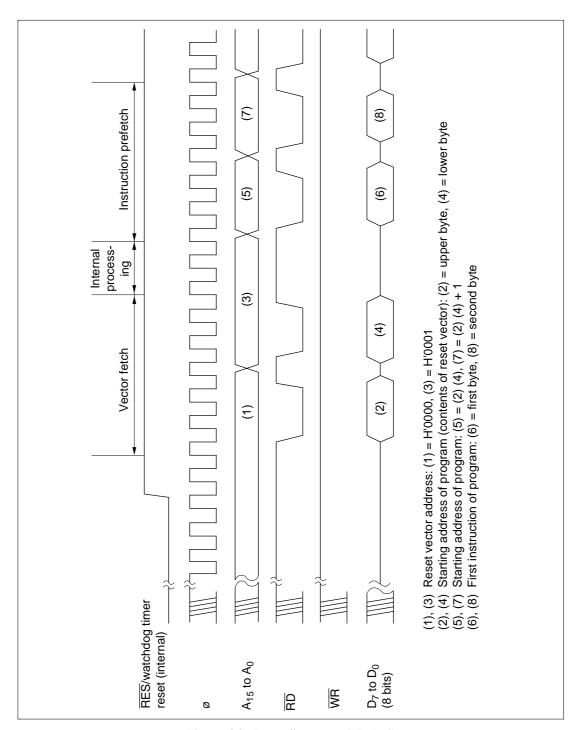

|      | 4.2.2  | Reset Sequence                        | 71  |

|      | 4.2.3  | Disabling of Interrupts after Reset   | 74  |

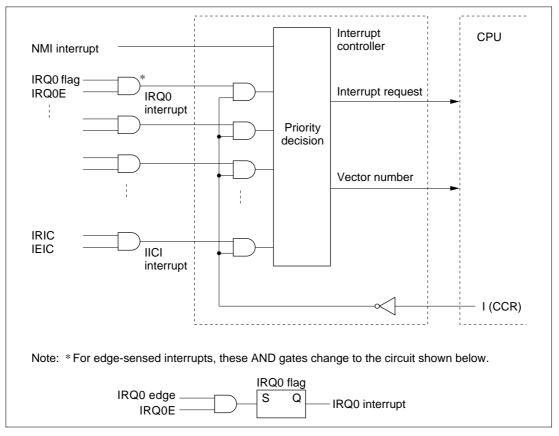

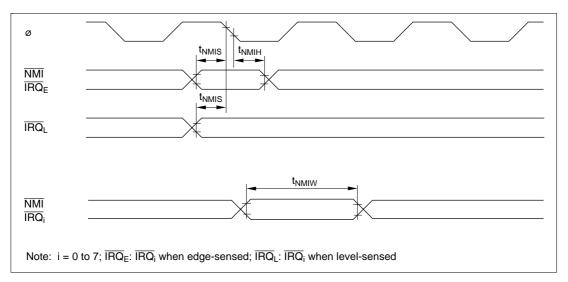

| 4.3  | Interr | upts                                  | 74  |

|      | 4.3.1  | Overview                              |     |

|      | 4.3.2  | Interrupt-Related Registers           | 76  |

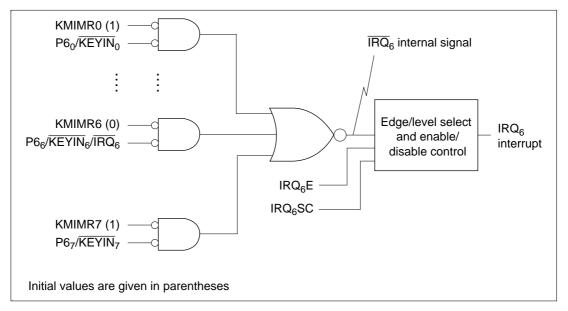

|      | 4.3.3  | External Interrupts                   | 80  |

|      | 4.3.4  | Internal Interrupts                   | 80  |

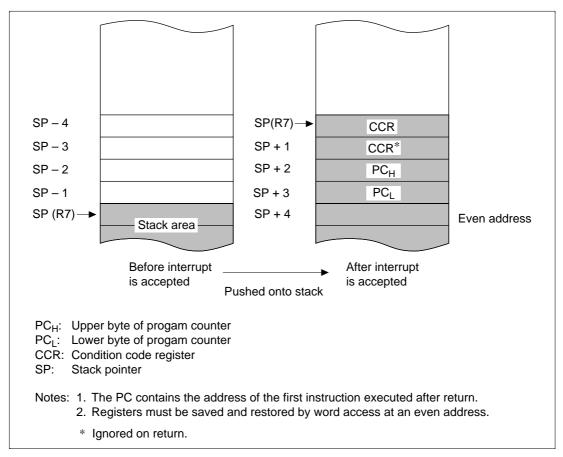

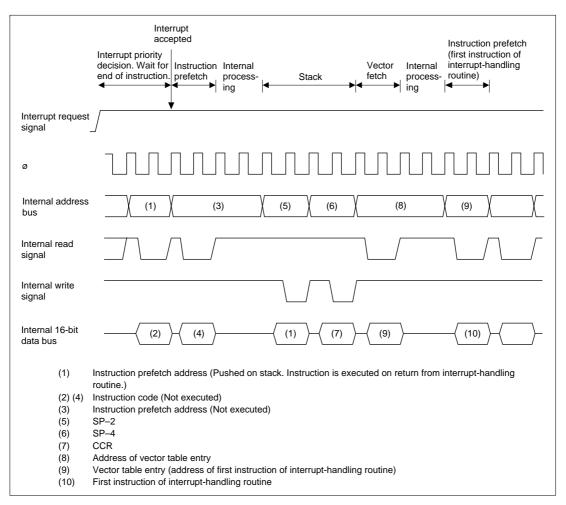

|      | 4.3.5  | Interrupt Handling                    | 81  |

|      | 4.3.6  | Interrupt Response Time               | 86  |

|      | 4.3.7  | Precaution                            | 86  |

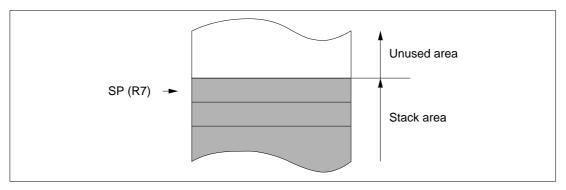

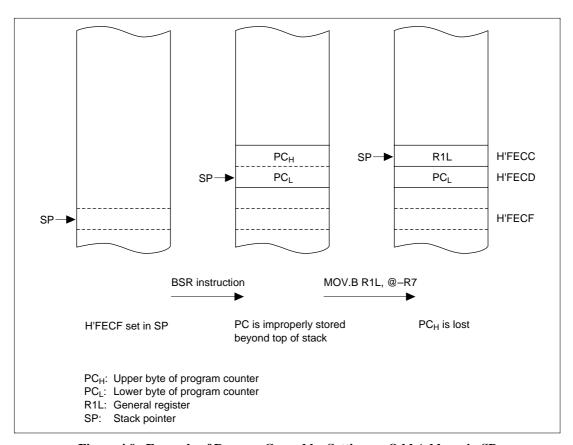

| 4.4  | Note   | on Stack Handling                     | 87  |

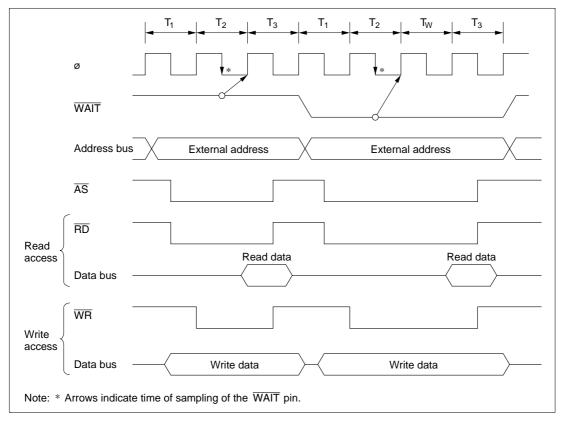

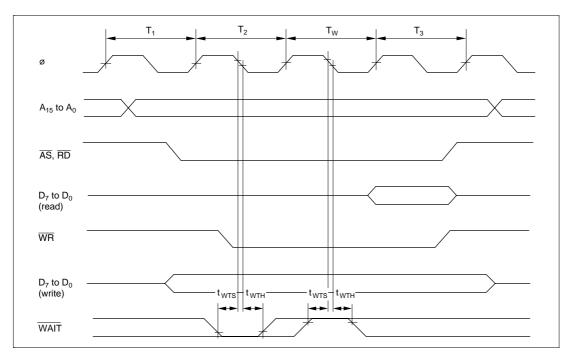

| Sect |        | Wait-State Controller                 |     |

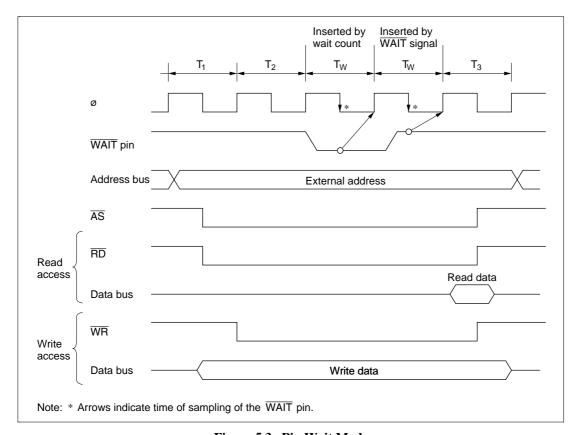

| 5.1  | Overv  | view                                  | 89  |

|      | 5.1.1  | Features                              | 89  |

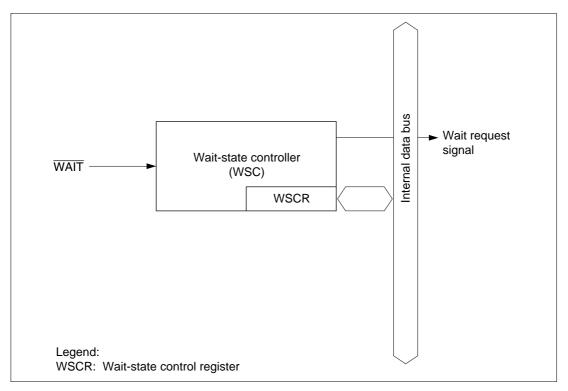

|      | 5.1.2  | Block Diagram                         | 89  |

|      | 5.1.3  | Input/Output Pins                     | 90  |

|      | 5.1.4  | Register Configuration                | 90  |

| 5.2  | Regis  | ter Description                       | 90  |

|      | 5.2.1  | Wait-State Control Register (WSCR)    | 90  |

| 5.3  | Wait   | Modes                                 | 92  |

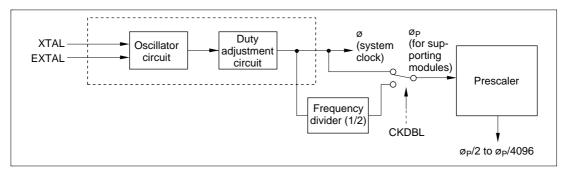

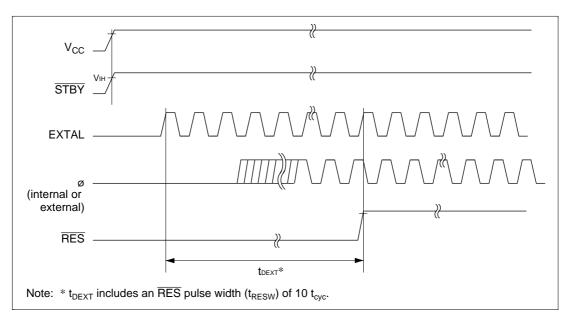

| Sect | ion 6  | Clock Pulse Generator                 | 95  |

| 6.1  | Overv  | view                                  | 95  |

|      | 6.1.1  | Block Diagram                         | 95  |

|      | 6.1.2  | Wait-State Control Register (WSCR)    | 96  |

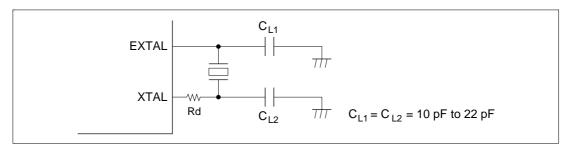

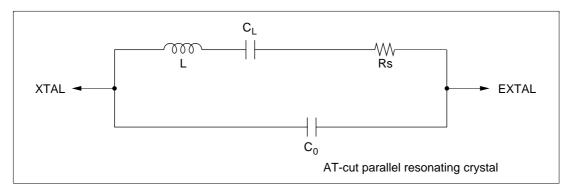

| 6.2  | Oscill | ator Circuit                          | 97  |

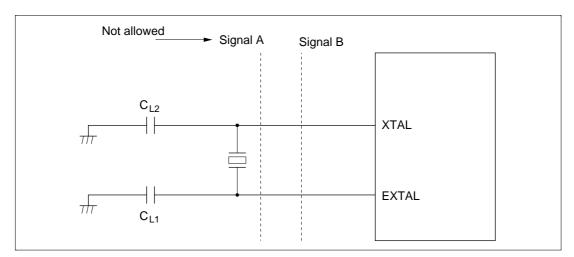

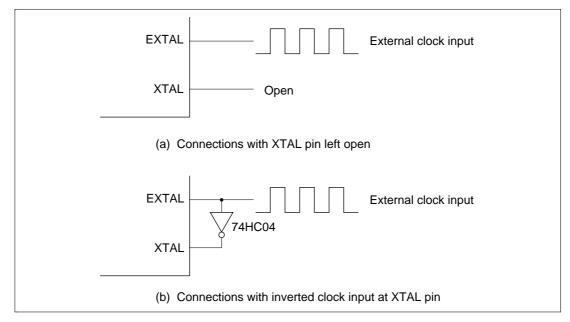

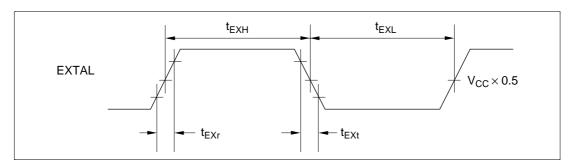

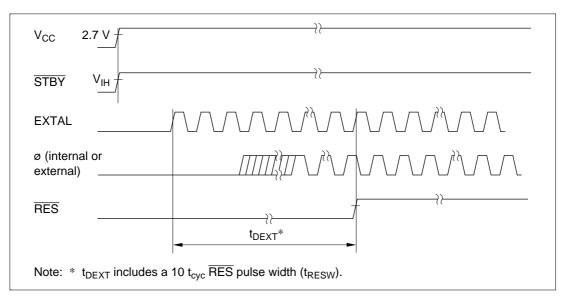

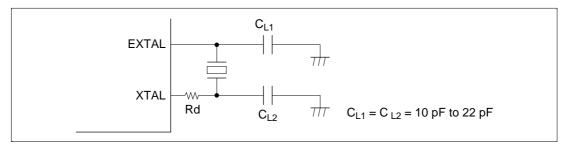

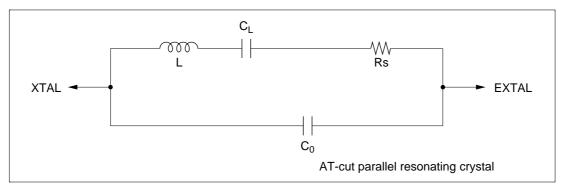

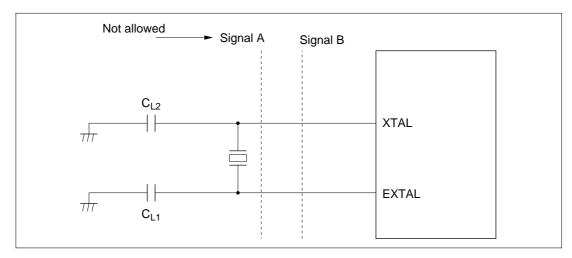

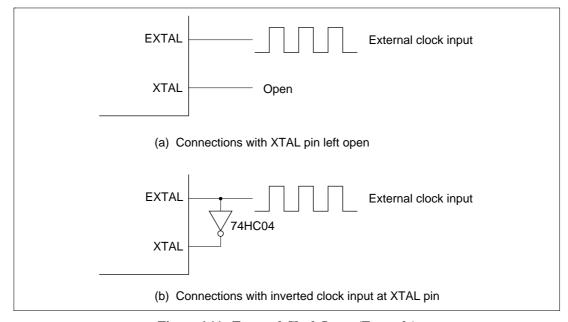

|      | 6.2.1  | Oscillator (Generic Device)           | 97  |

|      | 6.2.2  | Oscillator Circuit (H8/3337SF)        | 101 |

| 6.3  | Duty   | Adjustment Circuit                    | 105 |

| 6.4  | Presca | aler                                  | 105 |

| Secti | ion 7   | I/O Ports                               | 107 |

|-------|---------|-----------------------------------------|-----|

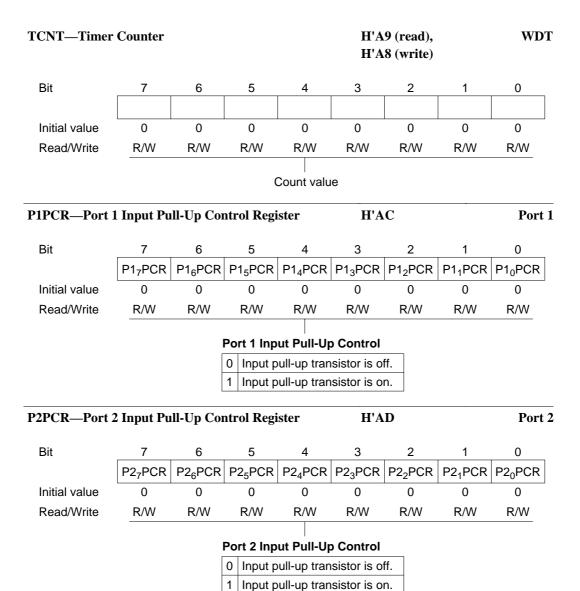

| 7.1   | Overvi  | ew                                      | 107 |

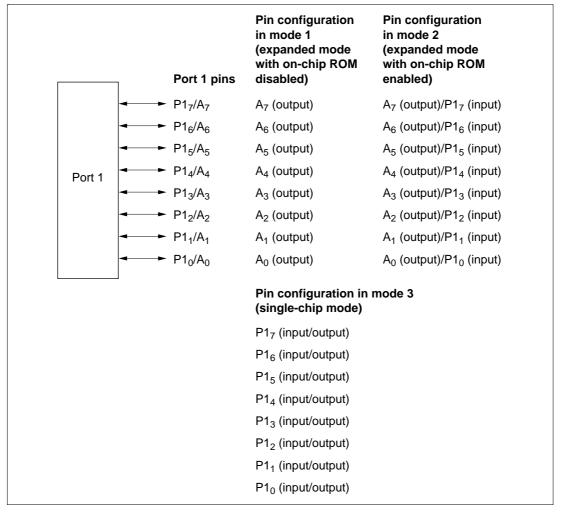

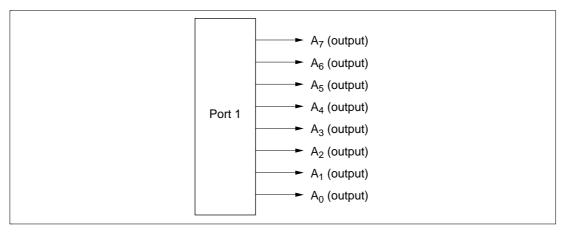

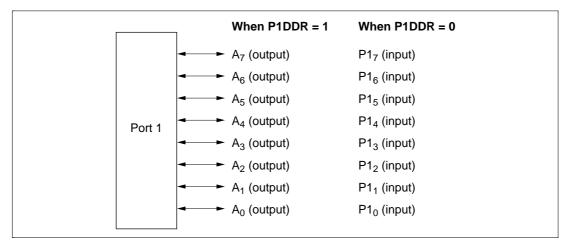

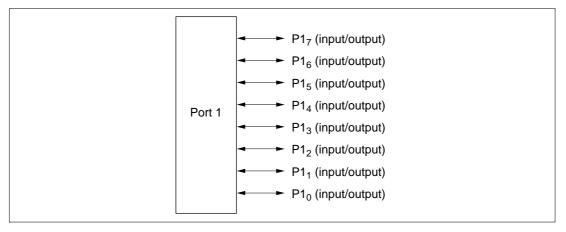

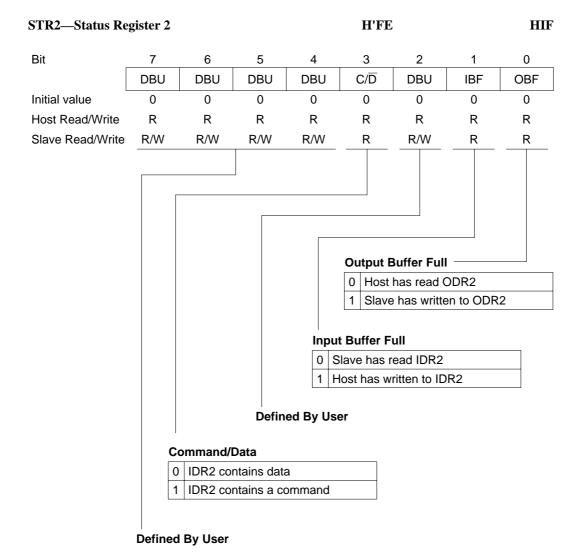

| 7.2   | Port 1. |                                         | 112 |

|       | 7.2.1   | Overview                                | 112 |

|       | 7.2.2   | Register Configuration and Descriptions | 113 |

|       | 7.2.3   | Pin Functions in Each Mode              | 115 |

|       | 7.2.4   | Input Pull-Up Transistors               | 117 |

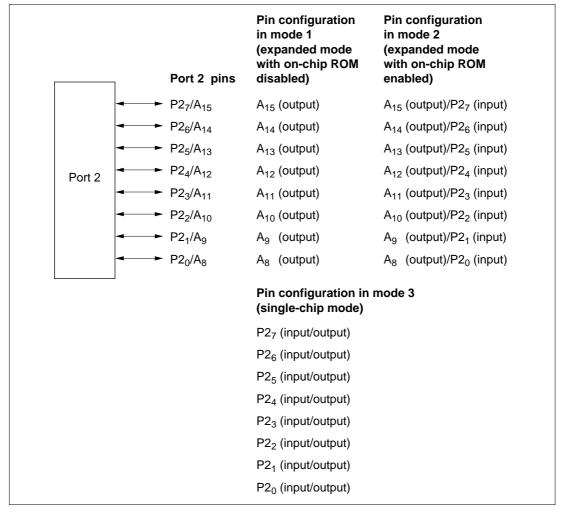

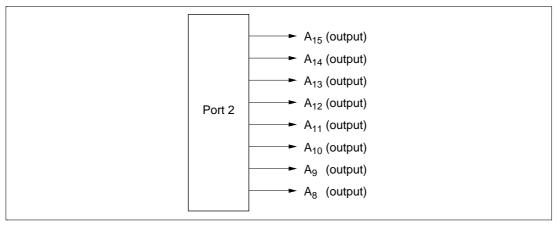

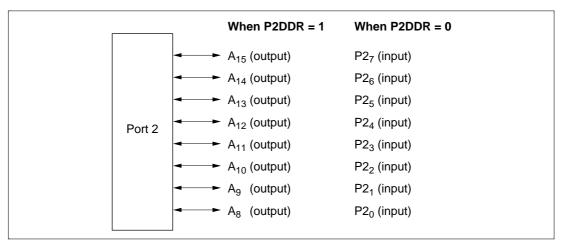

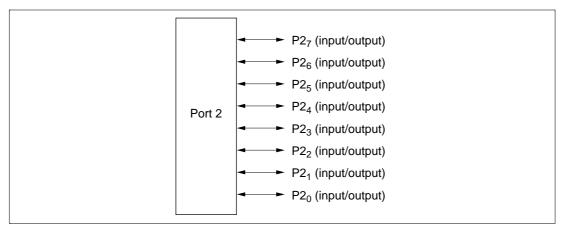

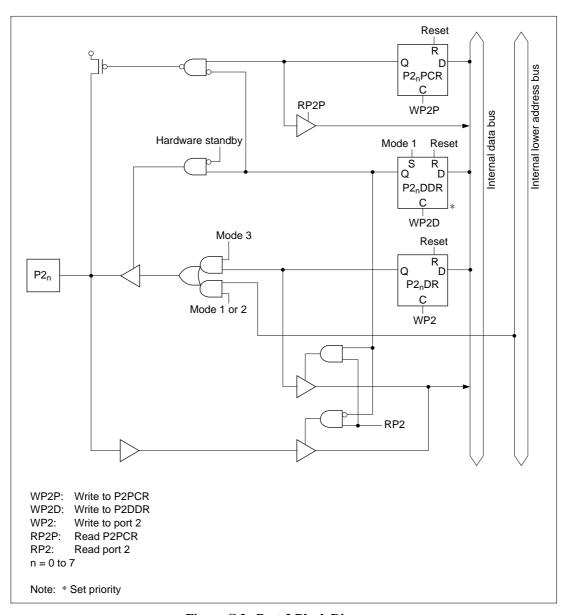

| 7.3   | Port 2. |                                         | 118 |

|       | 7.3.1   | Overview                                | 118 |

|       | 7.3.2   | Register Configuration and Descriptions | 119 |

|       | 7.3.3   | Pin Functions in Each Mode              | 121 |

|       | 7.3.4   | Input Pull-Up Transistors               | 123 |

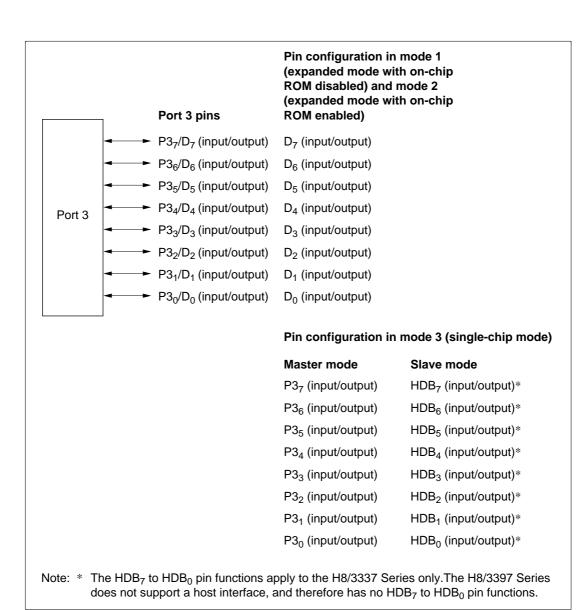

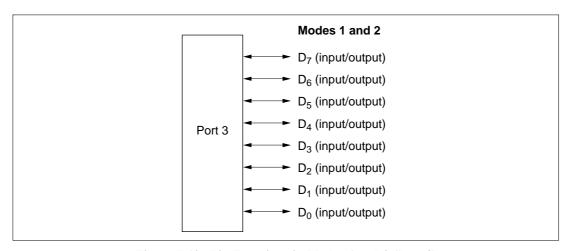

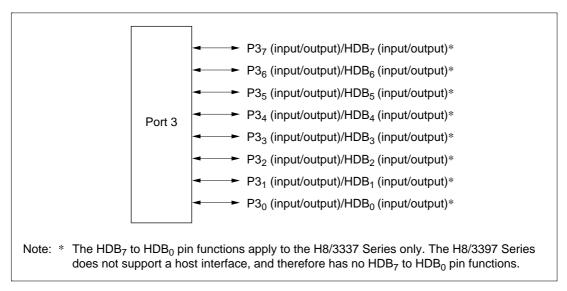

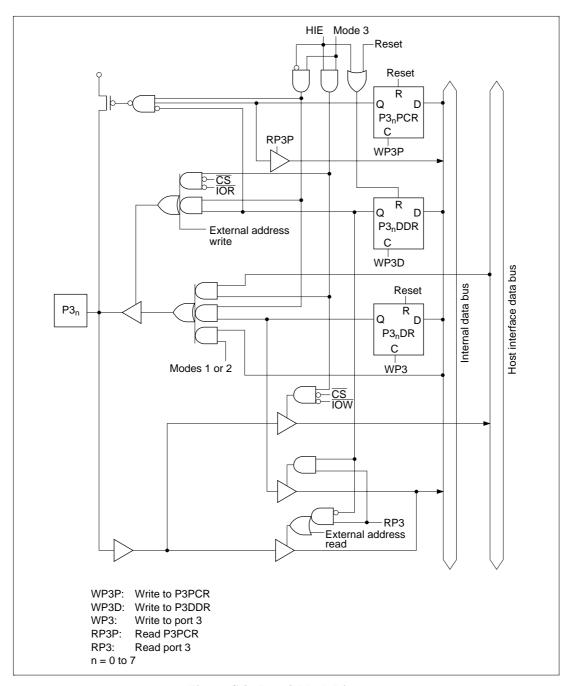

| 7.4   | Port 3. |                                         | 123 |

|       | 7.4.1   | Overview                                | 123 |

|       | 7.4.2   | Register Configuration and Descriptions | 125 |

|       | 7.4.3   | Pin Functions in Each Mode              | 127 |

|       | 7.4.4   | Input Pull-Up Transistors.              | 129 |

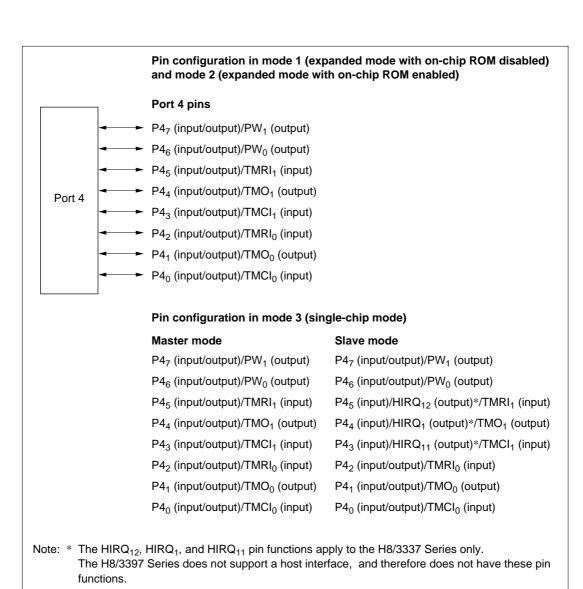

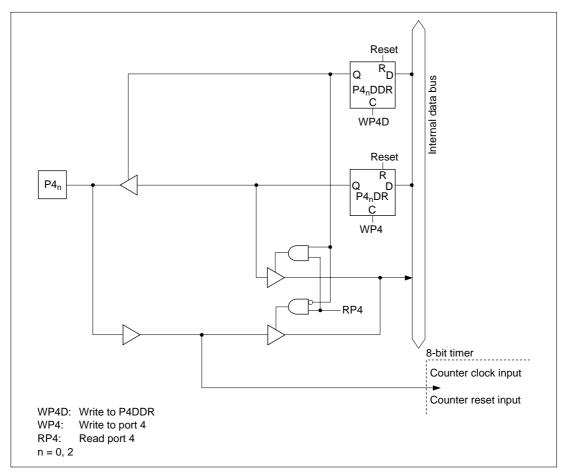

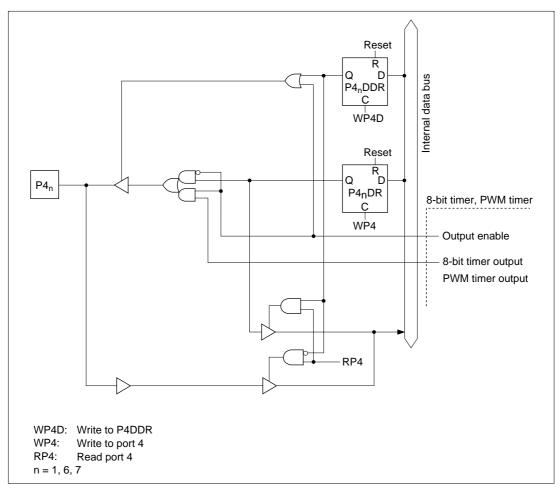

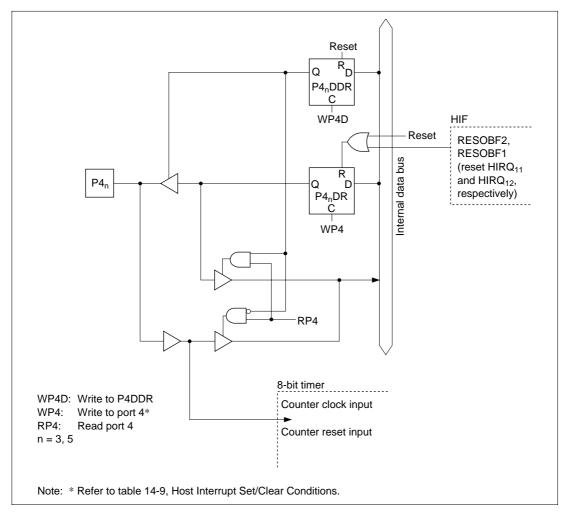

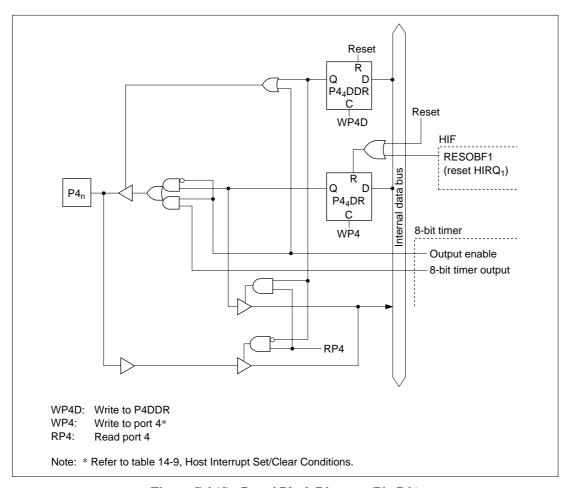

| 7.5   | Port 4. |                                         | 129 |

|       | 7.5.1   | Overview                                | 129 |

|       | 7.5.2   | Register Configuration and Descriptions | 131 |

|       | 7.5.3   | Pin Functions                           | 133 |

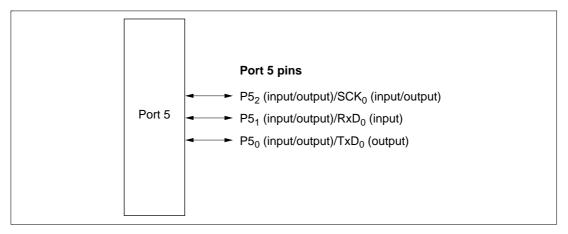

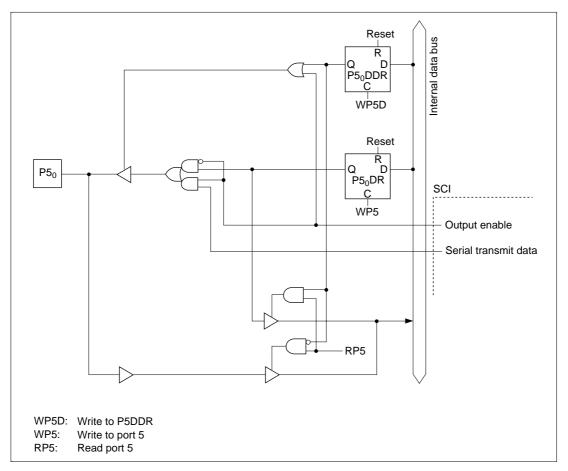

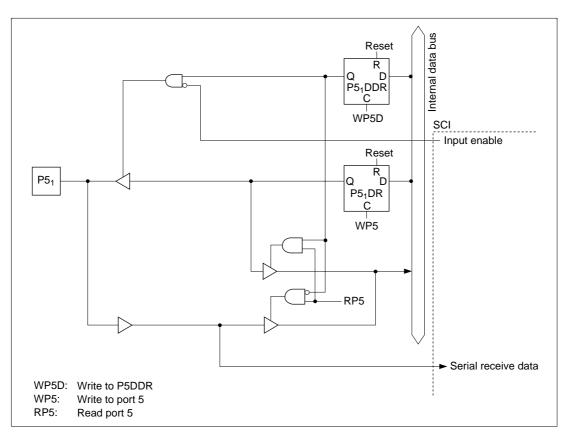

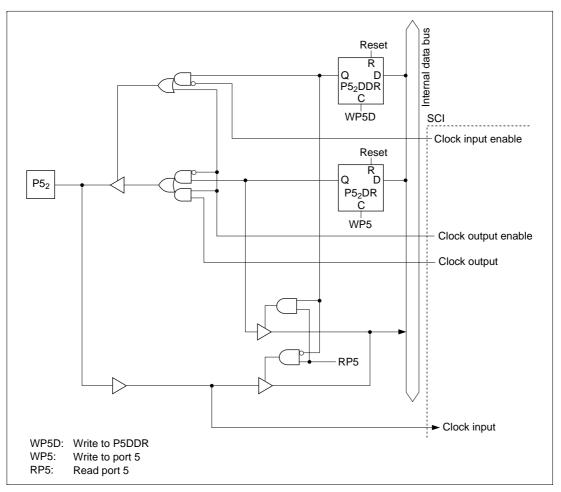

| 7.6   | Port 5. |                                         | 135 |

|       | 7.6.1   | Overview                                | 135 |

|       | 7.6.2   | Register Configuration and Descriptions | 135 |

|       | 7.6.3   | Pin Functions                           | 137 |

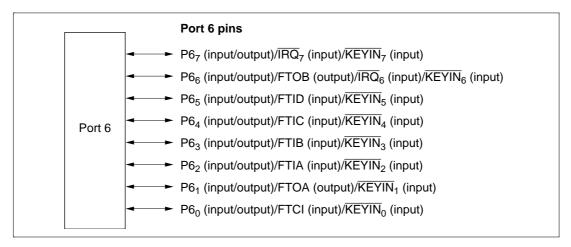

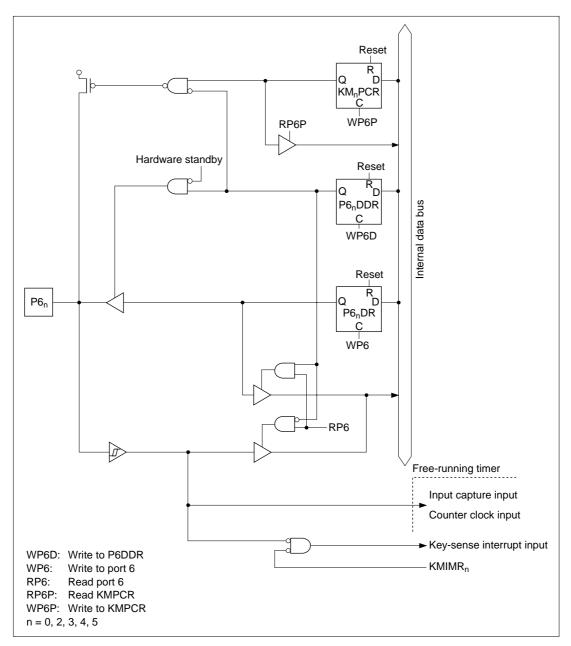

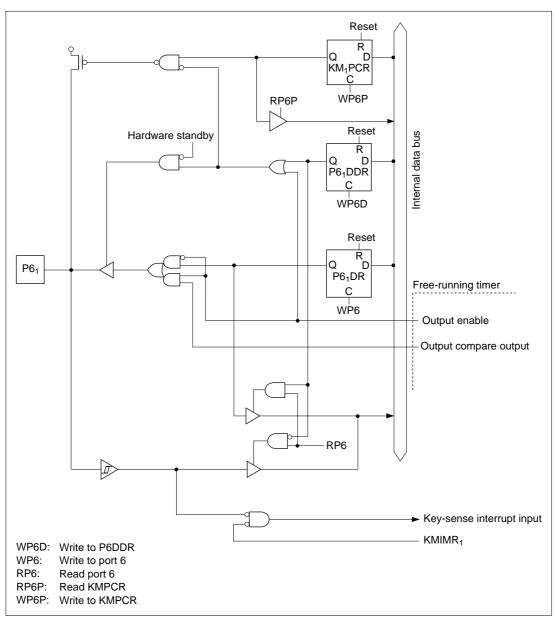

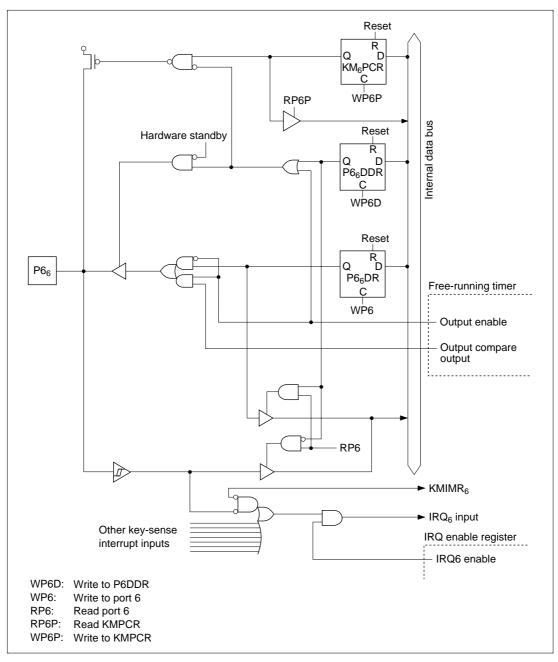

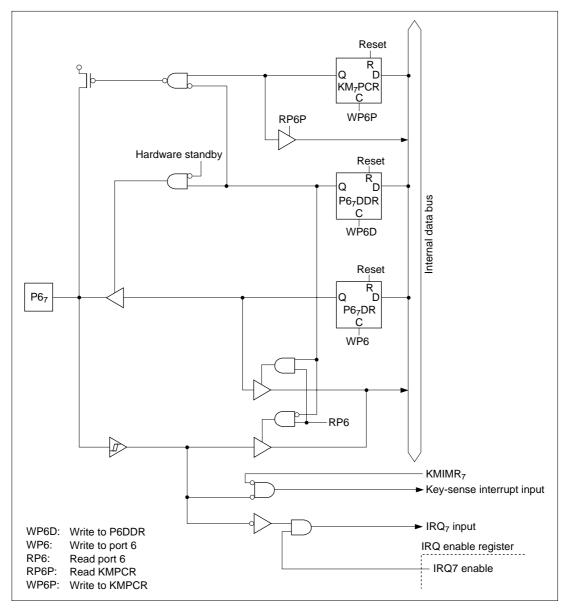

| 7.7   | Port 6. |                                         | 138 |

|       | 7.7.1   | Overview                                | 138 |

|       | 7.7.2   | Register Configuration and Descriptions | 138 |

|       | 7.7.3   | Pin Functions                           | 141 |

|       | 7.7.4   | Input Pull-Up Transistors               | 143 |

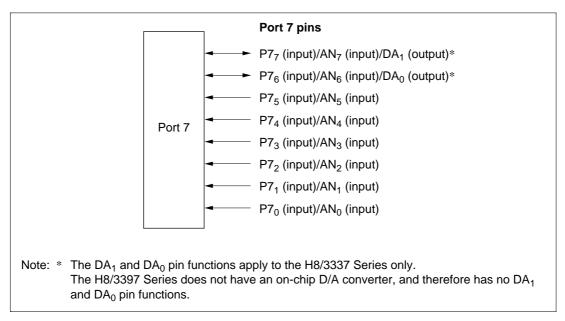

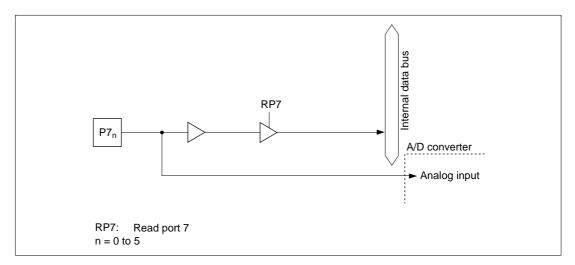

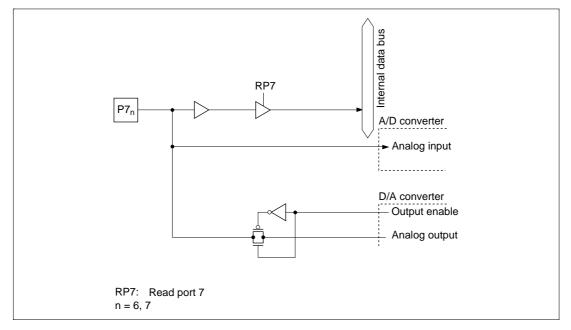

| 7.8   | Port 7. |                                         | 144 |

|       | 7.8.1   | Overview                                | 144 |

|       | 7.8.2   | Register Configuration and Descriptions | 144 |

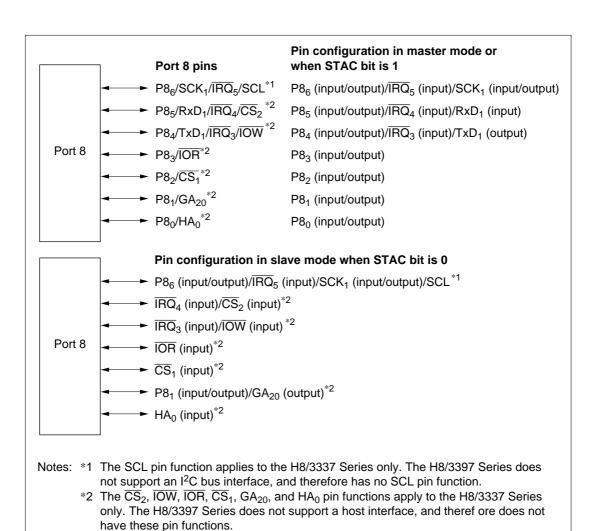

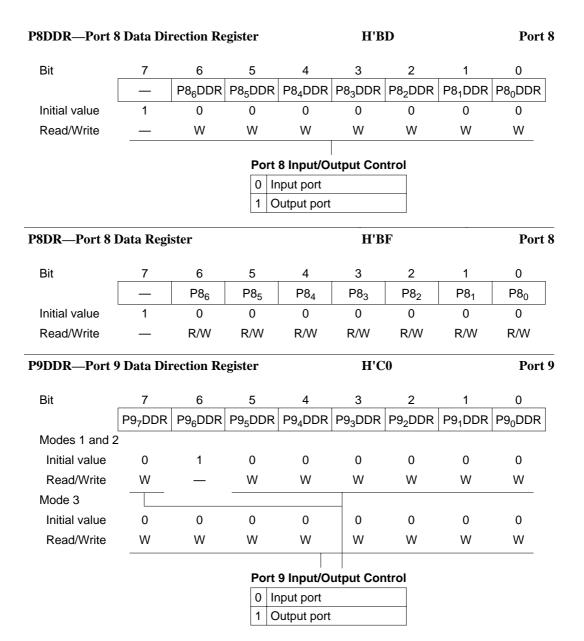

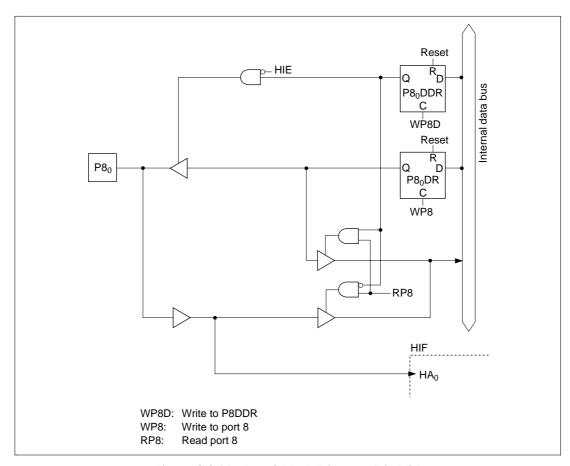

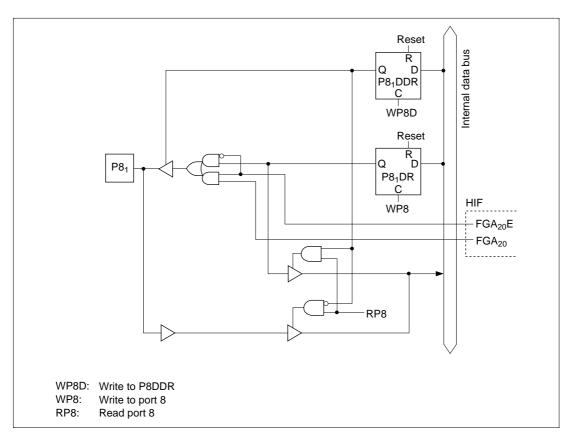

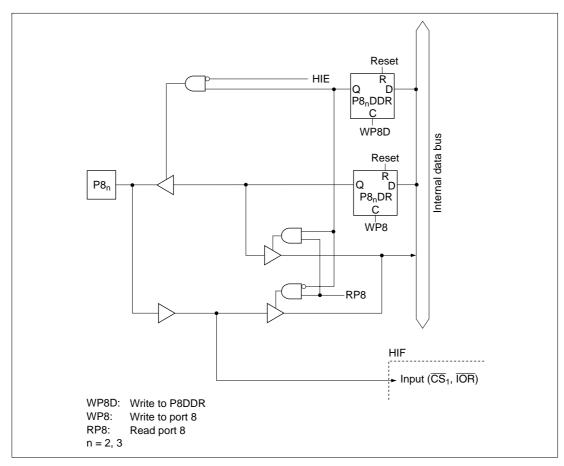

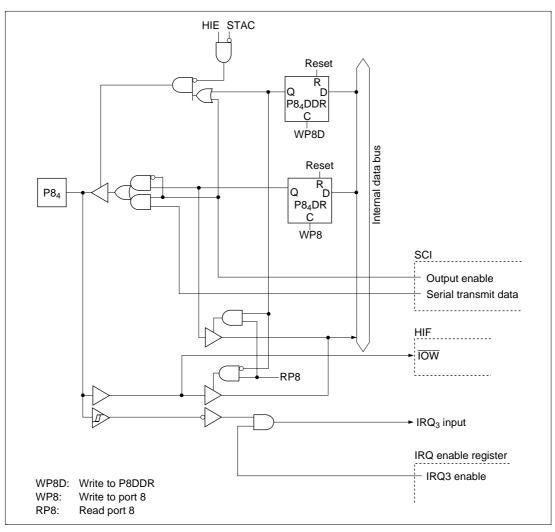

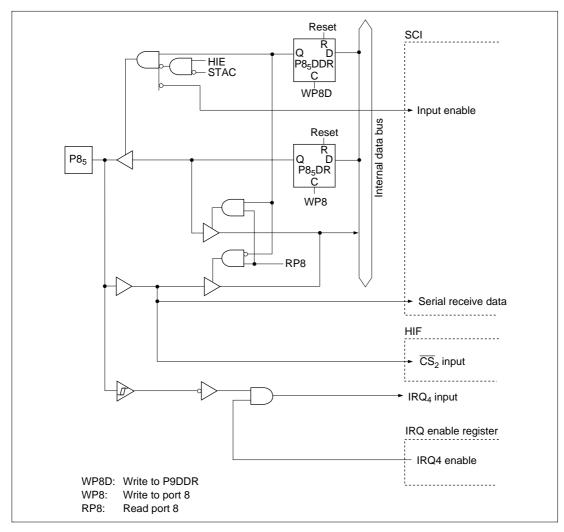

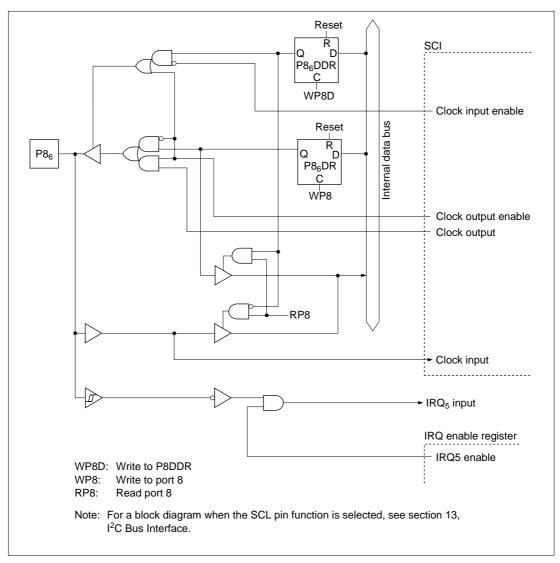

| 7.9   | Port 8. |                                         | 145 |

|       | 7.9.1   | Overview                                | 145 |

|       | 7.9.2   | Register Configuration and Descriptions | 146 |

|       | 7.9.3   | Pin Functions                           | 148 |

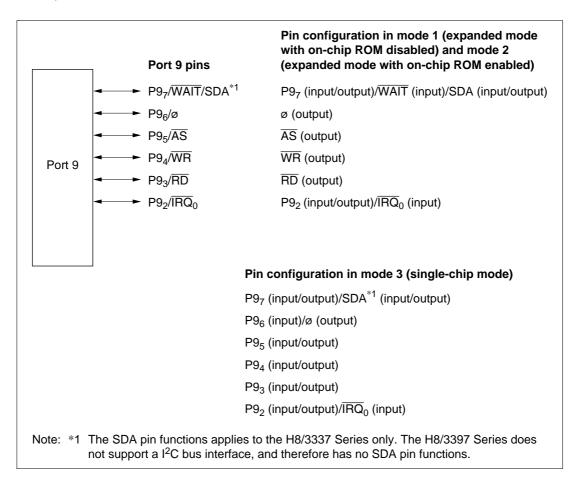

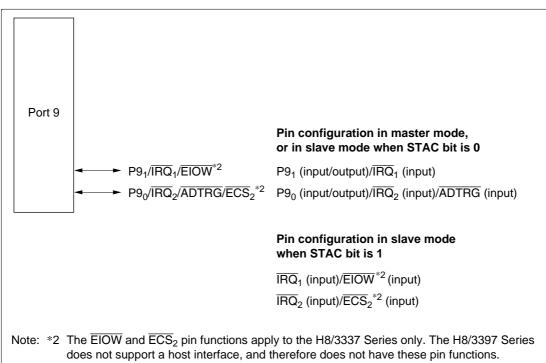

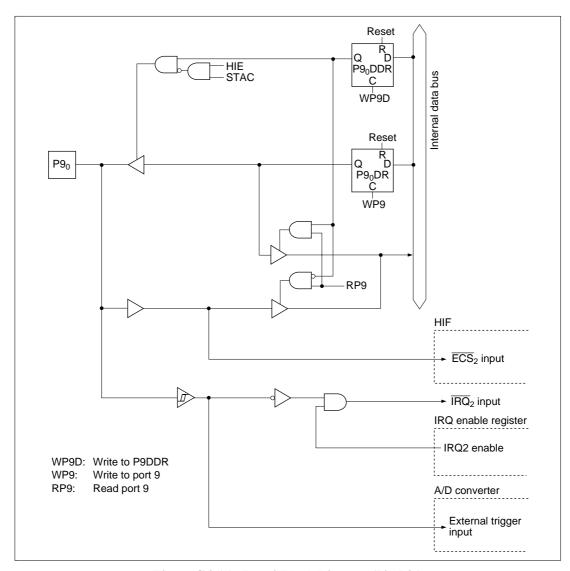

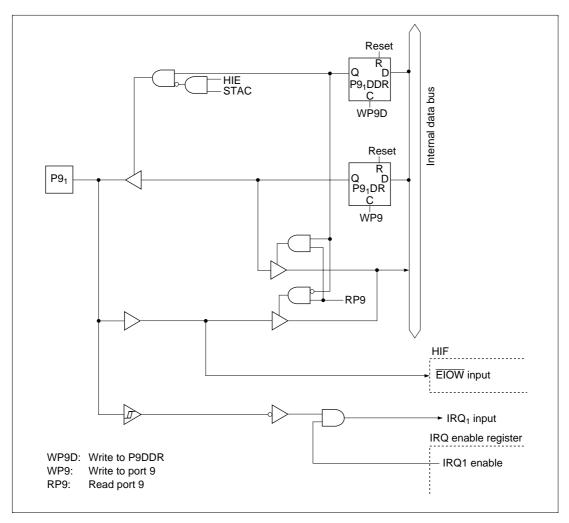

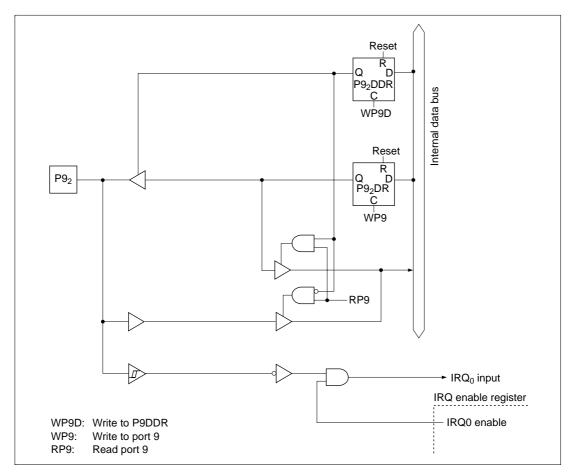

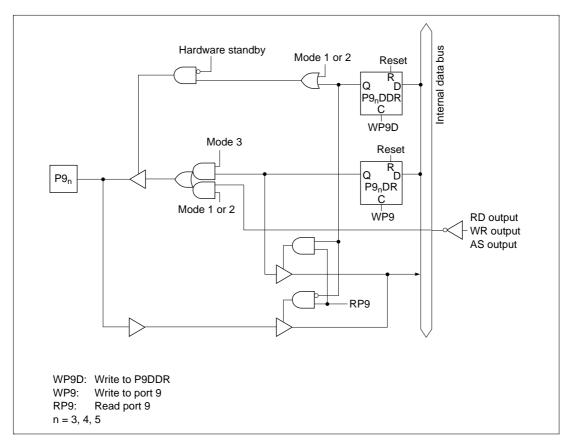

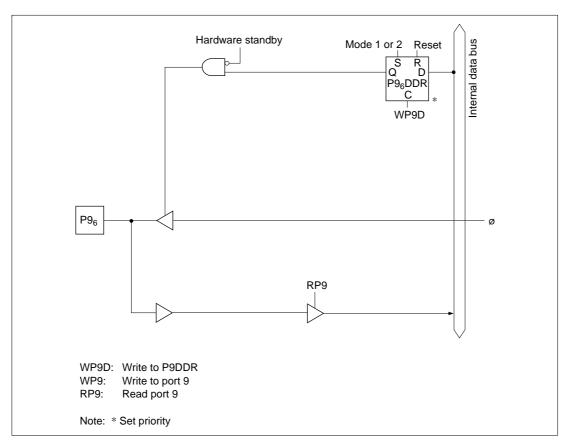

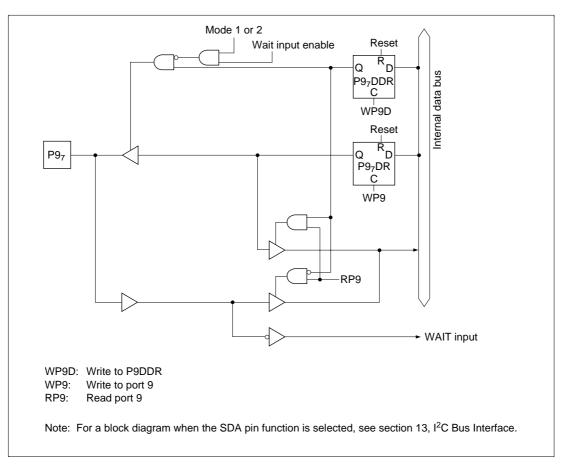

| 7.10  | Port 9. |                                         | 151 |

|       | 7.10.1  | Overview                                | 151 |

|       | 7.10.2  | Register Configuration and Descriptions | 152 |

|       | 7.10.3  | Pin Functions                           | 154 |

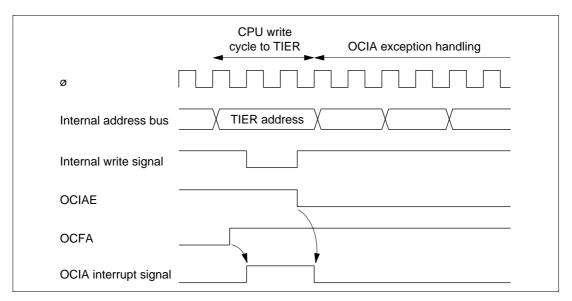

| Sect | ion 8   | 16-Bit Free-Running Timer                               | 157 |

|------|---------|---------------------------------------------------------|-----|

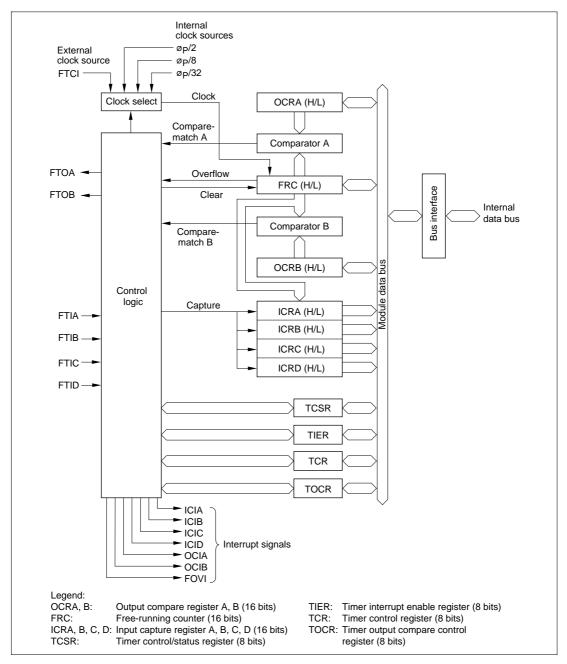

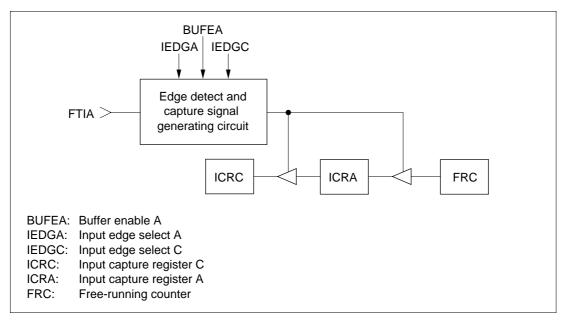

| 8.1  | Overv   | iew                                                     | 157 |

|      | 8.1.1   | Features                                                | 157 |

|      | 8.1.2   | Block Diagram                                           | 158 |

|      | 8.1.3   | Input and Output Pins                                   | 159 |

|      | 8.1.4   | Register Configuration                                  | 160 |

| 8.2  | Regist  | er Descriptions                                         | 161 |

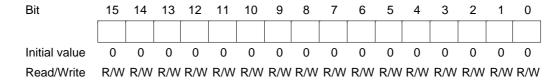

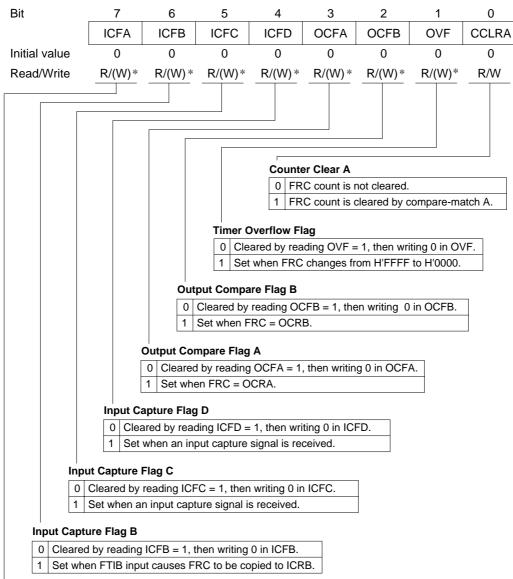

|      | 8.2.1   | Free-Running Counter (FRC)                              | 161 |

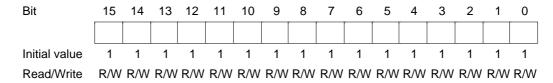

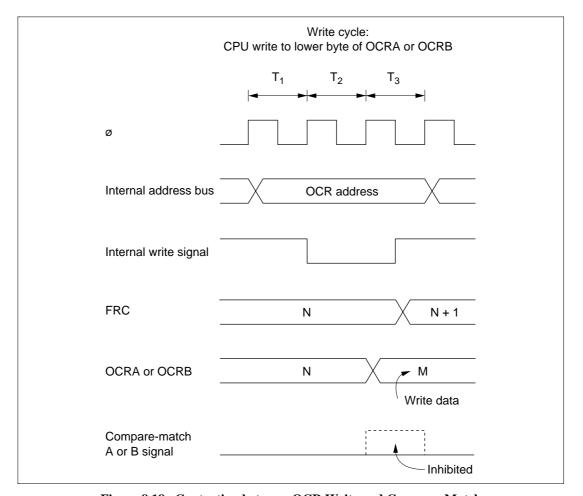

|      | 8.2.2   | Output Compare Registers A and B (OCRA and OCRB)        | 161 |

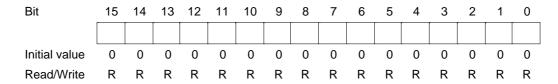

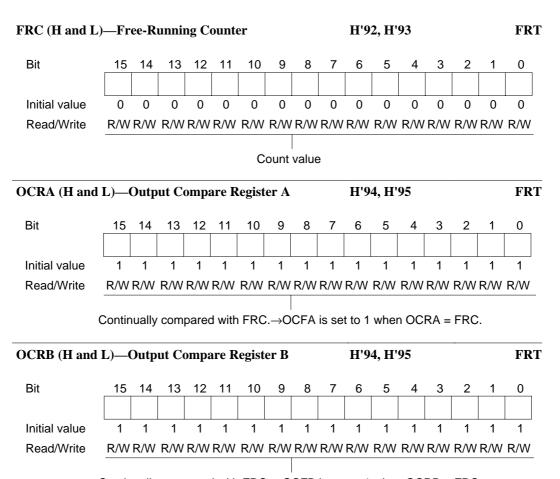

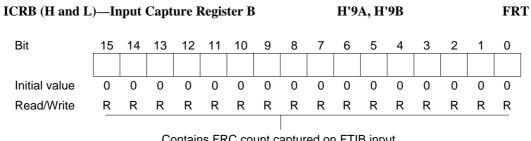

|      | 8.2.3   | Input Capture Registers A to D (ICRA to ICRD)           | 162 |

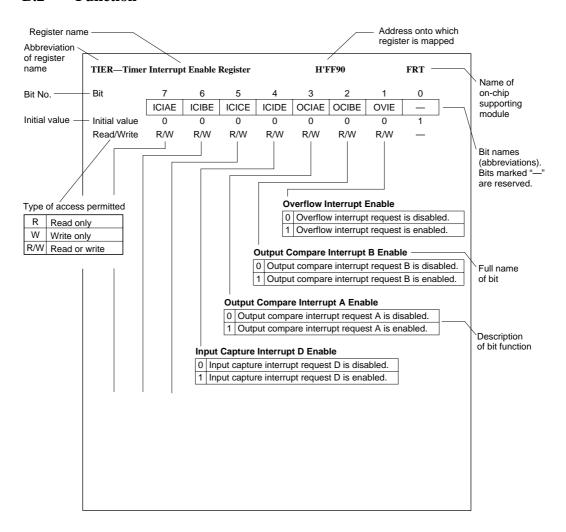

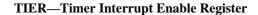

|      | 8.2.4   | Timer Interrupt Enable Register (TIER)                  | 164 |

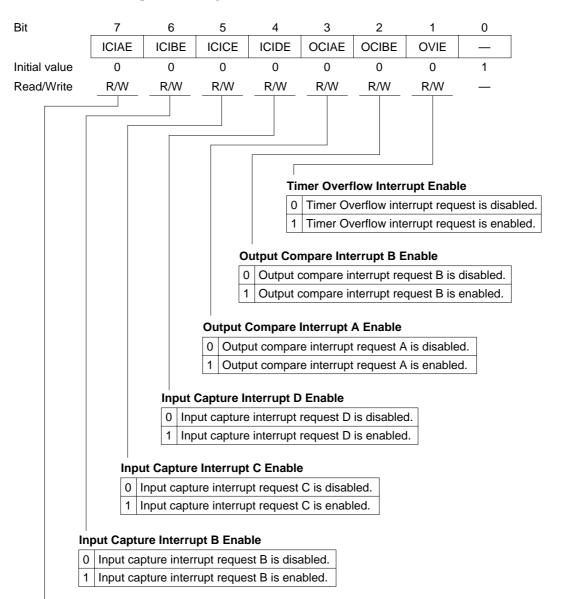

|      | 8.2.5   | Timer Control/Status Register (TCSR)                    | 166 |

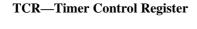

|      | 8.2.6   | Timer Control Register (TCR)                            | 168 |

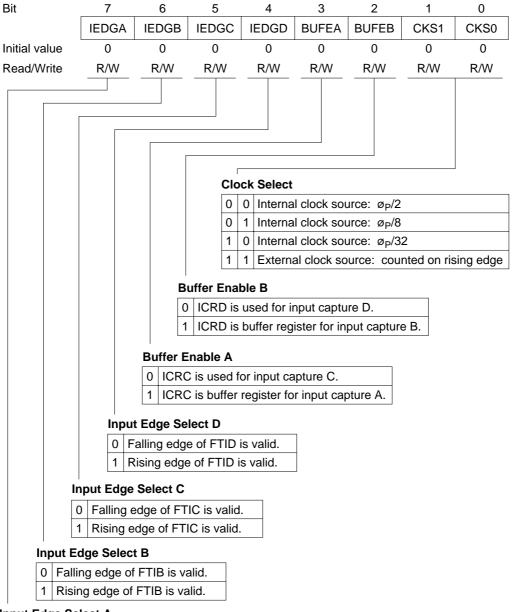

|      | 8.2.7   | Timer Output Compare Control Register (TOCR)            |     |

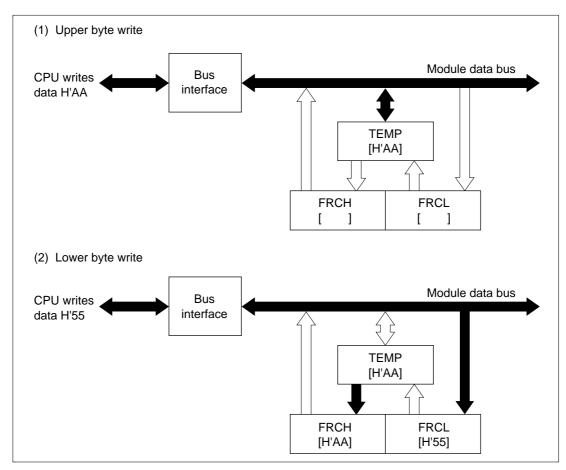

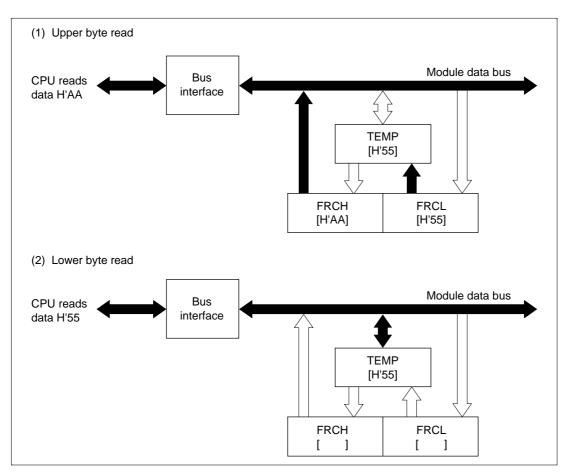

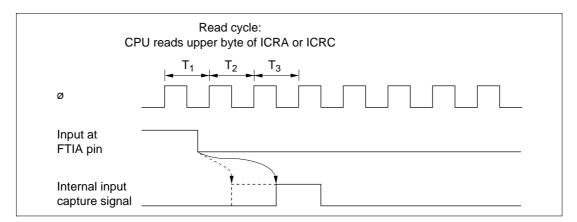

| 8.3  | CPU I   | nterface                                                | 172 |

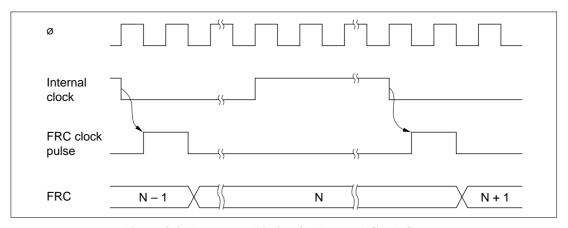

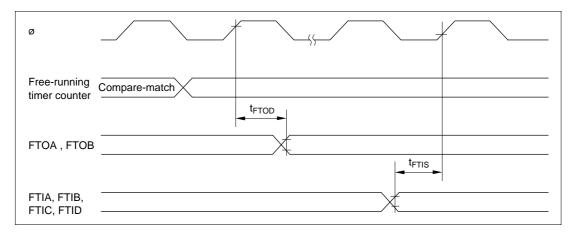

| 8.4  | Opera   | tion                                                    | 175 |

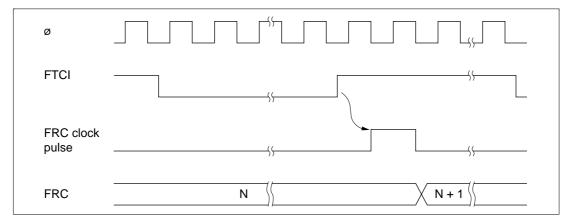

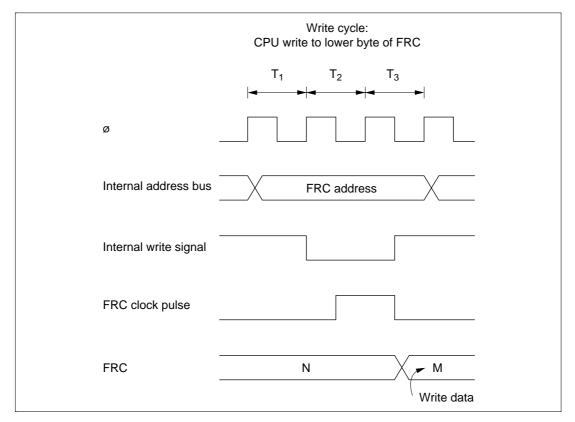

|      | 8.4.1   | FRC Increment Timing                                    | 175 |

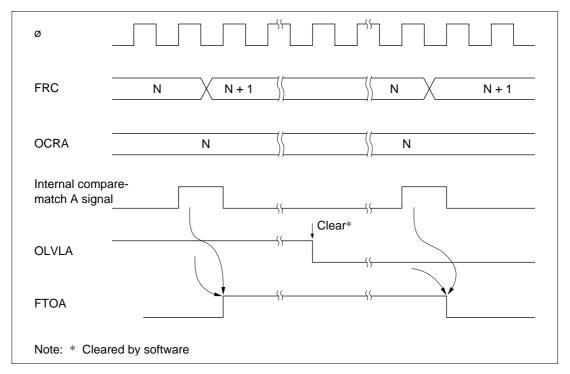

|      | 8.4.2   | Output Compare Timing                                   |     |

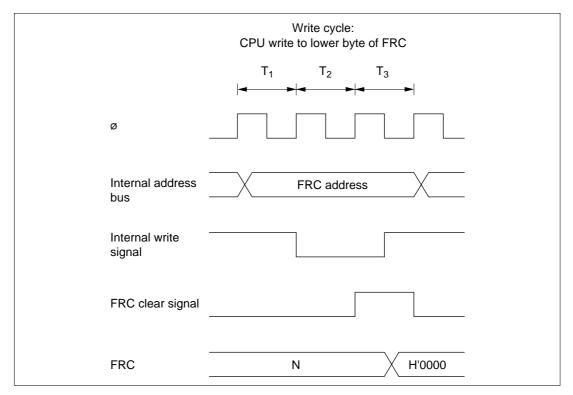

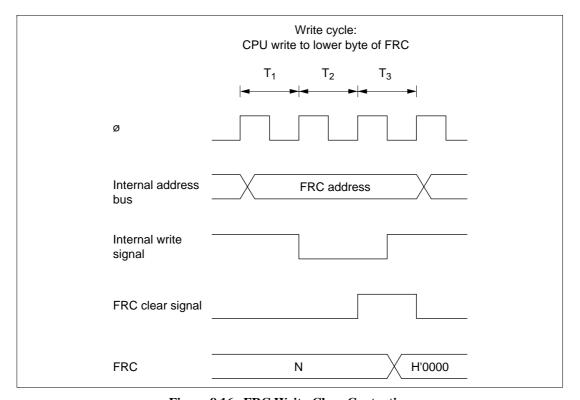

|      | 8.4.3   | FRC Clear Timing                                        |     |

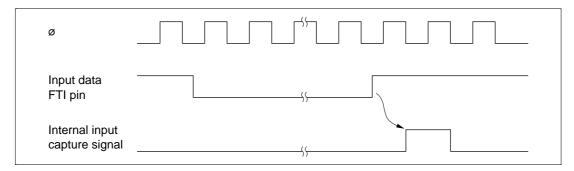

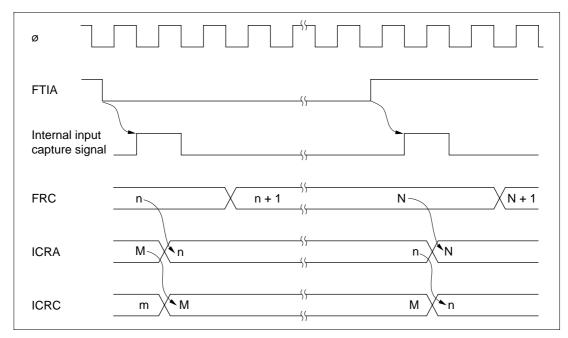

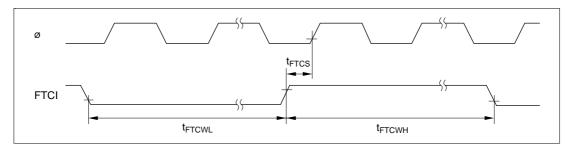

|      | 8.4.4   | Input Capture Timing                                    |     |

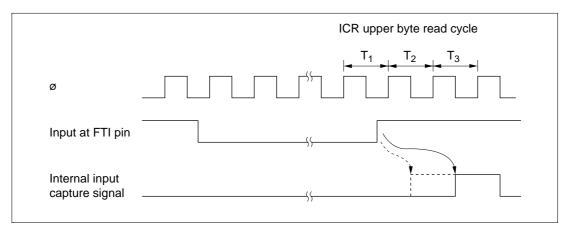

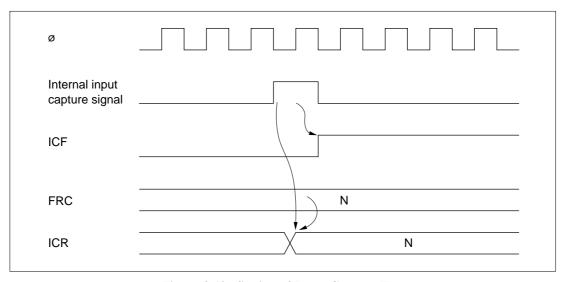

|      | 8.4.5   | Timing of Input Capture Flag (ICF) Setting              |     |

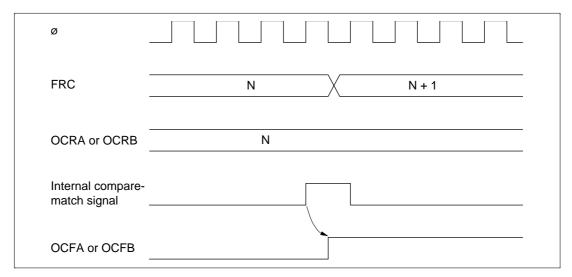

|      | 8.4.6   | Setting of Output Compare Flags A and B (OCFA and OCFB) |     |

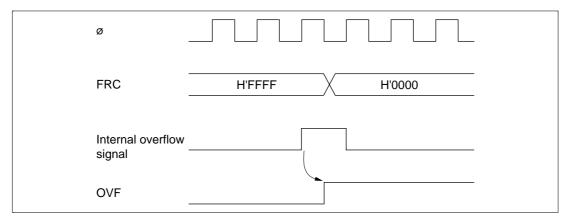

|      | 8.4.7   | Setting of Timer Overflow Flag (OVF)                    |     |

| 8.5  | Interru | ipts                                                    |     |

| 8.6  |         | e Application                                           |     |

| 8.7  | Applic  | cation Notes                                            | 185 |

|      |         |                                                         |     |

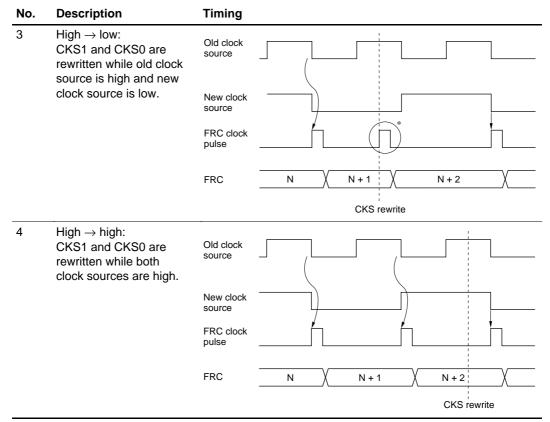

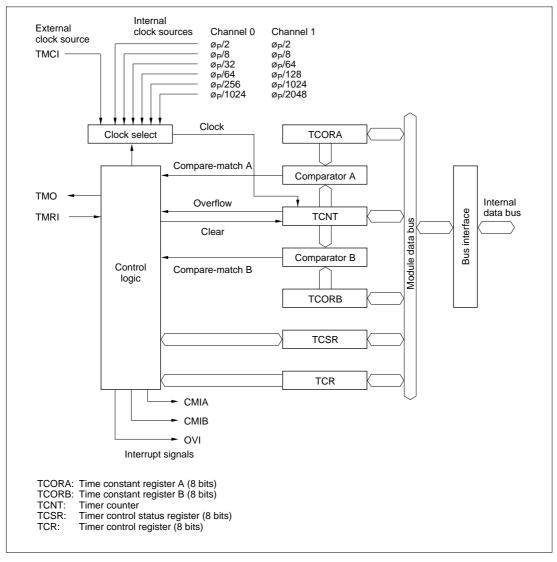

| Sect | ion 9   | 8-Bit Timers                                            | 191 |

| 9.1  | Overv   | iew                                                     | 191 |

|      | 9.1.1   | Features                                                | 191 |

|      | 9.1.2   | Block Diagram                                           | 192 |

|      | 9.1.3   | Input and Output Pins                                   | 193 |

|      | 9.1.4   | Register Configuration                                  | 193 |

| 9.2  | Regist  | er Descriptions                                         | 194 |

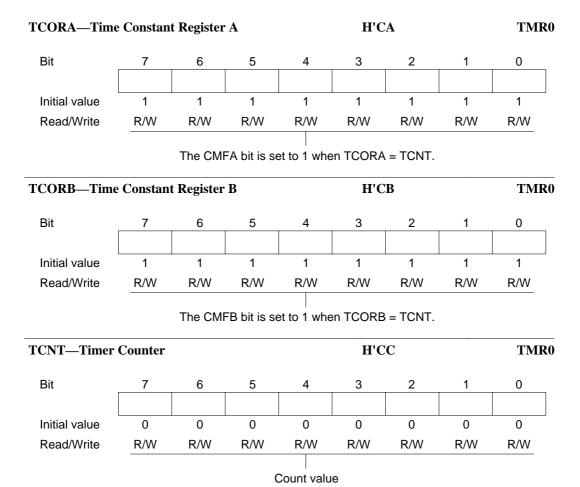

|      | 9.2.1   | Timer Counter (TCNT)                                    | 194 |

|      | 9.2.2   | Time Constant Registers A and B (TCORA and TCORB)       | 194 |

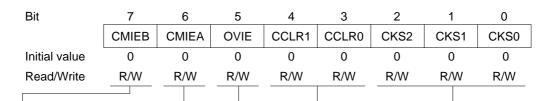

|      | 9.2.3   | Timer Control Register (TCR)                            |     |

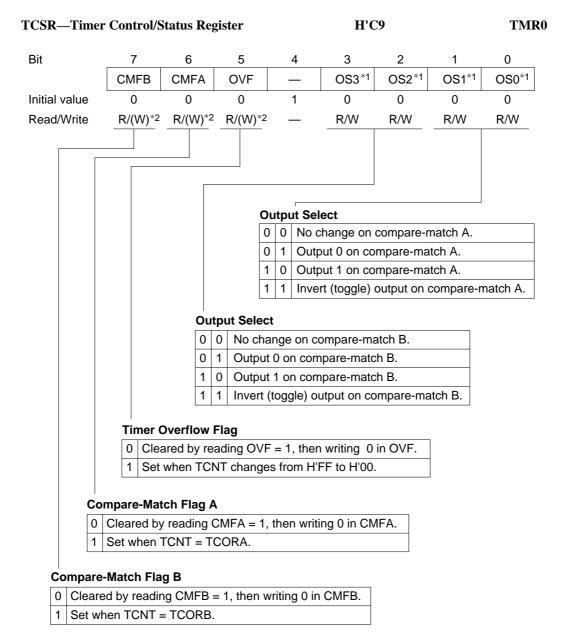

|      | 9.2.4   | Timer Control/Status Register (TCSR)                    | 198 |

|      | 9.2.5   | Serial/Timer Control Register (STCR)                    |     |

| 9.3  | Opera   | tion                                                    |     |

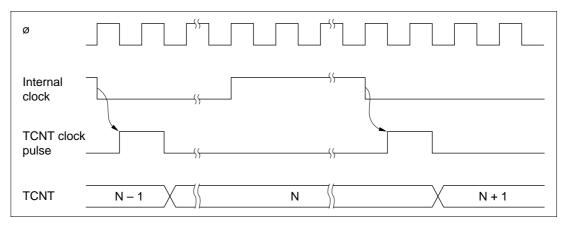

|      | 9.3.1   | TCNT Increment Timing                                   |     |

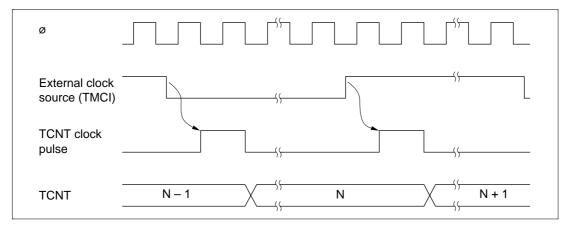

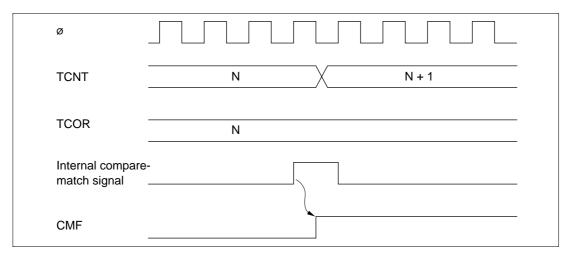

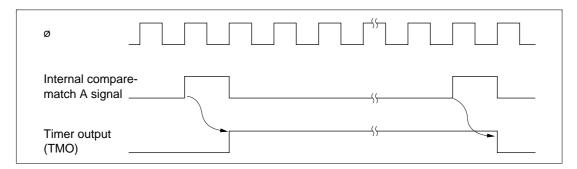

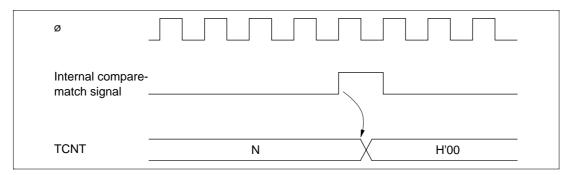

|      | 9.3.2   | Compare-Match Timing                                    |     |

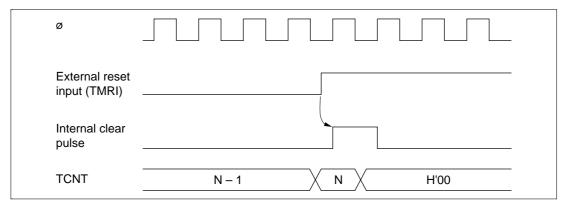

|      | 9.3.3   | External Reset of TCNT                                  | 205 |

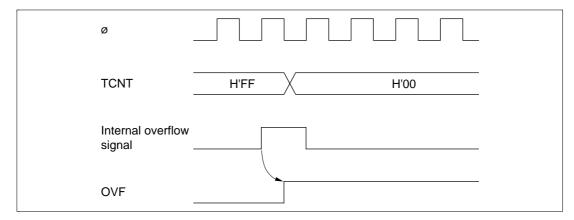

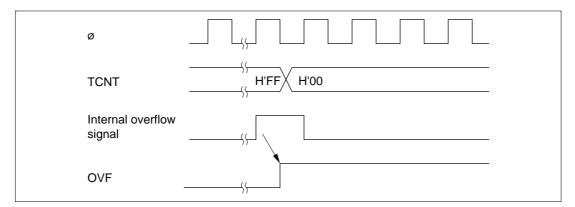

|       | 9.3.4    | Setting of Overflow Flag (OVF)                         | 205 |

|-------|----------|--------------------------------------------------------|-----|

| 9.4   | Interruj | pts                                                    | 206 |

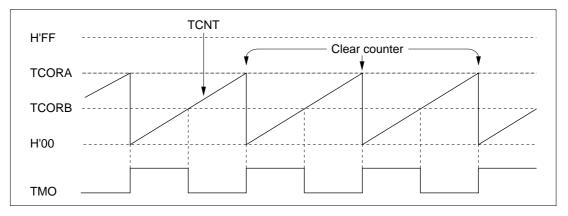

| 9.5   | Sample   | Application                                            | 206 |

| 9.6   | Applica  | ation Notes                                            | 207 |

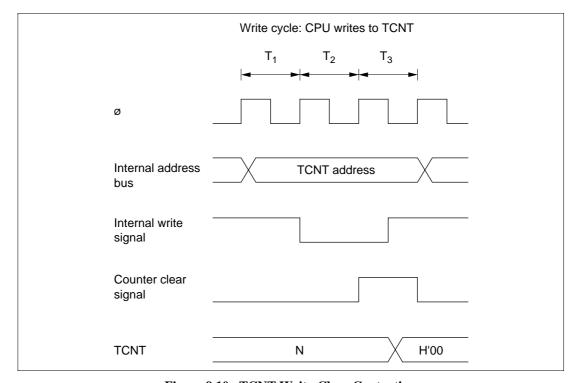

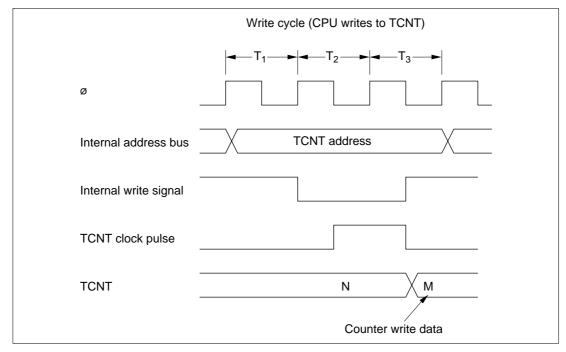

|       | 9.6.1    | Contention between TCNT Write and Clear                | 207 |

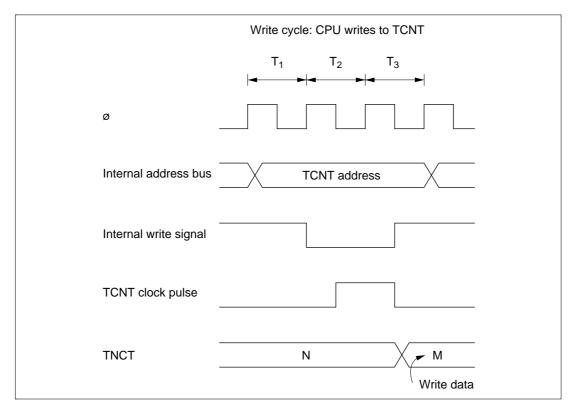

|       | 9.6.2    | Contention between TCNT Write and Increment            | 208 |

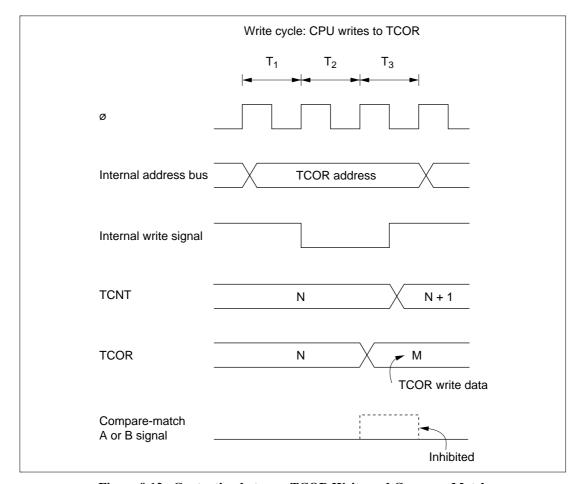

|       | 9.6.3    | Contention between TCOR Write and Compare-Match        | 209 |

|       | 9.6.4    | Contention between Compare-Match A and Compare-Match B | 210 |

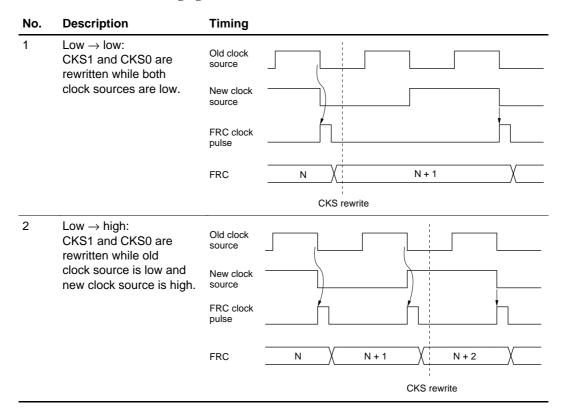

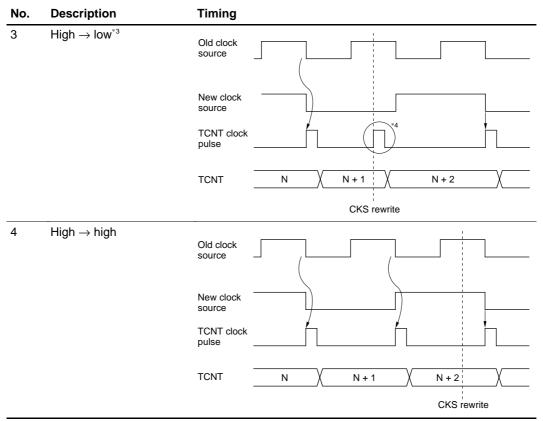

|       | 9.6.5    | Increment Caused by Changing of Internal Clock Source  | 210 |

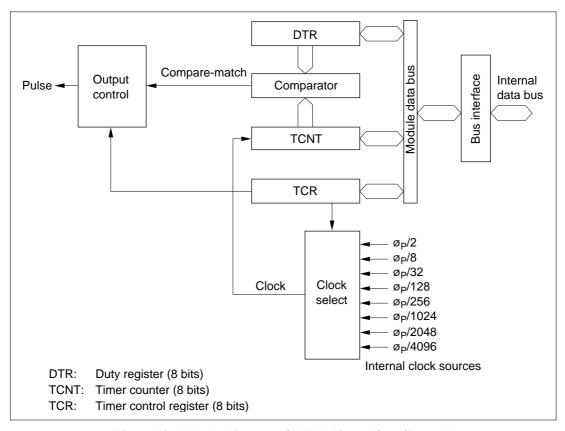

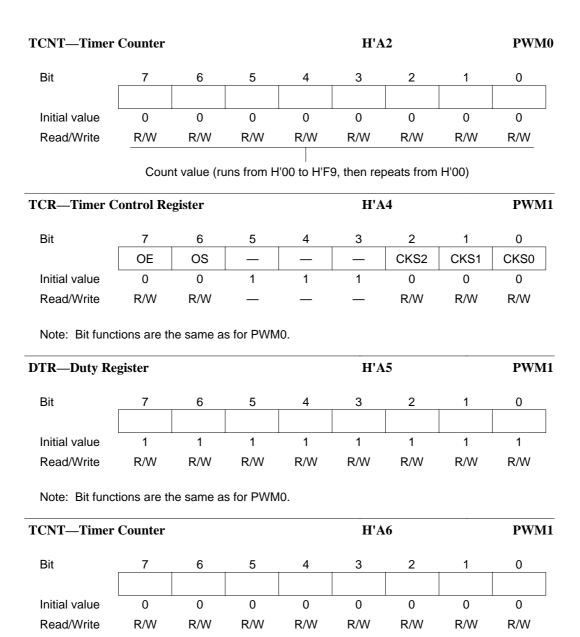

| Secti | ion 10   | PWM Timers                                             | 213 |

| 10.1  | Overvi   | ew                                                     | 213 |

|       | 10.1.1   | Features                                               | 213 |

|       | 10.1.2   | Block Diagram                                          | 214 |

|       | 10.1.3   | Input and Output Pins                                  | 214 |

|       | 10.1.4   | Register Configuration                                 | 215 |

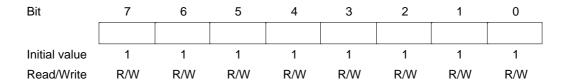

| 10.2  | Registe  | er Descriptions                                        | 215 |

|       | 10.2.1   | Timer Counter (TCNT)                                   | 215 |

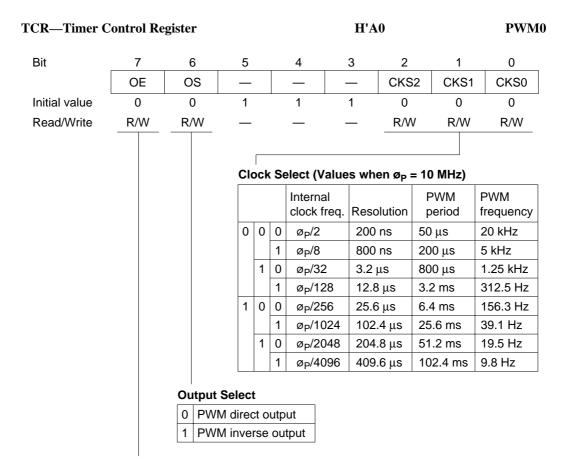

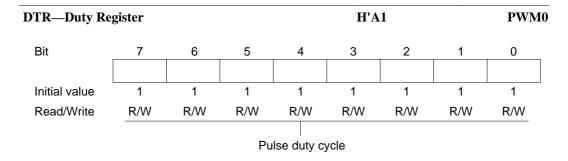

|       | 10.2.2   | Duty Register (DTR)                                    | 216 |

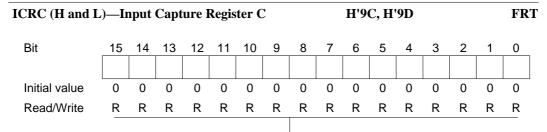

|       |          | Timer Control Register (TCR)                           |     |

| 10.3  |          | on                                                     |     |

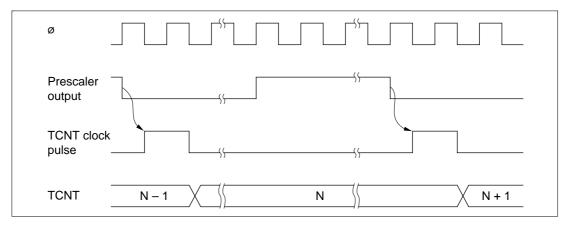

|       | 10.3.1   | Timer Incrementation.                                  | 219 |

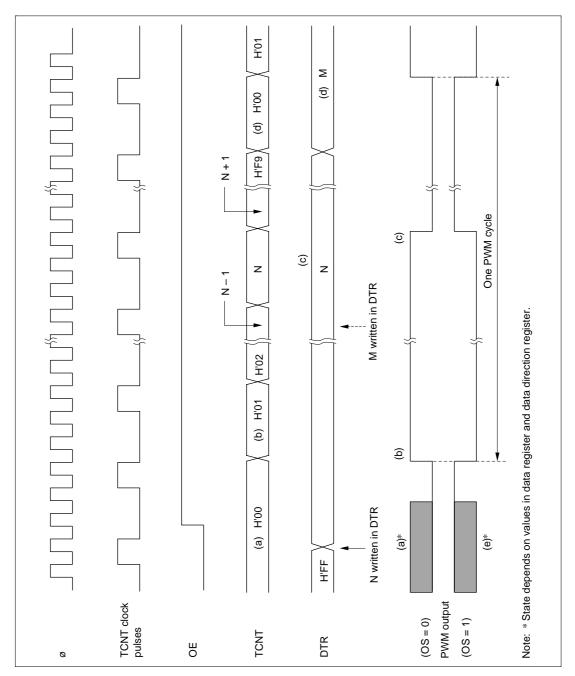

|       | 10.3.2   | PWM Operation                                          | 220 |

| 10.4  | Applica  | ation Notes                                            | 221 |

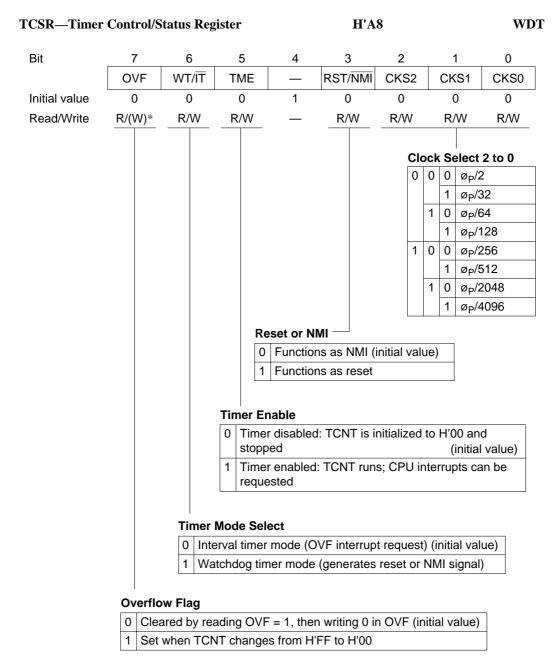

| Sect  | ion 11   | Watchdog Timer                                         | 223 |

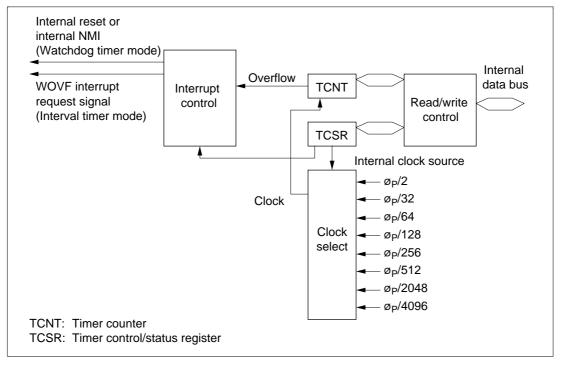

| 11.1  |          | ew                                                     |     |

|       | 11.1.1   | Features                                               | 223 |

|       |          | Block Diagram                                          |     |

|       |          | Register Configuration.                                |     |

| 11.2  | Registe  | er Descriptions                                        | 225 |

|       | _        | Timer Counter (TCNT)                                   |     |

|       | 11.2.2   | Timer Control/Status Register (TCSR)                   | 225 |

|       |          | System Control Register (SYSCR)                        |     |

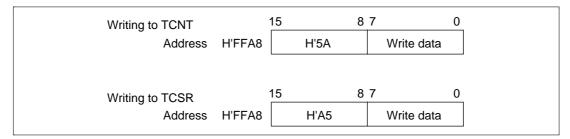

|       | 11.2.4   | Register Access                                        | 228 |

| 11.3  | Operati  | on                                                     | 229 |

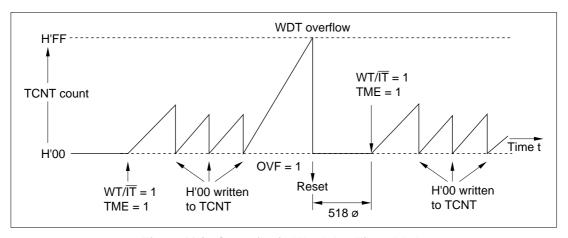

|       | _        | Watchdog Timer Mode                                    |     |

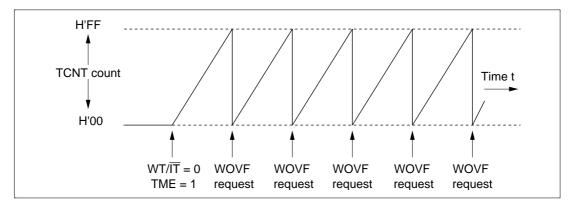

|       |          | Interval Timer Mode                                    |     |

|       | 11.3.3   | Setting the Overflow Flag                              | 230 |

| 11.4  |          | ation Notes                                            |     |

|       |          | Contention between TCNT Write and Increment            |     |

|       | 11.4.2   | Changing the Clock Select Bits (CKS2 to CKS0)          |     |

|       | 11.4.3   | Recovery from Software Standby Mode                    |     |

|       |          | •                                                      |     |

|      | 11.4.4  | Switching between Watchdog Timer Mode and Interval Timer Mode | . 232 |

|------|---------|---------------------------------------------------------------|-------|

|      | 11.4.5  | Detection of Program Runaway                                  | . 232 |

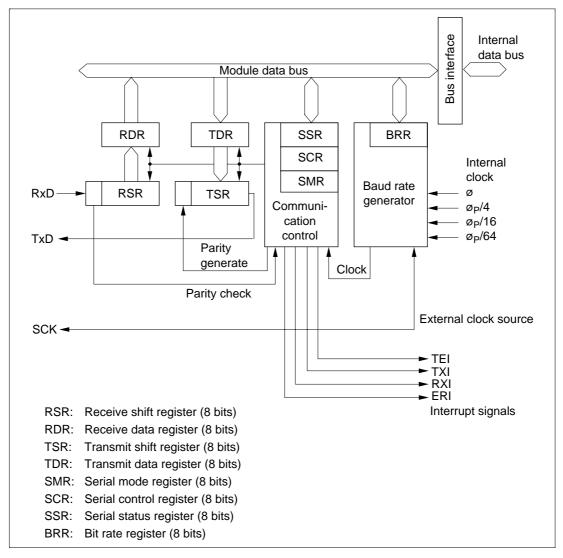

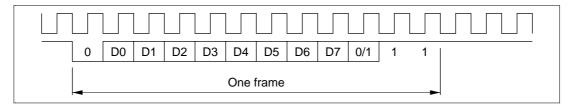

| Sect | ion 12  | Serial Communication Interface                                | . 233 |

| 12.1 | Overvi  | ew                                                            | . 233 |

|      | 12.1.1  | Features                                                      | . 233 |

|      | 12.1.2  | Block Diagram                                                 | . 234 |

|      |         | Input and Output Pins                                         |       |

|      |         | Register Configuration                                        |       |

| 12.2 |         | er Descriptions                                               |       |

|      | 12.2.1  | Receive Shift Register (RSR)                                  | . 237 |

|      |         | Receive Data Register (RDR)                                   |       |

|      |         | Transmit Shift Register (TSR)                                 |       |

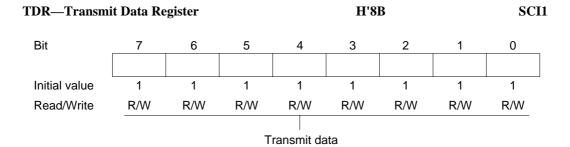

|      |         | Transmit Data Register (TDR)                                  |       |

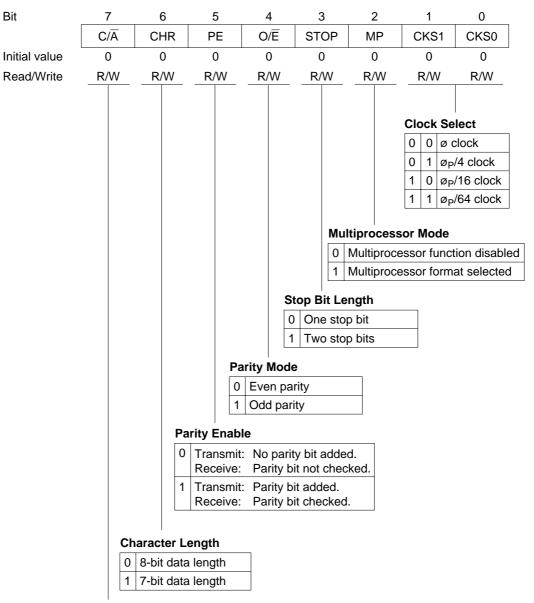

|      | 12.2.5  | Serial Mode Register (SMR)                                    | . 238 |

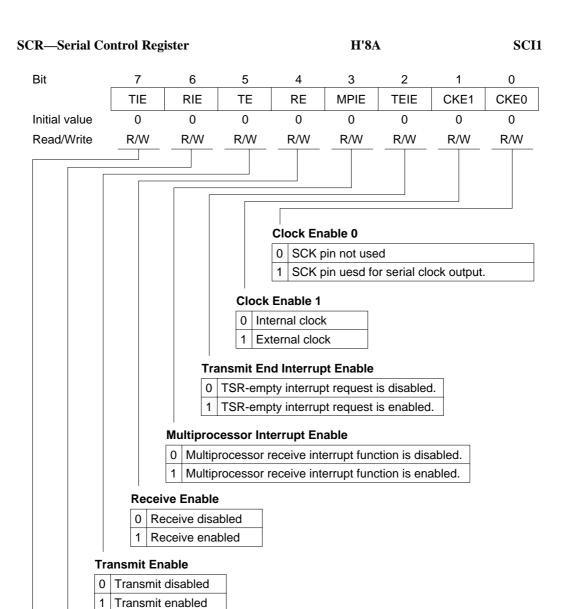

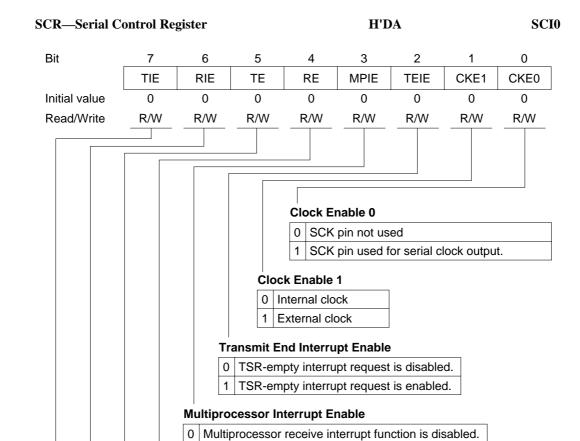

|      | 12.2.6  | Serial Control Register (SCR)                                 | . 240 |

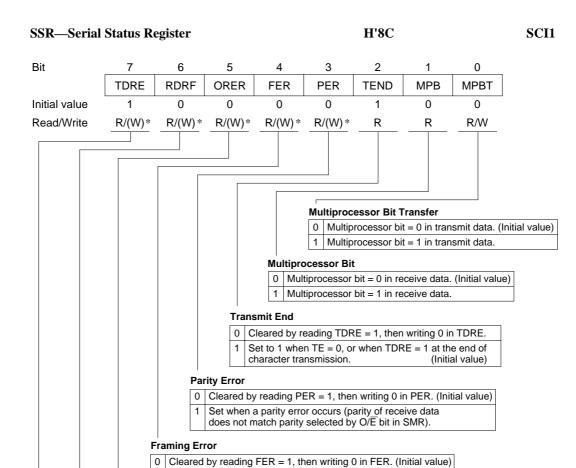

|      | 12.2.7  | Serial Status Register (SSR)                                  | . 243 |

|      | 12.2.8  | Bit Rate Register (BRR)                                       | . 246 |

|      |         | Serial/Timer Control Register (STCR)                          |       |

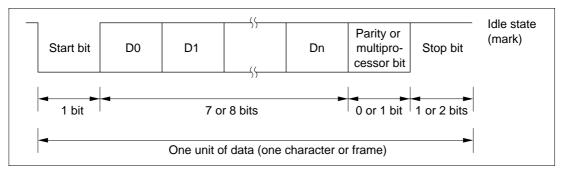

| 12.3 | Operat  | on                                                            | . 257 |

|      | 12.3.1  | Overview                                                      | . 257 |

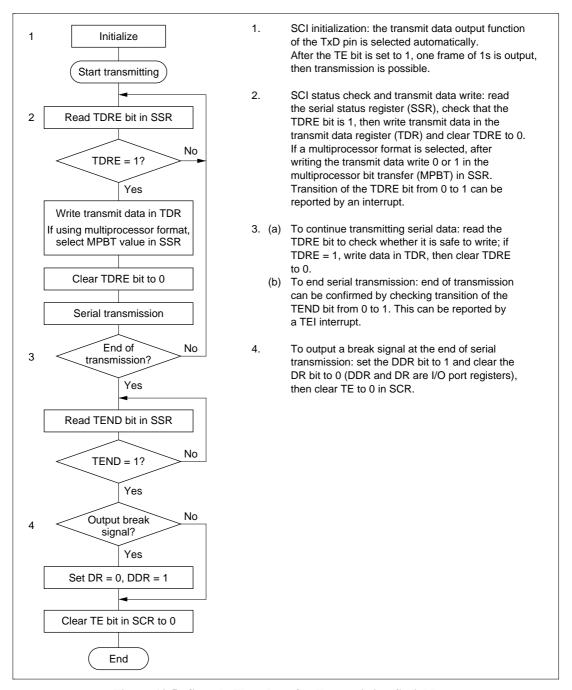

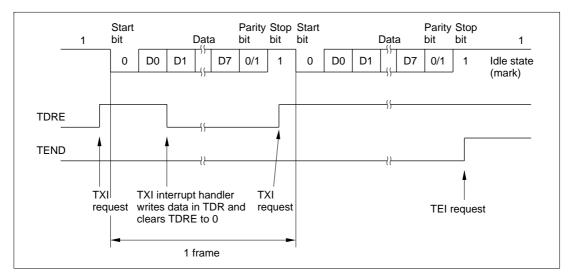

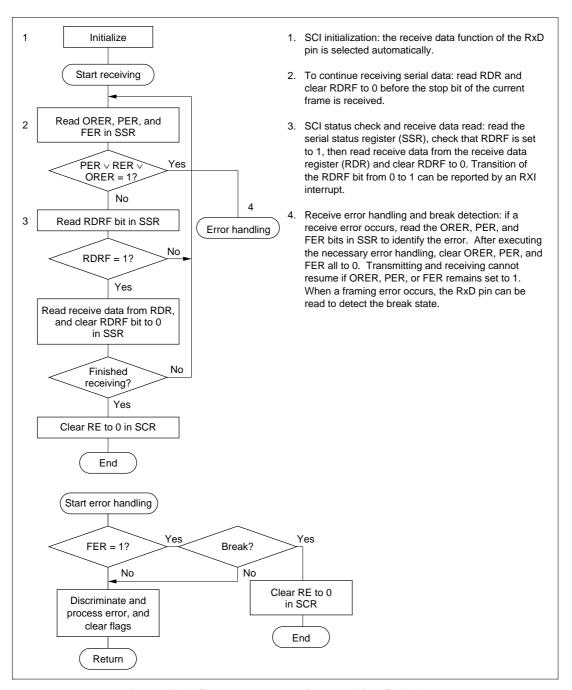

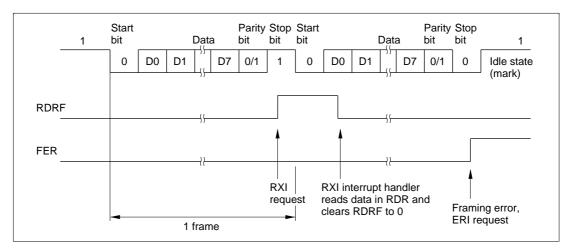

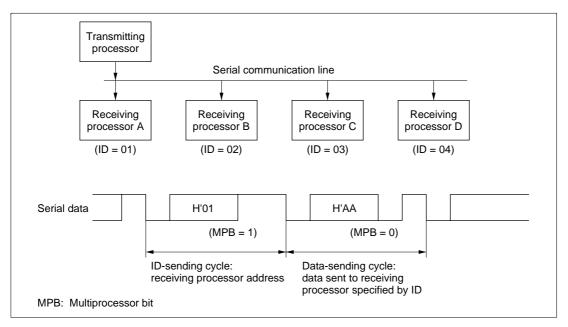

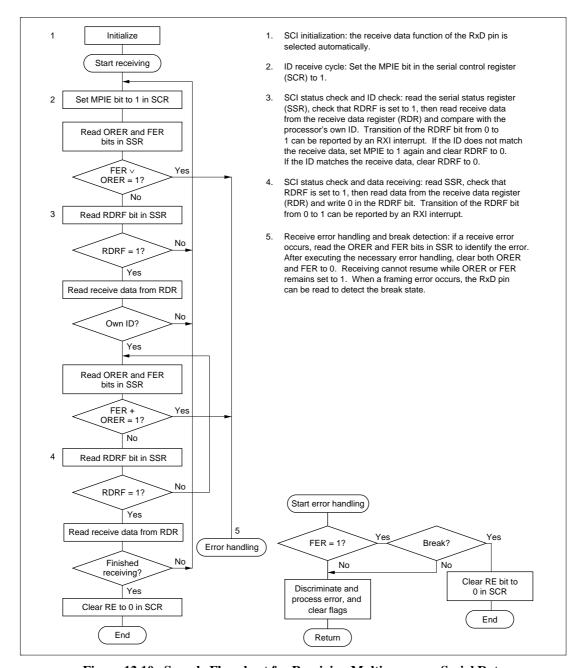

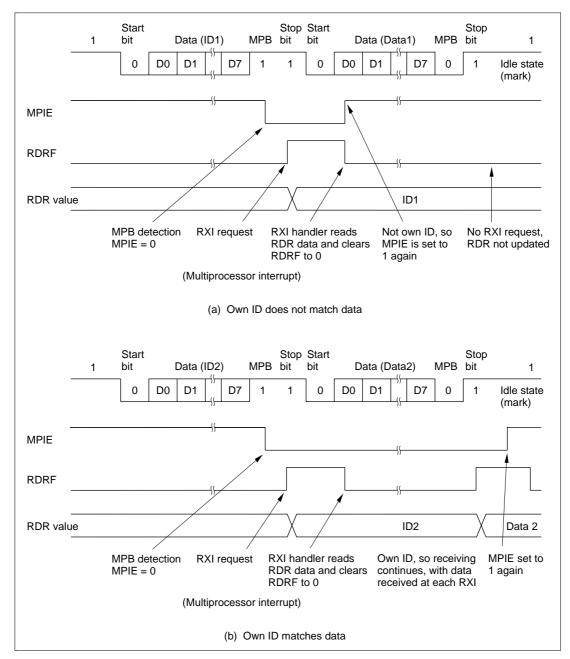

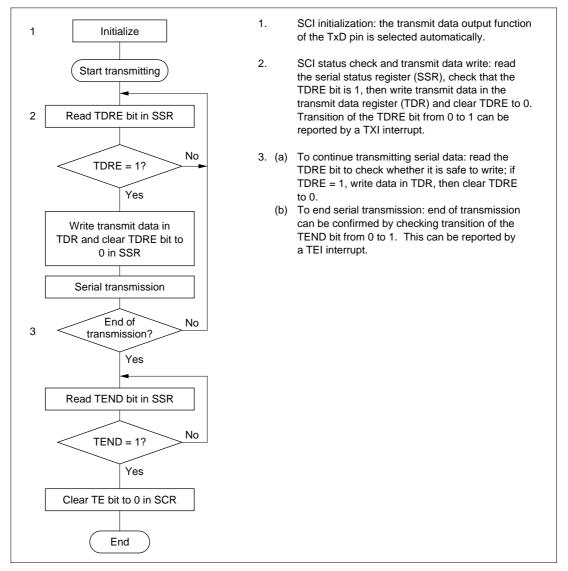

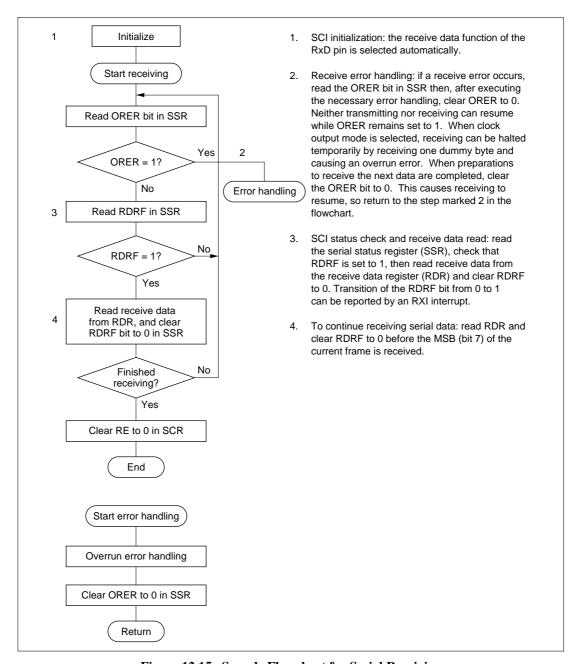

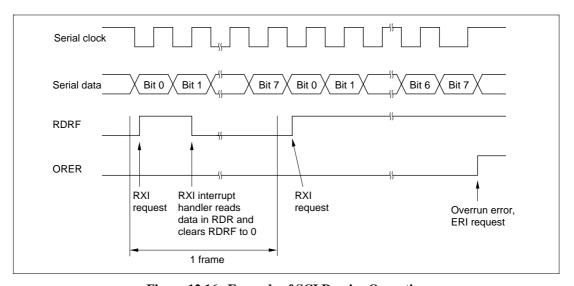

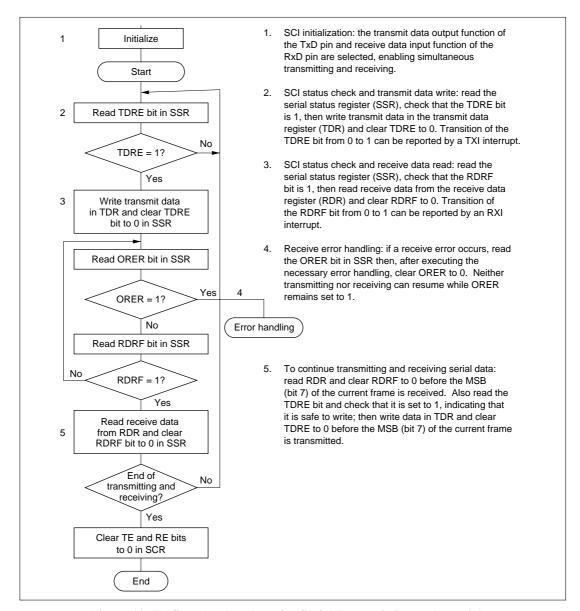

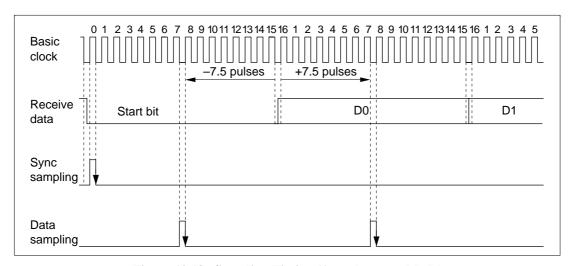

|      | 12.3.2  | Asynchronous Mode                                             | . 259 |

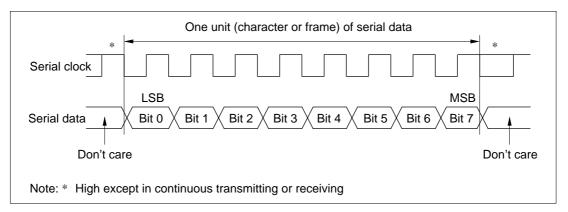

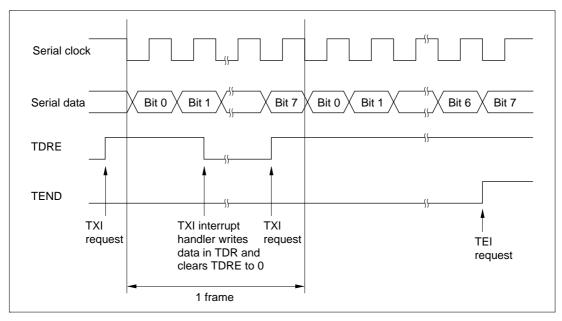

|      | 12.3.3  | Synchronous Mode                                              | . 272 |

| 12.4 | Interru | pts                                                           | . 278 |

| 12.5 | Applic  | ation Notes                                                   | . 278 |

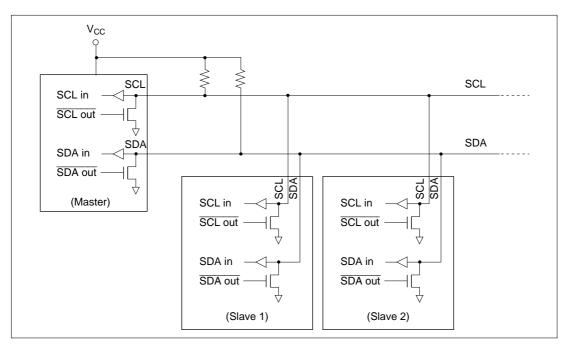

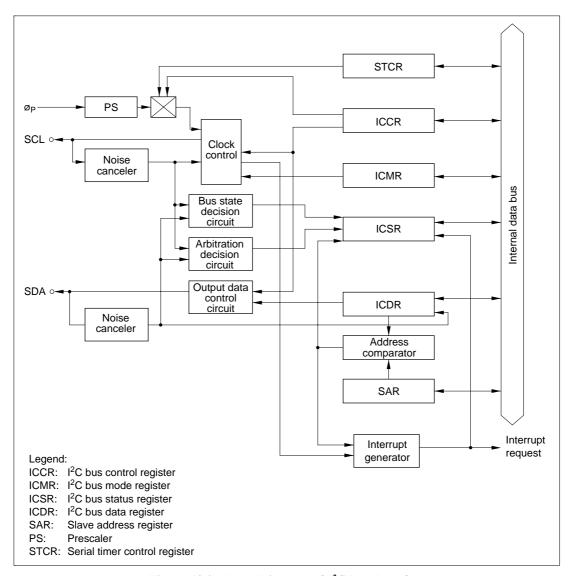

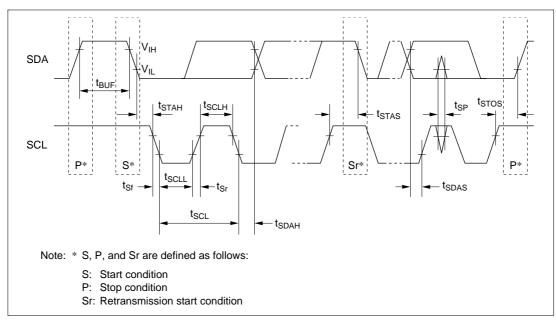

| Sect | ion 13  | I <sup>2</sup> C Bus Interface (H8/3337 Series Only) [Option] | . 281 |

| 13.1 |         | ew                                                            |       |

|      | 13.1.1  | Features                                                      | . 281 |

|      | 13.1.2  | Block Diagram                                                 | . 283 |

|      |         | Input/Output Pins                                             |       |

|      |         | Register Configuration                                        |       |

| 13.2 | Registe | er Descriptions                                               | . 285 |

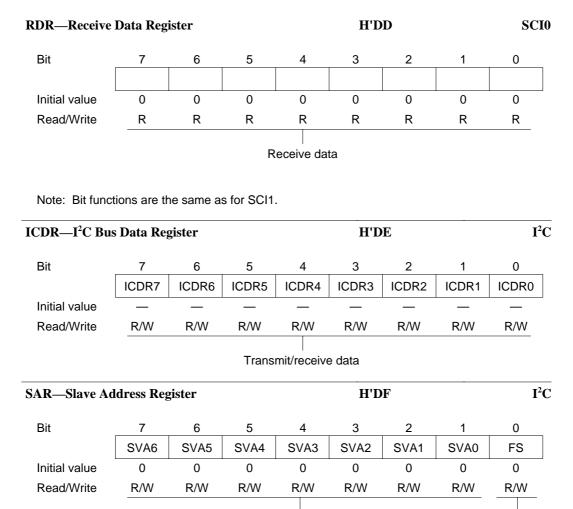

|      | 13.2.1  | I <sup>2</sup> C Bus Data Register (ICDR)                     | . 285 |

|      | 13.2.2  | Slave Address Register (SAR)                                  | . 285 |

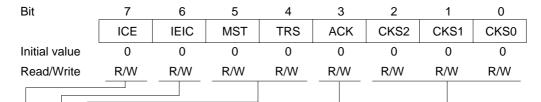

|      |         | I <sup>2</sup> C Bus Mode Register (ICMR)                     |       |

|      |         | I <sup>2</sup> C Bus Control Register (ICCR)                  |       |

|      |         | I <sup>2</sup> C Bus Status Register (ICSR)                   |       |

|      |         | Serial/Timer Control Register (STCR)                          |       |

| 13.3 |         | ion                                                           |       |

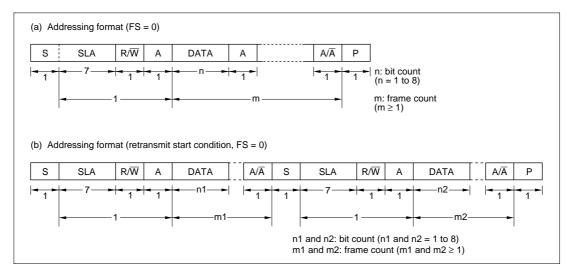

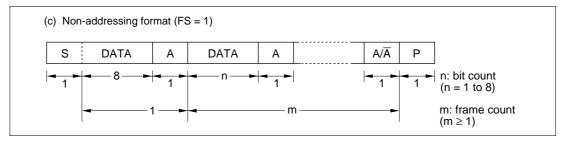

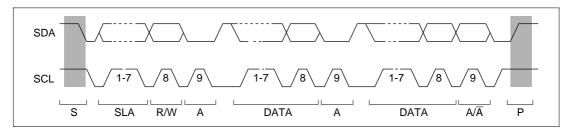

|      | 13.3.1  | I <sup>2</sup> C Bus Data Format                              | . 295 |

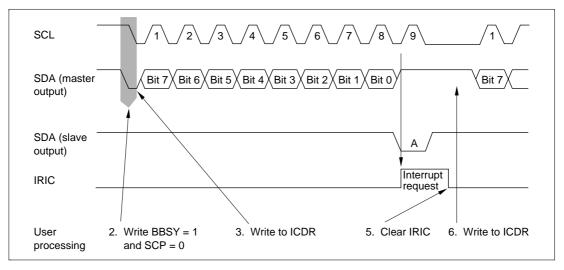

|      | 13.3.2  | Master Transmit Operation                                     | . 296 |

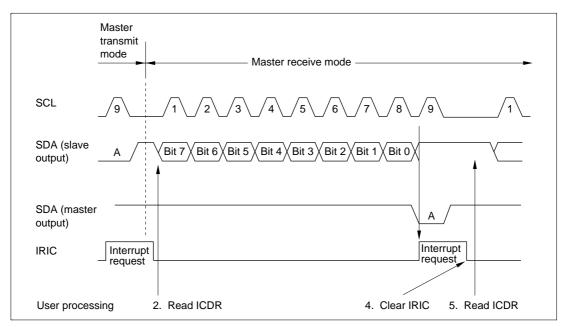

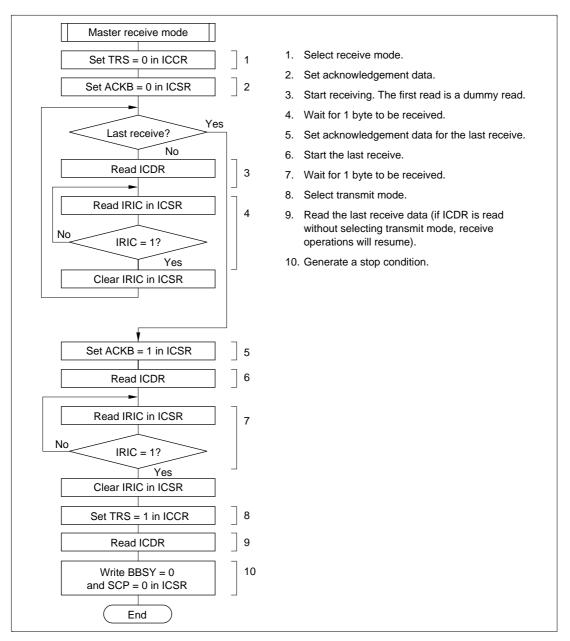

|      | 13.3.3  | Master Receive Operation                                      | . 298 |

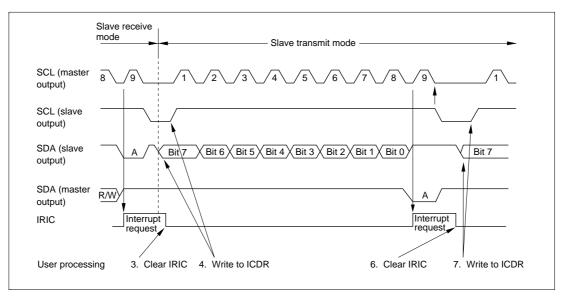

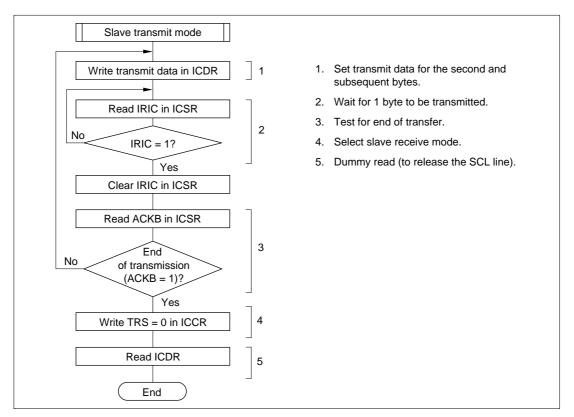

|       | 13.3.4   | Slave Transmit Operation                                        | 300 |

|-------|----------|-----------------------------------------------------------------|-----|

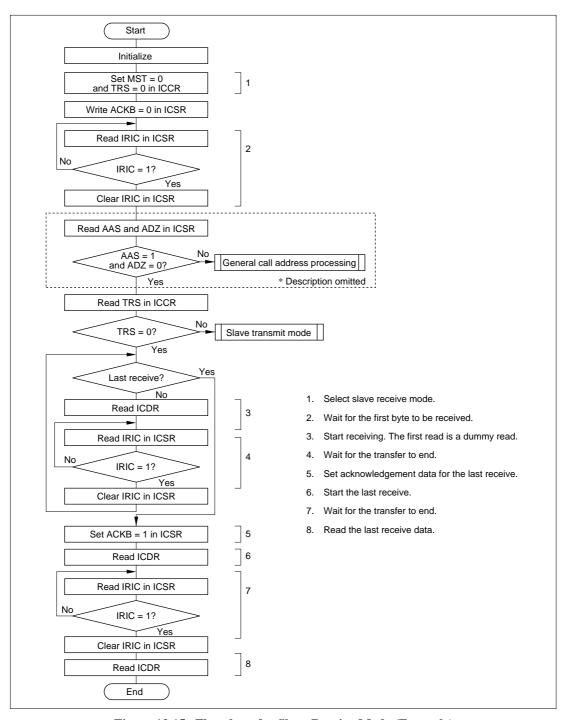

|       | 13.3.5   | Slave Receive Operation                                         | 302 |

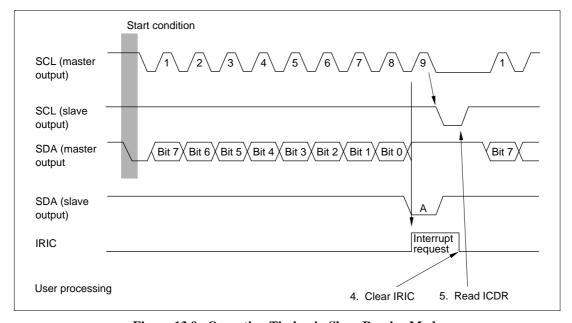

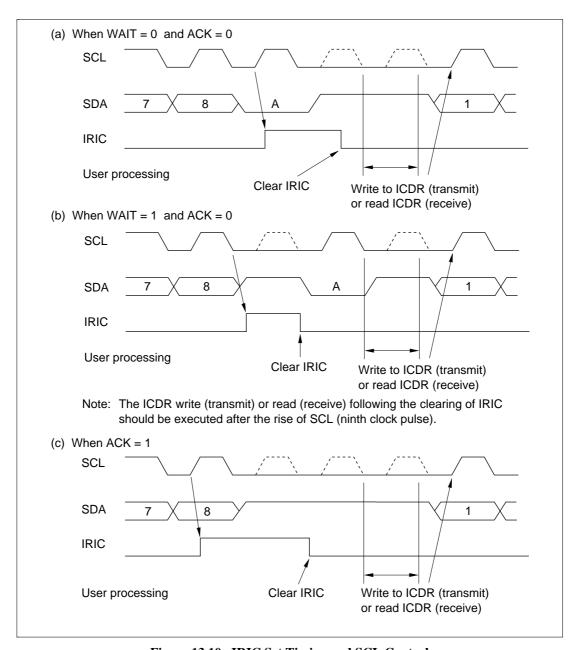

|       |          | IRIC Set Timing and SCL Control                                 |     |

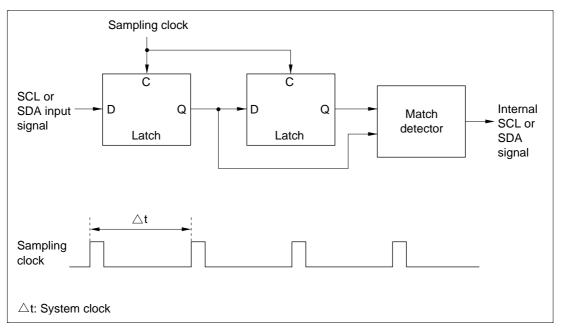

|       | 13.3.7   | Noise Canceler                                                  | 304 |

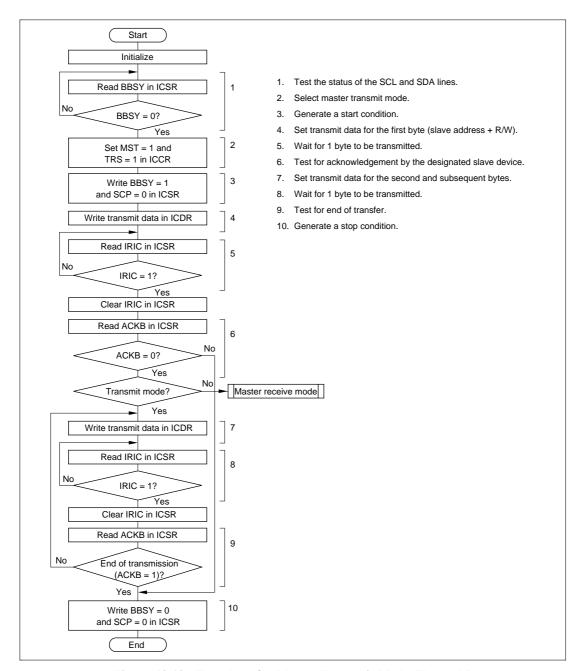

|       | 13.3.8   | Sample Flowcharts                                               | 305 |

| 13.4  | Applica  | ation Notes                                                     | 309 |

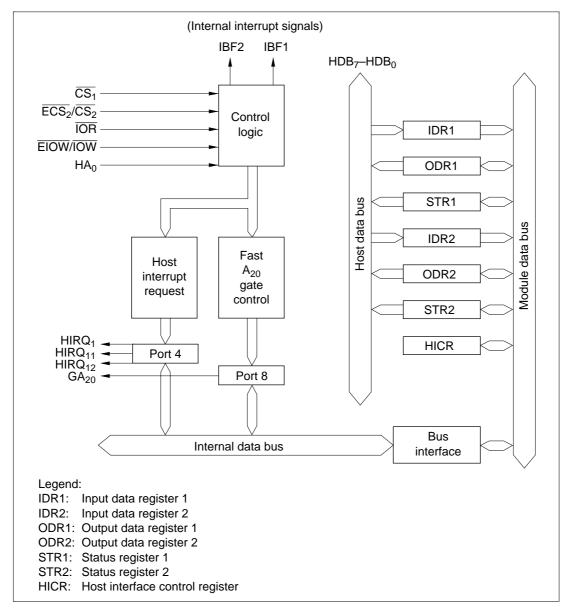

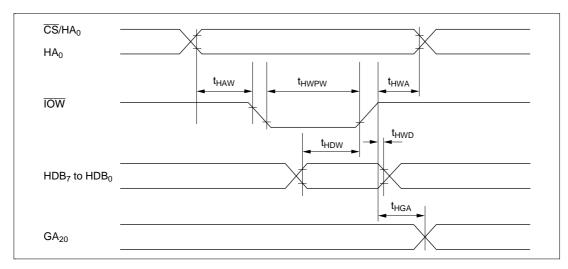

| Secti | ion 14   | Host Interface (H8/3337 Series Only)                            | 315 |

| 14.1  | Overvi   | ew                                                              | 315 |

|       | 14.1.1   | Block Diagram                                                   | 316 |

|       | 14.1.2   | Input and Output Pins                                           | 317 |

|       | 14.1.3   | Register Configuration.                                         | 318 |

| 14.2  | Registe  | er Descriptions                                                 | 319 |

|       | 14.2.1   | System Control Register (SYSCR)                                 | 319 |

|       | 14.2.2   | Host Interface Control Register (HICR)                          | 319 |

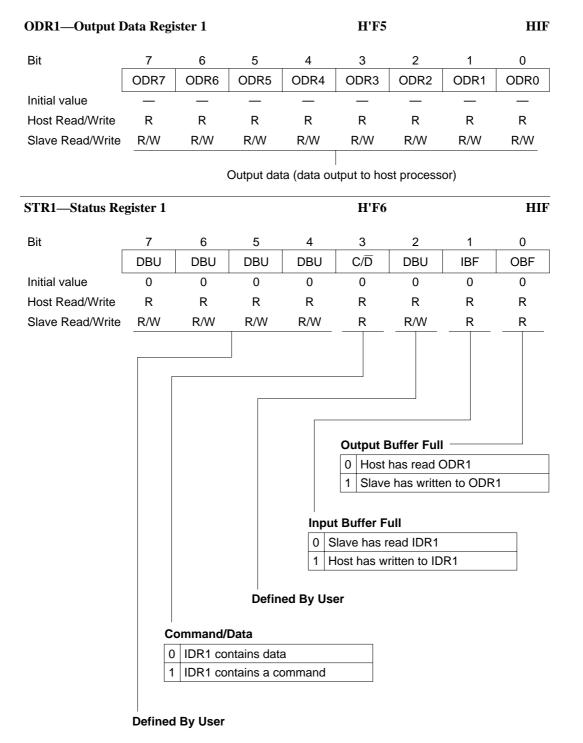

|       | 14.2.3   | Input Data Register 1 (IDR1)                                    | 320 |

|       | 14.2.4   | Output Data Register 1 (ODR1)                                   | 321 |

|       | 14.2.5   | Status Register 1 (STR1)                                        | 321 |

|       | 14.2.6   | Input Data Register 2 (IDR2)                                    | 322 |

|       | 14.2.7   | Output Data Register 2 (ODR2)                                   | 323 |

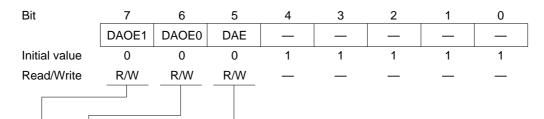

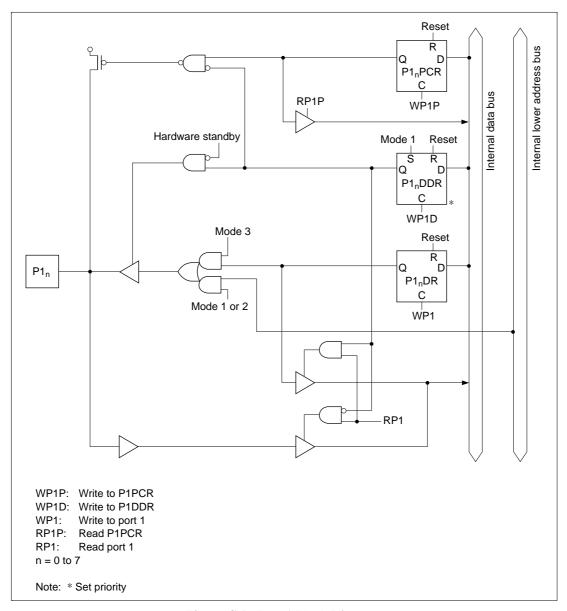

|       | 14.2.8   | Status Register 2 (STR2)                                        | 323 |

|       | 14.2.9   | Serial/Timer Control Register (STCR)                            | 325 |

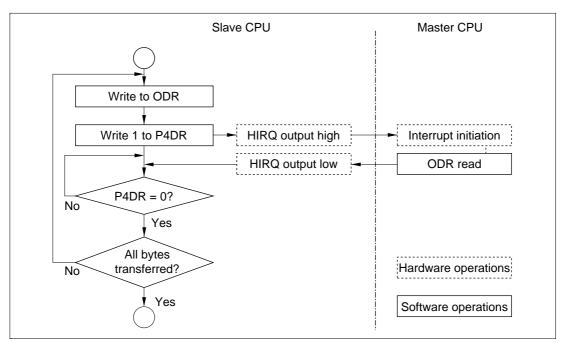

| 14.3  | Operati  | on                                                              | 326 |

|       | 14.3.1   | Host Interface Operation                                        | 326 |

|       | 14.3.2   | Control States                                                  | 326 |

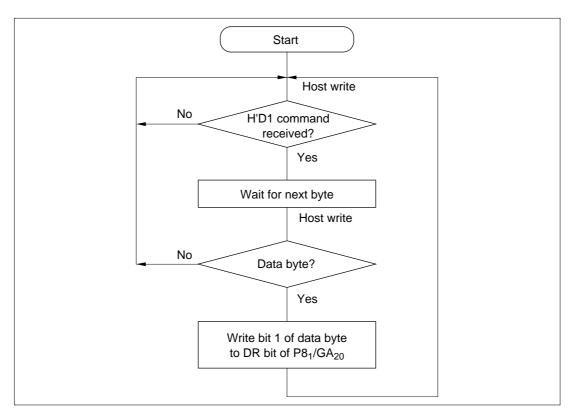

|       | 14.3.3   | A <sub>20</sub> Gate                                            | 327 |

| 14.4  | Interruj | pts                                                             | 330 |

|       | 14.4.1   | IBF1, IBF2                                                      | 330 |

|       | 14.4.2   | HIRQ <sub>11</sub> , HIRQ <sub>1</sub> , and HIRQ <sub>12</sub> | 330 |

| 14.5  | Applica  | ation Note                                                      | 331 |

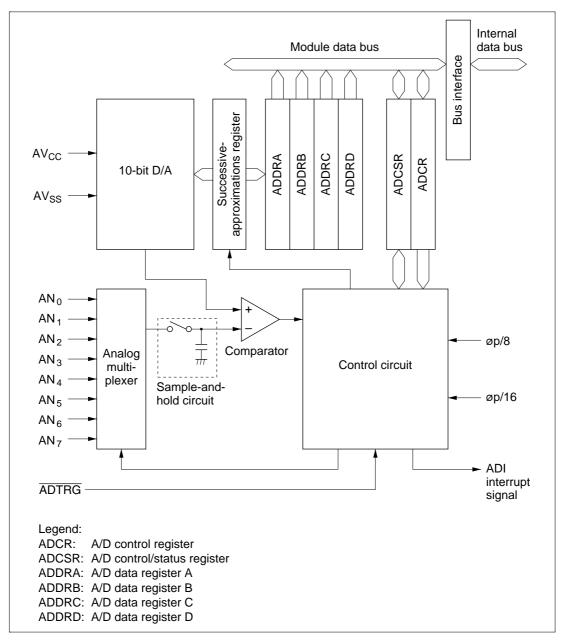

| Secti | ion 15   | A/D Converter                                                   | 333 |

| 15.1  | Overvi   | ew                                                              | 333 |

|       | 15.1.1   | Features                                                        | 333 |

|       | 15.1.2   | Block Diagram                                                   | 334 |

|       | 15.1.3   | Input Pins                                                      | 335 |

|       | 15.1.4   | Register Configuration.                                         | 336 |

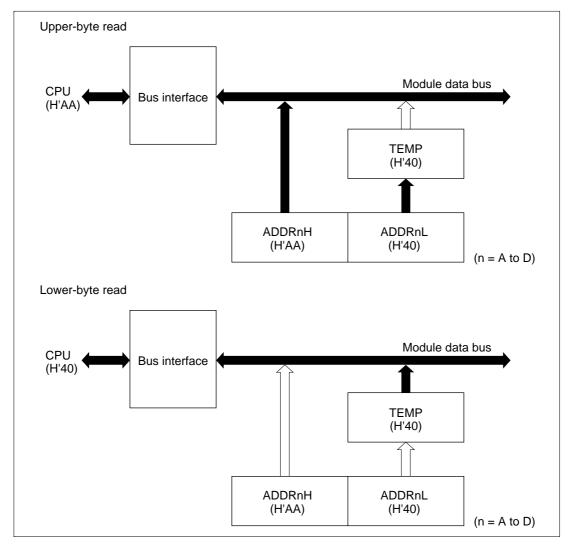

| 15.2  | Registe  | er Descriptions                                                 | 337 |

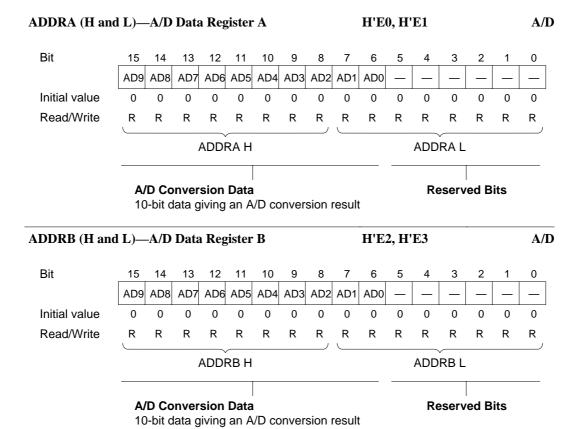

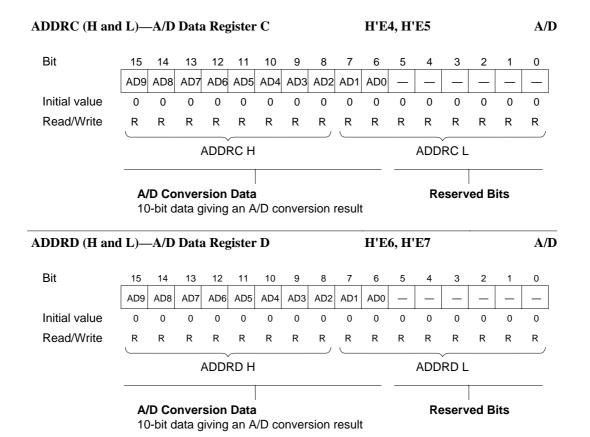

|       | 15.2.1   | A/D Data Registers A to D (ADDRA to ADDRD)                      | 337 |

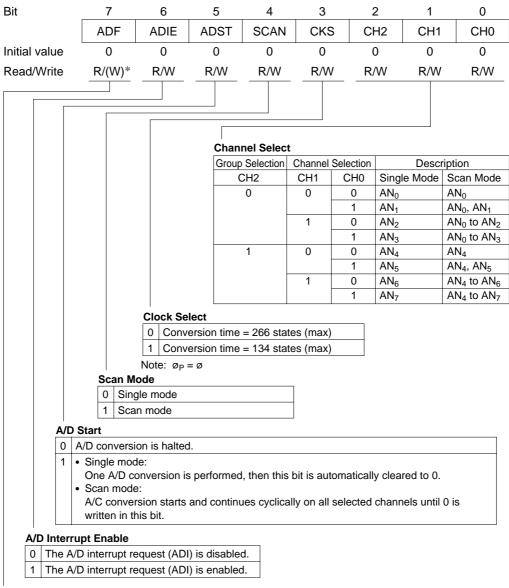

|       | 15.2.2   | A/D Control/Status Register (ADCSR)                             | 338 |

|       | 15.2.3   | A/D Control Register (ADCR)                                     | 340 |

| 15.3  | CPU In   | iterface                                                        | 340 |

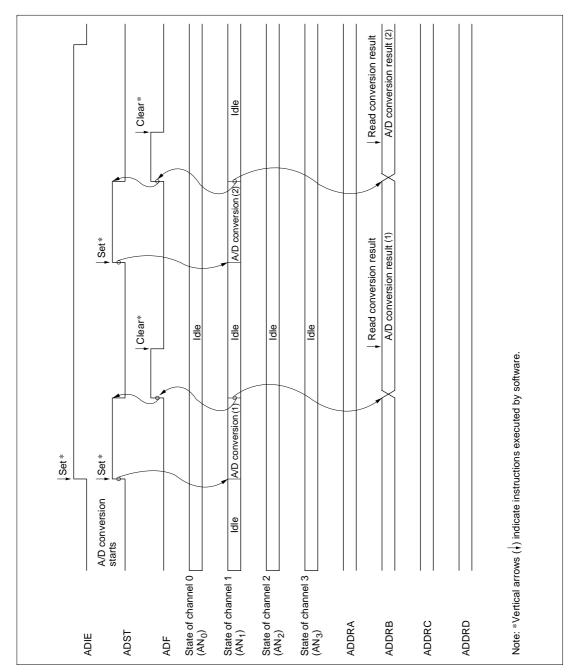

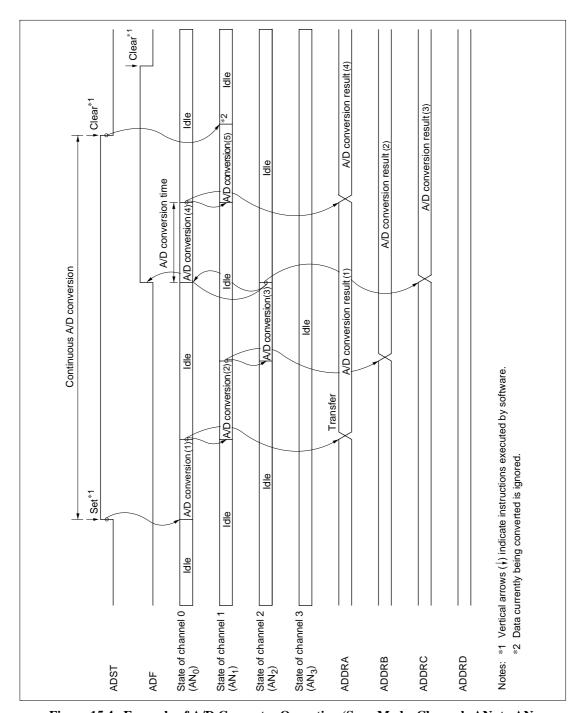

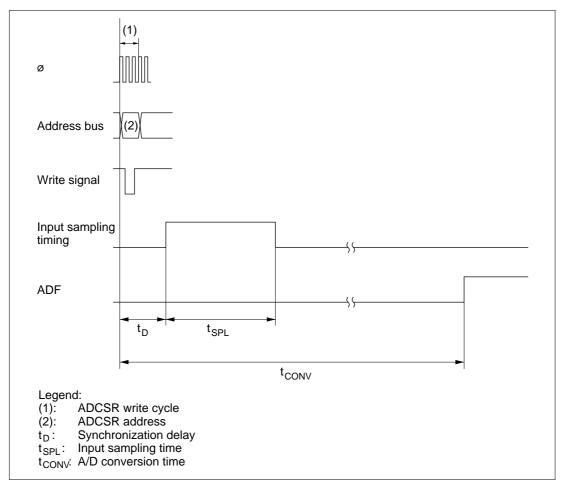

| 15.4  | Operati  | ion                                                             | 342 |

| 15.4.2 Scan Mode (SCAN = 1)                                                                                                                                       | 346 347 348 348 348 348 349 351 352 353 353   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

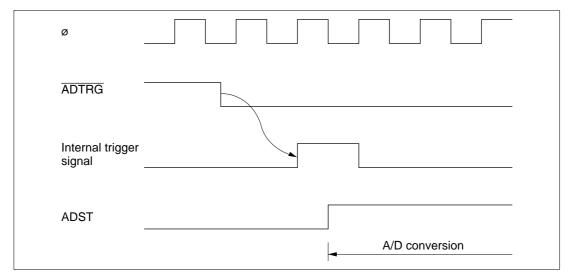

| 15.4.4 External Trigger Input Timing                                                                                                                              | 347 348 348 348 348 348 349 351 352 353 353   |

| 15.5 Interrupts                                                                                                                                                   | 348 348 348 348 348 348 349 351 352 353 353   |

| 15.6 Useage Notes                                                                                                                                                 | 348 348 348 348 349 351 352 353 353           |

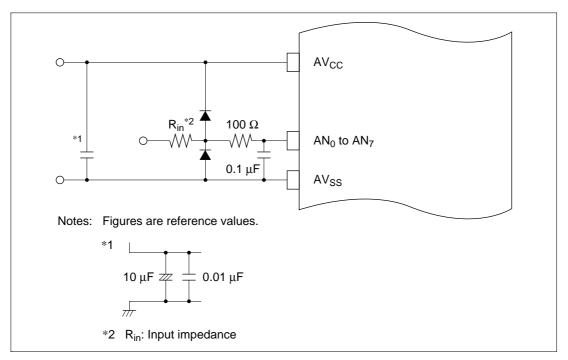

| 15.6.1 Setting Ranges of Analog Power Supply Pins, Etc. 15.6.2 Notes on Board Design                                                                              | 348 348 348 349 351 352 353 353               |

| 15.6.2 Notes on Board Design                                                                                                                                      | 348 348 349 351 352 353 353                   |

| 15.6.3 Notes on Noise                                                                                                                                             | 348<br>349<br>351<br>352<br>353<br>353<br>353 |

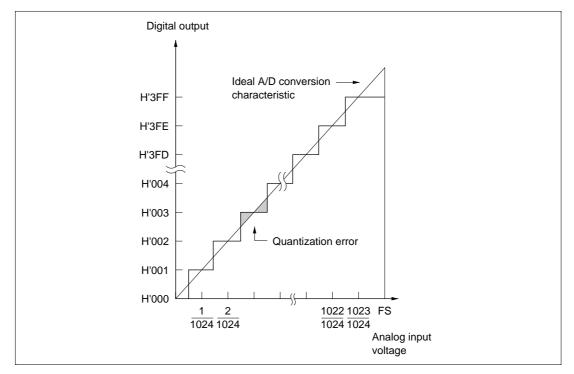

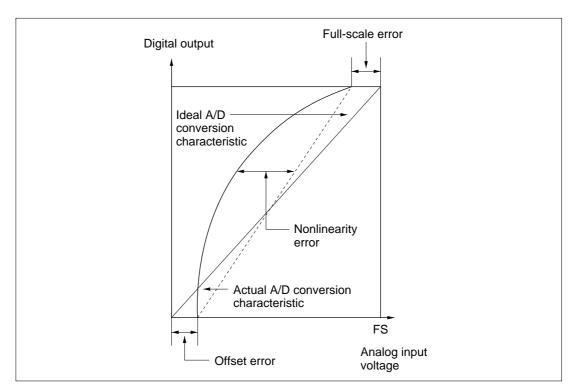

| 15.6.4 A/D Conversion Accuracy Definitions                                                                                                                        |                                               |

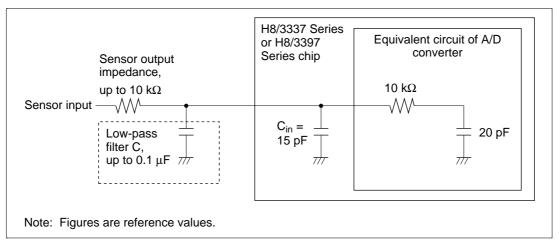

| 15.6.5 Allowable Signal-Source Impedance                                                                                                                          |                                               |

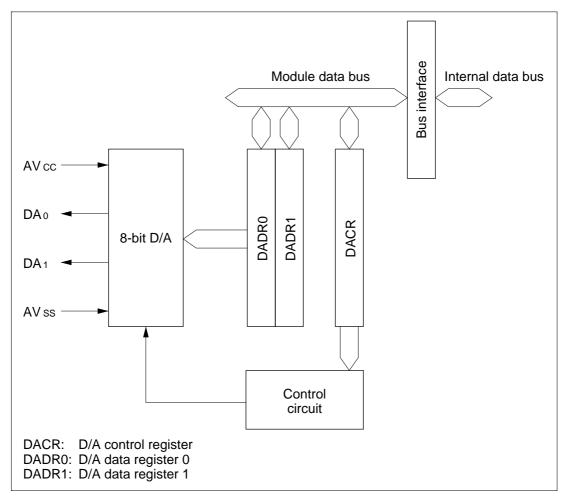

| Section 16 D/A Converter (H8/3337 Series Only)  16.1 Overview  16.1.1 Features  16.1.2 Block Diagram  16.1.3 Input and Output Pins  16.1.4 Register Configuration |                                               |

| Section 16 D/A Converter (H8/3337 Series Only)                                                                                                                    |                                               |

| 16.1 Overview                                                                                                                                                     |                                               |

| 16.1 Overview                                                                                                                                                     |                                               |

| 16.1.2 Block Diagram                                                                                                                                              |                                               |

| 16.1.3 Input and Output Pins                                                                                                                                      | 354                                           |

| 16.1.4 Register Configuration                                                                                                                                     |                                               |

| 16.1.4 Register Configuration                                                                                                                                     | 355                                           |

| 163 B : ( B : : :                                                                                                                                                 |                                               |

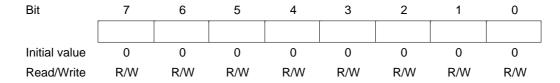

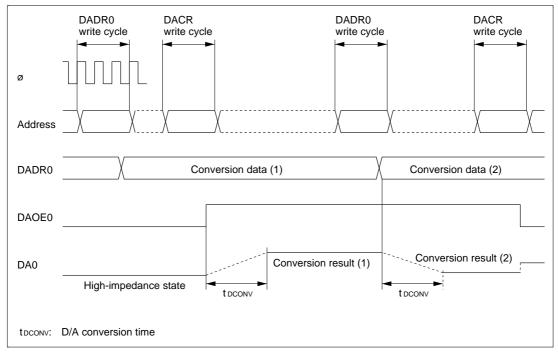

| 16.2 Register Descriptions                                                                                                                                        | 356                                           |

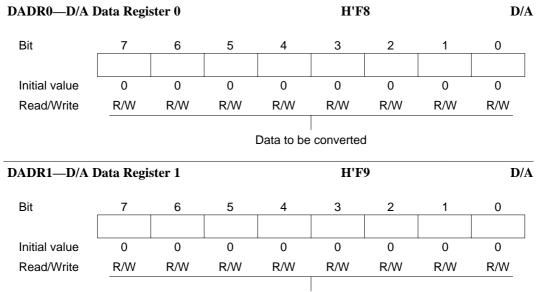

| 16.2.1 D/A Data Registers 0 and 1 (DADR0, DADR1)                                                                                                                  | 356                                           |

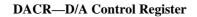

| 16.2.2 D/A Control Register (DACR)                                                                                                                                | 356                                           |

| 16.3 Operation                                                                                                                                                    |                                               |

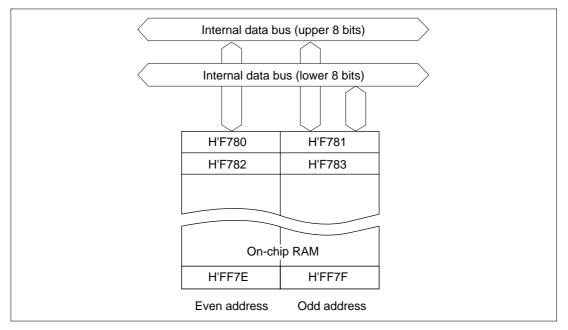

| Section 17 RAM                                                                                                                                                    | 359                                           |

| 17.1 Overview                                                                                                                                                     |                                               |

| 17.1.1 Block Diagram                                                                                                                                              |                                               |

| 17.1.2 RAM Enable Bit (RAME) in System Control Register (                                                                                                         | SYSCR) 360                                    |

| 17.2 Operation                                                                                                                                                    |                                               |

| 17.2.1 Expanded Modes (Modes 1 and 2)                                                                                                                             |                                               |

| 17.2.2 Single-Chip Mode (Mode 3)                                                                                                                                  |                                               |

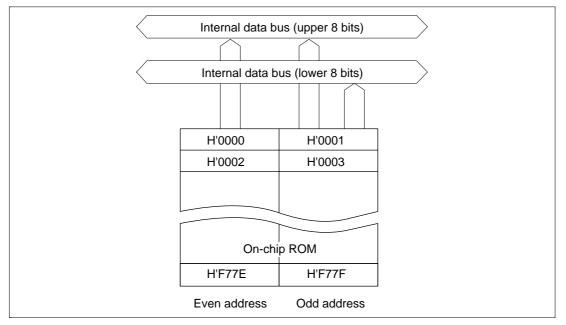

| Section 18 ROM (Mask ROM Version/ZTAT Version)                                                                                                                    | 361                                           |

| 18.1 Overview                                                                                                                                                     |                                               |

|                                                                                                                                                                   |                                               |

| 18.1.1 Block Diagram                                                                                                                                              |                                               |

| 18.1.1 Block Diagram                                                                                                                                              | ······································        |

|                                                                                                                                                                   |                                               |

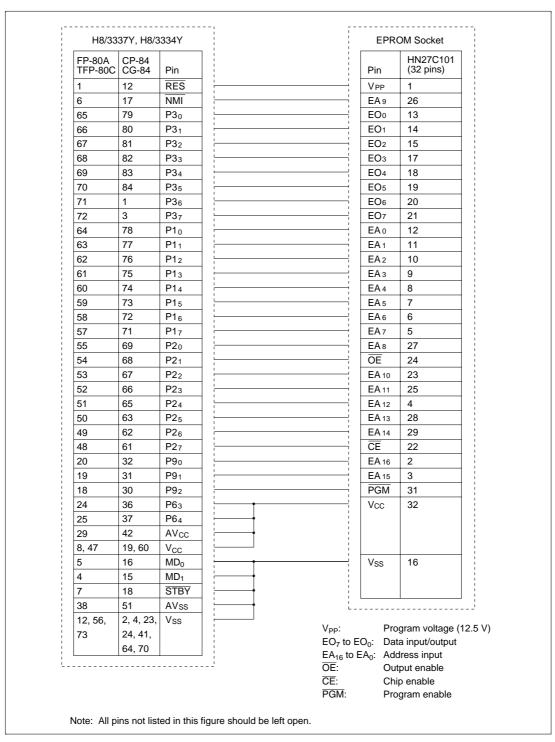

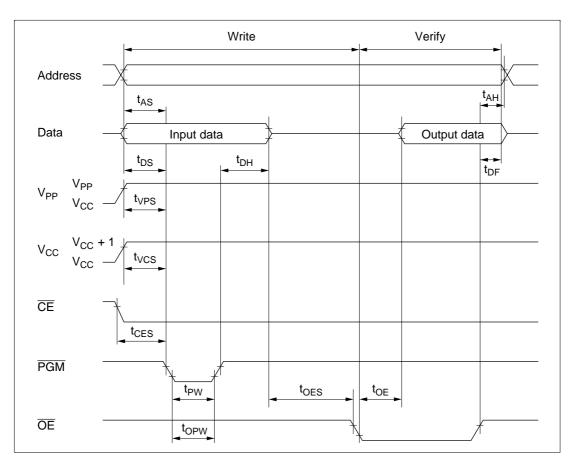

| 18.2 Writer Mode (H8/3337Y, H8/3334Y)                                                                                                                             |                                               |

| Sect | ion 19  | ROM (32-kbyte Dual-Power-Supply Flash Memory Version)          | 373 |

|------|---------|----------------------------------------------------------------|-----|

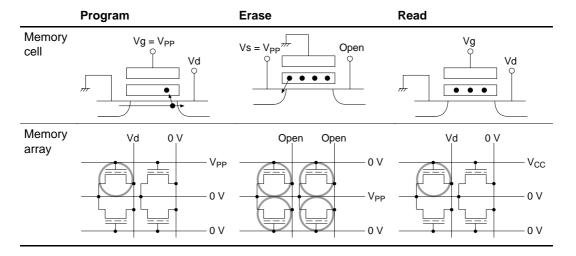

| 19.1 | Flash N | Memory Overview                                                | 373 |

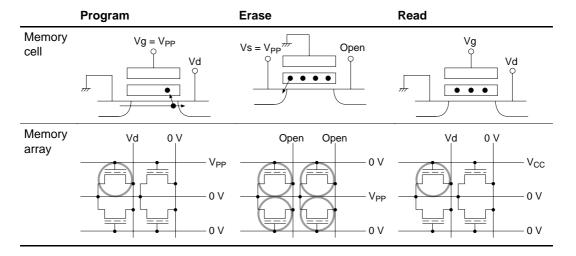

|      | 19.1.1  | Flash Memory Operating Principle                               | 373 |

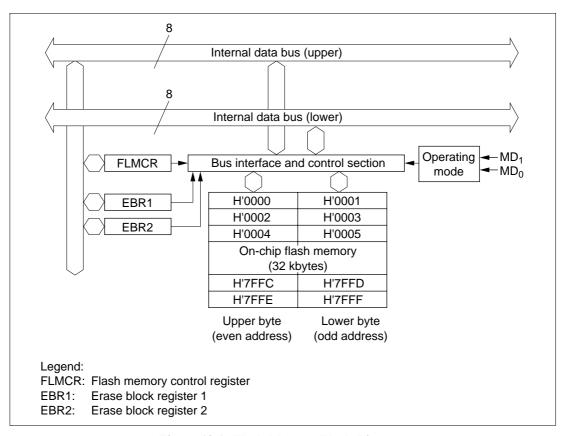

|      | 19.1.2  | Mode Programming and Flash Memory Address Space                | 374 |

|      | 19.1.3  | Features                                                       | 374 |

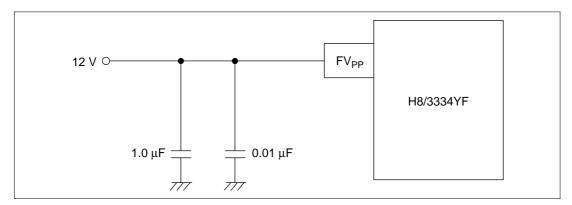

|      | 19.1.4  | Block Diagram                                                  | 375 |

|      | 19.1.5  | Input/Output Pins                                              | 376 |

|      | 19.1.6  | Register Configuration                                         | 376 |

| 19.2 | Flash N | Memory Register Descriptions                                   | 377 |

|      | 19.2.1  | Flash Memory Control Register (FLMCR)                          | 377 |

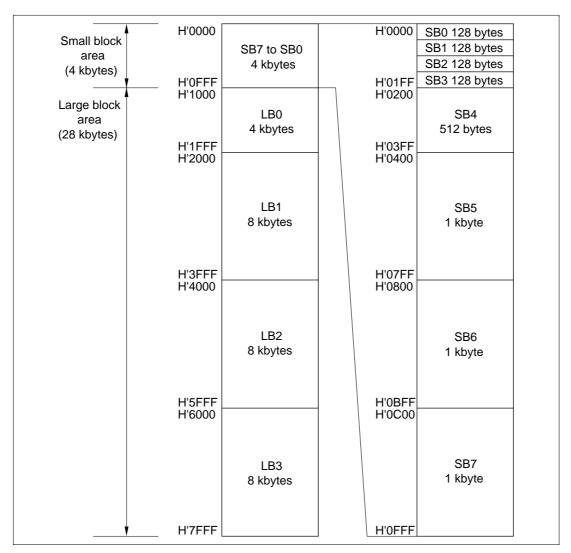

|      | 19.2.2  | Erase Block Register 1 (EBR1)                                  | 378 |

|      | 19.2.3  | Erase Block Register 2 (EBR2)                                  | 379 |

|      | 19.2.4  | Wait-State Control Register (WSCR)                             | 380 |

| 19.3 | On-Bo   | ard Programming Modes                                          | 383 |

|      | 19.3.1  | Boot Mode                                                      | 384 |

|      | 19.3.2  | User Programming Mode                                          | 390 |

| 19.4 | Program | mming and Erasing Flash Memory                                 | 392 |

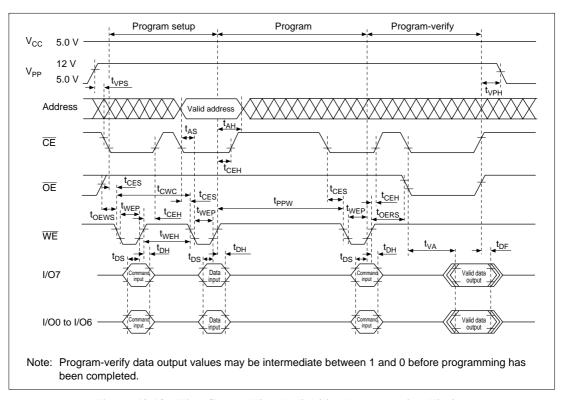

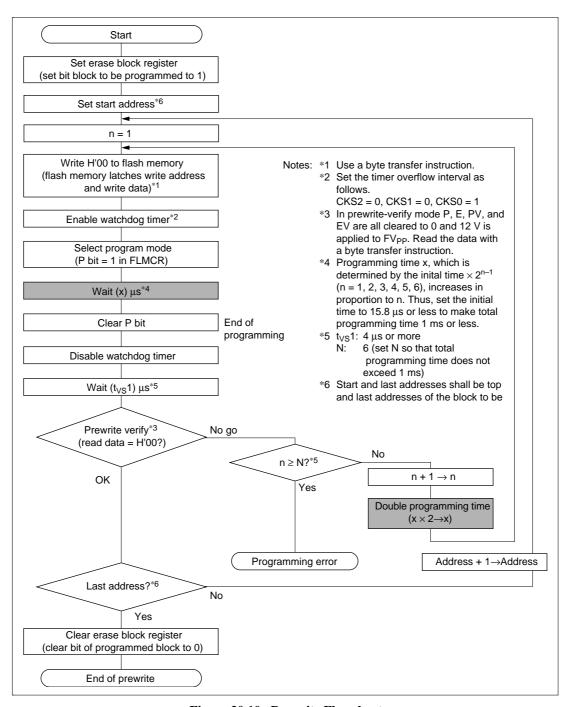

|      | 19.4.1  | Program Mode                                                   | 392 |

|      | 19.4.2  | Program-Verify Mode                                            | 393 |

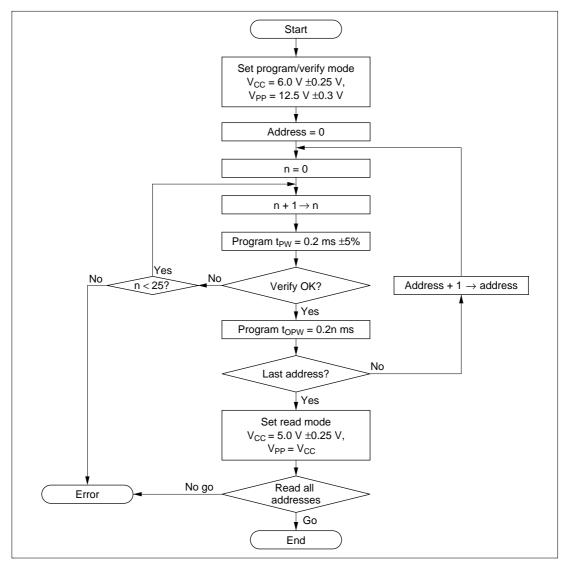

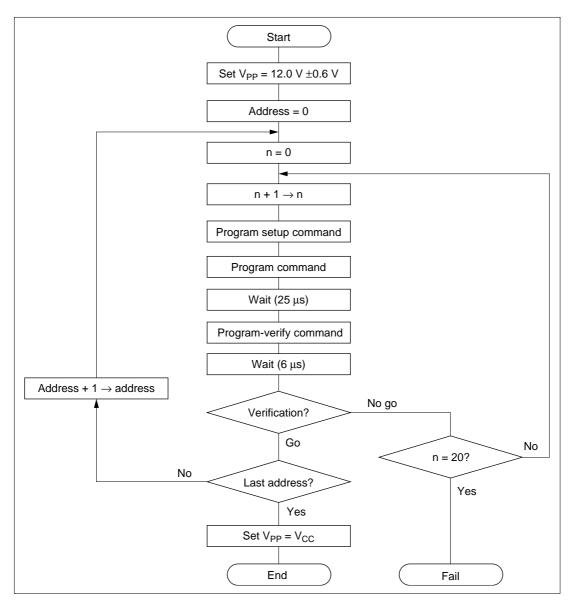

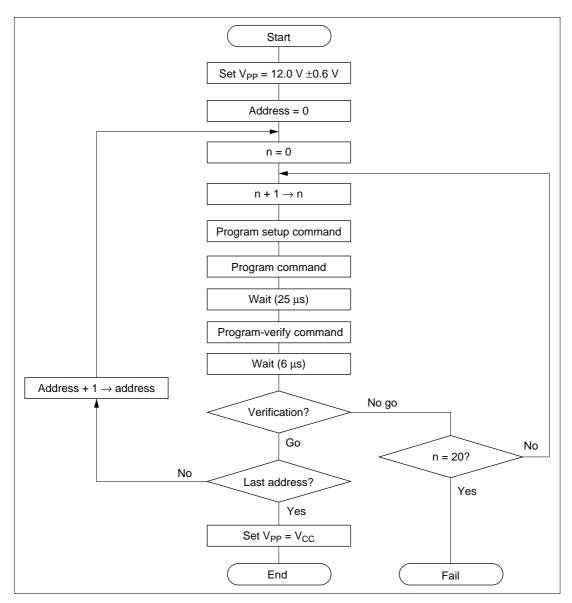

|      | 19.4.3  | Programming Flowchart and Sample Program                       | 394 |

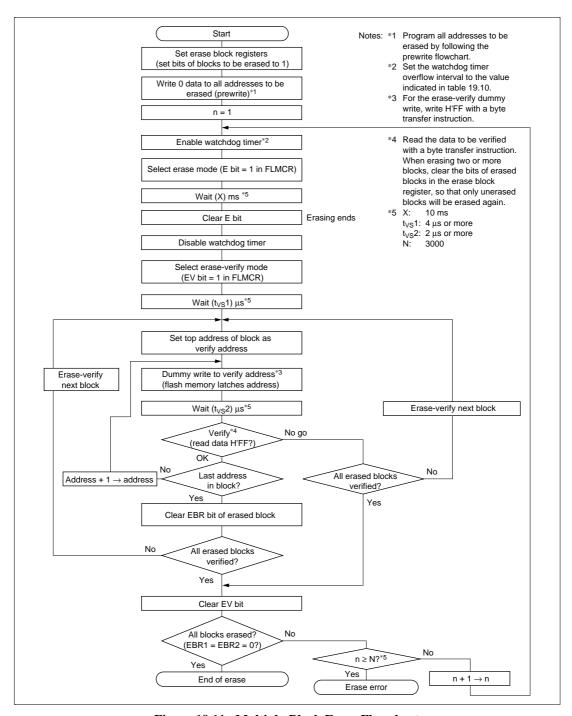

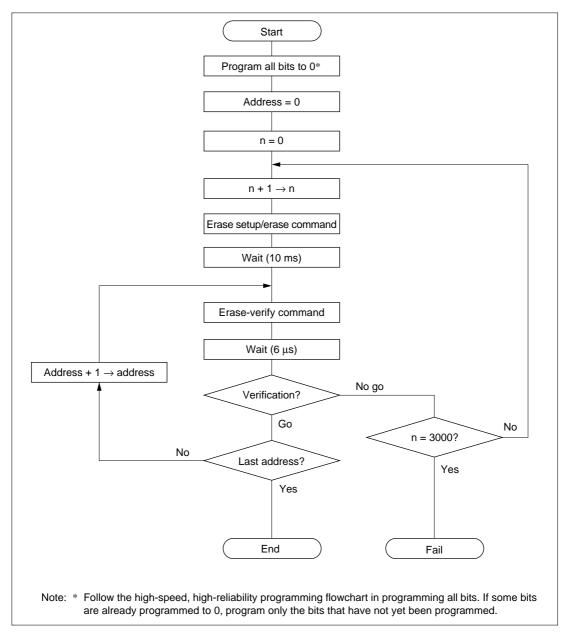

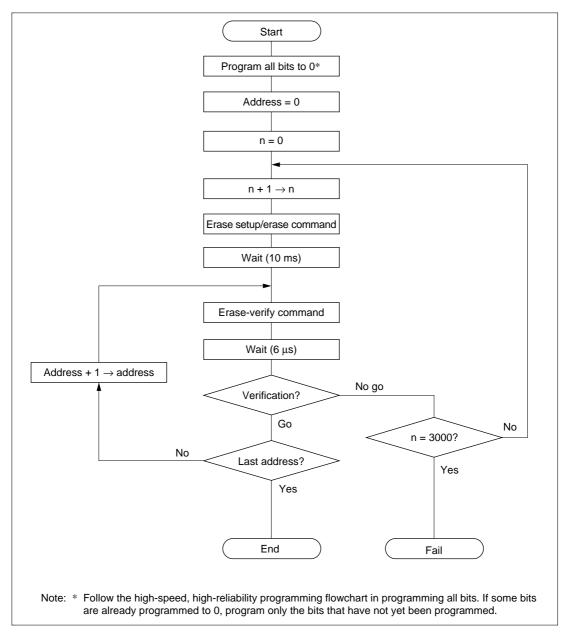

|      | 19.4.4  | Erase Mode                                                     | 396 |

|      | 19.4.5  | Erase-Verify Mode                                              | 396 |

|      |         | Erasing Flowchart and Sample Program                           |     |

|      | 19.4.7  | Prewrite Verify Mode                                           | 410 |

|      | 19.4.8  | Protect Modes                                                  | 410 |

|      | 19.4.9  | Interrupt Handling during Flash Memory Programming and Erasing | 411 |

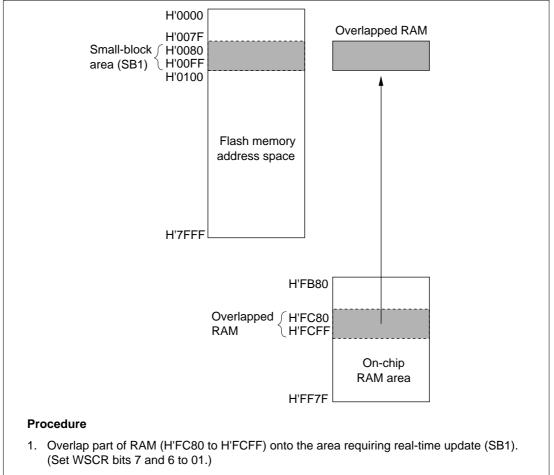

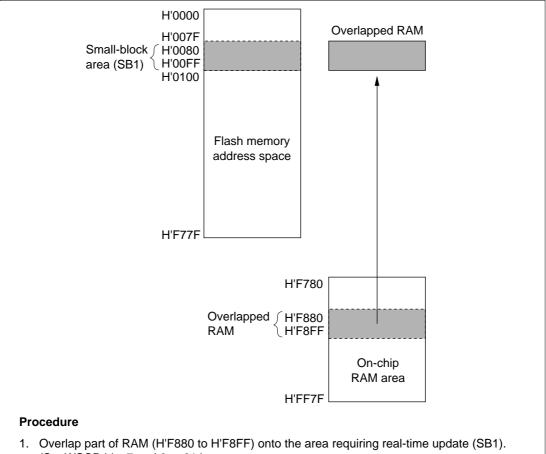

| 19.5 | Flash N | Memory Emulation by RAM                                        | 413 |

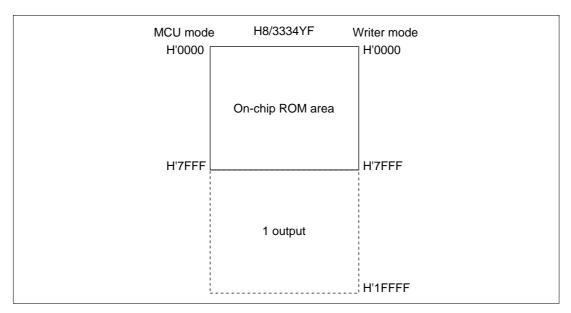

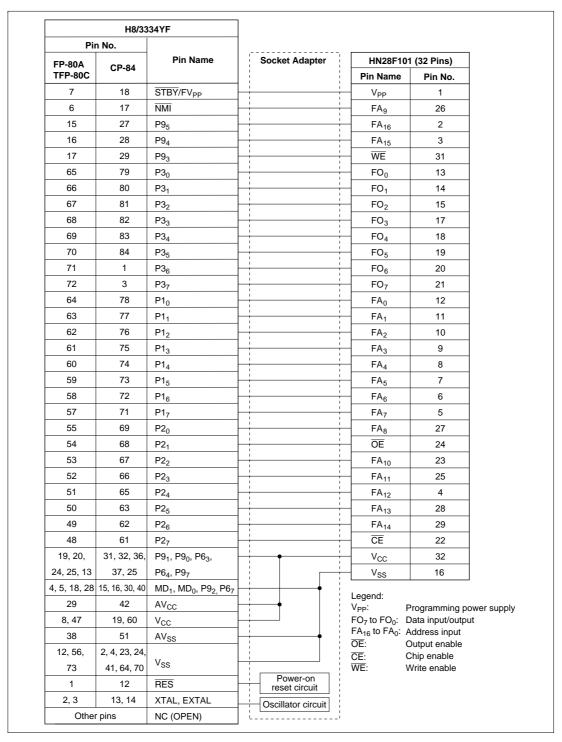

| 19.6 |         | Memory Writer Mode (H8/3334YF)                                 |     |

|      |         | Writer Mode Setting                                            |     |

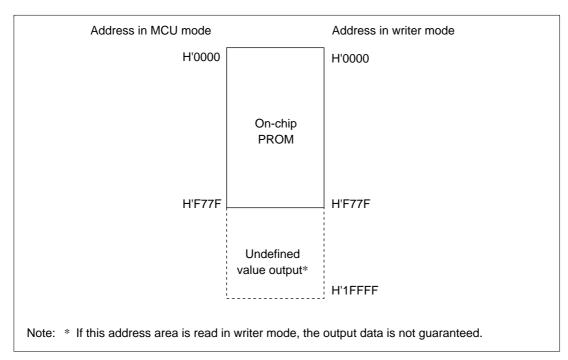

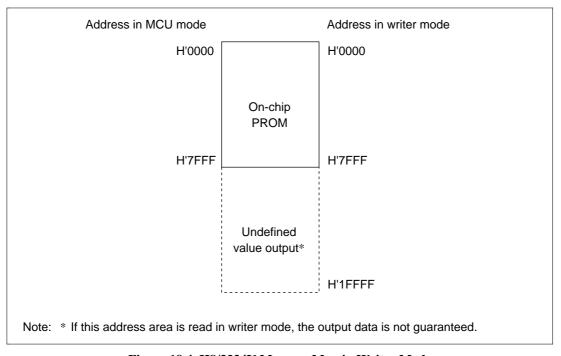

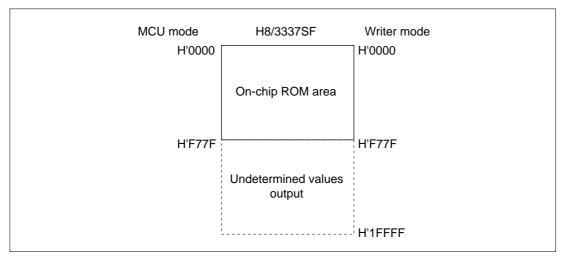

|      |         | Socket Adapter and Memory Map                                  |     |

|      | 19.6.3  | Operation in Writer Mode                                       | 418 |

| 19.7 | Flash N | Memory Programming and Erasing Precautions                     | 426 |

| Sect | ion 20  | ROM (60-kbyte Dual-Power-Supply Flash Memory Version)          | 433 |

| 20.1 | Flash N | Memory Overview                                                | 433 |

|      | 20.1.1  | Flash Memory Operating Principle                               | 433 |

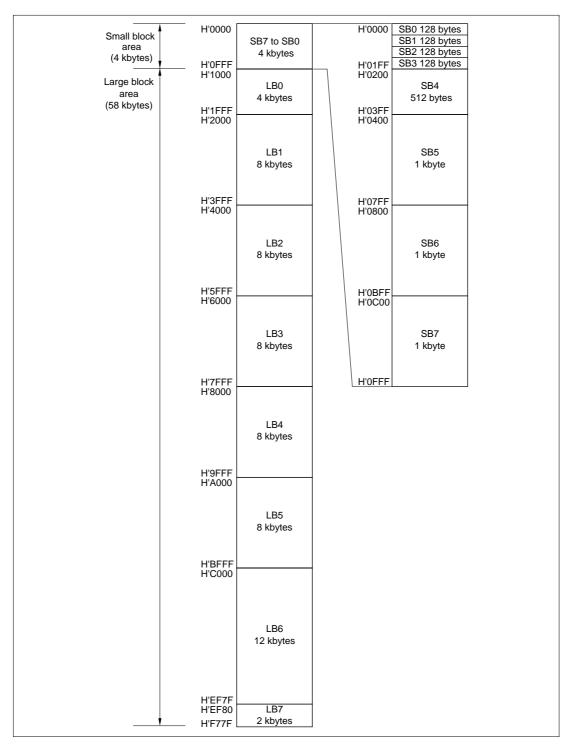

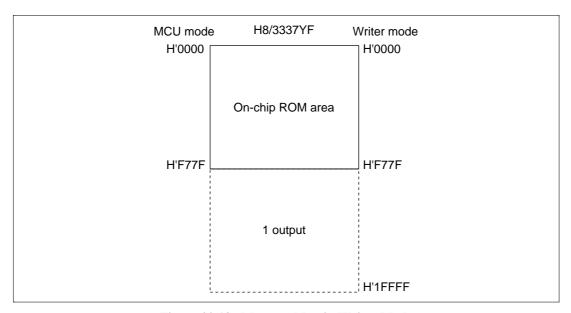

|      | 20.1.2  | Mode Programming and Flash Memory Address Space                | 434 |

|      | 20.1.3  | Features                                                       | 434 |

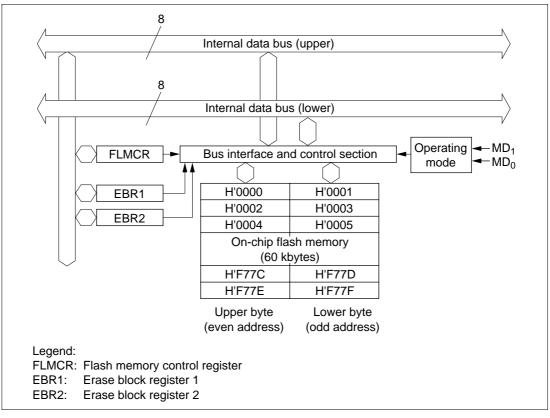

|      |         | Block Diagram                                                  |     |

|      |         | Input/Output Pins                                              |     |

|      |         | Register Configuration                                         |     |

| 20.2 |         | Memory Register Descriptions                                   |     |

|      | 20.2.1  | Flash Memory Control Register (FLMCR)                          | 437 |

|      | 20.2.2  | Erase Block Register 1 (EBR1)                                  | 438 |

|------|---------|----------------------------------------------------------------|-----|

|      | 20.2.3  | Erase Block Register 2 (EBR2)                                  | 439 |

|      | 20.2.4  | Wait-State Control Register (WSCR)                             | 440 |

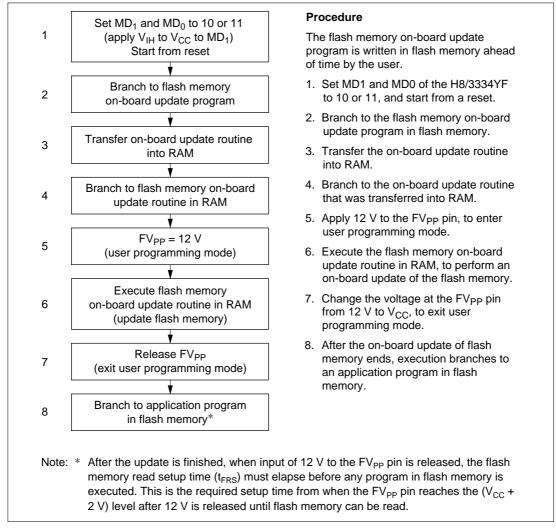

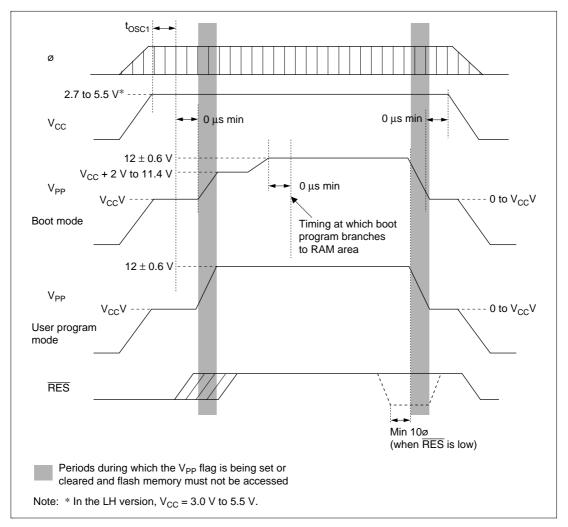

| 20.3 | On-Bo   | ard Programming Modes                                          | 443 |

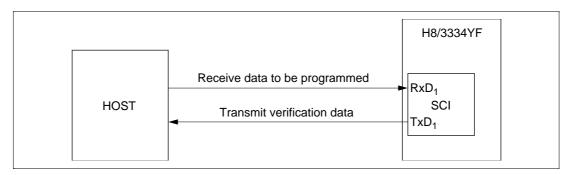

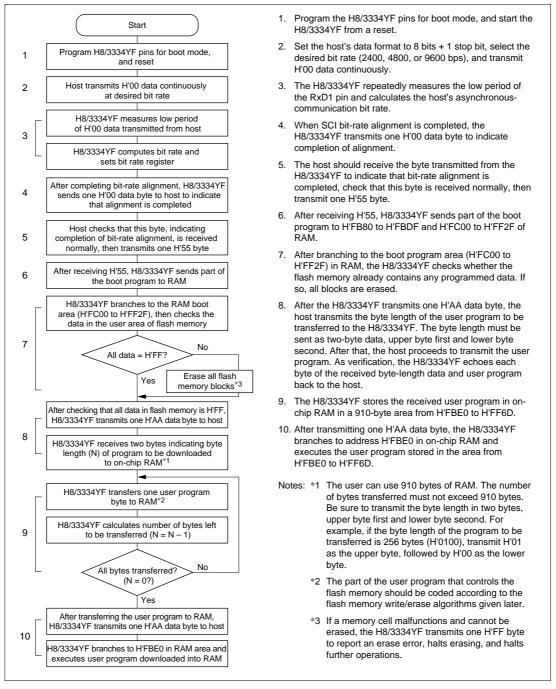

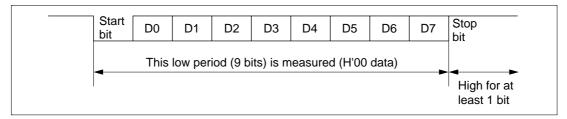

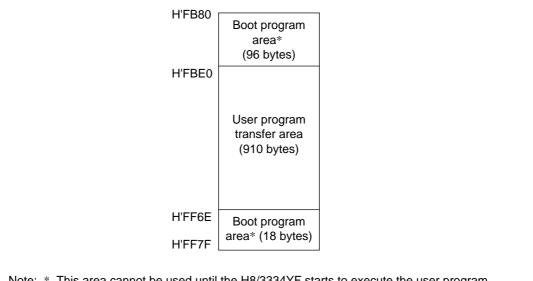

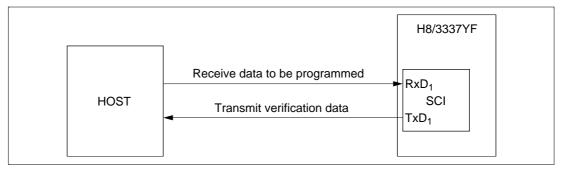

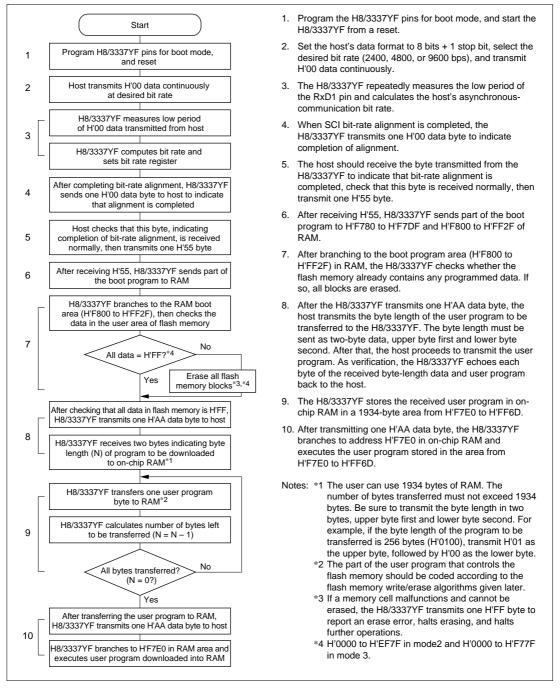

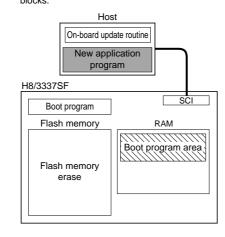

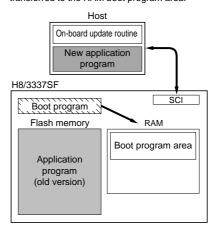

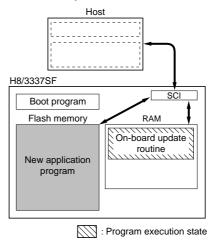

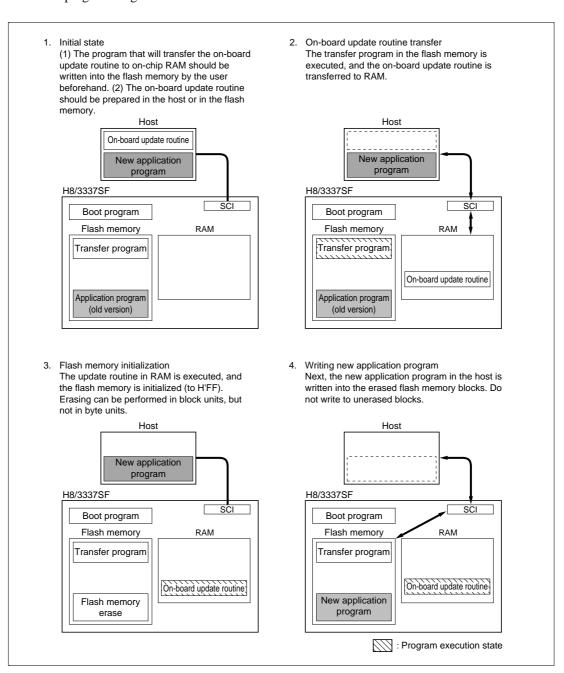

|      | 20.3.1  | Boot Mode                                                      | 444 |

|      | 20.3.2  | User Programming Mode                                          | 450 |

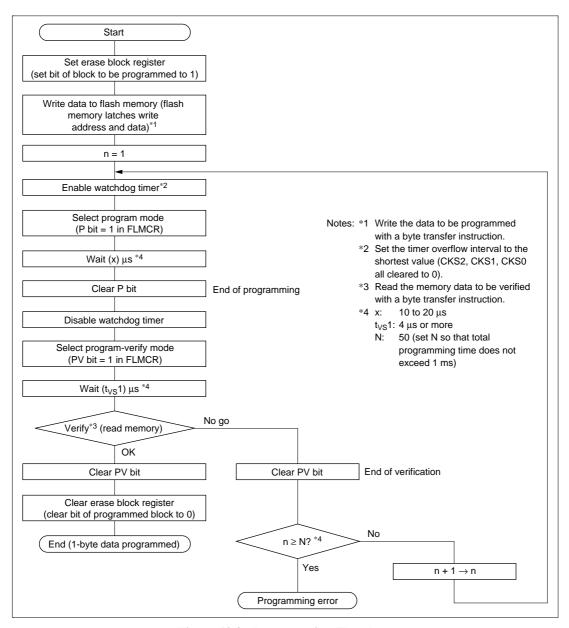

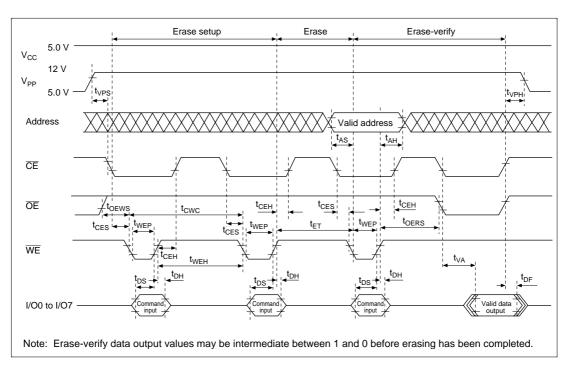

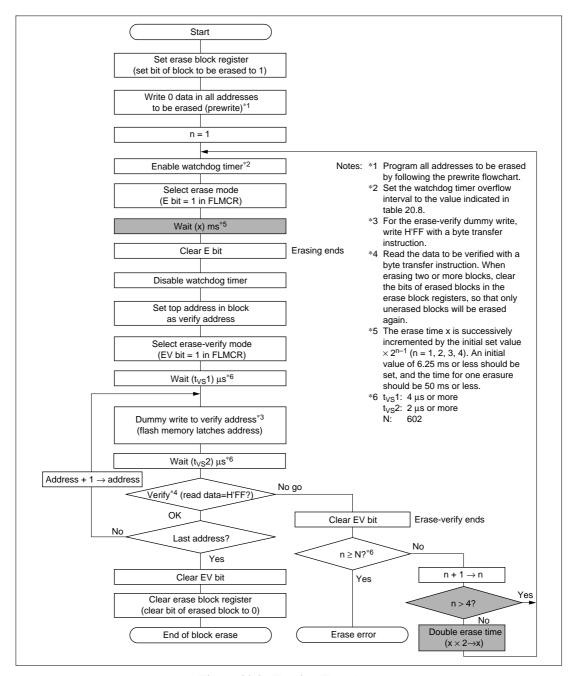

| 20.4 | Prograi | mming and Erasing Flash Memory                                 | 452 |

|      | 20.4.1  | Program Mode                                                   | 452 |

|      | 20.4.2  | Program-Verify Mode                                            | 453 |

|      | 20.4.3  | Programming Flowchart and Sample Program                       | 454 |

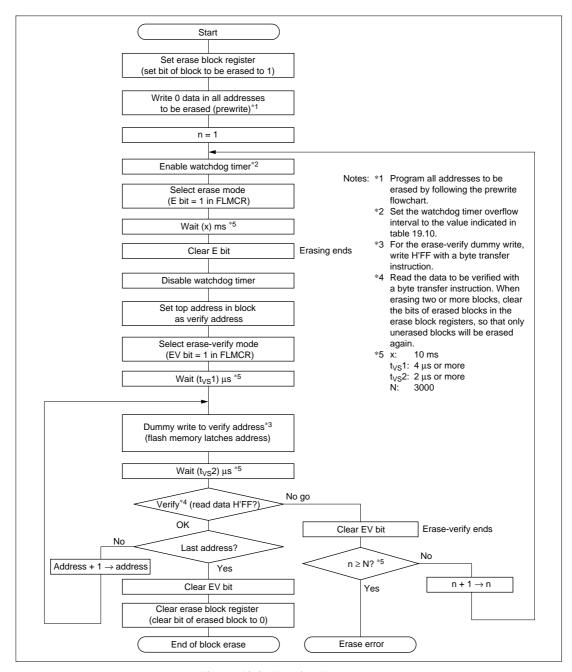

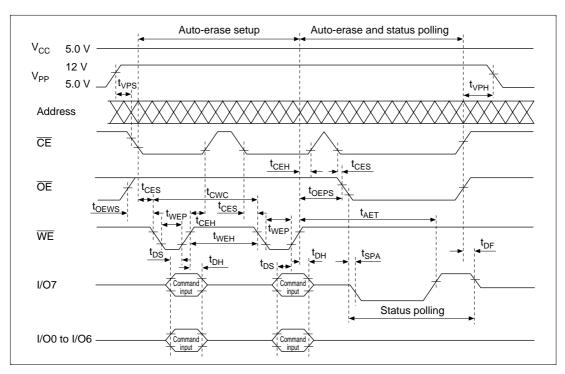

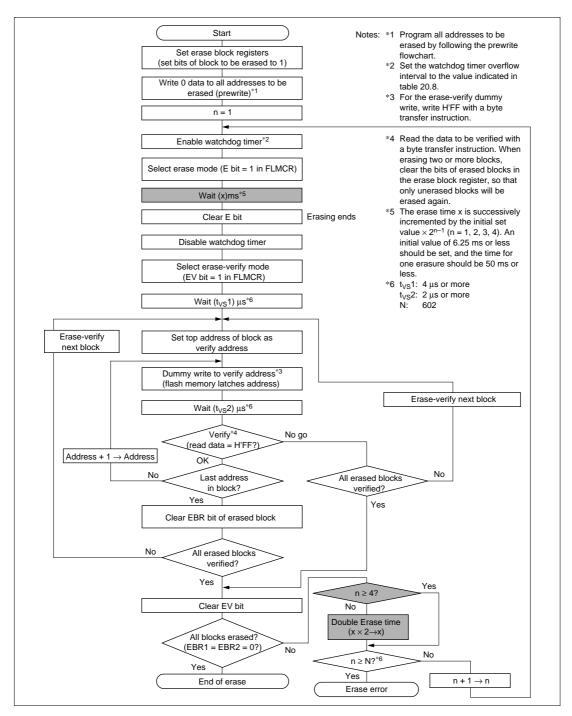

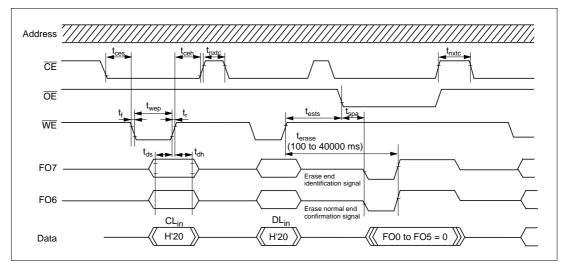

|      | 20.4.4  | Erase Mode                                                     | 456 |

|      | 20.4.5  | Erase-Verify Mode                                              | 456 |

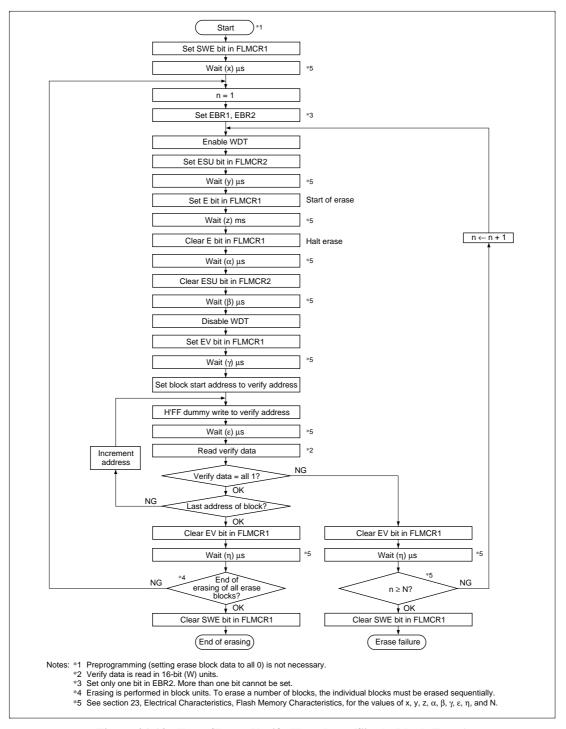

|      | 20.4.6  | Erasing Flowchart and Sample Program                           | 457 |

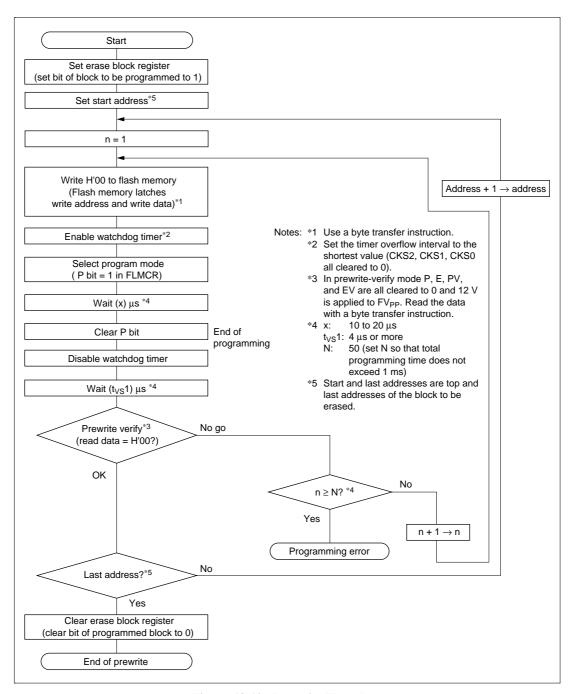

|      | 20.4.7  | Prewrite Verify Mode                                           | 470 |

|      | 20.4.8  | Protect Modes                                                  | 470 |

|      | 20.4.9  | Interrupt Handling during Flash Memory Programming and Erasing | 471 |

| 20.5 | Flash N | Memory Emulation by RAM                                        | 473 |

| 20.6 | Flash N | Memory Writer Mode (H8/3337YF)                                 | 476 |

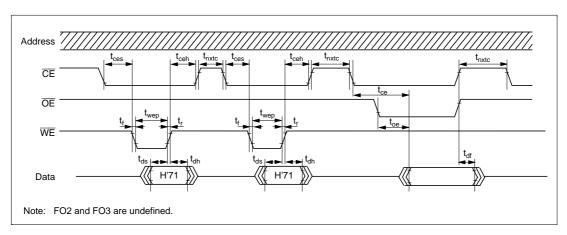

|      | 20.6.1  | Writer Mode Setting                                            | 476 |

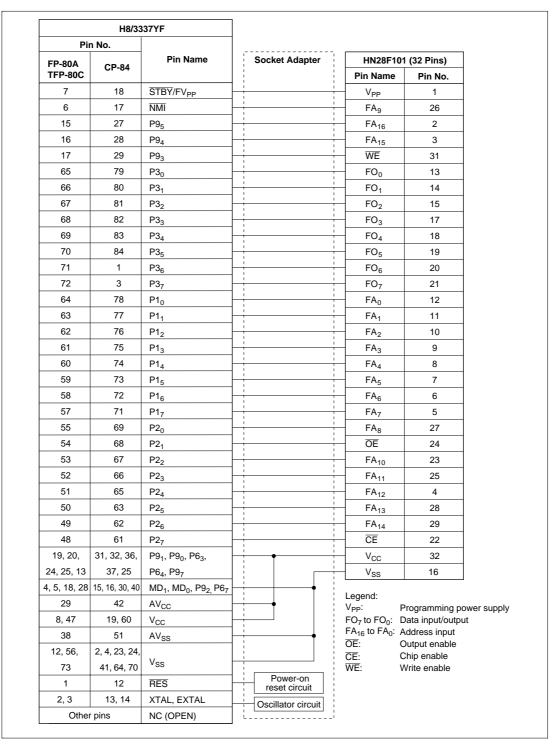

|      | 20.6.2  | Socket Adapter and Memory Map                                  | 476 |

|      | 20.6.3  | Operation in Writer Mode                                       | 478 |

| 20.7 | Flash N | Memory Programming and Erasing Precautions                     | 486 |

|      |         |                                                                |     |

| Sect |         | ROM (60-kbyte Single-Power-Supply Flash Memory Version)        |     |

| 21.1 |         | Memory Overview                                                |     |

|      |         | Mode Pin Settings and ROM Space                                |     |

|      |         | Features                                                       |     |

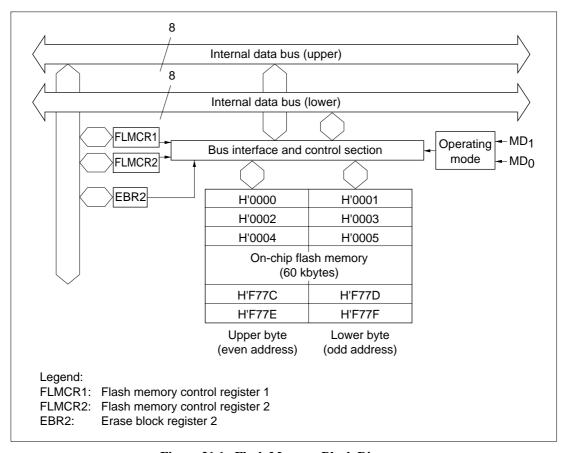

|      |         | Block Diagram                                                  |     |

|      | 21.1.4  | Input/Output Pins                                              | 498 |

|      |         | Register Configuration                                         |     |

|      |         | Mode Control Register (MDCR)                                   |     |

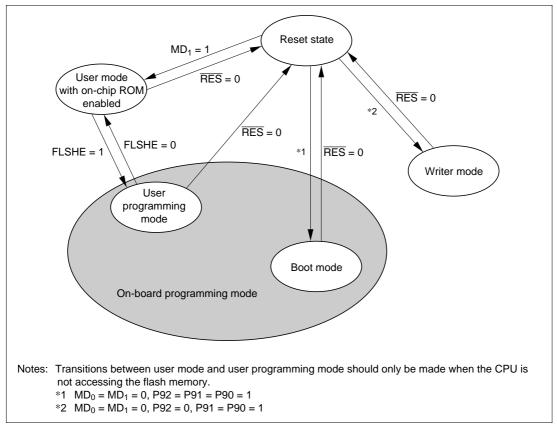

|      |         | Flash Memory Operating Modes                                   |     |

| 21.2 |         | Memory Register Descriptions                                   |     |

|      |         | Flash Memory Control Register 1 (FLMCR1)                       |     |

|      |         | Flash Memory Control Register 2 (FLMCR2)                       |     |

|      | 21.2.3  | Erase Block Register 2 (EBR2)                                  | 507 |

|      |         | Wait-State Control Register (WSCR)                             |     |

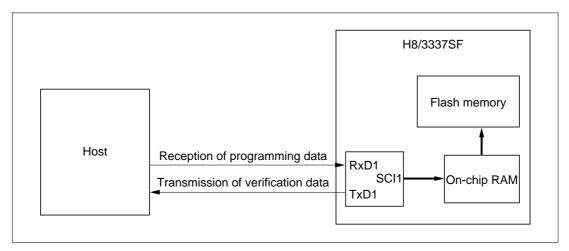

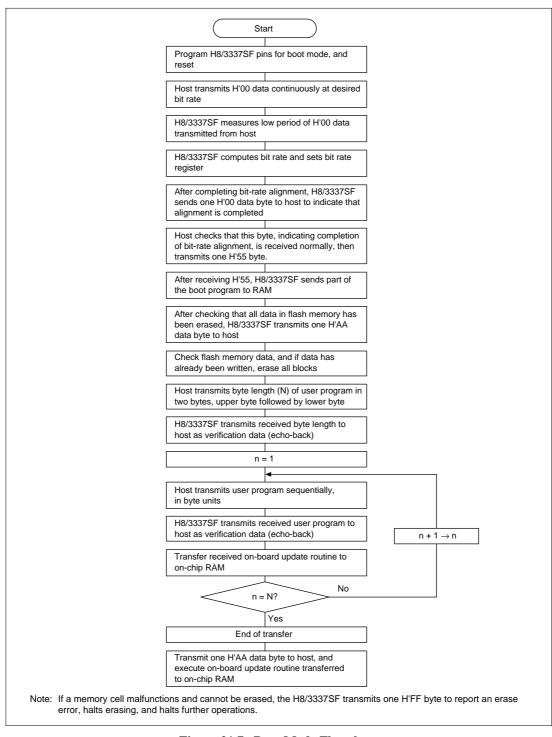

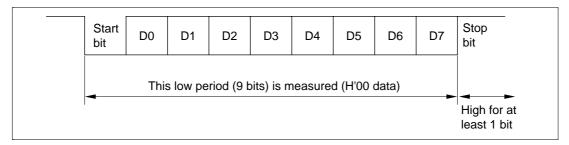

| 21.3 |         | ard Programming Modes                                          |     |

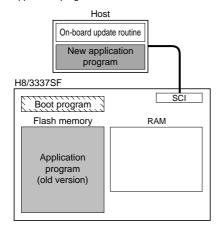

|      |         | Boot Mode                                                      |     |

|      |         | User Programming Mode                                          |     |

| 21.4 | Prograi | mming/Erasing Flash Memory                                     |     |

|      | 21.4.1  | - 8                                                            |     |

|      | 21.4.2  | Program-Verify Mode                                            | 517 |

|       | 21.4.3   | Erase Mode                                                     | 519 |

|-------|----------|----------------------------------------------------------------|-----|

|       | 21.4.4   | Erase-Verify Mode.                                             | 519 |

|       | 21.4.5   | Protect Modes                                                  | 521 |

|       | 21.4.6   | Interrupt Handling during Flash Memory Programming and Erasing | 523 |

| 21.5  |          | Memory Writer Mode (H8/3337SF)                                 |     |

|       |          | Writer Mode Setting                                            |     |

|       | 21.5.2   | Socket Adapter and Memory Map                                  | 524 |

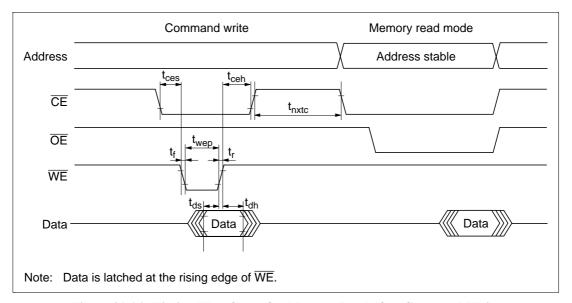

|       | 21.5.3   | Operation in Writer Mode                                       | 525 |

| 21.6  | Flash N  | Memory Programming and Erasing Precautions                     | 536 |

| Secti | on 22    | Power-Down State                                               | 539 |

| 22.1  | Overvi   | ew                                                             | 539 |

|       | 22.1.1   | System Control Register (SYSCR)                                | 540 |

| 22.2  | Sleep N  | Mode                                                           | 542 |

|       | 22.2.1   | Transition to Sleep Mode                                       | 542 |

|       | 22.2.2   | Exit from Sleep Mode                                           | 542 |

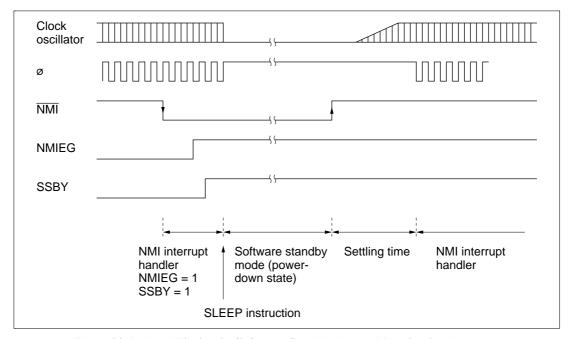

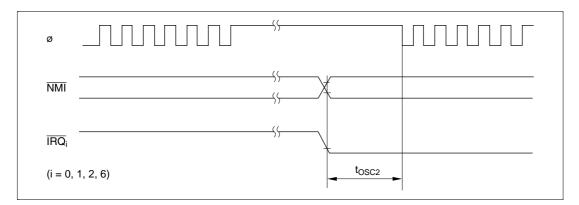

| 22.3  | Softwa   | re Standby Mode                                                | 543 |

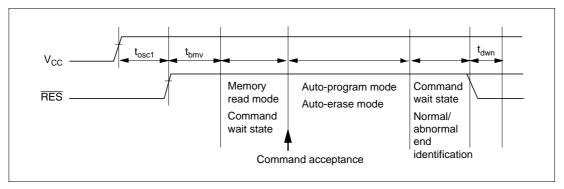

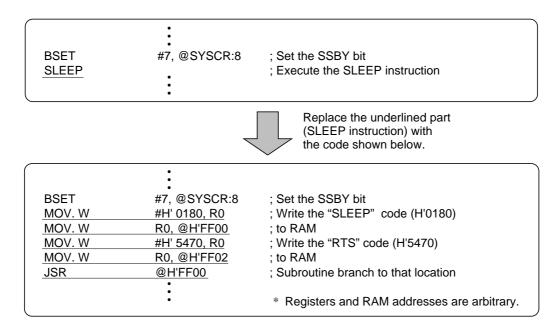

|       | 22.3.1   | Transition to Software Standby Mode                            | 543 |

|       | 22.3.2   | Exit from Software Standby Mode                                | 543 |

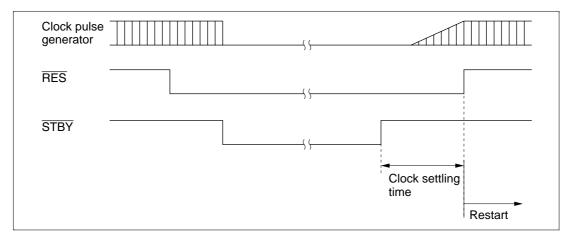

|       |          | Clock Settling Time for Exit from Software Standby Mode        |     |

|       |          | Sample Application of Software Standby Mode                    |     |

|       |          | Application Notes                                              |     |

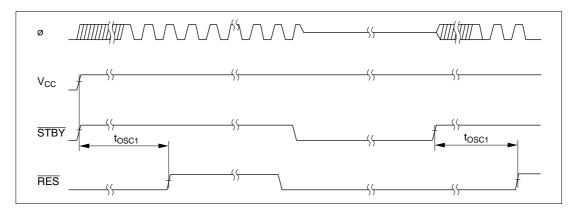

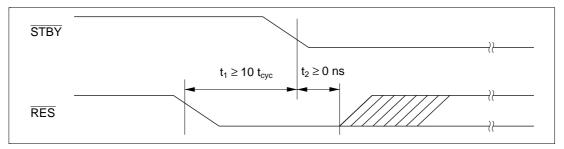

| 22.4  | Hardwa   | are Standby Mode                                               | 547 |

|       | 22.4.1   | Transition to Hardware Standby Mode                            |     |

|       |          | Recovery from Hardware Standby Mode                            |     |

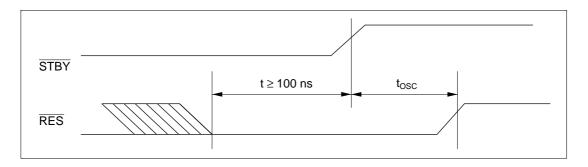

|       | 22.4.3   | Timing Relationships in Hardware Standby Mode                  | 548 |

| Secti | on 23    | Electrical Characteristics                                     | 549 |

| 23.1  | Absolu   | te Maximum Ratings                                             | 549 |