## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

SH7040, SH7041, SH7042, SH7043, SH7044, SH7045 Group

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH RISC engine Family/SH7040 Series (CPU Core SH-2)

Renesas 32-Bit RISC Microcomputer SuperH RISC engine Family/ SH7040 Series (CPU Core SH-2)

SH7040, SH7041, SH704 SH7043, SH7044, SH704 Group

Hardware Manual

REJ09B0

product best suited to the customer's application; they do not convey any license under any intellectual propert other rights, belonging to Renesas Technology Corporation or a third party. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application example

These materials are intended as a reference to assist our customers in the selection of the Renesas Technology C

Notes regarding these materials

these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms information on products at the time of publication of these materials, and are subject to change by Renesas Tec Corporation without notice due to product improvements or other reasons. It is therefore recommended that cus Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the

- information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from or errors

- Please also pay attention to information published by Renesas Technology Corporation by various means, inc Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, algorithms, please be sure to evaluate all information as a total system before making a final decision on the app

- information and products. Renesas Technology Corporation assumes no responsibility for any damage, liabilit

- resulting from the information contained herein.

- Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system

- under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporatio

- authorized Renesas Technology Corporation product distributor when considering the use of a product contain

- specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or und The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or

- materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported u from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of deprohibited.

- Please contact Renesas Technology Corporation for further details on these materials or the products contained

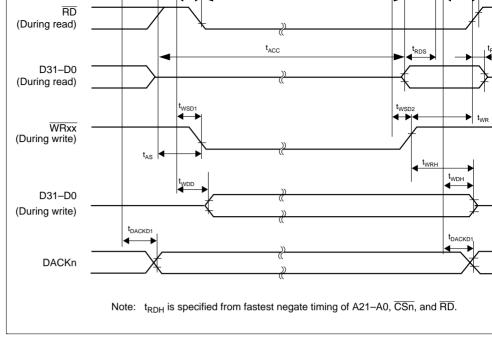

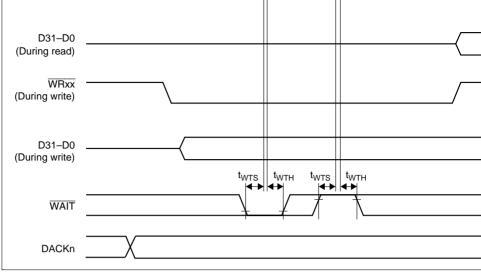

performance during external memory access.

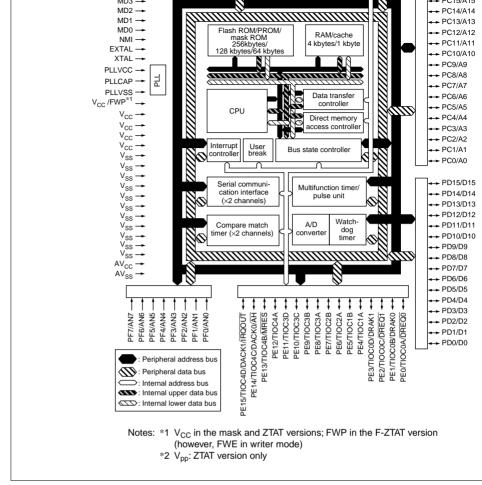

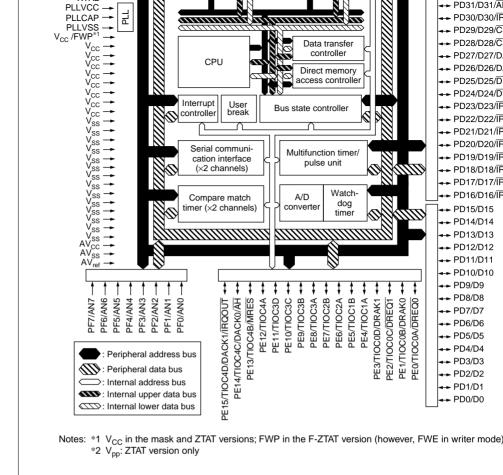

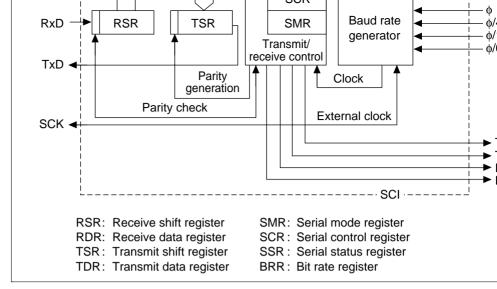

In addition, the SH7040 series includes on-chip peripheral functions necessary for syste configuration, such as large-capacity ROM and RAM, timers, a serial communication in (SCI), an A/D converter, an interrupt controller, and I/O ports. Memory or peripheral LS connected efficiently with an external memory access support function. This greatly red system cost.

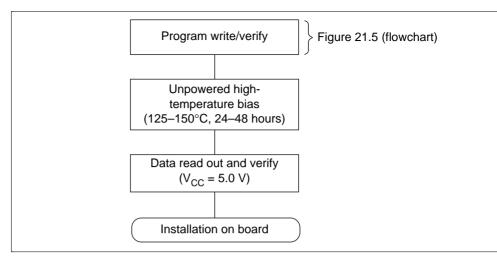

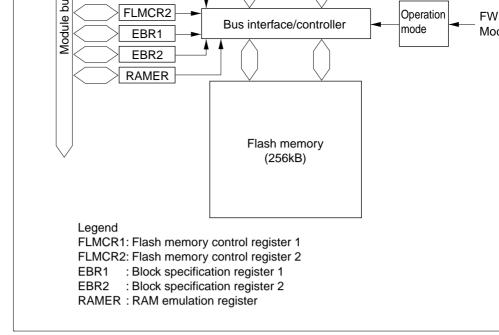

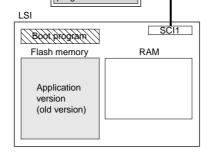

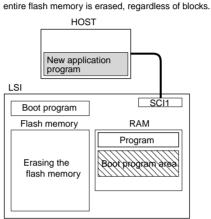

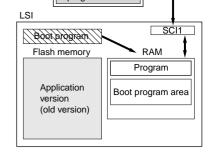

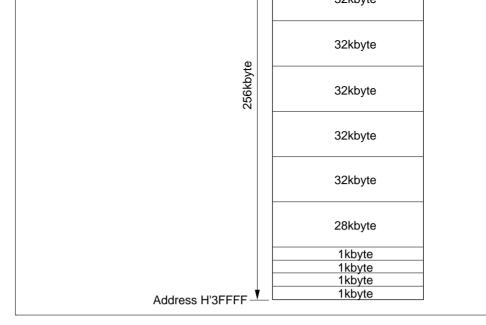

There are versions of on-chip ROM: mask ROM, PROM, and flash memory. The flash can be programmed with a programmer that supports SH7040 series programming, and be programmed and erased by software.

This hardware manual describes the SH7040 series hardware. Refer to the programming for a detailed description of the instruction set.

#### **Related Manual**

SH7040 series instructions

SH-1/SH-2/SH-DSP Programming Manual

Please consult your Renesas Technology sales representative for details for development environment system.

|            |         |        |        |         |                                                                        | 16 MHz                                         | 3.3 V                                 | HD6437040AVCF                                                                     |

|------------|---------|--------|--------|---------|------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------|

|            | SH7041A | A mask | 64 kB  | 32 bits | ±4LSB QFP2020-144 -20°C to 75° (Mid-Speed) QFP2020-144Cu*              | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6437041AF28<br>HD6437041AVF1                                                    |

|            |         |        |        |         | QFP2020-144Cu*                                                         | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6437041ACF2<br>HD6437041AVCF                                                    |

|            | SH7042  |        | 128 kB | 16 bits | ±15LSB QFP2020-112 -20°C to 75° (High-Speed)                           | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6437042F28<br>HD6437042VF16                                                     |

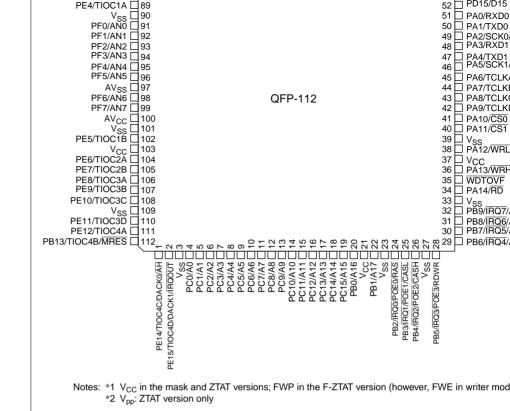

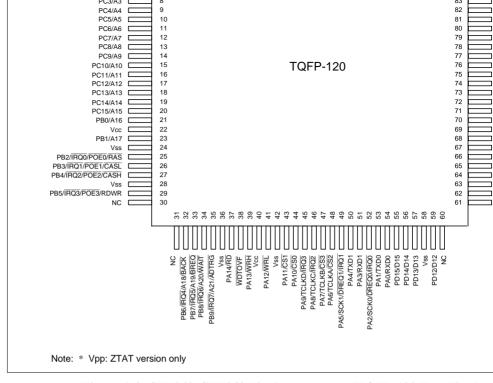

|            | SH7042A | A mask | 128 kB | 16 bits | ±4LSB QFP2020-112 -20°C to 75° (Mid-Speed) TQFP1414-120 QFP2020-112Cu* | 28 MHz<br>16 MHz<br>16 MHz                     | 5 V<br>3.3 V<br>3.3 V                 | HD6437042AF28<br>HD6437042AVF1<br>HD6437042AVX1                                   |

|            |         |        |        |         |                                                                        | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6437042ACF2<br>HD6437042AVCF                                                    |

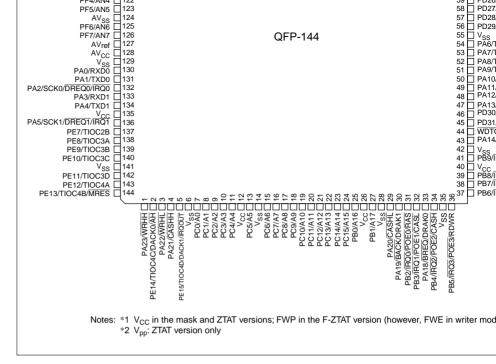

|            | SH7043  |        | 128 kB | 32 bits | ±15LSB QFP2020-144 -20°C to 75° (High-Speed)                           | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6437043F28<br>HD6437043VF16                                                     |

|            | SH7043A | A mask | 128 kB | 32 bits | ±4LSB QFP2020-144 -20°C to 75°<br>(Mid-Speed)<br>QFP2020-144Cu*        | 16 MHz                                         | 5 V<br>3.3 V                          | HD6437043AF28<br>HD6437043AVF1                                                    |

|            |         |        |        |         |                                                                        | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6437043ACF2<br>HD6437043AVCF                                                    |

|            | SH7044  | A mask | 256 kB | 16 bits | ±4LSB QFP2020-112 -20°C to 75°<br>(Mid-Speed)                          | C 28 MHz                                       | 5 V                                   | HD6437044F28                                                                      |

|            | SH7045  | A mask | 256 kB | 32bits  | ±4LSB QFP2020-144 -20°C to 75° (Mid-Speed)                             | C 28 MHz                                       | 5 V                                   | HD6437045F28                                                                      |

| ROM<br>ess | SH7040A | A mask |        | 16 bits | ±4LSB QFP2020-112 -20°C to 75° (Mid-Speed) TQFP1414-120 QFP2020-112Cu* | 28 MHz<br>16 MHz<br>16 MHz<br>28 MHz<br>16 MHz | 5 V<br>3.3 V<br>3.3 V<br>5 V<br>3.3 V | HD6417040AF28<br>HD6417040AVF1<br>HD6417040AVX1<br>HD6417040ACF2<br>HD6417040AVCF |

|            | SH7041A | A mask |        | 32 bits | ±4LSB QFP2020-144 -20°C to 75°<br>(Mid-Speed)<br>QFP2020-144Cu*        | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6417041AF28<br>HD6417041AVF1                                                    |

|            |         |        |        |         |                                                                        | 28 MHz<br>16 MHz                               | 5 V<br>3.3 V                          | HD6417041ACF2<br>HD6417041AVCF                                                    |

| _          | te an   |        |        |         | al.                                                                    |                                                |                                       |                                                                                   |

\* RAM emulation permitted

10001111dddddddd

RENESAS

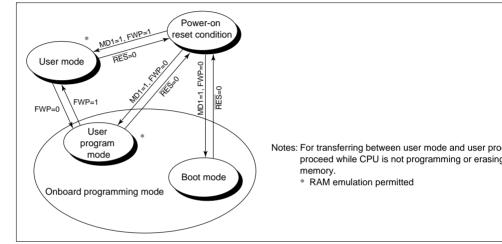

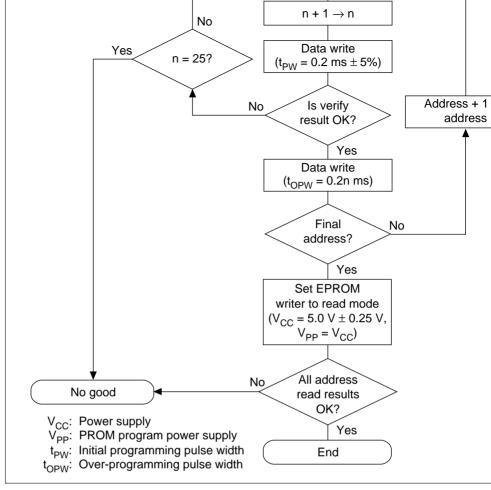

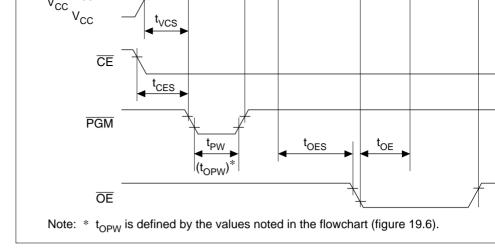

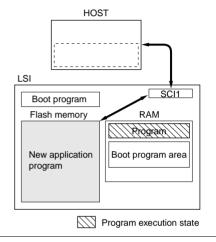

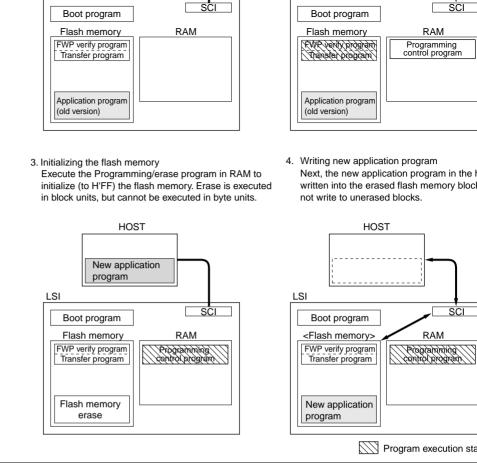

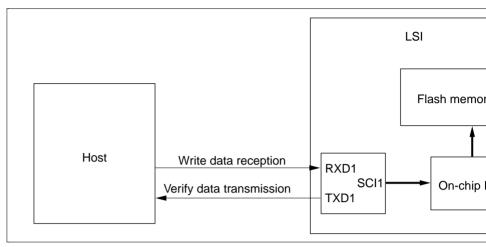

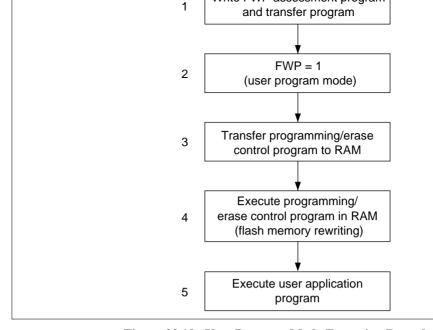

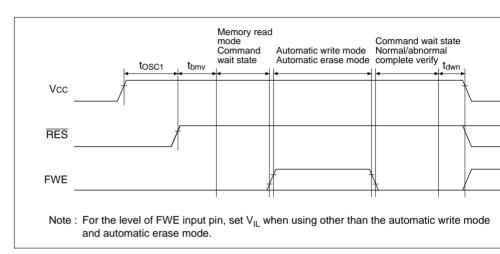

1.4 The F-ZTAT Version Onboard **Programming**

Memory

Figure 1.6 Condition

Transfer for Flash

2.4 Instruction Set

Table 2.16 Branch

by Classification

Instructions 4.2.3 Notes on

**Board Design** 4.5 Usage Notes

11.1.4 Register

Configuration Table 11.2 DMAC

Registers

memory.

proceed while CPU is not programming or erasing the fl

Table amended

BF/S label

Deleted

Newly added

Note \*5 deleted

42

70

83 to 85

218

Delayed branch, if T = 0, disp  $\times 2 +$

$PC \rightarrow PC$ ; if T = 1, nop

| Operation Register (DMAOR)                                                          |     | Bits 15–10—Reserved bits: Data are 0 when read value always be 0.              |

|-------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------|

|                                                                                     | 227 | Description amended                                                            |

|                                                                                     |     | • Bits 7–3—Reserved bits: Data are 0 when read. T value always be 0.           |

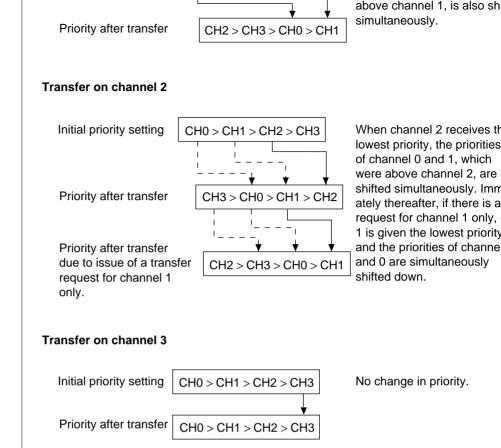

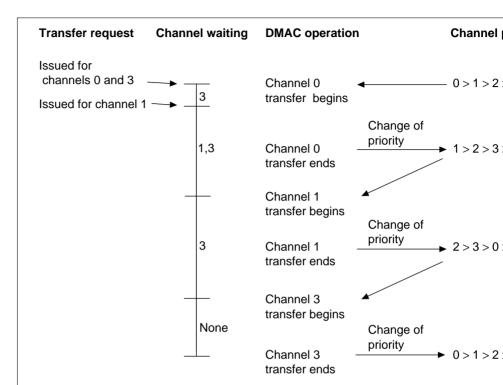

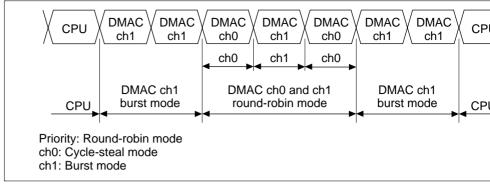

| 11.3.3 Channel Priority                                                             | 233 | Figure amended                                                                 |

| Figure 11.3 Round<br>Robin Mode                                                     |     | Channel 0 is given the lowest priority.                                        |

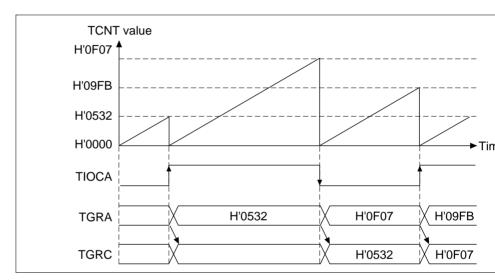

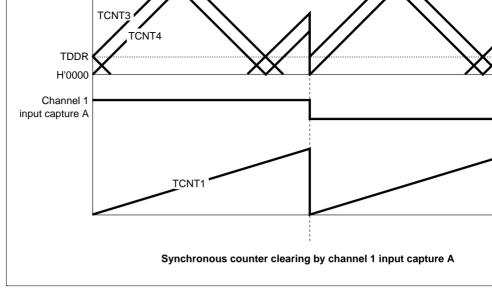

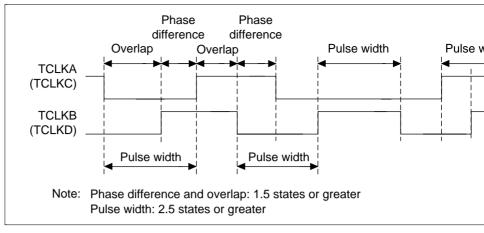

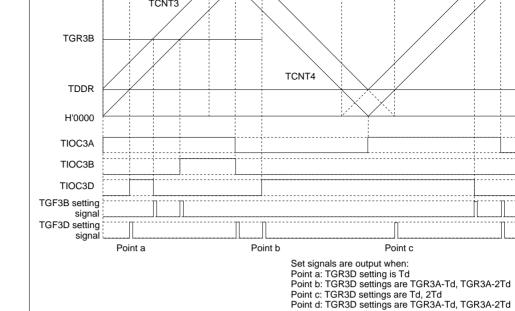

| 12.4.5 Cascade<br>Connection Mode                                                   | 337 | Figure amended                                                                 |

| Figure 12.23<br>Cascade Connection<br>Operation Example<br>(Phase Counting<br>Mode) |     | TCLKC                                                                          |

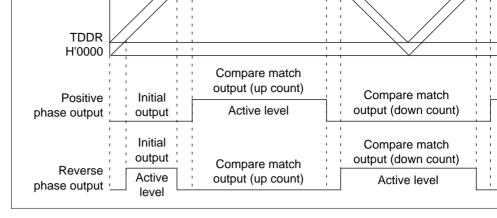

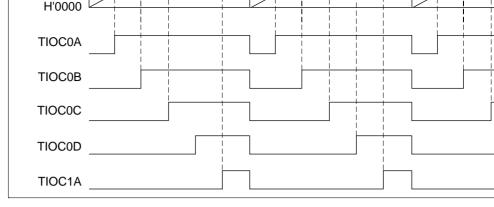

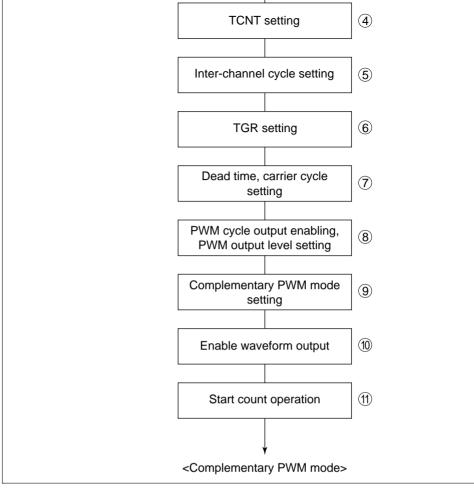

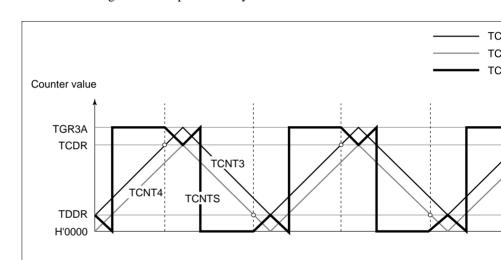

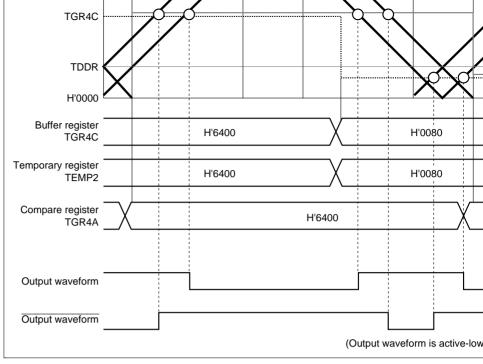

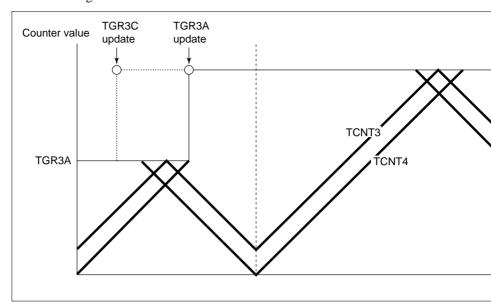

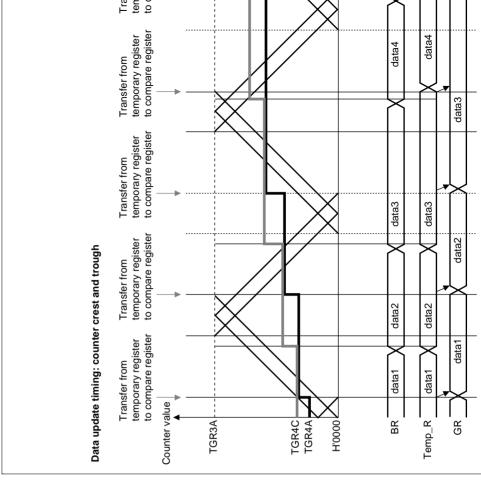

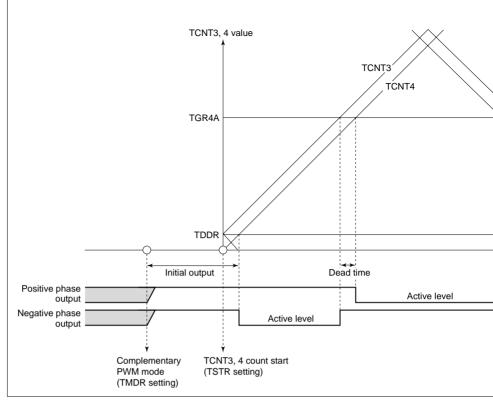

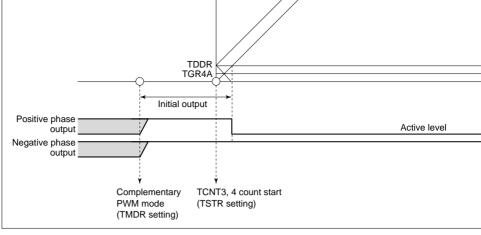

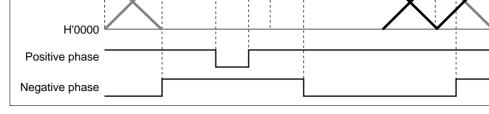

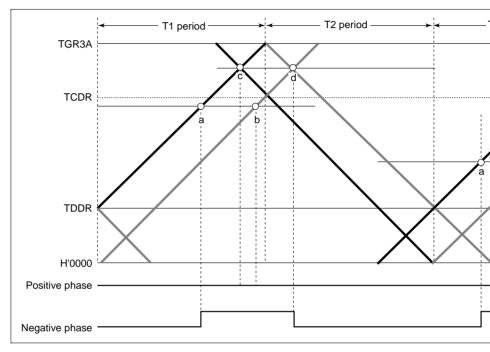

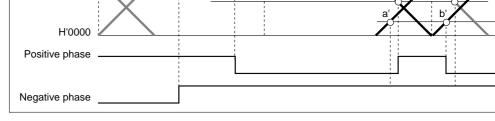

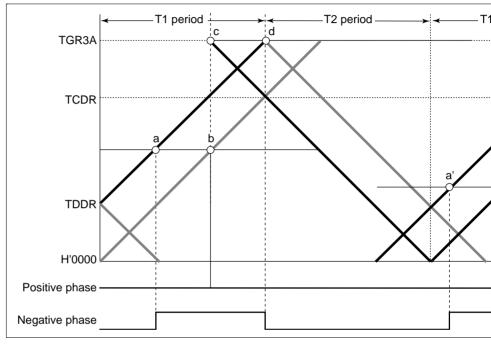

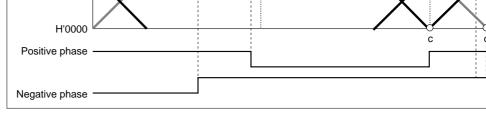

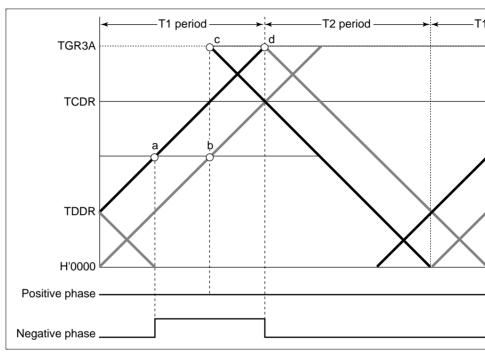

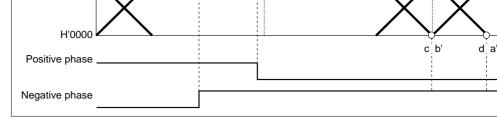

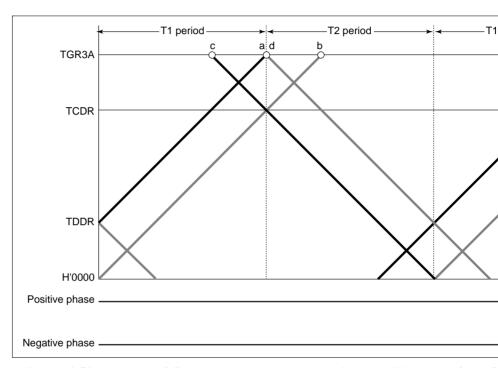

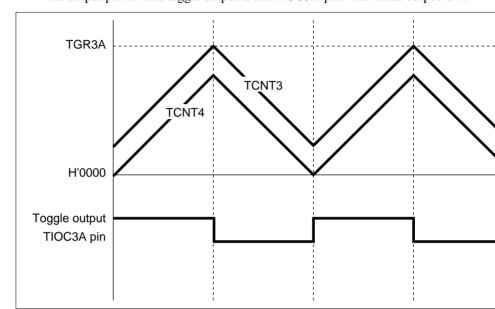

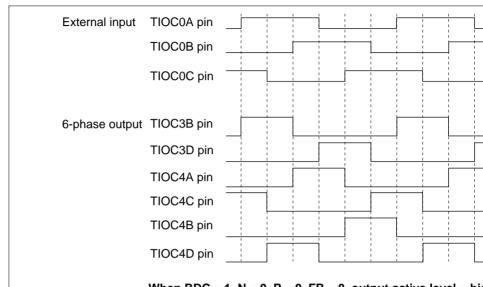

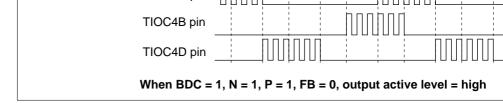

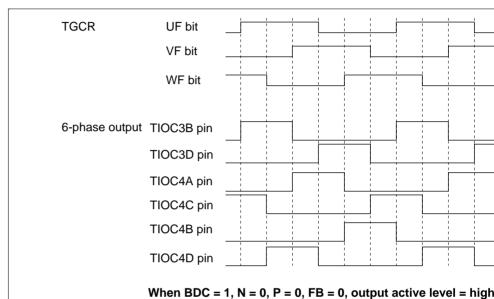

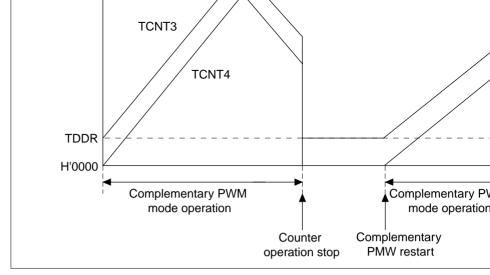

| 12.4.9<br>Complementary<br>PWM Mode                                                 | 373 | Figure amended  When BDC = 1, N = 0, P = 0, FB = 0, output active level = high |

| Figure 12.55<br>Example of Output<br>Phase Switching by<br>External Input (1)       |     |                                                                                |

| 14.2.0 Dit Nate                                                            | <del>4</del> 31 | rabic arrici | lacc  |         |           |    |   |   |

|----------------------------------------------------------------------------|-----------------|--------------|-------|---------|-----------|----|---|---|

| Register (BRR)                                                             |                 | Bit Rate     |       | 27      | .0336     |    |   |   |

| Table 14.3 Bit Rates                                                       |                 | (Bits/s)     | n     | N       | Error (%) |    |   |   |

| and BRR Settings in                                                        |                 | 110          | 3     | 119     | 0.00      |    |   |   |

| Asynchronous Mode                                                          |                 | 150          | 3     | 87      | 0.00      |    |   |   |

| (cont)                                                                     |                 | 300          | 2     | 175     | 0.00      |    |   |   |

|                                                                            |                 | 600          | 1     | 87      | 0.00      |    |   |   |

|                                                                            |                 | 1200         | 1     | 175     | 0.00      |    |   |   |

|                                                                            |                 | 2400         | 1     | 87      | 0.00      |    |   |   |

|                                                                            |                 | 4800         | 0     | 175     | 0.00      |    |   |   |

|                                                                            |                 | 9600         | 0     | 87      | 0.00      |    |   |   |

|                                                                            |                 | 14400        | 0     | 58      | -0.56     |    |   |   |

|                                                                            |                 | 19200        | 0     | 43      | 0.00      |    |   |   |

|                                                                            |                 | 28800        | 0     | 28      | 1.15      |    |   |   |

|                                                                            |                 | 31250        | 0     | 26      | 0.12      |    |   |   |

|                                                                            |                 | 38400        | 0     | 21      | 0.00      |    |   |   |

| Table 14.4 Bit Rates and BRR Settings in                                   | 495             | Table amer   | ndec  | l       | _         | _  | _ | _ |

| Clocked                                                                    |                 | 5M           |       |         | 0         | 0* | _ | _ |

| Synchronous Mode                                                           |                 | 7M           |       |         |           |    | _ | _ |

| (cont)                                                                     |                 |              |       |         |           |    |   |   |

| 14.3.4 Clock<br>Synchronous<br>Operation<br>Figure 14.22<br>Example of SCI | 529             | Figure ame   | nde   |         |           |    |   |   |

| Receive Operation                                                          |                 |              | \ BIL | <u></u> |           |    |   |   |

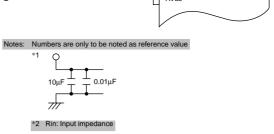

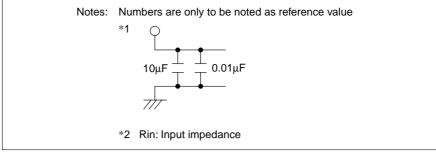

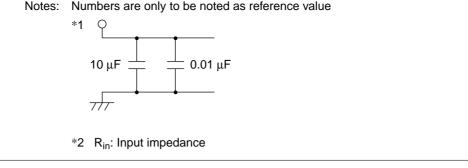

|                                                                                                                                  |     |          | Kin. input impedan               |                                               |                                |

|----------------------------------------------------------------------------------------------------------------------------------|-----|----------|----------------------------------|-----------------------------------------------|--------------------------------|

| 16.7.2 Handling of Analog Input Pins                                                                                             | 585 | Note an  |                                  |                                               |                                |

| Figure 16.8 Example of Analog Input Pin Protection Circuit                                                                       |     | Notes:   | Numbers a                        | re only to be noted as re                     | eference value                 |

| 19.2 Port A                                                                                                                      | 649 | Table a  | mended                           |                                               |                                |

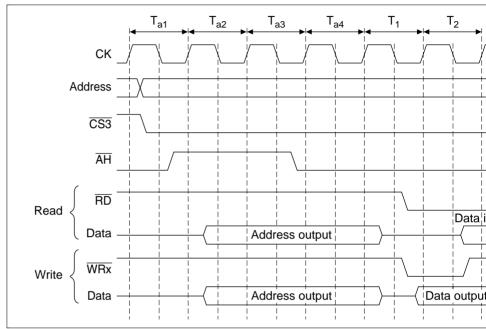

| Table 19.2 Port A,<br>FP-144 Version                                                                                             |     |          | D)/AH (output)<br>D)/CK (output) | PA16 (I/O)/AH (output) PA15 (I/O)/CK (output) | PA16 (I/O)<br>PA15 (I/O)/CK (o |

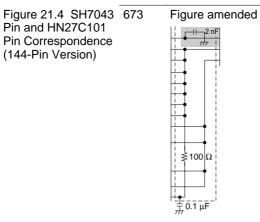

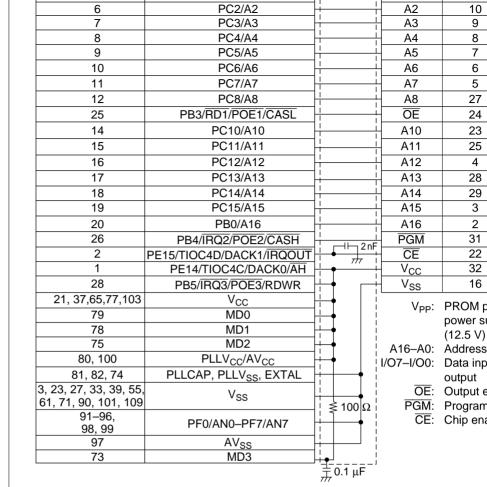

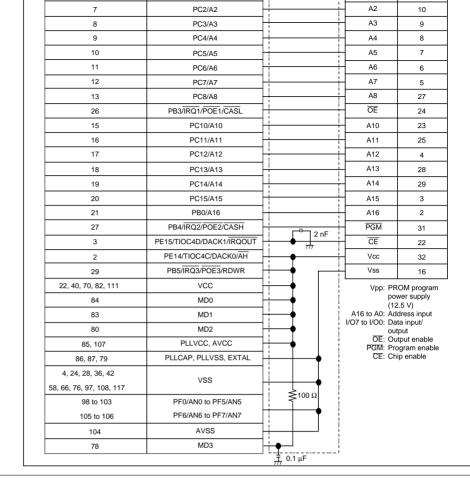

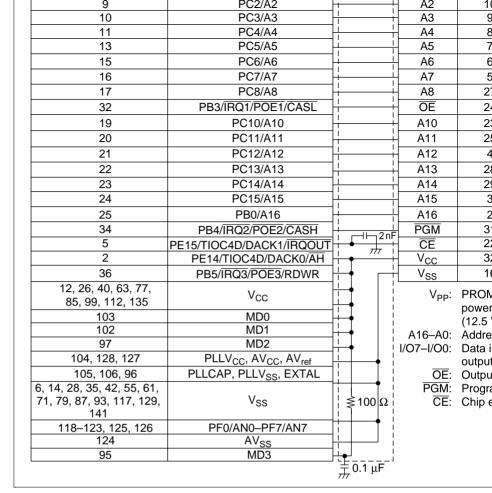

| 21.2.2 Socket Adapter Pin Correspondence and Memory Map Figure 21.2 SH7042 Pin and HN27C101 Pin Correspondence (112-Pin Version) | 671 | Figure a | 2                                |                                               |                                |

683

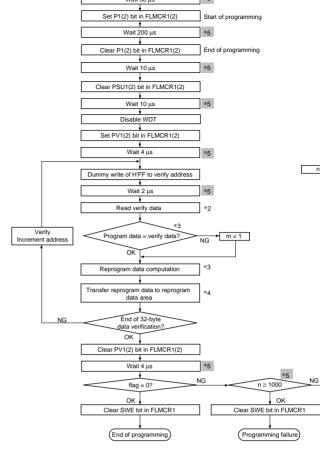

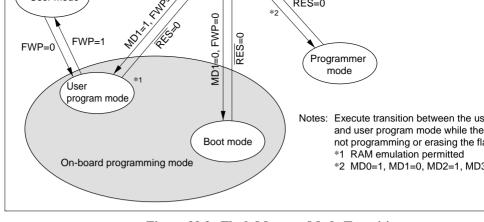

22.2.2 Mode Transition Diagram Figure 22.2 Flash Memory Mode Transitions

Note amended

Execute transition between the user mode and user prog while the CPU is not programming or erasing the flash me

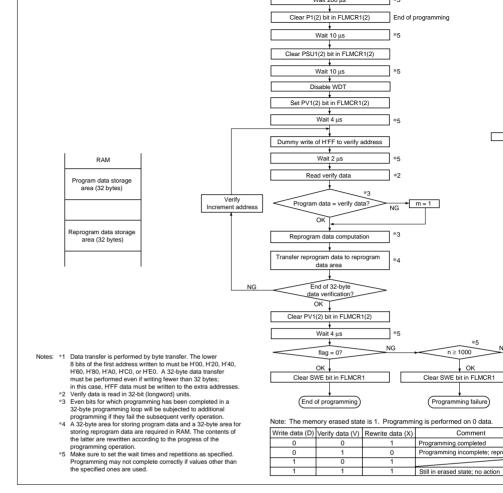

#### Note \*5 added.

\*5 Make sure to set the wait times and repetitions as specified. Programming may not complete correctly if values other than the specified ones are used.

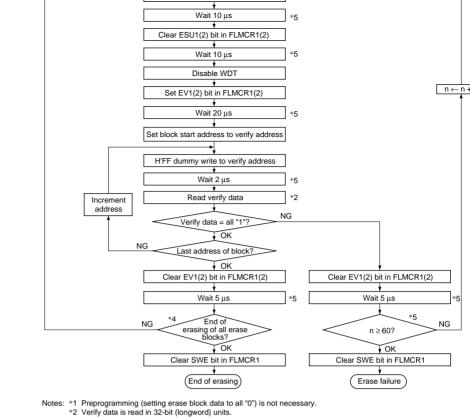

Notes: \*1 Preprogramming (setting erase block data to all "0") is not necessary. \*2 Verify data is read in 32-bit (longword) units.

- \*3 Set only one bit in EBR1(2). More than one bit cannot be set.

\*4 Erasing is performed in block units. To erase a number of blocks, each block must be erased in to \*5 Make sure to set the wait times and repetitions as specified. Erasing may not complete correctly in than the specified ones are used.

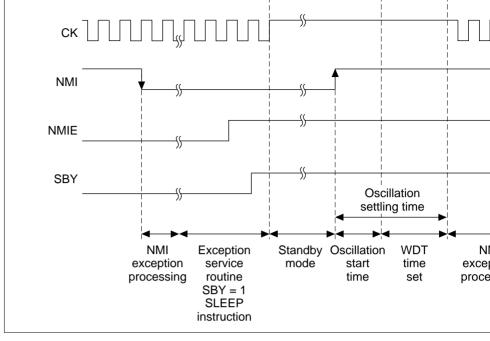

24.4.2 Canceling the 747 Standby Mode

Cancellation by a Manual Reset deleted

25. Electrical Characteristics (5V, 33.3 MHz Version)

Deleted

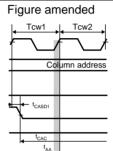

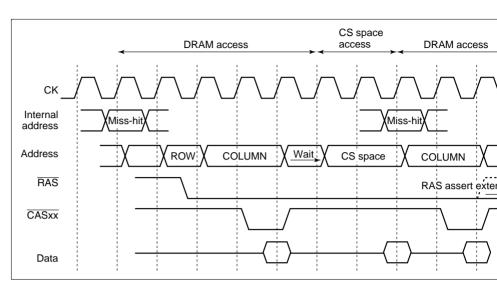

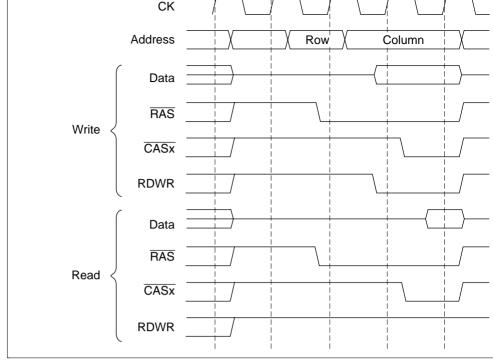

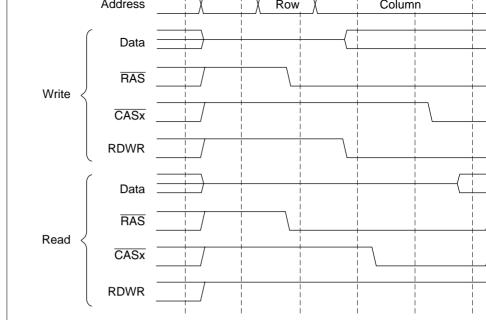

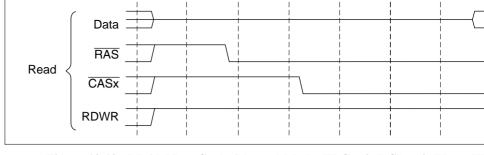

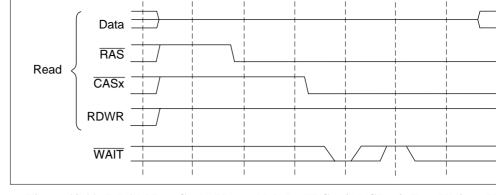

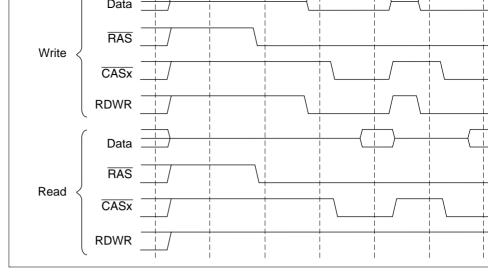

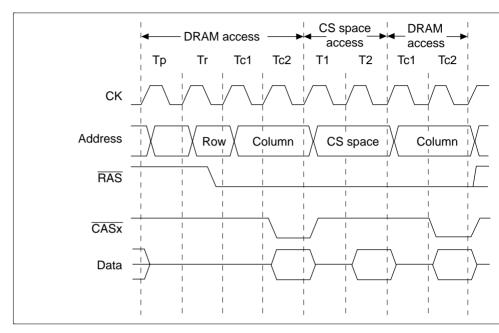

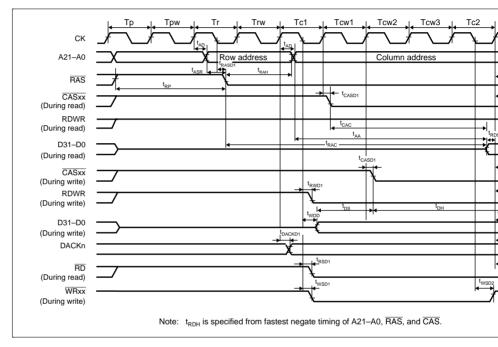

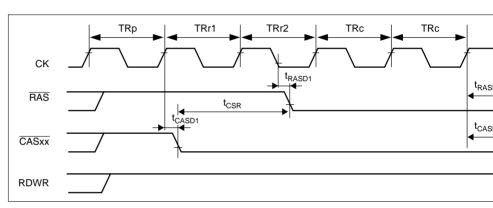

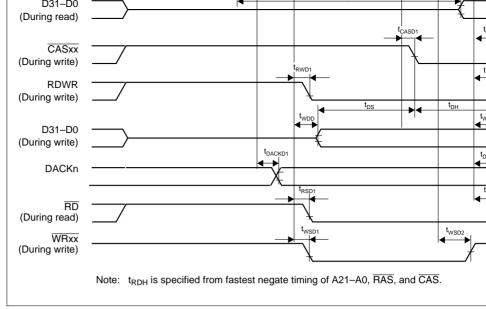

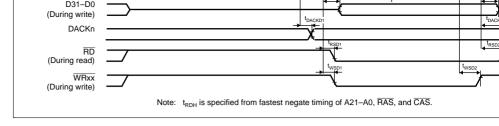

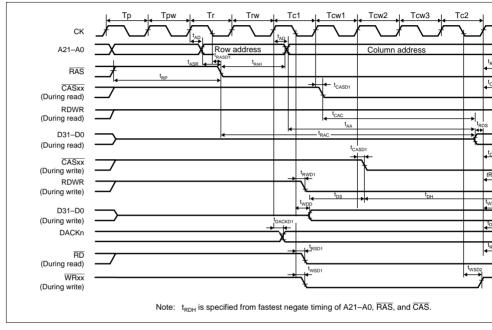

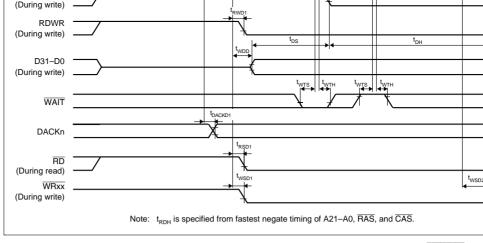

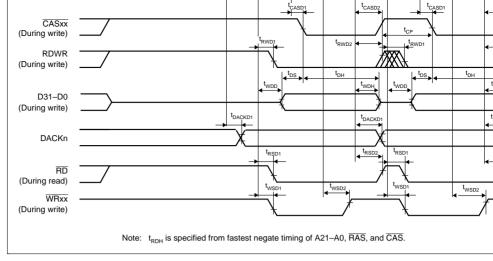

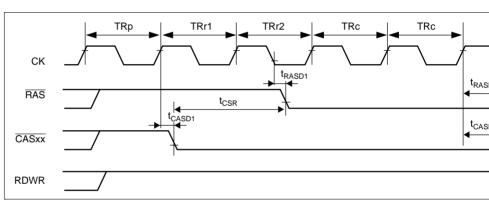

Figure 25.12 DRAM Cycle (Normal Mode, 1 Wait, TPC=0, RCD=0)

Figure 25.13 DRAM 764

Cycle (Normal Mode, 2 Waits, TPC=1, RCD=1)

|                                                                          |     | Analog<br>supply   | .,                                   | А                                     | I <sub>cc</sub>                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                          | 8                                      | mA                                     | f = 16.7MH                                                             |

|--------------------------------------------------------------------------|-----|--------------------|--------------------------------------|---------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------|----------------------------------------|------------------------------------------------------------------------|

|                                                                          |     | current            |                                      | A                                     | I <sub>ref</sub>                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.5                                        | 1*3                                    | mA                                     | QFP144 ve                                                              |

|                                                                          |     | *3 2 mA i          | n the A mask                         | version o                             | of MAS                               | K produ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cts.                                       |                                        |                                        |                                                                        |

| 26.3.2 Control                                                           | 786 | Note ar            | mended                               |                                       |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |                                        |                                        |                                                                        |

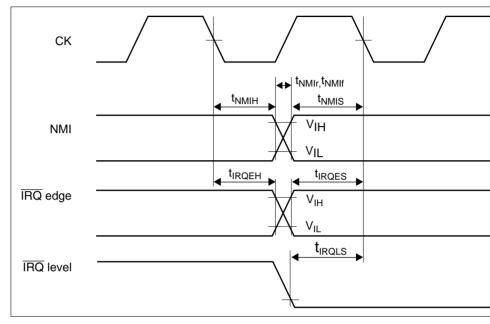

| Signal Timing                                                            |     | Notes:             | *1 SH7                               | 042/43                                | ZTA                                  | AT (ex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cludi                                      | ng A r                                 | nask)                                  | are 3.2V                                                               |

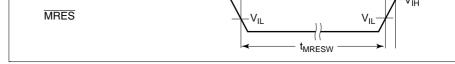

| Table 26.5 Control<br>Signal Timing                                      |     |                    | are a<br>show<br>have<br>BRE<br>setu | asynch<br>vn here<br>produ<br>Q) or o | ronce<br>are<br>iced<br>clock<br>are | ous inperior in proving the contract of the co | outs,<br>ided,<br>ges a<br>for Ni<br>rovid | but wh<br>the sig<br>t clock<br>MI and | nen the<br>gnals a<br>rise (<br>I IRQ7 | Q7-IRQ<br>e setup ti<br>are consi<br>for RES,<br>-IRQ0).<br>ion is del |

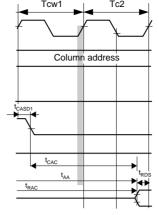

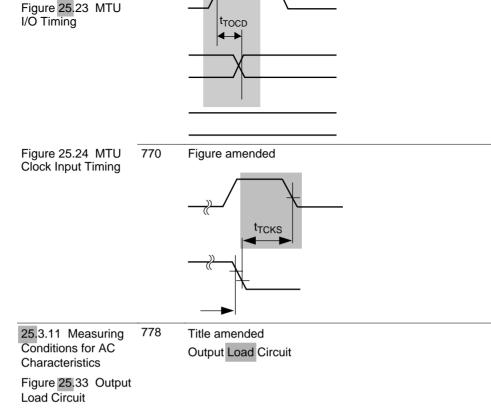

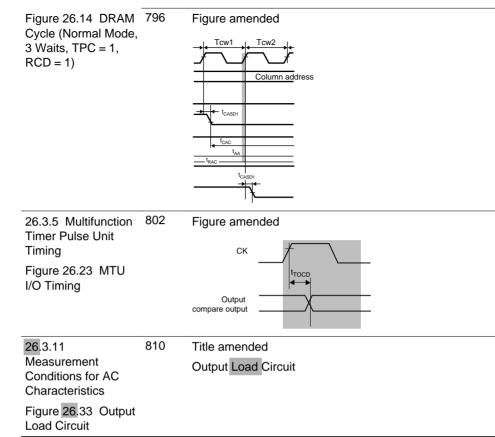

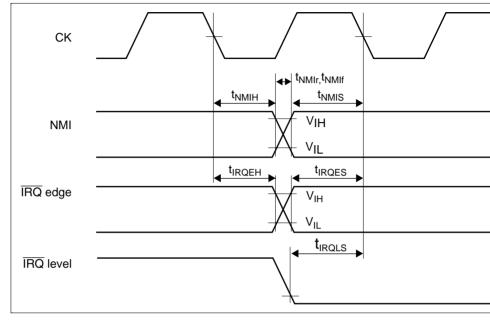

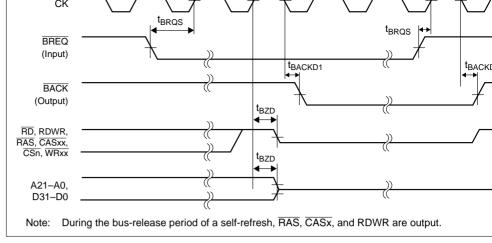

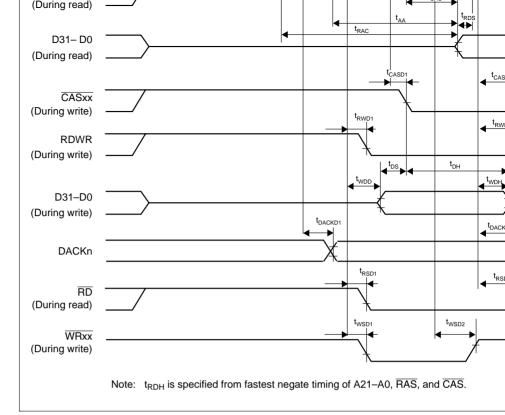

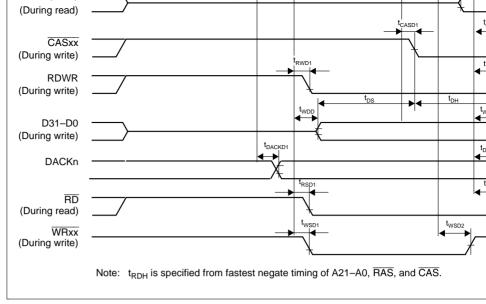

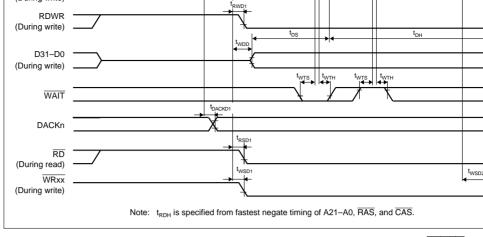

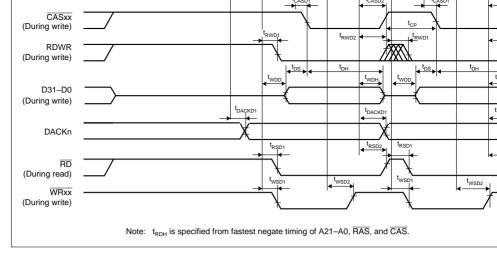

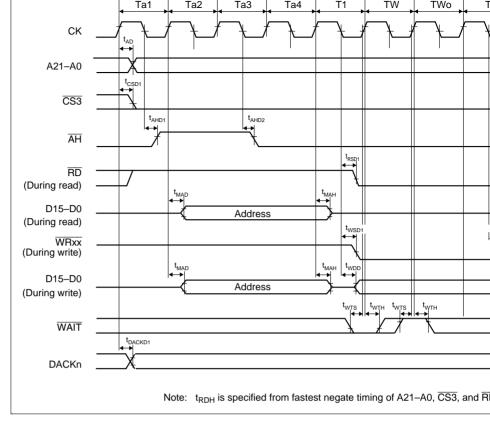

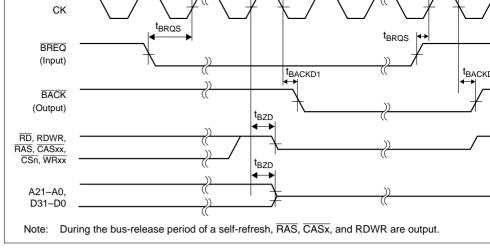

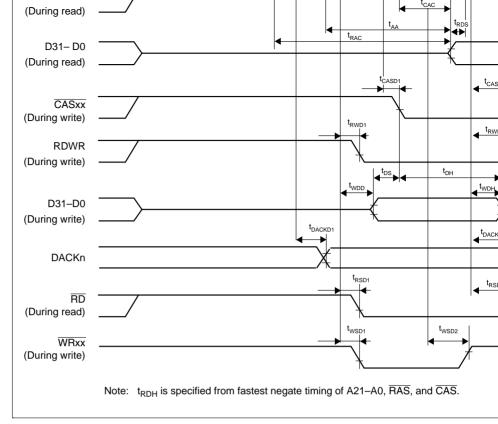

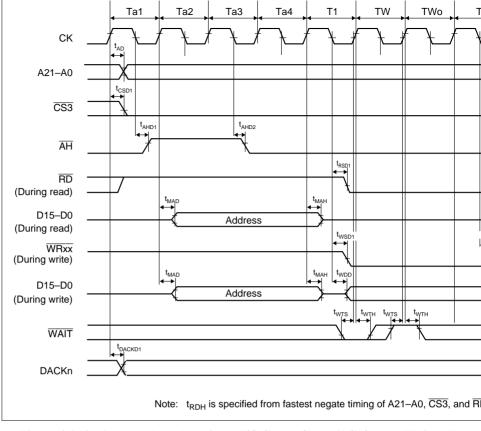

| 26.3.3 Bus Timing                                                        | 795 | Figure             | amended                              | t                                     |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |                                        |                                        |                                                                        |

| Figure 26.12 DRAM<br>Cycle (Normal Mode,<br>1 Wait, TPC = 0,<br>RCD = 0) |     | t <sub>CASD1</sub> | tcac                                 | n addres                              | ss ·                                 | <b>*</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |                                        |                                        |                                                                        |

|                                                                          |     | t <sub>RAC</sub>   | t <sub>AA</sub>                      |                                       |                                      | <b>★</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |                                        |                                        |                                                                        |

| Class          | Pin Name                     | Power-C | nManual | Standby | y Sleep | Release | Ri |

|----------------|------------------------------|---------|---------|---------|---------|---------|----|

| Clock          | CK                           | 0       | 0       | H*1     | 0       | 0       | 0  |

| System         | RES                          | 1       | I       | I       | I       | I       | I  |

| control        | MRES                         | Z*4     | I       | Z       | ı       | I       | Z  |

|                | WDTOVF                       | O*3     | O*3     | 0       | 0       | 0       | 0  |

|                | BREQ                         | Z*4     | I       | Z       | I       | Ī       | I  |

|                | BACK                         | Z*4     | 0       | Z       | 0       | L       | L  |

| Interrupt      | NMI                          | I       | I       | I       | Ī       | I       | I  |

|                | IRQ0-IRQ7                    | Z*4     | I       | Z       | I       | Ī       | Z  |

|                | IRQOUT (PD30)                | Z*4     | 0       | H*1     | Н       | 0       | H³ |

|                | IRQOUT (PE15)                | Z*4     | 0       | Z       | Н       | 0       | Z  |

| Address<br>bus | A0-A21                       | O*2     | 0       | Z       | 0       | Z       | Z  |

| Data bus       | D0-D31                       | Z*4     | I/O     | Z       | I/O     | Z       | Z  |

| Bus            | WAIT                         | Z*4     | 1       | Z       | Ī       | Z       | Z  |

| control        | RD/WR, RAS                   | Z*4     | 0       | 0       | 0       | Z       | Z  |

|                | CASH, CASL,<br>CASLH, CASLL  | Z*4     | 0       | 0       | 0       | Z       | Z  |

|                | RD                           | Н       | 0       | Z       | 0       | Z       | Z  |

|                | CS0, CS1                     | Н       | 0       | Z       | 0       | Z       | Z  |

|                | CS2, CS3                     | Z*4     | 0       | Z       | 0       | Z       | Z  |

|                | WRHH, WRHL, WRH, WRL         | Н       | 0       | Z       | 0       | Z       | Z  |

|                | ĀH                           | Z*4     | 0       | Z       | 0       | Z       | Z  |

| DMAC           | DACK0, DACK1<br>(PD26, PD27) | Z*4     | 0       | O*1     | 0       | 0       | O, |

|                | DACK0, DACK1                 | Z*4     | 0       | Z       | 0       | 0       | Z  |

|                | (PE14, PE15)                 |         |         |         |         |         |    |

|                |                              | Z*4     | 0       | O*1     | 0       | 0       | 0  |

woods burning reset, Power-Down, and Bus Right Release Modes (144 Pin)

|           | RXD0-RXD1                                                                                                                                                                                                                     | Z*4 | ī   | Z   | 1 | 1 2   |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---|-------|--|

| A/D       | ADTRG                                                                                                                                                                                                                         | Z*4 | I   | Z   | 1 | l Z   |  |

| converter | AN0-AN7                                                                                                                                                                                                                       | Z   | I   | Z   | 1 | l Z   |  |

| I/O Port  | PA0-PA23                                                                                                                                                                                                                      | Z*4 | I/O | K*1 | K | I/O F |  |

|           | PB0-PB9                                                                                                                                                                                                                       | _   |     |     |   |       |  |

|           | PC0-PC15                                                                                                                                                                                                                      | _   |     |     |   |       |  |

|           | PD0-PD31                                                                                                                                                                                                                      | _   |     |     |   |       |  |

|           | PE0-PE8,PE10                                                                                                                                                                                                                  | _   |     |     |   |       |  |

|           | PE9,PE11-PE15                                                                                                                                                                                                                 | Z*4 | I/O | Z   | K | I/O 2 |  |

|           | PF0-PF17                                                                                                                                                                                                                      | Z   | I   | Z   | I | 1 2   |  |

| Notes: 1. | Notes: 1. There are instances where bus right release and transition to software s occur simultaneously due to the timing between BREQ and internal oper cases, standby mode results, but the standby state may be different. |     |     |     |   |       |  |

No

The initial pin states depend on the mode. See section 18, Pin Function

(PFC), for details.

- 2. I: Input, O: Output, H: High-level output, L: Low-level output, Z: High imp K: Input pin with high impedance, output pin mode maintained.

- high impedance.

- \*2 A21-A18 will become input ports after power-on reset.

- \*3 Input in the SH7044/SH7045 F-ZTAT version. \*4 General use I/O ports PAn, PBn, PCn, PDn, and PEn, as well as pins m them, are unstable during the  $\overline{\mbox{RES}}$  setup time (t\_RESS) immediately after goes to low level.

\*1 If the standby control register port high-impedance bits are set to 1, outp

| Address<br>bus | A0-A21                                                               | Owz | 0   | Z   | 0   | Z   | Z  |

|----------------|----------------------------------------------------------------------|-----|-----|-----|-----|-----|----|

| Data bus       | D0-D31                                                               | Z*4 | I/O | Z   | I/O | Z   | Z  |

| Bus            | WAIT                                                                 | Z*4 | I   | Z   | Ī   | Z   | Z  |

| control        | RDWR, RAS                                                            | Z*4 | 0   | 0   | 0   | Z   | Z  |

|                | CASH, CASL                                                           | Z*4 | 0   | 0   | 0   | Z   | Z  |

|                | RD                                                                   | Н   | 0   | Z   | 0   | Z   | Z  |

|                | CS0, CS1                                                             | Н   | 0   | Z   | 0   | Z   | Z  |

|                | CS2, CS3                                                             | Z*4 | 0   | Z   | 0   | Z   | Z  |

|                | WRH, WRL                                                             | Н   | 0   | Z   | 0   | Z   | Z  |

|                | ĀH                                                                   | Z*4 | 0   | Z   | 0   | Z   | Z  |

| DMAC           | DACK0-DACK1                                                          | Z*4 | 0   | Z   | 0   | 0   | Z  |

|                | DRAK0-DRAK1                                                          | Z*4 | 0   | Z   | 0   | 0   | Z  |

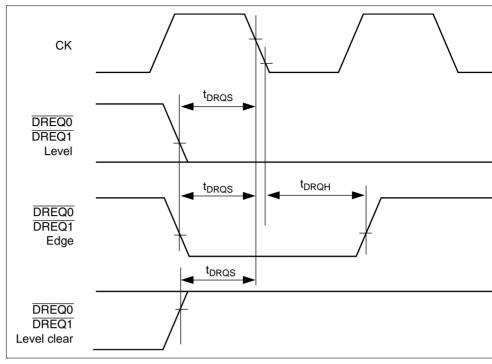

|                | DREQ0-DREQ1                                                          | Z*4 | I   | Z   | I   | 1   | Z  |

| MTU            | TIOC0A-TIOC0D,<br>TIOC1A-TIOC1D,<br>TIOC2A-TIOC2D,<br>TIOC3A, TIOC3C | Z*4 | I/O | K*1 | I/O | I/O | K* |

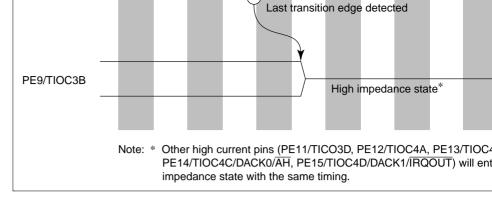

|                | TIOC3B,TIOC3D,<br>TIOC4A-TIOC4D                                      | Z*4 | I/O | Z   | I/O | I/O | Z  |

|                | TCLKA-TCLKD                                                          | Z*4 | Ī   | Z   | Ī   | Ī   | Z  |

|                |                                                                      |     |     |     |     |     |    |

|        | PC0-PC15                            | _   |     |   |   |     |   |

|--------|-------------------------------------|-----|-----|---|---|-----|---|

|        | PD0-PD15                            |     |     |   |   |     |   |

|        | PE0-PE8-PE10                        | _   |     |   |   |     |   |

|        | PE9,PE11-PE15                       | Z*4 | I/O | Z | K | I/O | 2 |

|        | PF0-PF7                             | Z   | Ī   | Z | Ī | Ī   | Ž |

| Notes: | There are instance occur simultaneo |     |     |   |   |     |   |

cases, standby mode results, but the standby state may be different. The initial pin states depend on the mode. See section 18, Pin Function (PFC), for details. 2. I: Input, O: Output, H: High-level output, L: Low-level output, Z: High imp

- K: Input pin with high impedance, output pin mode maintained. \*1 If the standby control register port high-impedance bits are set to 1, outp

- high impedance.

- \*2 A21-A18 will become input ports after power-on reset.

- \*3 Input in the SH7044/SH7045 F-ZTAT version. \*4 General use I/O ports PAn, PBn, PCn, PDn, and PEn, as well as pins m them, are unstable during the  $\overline{\text{RES}}$  setup time ( $t_{\text{RESS}}$ ) immediately after goes to low level.

|         | Z-TAT<br>version    | -       | HD6477042F28<br>HD6477042VF16                     | HD6477042F28<br>HD6477042VF16                                    | QFP2020-112<br>QFP2020-112                 |

|---------|---------------------|---------|---------------------------------------------------|------------------------------------------------------------------|--------------------------------------------|

| SH7042A | Mask ROM<br>verion  | A MASK  | HD6437042AF28<br>HD6437042AVF16<br>HD6437042AVX16 | HD6437042A(***)F28<br>HD6437042A(***)VF16<br>HD6437042A(***)VX16 | QFP2020-112<br>QFP2020-112<br>TQFP1414-120 |

|         |                     |         | HD6437042ACF28<br>HD6437042AVCF16                 | HD6437042A(***)CF28<br>HD6437042A(***)VCF16                      | QFP2020-112Cu*1<br>QFP2020-112Cu*1         |

| Product |                     | Mask    |                                                   |                                                                  |                                            |

| Туре    |                     | Version | Product Code                                      | Mark Code                                                        | Package                                    |

| SH7042A | Z-TAT<br>version    | A MASK  | HD6477042AF28<br>HD6477042AVF16<br>HD6477042AVX16 | HD6477042AF28<br>HD6477042AVF16<br>HD6477042AVX16                | QFP2020-112<br>QFP2020-112<br>TQFP1414-120 |

|         |                     |         | HD6477042ACF28<br>HD6477042AVCF16                 | HD6477042ACF28<br>HD6477042AVCF16                                | QFP2020-112Cu*1<br>QFP2020-112Cu*1         |

| SH7043  | Mask ROM<br>version | =       | HD6437043F28<br>HD6437043VF16                     | HD6437043(***)F28<br>HD6437043(***)VF16                          | QFP2020-144<br>QFP2020-144                 |

|         | Z-TAT<br>version    | -       | HD6477043F28<br>HD6477043VF16                     | HD6477043F28<br>HD6477043VF16                                    | QFP2020-144<br>QFP2020-144                 |

| SH7043A | Mask ROM<br>version | A MASK  | HD6437043AF28<br>HD6437043AVF16                   | HD6437043A(***)F28<br>HD6437043A(***)VF16                        | QFP2020-144<br>QFP2020-144                 |

|         |                     |         | HD6437043ACF28<br>HD6437043AVCF16                 | HD6437043A(***)CF28<br>HD6437043A(***)VCF16                      | QFP2020-144Cu*1<br>QFP2020-144Cu*1         |

|         | Z-TAT<br>version    | A MASK  | HD6477043AF28<br>HD6477043AVF16                   | HD6477043AF28<br>HD6477043AVF16                                  | QFP2020-144<br>QFP2020-144                 |

|         |                     |         | HD6477043ACF28<br>HD6477043AVCF16                 | HD6477043ACF28<br>HD6477043AVCF16                                | QFP2020-144Cu*1<br>QFP2020-144Cu*1         |

| SH7044  | Mask ROM<br>version | A MASK  | HD6437044F28                                      | HD6437044(***)F28                                                | QFP2020-112                                |

|         | F-ZTAT<br>version   |         | HD64F7044F28                                      | HD64F7044F28                                                     | QFP2020-112                                |

| SH7045  | Mask ROM            | A MASK  | HD6437045F28                                      | HD6437045(***)F28                                                | QFP2020-144                                |

HD64F7045F28

HD64F7045F28

HD6417041AVCF16 HD6417041AVCF16

HD6437042 (\*\*\*)F28

HD6437042 (\*\*\*)VF16

HD6437042F28

HD6437042VF16

QFP2020-144Cu\*1 H

Н

Н

QFP2020-112

QFP2020-112

QFP2020-144

F-ZTAT version

version

SH7042

Mask ROM -

verion

(\*\*\*) is the ROM code. NoteS: 1. Package with Copper used as the lead material.

2. \*\*\* in the Order Model No. is the ROM code, consisting of a letter and a number (ex. E00). The letter indicates the voltage and frequency, as sho

- E, F, G, H: 5.0 V, 28 MHz • P, Q, R: 3.3 V, 16 MHz

| Section 2                   |         | CPU                         |

|-----------------------------|---------|-----------------------------|

| 2.1                         | Registe | er Configuration            |

|                             | 2.1.1   | General Registers (Rn)      |

|                             | 2.1.2   | Control Registers           |

|                             | 2.1.3   | System Registers            |

| 2.1.4 Initial Values of Reg |         | Initial Values of Registers |

| 2.2                         | Data Fo | ormats                      |

|                             | 2.2.1   | Data Format in Registers    |

|                             | 2.2.2   | Data Format in Memory       |

|                             | 2.2.3   | Immediate Data Format       |

| 2.3                         | Instruc | tion Features               |

|                             | 2.3.1   | RISC-Type Instruction Set   |

|                             | 2.3.2   | Addressing Modes            |

|                             | 2.3.3   | Instruction Format          |

| 2.4                         | Instruc | tion Set by Classification  |

|                             |         |                             |

Processing States .....

Operating Modes, Types, and Selection.....

Explanation of Operating Modes.....

Pin Configuration.....

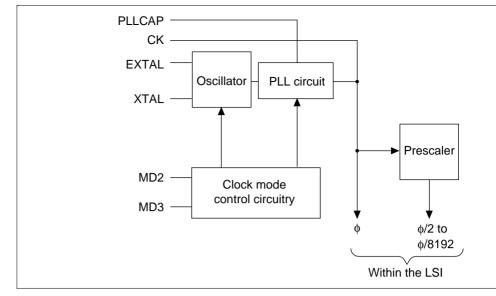

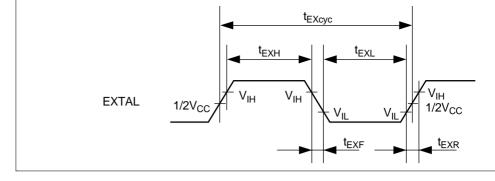

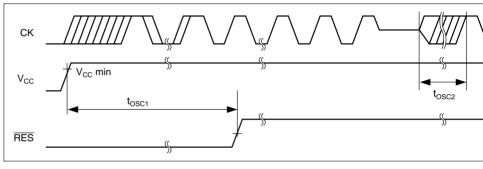

Oscillator.....

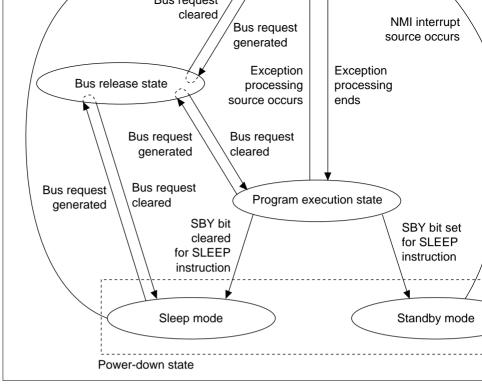

State Transitions

Power-Down State

Operating Modes.....

Clock Pulse Generator (CPG)

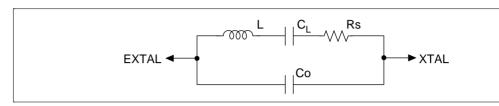

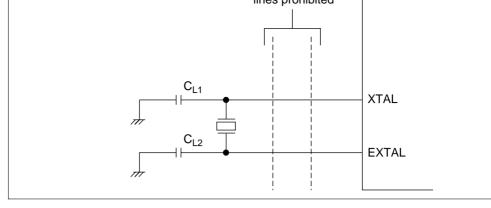

Connecting a Crystal Oscillator.....

4.1 Overview 4.1.1 Block Diagram

2.5

3.1

3.2

3.3

4.2

2.5.1

2.5.2

Section 3

Section 4

4.2.1

|      | 5.2.2   | Manual Reset                                                            |

|------|---------|-------------------------------------------------------------------------|

| 5.3  | Addres  | ss Errors                                                               |

|      | 5.3.1   | Address Error Exception Processing                                      |

| 5.4  | Interru | pts                                                                     |

|      | 5.4.1   | Interrupt Priority Level                                                |

|      | 5.4.2   | Interrupt Exception Processing                                          |

| 5.5  | Except  | tions Triggered by Instructions                                         |

|      | 5.5.1   | Trap Instructions                                                       |

|      | 5.5.2   | Illegal Slot Instructions                                               |

|      | 5.5.3   | General Illegal Instructions                                            |

| 5.6  | When    | Exception Sources Are Not Accepted                                      |

|      | 5.6.1   | Immediately after a Delayed Branch Instruction                          |

|      | 5.6.2   | Immediately after an Interrupt-Disabled Instruction                     |

| 5.7  | Stack S | Status after Exception Processing Ends                                  |

| 5.8  | Notes   | on Use                                                                  |

|      | 5.8.1   | Value of Stack Pointer (SP)                                             |

|      | 5.8.2   | Value of Vector Base Register (VBR)                                     |

|      | 5.8.3   | Address Errors Caused by Stacking of Address Error Exception Processing |

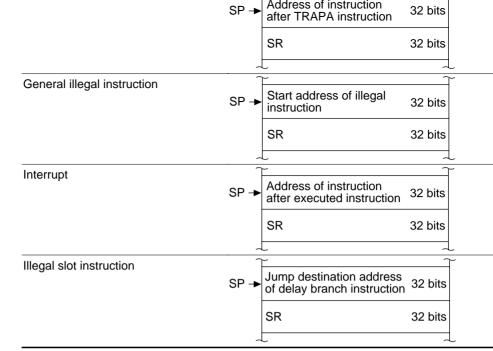

| Sect | ion 6   | Interrupt Controller (INTC)                                             |

| 6.1  | Overvi  | iew                                                                     |

|      | 6.1.1   | Features                                                                |

|      | 6.1.2   | Block Diagram                                                           |

|      | 6.1.3   | Pin Configuration                                                       |

|      | 6.1.4   | Register Configuration                                                  |

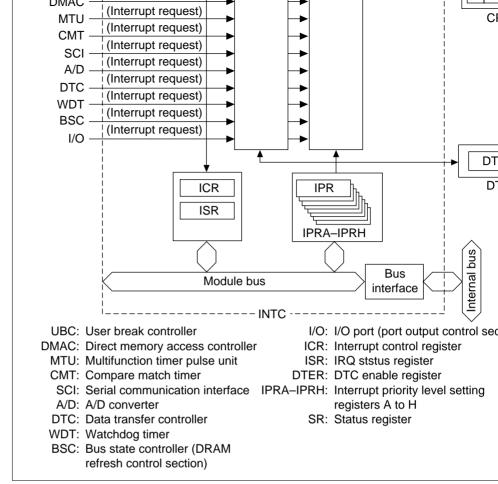

| 6.2  | Interru | pt Sources                                                              |

Resets

Power-On Reset

NMI Interrupts.....

User Break Interrupt

RENESAS

5.2

5.2.1

6.2.1 6.2.2

ii

|      | 6.6.3  | Handling DTC Activating Sources but Not CPU Interrupt or DMAC Activating Sources |

|------|--------|----------------------------------------------------------------------------------|

|      | 6.6.4  | Treating CPU Interrupt Sources but Not DTC                                       |

|      |        | or DMAC Activating Sources                                                       |

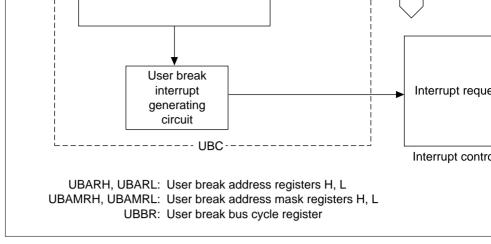

| Sect | tion 7 | User Break Controller (UBC)                                                      |

| 7.1  | Overvi | iew                                                                              |

|      | 7.1.1  | Features                                                                         |

|      | 7.1.2  | Block Diagram                                                                    |

|      | 7.1.3  | Register Configuration                                                           |

| 7.2  | Regist | er Descriptions                                                                  |

|      | 7.2.1  | User Break Address Register (UBAR)                                               |

|      | 7.2.2  | User Break Address Mask Register (UBAMR)                                         |

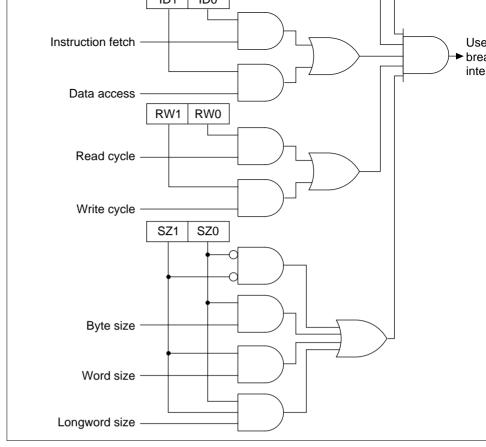

|      | 7.2.3  | User Break Bus Cycle Register (UBBR)                                             |

| 7.3  | Operat | ion                                                                              |

|      | 7.3.1  | Flow of the User Break Operation                                                 |

|      | 7.3.2  | Break on On-Chip Memory Instruction Fetch Cycle                                  |

|      | 7.3.3  | Program Counter (PC) Values Saved                                                |

| 7.4  | Use Ex | xamples                                                                          |

|      | 7.4.1  | Break on CPU Instruction Fetch Cycle                                             |

|      | 7.4.2  | Break on CPU Data Access Cycle                                                   |

|      | 7.4.3  | Break on DMA/DTC Cycle                                                           |

| 7.5  |        | ns on Use                                                                        |

|      |        |                                                                                  |

6.6.2

7.5.1

7.5.2

7.5.3

7.5.4

RENESAS

On-Chip Memory Instruction Fetch

Instruction Fetch at Branches Contention between User Break and Exception Handling.....

Break at Non-Delay Branch Instruction Jump Destination.....

Cautions on Use.....

but Not DMAC Activating Sources .....

or DTC Activating Sources

Handling DMAC Activating Sources but Not CPU Interrupt

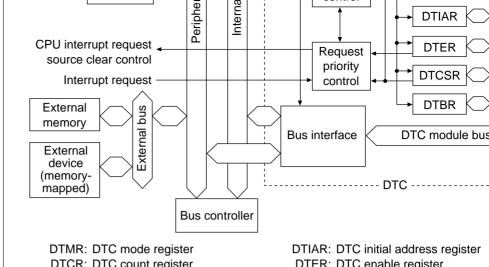

|                                   | 8.2.9                                                                              | DTC Information Base Register (DTBR)                                                                                                                                                                                                           |  |  |

|-----------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8.3                               | Operation                                                                          |                                                                                                                                                                                                                                                |  |  |

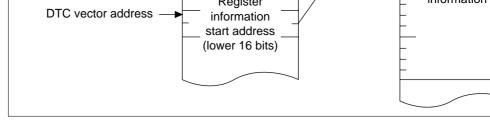

|                                   | 8.3.1                                                                              | Overview of Operation                                                                                                                                                                                                                          |  |  |

|                                   | 8.3.2                                                                              | Activating Sources                                                                                                                                                                                                                             |  |  |

|                                   | 8.3.3                                                                              | DTC Vector Table                                                                                                                                                                                                                               |  |  |

|                                   | 8.3.4                                                                              | Register Information Placement                                                                                                                                                                                                                 |  |  |

|                                   | 8.3.5                                                                              | Normal Mode                                                                                                                                                                                                                                    |  |  |

|                                   | 8.3.6                                                                              | Repeat Mode                                                                                                                                                                                                                                    |  |  |

|                                   | 8.3.7                                                                              | Block Transfer Mode                                                                                                                                                                                                                            |  |  |

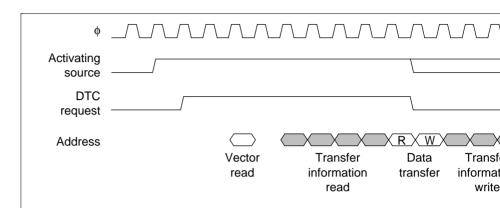

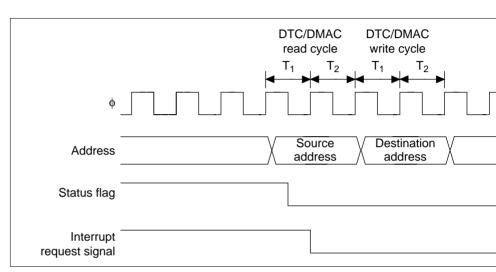

|                                   | 8.3.8                                                                              | Operation Timing                                                                                                                                                                                                                               |  |  |

|                                   | 8.3.9                                                                              | DTC Execution State Counts                                                                                                                                                                                                                     |  |  |

|                                   | 8.3.10                                                                             | DTC Usage Procedure                                                                                                                                                                                                                            |  |  |

|                                   | 8.3.11                                                                             | DTC Use Example                                                                                                                                                                                                                                |  |  |

| 8.4                               | Caution                                                                            | ns on Use                                                                                                                                                                                                                                      |  |  |

|                                   |                                                                                    |                                                                                                                                                                                                                                                |  |  |

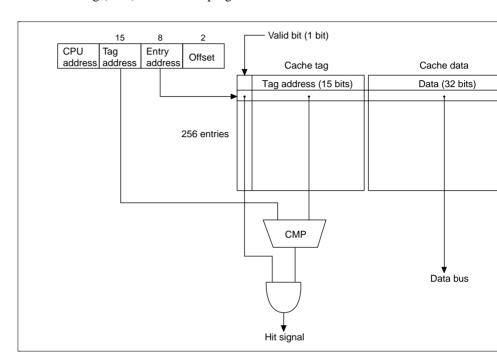

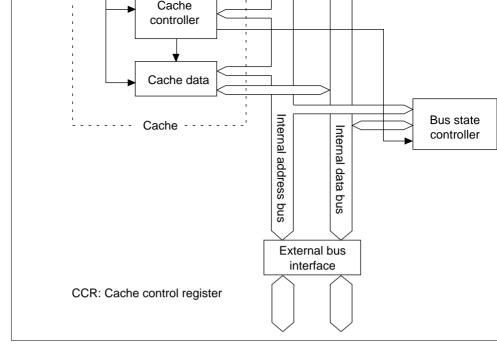

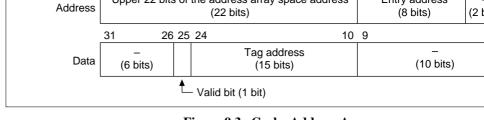

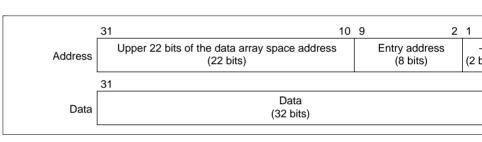

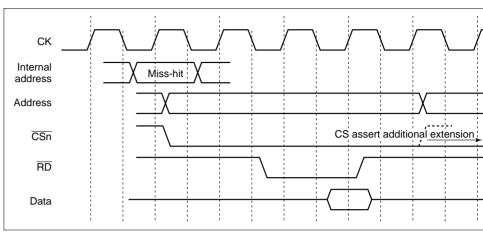

| Sect                              | tion 9                                                                             | Cache Memory (CAC)                                                                                                                                                                                                                             |  |  |

| 9.1                               | Overview                                                                           |                                                                                                                                                                                                                                                |  |  |

|                                   | 9.1.1                                                                              | Features                                                                                                                                                                                                                                       |  |  |

|                                   | 9.1.2                                                                              | Block Diagram                                                                                                                                                                                                                                  |  |  |

|                                   | 7.1.2                                                                              | Block Blagfulli                                                                                                                                                                                                                                |  |  |

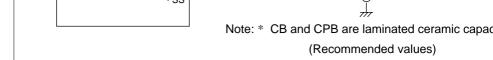

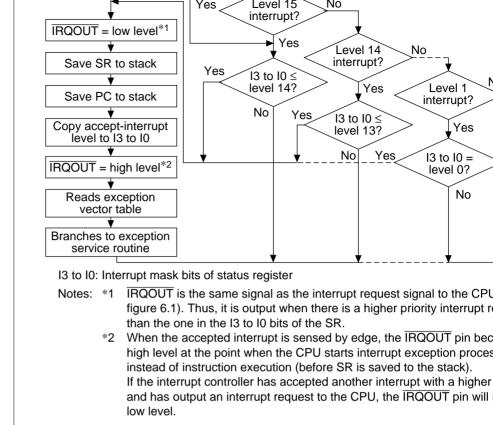

|                                   | 9.1.3                                                                              |                                                                                                                                                                                                                                                |  |  |