# RENESAS

# DATASHEET

FN6508

Rev 4.00

February 15, 2013

### ISL1536

Dual Channel Central Office ADSL2+ Line Driver

The ISL1536 is a very low power dual channel differential amplifier designed for central office line driving for DMT ADSL2+. This device features a high drive capability of 400mA while consuming only 4mA of supply current per amplifier from ±12V supplies. It integrates gain and bias resistors while maintaining high slew rate and low distortion.

### **Ordering Information**

| PART<br>NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|-----------------------------------|-----------------|------------------------|----------------------|----------------|

| ISL1536IRZ                        | 153 6IRZ        | -40 to +85             | 16 Ld QFN            | L16.4x4E       |

| ISL1536IRZ-T13*                   | 153 6IRZ        | -40 to +85             | 16 Ld QFN            | L16.4x4E       |

NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- For Moisture Sensitivity Level (MSL), please see device information page for ISL1536. For more information on MSL, please see tech brief <u>TB363</u>.

#### Features

- Internal Fixed Gain A<sub>V</sub> = 12.85

- Integrated Feedback Resistors

- 43.4V<sub>P-P</sub> Differential Output Drive into  $100\Omega$

- 41.6V<sub>P-P</sub> Minimum Differential Output Drive into  $60\Omega$

- 59dBc Typical Driver Output Distortion Driving  $50\Omega$  at 2MHz

- · Low Quiescent Current of 3mA per Amplifier

- Power-Down Disable Control

- Pb-Free (RoHS Compliant)

#### Applications

- ADSL, ADSL2, ADSL2+ Line Drivers

- G.SHDSL, HDSL2 Line Drivers

- Video Distribution Amplifiers

- · Video Twisted-pair Line Drivers

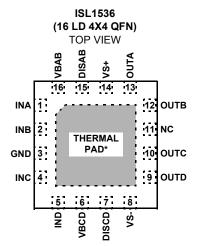

#### Pinout

\*GND FOR BOTH SINGLE/DUAL SUPPLY

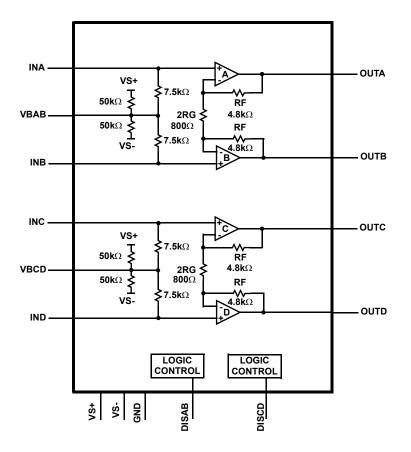

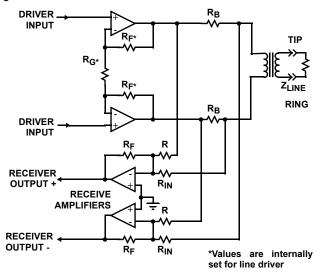

#### Block Diagram

#### **Pin Descriptions**

| 16 LD QFN | PIN NAME | FUNCTION                                         |

|-----------|----------|--------------------------------------------------|

| 1         | INA      | Amplifier A input                                |

| 2         | INB      | Amplifier B input                                |

| 3         | GND      | Ground connection                                |

| 4         | INC      | Amplifier C input                                |

| 5         | IND      | Amplifier D input                                |

| 6         | VBCD     | Voltage bias for amplifier C, D                  |

| 7         | DISCD    | Enable/disable amplifiers C, D (DSL Channel #2)  |

| 8         | VS-      | Negative supply                                  |

| 9         | OUTD     | Amplifier D output                               |

| 10        | OUTC     | Amplifier C output                               |

| 11        | NC       | No internal connection. Connect to GND on PCB.   |

| 12        | OUTB     | Amplifier B output                               |

| 13        | OUTA     | Amplifier A output                               |

| 14        | VS+      | Positive supply                                  |

| 15        | DISAB    | Enable/disable amplifiers A, B (DSL Channel #1). |

| 16        | VBAB     | Voltage bias for amplifier A, B                  |

| Absolute | Maximum | Ratings | (T <sub>A</sub> = +25°C) |

|----------|---------|---------|--------------------------|

|----------|---------|---------|--------------------------|

| V <sub>S</sub> + to V <sub>S</sub> - Supply Voltage. | /<br>/<br>+<br>A |

|------------------------------------------------------|------------------|

| ESD Rating<br>Human Body Model                       | /                |

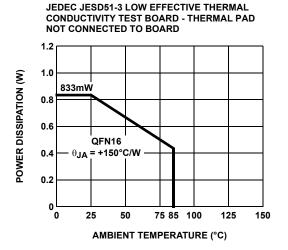

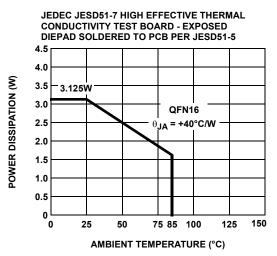

#### **Thermal Information**

| Thermal Resistance (Typical, Note 4)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| 16 Lead QFN                                      | 40                     |

| Ambient Operating Temperature Range40            | °C to +85°C            |

| Storage Temperature Range60°                     | C to +150°C            |

| Operating Junction Temperature                   | +150°C                 |

| Power Dissipation                                | . See curves           |

| Pb-Free Reflow Profile                           | e link below           |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTE:

4. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief <u>TB379</u> for details.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| PARAMETER             | DESCRIPTION                      | CONDITIONS                                                                          | MIN<br>(Note 5) | ТҮР    | MAX<br>(Note 5) | UNIT   |

|-----------------------|----------------------------------|-------------------------------------------------------------------------------------|-----------------|--------|-----------------|--------|

| AC PERFORMA           | NCE                              | ł                                                                                   |                 |        |                 |        |

| A <sub>V</sub>        | Gain                             |                                                                                     | 12.6            | 12.85  | 13.1            | V/V    |

| BW                    | -3dB Bandwidth                   |                                                                                     |                 | 50     |                 | MHz    |

| THD                   | Total Harmonic Distortion        | f = 1MHz, $V_0$ = 10Vo <sub>P-P</sub> - diff, $R_L$ = 50 $\Omega$ to GND            |                 | -69    |                 | dBc    |

|                       |                                  | f = 2.2MHz, $V_O$ = 10Vo <sub>P-P</sub> - diff, R <sub>L</sub> = 50 $\Omega$ to GND |                 | -59    |                 | dBc    |

| SR                    | Slew Rate, Single-Ended Signal   | V <sub>OUT</sub> from -4.5V to +4.5V                                                | 200             | 400    |                 | V/µs   |

| DC PERFORMA           | NCE                              |                                                                                     | 1               |        | 1               |        |

| V <sub>OS-DM</sub>    | Differential Mode Offset Voltage |                                                                                     | -50             |        | +50             | mV     |

| V <sub>OS-CM</sub>    | Common Mode Offset Voltage       |                                                                                     | -125            |        | 125             | mV     |

| INPUT CHARAC          | TERISTICS                        | -                                                                                   | I               |        |                 |        |

| I <sub>B</sub> +      | Non-Inverting Input Bias Current |                                                                                     | -5              |        | +5              | μA     |

| e <sub>N</sub>        | Input Noise Voltage              | f = 10kHz                                                                           |                 | 8.0    |                 | nV√Hz  |

| i <sub>N</sub> +      | +Input Noise Current             | f = 10kHz                                                                           |                 | 1.0    |                 | pA/√Hz |

| RIN                   | Input Resistance                 |                                                                                     | 6               | 7.5    | 9               | kΩ     |

| V <sub>IH</sub>       | Input High Voltage               | DIS inputs                                                                          | 2.2             |        |                 | V      |

| V <sub>IL</sub>       | Input Low Voltage                | DIS inputs                                                                          |                 |        | 0.8             | V      |

| Ι <sub>ΙΗ</sub>       | Input High Current for DIS       | DIS = 5V                                                                            | 20              | 58     | 100             | μA     |

| կլ                    | Input Low Current for DIS        | DIS = 0V                                                                            | -25             | -7     | 0               | μA     |

| OUTPUT CHAR           | ACTERISTICS                      | -                                                                                   | I               |        |                 |        |

| V <sub>OUT</sub> -50  | Loaded Output Swing Single-Ended | $R_{L} = 50\Omega$ to GND                                                           | ±10.4           | ±10.85 |                 | V      |

| V <sub>OUT</sub> -30  | Loaded Output Swing Single-Ended | $R_L = 30\Omega$ to GND                                                             | ±9.8            | ±10.4  |                 | V      |

| V <sub>OUT</sub> -DIS | Disable Output Voltage           |                                                                                     |                 |        | ±800            | mV     |

| IOUT                  | Output Current                   | $R_L = 0\Omega$                                                                     |                 | 600    |                 | mA     |

#### **Electrical Specifications** $V_S = \pm 12V$ , $R_L = 50\Omega$ to GND, DISAB = DISCD = 0, $T_A = \pm 25^{\circ}C$ , unless otherwise specified.

| PARAMETER                     | DESCRIPTION                           | CONDITIONS                  | MIN<br>(Note 5) | ТҮР   | MAX<br>(Note 5) | UNIT |

|-------------------------------|---------------------------------------|-----------------------------|-----------------|-------|-----------------|------|

| SUPPLY CHARA                  | CTERISTICS                            |                             | 4               |       | <u>  </u>       |      |

| V <sub>S(MAX)</sub>           | Maximum Operating Supply Voltage      |                             |                 | ±13.2 |                 | V    |

| V <sub>S(MIN)</sub>           | Minimum Operating Supply Voltage      |                             |                 | ±7.5  |                 | V    |

| IS <sup>+</sup> (Enable)      | Positive Supply Current per Amplifier | All outputs at 0V, DIS = 0V |                 | 4.0   | 5               | mA   |

| I <sub>S</sub> - (Enable)     | Negative Supply Current per Amplifier | All outputs at 0V, DIS = 0V | -4.85           | -3.9  |                 | mA   |

| IS <sup>+</sup> (Power Down)  | Positive Supply Current per Amplifier | All outputs at 0V, DIS = 5V |                 | 0.3   | 0.75            | mA   |

| I <sub>S</sub> - (Power Down) | Negative Supply Current per Amplifier | All outputs at 0V, DIS = 5V | -0.75           | 0     |                 | mA   |

| I <sub>GND</sub>              | GND Supply Current per Amplifier      | All outputs at 0V           |                 | 0.3   |                 | mA   |

NOTE:

5. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

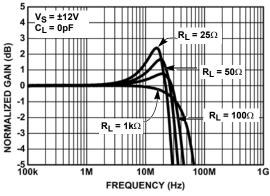

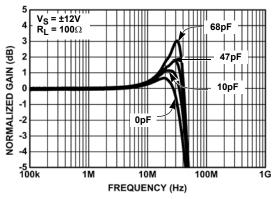

FIGURE 1. DIFFERENTIAL FREQUENCY RESPONSE vs RL

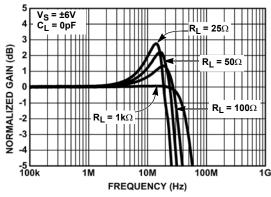

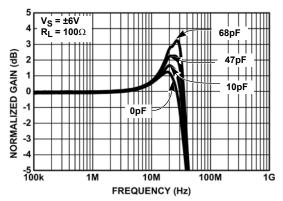

FIGURE 3. DIFFERENTIAL FREQUENCY RESPONSE vs CL

FIGURE 2. DIFFERENTIAL FREQUENCY RESPONSE vs RL

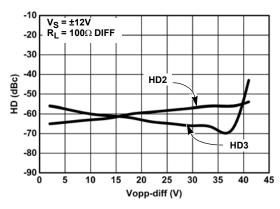

#### Typical Performance Curves (Continued)

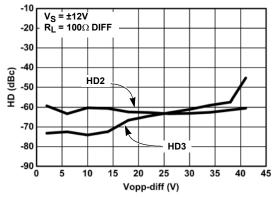

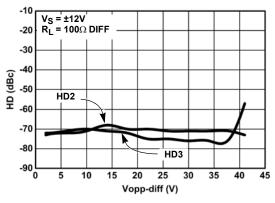

FIGURE 6. 1MHz 2ND AND 3RD HARMONICS vs DIFFERENTIAL OUTPUT VOLTAGE

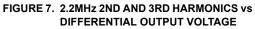

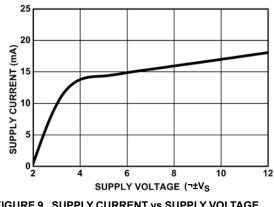

FIGURE 9. SUPPLY CURRENT vs SUPPLY VOLTAGE (ALL AMPLIFIERS ENABLED)

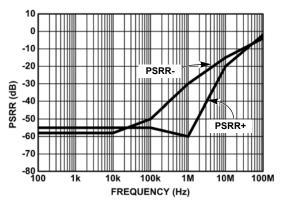

FIGURE 8. PSRR vs FREQUENCY

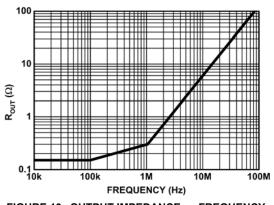

FIGURE 10. OUTPUT IMPEDANCE vs FREQUENCY

#### Typical Performance Curves (Continued)

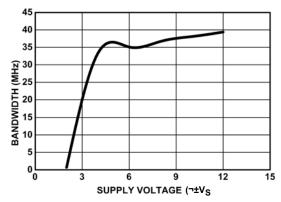

FIGURE 11. DIFFERENTIAL 3dB BANDWIDTH vs SUPPLY VOLTAGE

FIGURE 13. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

FIGURE 12. CHANNEL SEPARATION vs FREQUENCY

#### Applications Information

#### **Product Description**

The ISL1536 consists of two sets of high-power line driver amplifiers that can be connected for full duplex differential line transmission. The amplifiers are designed to be used with ADSL2+ signals up to 2.2MHz. Each amplifier has identical positive gain connections resulting in optimum common-mode rejection. A typical interface circuit configuration is shown in Figure 15.

FIGURE 15. TYPICAL INTERFACE CIRCUIT CONFIGURATION

#### Integrated Components

ISL1536 integrates bias and feedback resistors, minimizing the number of external components. The gain is fixed at +12.85V/V.

The VBAB and VBCD pins also integrate a pair of  $7.5k\Omega$  and  $50k\Omega$  resistors on each port to bias the line driver for single and dual supply usage. When powering the line driver with a single supply, VBAB and VBCD pins are floated. When using dual supplies, VBAB and VBCD pins are grounded.

Integration of these components in the line driver minimizes assembly cost and board space.

#### Impedance Matching

${\sf R}_B$  in Figure 15 depends on the line impedance and transformer's turns ratio. Line impedance is characterized to be 100 $\Omega$  across tip and ring. If a 1:N tranformer is used,  ${\sf R}_B$  can be calculated according to Equation 1:

$$\left(\mathsf{RB} = \frac{100}{\mathsf{N}^2} \times 0.5\right) \tag{EQ. 1}$$

#### **Revision History**

| REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FN6508.4 | Added Note 3 to "Ordering Information" on page 1.<br>Changed HBM from 3kV to 4kV in "Absolute Maximum Ratings" on page 3.<br>Changed MM from 300V to 250V in "Absolute Maximum Ratings" on page 3<br>Added Note 5 to "Electrical Specifications" table on page 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FN6508.3 | On page 4, changed the "Maximum Operating Supply Voltage" TYP from ±12.6V to ±13.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | On page 3 in the "Electrical Specifications" table, changed V <sub>OUT</sub> -DIS Max spec from ±300mV to ±800mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | Added Revision History beginning from rev 3.<br>Changed the logic high level (VIH) on page 3 from Min 2.0V to Min 2.2V, which is consistent with the intended<br>applications (AFE output logic high levels are typically at 3.3V with 2.4V minimum) while providing added margin<br>to internal threshold variation.<br>On page 1 in the first paragraph, changed: "This device features a high drive capability of 400mA while<br>consuming only 3mA" to "This device features a high drive capability of 400mA while consuming only 4mA".<br>Added Theta JA and applicable note to "Thermal Information" on page 3.<br>Removed VS, Supply Voltage row in spec table. Added Maximum and Minimum Operating Supply Voltages<br>(V <sub>S(MAX)</sub> and V <sub>S(MIN)</sub> ) with typical specs of ±12.6V and ±7.5V to "SUPPLY CHARACTERISTICS" on page 4.<br>Added "DISAB = DISCD = 0" to "Electrical Specifications" table common conditions. |

|          | FN6508.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

© Copyright Intersil Americas LLC 2008-2013. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

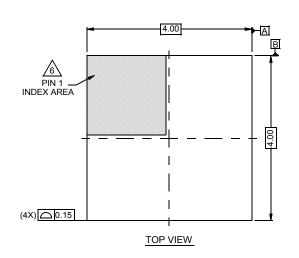

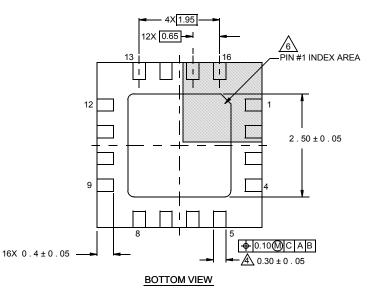

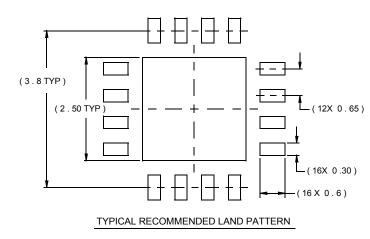

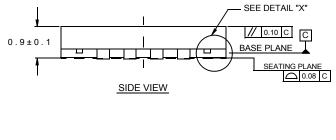

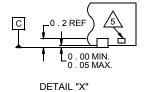

## Package Outline Drawing

#### L16.4x4E

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 4/08

NOTES:

- Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Buffers & Line Drivers category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

5962-9217601MSA 634810D HEF4043BP NL17SG125DFT2G NL17SZ126P5T5G NLU1GT126CMUTCG NLU3G16AMX1TCG NLV27WZ125USG MC74HCT365ADTR2G BCM6306KMLG 54FCT240CTDB Le87401NQC Le87402MQC 028192B 042140C 051117G 070519XB 065312DB 091056E 098456D NL17SG07DFT2G NL17SG17DFT2G NL17SG34DFT2G NL17SZ07P5T5G NL17SZ125P5T5G NLU1GT126AMUTCG NLV27WZ16DFT2G 5962-8982101PA 5962-9052201PA 74LVC07ADR2G MC74VHC1G125DFT1G NL17SH17P5T5G NL17SZ125CMUTCG NLV17SZ07DFT2G NLV37WZ17USG NLVHCT244ADTR2G NC7WZ17FHX 74HCT126T14-13 NL17SH125P5T5G NLV14049UBDTR2G NLV37WZ07USG 74VHC541FT(BE) 74LVC1G17FW4-7 74LVC1G126FZ4-7 BCM6302KMLG 74LVC1G07FZ4-7 74LVC1G125FW4-7 74AUP2G3404FW3-7 MAX9972ACCS+D 74AUP1G34FW5-7