## ISL54062

Negative Signal Swing, Sub-ohm, Dual SPDT with Click and Pop Elimination Single Supply Switch

FN6581 Rev 1.00 Nov 3, 2009

The Intersil ISL54062 device is a low ON-resistance, low voltage, bidirectional, dual single-pole/double-throw (SPDT) analog switch. It is designed to operate from a single +1.8V to +6.5V supply and pass signals that swing down to 6.5V below the positive supply rail. Targeted applications include battery powered equipment that benefit from low  $r_{ON} \, (0.56\Omega)$ , low power consumption (20nA) and fast switching speeds (toN = 55ns, toFF = 18ns). The digital inputs are 1.8V logic-compatible up to a +3V supply. The ISL54062 also features integrated circuitry to eliminate click and pop noise to an audio speaker. The ISL54062 is offered in a small form factor package, alleviating board space limitations. It is available in a tiny 10 Ld 1.8x1.4mm  $\mu TQFN$  or 10 Ld 3x3mm TDFN package.

The ISL54062 is a committed dual single-pole/double-throw (SPDT) that consist of two normally open (NO) and two normally closed (NC) switches with independent logic control. This configuration can be used as a dual 2-to-1 multiplexer.

**TABLE 1. FEATURES AT A GLANCE**

| ISI                                    | _54062                  |

|----------------------------------------|-------------------------|

| Number of Switches                     | 2                       |

| sw                                     | SPDT or 2-to-1 MUX      |

| 4.3V r <sub>ON</sub>                   | 0.57Ω                   |

| 4.3V t <sub>ON</sub> /t <sub>OFF</sub> | 43ns/23ns               |

| 2.7V r <sub>ON</sub>                   | 0.82Ω                   |

| 2.7V t <sub>ON</sub> /t <sub>OFF</sub> | 55ns/18ns               |

| 1.8V r <sub>ON</sub>                   | 1.8Ω                    |

| 1.8V t <sub>ON</sub> /t <sub>OFF</sub> | 145ns/28ns              |

| Packages                               | 10 Ld μTQFN, 10 Ld TDFN |

#### **Features**

- · Pb-free (RoHS Compliant)

- Negative Signal Swing (Max 6.5V Below V+)

- · Audio Click and Pop Elimination Circuitry

- ON-Resistance (r<sub>ON</sub>)

|   | - V+ = +4.5V                                                                      |

|---|-----------------------------------------------------------------------------------|

|   | - V+ = +4.3V 0.57Ω                                                                |

|   | - V+ = +2.7V                                                                      |

|   | - V+ = +1.8V                                                                      |

| • | $r_{\mbox{ON}}$ Matching Between Channels                                         |

| • | $r_{\mbox{ON}}$ Flatness Across Signal Range                                      |

| • | $\label{eq:lowTHD+N @ 32} \mbox{Load} \ \dots \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ |

| • | Single Supply Operation +1.8V to +6.5V                                            |

| • | Low Power Consumption @ 3V ( $P_D$ ) 24nW                                         |

| • | Fast Switching Action (V+ = +4.3V)                                                |

|   | - t <sub>ON</sub>                                                                 |

|   | - t <sub>OFF</sub>                                                                |

| • | ESD HBM Rating>6kV                                                                |

|   |                                                                                   |

- · Guaranteed Break-before-Make

- 1.8V Logic Compatible (+3V supply)

- · Low I+ Current when V<sub>INH</sub> is not at the V+ Rail

- Available in 10 Ld µTQFN 1.8x1.4mm and 10 Ld 3x3mm TDFN

## **Applications**

- · Audio and Video Switching

- · Battery powered, Handheld, and Portable Equipment

- MP3 and Multimedia Players

- Cellular/mobile Phones

- Pagers

- Laptops, Notebooks, Palmtops

- Portable Test and Measurement

- · Medical Equipment

#### Related Literature

- Technical Brief TB363 "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)"

- Application Note AN557 "Recommended Test Procedures for Analog Switches"

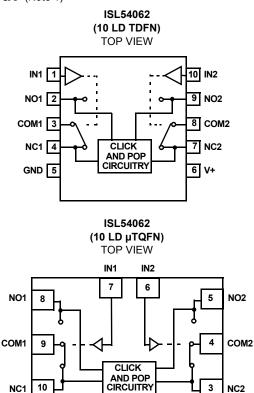

## Pinout (Note 1)

2

### Truth Table

| IN1 | IN2 | NC1 | NO1 | NC2 | NO2 |

|-----|-----|-----|-----|-----|-----|

| 0   | 0   | ON  | OFF | ON  | OFF |

| 0   | 1   | ON  | OFF | OFF | ON  |

| 1   | 0   | OFF | ON  | ON  | OFF |

| 1   | 1   | OFF | ON  | OFF | ON  |

NOTE: Logic "0" ≤0.5V. Logic "1" ≥1.4V with a 3V supply.

## Pin Descriptions

| PIN  | FUNCTION                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| V+   | IC Power Supply (+1.8V to +6.5V). Decouple V+ to ground by placing a 0.1µF capacitor at the V+ and GND supply lines as near as the IC as possible. |

| GND  | Ground Connection                                                                                                                                  |

| INx  | Digital Control Input                                                                                                                              |

| COMx | Analog Switch Common Pin                                                                                                                           |

| NOx  | Analog Switch Normally Open Pin                                                                                                                    |

| NCx  | Analog Switch Normally Closed Pin                                                                                                                  |

#### NOTE:

1. Switches Shown for INx = Logic "0".

GND

# **Ordering Information**

| PART<br>NUMBER                 | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE<br>(Pb-Free)             | PKG.<br>DWG. # |

|--------------------------------|-----------------|---------------------|----------------------------------|----------------|

| ISL54062IRTZ<br>(Note 3)       | 4062            | -40 to +85          | 10 Ld 3x3 TDFN                   | L10.3x3A       |

| ISL54062IRTZ-T<br>(Notes 2, 3) | 4062            | -40 to +85          | 10 Ld 3x3 TDFN (Tape and Reel)   | L10.3x3A       |

| ISL54062IRUZ-T<br>(Notes 2, 4) | 8               | -40 to +85          | 10 Ld Thin μTQFN (Tape and Reel) | L10.1.8x1.4A   |

- 2. Please refer to TB347 for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

| Absolute Maximum Ratings                                                                                                                                    | Thermal Information                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| V+ to GND                                                                                                                                                   | eq:thm:thm:thm:thm:thm:thm:thm:thm:thm:thm                                                |

| (Pulsed 1ms, 10% Duty Cycle, Max)       ±500mA         ESD Rating:       ->6kV         Machine Model       ->400V         Charged Device Model       >1.5kV | Operating Conditions  Temperature Range -40°C to +85°C  Power Supply Range +1.8V to +6.5V |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5. Signals on NC, NO, IN, or COM exceeding V+ or GND by specified amount are clamped by internal diodes. Limit forward diode current to maximum current ratings.

- 6. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 7. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 8. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

Electrical Specifications - 5V Supply Test Conditions: V+ = +4.5V to +5.5V, GND = 0V, V<sub>INH</sub> = 2.4V, V<sub>INL</sub> = 0.8V (Note 9), Unless Otherwise Specified.

| PARAMETER                                       | TEST CONDITIONS                                                                           | TEMP<br>(°C) | MIN<br>(Notes 10, 11) | TYP  | MAX<br>(Notes 10, 11) | UNITS     |

|-------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|-----------------------|------|-----------------------|-----------|

| ANALOG SWITCH CHARACTERI                        | STICS                                                                                     |              |                       |      |                       |           |

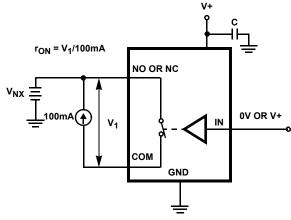

| ON-Resistance, r <sub>ON</sub>                  | $V+ = 4.5V$ , $I_{COM} = 100$ mA, $V_{NO}$ or $V_{NC} = (V+ -6.5)$                        | 25           | -                     | 0.55 | -                     | Ω         |

|                                                 | to V+ (see Figure 5)                                                                      | Full         | -                     | 0.68 | -                     | Ω         |

| r <sub>ON</sub> Matching Between Channels,      | V+ = 4.5V, $I_{COM}$ = 100mA, $V_{NO}$ or $V_{NC}$ = Voltage at                           | 25           | -                     | 15   | -                     | mΩ        |

| Δr <sub>ON</sub>                                | max r <sub>ON,</sub> (Note 13)                                                            | Full         | -                     | 30   | -                     | $m\Omega$ |

| r <sub>ON</sub> Flatness, R <sub>FLAT(ON)</sub> | $V = 4.5V$ , $I_{COM} = 100$ mA, $V_{NO}$ or $V_{NC} = (V + -6.5)$                        | 25           | -                     | 0.11 | -                     | Ω         |

|                                                 | to V+, (Note 12)                                                                          | Full         | -                     | 0.14 | -                     | Ω         |

| COM ON Leakage Current,                         | $V+ = 5V$ , $V_{COM} = -1.5V$ , $5V$ , $V_{NO}$ or $V_{NC} = Float$                       | 25           | -                     | 49   | -                     | nA        |

| ICOM(ON)                                        |                                                                                           | Full         | -                     | 0.7  | -                     | μΑ        |

| DYNAMIC CHARACTERISTICS                         |                                                                                           |              |                       |      |                       |           |

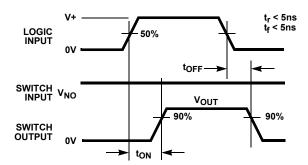

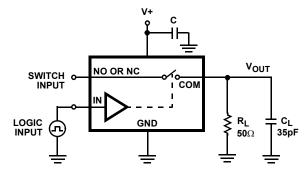

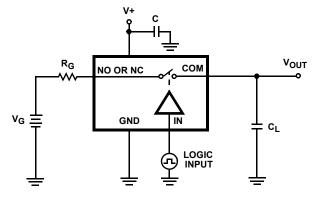

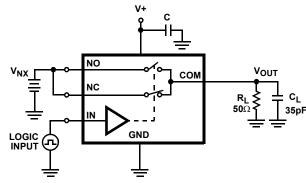

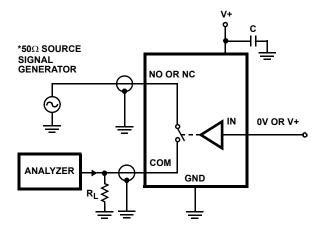

| Turn-ON Time, t <sub>ON</sub>                   | V+ = 4.5V, $V_{NO}$ or $V_{NC}$ = 3.0V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF (see Figure 1) | 25           | -                     | 35   | -                     | ns        |

|                                                 |                                                                                           | Full         | -                     | 50   | -                     | ns        |

| Turn-OFF Time, t <sub>OFF</sub>                 | $V + = 4.5V$ , $V_{NO}$ or $V_{NC} = 3.0V$ , $R_L = 50\Omega$ ,                           | 25           | -                     | 16   | -                     | ns        |

|                                                 | C <sub>L</sub> = 35pF (see Figure 1)                                                      | Full         | -                     | 22   | -                     | ns        |

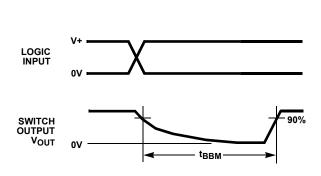

| Break-Before-Make Time Delay, t <sub>D</sub>    | V+ = 5.5V, $V_{NO}$ or $V_{NC}$ = 3.0V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF (see Figure 3) | Full         | -                     | 18   | -                     | ns        |

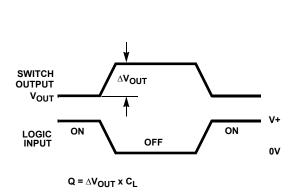

| Charge Injection, Q                             | $V_G = 0V$ , $R_G = 0\Omega$ , $C_L = 1.0$ nF (see Figure 2)                              | 25           | -                     | 170  | -                     | рС        |

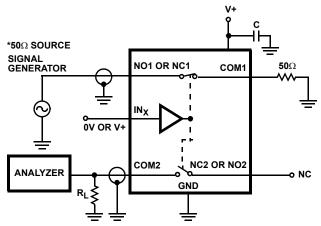

| OFF-Isolation                                   | $R_L$ = 50 $\Omega$ , $C_L$ = 5pF, f = 100kHz, $V_{COM}$ = 1 $V_{RMS}$ (see Figure 4)     | 25           | -                     | 60   | -                     | dB        |

| Crosstalk (Channel-to-Channel)                  | $R_L = 50\Omega$ , $C_L = 5pF$ , $f = 1MHz$ , $V_{COM} = 1V_{RMS}$ (see Figure 6)         | 25           | -                     | -75  | -                     | dB        |

| Total Harmonic Distortion                       | f = 20Hz to 20kHz, $V_{COM}$ = 0.5 $V_{P-P}$ , $R_{L}$ = 32 $\Omega$                      | 25           | -                     | 0.02 | -                     | %         |

| -3dB Bandwidth                                  | $V_{COM}$ = $1V_{RMS}$ , $R_L$ = $50\Omega$ , $C_L$ = $5pF$                               | 25           | -                     | 60   | -                     | MHz       |

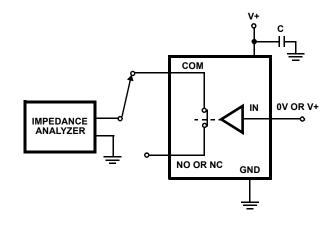

| NO x or NCx OFF Capacitance, C <sub>OFF</sub>   | f = 1MHz                                                                                  | 25           | -                     | 36   | -                     | pF        |

# Electrical Specifications - 5V Supply Test Conditions: V+ = +4.5V to +5.5V, GND = 0V, V<sub>INH</sub> = 2.4V, V<sub>INL</sub> = 0.8V (Note 9), Unless Otherwise Specified. (Continued)

| PARAMETER                                          | TEST CONDITIONS                       | TEMP<br>(°C) | MIN<br>(Notes 10, 11) | TYP  | MAX<br>(Notes 10, 11) | UNITS |

|----------------------------------------------------|---------------------------------------|--------------|-----------------------|------|-----------------------|-------|

| COMx ON Capacitance,<br>CCOM(ON)                   | f = 1MHz (see Figure 7)               | 25           | -                     | 88   | -                     | pF    |

| POWER SUPPLY CHARACTE                              | RISTICS                               |              | •                     |      | •                     |       |

| Positive Supply Current, I+                        | V+ = 5.5V, V <sub>IN</sub> = 0V or V+ | 25           | -                     | 0.02 | 0.1                   | μA    |

|                                                    |                                       | Full         | -                     | 2.5  | -                     | μA    |

| DIGITAL INPUT CHARACTER                            | ISTICS                                |              |                       |      |                       |       |

| Input Voltage Low, V <sub>INL</sub>                |                                       | Full         | -                     | -    | 0.8                   | V     |

| Input Voltage High, V <sub>INH</sub>               |                                       | Full         | 2.4                   | -    | -                     | ٧     |

| Input Current, I <sub>INH</sub> , I <sub>INL</sub> | V+ = 5.5V, V <sub>IN</sub> = 0V or V+ | 25           | -0.1                  | 1    | 0.1                   | μA    |

|                                                    |                                       | Full         | -                     | 0.89 | -                     | μA    |

# **Electrical Specifications - 4.3V Supply**Test Conditions: V+ = +3.9V to +4.5V, GND = 0V, $V_{INH} = 1.6V$ , $V_{INL} = 0.5V$ (Note 9), Unless Otherwise Specified.

| PARAMETER                                       | TEST CONDITIONS                                                                           | TEMP<br>(°C) | MIN<br>(Notes 10, 11) | TYP  | MAX<br>(Notes 10, 11) | UNITS |

|-------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|-----------------------|------|-----------------------|-------|

| ANALOG SWITCH CHARACTE                          | RISTICS                                                                                   |              |                       |      |                       |       |

| ON-Resistance, r <sub>ON</sub>                  | V+ = 4.3V, I <sub>COM</sub> = 100mA, V <sub>NO</sub> or V <sub>NC</sub> = (V+ - 6.5V)     | 25           | -                     | 0.57 | -                     | Ω     |

|                                                 | to V+, (See Figure 5)                                                                     | Full         | -                     | 0.68 | -                     | Ω     |

| r <sub>ON</sub> Matching Between                | V+ = 4.3V, I <sub>COM</sub> = 100mA, V <sub>NO</sub> or V <sub>NC</sub> = Voltage at      | 25           | -                     | 15   | -                     | mΩ    |

| Channels, ∆r <sub>ON</sub>                      | max r <sub>ON,</sub> (Note 12)                                                            | Full         | -                     | 30   | -                     | mΩ    |

| r <sub>ON</sub> Flatness, R <sub>FLAT(ON)</sub> | V+ = 4.3V, I <sub>COM</sub> = 100mA, V <sub>NO</sub> or V <sub>NC</sub> = (V+ - 6.5V)     | 25           | -                     | 0.1  | -                     | Ω     |

|                                                 | to V+, (Note 13)                                                                          | Full         | -                     | 0.14 | -                     | Ω     |

| COM ON Leakage Current,                         | V+ = 4.3V, V <sub>COM</sub> = -1.2V, 4.3V, V <sub>NO</sub> or V <sub>NC</sub> = Float     | 25           | -0.1                  | -    | 0.1                   | μΑ    |

| ICOM(ON)                                        |                                                                                           | Full         | -                     | 1.1  | -                     | μA    |

| DYNAMIC CHARACTERISTICS                         |                                                                                           | 1            |                       |      | 1                     |       |

| Turn-ON Time, t <sub>ON</sub>                   | V+ = 3.9V, $V_{NO}$ or $V_{NC}$ = 3.0V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF (see Figure 1) | 25           | -                     | 43   | -                     | ns    |

|                                                 |                                                                                           | Full         | -                     | 50   | -                     | ns    |

| Turn-OFF Time, t <sub>OFF</sub>                 | $V+ = 3.9V$ , $V_{NO}$ or $V_{NC} = 3.0V$ , $R_L = 50\Omega$ , $C_L = 35pF$               | 25           | -                     | 23   | -                     | ns    |

|                                                 | (see Figure 1)                                                                            | Full         | -                     | 23   | -                     | ns    |

| Break-Before-Make Time Delay, $t_{\rm D}$       | V+ = 4.5V, $V_{NO}$ or $V_{NC}$ = 3.0V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF (see Figure 3) | Full         | -                     | 22   | -                     | ns    |

| Charge Injection, Q                             | $C_L = 1.0$ nF, $V_G = 0$ V, $R_G = 0\Omega$ (see Figure 2)                               | 25           | -                     | 200  | -                     | рС    |

| OFF-Isolation                                   | $R_L$ = 50 $\Omega$ , $C_L$ = 5pF, f = 100kHz, $V_{COM}$ = 1 $V_{RMS}$ (see Figure 4)     | 25           | -                     | 60   | -                     | dB    |

| Crosstalk (Channel-to-Channel)                  | $R_L$ = 50 $\Omega$ , $C_L$ = 5pF, f = 1MHz, $V_{COM}$ = 1 $V_{RMS}$ (see Figure 6)       | 25           | -                     | -75  | -                     | dB    |

| Total Harmonic Distortion                       | f = 20Hz to 20kHz, $V_{COM}$ = $2V_{P-P}$ , $R_L$ = $32\Omega$                            | 25           | -                     | 0.04 | -                     | %     |

| NOx or NCx OFF Capacitance, C <sub>OFF</sub>    | f = 1MHz                                                                                  | 25           | -                     | 36   | -                     | pF    |

| COMx ON Capacitance,<br>C <sub>COM(ON)</sub>    | f = 1MHz (see Figure 7)                                                                   | 25           | -                     | 88   | -                     | pF    |

# Electrical Specifications - 4.3V SupplyTest Conditions: V+ = +3.9V to +4.5V, GND = 0V, V<sub>INH</sub> = 1.6V, V<sub>INL</sub> = 0.5V (Note 9), Unless Otherwise Specified. (Continued)

| PARAMETER                                          | TEST CONDITIONS                        | TEMP<br>(°C) | MIN<br>(Notes 10, 11) | ТҮР   | MAX<br>(Notes 10, 11) | UNITS |

|----------------------------------------------------|----------------------------------------|--------------|-----------------------|-------|-----------------------|-------|

| POWER SUPPLY CHARACT                               | ERISTICS                               | ·            |                       |       |                       |       |

| Positive Supply Current, I+                        | V+ = +4.5V, V <sub>IN</sub> = 0V or V+ | 25           | -                     | 0.003 | 0.1                   | μA    |

|                                                    |                                        | Full         | -                     | 2.6   | -                     | μΑ    |

| Positive Supply Current, I+                        | V+ = +4.2V, V <sub>IN</sub> = 2.85V    | 25           | -                     | 0.89  | 12                    | μA    |

| DIGITAL INPUT CHARACTE                             | RISTICS                                | -            |                       |       | 1                     |       |

| Input Voltage Low, V <sub>INL</sub>                |                                        | Full         | -                     | -     | 0.5                   | V     |

| Input Voltage High, V <sub>INH</sub>               |                                        | Full         | 1.6                   | -     | -                     | V     |

| Input Current, I <sub>INH</sub> , I <sub>INL</sub> | V+ = 4.5V, V <sub>IN</sub> = 0V or V+  | 25           | -0.5                  | -     | 0.5                   | μΑ    |

|                                                    |                                        | Full         | -                     | 0.5   | -                     | μΑ    |

# **Electrical Specifications - 3V Supply** Test Conditions: V+ = +2.7V to +3.3V, GND = 0V, $V_{INH} = 1.4V$ , $V_{INL} = 0.5V$ (Note 9), Unless Otherwise Specified.

| PARAMETER                                          | TEST CONDITIONS                                                                           | TEMP<br>(°C) | MIN<br>(Notes 10, 11) | TYP  | MAX<br>(Notes 10, 11) | UNITS |

|----------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|-----------------------|------|-----------------------|-------|

| ANALOG SWITCH CHARACTE                             | RISTICS                                                                                   |              |                       |      |                       |       |

| ON-Resistance, r <sub>ON</sub>                     | $V+ = 2.7V$ , $I_{COM} = 100$ mA, $V_{NO}$ or $V_{NC} = (V+ -6.5V)$                       | 25           | -                     | 0.82 | -                     | Ω     |

|                                                    | to V+ (see Figure 5)                                                                      | Full         | -                     | 0.94 | -                     | Ω     |

| r <sub>ON</sub> Matching Between                   | V+ = 2.7V, $I_{COM}$ = 100mA, $V_{NO}$ or $V_{NC}$ = Voltage at                           | 25           | -                     | 10   | -                     | mΩ    |

| Channels, ∆r <sub>ON</sub>                         | max r <sub>ON</sub> (Note 13)                                                             | Full         | -                     | 30   | -                     | mΩ    |

| r <sub>ON</sub> Flatness, R <sub>FLAT(ON)</sub>    | $V = 2.7V$ , $I_{COM} = 100$ mA, $V_{NO}$ or $V_{NC} = (V - 6.5V)$                        | 25           | -                     | 0.35 | 0.5                   | Ω     |

|                                                    | to V+ (Notes 12, 14)                                                                      | Full         | -                     | 0.4  | 0.55                  | Ω     |

| DYNAMIC CHARACTERISTICS                            |                                                                                           |              |                       |      |                       |       |

| Turn-ON Time, t <sub>ON</sub>                      | $V + = 2.7V$ , $V_{NO}$ or $V_{NC} = 1.5V$ , $R_L = 50\Omega$ , $C_L = 35pF$              | 25           | -                     | 55   | -                     | ns    |

|                                                    | (see Figure 1)                                                                            | Full         | -                     | 82   | -                     | ns    |

| Turn-OFF Time, t <sub>OFF</sub>                    | $V = 2.7V$ , $V_{NO}$ or $V_{NC} = 1.5V$ , $R_L = 50\Omega$ , $C_L = 35pF$                | 25           | -                     | 18   | -                     | ns    |

|                                                    | (see Figure 1)                                                                            | Full         | -                     | 24   | -                     | ns    |

| Break-Before-Make Time Delay, $t_{\mathrm{D}}$     | V+ = 3.3V, $V_{NO}$ or $V_{NC}$ = 1.5V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF (see Figure 3) | Full         | -                     | 30   | -                     | ns    |

| Charge Injection, Q                                | $C_L$ = 1.0nF, $V_G$ = 0V, $R_G$ = 0 $\Omega$ (see Figure 2)                              | 25           | -                     | 150  | -                     | рС    |

| OFF-Isolation                                      | $R_L$ = 50 $\Omega$ , $C_L$ = 5pF, f = 100kHz, $V_{COM}$ = 1 $V_{RMS}$ (see Figure 4)     | 25           | -                     | 60   | -                     | dB    |

| Crosstalk (Channel-to-Channel)                     | $R_L$ = 50 $\Omega$ , $C_L$ = 5pF, f = 1MHz, $V_{COM}$ = 1 $V_{RMS}$ (see Figure 6)       | 25           | -                     | -75  | -                     | dB    |

| Total Harmonic Distortion                          | f = 20Hz to 20kHz, $V_{COM}$ = 0.5 $V_{P-P}$ , $R_{L}$ = 32 $\Omega$                      | 25           | -                     | 0.04 | -                     | %     |

| NOx or NCx OFF Capacitance, COFF                   | f = 1MHz                                                                                  | 25           | -                     | 36   | -                     | pF    |

| COMx ON Capacitance, CCOM(ON)                      | f = 1MHz (see Figure 7)                                                                   | 25           | -                     | 88   | -                     | pF    |

| DIGITAL INPUT CHARACTERIS                          | STICS                                                                                     |              |                       |      |                       |       |

| Input Voltage Low, V <sub>INL</sub>                |                                                                                           | 25           | -                     | -    | 0.5                   | V     |

| Input Voltage High, V <sub>INH</sub>               |                                                                                           | 25           | 1.4                   | -    | -                     | V     |

| Input Current, I <sub>INH</sub> , I <sub>INL</sub> | V+ = 3.3V, V <sub>IN</sub> = 0V or V+                                                     | 25           | -0.5                  | -    | 0.5                   | μΑ    |

|                                                    |                                                                                           | Full         | -                     | 0.4  | -                     | μA    |

# Electrical Specifications - 1.8V Supply Test Conditions: V+ = +1.8V, GND = 0V, V<sub>INH</sub> = 1.0V, V<sub>INL</sub> = 0.4V (Note 9), Unless Otherwise Specified.

| PARAMETER                                          | TEST CONDITIONS                                                                           | TEMP<br>(°C) | MIN<br>(Notes 10, 11) | TYP                    | MAX<br>(Notes 10, 11) | UNITS |

|----------------------------------------------------|-------------------------------------------------------------------------------------------|--------------|-----------------------|------------------------|-----------------------|-------|

| ANALOG SWITCH CHARACTE                             | RISTICS                                                                                   | •            |                       |                        |                       |       |

| ON-Resistance, r <sub>ON</sub>                     | $V+ = 1.8V$ , $I_{COM} = 100$ mA, $V_{NO}$ or $V_{NC} = (V+ -6.5V)$                       | 25           | -                     | 1.87                   | -                     | Ω     |

|                                                    | to V+, (see Figure 5)                                                                     | Full         | -                     | 11) TYP (Notes 10, 11) | Ω                     |       |

| r <sub>ON</sub> Matching Between                   | V+ = 1.8V, $I_{COM}$ = 100mA, $V_{NO}$ or $V_{NC}$ = Voltage at                           | 25           | -                     | 16                     | -                     | mΩ    |

| Channels, $\Delta r_{ON}$                          |                                                                                           | Full         | -                     | 30                     | -                     | mΩ    |

| r <sub>ON</sub> Flatness, R <sub>FLAT(ON)</sub>    | $V+ = 1.8V$ , $I_{COM} = 100$ mA, $V_{NO}$ or $V_{NC} = (V+ -6.5V)$                       | 25           | -                     | 1.34                   | -                     | Ω     |

|                                                    | to V+ (Note 12)                                                                           | Full         | -                     | 1.43                   | -                     | Ω     |

| DYNAMIC CHARACTERISTICS                            | <b>S</b>                                                                                  |              |                       |                        |                       |       |

| Turn-ON Time, t <sub>ON</sub>                      | $V+ = 1.8V$ , $V_{NO}$ or $V_{NC} = 1.8V$ , $R_L = 50\Omega$ , $C_L = 35pF$               | 25           | -                     | 145                    | -                     | ns    |

|                                                    | (see Figure 1)                                                                            | Full         | -                     | 150                    | -                     | ns    |

| Turn-OFF Time, t <sub>OFF</sub>                    | (see Figure 1)                                                                            | 25           | -                     | 20                     | -                     | ns    |

|                                                    |                                                                                           | Full         | -                     | 22                     | -                     | ns    |

| Break-Before-Make Time Delay, t <sub>D</sub>       | V+ = 1.8V, $V_{NO}$ or $V_{NC}$ = 1.8V, $R_L$ = 50 $\Omega$ , $C_L$ = 35pF (see Figure 3) | Full         | -                     | 130                    | -                     | ns    |

| Charge Injection, Q                                | $C_L$ = 1.0nF, $V_G$ = 0V, $R_G$ = 0 $\Omega$ (see Figure 2)                              | 25           | -                     | 40                     | -                     | pC    |

| -3dB Bandwidth                                     | $V_{COM} = 1V_{RMS}$ , $R_L = 50\Omega$ , $C_L = 5pF$                                     | 25           | -                     | 60                     | -                     | MHz   |

| NOx or NCx OFF Capacitance, COFF                   | f = 1MHz                                                                                  | 25           | -                     | 36                     | -                     | pF    |

| COMx ON Capacitance, CCOM(ON)                      | f = 1MHz (see Figure 7)                                                                   | 25           | -                     | 88                     | -                     | pF    |

| DIGITAL INPUT CHARACTERI                           | STICS                                                                                     |              | l .                   |                        |                       | 1     |

| Input Voltage Low, V <sub>INL</sub>                |                                                                                           | 25           | -                     | -                      | 0.4                   | V     |

| Input Voltage High, V <sub>INH</sub>               |                                                                                           | 25           | 1.0                   | -                      | -                     | V     |

| Input Current, I <sub>INH</sub> , I <sub>INL</sub> | V+ = 2.0V, V <sub>IN</sub> = 0V or V+                                                     | 25           | -0.5                  | -                      | 0.5                   | μA    |

| Input Current, I <sub>INH</sub> , I <sub>INL</sub> | V+ = 2.0V, V <sub>IN</sub> = 0V or V+                                                     | Full         | -                     | 0.38                   | -                     | μA    |

- 9.  $V_{IN}$  = input voltage to perform proper function.

- 10. The algebraic convention, whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- 11. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 12. Flatness is defined as the difference between maximum and minimum value of on-resistance over the specified analog signal range.

- 13. r<sub>ON</sub> matching between channels is calculated by subtracting the channel with the highest max r<sub>ON</sub> value from the channel with lowest max r<sub>ON</sub> value, between NC1 and NC2 or between NO1 and NO2.

- 14. Limits established by characterization and are not production tested.

## Test Circuits and Waveforms

Logic input waveform is inverted for switches that have the opposite logic sense.

Repeat test for all switches. C<sub>L</sub> includes fixture and stray capacitance.

$V_{OUT} = V_{(NO \text{ or NC})} \frac{R_L}{R_L + r_{ON}}$

FIGURE 1B. TEST CIRCUIT

FIGURE 1A. MEASUREMENT POINTS

FIGURE 1. SWITCHING TIMES

FIGURE 2A. MEASUREMENT POINTS

Repeat test for all switches.

FIGURE 2B. TEST CIRCUIT

FIGURE 2. CHARGE INJECTION

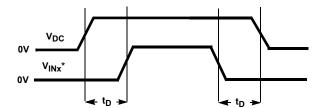

FIGURE 3A. MEASUREMENT POINTS

Repeat test for all switches.  $C_L$  includes fixture and stray capacitance.

FIGURE 3B. TEST CIRCUIT

FIGURE 3. BREAK-BEFORE-MAKE TIME

## Test Circuits and Waveforms (Continued)

Signal direction through switch is reversed, worst case values are recorded. Repeat test for all switches.

FIGURE 4. OFF-ISOLATION TEST CIRCUIT

Signal direction through switch is reversed, worst case values are recorded. Repeat test for all switches.

FIGURE 6. CROSSTALK TEST CIRCUIT

Repeat test for all switches.

FIGURE 5. ron TEST CIRCUIT

FIGURE 7. ON CAPACITANCE TEST CIRCUIT

### Test Circuits and Waveforms (Continued)

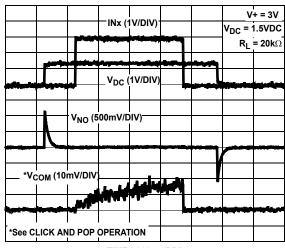

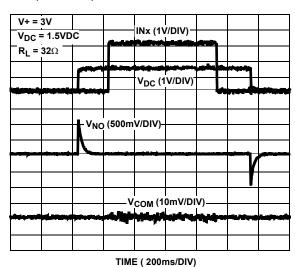

\*V<sub>INx</sub> waveform for Click and Pop Elimination on NOx terminal. For Click and Pop Elimination on NCx terminal invert V<sub>INx</sub>.

t<sub>D</sub> = 200ms measured at 50% points.

FIGURE 8A. CLICK AND POP WAVEFORM

FIGURE 8B. CLICK AND POP TEST CIRCUIT

#### FIGURE 8. CLICK AND POP ELIMINATION

# **Detailed Description**

The ISL54062 is a bi-directional, dual single pole-double throw (SPDT) analog switch that offers precise switching from a single 1.8V to 6.5V supply with low ON-resistance (0.83 $\Omega$ ), high speed operation (toN = 55ns, toFF = 18ns) and negative signal swing capability. The device is especially well suited for portable battery powered equipment due to its low operating supply voltage (1.8V), low power consumption (20nA @ 3V), and a tiny 1.8mmx1.4mm  $\mu$ TQFN package or a 3x3 TDFN package. The low ON-resistance and roN flatness provide very low insertion loss and signal distortion for applications that require signal switching with minimal interference by the switch.

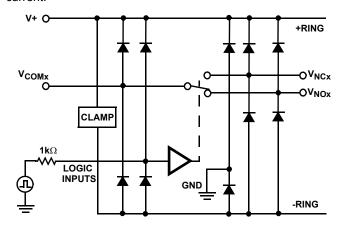

#### Supply Sequencing and Overvoltage Protection

With any CMOS device, proper power supply sequencing is required to protect the device from excessive input currents which might permanently damage the IC. The ISL54062 contains ESD protection diodes on each pin of the IC (see Figure 9). These diodes connect to either a +Ring or -Ring for ESD protection. To prevent forward biasing the ESD diodes to the +Ring, V+ must be applied before any input signals, and the input signal voltages must remain between recommended operating range.

If these conditions cannot be guaranteed, then precautions must be implemented to prohibit the current and voltage at the logic pin and signal pins from exceeding the maximum ratings of the switch. The following two methods can be used to provided additional protection to limit the current in the event that the voltage at a logic pin or switch terminal goes above the V+ rail.

Logic inputs can be protected by adding a  $1k\Omega$  resistor in series with the logic input (see Figure 9). The resistor limits the input current below the threshold that produces permanent damage.

This method is not acceptable for the signal path inputs. Adding a series resistor to the switch input defeats the purpose of using a low  $r_{ON}$  switch. Alternatively, connecting external Schottky diodes from the V+ rail to the signal pins will shunt the fault current through the Schottky diode instead of through the internal ESD diodes, thereby protecting the switch. These Schottky diodes must be sized to handle the expected fault current.

FIGURE 9. OVERVOLTAGE PROTECTION

#### Power-Supply Considerations

The ISL54062 construction is typical of most single supply CMOS analog switches which have two supply pins: V+ and GND. V+ and GND provide the CMOS switch bias and sets their analog voltage limits. Unlike switches with a 5.5V maximum supply voltage, the ISL54062's 6.5V maximum supply voltage provides plenty of head room for the 10% tolerance of 5V supplies due to overshoot and noise spikes.

The minimum recommended supply voltage is 1.8V. It is important to note that the input signal range, switching times, and ON-resistance degrade at lower supply voltages. Refer to

the "Electrical Specifications" tables, beginning on page 3, and "Typical Performance Curves", beginning on page 11, for details.

V+ and GND also power the internal logic and level shifters. The level shifters convert the input logic levels to V+ and GND signals levels to drive the analog switch gate terminals. A high frequency decoupling capacitor placed as close to the V+ and GND pin as possible is recommended for proper operation of the switch. A value of 0.1µF is highly recommended.

#### Negative Signal Swing Capability

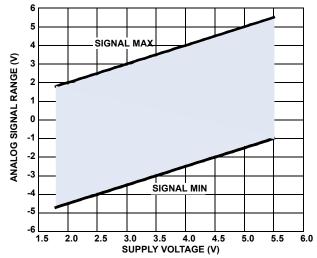

The ISL54062 contains circuitry that allows the analog switch signal to swing below ground. The device has an analog signal range of 6.5V below V+ up to the V+ rail (see Figure 16) while maintaining low  $r_{ON}$  performance. For example, if V+ = 5V, then the analog input signal range is from -1.5V to +5V. If V+ = 2.7V then the range is from -3.8V to +2.7V.

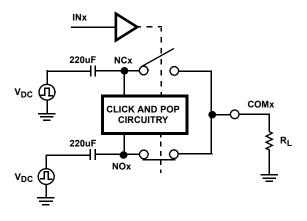

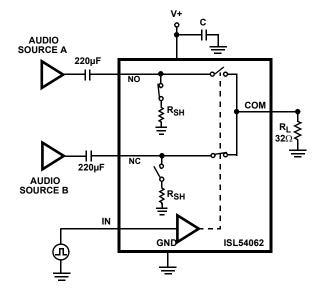

#### Click and Pop Operation

The ISL54062 contains circuitry that prevents audible click and pop noises that may occur when audio sources are powered on or off. Single supply audio sources are biased at a DC offset that can generate transients during power on/off. A DC blocking capacitor is needed to remove the DC bias at the speaker load. For  $32\Omega$  headphones, a  $220\mu\text{F}$  capacitor is typically used to preserve the audio bandwidth. The power on/off transients are AC coupled by the  $220\mu\text{F}$  capacitor to the speaker load causing a click and pop noise.

The ISL54062 has shunt switches on the NO and NC pins to eliminate click and pop transients (see Figure 10). These switches are driven complimentary to the main switch. When NC is connected to COM, the shunt switch is active on the NO pin (and vice versa). The shunt switches connect an impedance (140 $\Omega$  typical, see Figure 24) from the NO/NC pin to ground to discharge any transients that may appear on the NO or NC pins.

When a DC bias becomes active at the source, the NO and NC terminals will also have a DC offset due to capacitor dv/dt principle. The DC offset will be discharged through the shunt impedance on the NO and NC terminals instead of the speaker, eliminating click and pop noise.

\*Under high impedance loads such as the input impedance of pre-amplifiers ( $20k\Omega$ ), the COM terminal voltage may rise due to small leakage currents charging the COM capacitance. This is not seen when low impedance loads such as headphones ( $32\Omega$ ) are used because the small leakage currents does not result in significant potential drop across the load. If the user desires to reduce the voltage build up on the COM pin, a  $1k\Omega$  resistor to ground may be placed on the COM pin. This impedance is small enough to reduce the voltage build up significantly while not increasing the power dissipation dramatically. Current consumption considerations will need to

be taken for driving a smaller load impedance under this scenario.

FIGURE 10. CLICK AND POP OPERATION

#### Click and Pop Elimination with INx Pin

Audio click and pop elimination can be driven with the Input Select (INx) pin. When INx = 0, the NOx terminals are connected to the shunt impedance. When INx = 1, the NCx terminals are connected to the shunt impedance. In this situation, only one of the source transient voltages will be shunted to ground, depending on the Input Select state. The Input Select pin should be driven 200ms after any source transients occurs to prevent audible transients at the speaker load.

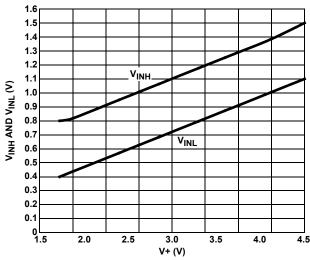

### Logic-Level Thresholds

This switch family is 1.8V CMOS compatible (0.45V  $V_{OLMAX}$  and 1.35V  $V_{OHMIN}$ ) over a supply range of 1.8V to 3.3V (see Figure 18). At 3.3V the  $V_{IL}$  level is 0.5V maximum. This is still below the 1.8V CMOS guaranteed low output maximum level of 0.45V, but noise margin is reduced to approximately 50mV. At 3.3V the  $V_{IH}$  level is 1.4V minimum. While this is above the 1.8V CMOS guaranteed high output minimum of 1.35V, under most operating conditions the switch will recognize this as a valid logic high.

The digital input stages draw supply current whenever the digital input voltage is not at one of the supply rails. Driving the digital input signals from GND to V+ with a fast transition time minimizes power dissipation. The ISL54062 has been designed to minimize the supply current whenever the digital input voltage is not driven to the supply rails (0V to V+). For example, driving the device with 2.85V logic high while operating with a 4.2V supply the device draws only  $1\mu A$  of current.

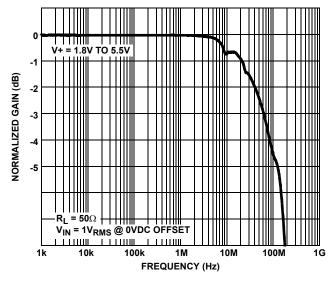

#### **High-Frequency Performance**

In  $50\Omega$  systems, the ISL54062 has an ON switch -3dB bandwidth of 60MHz (see Figure 21). The frequency response

is very consistent over a wide V+ range, and for varying analog signal levels.

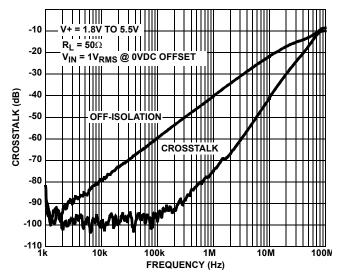

An OFF switch acts like a capacitor across the open terminals and AC couples higher frequencies, resulting in signal feedthrough from a switch's input to its output. Off-Isolation is the resistance to this feed-through. Crosstalk indicates the amount of feed-through from one switch channel to another switch channel. Figure 22 details the high Off-Isolation and Crosstalk rejection provided by this part. At 100kHz, Off-Isolation is about 60dB in  $50\Omega$  systems, decreasing approximately 20dB per decade as frequency increases. At 1MHz, Crosstalk is about -75dB in  $50\Omega$  systems, decreasing approximately 20dB per decade as frequency increases.

### Leakage Considerations

Reverse ESD protection diodes are internally connected between each analog-signal pin, V+ and GND. One of these diodes conducts if any analog signal exceeds the recommended analog signal range.

Virtually all the analog switch leakage current comes from the ESD diodes and reversed biased junctions in the switch cell. Although the ESD diodes on a given signal pin are identical and therefore fairly well balanced, they are reverse biased differently. Each is biased to either the +Ring or -Ring and the analog input signal. This means their leakages will vary as the signal varies. The difference in the two diode leakages to the +Ring or -Ring and the reverse biased junctions at the internal switch cell constitutes the analog-signal-path leakage current.

### Typical Performance Curves T<sub>A</sub> = +25°C, Unless Otherwise Specified

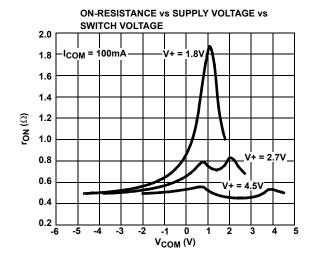

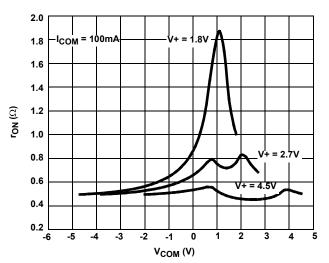

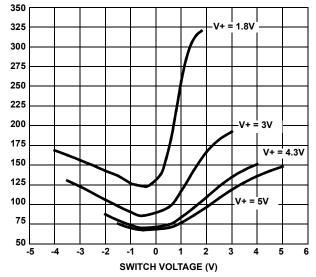

FIGURE 11. ON-RESISTANCE vs SUPPLY VOLTAGE vs SWITCH VOLTAGE

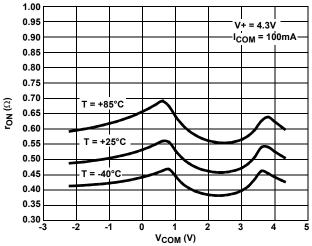

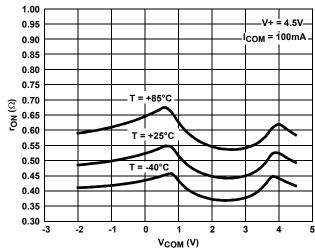

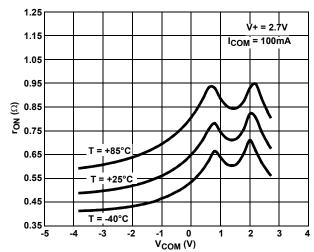

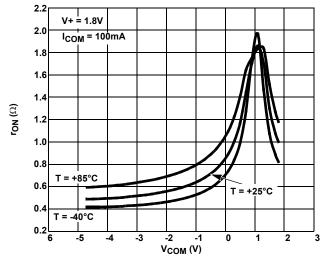

FIGURE 13. ON-RESISTANCE vs SWITCH VOLTAGE

FIGURE 12. ON-RESISTANCE vs SWITCH VOLTAGE

FIGURE 14. ON-RESISTANCE vs SWITCH VOLTAGE

# Typical Performance Curves T<sub>A</sub> = +25°C, Unless Otherwise Specified (Continued)

FIGURE 15. ON-RESISTANCE vs SWITCH VOLTAGE

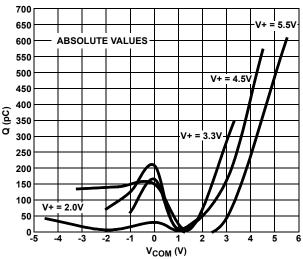

FIGURE 17. CHARGE INJECTION vs SWITCH VOLTAGE

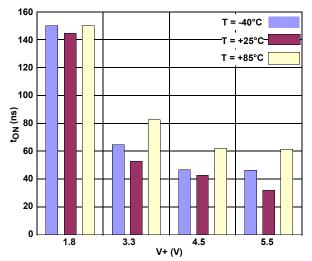

FIGURE 19. TURN-ON TIME vs SUPPLY VOLTAGE

FIGURE 16. ANALOG SIGNAL RANGE vs SUPPLY VOLTAGE

FIGURE 18. DIGITAL SWITCHING POINT vs SUPPLY VOLTAGE

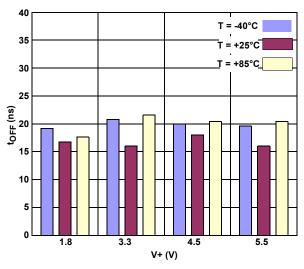

FIGURE 20. TURN-OFF TIME vs SUPPLY VOLTAGE

# Typical Performance Curves T<sub>A</sub> = +25°C, Unless Otherwise Specified (Continued)

FIGURE 21. FREQUENCY RESPONSE

FIGURE 22. CROSSTALK AND OFF-ISOLATION

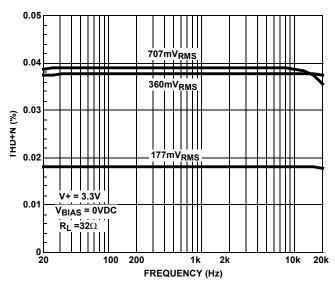

FIGURE 23. TOTAL HARMONIC DISTORTION vs FREQUENCY

FIGURE 24. SHUNT RESISTANCE vs SWITCH VOLTAGE

RENESAS

# Typical Performance Curves $T_A = +25$ °C, Unless Otherwise Specified (Continued)

TIME ( 200ms/DIV)

FIGURE 25. CLICK AND POP ELIMINATION  $20k\Omega$  LOAD 200ms DELAY

# Die Characteristics

#### SUBSTRATE POTENTIAL (POWERED UP):

GND (DFN Paddle Connection: Tie to GND or Float)

#### TRANSISTOR COUNT:

432

#### PROCESS:

Submicron CMOS

FIGURE 26. CLICK AND POP ELIMINATION 32  $\Omega$  LOAD 200ms DELAY

© Copyright Intersil Americas LLC 2009. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see <a href="https://www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

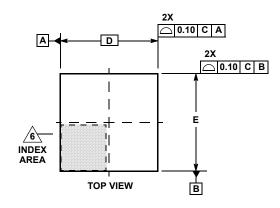

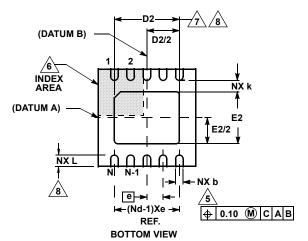

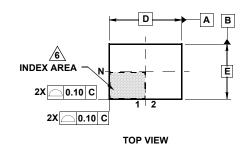

# Thin Dual Flat No-Lead Plastic Package (TDFN)

L10.3x3A

10 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE

|        | ı        |         |      |       |

|--------|----------|---------|------|-------|

| SYMBOL | MIN      | NOMINAL | MAX  | NOTES |

| Α      | 0.70     | 0.75    | 0.80 | -     |

| A1     | -        | -       | 0.05 | -     |

| A3     | 0.20 REF |         |      | -     |

| b      | 0.20     | 0.25    | 0.30 | 5, 8  |

| D      | 2.95     | 3.0     | 3.05 | -     |

| D2     | 2.25     | 2.30    | 2.35 | 7, 8  |

| E      | 2.95     | 3.0     | 3.05 | -     |

| E2     | 1.45     | 1.50    | 1.55 | 7, 8  |

| е      | 0.50 BSC |         |      | -     |

| k      | 0.25     | -       | -    | -     |

| L      | 0.25     | 0.30    | 0.35 | 8     |

| N      | 10       |         |      | 2     |

| Nd     | 5        |         |      | 3     |

Rev. 3 3/06

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- 3. Nd refers to the number of terminals on D.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Dimensions D2 and E2 are for the exposed pads which provide improved electrical and thermal performance.

- 8. Nominal dimensions are provided to assist with PCB Land Pattern Design efforts, see Intersil Technical Brief TB389.

- Compliant to JEDEC MO-229-WEED-3 except for D2 dimensions.

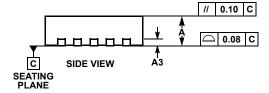

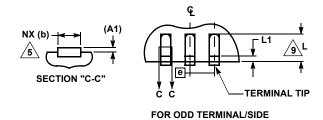

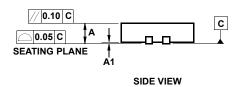

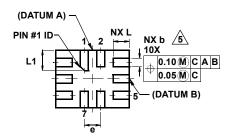

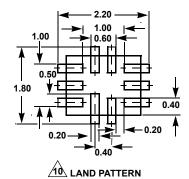

# Ultra Thin Quad Flat No-Lead Plastic Package (UTQFN)

NX (b) (A1)

SECTION "C-C"

C C TERMINAL TIP

**BOTTOM VIEW**

L10.1.8x1.4A

10 LEAD ULTRA THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE

|        | ı         |         |      |       |

|--------|-----------|---------|------|-------|

| SYMBOL | MIN       | NOMINAL | MAX  | NOTES |

| А      | 0.45      | 0.50    | 0.55 | -     |

| A1     | -         | -       | 0.05 | -     |

| A3     | 0.127 REF |         |      | -     |

| b      | 0.15      | 0.20    | 0.25 | 5     |

| D      | 1.75      | 1.80    | 1.85 | -     |

| E      | 1.35      | 1.40    | 1.45 | -     |

| е      | 0.40 BSC  |         |      | -     |

| L      | 0.35      | 0.40    | 0.45 | -     |

| L1     | 0.45      | 0.50    | 0.55 | -     |

| N      | 10        |         |      | 2     |

| Nd     | 2         |         |      | 3     |

| Ne     | 3         |         |      | 3     |

| θ      | 0         | -       | 12   | 4     |

Rev. 3 6/06

- 1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

- 2. N is the number of terminals.

- Nd and Ne refer to the number of terminals on D and E side, respectively.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Maximum package warpage is 0.05mm.

- 8. Maximum allowable burrs is 0.076mm in all directions.

- 9. JEDEC Reference MO-255.

- For additional information, to assist with the PCB Land Pattern Design effort, see Intersil Technical Brief TB389.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analogue Switch ICs category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

FSA3051TMX NLAS4684FCTCG NLAS5223BLMNR2G NLVAS4599DTT1G NLX2G66DMUTCG 425541DB 425528R 099044FB

NLAS5123MNR2G PI5A4599BCEX NLAS4717EPFCT1G PI5A3167CCEX SLAS3158MNR2G PI5A392AQE PI5A4157ZUEX

PI5A3166TAEX FSA634UCX TC4066BP(N,F) DG302BDJ-E3 PI5A100QEX HV2605FG-G HV2301FG-G RS2117YUTQK10

RS2118YUTQK10 RS2227XUTQK10 ADG452BRZ-REEL7 MAX4066ESD+ MAX391CPE+ MAX4730EXT+T MAX314CPE+

BU4066BCFV-E2 MAX313CPE+ BU4S66G2-TR NLAS3158MNR2G NLASB3157MTR2G TS3A4751PWR NLAS4157DFT2G

NLAS4599DFT2G NLAST4599DFT2G NLAST4599DTT1G DG300BDJ-E3 DG2503DB-T2-GE1 DG2502DB-T2-GE1

TC4W53FU(TE12L,F) 74HC2G66DC.125 ADG619BRMZ-REEL ADG1611BRUZ-REEL7 LTC201ACN#PBF 74LV4066DB,118

FSA2275AUMX