# RENESAS

# DATASHEET

# ISL6535

Synchronous Buck Pulse-Width Modulator (PWM) Controller

FN9255 Rev 4.00 January 4, 2021

The <u>ISL6535</u> is a high performance synchronous controller for demanding DC/DC converter applications. It provides overcurrent fault protection and is designed to safely start-up into prebiased output loads.

The output voltage of the converter can be precisely regulated to as low as 0.597V, with a maximum tolerance of  $\pm 1\%$  over the commercial temperature range, and  $\pm 1.5\%$  over the industrial temperature range.

The ISL6535 provides simple, single feedback loop, voltage mode control with fast transient response. It includes a triangle wave oscillator that is adjustable from below 50kHz to over 1.5MHz. Full (0% to 100%) PWM duty cycle support is provided.

The error amplifier features a 15MHz gain bandwidth product and  $6V/\mu s$  slew rate, which enables high converter bandwidth for fast transient performance.

The ISL6535's overcurrent protection monitors the current by using the  $r_{\mbox{DS}(\mbox{ON})}$  of the upper MOSFET, which eliminates the need for a current sensing resistor.

#### **Pin Configurations** ISL6535 (14 LD SOIC) TOP VIEW 14 VCC RT 1 OCSET 2 13 PVCC SS 3 12 LGATE COMP 4 11 PGND FB 5 10 BOOT EN 6 9 UGATE GND 8 PHASE ISL6535 (16 LD QFN) TOP VIEW SSDON OCSET 202 R 13 O 16 i 15 i i 14 i PVCC SS 12 COMP LGATE PAD 10 PGND FB EN 9 BOOT л 6 17 8 5

GND GND UGATE

## **Features**

- Operates from +12V input

- Excellent output voltage regulation

- 0.597V internal reference

- ±1% over the commercial temperature range

- ±1.5% over the industrial temperature range

- Simple single-loop control design

- Voltage-mode PWM control

- Fast transient response

- High-bandwidth error amplifier

- Full 0% to 100% duty ratio

- Leading and falling edge modulation

- Small converter size

- Constant frequency operation

- Oscillator programmable from 50kHz to over 1.5MHz

- 12V high-speed MOSFET gate drivers

- 2.0A source/3A sink at 12V low-side gate drive

- 1.25A source/2A sink at 12V high-side gate drive

- Drives two N-channel MOSFETs

- Overcurrent fault monitor

- High-side MOSFET's r<sub>DS(ON)</sub> sensing

- Reduced ~120ns blanking time

- · Converter can source and sink current

- Soft-start done and an external reference pin for tracking applications are available in the QFN package

- Pin compatible with ISL6522

- Supports start-up into prebiased loads

- Pb-free (RoHS compliant)

### **Applications**

- Power Supply for some Pentium<sup>™</sup>, PowerPC<sup>™</sup>, as well as graphic CPUs

- High-power 12V input DC/DC regulators

- · Low-voltage distributed power supplies

# **Pin Descriptions**

| PIN #<br>SOIC | PIN #<br>QFN | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|---------------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

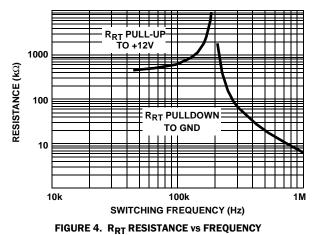

| 1             | 14           | RT       | $\label{eq:response} \begin{array}{l} \mbox{This pin provides oscillator switching frequency adjustment. By placing a resistor (R_{RT}) from this pin to GND, the switching frequency is set from between 200kHz and 1.5MHz according Equation 1: R_{RT}[k\Omega] \approx \frac{6500}{F_{S}[kHz] - 200[kHz]} - 1.3k\Omega \qquad \mbox{(R}_{RT} \mbox{ to GND)} \end{tabular}$ |  |  |

|               |              |          | connecting the RT pin with a resistor to VCC according to Equation 2:<br>$R_{RT}[k\Omega] \approx \frac{55000}{200[kHz] - F_{s}[kHz]} + 70k\Omega \qquad (R_{RT} \text{ to VCC})$ (EQ. 2)                                                                                                                                                                                      |  |  |

| 2             | 15           | OCSET    | The current limit is programmed by connecting this pin with a resistor and capacitor to the drain of the high-side MOSEFT. A 200µA current source develops a voltage across the resistor, which is then compared with the voltage developed across the high-side MOSFET. A blanking period of 120ns is provided for noise immunity.                                            |  |  |

| 3             | 1            | SS       | Connect a capacitor from this pin to ground. This capacitor, along with an internal $30\mu A$ current source, sets the soft-start interval of the converter.                                                                                                                                                                                                                   |  |  |

| 4             | 2            | COMP     | COMP and FB are the available external pins of the error amplifier. The FB pin is the inverting                                                                                                                                                                                                                                                                                |  |  |

| 5             | 3            | FB       | input of the error amplifier and the COMP pin is the error amplifier output. These pins are used to compensate the voltage-control feedback loop of the converter.                                                                                                                                                                                                             |  |  |

| 6             | 4            | EN       | This pin is a TTL compatible input. Pull this pin below 0.8V to disable the converter. In shutdown the soft-start pin is discharged and the UGATE and LGATE pins are held low.                                                                                                                                                                                                 |  |  |

| 7             | 6            | GND      | Signal ground for the IC. All voltage levels are measured with respect to this pin.                                                                                                                                                                                                                                                                                            |  |  |

| 8             | 7            | PHASE    | This pin connects to the source of the high-side MOSFET and the drain of the low-side MOSFET. This pin represents the return path for the high-side gate driver. During normal switching, this pin is used for high-side current sensing.                                                                                                                                      |  |  |

| 9             | 8            | UGATE    | Connect UGATE to the upper MOSFET gate. This pin provides the gate drive for the upper MOSFET.                                                                                                                                                                                                                                                                                 |  |  |

| 10            | 9            | воот     | This pin provides bias to the upper MOSFET driver. A bootstrap circuit may be used to create a BOOT voltage suitable to drive a standard N-channel MOSFET.                                                                                                                                                                                                                     |  |  |

| 11            | 10           | PGND     | This is the power ground connection. Tie the lower MOSFET source and board ground to this pin.                                                                                                                                                                                                                                                                                 |  |  |

| 12            | 11           | LGATE    | Connect LGATE to the lower MOSFET gate. This pin provides the gate drive for the lower MOSFET.                                                                                                                                                                                                                                                                                 |  |  |

| 13            | 12           | PVCC     | Provide a $12V \pm 10\%$ bias supply for the lower gate drive to this pin. This pin should be bypassed with a capacitor to PGND.                                                                                                                                                                                                                                               |  |  |

| 14            | 13           | VCC      | Provide a 12V bias supply for the chip to this pin. The pin should be bypassed with a capacitor to GND.                                                                                                                                                                                                                                                                        |  |  |

| -             | 5            | REFIN    | Upon enable if REFIN is less than 2.2V, the external reference pin is used as the control reference instead of the internal 0.597V reference. An internal 6µA pull-up to 5V is provided for disabling this functionality.                                                                                                                                                      |  |  |

| -             | 16           | SSDONE   | Provides an open-drain signal at the end of soft-start.                                                                                                                                                                                                                                                                                                                        |  |  |

| -             | PAD          | EPAD     | The exposed pad is at GND potential, but does not conduct current; the GND and PGND pins must be used for bias current. The pad should be tied to a GND plane with as many thermal vias as possible, for optimal thermal performance.                                                                                                                                          |  |  |

# **Ordering Information**

| PART NUMBER<br>(Notes 4, 5)  | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |

|------------------------------|-----------------|---------------------|-----------------------------|----------------|

| ISL6535CBZ (Note 1)          | 6535CBZ         | 0 to +70            | 14 Ld SOIC                  | M14.15         |

| ISL6535IBZ ( <u>Note 1</u> ) | 6535IBZ         | -40 to +85          | 14 Ld SOIC                  | M14.15         |

| ISL6535CRZ ( <u>Note 2</u> ) | 65 35CRZ        | 0 to +70            | 16 Ld 4x4 QFN               | L16.4x4        |

| ISL6535IRZ ( <u>Note 3</u> ) | 65 35IRZ        | -40 to +85          | 16 Ld 4x4 QFN               | L16.4x4        |

1. Add "-T" suffix for 2.5k unit tape and reel option. Please refer to TB347 for details on reel specifications.

2. Add "-T" suffix for 6k unit tape and reel option. Please refer to TB347 for details on reel specifications.

3. Add "-T" suffix for 6k unit or -TK for 1k unit tape and reel options. Please refer to TB347 for details on reel specifications.

- 4. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 5. For Moisture Sensitivity Level (MSL), please see product information page for ISL6535. For more information on MSL, please see tech brief TB363.

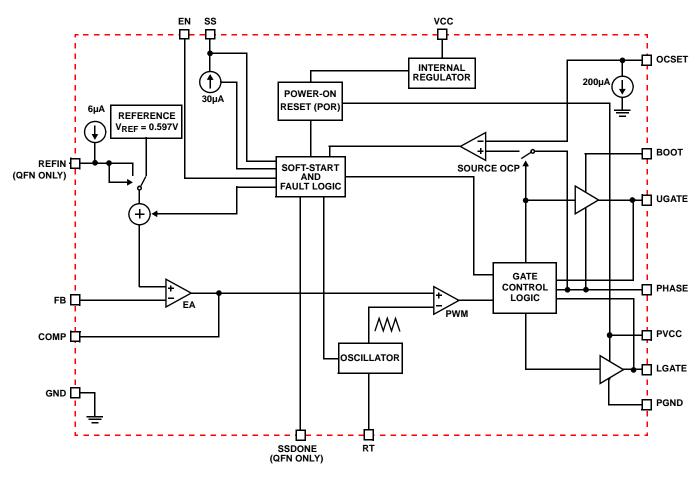

## **Block Diagram**

FIGURE 1. BLOCK DIAGRAM

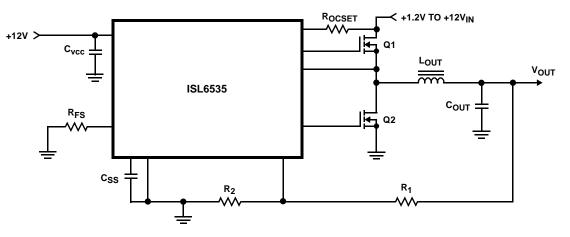

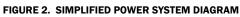

# **Simplified Power System Diagram**

FIGURE 3. TYPICAL APPLICATION

#### **Absolute Maximum Ratings**

| Supply Voltage, V <sub>PVCC</sub> , V <sub>VCC</sub> (GND - 0.3V) to + 16V               |  |

|------------------------------------------------------------------------------------------|--|

| Enable Voltage, V <sub>EN</sub> (GND - 0.3V) to + 16V                                    |  |

| Soft-start Done Voltage, V <sub>SSDONE</sub> (GND - 0.3V) to + 16V                       |  |

| OCSET Voltage, V <sub>OCSET</sub> (GND - 0.3V) to + 16V                                  |  |

| Boot Voltage, V <sub>BOOT</sub> (GND - 0.3V) to + 36V                                    |  |

| Phase Voltage, V <sub>PHASE</sub> (V <sub>BOOT</sub> - 16V) to V <sub>BOOT</sub> + 0.3V  |  |

| UGATE Voltage V <sub>UGATE</sub> (V <sub>PHASE</sub> - 0.3V) to V <sub>BOOT</sub> + 0.3V |  |

| LGATE Voltage V <sub>LGATE</sub> (GND - 0.3V) to V <sub>PVCC</sub> + 0.3V                |  |

| All Other Pins                                                                           |  |

| ESD Rating                                                                               |  |

| ESD Classification Class 2                                                               |  |

|                                                                                          |  |

#### **Recommended Operating Conditions**

| Supply Voltage                                                |

|---------------------------------------------------------------|

| V <sub>VCC</sub> , V <sub>PVCC</sub>                          |

| Boot to Phase Voltage, V <sub>BOOT</sub> - V <sub>PHASE</sub> |

| Ambient Temperature Range                                     |

| ISL6535C0°C to +70°C                                          |

| ISL6535I40°C to +85°C                                         |

#### **Thermal Information**

| Thermal Resistance (Typical)              | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C∕W) |

|-------------------------------------------|------------------------|------------------------|

| SOIC Package ( <u>Notes 6, 8</u> )        | 80                     | 45                     |

| QFN Package ( <u>Notes 7</u> , <u>9</u> ) | 42                     | 4                      |

| Maximum Junction Temperature              |                        | +150°C                 |

| Maximum Storage Temperature Range         | 6                      | 5°C to +150°C          |

| Pb-Free Reflow Profile                    |                        | see <u>TB493</u>       |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 6.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board. See Tech Brief <u>TB379</u>.

- 7. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>.

- 8. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

- 9. For  $\theta_{JC}$  the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Recommended Operating Conditions, unless otherwise noted specifications. **Boldface limits apply across the** operating temperature range, -40°C to +85°C (ISL6535I), 0°C to +70°C (ISL6535C).

| PARAMETER                                           | SYMBOL            | TEST CONDITIONS                                               | MIN<br>(Note 11) | ТҮР  | MAX<br>( <u>Note 11</u> ) | UNIT             |

|-----------------------------------------------------|-------------------|---------------------------------------------------------------|------------------|------|---------------------------|------------------|

| V <sub>CC</sub> SUPPLY CURRENT                      |                   |                                                               | ,                |      | ,,                        |                  |

| Shutdown Supply V <sub>CC</sub>                     | Ivcc              | SS/EN = OV                                                    | 3.5              | 6.1  | 8.5                       | mA               |

| Shutdown Supply V <sub>PVCC</sub>                   | IPVCC             | SS/EN = OV                                                    | 0.30             | 0.50 | 0.75                      | mA               |

| POWER-ON RESET                                      |                   |                                                               |                  |      |                           |                  |

| V <sub>CC</sub> /V <sub>PVCC</sub> Rising Threshold |                   |                                                               | 6.45             | 7.10 | 7.55                      | v                |

| V <sub>CC</sub> /V <sub>PVCC</sub> Hysteresis       |                   |                                                               | 170              | 250  | 500                       | mV               |

| OCSET Rising Threshold                              |                   |                                                               | 0.70             | 0.73 | 0.75                      | ۷                |

| OCSET Hysteresis                                    |                   |                                                               | 180              | 200  | 220                       | mV               |

| Enable - Rising Threshold                           |                   |                                                               | 1.40             | 1.50 | 1.60                      | v                |

| Enable - Hysteresis                                 |                   |                                                               | 175              | 250  | 325                       | mV               |

| OSCILLATOR                                          |                   |                                                               |                  |      | <u> </u>                  |                  |

| Trim Test Frequency                                 |                   | R <sub>RT</sub> = OPEN V <sub>VCC</sub> = 12                  | 175              | 200  | 220                       | kHz              |

| Total Variation                                     |                   | $8k\Omega < R_{RT}$ to GND < 200k $\Omega$ ( <u>Note 10</u> ) | -                | ±15  | -                         | %                |

| Ramp Amplitude                                      | ΔV <sub>OSC</sub> | R <sub>RT</sub> = OPEN                                        | 1.7              | 1.9  | 2.15                      | V <sub>P-P</sub> |

| ERROR AMPLIFIER                                     | 1                 |                                                               | 1                |      | u 1                       |                  |

| DC Gain                                             |                   | $R_L = 10k\Omega, C_L = 100pF$ ( <u>Note 10</u> )             | -                | 88   | -                         | dB               |

| Gain-Bandwidth Product                              | GBWP              | $R_L = 10$ kΩ, $C_L = 100$ pF ( <u>Note 10</u> )              | -                | 15   | -                         | MHz              |

**Electrical Specifications** Recommended Operating Conditions, unless otherwise noted specifications. **Boldface limits apply across the operating temperature range**, -40°C to +85°C (ISL6535I), 0°C to +70°C (ISL6535C). (Continued)

| PARAMETER                       | SYMBOL                | TEST CONDITIONS                                                           | MIN<br>( <u>Note 11</u> ) | ТҮР   | MAX<br>( <u>Note 11</u> ) | UNIT |

|---------------------------------|-----------------------|---------------------------------------------------------------------------|---------------------------|-------|---------------------------|------|

| Slew Rate                       | SR                    | $R_L = 10k\Omega, C_L = 100pF(Note 10)$                                   | -                         | 6     | -                         | V/µs |

| PROTECTION                      | <b>I</b>              |                                                                           | I                         |       |                           |      |

| OCSET Current                   | IOCSET                | $T_J = 0^{\circ}C \text{ to } +70^{\circ}C$                               | 180                       | 200   | 220                       | μA   |

| OCSET Current                   | IOCSET                | T <sub>J</sub> = -40 °C to +85 °C                                         | 176                       | 200   | 224                       | μA   |

| OCSET Measurement Offset        | OCP <sub>OFFSET</sub> | OCSET= 1.5V to 15.4V ( <u>Note 10</u> )                                   | -                         | ±10   | -                         | mV   |

| Soft-Start Current              | I <sub>SS</sub>       |                                                                           | 22                        | 30    | 38                        | μA   |

| REFERENCE                       | L.                    |                                                                           |                           | 1     |                           |      |

| Reference Voltage               |                       | $T_J = 0^{\circ}C \text{ to } +70^{\circ}C$                               | 0.591                     | 0.597 | 0.603                     | v    |

|                                 |                       | T <sub>J</sub> = -40°C to +85°C                                           | 0.588                     | 0.597 | 0.606                     | V    |

| System Accuracy                 |                       | $T_J = 0^{\circ}C \text{ to } +70^{\circ}C$                               | -1.0                      | -     | 1.0                       | %    |

|                                 |                       | $T_J = -40^{\circ}C \text{ to } +85^{\circ}C$                             | -1.5                      | -     | 1.5                       | %    |

| REFIN Current Source (QFN Only) |                       |                                                                           | -4                        | -6    | -8                        | μA   |

| REFIN Threshold (QFN Only)      |                       |                                                                           | 2.10                      | -     | 3.50                      | v    |

| REFIN Offset (QFN Only)         |                       |                                                                           | -3                        | -     | 3                         | mV   |

| GATE DRIVERS                    | <b>I</b>              |                                                                           | I                         |       |                           |      |

| Upper Drive Source Current      | IU_SOURCE             | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V, 3nF Load ( <u>Note 10</u> ) | -                         | 1.25  | -                         | Α    |

| Upper Drive Source Impedance    | R <sub>U_SOURCE</sub> | 90mA Source Current                                                       | -                         | 2.0   | -                         | Ω    |

| Upper Drive Sink Current        | I <sub>U_SINK</sub>   | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V, 3nF Load ( <u>Note 10</u> ) | -                         | 2     | -                         | Α    |

| Upper Drive Sink Impedance      | R <sub>U_SINK</sub>   | 90mA Source Current                                                       | -                         | 1.3   | -                         | Ω    |

| Lower Drive Source Current      | IL_SOURCE             | V <sub>PVCC</sub> = 12V, 3nF Load ( <u>Note 10</u> )                      | -                         | 2     | -                         | Α    |

| Lower Drive Source Impedance    | RL_SOURCE             | 90mA Source Current                                                       | -                         | 1.3   | -                         | Ω    |

| Lower Drive Sink Current        | IL_SINK               | V <sub>PVCC</sub> = 12V, 3nF Load ( <u>Note 10</u> )                      | -                         | 3     | -                         | Α    |

| Lower Drive Sink Impedance      | R <sub>L_SINK</sub>   | 90mA Source Current                                                       | -                         | 0.94  | -                         | Ω    |

| SSDONE (QFN ONLY)               | 1                     |                                                                           | 1                         | ı     | ·                         |      |

| SSDONE Low Output Voltage       |                       | I <sub>SSDONE</sub> = 2mA                                                 | -                         | -     | 0.30                      | v    |

NOTE:

10. Limits should be considered typical and are not production tested.

11. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

## **Typical Performance Curves**

### **Functional Description**

#### Initialization

The ISL6535 automatically initializes upon receipt of power. Special sequencing of the input supplies is not necessary. The Power-On Reset (POR) function continually monitors the bias voltage at the VCC pin and the driver input on the PVCC pin. When the voltages at VCC and PVCC exceed their rising POR thresholds, a 30µA current source driving the SS pin is enabled. Upon the SS pin exceeding 1V, the ISL6535 begins ramping the noninverting input of the error amplifier from GND to the System Reference. During initialization the MOSFET drivers, pull UGATE to PHASE and LGATE to PGND.

#### Soft-Start

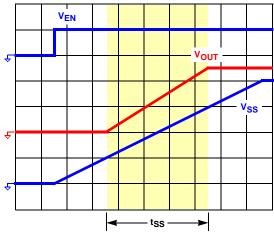

During soft-start, an internal  $30\mu$ A current source charges the external capacitor (C<sub>SS</sub>) on the SS pin up to ~4V. If the ISL6535 is utilizing the internal reference, then as the SS pin's voltage ramps from 1V to 3V, the soft-start function scales the reference input (positive terminal of error amp) from GND to VREF (0.597V nominal). If the ISL6535 is utilizing an externally supplied reference, when the voltage on the SS pin reaches 1V, the internal reference input (into of the error amp) ramps from GND to the externally supplied reference at the same rate as the voltage on the SS pin. Figure 6 shows a typical soft-start interval. The rise time of the output voltage is, therefore, dependent upon the value of the soft-start capacitor, CSS. If the internal reference is used, then the soft-start capacitance value can be calculated through Equation 3:

$$C_{SS} = \frac{30\mu A \cdot t_{SS}}{2V}$$

(EQ. 3)

If an external reference is used, then the soft-start capacitance can be calculated through Equation 4:

$$C_{SS} = \frac{30\mu A \cdot t_{SS}}{V_{REFEXT}}$$

(EQ. 4)

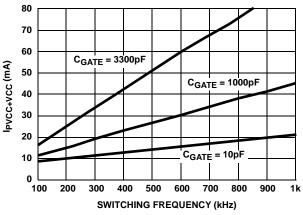

FIGURE 5. BIAS SUPPLY CURRENT vs FREQUENCY

FIGURE 6. TYPICAL SOFT-START INTERVAL

#### **Prebiased Load Start-Up**

Drivers are held in tri-state (UG pulled to Phase, LG pulled to PGND) at the beginning of a soft-start cycle until two PWM pulses are detected. The low-side MOSFET is turned on first to provide for charging of the bootstrap capacitor. This method of driver activation provides support for start-up into prebiased loads by not activating the drivers until the control loop has entered its linear region, thereby substantially reducing output transients that would otherwise occur had the drivers been activated at the beginning of the soft-start cycle.

#### SSDONE

Soft-start is only available in the 16 Ld QFN packaging option of the ISL6535. When the soft-start pin reaches 4V, an open drain signal is provided to support sequencing requirements. The SSDONE is deasserted by disabling of the part, including pulling SS low, and by POR and OCP events.

#### Oscillator

The oscillator is a triangular waveform, providing for leading and falling edge modulation. The peak-to-peak of the ramp amplitude is set at 1.9V and varies as a function of frequency. At 50kHz the peak-to-peak amplitude is approximately 1.8V while at 1.5MHz it is approximately 2.2V. In the event the regulator operates at 100% duty cycle for 64 clock cycles an automatic boot cap refresh circuit will activate turning on LG for approximately 1/2 of a clock cycle.

#### **Overcurrent Protection**

The OCP function is enabled with the drivers at start-up. OCP is implemented via a resistor ( $R_{OCSET}$ ) and a capacitor ( $C_{OCSET}$ ) connecting the OCSET pin and the drain of the high-side MOSEFT. An internal 200µA current source develops a voltage across  $R_{OCSET}$ , which is then compared with the voltage developed across the high-side MOSFET at turn-on as measured at the PHASE pin. When the voltage drop across the MOSFET exceeds the voltage drop across the resistor, a sourcing OCP event occurs. The  $C_{OCSET}$  is placed in parallel with  $R_{OCSET}$  to smooth the voltage across  $R_{OCSET}$  in the presence of switching noise on the input bus.

A 120ns blanking period is used to reduce the current sampling error due to leading-edge switching noise. An additional simultaneous 120ns low pass filter is used to further reduce measurement error due to noise.

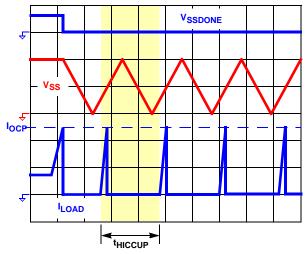

OCP faults cause the regulator to disable (upper and lower drives disabled, SSDONE pulled low, soft-start capacitor discharged) itself for a fixed period of time, after which a normal soft-start sequence is initiated. If the voltage on the SS pin is already at 4V and an OCP is detected, a 30µA current sink is immediately applied to the SS pin. If an OCP is detected during soft-start, the 30µA current sink will not be applied until the voltage on the SS pin has reached 4V. This current sink discharges the CSS capacitor in a linear fashion. Once the voltage on the SS pin has reached approximately 0V, the normal soft-start sequence is initiated. If the fault is still present on the subsequent restart, the ISL6535 will repeat this process in a hiccup mode. Figure 7 shows a typical reaction to a repeated overcurrent condition that places the regulator in a hiccup mode. If the regulator is

repeatedly tripping overcurrent, the hiccup period can be approximated by <u>Equation 5</u>:

$$t_{\text{HICCUP}} = \frac{8V \cdot C_{\text{SS}}}{30\mu\text{A}}$$

(EQ. 5)

The OCP trip point varies mainly due to MOSFET  $r_{DS(ON)}$  variations and layout noise concerns. To avoid overcurrent tripping in the normal operating load range, find the ROCSET resistor from the following equations with:

1. The maximum  $r_{DS(ON)}$  at the highest junction temperature.

2. The minimum I<sub>OCSET</sub> from the specification table.

Determine the overcurrent trip point greater than the maximum output continuous current at maximum inductor ripple current.

$$R_{OCSET} = \frac{I_{OC\_SOURCE} \bullet r_{DS(ON)}}{200 \mu A}$$

DETAILED OCP EQUATION

$$R_{OCSET} = \frac{\left(I_{OC}SOURCE} + \frac{\Delta I}{2}\right) \bullet r_{DS(ON)}}{I_{HSOC} \bullet N_{II}}$$

$$\Delta I = \frac{V_{IN} - V_{OUT}}{f_{SW} \bullet L_{OUT}} \bullet \frac{V_{OUT}}{V_{IN}}$$

$f_{SW}$  = Regulator Switching Frequency (EQ. 6)

#### **High Speed MOSFET Gate Driver**

The integrated driver has the same drive capability and feature as the Intersil's 12V gate driver, ISL6612. The PWM tri-state feature helps prevent a negative transient on the output voltage when the output is being shut down. This eliminates the Schottky diode that is used in some systems for protecting the microprocessor from reversed output voltage damage. See the <u>ISL6612</u> datasheet for specification parameters that are not defined in the current ISL6535 "Electrical Specifications" table on <u>page 5</u>.

#### **Reference Input**

The REFIN pin allows the user to bypass the internal 0.597V reference with an external reference. If REFIN is NOT above ~2.2V, the external reference pin is used as the control reference instead of the internal 0.597V reference. When is not using the external reference option, the REFIN pin should be left floating. An internal 6 $\mu$ A pull-up keeps this REFIN pin above 2.2V in this situation.

#### **Internal Reference and System Accuracy**

The internal reference is set to 0.597V. The total DC system accuracy of the system is to be within 1.0% over commercial temperature range and 1.5% over the industrial temperature range. System accuracy includes error amplifier offset and reference error. The use of REFIN may add up to 3mV of offset error into the system (as the error amplifier offset is trimmed out via the internal system reference).

FN9255 Rev 4.00 January 4, 2021

# **Application Guidelines**

#### **Layout Considerations**

As in any high frequency switching converter, layout is very important. Switching current from one power device to another can generate voltage transients across the impedances of the interconnecting bond wires and circuit traces. These interconnecting impedances should be minimized by using wide, short printed circuit traces. The critical components should be located as close together as possible using ground plane construction or single point grounding.

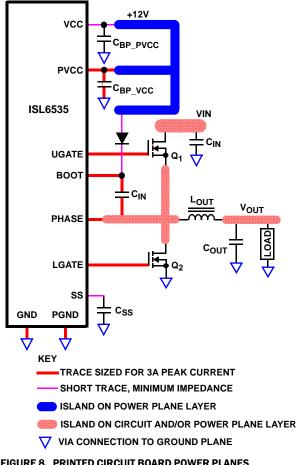

A multilayer printed circuit board is recommended. Figure 8 shows the critical components of the converter. Note that capacitors  $C_{IN}$  and  $C_{OUT}$  could each represent numerous physical capacitors. Dedicate one solid layer (usually a middle layer of the PC board) for a ground plane and make all critical component ground connections with vias to this layer. Dedicate another solid layer as a power plane and break this plane into smaller islands of common voltage levels. Keep the metal runs from the PHASE terminals to the output inductor short. The power plane should support the input power and output power nodes. Use copper filled polygons on the top and bottom circuit layers for the phase nodes. Use the remaining printed circuit layers for small signal wiring.

FIGURE 8. PRINTED CIRCUIT BOARD POWER PLANES AND ISLANDS

Locate the ISL6535 within 2 to 3 inches of the MOSFETs,  $Q_1$  and  $Q_2$  (1 inch or less for 500kHz or higher operation). The circuit traces for the MOSFETs' gate and source connections from the ISL6535 must be sized to handle up to 3A peak current. Minimize any leakage current paths on the SS pin and locate the capacitor C<sub>SS</sub> close to the SS pin as the internal current source is only 30µA. Provide local V<sub>CC</sub> decoupling between VCC and GND pins. Locate the capacitor C<sub>BOOT</sub> as close as practical to the BOOT pin and the phase node.

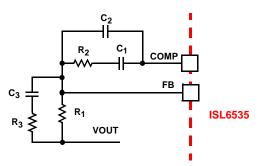

FIGURE 9. COMPENSATION CONFIGURATION FOR THE ISL6535 CIRCUIT

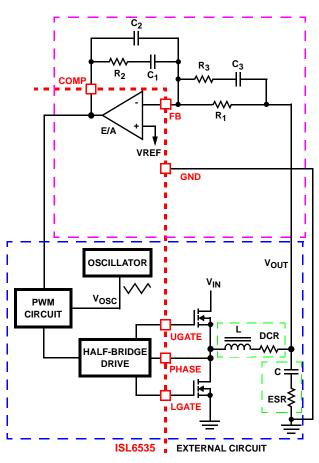

FIGURE 10. VOLTAGE-MODE BUCK CONVERTER COMPENSATION DESIGN

#### **Compensating the Converter**

The ISL6535 Single-phase converter is a voltage-mode controller. This section highlights the design consideration for a voltage-mode controller requiring external compensation. To address a broad range of applications, a type-3 feedback network is recommended (see Figure 9).

Figure 10 highlights the voltage-mode control loop for a synchronous-rectified buck converter. The output voltage is regulated to the reference voltage level. The error amplifier output is compared with the oscillator triangle wave to provide a pulse-width modulated wave with an amplitude of  $V_{IN}$  at the PHASE node. The PWM wave is smoothed by the output filter. The output filter capacitor bank's equivalent series resistance is represented by the series resistor ESR.

The modulator transfer function is the small-signal transfer function of  $V_{OUT}/V_{COMP}$ . This function is dominated by a DC gain and shaped by the output filter, with a double pole break frequency at  $F_{LC}$  and a zero at  $F_{CE}$ . For the purpose of this analysis, L and DCR represent the output inductance and its DCR, while C and ESR represents the total output capacitance and its equivalent series resistance.

$$F_{LC} = \frac{1}{2\pi \cdot \sqrt{L \cdot C}} \qquad F_{CE} = \frac{1}{2\pi \cdot C \cdot ESR}$$

(EQ. 7)

The compensation network consists of the error amplifier (internal to the ISL6535) and the external R<sub>1</sub> to R<sub>3</sub>, C<sub>1</sub> to C<sub>3</sub> components. The goal of the compensation network is to provide a closed loop transfer function with high OdB crossing frequency (F<sub>0</sub>; typically 0.1 to 0.3 of f<sub>SW</sub>) and adequate phase margin (better than 45°). Phase margin is the difference between the closed loop phase at F<sub>OdB</sub> and 180°. The equations that follow relate the compensation network's poles, zeros and gain to the components (R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub>) in Figures 9 and 10. Use the following guidelines for locating the poles and zeros of the compensation network:

1. Select a value for R<sub>1</sub> (1k $\Omega$  to 10k $\Omega$ , typically). Calculate value for R<sub>2</sub> for desired converter bandwidth (F<sub>0</sub>). If setting the output voltage to be equal to the reference set voltage, as shown in Figure 10, the design procedure can be followed as presented.

$$R_{2} = \frac{V_{OSC} \cdot R_{1} \cdot F_{0}}{D_{MAX} \cdot V_{IN} \cdot F_{LC}}$$

(EQ. 8)

As the ISL6535 supports 100% duty cycle, DMAX equals 1. The ISL6535 uses a fixed ramp amplitude ( $V_{OSC}$ ) of 1.9V, Equation 8 simplifies to Equation 9:

$$R_2 = \frac{1.9 \cdot R_1 \cdot F_0}{V_{IN} \cdot F_{LC}}$$

(EQ. 9)

2. Calculate C<sub>1</sub> such that F<sub>Z1</sub> is placed at a fraction of the F<sub>LC</sub>, at 0.1 to 0.75 of F<sub>LC</sub> (to adjust, change the 0.5 factor in <u>Equation 10</u> to the desired number). The higher the quality factor of the output filter and/or the higher the ratio F<sub>CE</sub>/F<sub>LC</sub>, the lower the F<sub>Z1</sub> frequency (to maximize phase boost at F<sub>LC</sub>).

$$C_1 = \frac{1}{2\pi \cdot R_2 \cdot 0.5 \cdot F_{LC}}$$

(EQ. 10)

3. Calculate  $C_2$  such that  $F_{P1}$  is placed at  $F_{CE}$ .

$$C_2 = \frac{C_1}{2\pi \cdot R_2 \cdot C_1 \cdot F_{CE} - 1}$$

(EQ. 11)

4. Calculate R<sub>3</sub> such that F<sub>Z2</sub> is placed at F<sub>LC</sub>. Calculate C<sub>3</sub> such that F<sub>P2</sub> is placed below f<sub>SW</sub> (typically, 0.3 to 1.0 times f<sub>SW</sub>). f<sub>SW</sub> represents the switching frequency of the regulator. Change the numerical factor (0.7) below to reflect desired placement of this pole. Placement of F<sub>P2</sub> lower in frequency helps reduce the gain of the compensation network at high frequency, in turn reducing the HF ripple component at the COMP pin and minimizing resultant duty cycle jitter.

$$R_{3} = \frac{R_{1}}{\frac{f_{SW}}{F_{LC}} - 1}$$

(EQ. 12)

$$C_{3} = \frac{1}{2\pi \cdot R_{3} \cdot 0.7 \cdot f_{SW}}$$

It is recommended that a mathematical model be used to plot the loop response. Check the loop gain against the error amplifier's open-loop gain. Verify phase margin results and adjust as necessary. The following equations describe the frequency response of the modulator ( $G_{MOD}$ ), feedback compensation ( $G_{FB}$ ) and closed-loop response ( $G_{CL}$ ):

$$\begin{split} \mathbf{G}_{\mathsf{MOD}}(f) &= \frac{\mathbf{D}_{\mathsf{MAX}} \cdot \mathbf{V}_{\mathsf{IN}}}{\mathbf{V}_{\mathsf{OSC}}} \cdot \frac{1 + \mathbf{s}(f) \cdot \mathsf{ESR} \cdot C}{1 + \mathbf{s}(f) \cdot (\mathsf{ESR} + \mathsf{DCR}) \cdot C + \mathbf{s}^2(f) \cdot \mathsf{L} \cdot C} \\ \mathbf{G}_{\mathsf{FB}}(f) &= \frac{1 + \mathbf{s}(f) \cdot \mathsf{R}_2 \cdot C_1}{\mathbf{s}(f) \cdot \mathsf{R}_1 \cdot (C_1 + C_2)} \cdot \frac{1 + \mathbf{s}(f) \cdot (\mathsf{R}_1 + \mathsf{R}_3) \cdot C_3}{(1 + \mathbf{s}(f) \cdot \mathsf{R}_3 \cdot C_3) \cdot \left(1 + \mathbf{s}(f) \cdot \mathsf{R}_2 \cdot \left(\frac{C_1 \cdot C_2}{C_1 + C_2}\right)\right)} \\ \mathbf{G}_{\mathsf{CL}}(f) &= \mathbf{G}_{\mathsf{MOD}}(f) \cdot \mathbf{G}_{\mathsf{FB}}(f) \qquad \text{where, } \mathbf{s}(f) = 2\pi \cdot f \cdot j \end{split}$$

$$(\mathsf{EQ}. 13)$$

#### **COMPENSATION BREAK FREQUENCY EQUATIONS**

$$F_{Z1} = \frac{1}{2\pi \cdot R_2 \cdot C_1} \qquad F_{P1} = \frac{1}{2\pi \cdot R_2 \cdot \frac{C_1 \cdot C_2}{C_1 + C_2}}$$

$$F_{Z2} = \frac{1}{2\pi \cdot (R_1 + R_3) \cdot C_3} \qquad F_{P2} = \frac{1}{2\pi \cdot R_3 \cdot C_3} \qquad (EQ. 14)$$

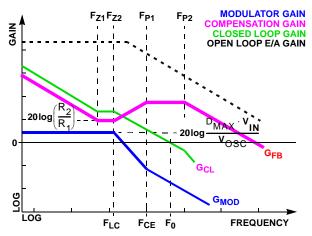

Figure 11 on page 11 shows an asymptotic plot of the DC/DC converter's gain vs frequency. The actual Modulator Gain has a high gain peak dependent on the quality factor (Q) of the output filter, which is not shown. Using the previously mentioned guidelines should yield a compensation gain similar to the curve plotted. The open loop error amplifier gain bounds the compensation gain. Check the compensation gain at Fp<sub>2</sub> against the capabilities of the error amplifier. The closed loop gain, G<sub>CL</sub>, is constructed on the log-log graph of Figure 11 by adding the modulator gain, G<sub>MOD</sub> (in dB), to the feedback compensation gain, gain, G<sub>FB</sub> (in dB). This is equivalent to multiplying the modulator transfer function and the compensation transfer function and then plotting the resulting gain.

FIGURE 11. ASYMPTOTIC BODE PLOT OF CONVERTER GAIN

A stable control loop has a gain crossing with close to a -20dB/decade slope and a phase margin greater than 45°. Include worst case component variations when determining phase margin. The mathematical model presented makes a number of approximations and is generally not accurate at frequencies approaching or exceeding half the switching frequency. When designing compensation networks, select target crossover frequencies in the range of 10% to 30% of the switching frequency, f<sub>SW</sub>.

# **Component Selection Guidelines**

#### **Output Capacitor Selection**

An output capacitor is required to filter the output and supply the load transient current. The filtering requirements are a function of the switching frequency and the ripple current. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitors and careful layout.

Modern microprocessors produce transient load rates above 1A/ns. High frequency capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR (Effective Series Resistance) and voltage rating requirements rather than actual capacitance requirements.

High frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements.

Use only specialized low-ESR capacitors intended for switching regulator applications for the bulk capacitors. The bulk capacitor's ESR will determine the output ripple voltage and the initial voltage drop after a high slew-rate transient. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes. However, the equivalent series inductance (ESL) of these capacitors increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading. Unfortunately, ESL is not a specified parameter. Work with your capacitor supplier and measure the

capacitor's impedance with frequency to select a suitable component. In most cases, multiple electrolytic capacitors of small case size perform better than a single large case capacitor.

#### **Output Inductor Selection**

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. The inductor value determines the converter's ripple current and the ripple voltage is a function of the ripple current. The ripple voltage and current are approximated by Equation 15:

$$\Delta I = \frac{V_{IN} - V_{OUT}}{F_{S \times L}} \bullet \frac{V_{OUT}}{V_{IN}} \qquad \Delta V_{OUT} = \Delta I \times ESR \qquad (EQ. 15)$$

Increasing the value of inductance reduces the ripple current and voltage. However, the large inductance values reduce the converter's response time to a load transient.

One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Given a sufficiently fast control loop design, the ISL6535 will provide either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level. During this interval the difference between the inductor current and the transient current level must be supplied by the output capacitor. Minimizing the response time can minimize the output capacitance required.

The response time to a transient load is different for the application of load and the removal of load. The following equations give the approximate response time interval for application and removal of a transient load:

$$t_{\text{RISE}} = \frac{L_{O} \times I_{\text{TRAN}}}{V_{\text{IN}} - V_{\text{OUT}}} \qquad t_{\text{FALL}} = \frac{L_{O} \times I_{\text{TRAN}}}{V_{\text{OUT}}}$$

(EQ. 16)

Where  $I_{TRAN}$  is the transient load current step,  $t_{RISE}$  is the response time to the application of load, and  $t_{FALL}$  is the response time to the removal of load. With a +5V input source, the worst case response time can be either at the application or removal of load and dependent upon the output voltage setting. Be sure to check both of these equations at the minimum and maximum output levels for the worst case response time.

#### **Input Capacitor Selection**

Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high frequency decoupling and bulk capacitors to supply the current needed each time  $Q_1$  turns on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of  $Q_1$  and the source of  $Q_2$ .

The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select a bulk capacitor with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25x greater than the maximum input voltage, a voltage rating of 1.5x greater is a conservative guideline. The RMS current rating requirement for the input capacitor of a buck regulator is approximately 1/2 the DC load current.

For a through hole design, several electrolytic capacitors (Panasonic HFQ series or Nichicon PL series or Sanyo MV-GX or equivalent) may be needed. For surface mount designs, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor surge current rating. These capacitors must be capable of handling the surge-current at power-up. The TPS series available from AVX, and the 593D series from Sprague are both surge current tested.

#### **MOSFET Selection/Considerations**

The ISL6535 requires at least two N-channel power MOSFETs. These should be selected based upon  $r_{DS(ON)}$ , gate supply requirements and thermal management requirements.

In high-current applications, the MOSFET power dissipation, package selection and heatsink are the dominant design factors. The power dissipation includes two loss components; conduction loss and switching loss. At a 300kHz switching frequency, the conduction losses are the largest component of power dissipation for both the upper and the lower MOSFETs. These losses are distributed between the two MOSFETs according to duty factor (see Equation 17). Only the upper MOSFET exhibits switching losses, since the schottky rectifier clamps the switching node before the synchronous rectifier turns on.

$$P_{UPPER} = I_O^2 \times r_{DS(ON)} \times D + \frac{1}{2} I_O \times V_{IN} \times t_{SW} \times f_{SW}$$

$$P_{LOWER} = I_O^2 \times r_{DS(ON)} \times (1 - D)$$

These equations assume linear voltage-current transitions and do not adequately model power loss due the reverse recovery of the lower MOSFETs body diode. The gate-charge losses are dissipated by the ISL6535 and don't heat the MOSFETs. However, large gate-charge increases the switching interval,  $t_{SW}$  which increases the upper MOSFET switching losses. Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal-resistance specifications. A separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air flow.

Standard-gate MOSFETs are normally recommended for use with the ISL6535. However, logic-level gate MOSFETs can be used under special circumstances. The input voltage, upper gate drive level, and the MOSFETs absolute gate-to-source voltage rating determine whether logic-level MOSFETs are appropriate.

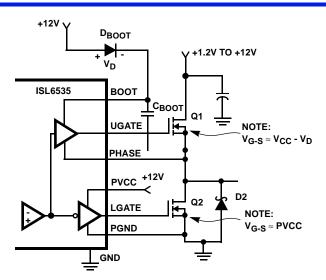

Figure 12 shows the upper gate drive (BOOT pin) supplied by a bootstrap circuit from +12V. The boot capacitor,  $C_{BOOT}$  develops a floating supply voltage referenced to the PHASE pin. This supply is refreshed each cycle to a voltage of +12V less the boot diode drop (V<sub>D</sub>) when the lower MOSFET, Q<sub>2</sub> turns on. A MOSFET can only be used for Q<sub>1</sub> if the MOSFETs absolute gate-to-source voltage rating exceeds the maximum voltage applied to +12V. For Q<sub>2</sub>, a logic-level MOSFET can be used if its absolute gate-to-source voltage rating also exceeds the maximum voltage applied to +12V.

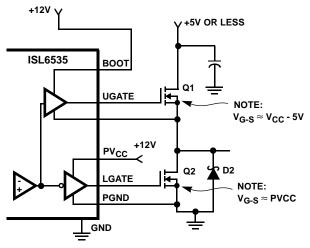

Figure 13 shows the upper gate drive supplied by a direct connection to +12V. This option should only be used in converter systems where the main input voltage is +5 V DC or less. The peak upper gate-to-source voltage is approximately +12V less the input supply. For +5V main power and +12V DC for the bias, the gate-to-source voltage of  $Q_1$  is 7V. A logic-level MOSFET is a good choice for  $Q_1$  and a logic-level MOSFET can be used for  $Q_2$  if its absolute gate-to-source voltage rating exceeds the maximum voltage applied to PVCC. This method reduces the number of required external components, but does not provide for immunity to phase node ringing during turn on and may result in lower system efficiency.

FIGURE 13. UPPER GATE DRIVE - DIRECT VCC DRIVE OPTION

#### **Schottky Selection**

Rectifier  $D_2$  is a clamp that catches the negative inductor swing during the dead time between turning off the lower MOSFET and turning on the upper MOSFET. The diode must be a Schottky type to prevent the lossy parasitic MOSFET body diode from conducting. It is acceptable to omit the diode and let the body diode of the lower MOSFET clamp the negative inductor swing, but efficiency could slightly decrease as a result. The diode's rated reverse breakdown voltage must be greater than the maximum input voltage.

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE            | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 4, 2021 | FN9255.4 | Updated Block Diagram mA units to µA.<br>Updated Absolute Maximum Ratings, added: OCSET Voltage, V <sub>OCSET</sub> .<br>Updated Overcurrent Protection: corrected from 30mA current sink to 30µA current sink.                                                                                                                                                                                                                                          |

| March 3, 2016   | FN9255.3 | Applied Intersil's new standards throughout datasheet.         Updated QFN Pin Configuration on page 1 by adding the word "PAD".         Updated "Pin Descriptions" on page 2 by adding EPAD.         Updated Note 1 to include tape and reel units.         Added Notes 2 and 3.         Added the UGATE Voltage and LGATE Voltage information to the "Absolute Maximum Ratings" on page 5.         Added Revision History and About Intersil sections. |

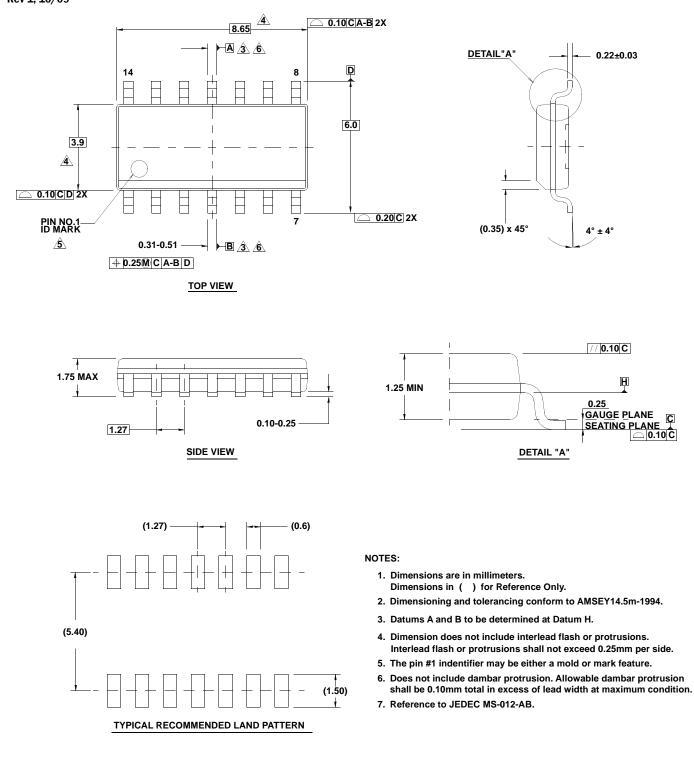

# **Package Outline Drawing**

M14.15

14 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE Rev 1, 10/09

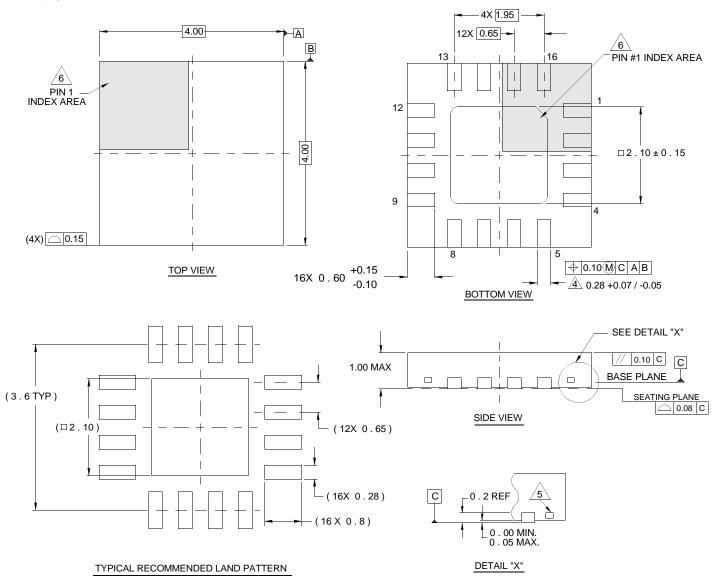

# **Package Outline Drawing**

L16.4x4

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 6, 02/08

NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Renesas manufacturer:

Other Similar products are found below :

AZ7500EP-E1 NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP6153MNTWG NCP81101BMNTXG NCP81205MNTXG SJE6600 SMBV1061LT1G SG3845DM NCP4204MNTXG NCP6132AMNR2G NCP81102MNTXG NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UBA2051C MAX8778ETJ+ NTBV30N20T4G NCP1015ST65T3G NCP1240AD065R2G NCP1240FD065R2G NCP1361BABAYSNT1G NCP1230P100G NCP1612BDR2G NX2124CSTR SG2845M NCP81101MNTXG TEA19362T/1J IFX81481ELV NCP81174NMNTXG NCP4308DMTTWG NCP4308DMNTWG NCP4308AMTTWG NCP1251FSN65T1G NCP1246BLD065R2G NTE7154 NTE7242 LTC7852IUFD-1#PBF LTC7852EUFD-1#PBF MB39A136PFT-G-BND-ERE1 NCP1256BSN100T1G LV5768V-A-TLM-E NCP1365BABCYDR2G NCP1365AABCYDR2G MCP1633T-E/MG MCP1633-E/MG NCV1397ADR2G NCP1246ALD065R2G